Vishay SST5198NL, SST5199NL, U5196NL, U5197NL, U5198NL Schematic [ru]

...

SST/U5196NL Series

New Product

Vishay Siliconix

Monolithic N-Channel JFET Duals

SST5198NL

SST5199NL

PRODUCT SUMMARY

Part Number V

U5196NL -0.7 to -4 -50 1 -15 5

U5197NL -0.7 to -4 -50 1 -15 5

SST/U5198NL -0.7 to -4 -50 1 -15 10

SST/U5199NL -0.7 to -4 -50 1 -15 15

FEATURES BENEFITS APPLICATIONS

D Anti Latchup Capability

D Monolithic Design

D High Slew Rate

D Low Offset/Drift Voltage

D Low Gate Leakage: 5 pA

D Low Noise

D High CMRR: 100 dB

GS(off)

(V) V

(BR)GSS

Min (V) gfs Min (mS) IG Max (pA) V

D External Substrate Bias—Avoids Latchup

D Tight Differential Match vs. Current

D Improved Op Amp Speed, Settling Time Accuracy

D Minimum Input Error/Trimming Requirement

D Insignificant Signal Loss/Error Voltage

D High System Sensitivity

D Minimum Error with Large Input Signal

U5196NL

U5197NL

- V

GS1

D Wideband Differential Amps

D High-Speed, Temp-Compensated,

D High Speed Comparators

D Impedance Converters

Max (mV)

GS2

Single-Ended Input Amps

U5198NL

U5199NL

DESCRIPTION

The SST/U5196NL series of JFET duals are designed for

high-performance differential amplification for a wide range of

precision test instrumentation applications. This series

features tightly matched specs, low gate leakage for accuracy,

and wide dynamic range with IG guaranteed at VDG = 20 V.

Pins 4 and 8 of the SST series and pin 4 on the U series part

numbers enable the substrate to be connected to a positive,

external bias (V

SUBSTRATE S

) to avoid latchup.

DD

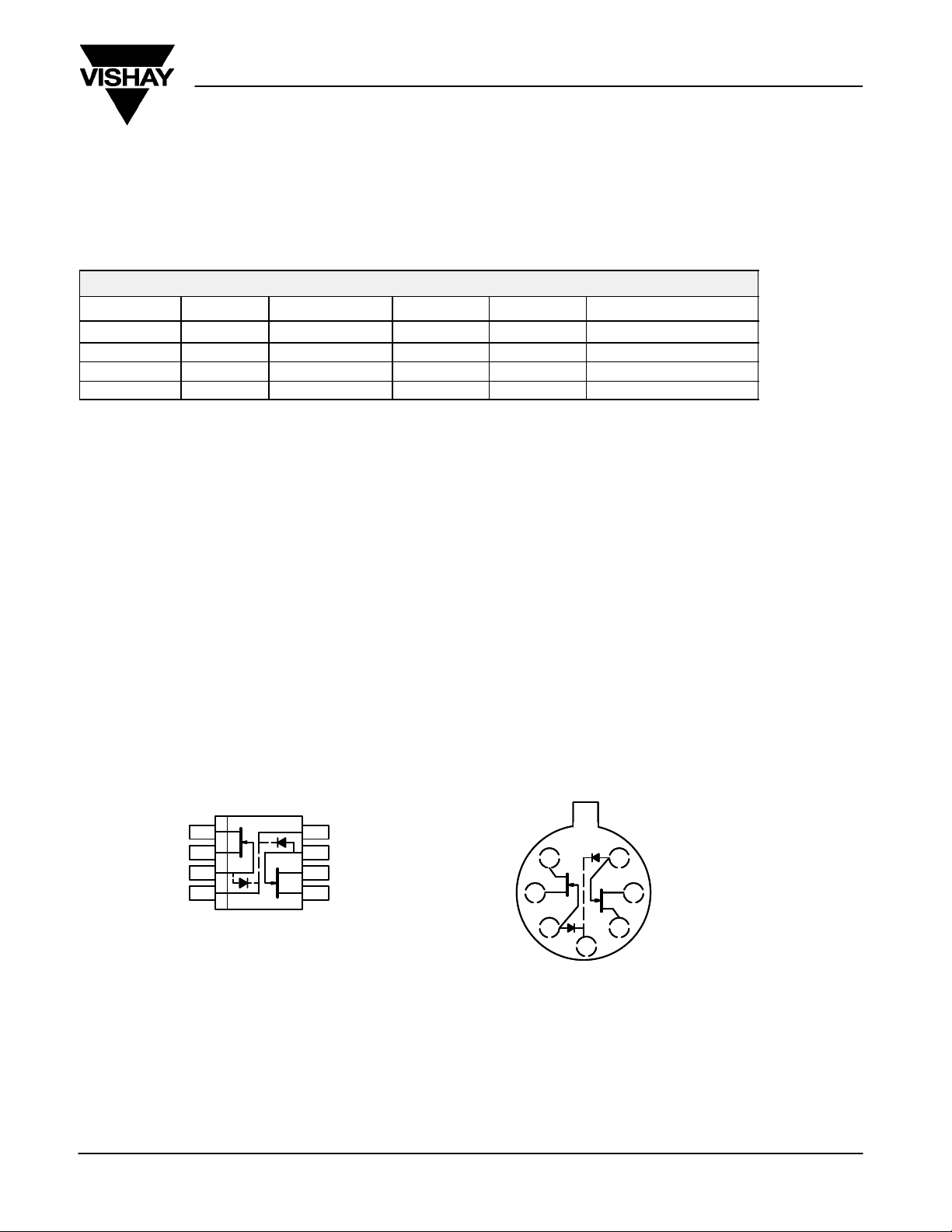

Narrow Body SOIC

S

1

1

D

2

1

G

3

1

4

Marking Codes:

SST5198NL - 5198NL

SST5199NL - 5199NL

Top View

8

7

6

5

SUBSTRATE

G

2

D

2

2

ABSOLUTE MAXIMUM RATINGS

Gate-Drain, Gate-Source Voltage -50 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Gate Current 50 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead Temperature (1/16” from case for 10 sec.) 300 _C. . . . . . . . . . . . . . . . . .

Storage Temperature -65 to 200_C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating Junction Temperature -55 to 150_C. . . . . . . . . . . . . . . . . . . . . . . . . .

The U series in the hermetically-sealed TO-78 package is

available with full military processing. The SST series SO-8

package provides ease of manufacturing and the symmetrical

pinout prevents improper orientation. The SO-8 package is

available with tape-and-reel options for compatibility with

automatic assembly methods.

For similar products see the low-noise SST/U401NL series

and the low-leakage U421NL/423NL data sheets.

TO-78

TO-78

S

S

1

1

1

1

D

D

1

1

2

2

3

3

G

G

1

1

Power Dissipation : Per Side

Notes

a. Derate 2 mW/_C above 85_C

b. Derate 4 mW/_C above 85_C

4

4

CASE, SUBSTRATE

CASE, SUBSTRATE

Top View

U5196NL, U5198NL

U5197NL, U5199NL

G

G

2

2

7

7

D

D

2

2

6

6

5

5

S

S

2

2

Total

a

b

250 mW. . . . . . . . . . . . . . . . . . . . . . . .

500 mW. . . . . . . . . . . . . . . . . . . . . . . . . . .

Document Number: 72156

S-03468—Rev. B, 11-Mar-03

www.vishay.com

7-1

SST/U5196NL Series

VDS = 20 V, VGS = 0 V

S

VDS = 20 V, ID = 200 A

VDS = 20 V, VGS = 0 V

S

VDS = 20 V, ID = 200 A

Vishay Siliconix

New Product

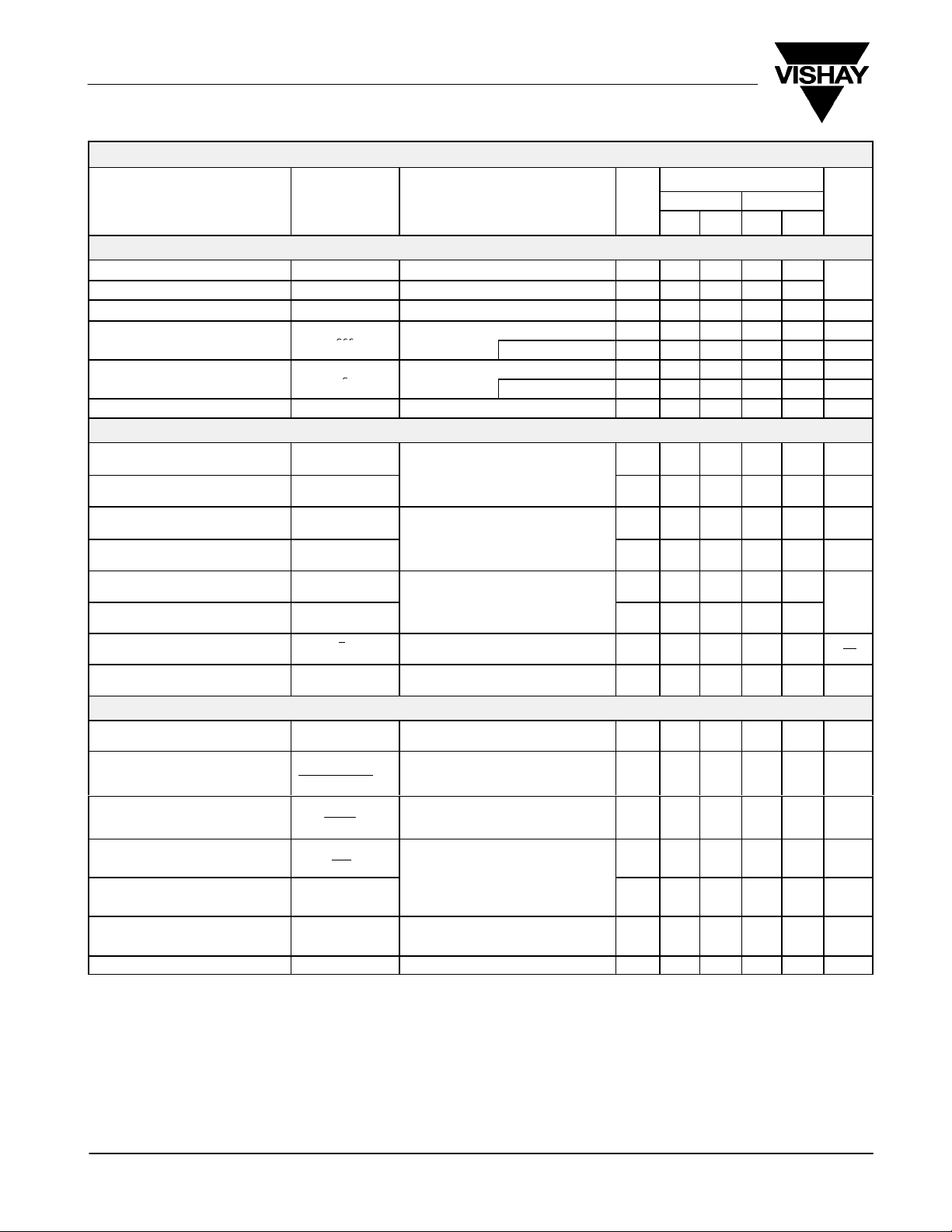

SPECIFICATIONS FOR U5196NL AND U5197NL (TA = 25_C UNLESS OTHERWISE NOTED)

Limits

U5196NL U5197NL

Parameter Symbol Test Conditions TypaMin Max Min Max Unit

Static

Gate-Source Breakdown Voltage V

Gate-Source Cutoff Voltage V

Saturation Drain Current

Gate Reverse Current I

Gate Operating Current I

Gate-Source Voltage V

b

(BR)GSS

GS(off)

I

DSS

GSS

Dynamic

Common-Source

Forward Transconductance

Common-Source

Output Conductance

Common-Source

Forward Transconductance

Common-Source

Output Conductance

Common-Source

Input Capacitance

Common-Source

Reverse Transfer Capacitance

Equivalent Input Noise Voltage e

Noise Figure NF

g

g

g

g

C

C

Matching

Differential Gate-Source Voltage

Gate-Source Voltage Differential

Change with Temperature

Saturation Drain Current Ratio

Transconductance Ratio

Differential Output Conductance

|

V

GS1–VGS2

|

V

GS1–VGS2

|

g

os1–gos2

T

I

DSS1

I

DSS2

g

g

fs1

fs2

GS

IG = -1 A, VDS = 0 V

VDS = 20 V, ID = 1 nA -2 -0.7 -4 -0.7 -4

VDS = 20 V, VGS = 0 V 3 0.7

VGS = -30 V, VDS = 0 V -10 -25 -25 pA

TA = 150_C

G

fs

os

fs

os

iss

rss

n

|

|

|

VDG = 20 V, ID = 200 A

TA = 125_C

VDG = 20 V, ID = 200 A

VDS = 20 V, VGS = 0 V

f = 1 kHz

V

= 20 V, ID = 200 A

D

f = 1 kHz

VDS = 20 V, VGS = 0 V

f = 1 MHz

VDS = 20 V, VGS = 0 V, f = 1 kHz 11 20 20

VDS = 20 V, VGS = 0 V

f = 100 Hz, R

VDG = 20 V, ID = 200 A

VDG = 20 V, ID = 200 A

T

A

VDS = 20 V, VGS = 0 V 0.98 0.95 1 0.95 1

V

= 20 V, ID = 200 A

D

= 10 M

G

= -55 to 125_C

f = 1 kHz

-57 -50 -50

0.7

7

-20 -50 -50 nA

-5 -15 -15 pA

-0.8 -15 -15 nA

-1.5 -0.2 -3.8 -0.2 -3.8 V

3.0 1 4 1 4 mS

8 50 50

0.8 0.7 1.6 0.7 1.6 mS

1 4 4

3 6 6

1 2 2

0.5 0.5 dB

5 5 mV

5 10

0.99 0.97 1 0.97 1

0.1 1 1

7

V

mA

S

S

pF

nV⁄

√Hz

V/_C

S

Differential Gate Current

Common Mode Rejection Ratio CMRR

www.vishay.com

7-2

|

|

I

* I

G1

G2

VDG = 20 V, ID = 200 A , TA = 125_C

VDG = 10 to 20 V, ID = 200 A

0.1 5 5 nA

100 dB

Document Number: 72156

S-03468—Rev. B, 11-Mar-03

SST/U5196NL Series

S

VDS = 20 V, ID = 200 A

g

Change with Temperature

TA = -55 to 125_C

I

DSS1

g

S

S

VDS = 20 V, ID = 200 A

G

VDG = 20 V, ID = 200 A

New Product

Vishay Siliconix

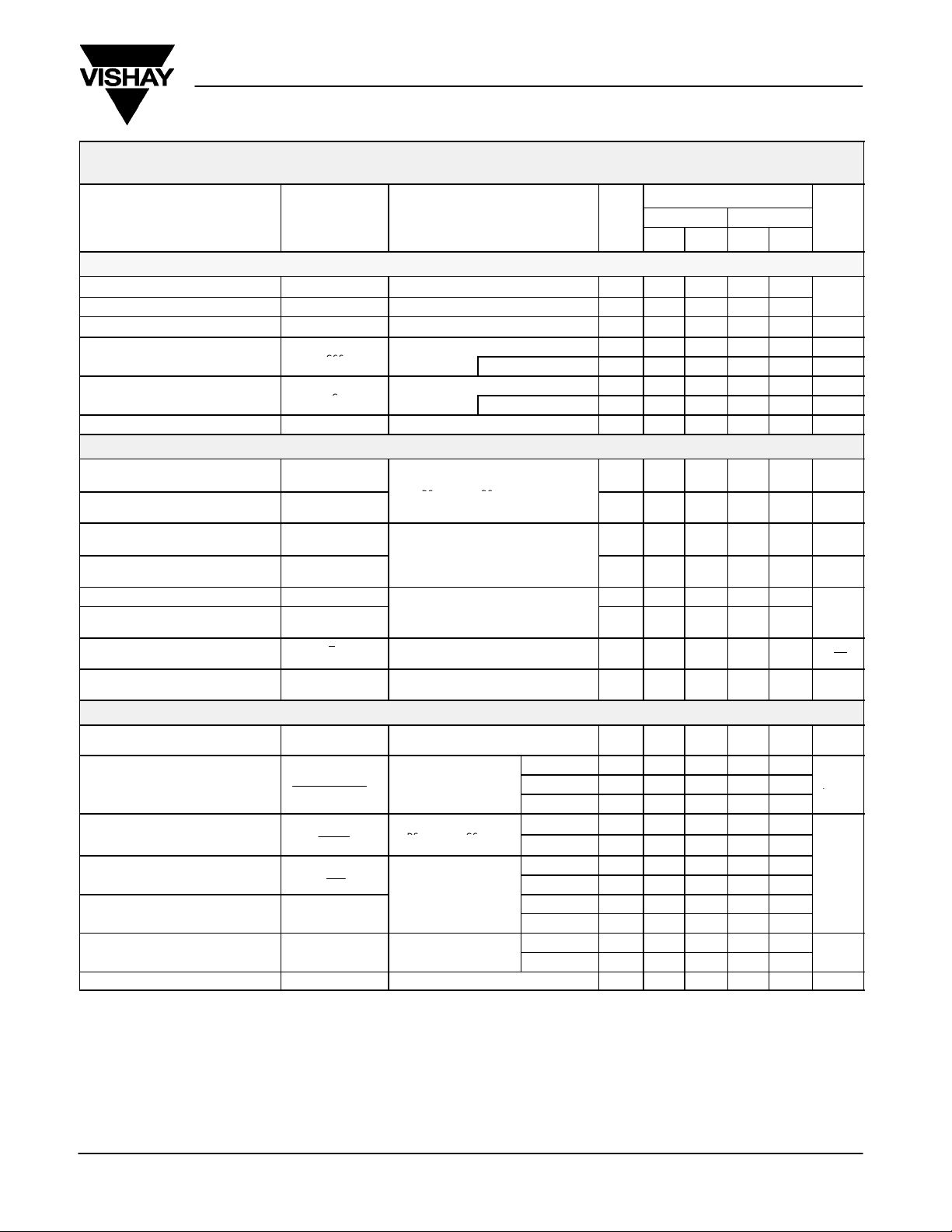

SPECIFICATIONS FOR SST/U5198NL AND SST/U5199NL

(TA = 25_C UNLESS OTHERWISE NOTED)

Limits

SST/U5198NL SST/U5199NL

Parameter Symbol Test Conditions TypaMin Max Min Max Unit

Static

Gate-Source Breakdown Voltage V

Gate-Source Cutoff Voltage V

Saturation Drain Current

Gate Reverse Current I

Gate Operating Current I

Gate-Source Voltage V

b

(BR)GSS

GS(off)

I

DSS

GSS

G

GS

IG = -1 A, VDS = 0 V

VDS = 20 V, ID = 1 nA -2 -0.7 -4 -0.7 -4

VDS = 20 V, VGS = 0 V 3 0.7

VGS = -30 V, VDS = 0 V -10 -25 -25 pA

TA = 150_C

VDG = 20 V, ID = 200 A

TA =125_C

VDG = 20 V, ID = 200 A

Dynamic

Common-Source

Forward Transconductance

Common-Source

Output Conductance

Common-Source

Forward Transconductance

Common-Source

Output Conductance

Common-Source Input Capacitance C

Common-Source

Reverse Transfer Capacitance

Equivalent Input Noise Voltage e

Noise Figure NF

g

fs

g

os

g

fs

g

os

iss

C

rss

n

VDS = 20 V, VGS = 0 V, f = 1 kHz

V

= 20 V, ID = 200 A

D

f = 1 kHz

VDS = 20 V, VGS = 0 V, f = 1 MHz

VDS = 20 V, VGS = 0 V, f = 1 kHz 11

VDS = 20 V, VGS = 0 V

f = 100 Hz, R

= 10 M (U Only)

G

Matching

Differential Gate-Source Voltage

Gate-Source Voltage Differential

e with Temperature

Chan

Saturation Drain Current Ratio

Transconductance Ratio

Differential Output Conductance

Differential Gate Current

Common Mode Rejection Ratio CMRR

Notes

a. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing. NQP

b. Pulse test: PW v300 s duty cycle v3%.

|

V

GS1–VGS2

|

V

GS1–VGS2

|

g

|

I

T

I

I

DSS2

g

fs1

g

fs2

os1–gos2

* I

G1

G2

|

|

VDG = 20 V, ID = 200 A

T

= -55 to 125_C

VDS = 20 V, VGS = 0 V

V

= 20 V, ID = 200 A

D

|

V

= 20 V, ID = 200 A,

D

|

VDG = 10 to 20 V, ID = 200 A

VDG = 20 V, ID = 200 A

f = 1 kHz

T

= 125_C

A

,

SST5198NL 15

SST5199NL 30

U Only 20 40

SST Only 0.97

U Only 0.95 1 0.95 1

SST Only 0.97

U Only 0.95 1 0.95 1

SST Only 0.2

U Only 1 1

SST Only 0.1

U Only 5 5

-57 -50 -50

0.7

7

-20 -50 -50 nA

-5 -15 -15 pA

-0.8 -15 -15 nA

-1.5 -0.2 -3.8 -0.2 -3.8 V

3.0 1 4 1 4 mS

8 50 50

0.8 0.7 1.6 0.7 1.6 mS

1 4 4

3 6 6

1 2 2

0.5 dB

10 15 mV

97 dB

mA

7

nV⁄

√Hz

V/_C

V

S

S

pF

nA

Document Number: 72156

S-03468—Rev. B, 11-Mar-03

www.vishay.com

7-3

Loading...

Loading...