GMF05LC-HS3

Vishay Semiconductors

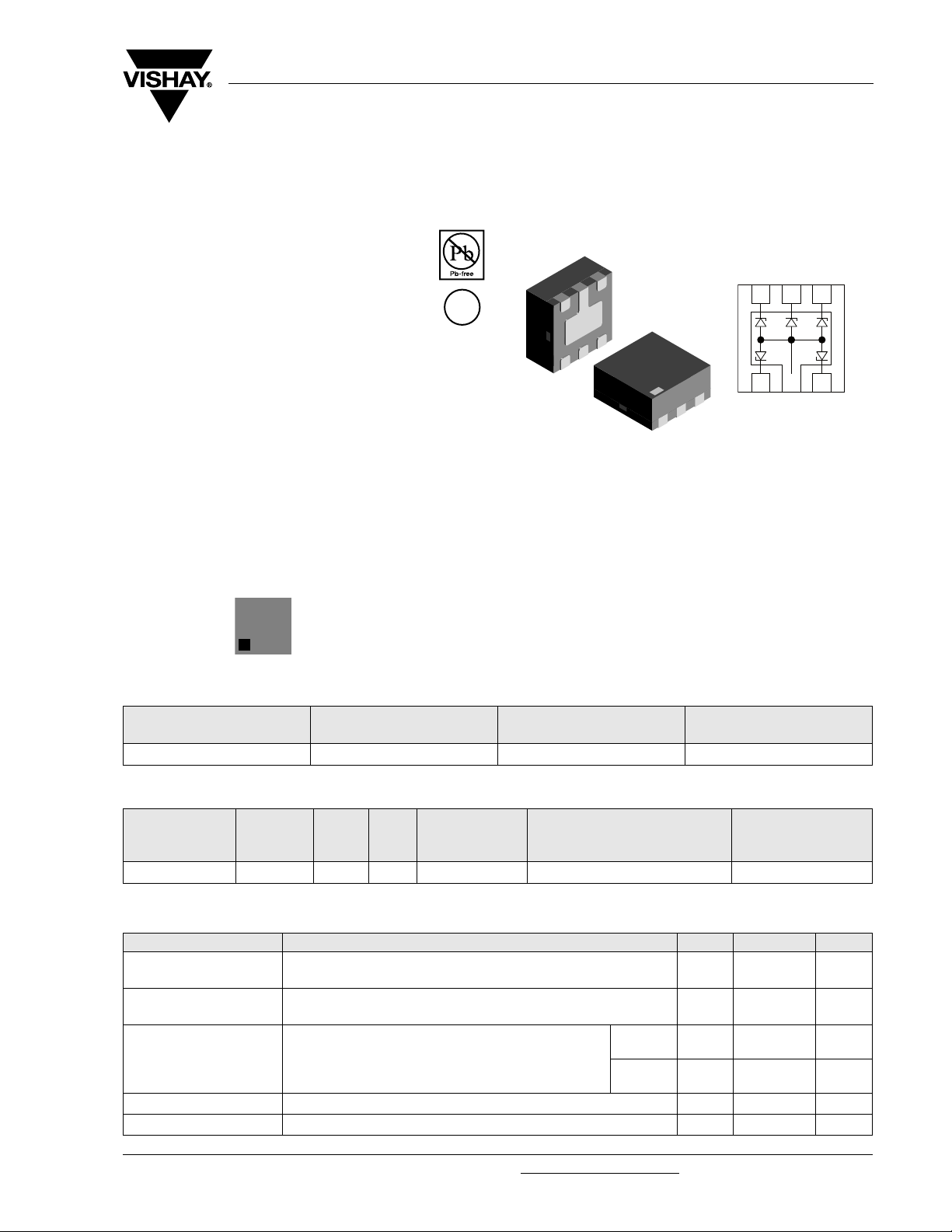

5-Line ESD-Protection Diode Array in LLP75-6A

Features

• Ultra compact LLP75-6A package

• 5-line ESD-protection

• Low leakage current I

• Low load capacitance of typ. 43 pF at

V

= 0 V

R

• ESD-immunity acc. IEC 61000-4-2

± 30 kV contact discharge

± 30 kV air discharge

• Working voltage range V

• Lead (Pb)-free component

• "Green" molding compound

• Nonmagnetic

• Component in accordance to RoHS 2002/95/EC

and WEEE 2002/96/EC

< 0.1 µA

R

RWM

= 5 V

e3

19957

1

6

1

54

2

3

19956

Marking (example only)

XX

YY

21001

dot = Pin 1 marking

XX = Date code

YY = Type code (see table below)

Ordering Information

Device name Ordering code

GMF05LC-HS3 GMF05LC-HS3-GS08 3000 15000

Taped units per reel

(8 mm tape on 7" reel)

Minimum order quantity

Package Data

Device name

GMF05LC-HS3 LLP75-6A F6 5.1 mg UL 94 V-0 MSL level 1 (according J-STD-020) 260 °C/10 s at terminals

Package

name

Type

code

Weight

Molding

compound

flammability rating

Moisture sensitivity level Soldering conditions

Absolute Maximum Ratings

Rating Test condition Symbol Valu e Unit

Peak pulse current

Peak pulse power

ESD-immunity

Operating temperature junction temperature

Storage temperature

BiAs-mode: each input (pin 1; 3 - pin 6) to ground (pin 2);

acc. IEC 61000-4-5; t

BiAs-mode: each input (pin 1; 3 - pin 6) to ground (pin 2);

acc. IEC 61000-4-5; t

acc. IEC61000-4-2; 10 pulses

BiAs-mode: each input (pin 1; 3 - pin 6) to ground (pin 2)

= 8/20 µs; single shot

p

= 8/20 µs; single shot

p

contact

discharge

air

discharge

I

P

V

V

T

PPM

PP

ESD

ESD

T

- 55 to + 125 °C

J

- 55 to + 150 °C

STG

5A

70 W

± 30 kV

± 30 kV

Document Number 85655

Rev. 1.6, 12-Mar-08

For technical support, please contact: ESD-Protection@vishay.com

www.vishay.com

1

GMF05LC-HS3

Vishay Semiconductors

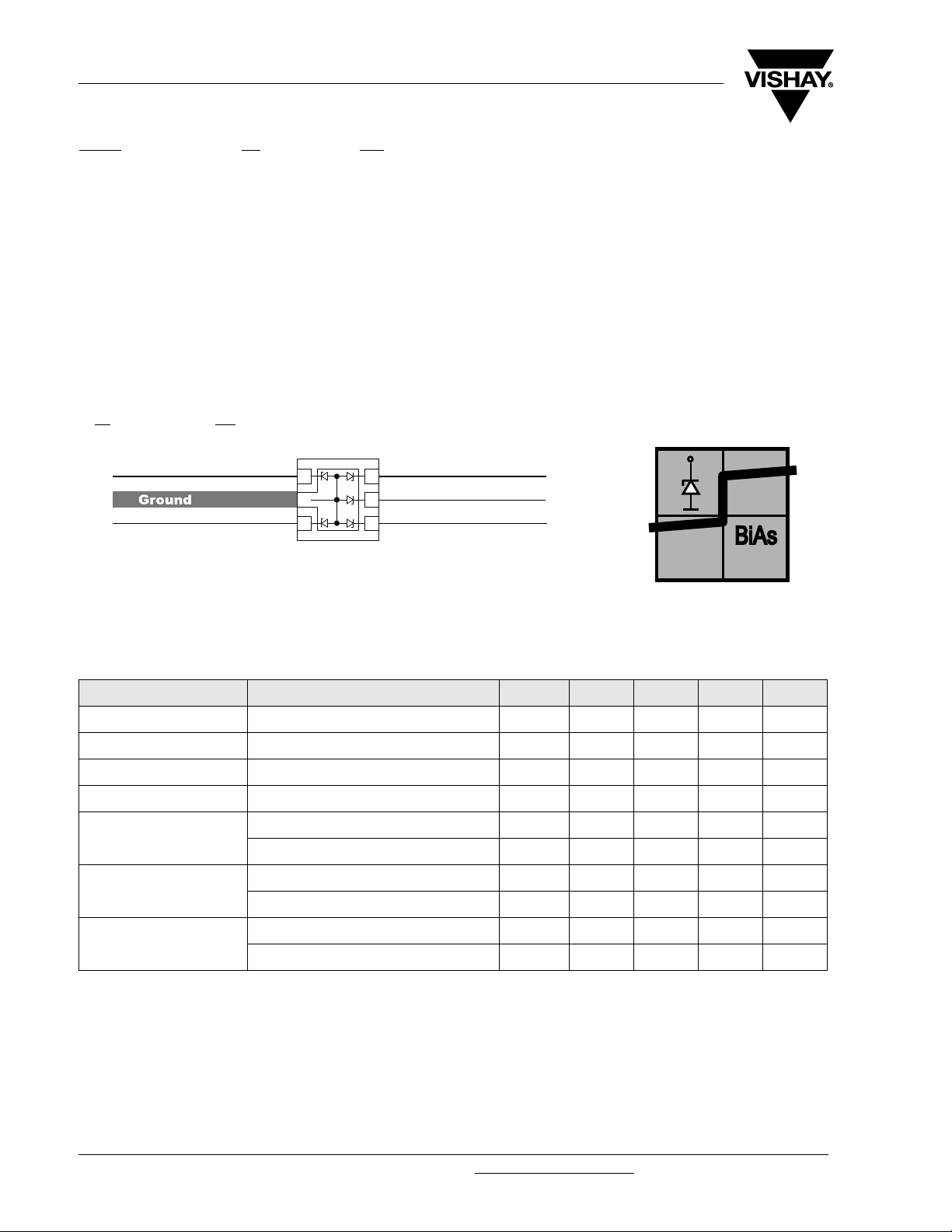

BiAs-Mode (5-line Bidirectional Asymmetrical protection mode)

With the GMF05LC-HS3 up to 5 signal- or data-lines (L1 - L5) can be protected against voltage transients.

With pin 2 connected to ground and pin 1; 3 up tp pin 6 connected to a signal- or data-line which has to be

protected. As long as the voltage level on the data- or signal-line is between 0 V (ground level) and the specified

Maximum Reverse Working Voltage (V

isolation to the ground line. The protection device behaves like an open switch.

As soon as any positive transient voltage signal exceeds the break through voltage level of the protection

diode, the diode becomes conductive and shorts the transient current to ground. Now the protection device

behaves like a closed switch. The Clamping Voltage (V

plus the voltage drop at the series impedance (resistance and inductance) of the protection device.

Any negative transient signal will be clamped accordingly. The negative transient current is flowing in the forward direction of the protection diode. The low Forward Voltage (V

ground level.

Due to the different clamping levels in forward and reverse direction the GMF05LC-HS3 clamping behaviour

is Bi

directional and Asymmetrical (BiAs).

) the protection diode between data line and ground offer a high

RWM

) is defined by the BReakthrough Voltage (VBR) level

C

) clamps the negative transient close to the

F

L5

L4

L3

20739

L1

L2

1

2

3

5

4

3

Electrical Characteristics

Ratings at 25 °C ambient temperature, unless otherwise specified

GMF05LC-HS3

BiAs mode: each input (pin 1, 3, 4, 5, 6) to ground (pin 2)

Parameter Test conditions/remarks Symbol Min. Typ . Max. Unit

Protection paths number of line which can be protected N lines 5 lines

at I

Reverse stand-off voltage

Reverse current

Reverse breakdown voltage

Reverse clamping voltage

Forward clamping voltage

Line capacitance

at I

at I

= 1 A; acc. IEC 61000-4-5 V

at I

PP

= I

PP

PPM

= 1 A; acc. IEC 61000-4-5 V

at I

F

= I

PP

PPM

at V

at V

= 1 µA V

R

= V

at V

R

at I

= 5 A; acc. IEC 61000-4-5 V

= 5 A; acc. IEC 61000-4-5 V

= 0 V; f = 1 MHz C

R

= 2.5 V; f = 1 MHz C

R

= 5 V I

RWM

= 1 mA V

R

RWM

R

BR

C

C

F

F

D

D

5V

0.01 0.1 µA

68V

89.5V

11.5 12.5 V

1.5 2 V

3.1 4 V

43 50 pF

25 pF

If a higher surge current or Peak Pulse current (IPP) is needed, some protection diodes in the GMF05LC-HS3

can also be used in parallel in order to "multiply" the performance.

If two diodes are switched in parallel you get

• double surge power = double peak pulse current (2 x I

PPM

)

• half of the line inductance = reduced clamping voltage

• half of the line resistance = reduced clamping voltage

www.vishay.com

2

• double line Capacitance (2 x C

• double Reverse leakage current (2 x I

For technical support, please contact: ESD-Protection@vishay.com

)

D

)

R

Document Number 85655

Rev. 1.6, 12-Mar-08

GMF05LC-HS3

Vishay Semiconductors

L1 L2

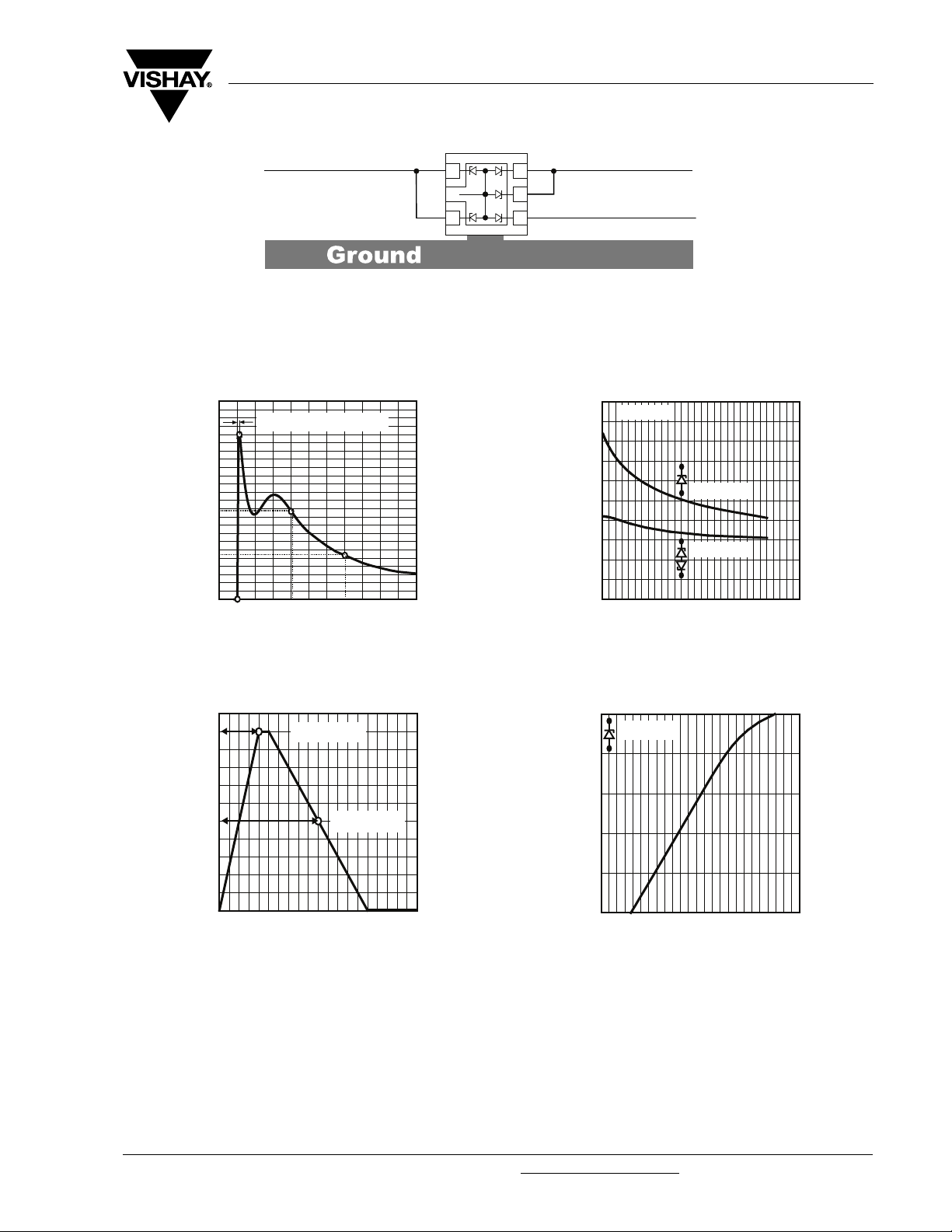

Typical Characteristics

T

= 25 °C, unless otherwise specified

amb

120 %

100 %

ESD

80 %

60 %

53 %

40 %

27 %

Discharge Current I

20 %

0 %

- 10 0 10 20 30 40 50 60 70 80 90 100

20557

Figure 1. ESD Discharge Current Wave Form

acc. IEC 61000-4-2 (330 Ω/150 pF)

rise time = 0.7 ns to 1 ns

Time (ns)

1

2

3

6

5

f = 1MHz

L3

20740

BiAs-mode

BiSy-mode

VR in V

20281

4

50

45

40

35

30

in pF

25

D

C

20

15

10

5

0

0123456

Figure 3. Typical Capacitance CD vs. Reverse Voltage V

R

8 µs to 100 %

20 µs to 50 %

Time (µs)

I

100 %

80 %

60 %

PPM

40 %

20 %

0 %

010203040

20548

Figure 2. 8/20 µs Peak Pulse Current Wave Form

acc. IEC 61000-4-5

100

BiAs-mode

10

1

(mA)

F

I

0.1

0.01

0.001

20282

0.5 0.6 0.7 0.8 0.9 1

VF (V)

Figure 4. Typical Forward Current IF vs. Forward Voltage V

F

Document Number 85655

Rev. 1.6, 12-Mar-08

For technical support, please contact: ESD-Protection@vishay.com

www.vishay.com

3

GMF05LC-HS3

Vishay Semiconductors

10

9

8

7

6

5

(V)

R

V

4

3

2

1

0

0.01 0.1 1 10 100 1000 10000

20283

BiSy-mode

BiAs-mode

IR (µA)

Figure 5. Typical Reverse Voltage VR vs.

20284

Reverse Current I

16

14

12

10

8

(V)

C

V

6

V

C

4

2

Measured acc. IEC 61000-4-5 (8/20µs - wave form)

0

0123456

R

BiSy-mode

BiAs-mode

IPP (A)

Figure 6. Typical Peak Clamping Voltage VC vs.

Peak Pulse Current I

PP

60

40

20

0

(V)

C-ESD

- 20

V

- 40

- 60

- 80

- 10 0 10 20 30 40 50 60 70 8090

21106

acc. IEC 61000-4-2

- 8 kV

contact discharge

t (ns)

Figure 8. Typical Clamping performance at - 8 kV

Contact Discharge (acc. IEC 61000-4-2)

300

acc. IEC 61000-4-2 contact discharge

200

positive discharge

100

(V)

C-ESD

V

21107

0

- 100

negative discharge

- 200

- 300

0 5 10 15 20 25 30

V

ESD

(kV)

V

C-ESD

Figure 9. Typical Peak Clamping Voltage at ESD

Contact Discharge (acc. IEC 61000-4-2)

80

acc. IEC 61000-4-2

60

40

20

(V)

C-ESD

0

V

- 20

- 40

- 60

- 10 0 10 20 30 40 50 60 70 8090

21105

+ 8 kV

contact discharge

t (ns)

Figure 7. Typical Clamping Performance at + 8 kV

Contact Discharge (acc. IEC 61000-4-2)

www.vishay.com

For technical support, please contact: ESD-Protection@vishay.com

4

Document Number 85655

Rev. 1.6, 12-Mar-08

Package Dimensions in millimeters (inches): LLP75-6A

GMF05LC-HS3

Vishay Semiconductors

18058

Document Number 85655

Rev. 1.6, 12-Mar-08

For technical support, please contact: ESD-Protection@vishay.com

www.vishay.com

5

GMF05LC-HS3

Vishay Semiconductors

Ozone Depleting Substances Policy Statement

It is the policy of Vishay Semiconductor GmbH to

1. Meet all present and future national and international statutory requirements.

2. Regularly and continuously improve the performance of our products, processes, distribution and operating

systems with respect to their impact on the health and safety of our employees and the public, as well as

their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are

known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs

and forbid their use within the next ten years. Various national and international initiatives are pressing for an

earlier ban on these substances.

Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use

of ODSs listed in the following documents.

1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments

respectively.

2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental

Protection Agency (EPA) in the USA.

3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting

substances and do not contain such substances.

We reserve the right to make changes to improve technical design

and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer

application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or

unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages,

and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated

with such unintended or unauthorized use.

Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany

www.vishay.com

6

For technical support, please contact: ESD-Protection@vishay.com

Document Number 85655

Rev. 1.6, 12-Mar-08

Legal Disclaimer Notice

Vishay

Notice

Specifications of the products displayed herein are subject to change without notice. Vishay Intertechnology, Inc.,

or anyone on its behalf, assumes no responsibility or liability for any errors or inaccuracies.

Information contained herein is intended to provide a product description only. No license, express or implied, by

estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Vishay's

terms and conditions of sale for such products, Vishay assumes no liability whatsoever, and disclaims any express

or implied warranty, relating to sale and/or use of Vishay products including liability or warranties relating to fitness

for a particular purpose, merchantability, or infringement of any patent, copyright, or other intellectual property right.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications.

Customers using or selling these products for use in such applications do so at their own risk and agree to fully

indemnify Vishay for any damages resulting from such improper use or sale.

Document Number: 91000 www.vishay.com

Revision: 08-Apr-05 1

Loading...

Loading...