VIA Technologies VX800 Series, VX820 Series, VX820UT, VX820, VX800UT Programming Manual

...Page 1

System

Programming

Manual

.

nc

I

s

e

VX800 / VX820

i

l

og

Series

i

a

d

e

nol

nt

r

h

c

e

de

i

qui

e

T

I

A

onf

C

R

A

V

D

N

Preliminary Revision 0.95

June 20, 2008

VIA TECHNOLOGIES, INC.

Page 2

Copyright Notice:

Copyright © 2007-2008 VIA Technologies Incorporated. All Rights Reserved. No part of this document may be reproduced, transmitted,

transcribed, stored in a retrieval system or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical,

chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated. The material in this document is for

information only and is subject to change without notice. VIA Technologies Incorporated reserves the right to make changes in the product design

without reservation and without notice to its users.

Trademark Notices:

VX800 and VX820 may only be used to identify products of VIA Technologies.

Windows Vista

Microsoft Corp.

Memory Stick

Memory Stick Pro

MultiMediaCard

TM

is a trademark of Motorola Incorporated.

SPI

AGP™ is a trademark of the AGP Implementors Forum.

PCI™ is a trademark of the PCI Special Interest Group.

PS/2™ is a trademark of International Business Machines Corp.

All trademarks are the properties of their respective owners.

TM

, Windows XP™, Windows 2000™, Windows ME™, Windows 98™, VMR™ and Plug and Play™ are registered trademarks of

TM

is a registered trademark of Sony Corporation.

TM

is a trademark of Sony Corporation.

TM

is a trademark of MultiMediaCard Association.

.

Disclaimer Notice:

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies, Inc. VIA Technologies makes no warranties,

implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is

believed to be accurate and reliable as of the publication date of this document. However, VIA Technologies assumes no responsibility for any

errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for

any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject

to change at any time, without notice and without obligation to notify any person of such change.

s

e

i

nc

I

l

Offices:

VIA Technologies Incorporated

USA Office:

940 Mission Court

Fremont, CA 94539

USA

Tel: (510) 683-3300

Fax: (510) 683-3301 or (510) 687-4654

Home Page:

http://www.viatech.com

VIA Technologies Incorporated

Taiwan Office:

st

Floor, No. 531

1

Chung-Cheng Road, Hsin-Tien

Taipei, Taiwan ROC

Tel: (886-2) 2218-5452

Fax: (886-2) 2218-5453

c

Home page:

e

nol

h

http://www.via.com.tw

og

de

i

i

nt

qui

e

a

d

e

r

T

V

I

A

onf

C

D

R

A

N

Page 3

VX800 / VX820 Series System Programming Manual

TABLE OF CONTENTS

TABLE OF CONTENTS....................................................................................................................................................................I

LIST OF TABLES ...........................................................................................................................................................................VI

LIST OF FIGURES .........................................................................................................................................................................VI

REGISTERS OVERVIEW ............................................................................................................................................................... 1

REGISTER DOCUMENT INTRODUCTION ........................................................................................................................................ 1

MODULE AND REGISTER SCOPE DEFINITIONS ............................................................................................................................. 2

Module Name Abbreviations................................................................................................................................................. 2

Register Scope Map Within Modules.................................................................................................................................... 2

REGISTER TABLE FORMAT ........................................................................................................................................................... 4

Column Definitions................................................................................................................................................................. 4

Attribute Definitions: ............................................................................................................................................................. 4

Special Default Value Definitions.......................................................................................................................................... 4

PCI ARBITER CONTROL ............................................................................................................................................................... 5

PCI CONFIGURATION SPACE I/O ................................................................................................................................................. 5

NORTH MODULE REGISTER DESCRIPTIONS........................................................................................................................ 6

DEVICE 0 FUNCTION 0 (D0F0): HOST CONTROLLER .................................................................................................................. 6

Header Registers (00-3Fh) ..................................................................................................................................................... 6

Multiple Function and Legacy Space Access Control (4F-C6h)......................................................................................... 9

Control Registers for Integrated Graphics / Video Processor (C7-FFh) .........................................................................10

DEVICE 0 FUNCTION 1 (D0F1): ERROR REPORTING ................................................................................................................. 12

Header Registers (00-3Fh) ................................................................................................................................................... 12

Host Bus Error Report (60-6Fh) ......................................................................................................................................... 15

DEVICE 0 FUNCTION 2 (D0F2): HOST BUS CONTROL................................................................................................................ 16

Header Registers (00-3Fh) ................................................................................................................................................... 16

Host CPU Control (50-5Fh) ................................................................................................................................................. 19

Host Interface DRDY Timing Control (60-6Fh) ................................................................................................................ 24

Host AGTL+ I/O Circuit (70–8Fh)...................................................................................................................................... 27

Miscellaneous Control (90–9Eh).......................................................................................................................................... 35

DEVICE 0 FUNCTION 3 (D0F3): DRAM BUS CONTROL ............................................................................................................ 36

Header Registers (00–3Fh)................................................................................................................................................... 36

DRAM Rank (Row) Ending / Beginning Address (40–4Fh) ............................................................................................. 39

MA Map / Command Rate (50–53h)................................................................................................................................... 41

Physical-to-Virtual Rank Mapping (54–57h) ..................................................................................................................... 42

Virtual Rank Interleave Address Select / Enable (58–5Fh) .............................................................................................. 43

DRAM Timing (60–64h)....................................................................................................................................................... 45

DRAM Queue / Arbitration (65–67h) ................................................................................................................................. 47

DRAM Control (68–69h)...................................................................................................................................................... 48

Refresh Control (6A–6Bh) ................................................................................................................................................... 48

DDR SDRAM Control (6C–6Fh)......................................................................................................................................... 49

DRAM Signal Timing Control (70–7Fh) ............................................................................................................................ 51

Read-Only Control (7C-7Fh)............................................................................................................................................... 54

Shadow RAM Control (80–83h) .......................................................................................................................................... 54

DRAM Above 4G Support (84-8Dh) ................................................................................................................................... 56

DRAM Clocking Control (90-9Fh)...................................................................................................................................... 58

UMA Registers (A0–AFh).................................................................................................................................................... 62

GMINT and AGPCINT Registers (B0–BFh) ..................................................................................................................... 64

I

V

T

A

c

e

nol

h

onf

C

N

og

de

i

A

D

s

e

i

nt

e

R

nc

I

l

a

i

qui

.

d

e

r

Preliminary Revision 0.95, June 20, 2008 -i- Table of Contents

Page 4

VX800 / VX820 Series System Programming Manual

DDR2 – I/O Pad Termination and Driving Control (D0–DFh) ........................................................................................ 66

DRAM Driving Control (E0–EBh)...................................................................................................................................... 73

DRAM CKG Control (EC–EFh)......................................................................................................................................... 75

DQ / DQS CKG Output Delay Control (F0–F9h).............................................................................................................. 76

DDR2 – DQ De-Skew Control (FA–FFh) ........................................................................................................................... 77

DEVICE 0 FUNCTION 4 (D0F4): POWER MANAGEMENT CONTROL .......................................................................................... 80

Header Registers (00-3Fh) ................................................................................................................................................... 80

Power Management Control (80–EFh)............................................................................................................................... 82

DEVICE 0 FUNCTION 5 (D0F5): APIC AND CENTRAL TRAFFIC CONTROL .............................................................................. 91

Header Registers (00–3Fh)................................................................................................................................................... 91

Legacy APIC Base I/O Registers (40–5Fh)......................................................................................................................... 93

Central Traffic - Downstream Control (60–7Fh)............................................................................................................... 95

Central Traffic - Upstream Control (80-85h)..................................................................................................................... 97

PCIe Message Controller and Power Management (A0–FFh) ......................................................................................... 99

DEVICE 0 FUNCTION 6 (D0F6): SCRATCH REGISTERS ............................................................................................................ 102

Header Registers (00-3Fh) ................................................................................................................................................. 102

Scratch Registers (40-7F)................................................................................................................................................... 104

Hash Data Control Registers (C0–FFh)............................................................................................................................ 105

DEVICE 0 FUNCTION 7 (D0F7): NORTH-SOUTH MODULE INTERFACE CONTROL.................................................................. 108

Header Registers (00-3Fh) ................................................................................................................................................. 108

North-South Module Interface Control (40–60h) ............................................................................................................ 111

Shadow RAM Control (61-6Fh) ........................................................................................................................................ 111

Host-PCI Bridge Control (70-FFh) ................................................................................................................................... 113

DEVICE 2 FUNCTION 0 (D2F0) – PCI EXPRESS ROOT PORT G0 (PCI-TO-PCI VIRTUAL BRIDGE) ...................................... 114

Header Registers (00-3Fh) ................................................................................................................................................. 115

PCI Express Capability Registers (40-67h)...................................................................................................................... 122

PCI Power Management Capability Structure Registers (68-6Fh)................................................................................ 128

PCI Message Signal Interrupt (MSI) Capability Structure Registers (70-87h) ............................................................ 129

Message Signal Interrupt (MSI) Capability Registers (88-97h) ..................................................................................... 130

Subsystem ID and Subsystem Vendor ID Capability Registers (98-9Fh)...................................................................... 130

PCI Express Transaction Layer Registers (A0-AFh) ...................................................................................................... 131

PCI Express Data Link Layer Registers (B0-BFh).......................................................................................................... 135

PCI Express Physical Layer Registers (C0-CFh)............................................................................................................. 140

PCI Express Power Management Module Registers (D0-D3h) ...................................................................................... 144

PCI Express Message Controller Related Registers (D8-DFh)....................................................................................... 145

PCI Express Electrical PHY Registers (E0-EFh)............................................................................................................. 145

PCI Express Electrical PHY Test Registers (F0-FFh)..................................................................................................... 147

DEVICE 2 FUNCTION 0 (D2F0) – PCI EXPRESS ROOT PORT G0 EXTENDED SPACE .............................................................. 149

Advanced Error Reporting Capability (100-13Fh).......................................................................................................... 149

Virtual Channel Capability (140-14Fh) ............................................................................................................................ 152

VC0 Resource (150-15Bh).................................................................................................................................................. 153

VC1 Resource (15C-19Fh) ................................................................................................................................................. 154

DEVICE 3 FUNCTION 0 (D3F0) – PCI EXPRESS ROOT PORT 0 (PCI-TO-PCI VIRTUAL BRIDGE).......................................... 155

Header Registers (00-3Fh) ................................................................................................................................................. 155

PCI Express Capability Registers (40-67h)...................................................................................................................... 162

PCI Power Management Capability Structure Registers (68-6Fh)................................................................................ 168

PCI Message Signal Interrupt (MSI) Capability Structure Registers (70-87h) ............................................................ 169

Message Signal Interrupt (MSI) Capability Registers (88-97h) ..................................................................................... 170

Subsystem ID and Subsystem Vendor ID Capability Registers (98-9Fh)...................................................................... 170

PCI Express Transaction Layer Registers (A0-AFh) ...................................................................................................... 171

PCI Express Data Link Layer Registers (B0-BFh).......................................................................................................... 175

PCI Express Physical Layer Registers (C0-CFh)............................................................................................................. 180

PCI Express Power Management Module Registers (D0-D3h) ...................................................................................... 184

PCI Express Message Controller Related Registers (D8-DFh)....................................................................................... 185

I

V

T

A

c

e

nol

h

onf

C

N

og

de

i

A

D

s

e

i

nt

e

R

nc

I

l

a

i

qui

.

d

e

r

Preliminary Revision 0.95, June 20, 2008 -ii- Table of Contents

Page 5

VX800 / VX820 Series System Programming Manual

PCI Express Electrical PHY Registers (E0-EFh)............................................................................................................. 185

PCI Express Electrical PHY Test Registers (F0-FFh)..................................................................................................... 186

DEVICE 3 FUNCTION 0 (D3F0) – PCI EXPRESS ROOT PORT 0 EXTENDED SPACE ................................................................. 188

Advanced Error Reporting Capability (100-13Fh).......................................................................................................... 188

Virtual Channel Capability (140-14Fh) ............................................................................................................................ 191

VC0 Resource (150-15Bh).................................................................................................................................................. 192

VC1 Resource (15C-19Fh) ................................................................................................................................................. 193

DEVICE 3 FUNCTION 1 (D3F1) – PCI EXPRESS ROOT PORT 1 (PCI-TO-PCI VIRTUAL BRIDGE).......................................... 194

Header Registers (00-3Fh) ................................................................................................................................................. 194

PCI Express Capability Registers (40-67h)...................................................................................................................... 201

PCI Power Management Capability Structure Registers (68-6Fh)................................................................................ 207

PCI Message Signal Interrupt (MSI) Capability Structure Registers (70-87h) ............................................................ 208

Message Signal Interrupt (MSI) Capability Registers (88-97h) ..................................................................................... 209

Subsystem ID and Subsystem Vendor ID Capability Registers (98-9Fh)...................................................................... 209

PCI Express Transaction Layer Registers (A0-AFh) ...................................................................................................... 210

PCI Express Data Link Layer Registers (B0-BFh).......................................................................................................... 214

PCI Express Physical Layer Registers (C0-CFh)............................................................................................................. 218

PCI Express Power Management Module Registers (D0-D3h) ...................................................................................... 222

PCI Express Message Controller Related Registers (D8-DFh)....................................................................................... 223

PCI Express Electrical PHY Registers (E0-EFh)............................................................................................................. 224

PCI Express Electrical PHY Test Registers (F0-FFh)..................................................................................................... 225

DEVICE 3 FUNCTION 1 (D3F1) – PCI EXPRESS ROOT PORT 1 EXTENDED SPACE.................................................................. 227

Advanced Error Reporting Capability (100-13Fh).......................................................................................................... 227

Virtual Channel Capability (140-14Fh) ............................................................................................................................ 230

VC0 Resource (150-15Bh).................................................................................................................................................. 231

VC1 Resource (15C-19Fh) ................................................................................................................................................. 232

PCI EXPRESS ROOT COMPLEX REGISTER BLOCK – HOST ..................................................................................................... 233

Virtual Channel Capability (000-00Fh) ............................................................................................................................ 233

VC0 Resource (010-01Bh).................................................................................................................................................. 234

Root Complex Link Declaration Enhanced Capability (040-04Fh) ............................................................................... 235

Link Entry for PEG0 (050-05Fh) ...................................................................................................................................... 235

Link Entry for PE0 (060-06Fh) ......................................................................................................................................... 236

Link Entry for PE1 (070-07Fh) ......................................................................................................................................... 236

Link Entry for HDAC (080-08Fh)..................................................................................................................................... 237

VC Arbitration Timer (200-20Fh)..................................................................................................................................... 238

Port Arbitration Timer for VC0 (210-219h) .................................................................................................................... 238

Host Side Upstream Arbitration Timers (230-23Fh)....................................................................................................... 240

PXPTRF (Central Traffic Controller) P2P Arbitration Timer of PCIe (250-253h)..................................................... 242

I

T

A

c

e

nol

h

onf

C

V

SOUTH MODULE REGISTER DESCRIPTIONS .................................................................................................................... 243

LEGACY I/O PORTS ................................................................................................................................................................... 243

Keyboard Controller I/O Registers................................................................................................................................... 245

DMA Controller I/O Registers .......................................................................................................................................... 249

DMA Controller Shadow Registers................................................................................................................................... 250

Interrupt Controller I/O Registers.................................................................................................................................... 251

Interrupt Controller I/O Shadow Registers ..................................................................................................................... 251

Timer / Counter I/O Registers........................................................................................................................................... 252

Timer / Counter Shadow Registers ................................................................................................................................... 252

CMOS / RTC I/O Registers ............................................................................................................................................... 252

Keyboard / Mouse Wakeup Index / Data Registers......................................................................................................... 255

Keyboard / Mouse Wakeup Registers............................................................................................................................... 256

MEMORY MAPPED I/O APIC REGISTERS................................................................................................................................258

Indexed I/O APIC Registers .............................................................................................................................................. 259

INDEXED I/O UART DMA CONTROL REGISTERS .................................................................................................................. 262

N

og

de

i

A

D

s

e

i

nt

e

R

nc

I

l

a

i

qui

.

d

e

r

Preliminary Revision 0.95, June 20, 2008 -iii- Table of Contents

Page 6

VX800 / VX820 Series System Programming Manual

DEVICE 12 FUNCTION 0 (D12F0) - SDIO HOST CONTROLLER............................................................................................... 264

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 264

PCI Device Specific Registers (40-FFh)............................................................................................................................ 266

SDIO HOST STANDARD REGISTERS (00-FFH) ......................................................................................................................... 271

IRDA HOST CONTROLLER I/O SPACE REGISTERS.................................................................................................................. 280

DEVICE 13 FUNCTION 0 (D13F0) – SECURE DIGITAL MEMORY CARD CONTROLLER........................................................... 291

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 291

PCI Card Reader - Specific Configuration Registers (40-FFh)...................................................................................... 295

SDC MMIO Registers (00-FFh) ........................................................................................................................................ 297

Data DMA Control Registers (00-FFh)............................................................................................................................. 305

CICH DMA Control Registers (00-FFh) .......................................................................................................................... 307

PCI Control Registers (00-FFh) ........................................................................................................................................310

DEVICE 15 FUNCTION 0 (D15F0): SERIAL ATA & EIDE CONTROLLER ............................................................................... 312

Header Registers (00-3Fh) ................................................................................................................................................. 312

SATA Registers (40-47h).................................................................................................................................................... 318

EIDE Registers (48-54h)..................................................................................................................................................... 320

SATA Link Control Registers (55-56h) ............................................................................................................................ 322

SATA PHY Control Registers (57-5Eh) ........................................................................................................................... 323

SATA Hot Plug and RAMBIST Status Registers (5F-63h)............................................................................................. 325

SATA Analog PHY Control (64-77h)................................................................................................................................ 326

Miscellaneous Registers (78-7Fh)...................................................................................................................................... 331

SATA Transport Control Registers (80-8Fh)................................................................................................................... 332

SATA SCR Registers (A0-AFh)......................................................................................................................................... 334

Legacy / Back Door Registers (B0-BFh) ........................................................................................................................... 336

EIDE Registers (C0-FFh)................................................................................................................................................... 338

DEVICE 16 FUNCTION 0-2 (D16F0-F2) – USB 1.1 UHCI PORTS 0-5...................................................................................... 342

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 342

USB 1.1-Specific Configuration Registers (40-FFh) ........................................................................................................ 345

USB 1.1 I/O Registers (00-13h).......................................................................................................................................... 349

DEVICE 16 FUNCTION 4 REGISTERS - USB 2.0 EHCI ............................................................................................................. 350

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 350

USB 2.0-Specific Configuration Registers (40-FCh)........................................................................................................ 353

EHCI USB 2.0 I/O Registers (00-B3h).............................................................................................................................. 360

DEVICE 17 FUNCTION 0 (D17F0) - BUS CONTROL AND POWER MANAGEMENT .................................................................... 364

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 364

ISA Bus Control (40-49h)................................................................................................................................................... 366

LPC Firmware Memory Control (4A-4Bh)...................................................................................................................... 370

Miscellaneous Control (4C-4Fh)........................................................................................................................................ 370

Function Control (50-51h) ................................................................................................................................................. 372

Serial IRQ, LPC and PC / PCI DMA Control (52-53h) .................................................................................................. 373

Plug and Play Control – PCI (54-57h) .............................................................................................................................. 374

GPIO and Miscellaneous Control (58-5Bh)...................................................................................................................... 376

Programmable Chip Select (PCS) Control (5C-66h)....................................................................................................... 378

Output Control (67h).......................................................................................................................................................... 379

High Precision Event Timers (HPET) (68-6Bh)............................................................................................................... 380

ISA Decoding Control (6C-6Fh)........................................................................................................................................ 381

PCI I/O Cycle Control (74-7Fh) ........................................................................................................................................ 383

Power Management-Specific Configuration Registers (80-CFh) ................................................................................... 386

UART / FIR Misc Control Registers (B0-BFh)................................................................................................................ 398

System Management Bus-Specific Configuration Registers (D0-E7h) .......................................................................... 401

Watchdog Timer Registers (E8-FFh)................................................................................................................................ 408

ACPI IO Space Registers (PMIO 00-0Bh)........................................................................................................................ 409

Processor Power Management Registers (PMIO 10-16h)............................................................................................... 412

General Purpose Power Management Registers (PMIO 20-52h)................................................................................... 413

I

V

T

A

c

e

nol

h

onf

C

N

og

de

i

A

D

s

e

i

nt

e

R

nc

I

l

a

i

qui

.

d

e

r

Preliminary Revision 0.95, June 20, 2008 -iv- Table of Contents

Page 7

VX800 / VX820 Series System Programming Manual

IO Trap Registers (PMIO 54-69h) .................................................................................................................................... 425

Watchdog Timer Memory Base (PM-MMIO 00-07h)..................................................................................................... 430

System Management Bus I/O Space Registers (SMIO 00-0Fh)...................................................................................... 431

SPI CONTROLLER ..................................................................................................................................................................... 437

DEVICE 17 FUNCTION 7 (D17F7): SOUTH-NORTH MODULE INTERFACE CONTROL .............................................................. 443

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 443

South -North Module Interface Control (40-5F).............................................................................................................. 445

DRAM Configuration (60h)............................................................................................................................................... 448

Shadow RAM Control (61-64h)......................................................................................................................................... 449

Conventional PCI Bus Control (70-7Fh) .......................................................................................................................... 450

HDAC Control (D0-DFh)................................................................................................................................................... 454

Dynamic Clock Control (E0-E3h) ..................................................................................................................................... 454

DRAM Above 4G Support (E4-FFh) ................................................................................................................................ 456

DEVICE 19 FUNCTION 0 (D19F0): PCI TO PCI BRIDGE.......................................................................................................... 457

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 457

DEVICE 20 FUNCTION 0 (D20F0) - HIGH DEFINITION AUDIO CONTROLLER (HDAC).......................................................... 463

PCI Configuration Space Header (00-3Fh)...................................................................................................................... 463

HDAC PCI EXTENDED CONFIGURATION SPACE (40-260H) ................................................................................................... 466

HIGH DEFINITION AUDIO CONTROLLER MEMORY MAPPED I/O REGISTERS (HDAC-MMIO) ........................................... 473

Global Capabilities and Control (00-1Bh)........................................................................................................................ 473

Interrupt Control (20-27h)................................................................................................................................................. 475

Synchronization Control (30-3Bh) .................................................................................................................................... 475

HDAC CORB (Command Output Ring Buffer) Control (40-4Eh)................................................................................ 476

HDAC RIRB (Response Input Ring Buffer) Control (50-5Eh) ...................................................................................... 477

HDAC Immediate Command Control (60-69h)............................................................................................................... 479

DMA Position Base Address (70-77h)............................................................................................................................... 480

HDAC Stream Descriptors (80-17Fh)............................................................................................................................... 481

Alias Registers (2030-2167h).............................................................................................................................................. 486

c

nol

h

og

de

i

e

s

e

i

nt

e

nc

I

l

a

i

qui

.

d

e

r

T

I

A

onf

C

R

A

V

D

N

Preliminary Revision 0.95, June 20, 2008 -v- Table of Contents

Page 8

VX800 / VX820 Series System Programming Manual

LIST OF TABLES

TABLE 1. VX800 / VX820 SERIES FEATURE COMPARISON TABLE.................................................................................. 1

TABLE 2. DYNAMIC DEFER SNOOP STALL TABLE........................................................................................................... 19

TABLE 3. CPU WRITE REQUEST POLICY............................................................................................................................. 22

TABLE 4. HOST / DRAM BANDWIDTH POLICY................................................................................................................... 23

TABLE 5. PROGRAMMING SETTING FOR DRAM CHANNELS ....................................................................................... 36

TABLE 6. RANK MA MAP TYPE TABLE................................................................................................................................. 41

TABLE 7. DRAM BANK ADDRESS TABLE ............................................................................................................................. 42

TABLE 8. RANK INTERLEAVE ADDRESS TABLE ............................................................................................................... 42

TABLE 9. CPU-TO-SMRAM CYCLE FLOW ............................................................................................................................ 55

TABLE 10. MD PADS ODT CONTROL IN DIFFERENT DRAM MODE .............................................................................67

TABLE 11. PAD ODT CONTROL GROUP SETTING ............................................................................................................. 67

TABLE 12. PHYSICAL PIN TO DRIVING GROUP MAPPING TABLE............................................................................... 73

TABLE 13. SCMD AND MA PINS POWER SAVING MODE SETTING............................................................................... 79

TABLE 14. CHIP SELECT PINS POWER SAVING MODE USAGE..................................................................................... 79

TABLE 15. PCIE PORT SUPPORT........................................................................................................................................... 114

TABLE 16. MAPPING TABLE FOR D2F0 RXC3 ................................................................................................................... 142

TABLE 17. MAPPING TABLE FOR D3F0 RXC3 ................................................................................................................... 182

TABLE 18. MAPPING TABLE FOR D3F1 RXC3 ................................................................................................................... 220

TABLE 19. KEYBOARD CONTROLLER COMMAND CODES .......................................................................................... 247

TABLE 20. CMOS REGISTER SUMMARY ............................................................................................................................ 253

TABLE 21. I/O REDIRECTION TABLE .................................................................................................................................. 260

TABLE 22. DETERMINATION OF TRANSFER TYPE.......................................................................................................... 272

TABLE 23. PROGRAMMING VALUES FOR I/O REGISTERS AT OFFSET 16-19H....................................................... 282

TABLE 24. COMMAND TYPE FIELD ENCODINGS ............................................................................................................. 298

TABLE 25. IDE/SATA SUPPORT OPTION .............................................................................................................................. 312

TABLE 26. PNP IRQ ROUTING TABLE ................................................................................................................................. 375

TABLE 27. INTERNAL APIC, PCI DEVICES IRQ ROUTING TABLE............................................................................... 375

TABLE 28. HPET IRQ ROUTING TABLE .............................................................................................................................. 375

TABLE 29. C3 LATENCY CONFIGURATION TABLE......................................................................................................... 404

TABLE 30. C4 LATENCY CONFIGURATION TABLE......................................................................................................... 405

T

c

e

A

I

nol

h

onf

C

LIST OF FIGURES

og

de

i

A

s

e

i

nt

e

R

nc

I

l

a

i

qui

.

d

e

r

FIGURE 1. DIMM / CHANNEL MAPPING DIAGRAM ..........................................................................................................44

FIGURE 2. LOOP BACK MODE SELECTIONS...................................................................................................................... 140

FIGURE 3. LOOP BACK MODE SELECTIONS...................................................................................................................... 180

FIGURE 4. LOOP BACK MODE SELECTIONS...................................................................................................................... 218

Preliminary Revision 0.95, June 20, 2008 -vi- Table of Contents

V

D

N

Page 9

VX800 / VX820 Series System Programming Manual

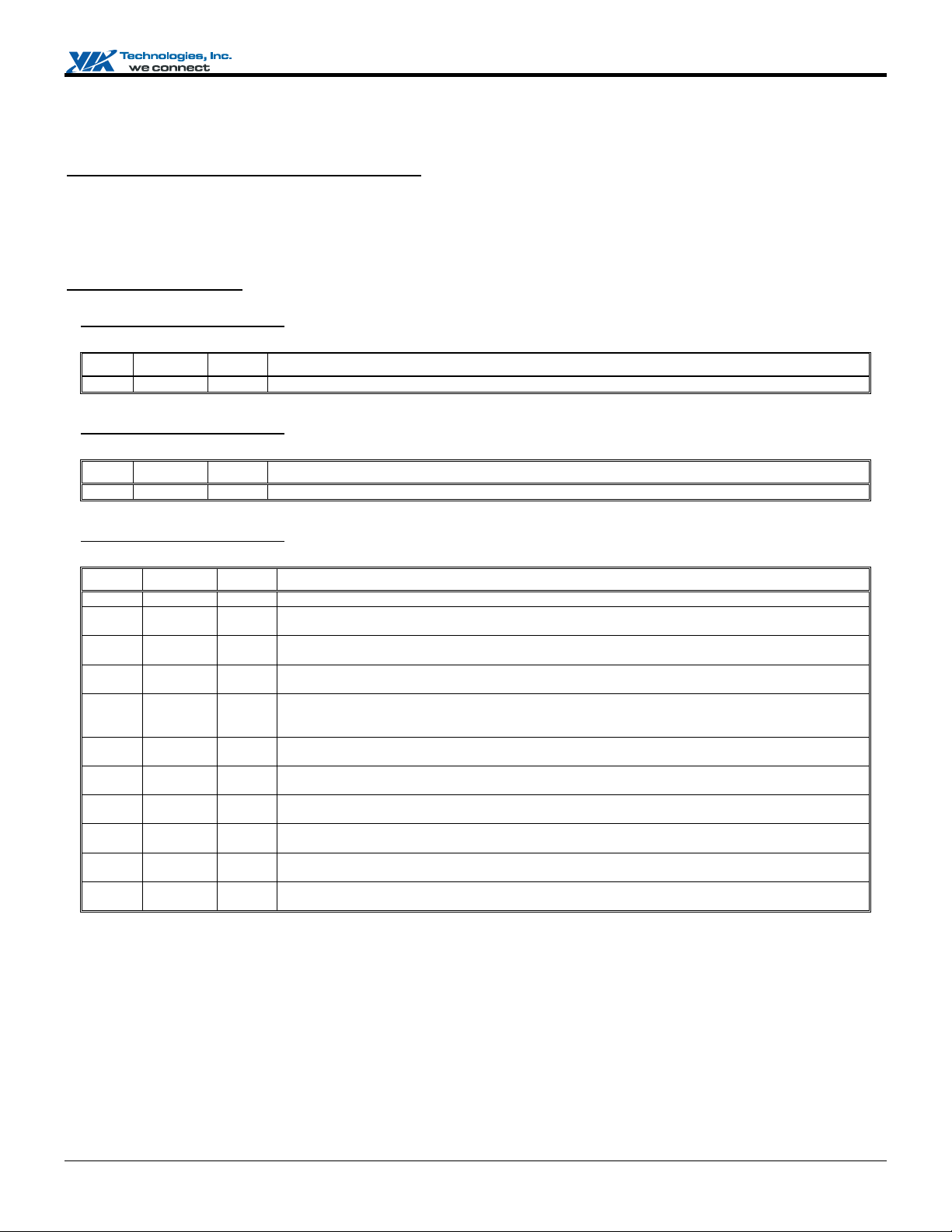

REGISTERS OVERVIEW

Register Document Introduction

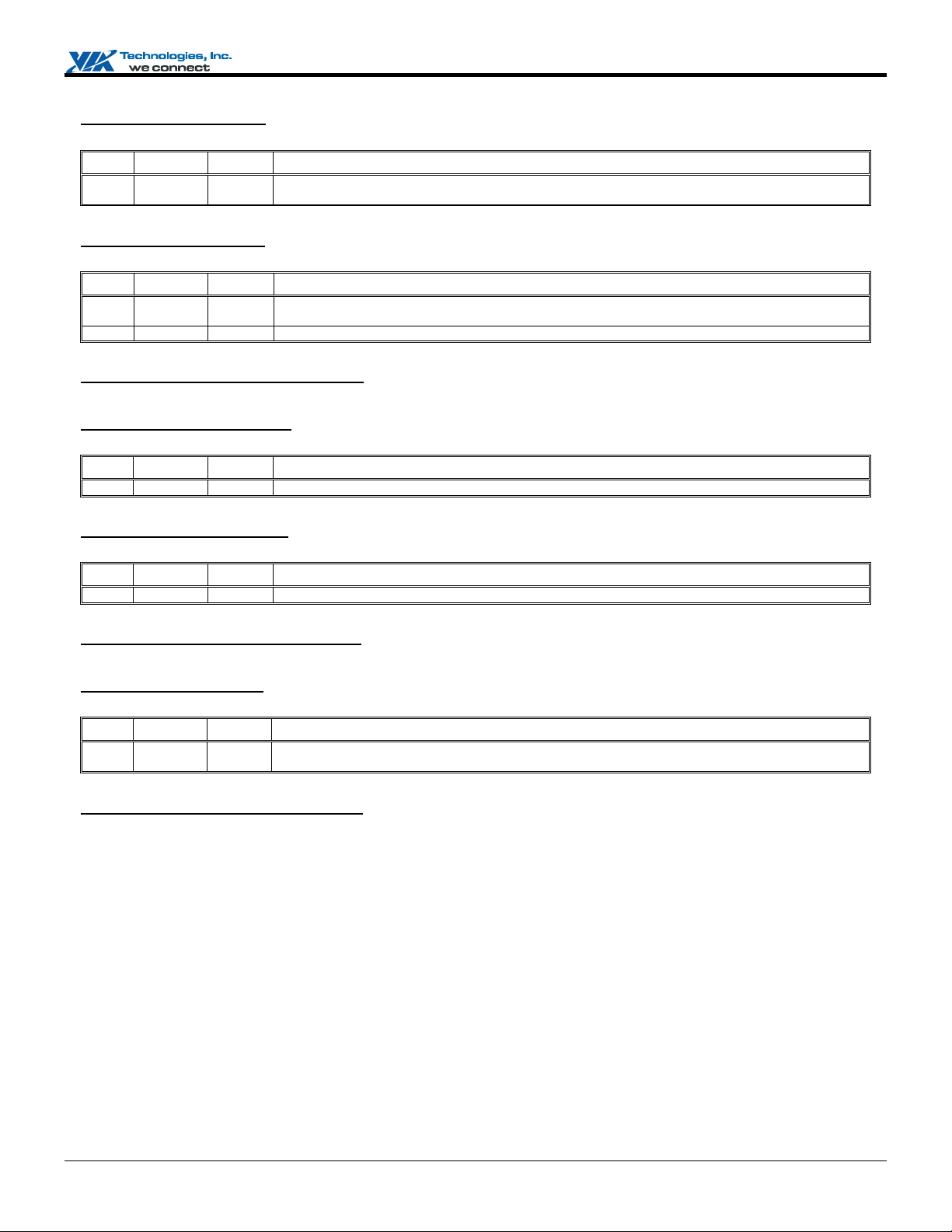

This document includes the registers for VIA VX800 and VX820 Series. Please refer to Table 1 for the specification differences

of these products.

This chip integrates functional modules of the traditional North Bridge and South Bridge chips, plus 3D/2D and Video Processors,

Video Decoding Accelerator and controller for external display interface. The register set is partitioned into three blocks: North

Module, South Module and Graphics and Video Module; of which, North Module and South Module registers are described in this

System Programming Manual while graphics and video registers are described in the Graphics and Video Programming

Guide.

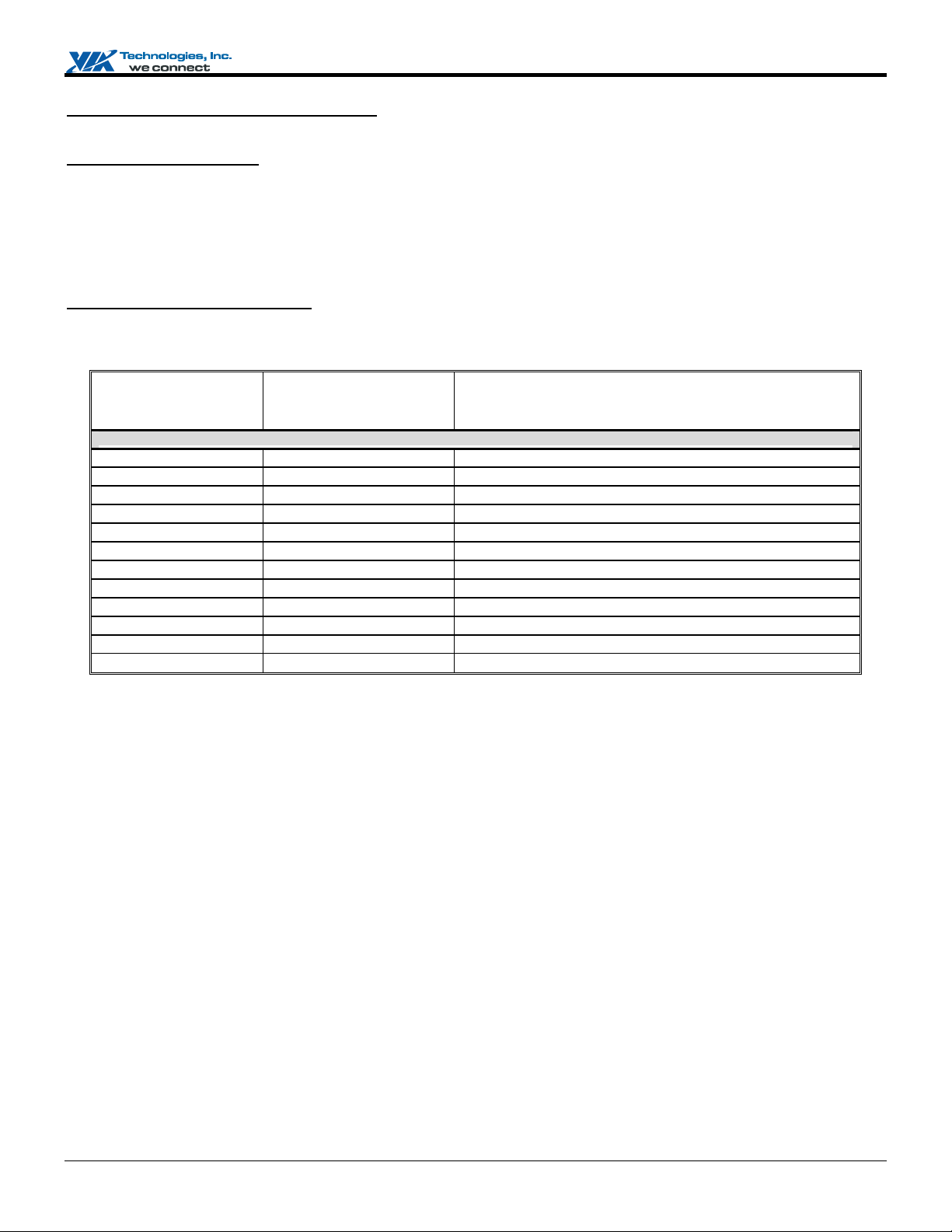

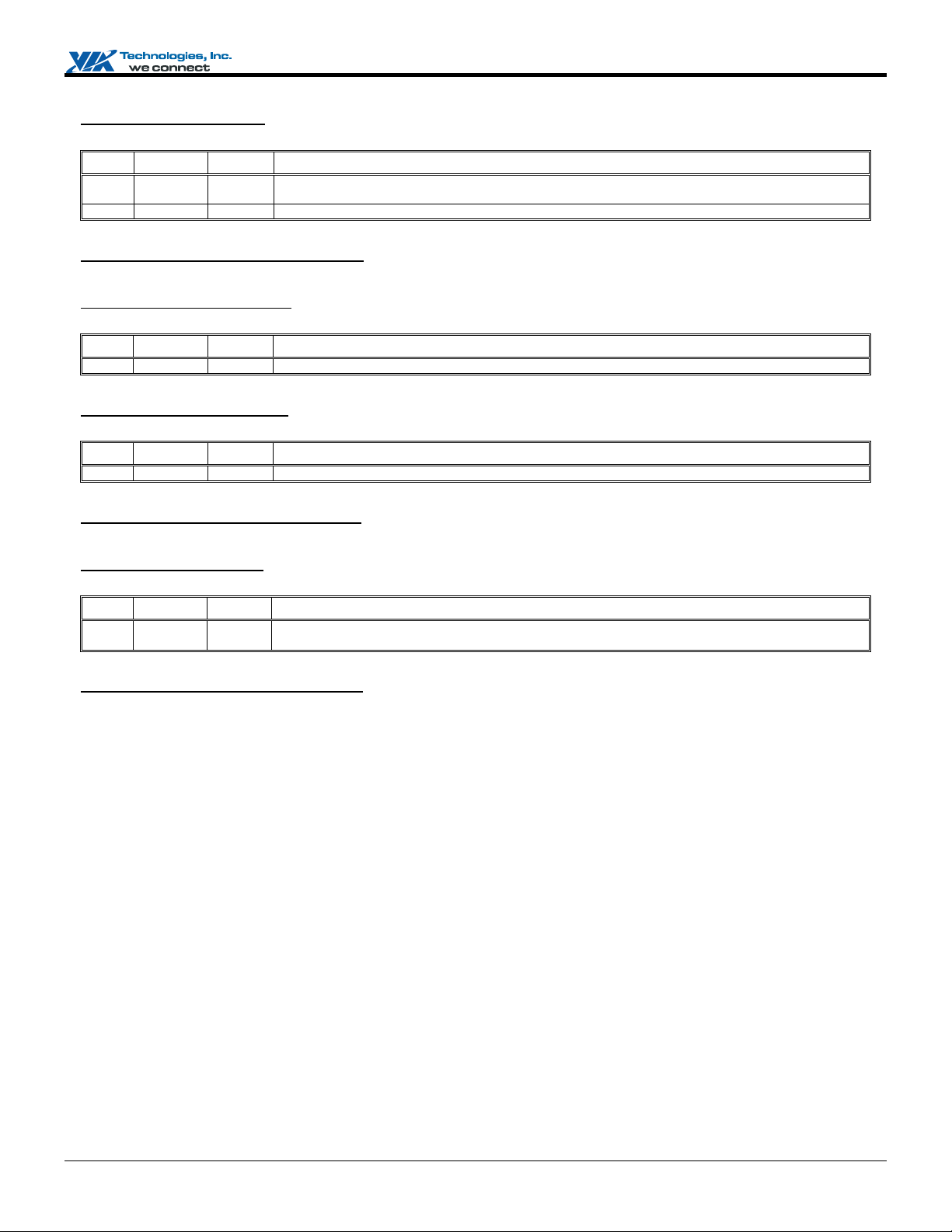

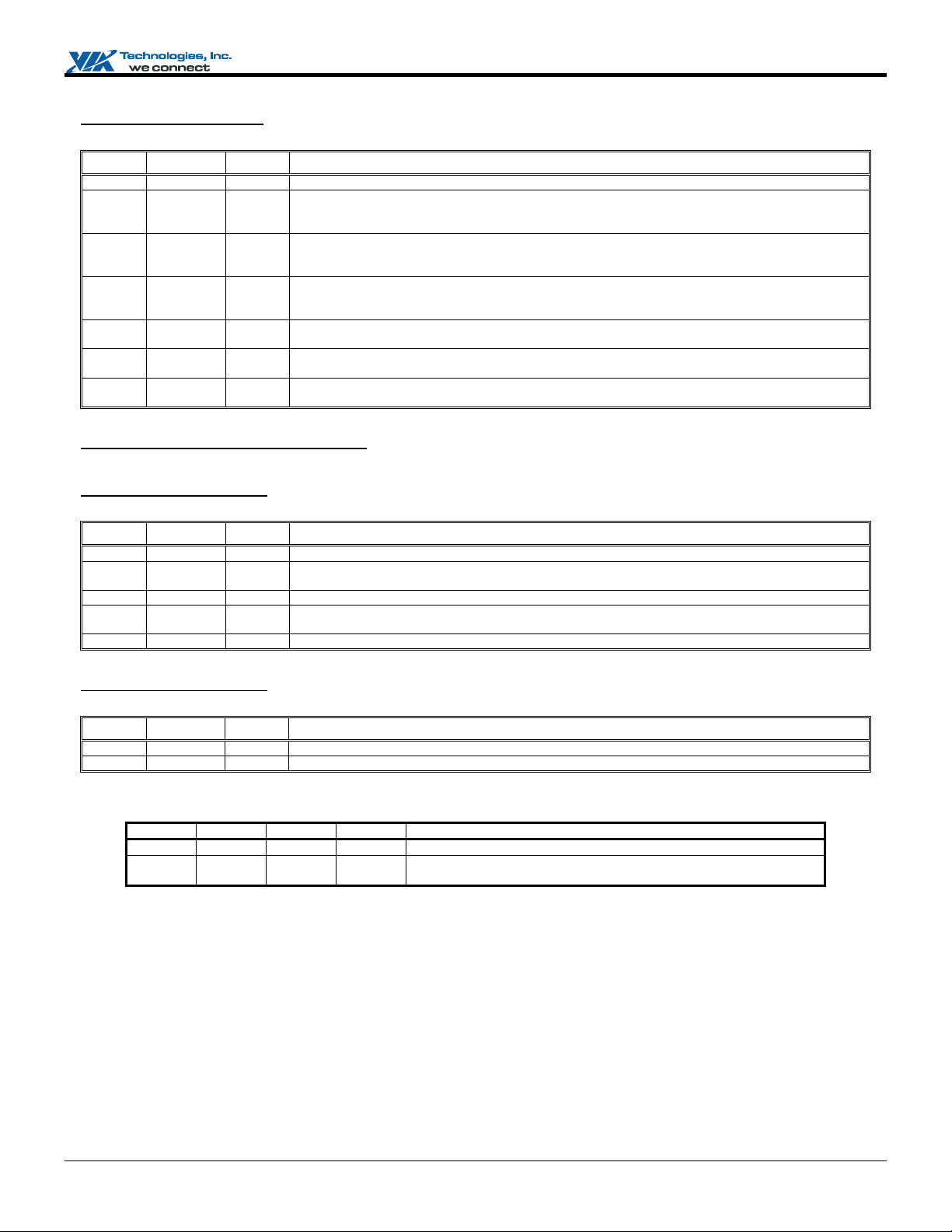

Table 1. VX800 / VX820 Series Feature Comparison Table

Product Model VX800UT VX800 VX820UT VX820

FSB Speed (MHz) 400-533 400-800 533 400-800

Integrated GFX Clock (MHz) 200 250 200 250

Memory Type

PCI Express Ports

PCI

SATA

Core Voltage

Package Dimension

Note 1. Registers related to features that the product does not support should be reserved.

DDR2 533 DDR2 667 DDR2 533 DDR2 667

3x1 1x4 + 2x1 2x1 2x1

Yes Yes No No

Yes (SATA 1.0) Yes (SATA 2.0) No No

1.25V 1.5V 1.25V 1.5V

ogi

33 x 33mm FCBGA

1236 balls

hnol

c

de

i

e

o

nf

R

A

I

A

T

C

s

e

i

nt

qu

e

I

a

.

nc

l

r

i

d

21 x 21mm FCBGA

e

1086 balls

V

D

N

Preliminary Revision 0.95, June 20, 2008 -1- Registers Overview

Page 10

VX800 / VX820 Series System Programming Manual

,

g

,

,

,

,

,

,

N

,

,

,

y Sp

t

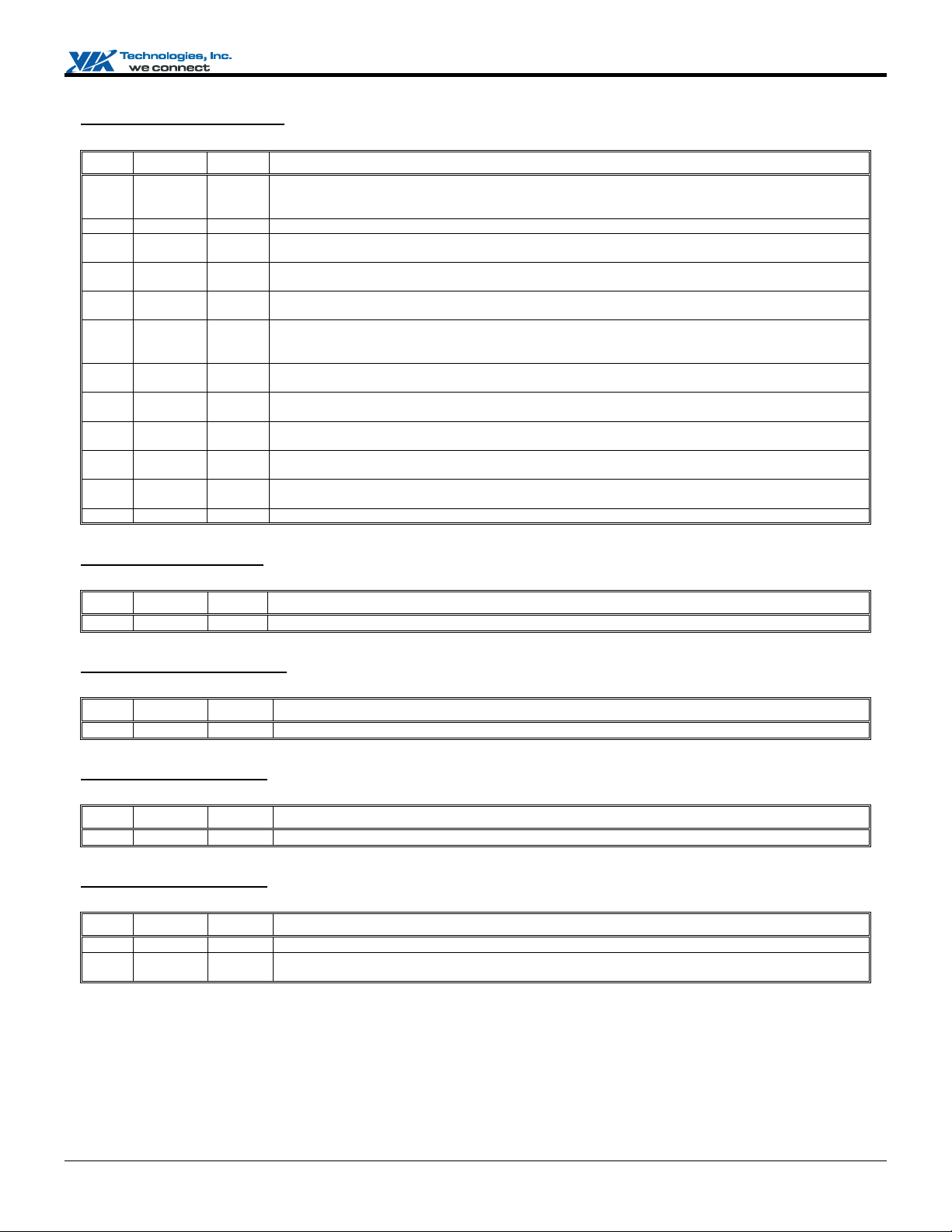

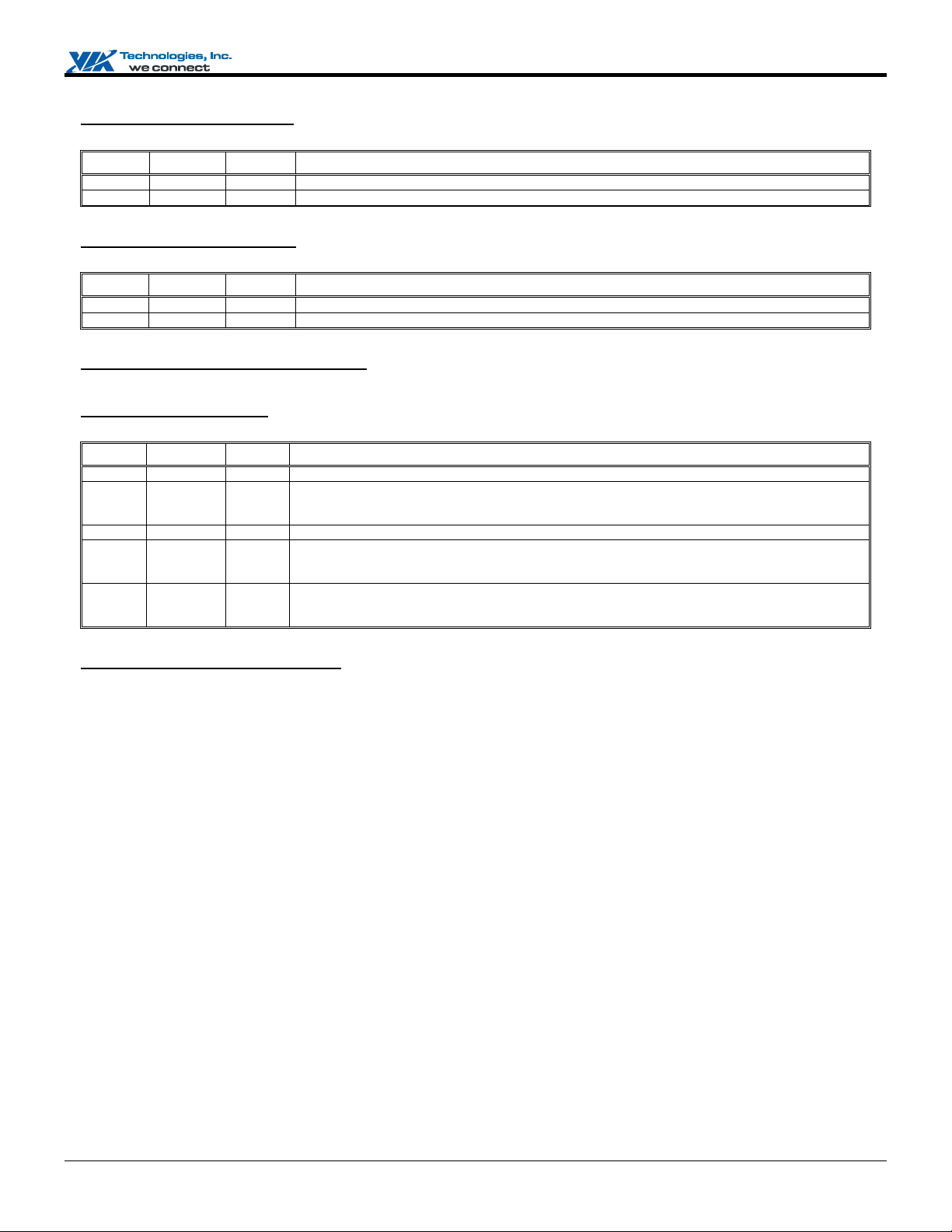

Module and Register Scope Definitions

Module Name Abbreviations

NM: North Module. It contains functional modules of the traditional North Bridge chip.

SM: South Module. It contains functional modules of the traditional South Bridge chip.

NSMIC: North-South Module Interface Control

SNMIC: South-North Module Interface Control

PM: Power Management

HDAC: High Definition Audio Controller

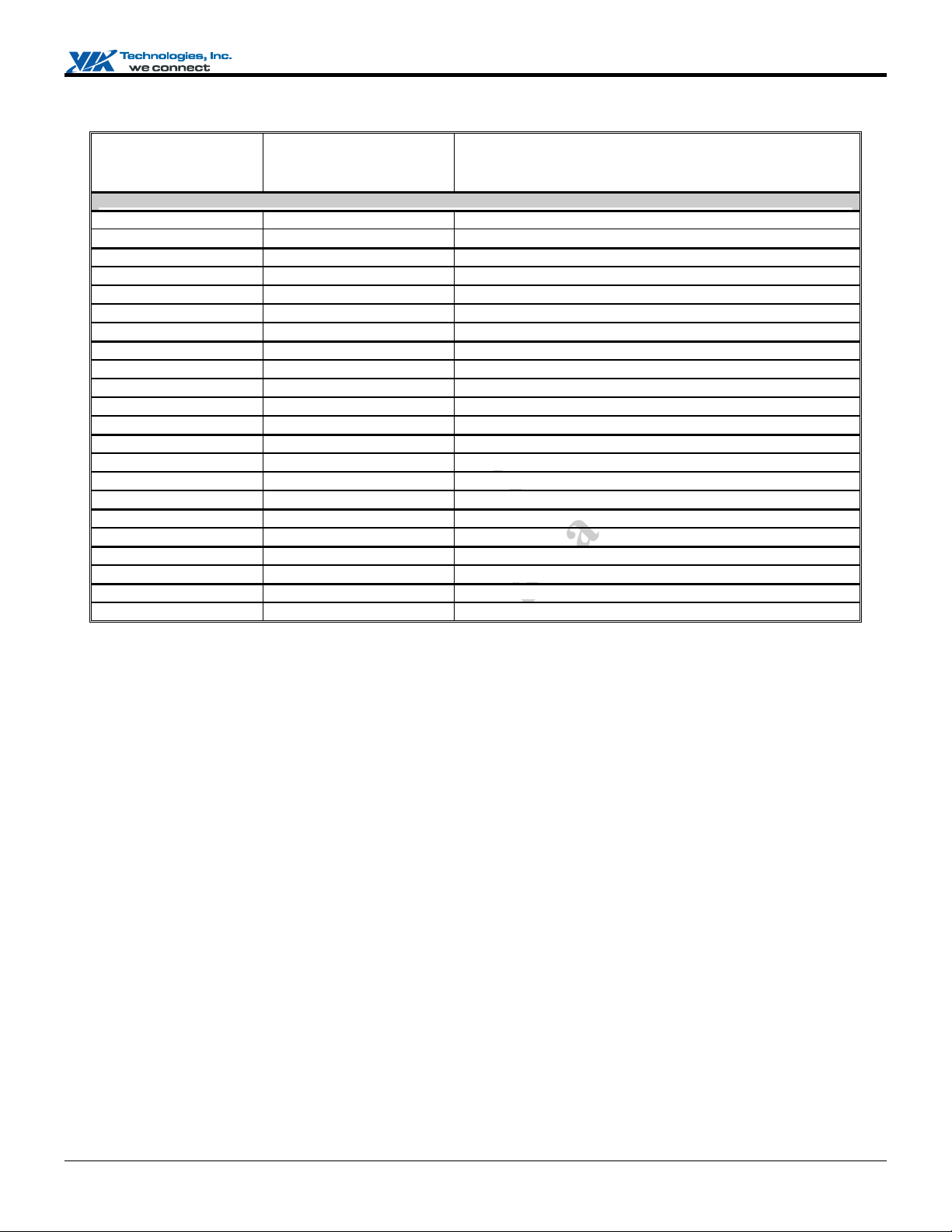

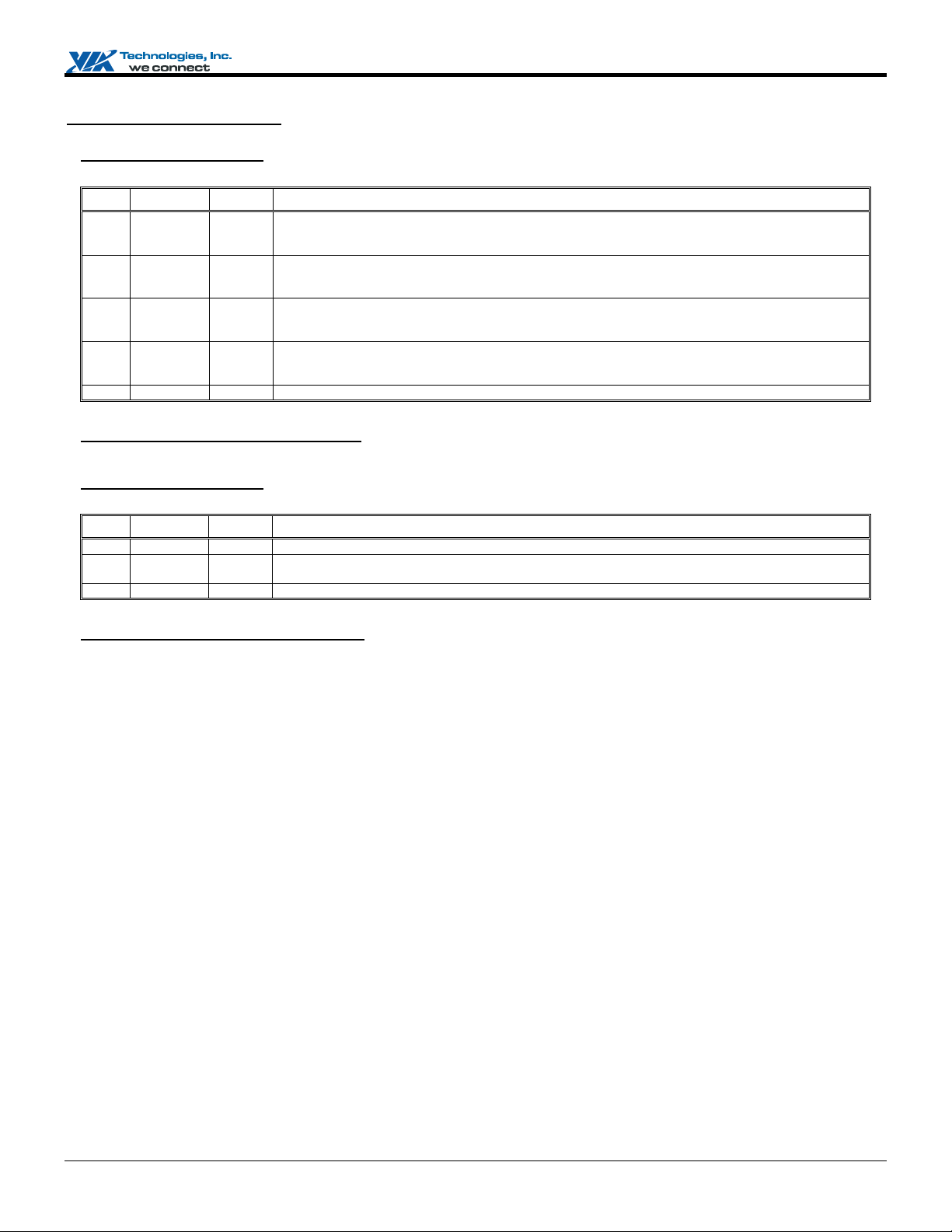

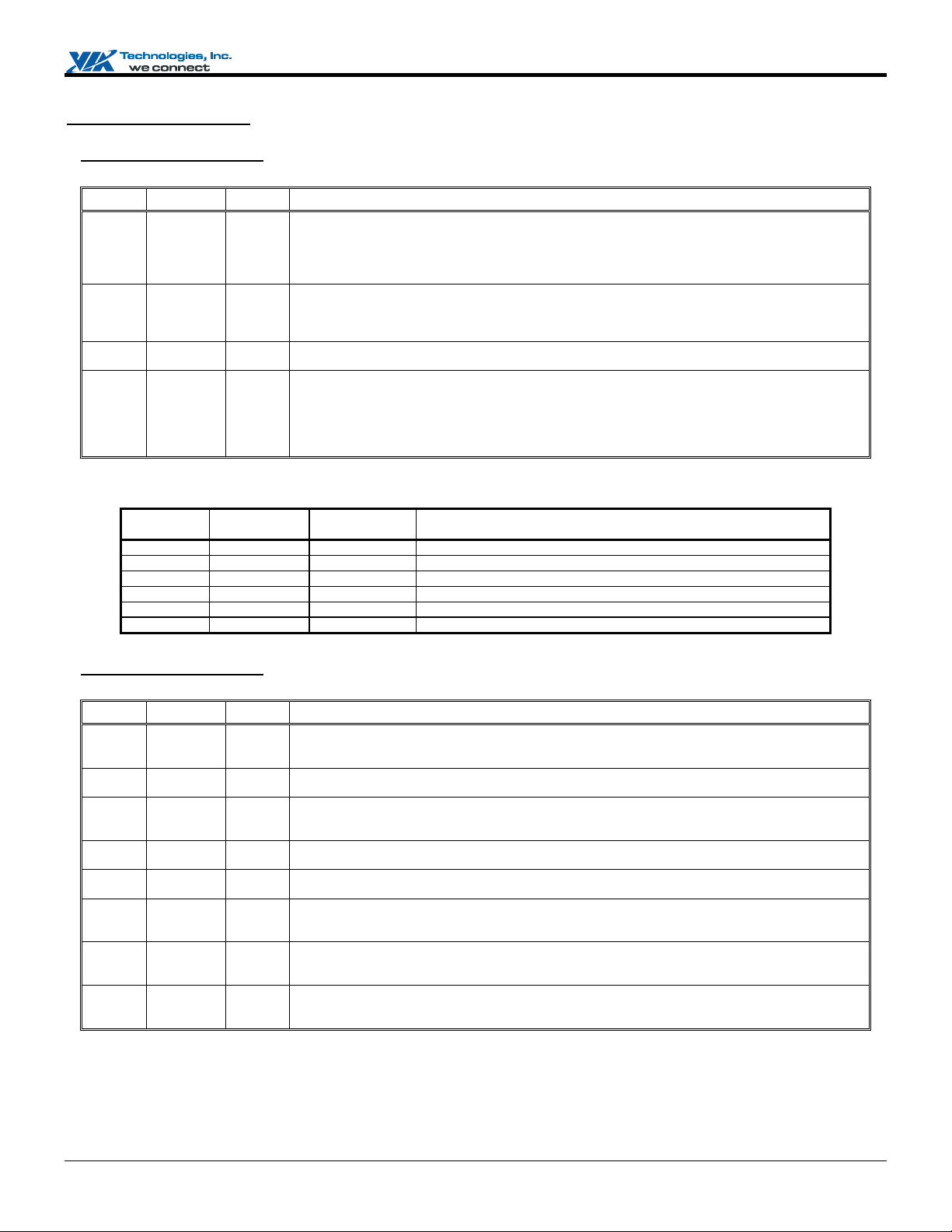

Register Scope Map Within Modules

To specifically identify every function, the following abbreviations will be applied in subsequent sections.

Abbreviation of

Register Space /

Module Name

.

Register Space Function

nc

I

s

D0F1

D0F2

D0F3

D0F4

D0F5

D0F6

D0F7

D2F0 / PEG0

D3F0 / PE0

D3F1 / PE1

RCRB-H

PCI Device 0

PCI Device 0

PCI Device 0

PCI Device 0

PCI Device 0

PCI Device 0

PCI Device 0

PCI Device 2

PCI Device 3

PCI Device 3

Memor

T

A

I

Function 1 Error Reportin

Function 2 Host Bus Control

Function 3 DRAM Bus Control

Function 4 Power Management and Chip Testing Control

Function 5 APIC and Central Traffic Control

Function 6 Scratch Registers

Function 7

Function 0 PCI Express Root Port G0 –x4, x2, x1

Function 0 PCI Express Root Port 0 –x1

hnol

Function 1 PCI Express Root Port 1 –x1

c

ace PCI Express Root Complex Register Block for Hos

ogi

orth-South Module Interface Control <NSMIC>

de

i

e

e

i

nt

qu

e

l

a

d

e

r

i

nf

o

R

C

A

V

D

N

Preliminary Revision 0.95, June 20, 2008 -2- Registers Overview

Page 11

y Sp

y Sp

y Sp

y Sp

,

,

,

,

r

p

y Sp

y Sp

,

y Sp

p

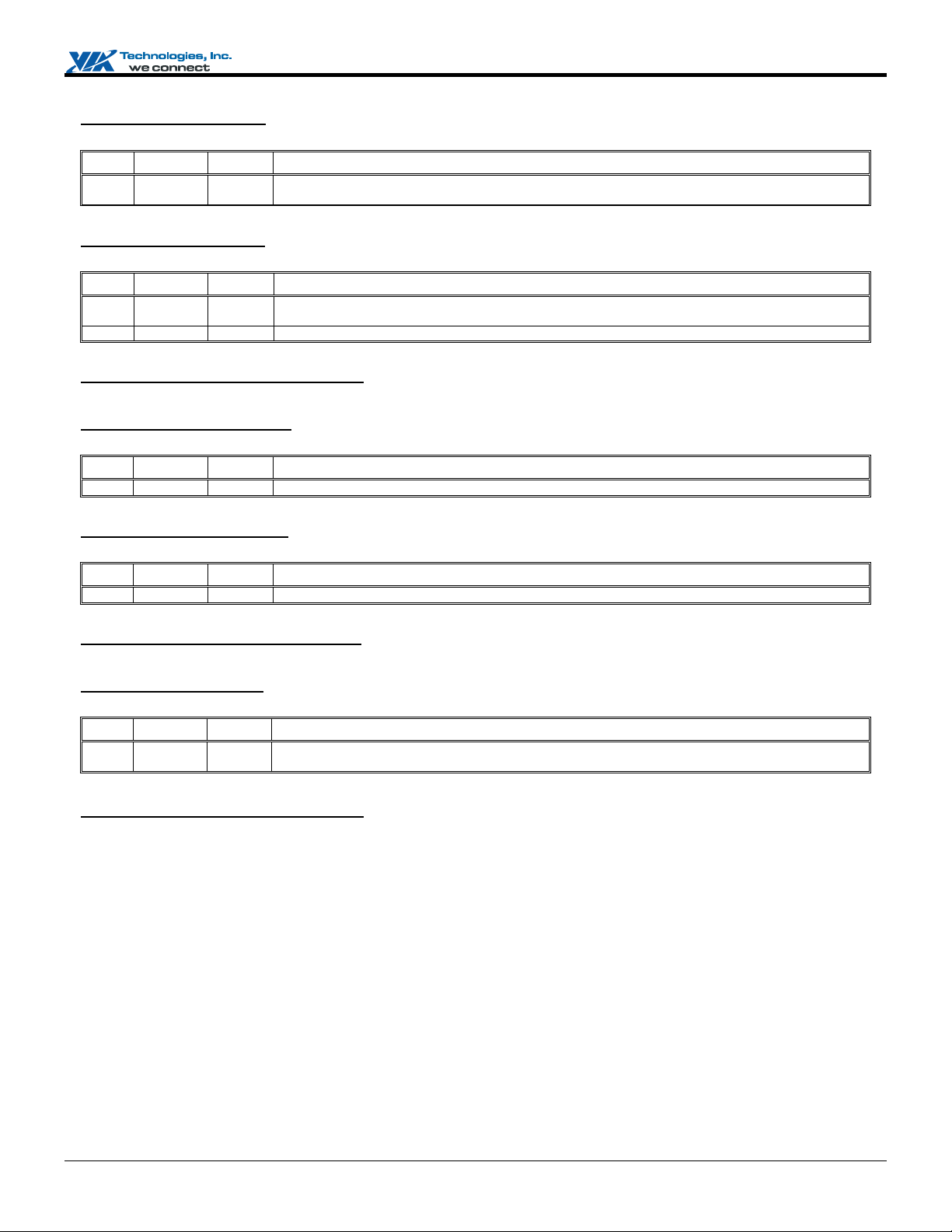

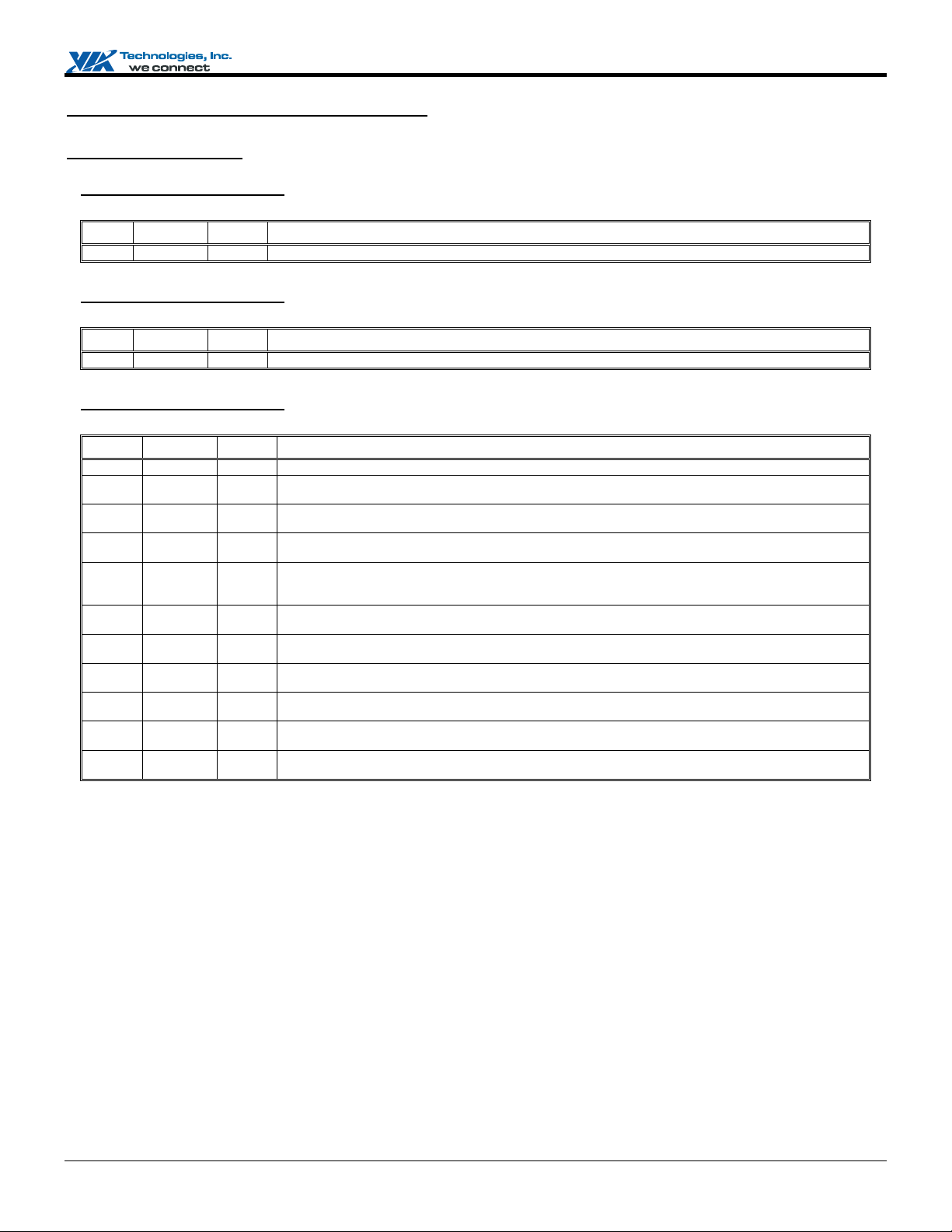

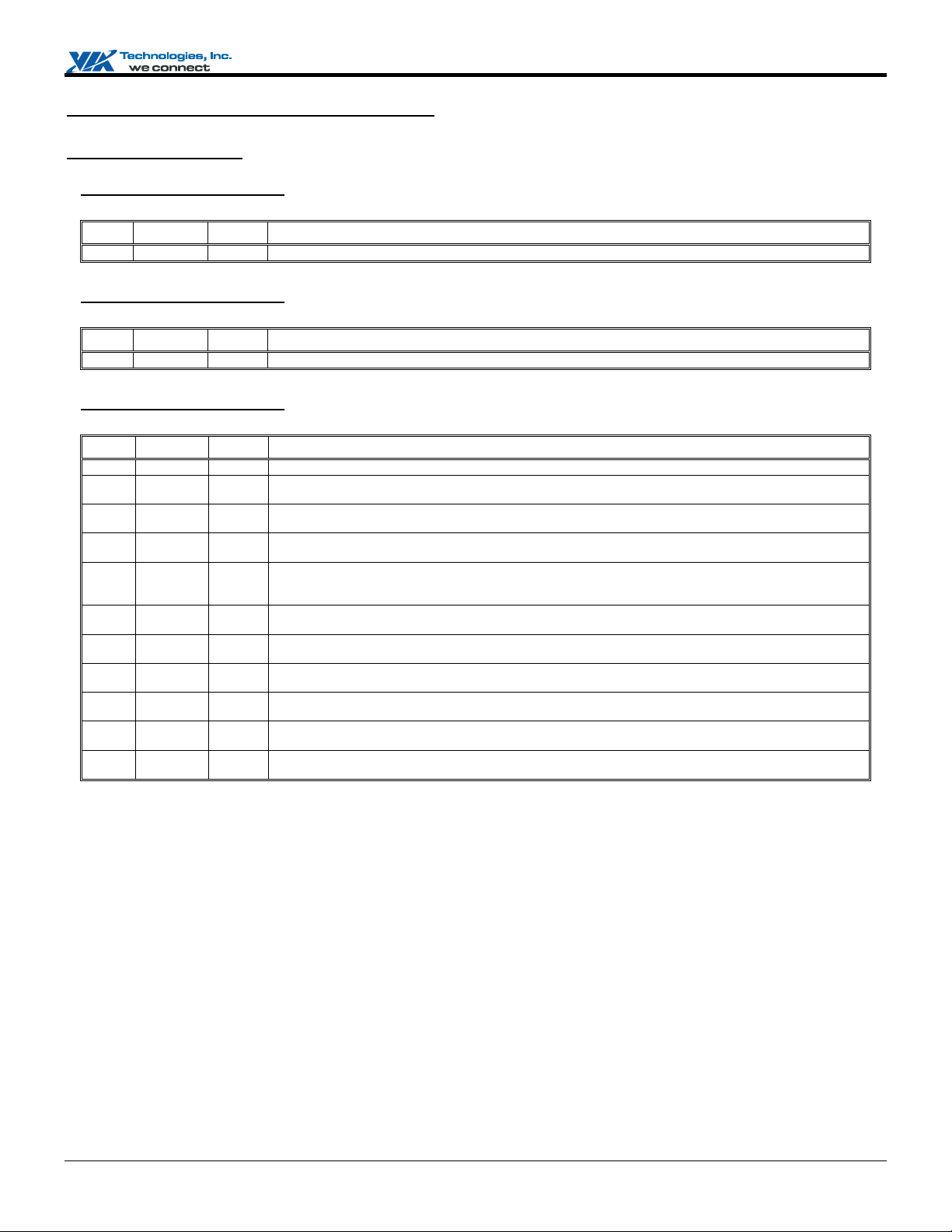

Abbreviation of

Register Space /

Module Name

VX800 / VX820 Series System Programming Manual

Register Space Function

SDIO-MMIO

SDC-MMIO

Data DMA-MMIO

CICH DMA-MMIO

PCI Control-MMIO

D16F0

D16F1

D16F2

D16F4

PMIO

PM-MMIO

SMIO

D19F0

HDAC-MMIO

-

FIR

Memory Space

Memor

Memor

Memor

Memor

PCI Device 16

PCI Device 16

PCI Device 16

PCI Device 16

IO S

Memor

Memor

PCI Device 19

Memor

IO S

A

I

SDIO Memory Mapped I/O Space Registers

ace Security Digital Controller Memory Mapped I/O Space

ace Data DMA Memory Mapped I/O Space Registers

ace CICH DMA Memory Mapped I/O Space Registers

ace PCI Control Memory Mapped I/O Space Registers

Function 0 USB 1.1 UHCI Ports 0-1

Function 1 USB 1.1 UHCI Ports 2-3

Function 2 USB 1.1 UHCI Ports 4-5

Function 4 USB 2.0 EHCI Controlle

nc

I

.

ace ACPI I/O Registers

ace Power Management Memory Mapped I/O Space Registers

ace System Management Bus I/O Space Registers

-

Function 0 PCI-to-PCI Bridge

ace HDAC Memory Mapped I/O Space Registers

ogi

s

e

l

a

i

e

ace IrDA Host Controller / IO Space Registers

nt

r

i

hnol

de

i

qu

e

R

T

c

e

nf

o

C

A

d

<

>

V

D

N

Preliminary Revision 0.95, June 20, 2008 -3- Registers Overview

Page 12

VX800 / VX820 Series System Programming Manual

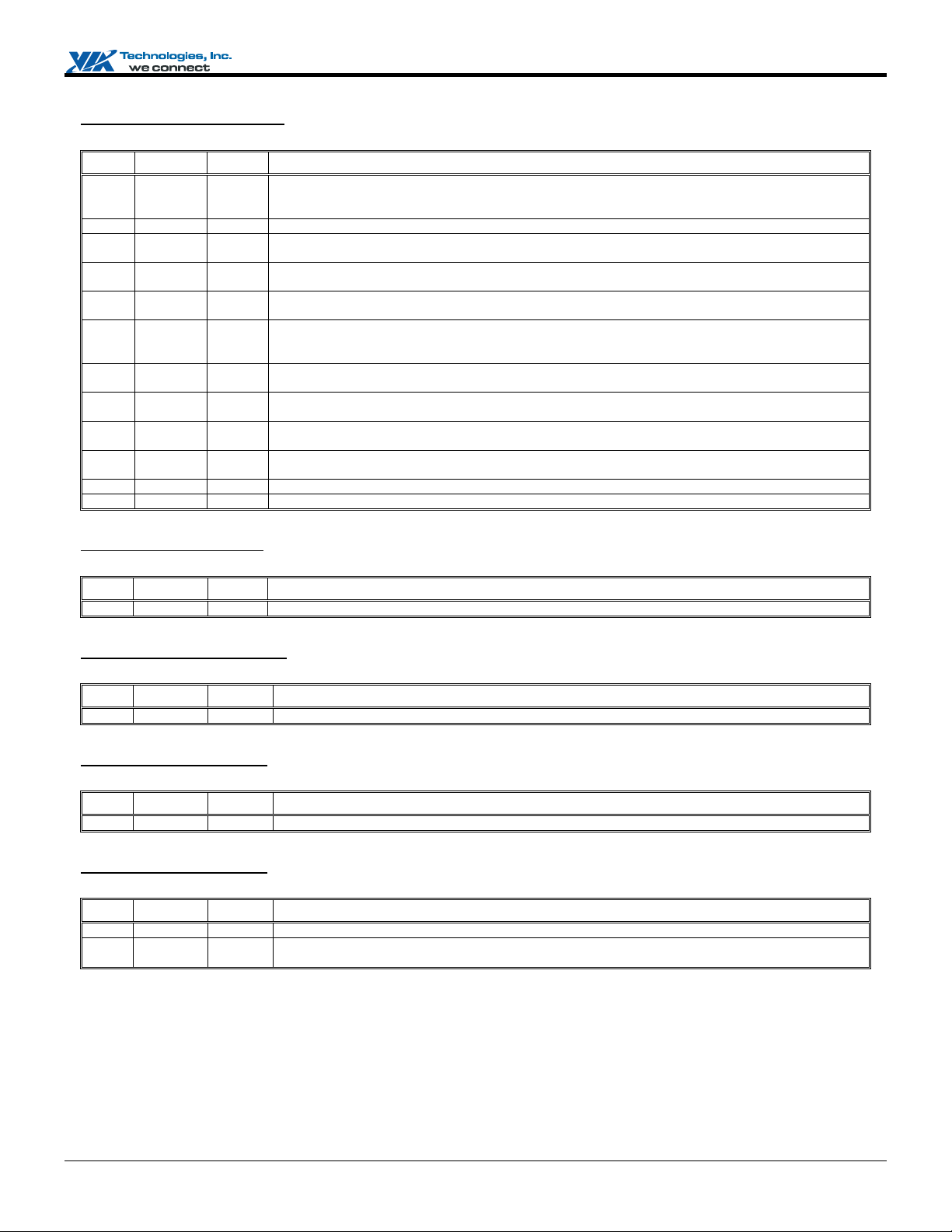

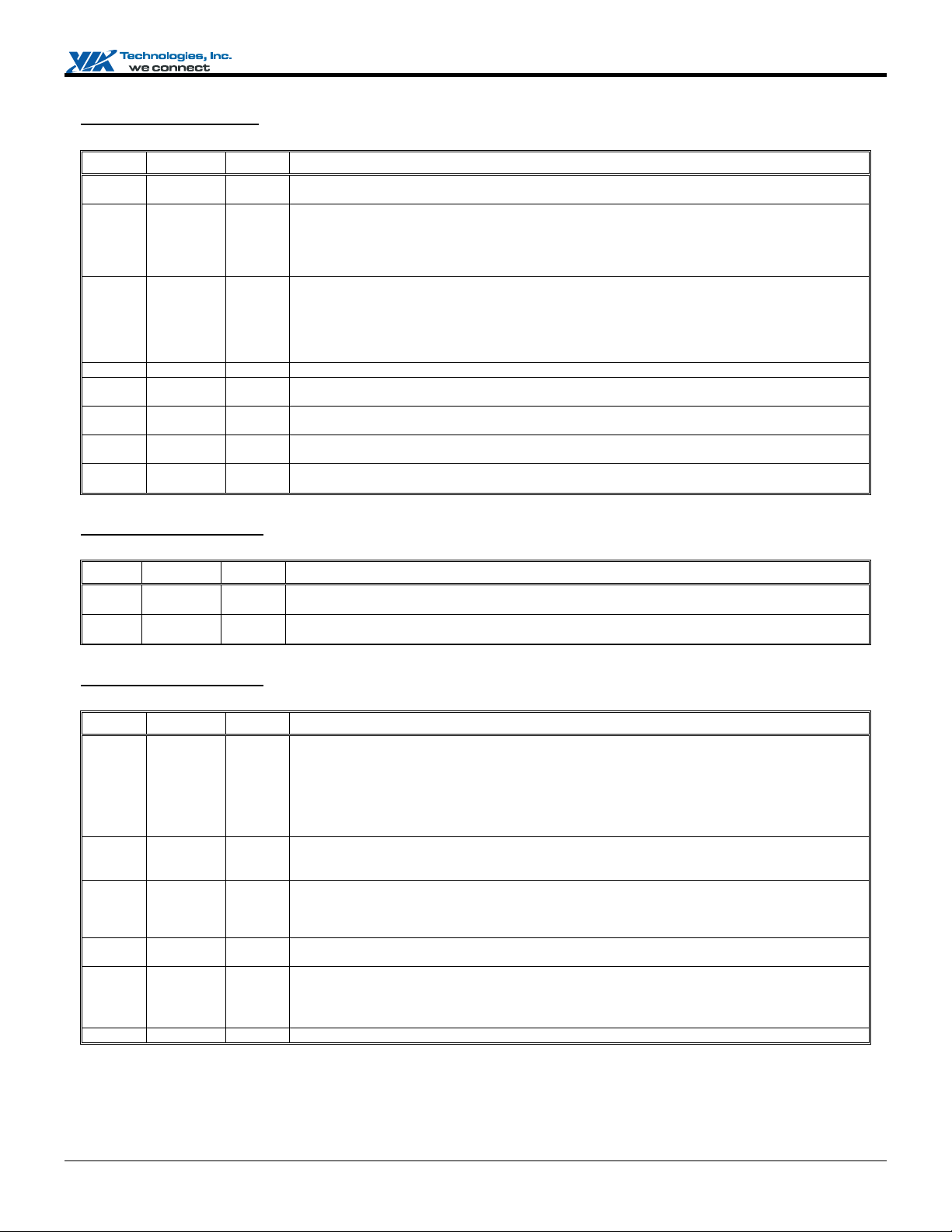

Register Table Format

Column Definitions

In the register descriptions, column “Default” indicates the power-on default value of register bit(s), while column “Attribute”

indicates access type of register bit.

Attribute Definitions

Read / Write Attributes: read / write attributes may be used together to specify combined attributes

RO: Read Only.

RZ: Read as Zero.

R1: Read as 1.

WO: Write Only. (register value can not be read by the software)

IW: Ignore Write.

MW: Must Write back what is read.

XW: Backdoor Write.

RW: Read / Write.

RW1: Write Once then Read Only after that.

RW1C: Read / Write of “1” clears bit to zero.

RsvdP: Reserved. Must do a read-modify-write to preserve the bit values.

RsvdZ: Reserved. Must write 0’s.

RSM: Bits are in resume-well.

Sticky Attributes: adding a “S” in tail to indicate a sticky register, which means that register will not be set or altered by hot reset.

Ex. RWS: Sticky-Read/Write. ROS: Sticky-Read Only. RW1CS: Sticky-Write-1-to-Clear.

Special Default Value Definitions

Dip: Means the default value is set by dip switch or strapping.

HwInit: Hardware initialized; bit default value is set by hardware to reflect related status.

:

.

nc

I

s

e

l

ogi

i

a

d

e

nt

r

i

hnol

de

i

A

qu

e

R

I

A

T

c

e

nf

o

C

V

D

N

Preliminary Revision 0.95, June 20, 2008 -4- Registers Overview

Page 13

VX800 / VX820 Series System Programming Manual

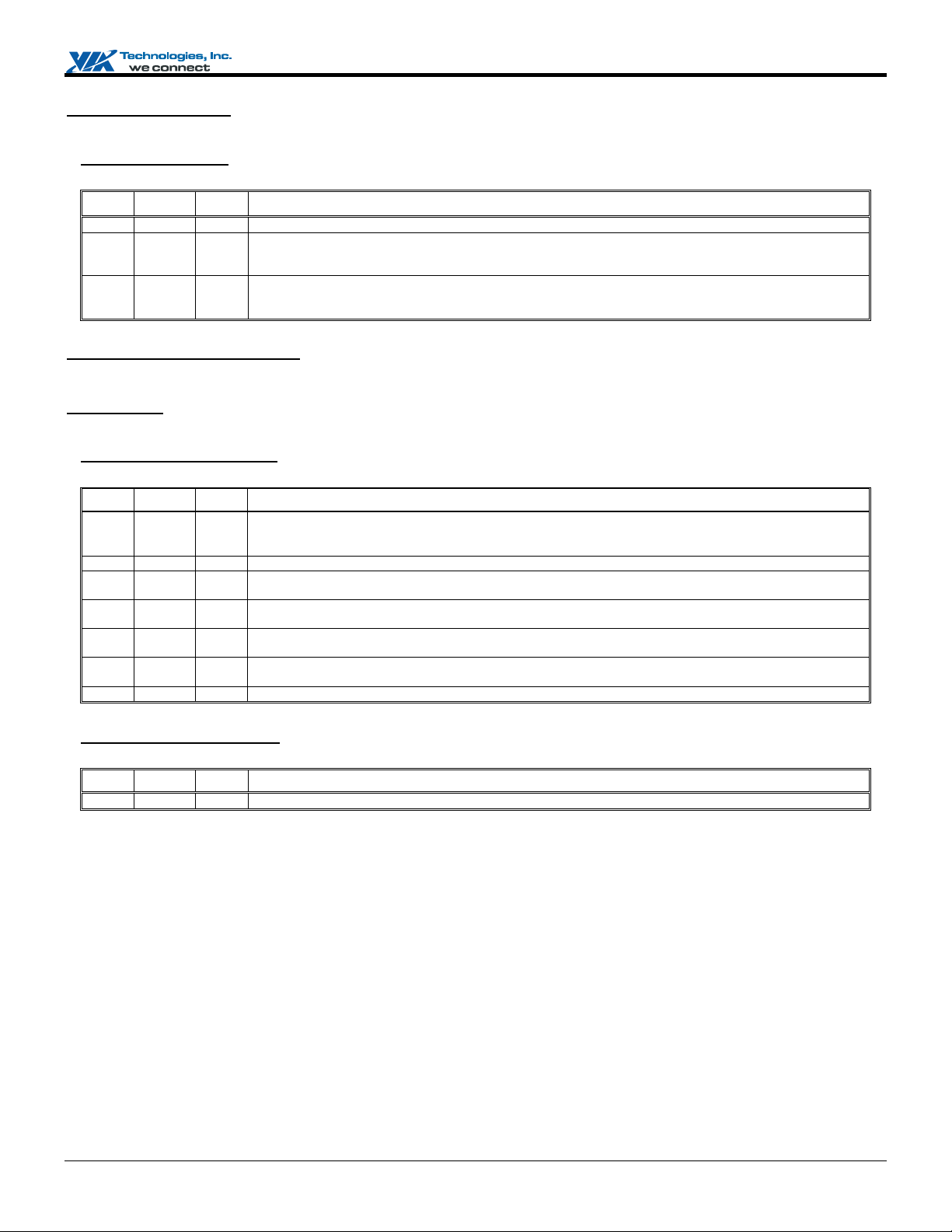

PCI Arbiter Control

I/O Port Address: 22h

PCI Arbiter Disable Default Value: 00h

Bit Attribute Default Description

7:2 RO 0

1 RW 0

0 RW 0

PCI Configuration Space I/O

This chip’s PCI space registers are addressed via the following configuration mechanism:

Mechanism #1

These ports respond only to double-word accesses. Byte or word accesses will be passed on unchanged.

I/O Port Address: CFB-CF8h

PCI Configuration Address Default Value: 0000 0000h

Reserved

PCI2 Arbiter Control

0: Enable PCI2 Bus Arbiter

1: Disable PCI2 Bus Arbiter

PCI1 Arbiter Control

0: Enable PCI1 Bus Arbiter (arbiter will respond to REQ# assertion)

1: Disable PCI1 Bus Arbiter (arbiter will not respond to PCI-1 REQ# and PREQ# assertion)

.

nc

I

s

e

Bit Attribute Default Description

31 RW 0

30:24 RO 0 Reserved (always reads 0)

23:16 RW 0

15:11 RW 0

10:8 RW 0

7:2 RW 0

1:0 RW 0 Fixed (always reads 0)

I/O Port Address: CFF-CFCh

PCI Configuration Data Default Value: 0000 0000h

Bit Attribute Default Description

31:0 RW 0

Note: Refer to PCI Bus Specification Version 2.3 for further details on operation of the above configuration registers.

V

Configuration Space Enable

0: Disable

1: Convert configuration data port writes to configuration cycles on the PCI bus

ogi

l

a

i

PCI Bus Number

Used to choose a specific PCI bus in the system

Device Number

Used to choose a specific device in the system

Function Number

Used to choose a specific function if the selected device supports multiple functions

Register Number (also called the "Offset")

Used to select a specific DWORD in the configuration space

T

A

I

PCI Configuration Data

c

e

C

hnol

de

i

nf

o

A

nt

qu

e

R

D

N

d

e

r

i

Preliminary Revision 0.95, June 20, 2008 -5- Registers Overview

Page 14

VX800 / VX820 Series System Programming Manual

NORTH MODULE REGISTER DESCRIPTIONS

Device 0 Function 0 (D0F0): Host Controller

Device 0 Function 0, the host controller, is connected to the PCI bus through AD11 as the IDSEL.

All registers are located in PCI configuration space and should be programmed using PCI configuration mechanism 1 through I/O

registers CF8 / CFC with bus number 0, device number 0 and function number 0.

Header Registers (00-3Fh)

Offset Address: 01-00h (D0F0)

Vendor ID Default Value: 1106h

Bit Attribute Default Description

15:0 RO 1106h

.

VIA Technologies ID Code

nc

Offset Address: 03-02h (D0F0)

Device ID Default Value: 0353h

Bit Attribute Default Description

15:0 RO 0353h

Offset Address: 05-04h (D0F0)

PCI Command Default Value: 0006h

Bit Attribute Default Description

15:10 RO 0

9 RO 0

8 RO 0

7 RO 0

6 RW 0

5 RO 0

4 RO 0

3 RO 0

V

2 RO 1b

1 RO 1b

0 RO 0

A

I

Device ID Code

og

Reserved

Fast Back-to-Back Cycle Enable

Hardwired to 0. (Not supported)

SERR# Enable

Hardwired to 0 (Not supported)

Address / Data Stepping

Hardwired to 0 (Not supported)

Parity Error Response

0: Ignore parity errors

T

1: Perform parity check and take normal action on detected parity errors

VGA Palette Snooping

Hardwired to 0 (Not implemented)

Memory Write and Invalidate

Hardwired to 0 (Not supported)

Respond To Special Cycle

Hardwired to 0 (Does not monitor special cycles)

PCI Master Function

Hardwired to 1 (May behave as a bus master)

Memory Space Access

Hardwired to 1 (Responds to memory space access)

I/O Space Access

Hardwired to 0 (Does not respond to I/O space)

c

e

nol

h

de

i

onf

C

A

D

N

e

i

nt

R

s

a

i

qui

e

I

l

d

e

r

Preliminary Revision 0.95, June 20, 2008 -6- North Module Register Descriptions

Page 15

VX800 / VX820 Series System Programming Manual

Offset Address: 07-06h (D0F0)

PCI Status Default Value: 0210h

Bit Attribute Default Description

15 RW1C 0

14 RO 0 Signaled System Error (SERR# asserted)

13 RW1C 0 Received Master-Abort (except special cycle)

12 RW1C 0

11 RO 0

10:9 RO 01b

8 RW1C 0

7 RO 0

6 RO 0

5 RO 0

4 RO 1b

3:0 RO 0

Offset Address: 08h (D0F0)

Revision ID Default Value: 00h

Detected Parity Error

0: No parity error detected

1: Error detected in either address or data phase

0: No abort received 1: Transaction aborted by the Master

Received Target-Abort

0: No abort received 1: Transaction aborted by the Target

Target-Abort Assertion

This chip does not assert Target-Abort

DEVSEL# Timing

00: Fast 01: Medium (default)

10: Slow 11: Reserved

Master Data Parity Error

This bit is set when bus master PERR# is asserted or observed; Rx04[6] should be set first to enable this function.

Capable of Accepting Fast Back-to-back as A Target

Hardwired to 0 (Not implemented)

User Definable Features

Hardwired to 0

66 MHz Capable

Hardwired to 0 (Not implemented)

Support New Capability List

0: No new capability 1: Support new capability

Reserved

s

e

i

og

nc

I

l

a

i

.

d

e

Bit Attribute Default Description

7:0 RO nnh

Offset Address: 0B-09h (D0F0)

Class Code Default Value: 06 0000h

Bit Attribute Default Description

23:0 RO 060000h

Offset Address: 0Ch (D0F0)

Class Code Default Value: 00h

Bit Attribute Default Description

7:0 RW 0

Offset Address: 0Dh (D0F0)

PCI Master Latency Timer Default Value: 00h

V

Chip Revision Code

Class Code

A

I

Cacheline Size

c

e

T

nol

h

de

i

onf

C

A

D

N

R

nt

qui

e

r

Bit Attribute Default Description

7:3 RW 0 PCI Bus Time Slice for CPU as A Master (in Unit of PCI clocks)

2:0 RO 0

Preliminary Revision 0.95, June 20, 2008 -7- North Module Register Descriptions

Reserved

Bit [2:1] is programmable; however, it’s read as 0.

Page 16

VX800 / VX820 Series System Programming Manual

Offset Address: 0Eh (D0F0)

Header Type Default Value: 00 or 80h

Bit Attribute Default Description

7:0 RO 00 or 80h

Offset Address: 0Fh (D0F0)

Built In Self Test (BIST) Default Value: 00h

Bit Attribute Default Description

7 RO 0

6:0 RO 0

Header Type

Could be 80 when Rx4F[0] = 1

BIST Support

Hardwired to 0 (Not supported)

Reserved

.

Offset Address: 10-2Bh (D0F0) – Reserved

Offset Address: 2D-2Ch (D0F0)

Subsystem Vendor ID Default Value: 0000h

Bit Attribute Default Description

15:0 RW1 0

Offset Address: 2F-2Eh (D0F0)

Subsystem ID Default Value: 0000h

Bit Attribute Default Description

15:0 RW1 0

Offset Address: 30-33h (D0F0) – Reserved

Offset Address: 34h (D0F0)

Capability Pointer Default Value: 00h

Subsystem Vendor ID

Subsystem ID

h

c

e

og

nol

de

i

s

e

i

nt

e

nc

I

l

a

i

qui

d

e

r

T

Bit Attribute Default Description

7:0 RO 0

I

Capability List Pointer

A

An offset address from the start of the configuration space

onf

C

A

R

Offset Address: 35-4Eh (D0F0) – Reserved

V

D

N

Preliminary Revision 0.95, June 20, 2008 -8- North Module Register Descriptions

Page 17

VX800 / VX820 Series System Programming Manual

Multiple Function and Legacy Space Access Control (4F-C6h)

Offset Address: 4Fh (D0F0)

Multiple Function Control Default Value: 00h

Bit Attribute Default Description

7:1 RO 0

0 RW 0

Offset Address: 50-B9h (D0F0) – Reserved

Offset Address: C0h (D0F0)

Graphics Memory and IO Space Access Control Default Value: 00h

Bit Attribute Default Description

7:2 RO 0

1 RW 0

0 RW 0

Offset Address: C1-C5h (D0F0) – Reserved

Offset Address: C6h (D0F0)

Legacy Space Access Control Default Value: 18h

Bit Attribute Default Description

7:2 RO 06h

1 RW 0

0 RO 0

V

Reserved

Multi-Function Support

0: Disable. Registers of functions 1-7 cannot be accessed, and the value returned will be 0FFFFFFFFh when

accessed.

1: Enable. The status will be reflected on Rx0E[7].

.

nc

Reserved

Memory Space Access

Three memory spaces of GFX are used: SL, MMIO, LL. Please see the following diagram for details.

0: Does not respond to memory space access

1: Responds to memory space access

I/O Space Access

The IO address ranges are 3B0h~3B7h, 3B8h~3BBh and 3C0h~3DFh.

0: Does not respond to I/O space access

1: Responds to I/O space access

og

e

i

s

i

I

l

a

d

e

nol

nt

r

h

de

i

A

qui

e

R

I

c

e

Reserved

MDA Resource Location

T

0: PCI2. Forward MDA access cycles to PCI2.

1: PCI1. Forward MDA access cycles to PCI1.

A

The setting of this bit overwrites the settings on the IO / Memory’s Base and Limit of other devices. MDA

Resources include Memory: B0000h-B7FFFFh and I/O Ports 3B4h, 3B5h, 3B8h, 3B9h, 3BAh, 3BFh.

Reserved

onf

C

D

N

Preliminary Revision 0.95, June 20, 2008 -9- North Module Register Descriptions

Page 18

VX800 / VX820 Series System Programming Manual

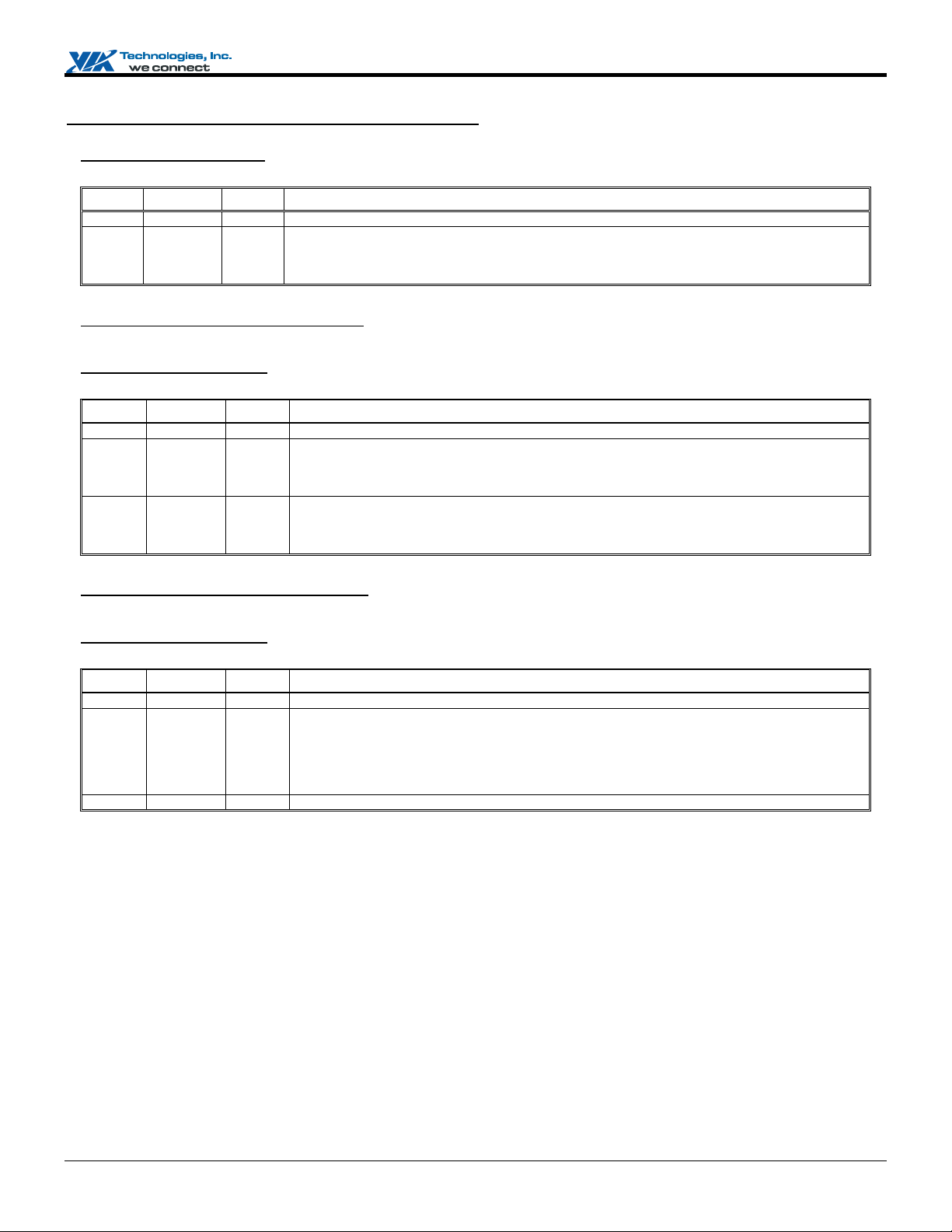

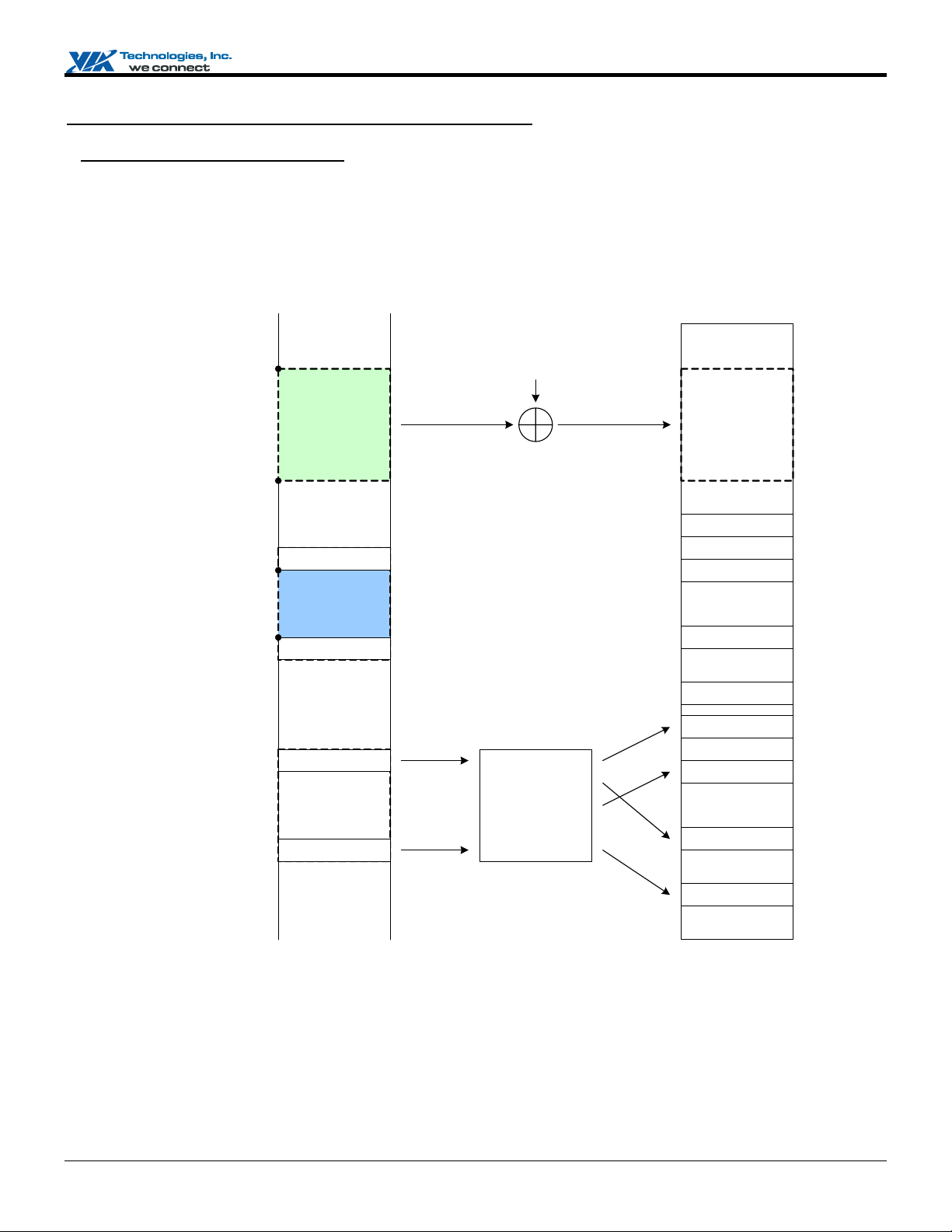

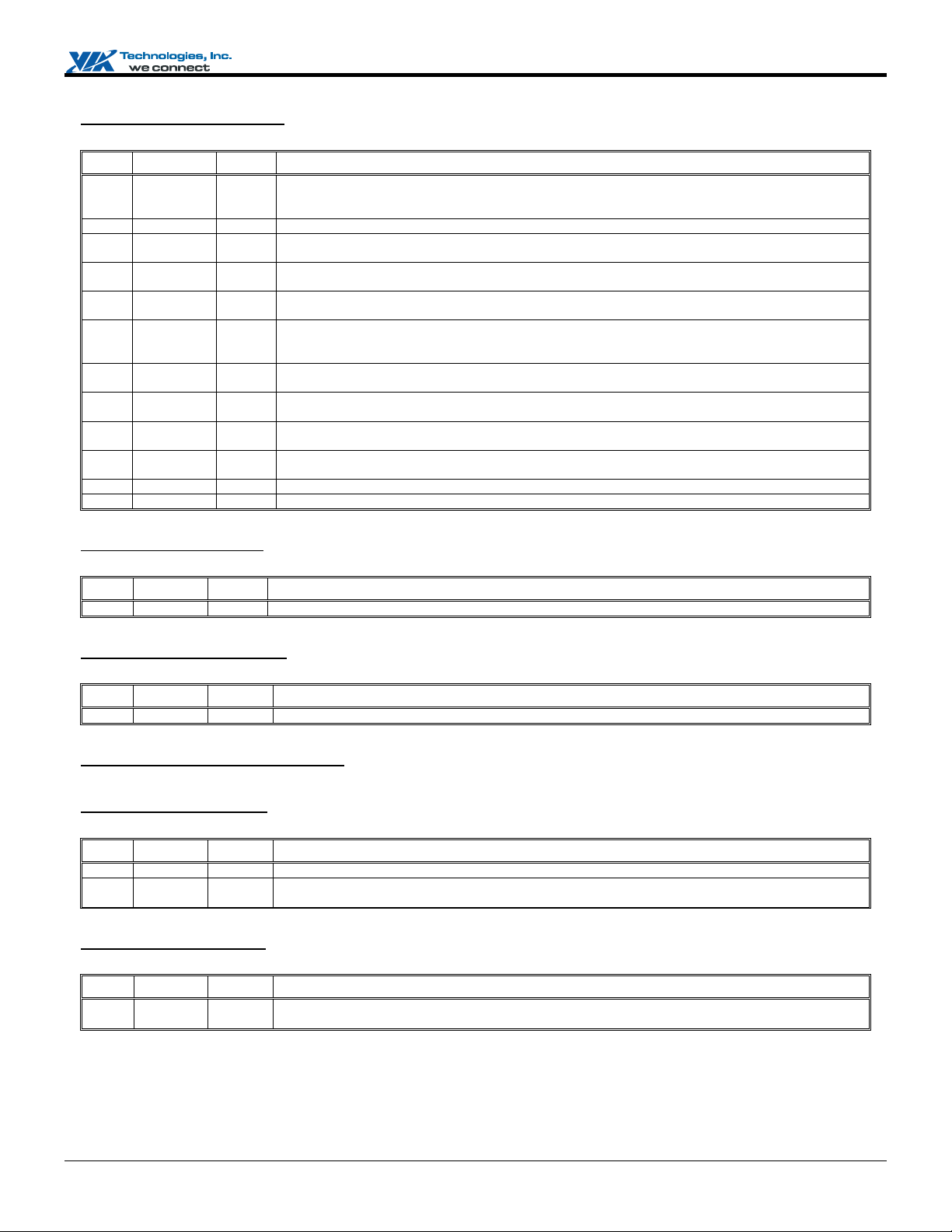

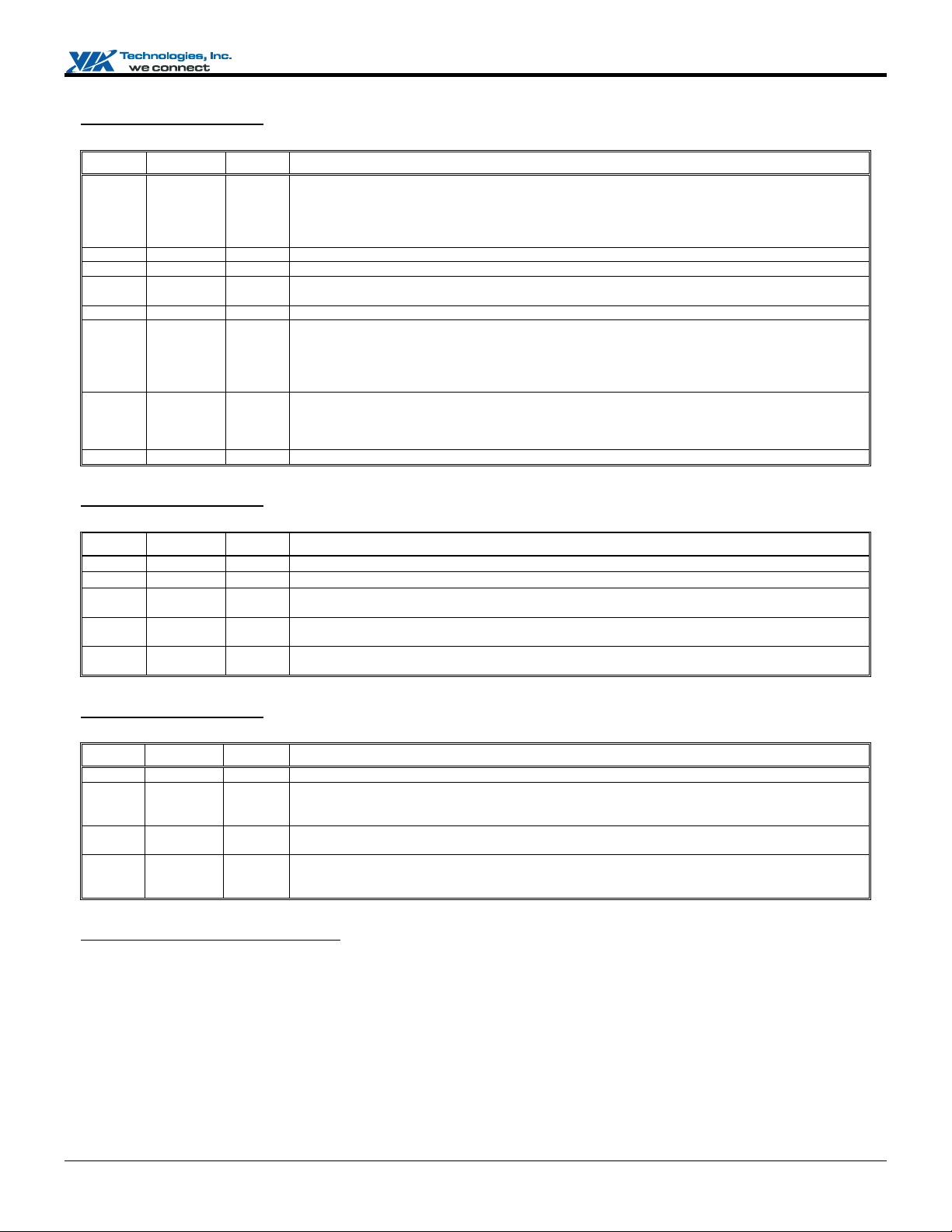

Control Registers for Integrated Graphics / Video Processor (C7-FFh)

Offset Address: C7h (D0F0) – Reserved

The integrated Graphics / Video processor uses up to two memory spaces; they are S.L. (System memory Local frame buffer)

and MMIO.

1. S.L. : Base address, RM0BS, is decided by D0F0 RxCF-C8, SL size is decided by D0F3 RxA1[6:4]

2. MMIO : Base address, RM1BS, is decided by D0F0 RxD7-D0, MMIO size is fixed to 128MB

PCI Address Space

M0LM =

RM0BS + RFBSZ

System Memory

Base Addr

.

nc

S.L.

I

S.L.

s

RM0BS

e

i

e

4 KB Page

d

4 KB Page

4 KB Page

4 KB Page

4 KB Page

4 KB Page

4 KB Page

M1LM =

RM1BS + 128MB

RM1BS

A

I

V

4 KB Page

MMIO

4 KB Page

e

T

4 KB Page

S.M.

4 KB Page

h

c

C

.....

nol

onf

.....

D

N

og

de

i

R

System

A

Memory

Mapping

Table

i

nt

qui

e

l

a

r

4 KB Page

Preliminary Revision 0.95, June 20, 2008 -10- North Module Register Descriptions

Page 19

VX800 / VX820 Series System Programming Manual

Offset Address: CB-C8h (D0F0)

GFX Shadow Memory Base 0 - S.L. Default Value: FFF0 0000h

Bit Attribute Default Description

31:4 RW FFF0 000h

3:0 RO 0h

Offset Address: CF-CCh (D0F0)

GFX Shadow Memory Base 1 - MMIO Default Value: FFF0 0000h

Bit Attribute Default Description

31:20 RW FFFh

19:0 RO 0

GFX’s Memory Base 0 Address[31:4] for S.L.

GFX’s Memory Base 0 Address[3:0] for S.L.

GFX’s Memory Base 1 Address[31:20] for MMIO

GFX’s Memory Base 1 Address[19:0] for MMIO

Offset Address: D0-FDh (D0F0) - Reserved

Offset Address: FEh (D0F0)

Internal GFX Related Control Default Value: 00h

Bit Attribute Default Description

7:5 RO 0

4 RW 0

3:2 RO 0

1 RW 0

0 RW 0

Offset Address: FFh (D0F0) - Reserved

Reserved

Enable Base VGA 16 bits Decode

0: All VGA alias range will be forwarded

1: Only forward base VGA range (Alias range will not be forwarded)

Reserved

Internal GFX Memory Space Access Control for MMIO (RM1BS~M1LM)

0: Disable. The cycle which belongs to GFX MMIO memory address range will not be passed to Internal GFX.

1: Enable. The cycle which belongs to GFX MMIO memory address range will be passed to Internal GFX.

Internal GFX Memory Space Access Control for S.L. (RM0BS~M0LM)

0: Disable. The cycle which belongs to S.L memory address range will not be passed to Internal GFX.

1: Enable. The cycle which belongs to S.L memory address range will be passed to Internal GFX.

nol

og

h

c

de

i

e

s

e

i

nt

e

nc

I

l

a

i

qui

.

d

e

r

T

I

A

onf

C

R

A

V

D

N

Preliminary Revision 0.95, June 20, 2008 -11- North Module Register Descriptions

Page 20

VX800 / VX820 Series System Programming Manual

Device 0 Function 1 (D0F1): Error Reporting

Header Registers (00-3Fh)

Offset Address: 01-00h (D0F1)

Vendor ID Default Value: 1106h

Bit Attribute Default Description

15:0 RO 1106h

Offset Address: 03-02h (D0F1)

Device ID Default Value: 1353h

Bit Attribute Default Description

15:0 RO 1353h

Offset Address: 05-04h (D0F1)

PCI Command Default Value: 0006h

Bit Attribute Default Description

15:10 RO 0

9 RO 0

8 RO 0

7 RO 0

6 RW 0

5 RO 0

4 RO 0

3 RO 0

2 RO 1b

1 RO 1b

0 RO 0

I

VIA Technologies ID Code

Device ID Code

.

nc

I

e

i

nt

R

s

a

i

qui

e

l

d

e

r

Reserved

Fast Back-to-Back Cycle Enable

Hardwired to 0 (Not supported)

SERR# Enable

Hardwired to 0 (Not supported)

Address / Data Stepping

Hardwired to 0 (Not supported)

Parity Error Response

0: Ignore parity errors

1: Perform parity check and take normal action on detected parity errors

VGA Palette Snooping

Hardwired to 0 (Not implemented)

Memory Write and Invalidate

Hardwired to 0 (Not supported)

Respond To Special Cycle

Hardwired to 0 (Does not monitor special cycles)

PCI Master Function

Hardwired to 1 (May behave as a bus master)

T

Memory Space Access

Hardwired to 1 (Responds to memory space access)

I/O Space Access

A

Hardwired to 0 (Does not respond to I/O space)

c

e

nol

h

onf

C

og

de

i

A

V

D

N

Preliminary Revision 0.95, June 20, 2008 -12- North Module Register Descriptions

Page 21

VX800 / VX820 Series System Programming Manual

Offset Address: 07-06h (D0F1)

PCI Status Default Value: 0200h

Bit Attribute Default Description

15 RO 0

14 RO 0

13 RO 0

12 RO 0

11 RO 0

10:9 RO 01b

8 RO 0

7 RO 0

6 RO 0

5 RO 0

4 RO 0

3:0 RO 0

Detected Parity Error

0: No parity error detected

1: Error detected in either address or data phase

Signaled System Error (SERR# asserted)

Received Master-Abort (except special cycle)

0: No abort received 1: Transaction aborted by the Master

Received Target-Abort

0: No abort received 1: Transaction aborted by the Target

Target-Abort Assertion

This chip does not assert Target-Abort

DEVSEL# Timing

00: Fast 01: Medium (default)

10: Slow 11: Reserved

Master Data Parity Error

This bit is set when bus master PERR# is asserted or observed ; Rx04[6] should be set first to enable this function.

Capable of Accepting Fast Back-to-back as A Target

Hardwired to 0 (Not implemented)

User Definable Features

Hardwired to 0

66 MHz Capable

Hardwired to 0 (Not implemented)

Support New Capability List

Reserved

e

i

s

nc

I

.

l

Offset Address: 08h (D0F1)

Revision ID Default Value: nnh

Bit Attribute Default Description

7:0 RO nnh

Offset Address: 0B-09h (D0F1)

Class Code Default Value: 06 0000h

Bit Attribute Default Description

23:0 RO 060000h

Offset Address: 0Ch (D0F1)

Class Code Default Value: 00h

Bit Attribute Default Description

7:0 RW 0

Offset Address: 0Dh (D0F1)

PCI Master Latency Timer Default Value: 00h

V

Chip Revision ID

A

I

e

Class Code

T

Cacheline Size

nol

h

c

onf

C

N

D

og

de

i

R

A

i

nt

qui

e

a

d

e

r

Bit Attribute Default Description

7:3 RO 0 PCI Bus Time Slice for CPU as a Master (in Unit of PCI Clocks)

2:0 RO 0

Preliminary Revision 0.95, June 20, 2008 -13- North Module Register Descriptions

Reserved

Bit [2:1] are programmable; however, it’s read as 0.

Page 22

VX800 / VX820 Series System Programming Manual

Offset Address: 0Eh (D0F1)

Header Type Default Value: 00 or 80h

Bit Attribute Default Description

7:0 RO 00 or 80h

Offset Address: 0Fh (D0F1)

Built In Self Test (BIST) Default Value: 00h

Bit Attribute Default Description

7 RO 0

6:0 RO 0

Header Type

Could be 80 when D0F0 Rx4F[0] = 1

BIST Support

Hardwired to 0 (Not supported)

Reserved

.

Offset Address: 10-2Bh (D0F1) – Reserved

Offset Address: 2D-2Ch (D0F1)

Subsystem Vendor ID Default Value: 0000h

Bit Attribute Default Description

15:0 RW1 0

Offset Address: 2F-2Eh (D0F1)

Subsystem ID Default Value: 0000h

Bit Attribute Default Description

15:0 RW1 0

Offset Address: 30-33h (D0F1) – Reserved

Offset Address: 34h (D0F1)

Capability Pointer Default Value: 00h

Subsystem Vendor ID

Subsystem ID

h

c

e

og

nol

de

i

s

e

i

nt

e

nc

I

l

a

i

qui

d

e

r

T

Bit Attribute Default Description

7:0 RO 0

Offset Address: 35-5Fh (D0F1) – Reserved

I

V

Capability List Pointer

A

An offset address from the start of the configuration space

onf

C

A

D

R

N

Preliminary Revision 0.95, June 20, 2008 -14- North Module Register Descriptions

Page 23

VX800 / VX820 Series System Programming Manual

Host Bus Error Report (60-6Fh)

Offset Address: 60h (D0F1)

Host Parity Status Default Value: 00h

Bit Attribute Default Description

7 RW1C 0

6 RW1C 0

5 RW1C 0

4 RW1C 0

3:0 RO 0

Offset Address: 61-67h (D0F1) – Reserved

Offset Address: 68h (D0F1)

Host Parity Command Default Value: 00h

Bit Attribute Default Description

7:4 RO 0

3 RW 0

2:0 RO 0

Offset Address: 69-FFh (D0F1) – Reserved

Host Address Parity Error Detected

0: Not detected

1: Detected

Host Data Parity Error Detected

0: Not detected

1: Detected

AGP Access Above 4G Detected

0: No above 4GB AGP cycles being detected

1: AGP Access Above 4GB detected

Host LOCK Cycle to PCI Detected

0: Not detected

1: Detected

Reserved

.

nc

I

s

e

i

l

Reserved

Parity Test Mode

0: Disable (normal mode) 1: Enable (invert the parity bit)

Reserved

nol

og

nt

i

a

d

e

r

h

c

e

de

i

qui

e

T

I

A

onf

C