Page 1

USER MANUAL

EPIA-M920

Mini-ITX embedded board

1.04-06182013-175200

Page 2

Copyright

Copyright © 2013 VIA Technologies Incorporated. All rights reserved.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language,

in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written

permission of VIA Technologies, Incorporated.

Trademarks

All trademarks are the property of their respective holders.

Disclaimer

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no

warranties, implied or otherwise, in regard to this document and to the products described in this document. The information

provided in this document is believed to be accurate and reliable as of the publication date of this document. However, VIA

Technologies assumes no responsibility for the use or misuse of the information (including use or connection of extra

device/equipment/add-on card)

The information and product specifications within this document are subject to change at any time, without notice and without

obligation to notify any person of such change.

VIA Technologies, Inc. reserves the right the make changes to the products described in this manual at any time without prior

notice.

Regulatory Compliance

FCC

FCC----A Radio Frequency Interference Statement

A Radio Frequency Interference Statement

FCCFCC

A Radio Frequency Interference StatementA Radio Frequency Interference Statement

This equipment has been tested and found to comply with the limits for a class A digital device, pursuant to part 15 of the FCC

rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a

commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in

accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a

residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his

personal expense.

Notice 1

Notice 1

Notice 1Notice 1

The changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to

operate the equipment.

Notice 2

Notice 2

Notice 2Notice 2

Shielded interface cables and A.C. power cord, if any, must be used in order to comply with the emission limits.

Notice 3

Notice 3

Notice 3Notice 3

The product described in this document is designed for general use, VIA Technologies assumes no responsibility for the conflicts

or damages arising from incompatibility of the product. Check compatibility issue with your local sales representatives before

placing an order.

in this document and for any patent infringements that may arise from the use of this document.

Tested To Comply

With FCC Standards

FOR HOME OR OFFICE USE

Page 3

Battery Recycling and Disposal

Only use the appropriate battery specified for this product.

Do not re-use, recharge, or reheat an old battery.

Do not attempt to force open the battery.

Do not discard used batteries with regular trash.

Discard used batteries according to local regulations.

Safety Precautions

Always read the safety instructions carefully.

Keep this User's Manual for future reference.

All cautions and warnings on the equipment should be noted.

Keep this equipment away from humidity.

Lay this equipment on a reliable flat surface before setting it up.

Make sure the voltage of the power source and adjust properly 110/220V before connecting

the equipment to the power inlet.

Place the power cord in such a way that people cannot step on it.

Always unplug the power cord before inserting any add-on card or module.

If any of the following situations arises, get the equipment checked by authorized service

personnel:

The power cord or plug is damaged.

Liquid has penetrated into the equipment.

The equipment has been exposed to moisture.

The equipment has not worked well or you cannot get it work according to User's Manual.

The equipment has dropped and damaged.

The equipment has obvious sign of breakage.

Do not leave this equipment in an environment unconditioned or in a storage temperature

above 60°C (140°F). The equipment may be damaged.

Do not leave this equipment in direct sunlight.

Never pour any liquid into the opening. Liquid can cause damage or electrical shock.

Do not place anything over the power cord.

Do not cover the ventilation holes. The openings on the enclosure protect the equipment

from overheating

Page 4

EPIA

EPIA----M920

EPIAEPIA

Box Contents and Ordering Information

Model Number

Model Number CPU Frequency

Model NumberModel Number

EPIA-M920-10E 1.0GHz Eden™ X2 Standard kit

EPIA-M920-12Q 1.2GHz QuadCore Standard kit

CPU Frequency Description

CPU FrequencyCPU Frequency

Description

DescriptionDescription

1 x SATA cable

1 x I/O bracket

1 x SATA cable

1 x I/O bracket

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

iv

Page 5

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

Table of Contents

1.

1. Product Overview

Product Overview................................

1.1.

Product OverviewProduct Overview

1.1.

Key Features and Benefits........................................................................... 2

1.1.1. VIA QuadCore /VIA Eden™ X2 Processor ......................................... 2

1.1.2. VIA VX11H MSPIII Chipset.................................................................... 3

1.1.3. Modular Expansion Options................................................................. 3

1.2.

Product Specifications................................................................................. 4

1.3.

Layout Diagram ............................................................................................. 7

1.4.

Product Dimensions..................................................................................... 2

1.5.

Height Distribution....................................................................................... 3

2.

2. I/O Interface

I/O Interface................................

2.2.

I/O InterfaceI/O Interface

2.1.

External I/O Ports ......................................................................................... 5

2.1.1. PS/2 Port.................................................................................................... 6

2.1.2. HDMI® Port............................................................................................... 7

2.1.3. COM Port.................................................................................................. 8

2.1.4. RJ45 LAN port: Gigabit Ethernet ......................................................... 9

2.1.5. Audio Ports.............................................................................................10

2.1.6. VGA Port................................................................................................. 11

2.1.7. USB 2.0 Port ........................................................................................... 12

2.1.8. USB 3.0 Port ........................................................................................... 13

2.2.

Onboard Connectors ................................................................................14

2.2.1. ATX Power Connector......................................................................... 14

2.2.2. LVDS panel connectors ....................................................................... 15

2.2.3. LVDS Inverter Connector ....................................................................18

2.2.4. Digital I/O pin headers ........................................................................ 20

2.2.5. External Thermal Resister.................................................................... 21

2.2.6. Front Panel Pin Header ........................................................................22

2.2.7. SMBus Pin Header................................................................................. 24

2.2.8. CPU and System Fan Connectors ...................................................... 25

2.2.9. SATA Connectors .................................................................................26

................................................................

................................................................

................................................................

................................................................

................................................................

................................................................

................................................................

................................................................

................................ 1111

................................................................

..........................................

................................................................

User Manual

User ManualUser Manual

.......... 5555

....................

v

Page 6

EPIA

2.2.10. USB 2.0 Pin Headers............................................................................. 27

2.2.11. COM Pin Header for COM2~COM4 ................................................ 28

2.2.12. PS/2 Keyboard and Mouse Pin Header ............................................29

2.2.13. Front Audio Pin Header ....................................................................... 30

2.2.14. SPI address select .................................................................................31

2.2.15. SPI Pin Header .......................................................................................32

2.2.16. LPC Pin Header ...................................................................................... 33

2.2.17. SPDIF Connector ................................................................................... 34

2.2.18. CMOS Battery Slot................................................................................ 35

2.2.19. USB3.0 Connector................................................................................. 36

3.

3. Jumpers

Jumpers ................................

3.3.

JumpersJumpers

3.1.

3.2.

3.3.

3.4.

3.4.1. VDD Power Select................................................................................ 41

3.5.

................................................................

................................................................

Clear CMOS Jumper.................................................................................. 37

SATA DOM Power Select Jumper ......................................................... 38

COM1 and COM2 Voltage Select Jumper........................................... 39

COM3 and COM4 Voltage Select Jumper........................................... 40

LVDS Jumper Settings ............................................................................... 42

................................................................

................................................................

...............................................

................................................................

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

............... 37

..............................

37

3737

4.

4. Expansion Slots

Expansion Slots................................

4.4.

Expansion SlotsExpansion Slots

4.1.

DDR3 Memory Slots ..................................................................................43

4.1.1. Installing a Memory Module .............................................................. 44

Figure 42: Locking the memory module ...........................................................44

4.1.2. Removing a Memory Module............................................................. 45

4.1.3. PCI Express Slot .................................................................................... 46

5.

5. Hardware Installatio

Hardware Installationnnn ................................

5.5.

Hardware InstallatioHardware Installatio

5.1.

Installing into a Chassis............................................................................. 47

5.1.1. Suggested minimum chassis dimensions ......................................... 47

5.1.2. Suggested minimum chassis height................................................... 48

5.1.3. Suggested keepout areas .................................................................... 50

6.

6. BIOS Setup Utility

BIOS Setup Utility................................

6.6.

BIOS Setup UtilityBIOS Setup Utility

................................................................

................................................................

................................................................

................................................................

................................................................

................................................................

................................................................

................................................................

........................................................

................................................................

..............................................................

................................................................

..................................

................................................................

........................ 47

................................................

.............................. 51

............................................................

.. 43

43

....

4343

47

4747

51

5151

vi

Page 7

EPIA

6.1.

Entering the BIOS Setup Utility............................................................... 51

6.2.

Control Keys................................................................................................ 51

6.3.

Navigating the BIOS Menus ..................................................................... 52

6.4.

Getting Help................................................................................................ 52

6.5.

Main Menu ................................................................................................... 53

6.5.1. BIOS Information ................................................................................... 53

6.5.2. Memory Information ............................................................................. 53

6.5.3. System Language................................................................................... 53

6.5.4. System Date............................................................................................ 54

6.5.5. System Time ........................................................................................... 54

6.6.

Advanced Settings ..................................................................................... 55

6.6.1. ACPI Settings.......................................................................................... 56

6.6.2. S5 RTC Wake Settings .......................................................................... 57

6.6.3. CPU Information .................................................................................... 58

6.6.4. SATA Configuration.............................................................................. 59

6.6.5. F71869 Super IO Configuration ......................................................... 60

6.6.6. F71869 H/W Monitor ...........................................................................61

6.6.7. Clock Generator Configuration.......................................................... 62

6.6.8. On Board Configuration ......................................................................63

6.7.

Chipset Settings .......................................................................................... 65

6.7.1. DRAM Configuration ............................................................................66

6.7.2. Video Configuration ............................................................................. 69

6.7.3. UART Configuration.............................................................................. 71

6.7.4. PMU_ACPI Configuration ....................................................................72

6.7.5. HDAC Configuration ............................................................................ 74

6.7.6. SDIO_CR Configuration .......................................................................75

6.7.7. Others Configuration............................................................................ 77

6.8.

Boot Settings ............................................................................................... 78

6.8.1. Boot Configuration................................................................................ 78

6.8.2. Boot Option Priorities ..........................................................................79

6.8.3. Network Device BBS Priorities ...........................................................79

6.9.

Security Settings ......................................................................................... 80

6.9.1. Security Settings .................................................................................... 80

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

vii

Page 8

EPIA

6.10. Save & Exit Options ................................................................................... 82

6.10.1. Save Changes and Exit ......................................................................... 82

6.10.2. Discard Changes and Exit.................................................................... 82

6.10.3. Save Changes and Reset...................................................................... 82

6.10.4. Discard Changes and Reset................................................................. 83

6.10.5. Save Changes .........................................................................................83

6.10.6. Discard Changes.................................................................................... 83

6.10.7. VIA Networking Bootagent................................................................. 83

6.10.8. Launch EFI Shell from filesystem device ......................................... 83

7.

7. Driver Installation

Driver Installation................................

7.7.

Driver InstallationDriver Installation

7.1.

Microsoft Driver Support.......................................................................... 85

7.2.

Linux Driver Support.................................................................................. 85

Appendix A. Power Consumption Report

Appendix A. Power Consumption Report................................

Appendix A. Power Consumption ReportAppendix A. Power Consumption Report

A.1. EPIA-M920 Rev. 2 DVT ATX POWER ............................................................ 87

A.1.1. Playing DVD – Power DVD 5.0 ...............................................................87

A.1.2. Playing MP3-Media Player ........................................................................88

A.1.3. Running Network Application ................................................................. 88

A.1.4. IDLE................................................................................................................ 89

A.1.5. RUN Burn-in Test ........................................................................................ 89

A.1.6. S3.................................................................................................................... 90

A.1.7. S5.................................................................................................................... 90

A.1.8. EuP/ErP Enable S3 ......................................................................................91

A.1.9. EuP/ErP Enable S5 ......................................................................................91

................................................................

................................................................

...............................................................

................................................................

...............................................................

................................................................

EPIA----M920

M920 User Manual

M920 M920

User Manual

User ManualUser Manual

EPIAEPIA

............................... 85

..............................................................

............................... 87

..............................................................

85

8585

87

8787

viii

Page 9

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

Lists of Figures

Figure 1: Layout diagram of the EPIA-M920 mainboard (top view) ...................... 7

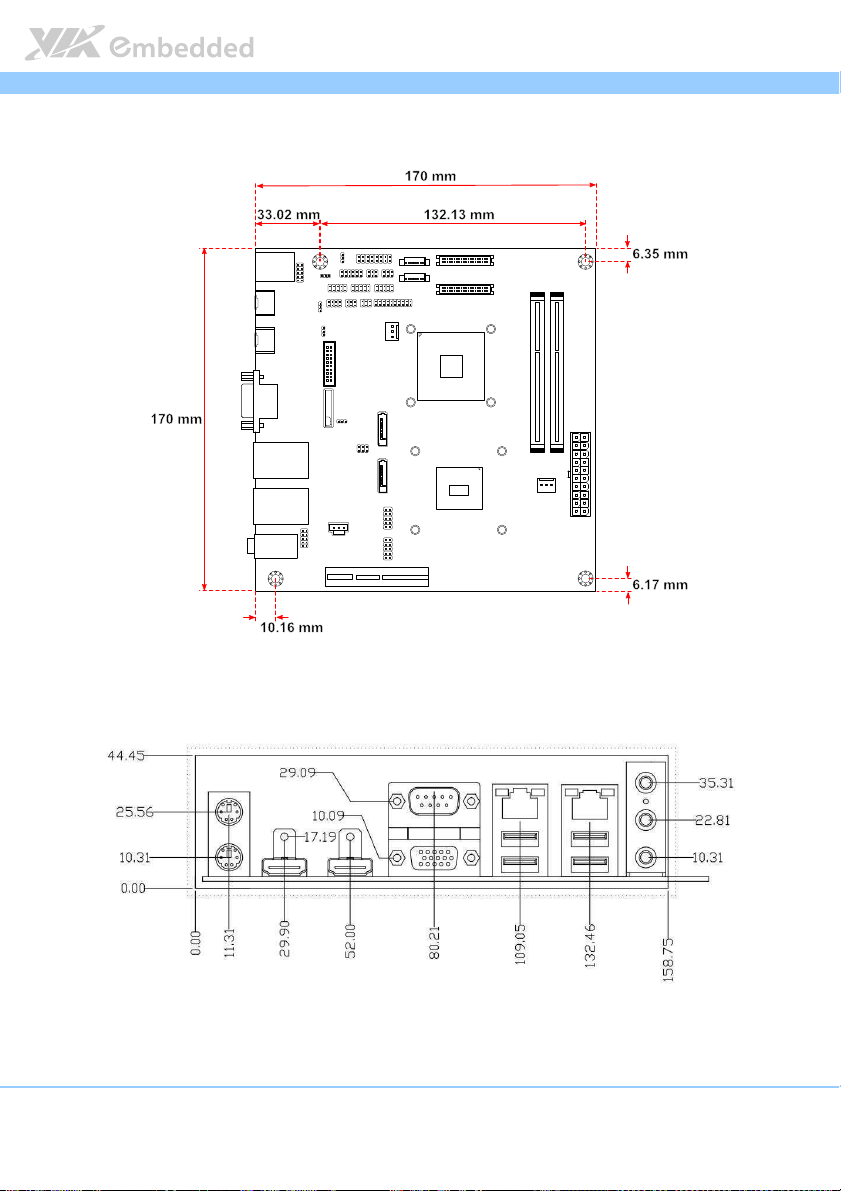

Figure 2: Mounting holes and dimensions of the EPIA-M920 mainboard............ 2

Figure 3: External I/O port dimensions of the EPIA-M920 mainboard ................. 2

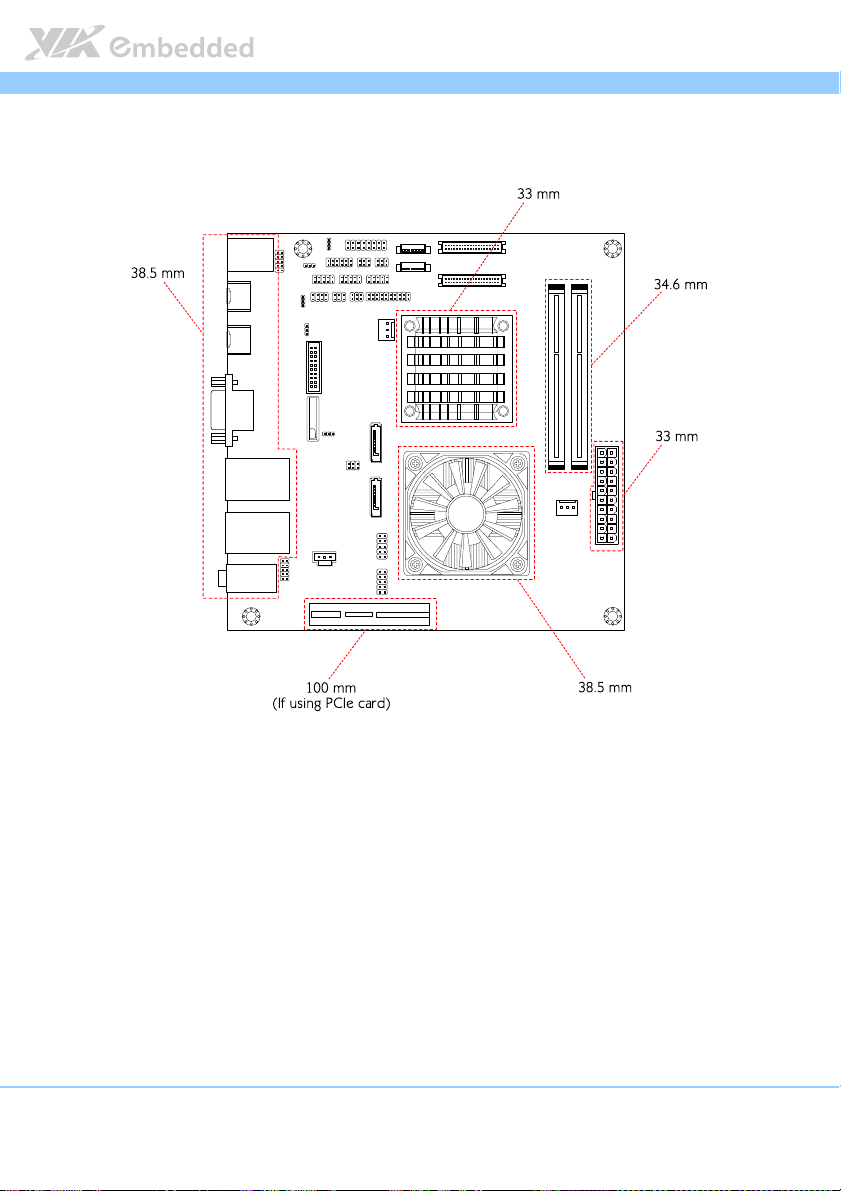

Figure 4: Height distribution of the EPIA-M920 mainboard (for Quad Core

model) ................................................................................................................................. 3

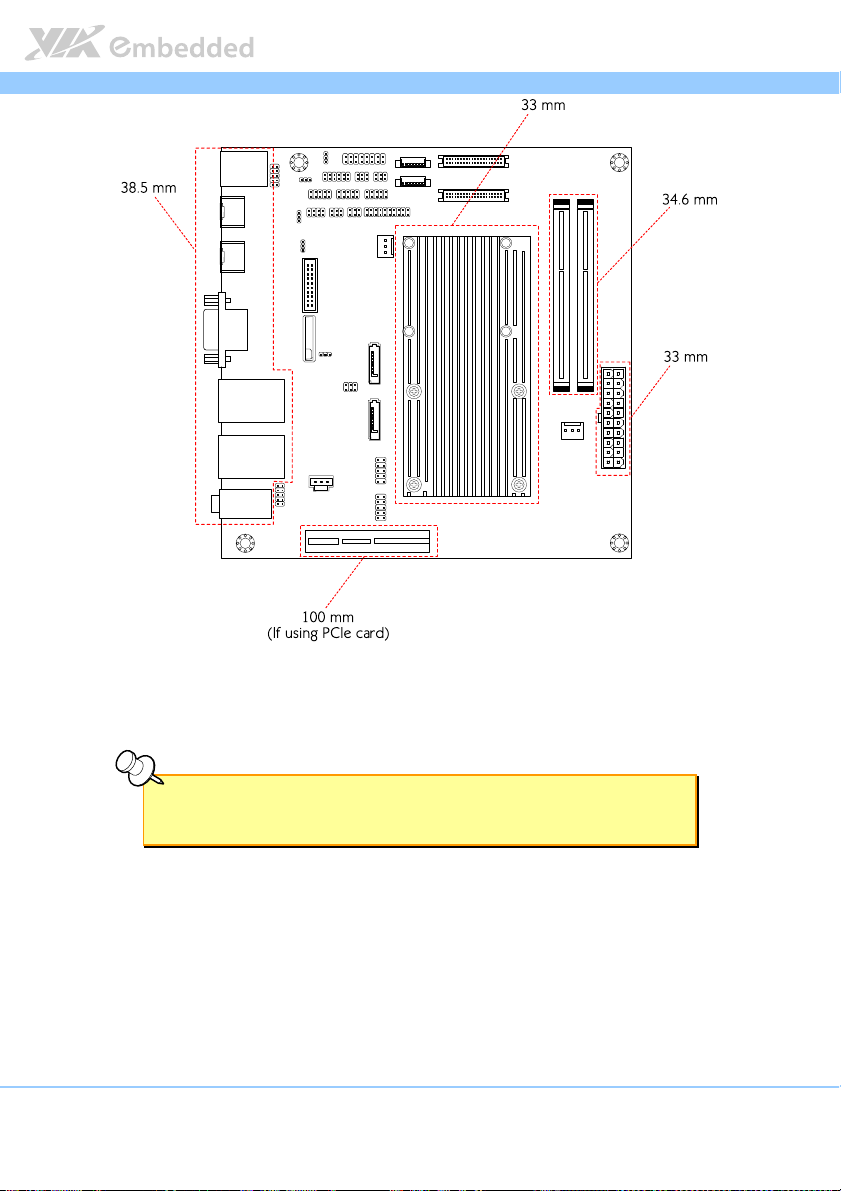

Figure 5: Height distribution of the EPIA-M920 mainboard (for Dual Core

model) ................................................................................................................................. 4

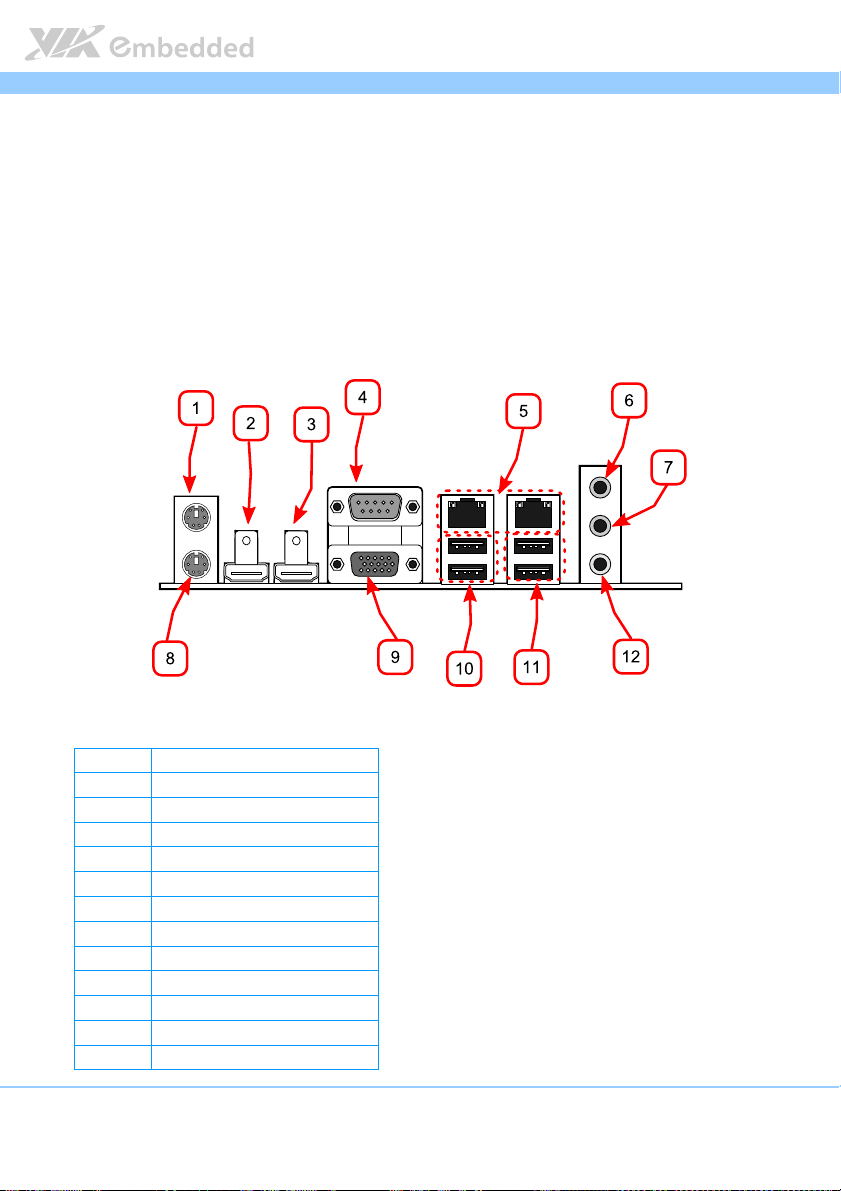

Figure 6: External I/O ports............................................................................................. 5

Figure 7: PS/2 port pinout diagram ............................................................................... 6

Figure 8: HDMI® port pinout diagram........................................................................... 7

Figure 9: COM port pinout diagram.............................................................................. 8

Figure 10: Gigabit Ethernet port pinout diagram ....................................................... 9

Figure 11: Audio jack receptacle stack....................................................................... 10

Figure 12: VGA port pinout diagram ..........................................................................11

Figure 13: USB port pinout diagram............................................................................ 12

Figure 14: USB 3.0 port pinout diagram..................................................................... 13

Figure 15: ATX power connector ................................................................................14

Figure 16: LVDS panel connector................................................................................ 15

Figure 17: LVDS Inverter connector ............................................................................ 18

Figure 18: Digital I/O pin headers ............................................................................... 20

Figure 19: External Thermal Resister........................................................................... 21

Figure 20: Front panel pin header ............................................................................... 22

Figure 21: SMBus pin header ........................................................................................ 24

Figure 22: CPU and System Fan connectors ..............................................................25

Figure 23: SATA connectors ......................................................................................... 26

Figure 24: USB pin headers ........................................................................................... 27

Figure 25: COM pin headers......................................................................................... 28

Figure 26: PS/2 keyboard and mouse pin header .................................................... 29

Figure 27: Front audio pin header ...............................................................................30

Figure 28: SPI address select ........................................................................................ 31

Figure 29: SPI pin header ............................................................................................... 32

ix

Page 10

EPIA

Figure 30: LPC pin header.............................................................................................. 33

Figure 31: SPDIF connector ...........................................................................................34

Figure 32: CMOS battery slot ....................................................................................... 35

Figure 33: USB 3.0 connectors .....................................................................................36

Figure 34: CLEAR CMOS jumper .................................................................................37

Figure 35: SATA DOM voltage select jumper.......................................................... 38

Figure 36: COM1 and COM2 voltage select jumper .............................................. 39

Figure 37: COM3 and COM4 voltage select jumper .............................................. 40

Figure 38: VDD Power Select....................................................................................... 41

Figure 39: LVDS jumper settings ..................................................................................42

Figure 40: DDR3 memory slots ....................................................................................43

Figure 41: Inserting the memory module................................................................... 44

Figure 42: Locking the memory module .................................................................... 44

Figure 43: Disengaging the SODIMM locking clips ................................................. 45

Figure 44: Removing the memory module ................................................................ 45

Figure 45: PCI Express slot ............................................................................................ 46

Figure 46: Suggested minimum chassis dimensions ................................................ 47

Figure 47: Suggested minimum internal chassis ceiling height (for dual core

model) ............................................................................................................................... 48

Figure 48: Suggested minimum internal chassis ceiling height (for quad core

model) ............................................................................................................................... 49

Figure 49: Suggested keepout areas ........................................................................... 50

Figure 50: Illustration of the Main menu screen....................................................... 53

Figure 51: Illustration of the Advanced Settings screen......................................... 55

Figure 52: Illustration of the ACPI Settings screen .................................................. 56

Figure 53: Illustration of S5 RTC Wake Settings screen.......................................... 57

Figure 54: Illustration of CPU Information screen .................................................... 58

Figure 55: Illustration of SATA Configuration screen ............................................. 59

Figure 56: Illustration of F71869 Super IO Configuration screen......................... 60

Figure 57: Illustration of F71869 H/W Monitor screen ........................................... 61

Figure 58: Illustration of Clock Generator Configuration screen ......................... 62

Figure 59: Illustration of On Board Configuration screen...................................... 63

Figure 60: Illustration of Chipset Settings screen..................................................... 65

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

x

Page 11

EPIA

Figure 61: Illustration of DRAM Configuration screen ............................................ 66

Figure 62: Illustration of Video Configuration screen .............................................69

Figure 63: Illustration of UART Configuration screen .............................................71

Figure 64: Illustration of PMU_ACPI Configuration screen.................................... 72

Figure 65: Illustration of Other Control screen........................................................ 73

Figure 66: Illustration of HDAC Configuration screen............................................ 74

Figure 67: Illustration of SDIO_CR Configuration screen....................................... 75

Figure 68: Illustration of Others Configuration screen ...........................................77

Figure 69: Illustration of Boot Settings screen.......................................................... 78

Figure 70: Illustration of Security Settings screen.................................................... 80

Figure 71: Illustration of Save & Exit Options screen .............................................82

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

xi

Page 12

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

Lists of Tables

Table 1: PS/2 port pinout ................................................................................................ 6

Table 2: HDMI® port pinout ........................................................................................... 7

Table 3: COM port pinout .............................................................................................. 8

Table 4: Gigabit Ethernet port pinout .......................................................................... 9

Table 5: Gigabit Ethernet LED color definition .......................................................... 9

Table 6: Audio jack receptacle pinout....................................................................... 10

Table 7: VGA port pinout ............................................................................................. 11

Table 8: USB port pinout............................................................................................... 12

Table 9: USB 3.0 port pinout........................................................................................ 13

Table 10: ATX power connector pinout ...................................................................14

Table 11: LVDS1 panel pinout ..................................................................................... 16

Table 12: LVDS2 panel pinout ..................................................................................... 17

Table 13: LVDS Inverter connector pinout................................................................ 19

Table 14: Digital I/O pin headers pinout................................................................... 20

Table 15: External thermal resister pinout................................................................ 21

Table 16: Front panel pin header pinout................................................................... 23

Table 17: SMBus pin header pinout............................................................................ 24

Table 18: CPU and System Fan connector pinouts .................................................25

Table 19: SATA connector pinouts............................................................................. 26

Table 20: USB pin header pinouts............................................................................... 27

Table 21: COM pin header pinout .............................................................................. 28

Table 22: PS/2 keyboard and mouse pin header pinout ........................................ 29

Table 23: Front audio pin header pinout................................................................... 30

Table 24: SPI address select pinout............................................................................ 31

Table 25: SPI pin header pinout ..................................................................................32

Table 26: LPC pin header pinout ................................................................................. 33

Table 27: SPDIF connector pinout ..............................................................................34

Table 28: CMOS battery slot pinout .......................................................................... 35

Table 29: USB 3.0 connector pinout........................................................................... 36

Table 30: CLEAR CMOS jumper settings ................................................................... 37

Table 31: SATA DOM voltage select jumper settings ........................................... 38

xii

Page 13

EPIA

Table 32: COM1 and COM2 voltage select jumper settings ...............................39

Table 33: COM3 and COM4 voltage select jumper settings ...............................40

Table 34: VDD Power Select pinout .......................................................................... 41

Table 35: LVDS jumper settings................................................................................... 42

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

xiii

Page 14

EPIA

1.

1. Product Overview

Product Overview

1.1.

Product OverviewProduct Overview

The VIA EPIA-M920 Mini-ITX mainboard is a high performance native x86

mainboard designed mainly for embedded, POS, Kiosk, ATM and digital media

application. It can also be used for various domain applications such as

desktop PC, industrial PC, etc. The mainboard is based on the VIA VX11H

MSPIII (Media System Processor) chipset that features the VIA Chrome

DX11 with 2D/3D graphics and video accelerators for rich digital media

performance.

The VIA EPIA-M920 includes a powerful, secure, and efficient VIA Eden

VIA QuadCore processor. The VIA Eden

Padlock Security Engine, VIA CoolStream

Technology Suite, and VIA TwinTurbo

QuadCore processor includes the VIA AES Security Engine, VIA CoolStream

Architecture and VIA PowerSaver

The VIA EPIA-M920 has two 1333 MHz DDR3 SODIMM slots that support up

to 16 GB memory size. The VIA EPIA-M920 provides support for high fidelity

audio with its included VIA VT2021 High Definition Audio Codec. In addition

it supports two SATA 3Gb/s storage devices.

™

X2 processor includes the VIA

™

Architecture, VIA StepAhead™

™

technology. Whereas the VIA

™

Technology.

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

™

640

™

X2 /

™

The VIA EPIA-M920 is compatible with a full range of Mini-ITX chassis as well

as FlexATX and MicroATX enclosures and power supplies. The VIA EPIA-

®

M920 is fully compatible with Microsoft

and Linux operating systems.

1

Page 15

EPIA

EPIA----M920

EPIAEPIA

1.1. Key Features and Benefits

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

1.1.1. VIA QuadCore /VIA Eden

™

X2 Processor

The VIA QuadCore is a 64-bit superscalar x86 quad core (Isaiah) processor

combine on two dies. It is based on advanced 40 nanometer process

technology packed into an ultra compact NanoBGA2 package measuring

21mm x 21mm. The VIA QuadCore processor delivers a superb performance

on multi-tasking, multimedia playback, productivity and internet browsing in a

low power budget.

The VIA Eden X2 is a 64-bit superscalar x86 dual core processor based on a

40 nanometer process technology. Packed into an ultra compact NanoBGA2

package (measuring 21mm x 21mm), it delivers an energy-efficient yet

powerful performance, with cool and quiet operation.

Note:

Note:

Note:Note:

For Windows 7 and Windows Server 2008 R2 users only:

If encounter the issue such as the operating system recognize the VIA Dual-Core CPU as two processors

instead of one processor with two cores. Download and install the hotfix released by Microsoft to

address this issue. The downloadable hotfix is available at http://support.microsoft.com/kb/2502664

http://support.microsoft.com/kb/2502664

http://support.microsoft.com/kb/2502664http://support.microsoft.com/kb/2502664

Both VIA QuadCore and Eden X2 processors are ideal for embedded system

applications such as industrial PCs, test machines, measuring equipment,

digital signage, medical PCs, monitoring systems, gaming machines, in-vehicle

entertainment, etc.

2

Page 16

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

1.1.2. VIA VX11H MSPIII Chipset

The VIA VX11H is the fourth generation, highly integrated Media System

Processor which provides high quality digital video streaming and high

definition video playback. It features the VIA Chrome

graphics and video processor, High Definition video decoder

™

640 DX11 2D/3D

and supports

DDR3 1333 controller and USB 3.0 interface.

The VIA VX11H offers superb-graphics performance, immersive visual

experience, and supports DirectX 11.0 that allows realistic 3D rendering and

increased visual acuity. It is also based on a highly sophisticated power

efficient architecture that enables such rich integration into a compact package.

1.1.3. Modular Expansion Options

The VIA EPIA-M920 ensures long-term usability with its support for industry

standard expansion options. Its support for legacy PCI expansion cards helps

to smooth and reduce the costs of transitioning to newer expansion

technologies. The VIA EPIA-M920 enables companies to slowly roll out

upgrades as necessary instead of having to replace everything all at once. This

ensures that companies using the EPIA-M920 obtain the maximum benefits

from its past investments in PCI expansion cards.

The VIA EPIA-M920 also includes a 4-Lane PCI Express 2.0 expansion slot that

provides protection against obsolescence.

3

Page 17

EPIA

EPIA----M920

EPIAEPIA

1.2. Product Specifications

Processor

Processor

ProcessorProcessor

VIA Nano X4 1.2GHz+ with fansink (27.5W)

VIA Eden X2 1.0GHz+ fanless

7 bit VID

Chipset

Chipset

ChipsetChipset

VIA VX11H MSPIII 33 x 33mm

System Memory

System Memory

System MemorySystem Memory

2 x DDR3 1333 SODIMM

Supports up to 16 GB memory size

Note:

Note:

Note:Note:

The real memory size may show less than 16GB due to some capacity are used for BIOS or other

functions.

VGA

VGA

VGAVGA

Integrated VIA Chrome™ 640 HD DX11 3D/2D graphics with MPEG2, WMV9/VC1,

H.264 decoding acceleration

Onboard

Onboard Peripherals

Onboard Onboard

Onboard I/O Connectors

Onboard I/O Connectors

Onboard I/O ConnectorsOnboard I/O Connectors

Peripherals

PeripheralsPeripherals

Serial

Serial ATA

ATA

Serial Serial

ATAATA

2 SATA connectors

Onboard LAN

Onboard LAN

Onboard LANOnboard LAN

2 x VIA VT6130 PCIe Gigabit Ethernet Controller

Onboard Audio

Onboard Audio

Onboard AudioOnboard Audio

VIA VT2021 High Definition Audio Codec

Onboard Super I

Onboard Super I////OOOO

Onboard Super IOnboard Super I

Fintek F71869E

2 x USB 2.0 pin headers for 4 ports

1 x USB3.0 pin header for 1 port

2 x SATA connectors

2 x SATA DOM Power selectors

1 x Dual channel 18/24-bit LVDS (DVP, VT1636)

1 x Single channel 18/24-bit LVDS (VX11H internal)

2 x Backlight control connectors for inverter power and brightness control

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

4

Page 18

EPIA

1 x Front audio pin header (Line-out/MIC-in)

1 x PS/2 keyboard/mouse pin header

3 x RS232 pin header (2 from VX11H, configurable 5V/12V)

1 x LPC pin header

1 x SMBus pin header

1 x S/PDIF Out connector

1 x Digital I/O pin headers (GPI x 4, GPO x 4)

1 x Front panel pin header

2 x Smart Fan pin headers for CPU and System

1 x ATX power connector

1 x PCIex4 slot

1 x SD card (SDHC/SDXC)

1 x SPI

1 x Clear CMOS

EPIA----M920

EPIAEPIA

Back Panel I/O

Back Panel I/O

Back Panel I/OBack Panel I/O

1 x Serial port (powered with selectable 5V/12V) + VGA port

2 x HDMI® ports

1 x GigaLAN port + 2 x USB3.0 ports

1 x GigaLAN port + 2 x USB2.0 ports

3 x Audio jacks: Line-in, Line-out and MIC-in

2 x PS/2 KB/MS ports

I/O Bracket

I/O Bracket

I/O BracketI/O Bracket

Standard

BIOS

BIOS

BIOSBIOS

AMI BIOS ROM APTIO uEFI 4MB

Operating System

Operating System

Operating SystemOperating System

Windows 7

Windows Embedded Standard 7

Windows Embedded POSReady 7

Windows XP

Windows Embedded Standard

Linux

Power

Power

PowerPower

ATX Power connector

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

5

Page 19

EPIA

System Monitoring & Management

System Monitoring & Management

System Monitoring & ManagementSystem Monitoring & Management

Wake-on-LAN

Keyboard Power-on

Timer Power-on

System power management

AC power failure recovery

Watch Dog Timer

EPIA----M920

EPIAEPIA

Operating Conditions

Operating Conditions

Operating ConditionsOperating Conditions

Operating Temperature

Operating Temperature

Operating TemperatureOperating Temperature

0°C up to 60°C

Operating Humidity

Operating Humidity

Operating HumidityOperating Humidity

0% ~ 95% (relative humidity; non-condensing)

Form Factor

Form Factor

Form FactorForm Factor

Mini-ITX (8-layer)

17 cm x 17 cm

Compliance

Compliance

ComplianceCompliance

CE

FCC

BSMI

RoHS

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

6

Page 20

EPIA

EPIA----M920

EPIAEPIA

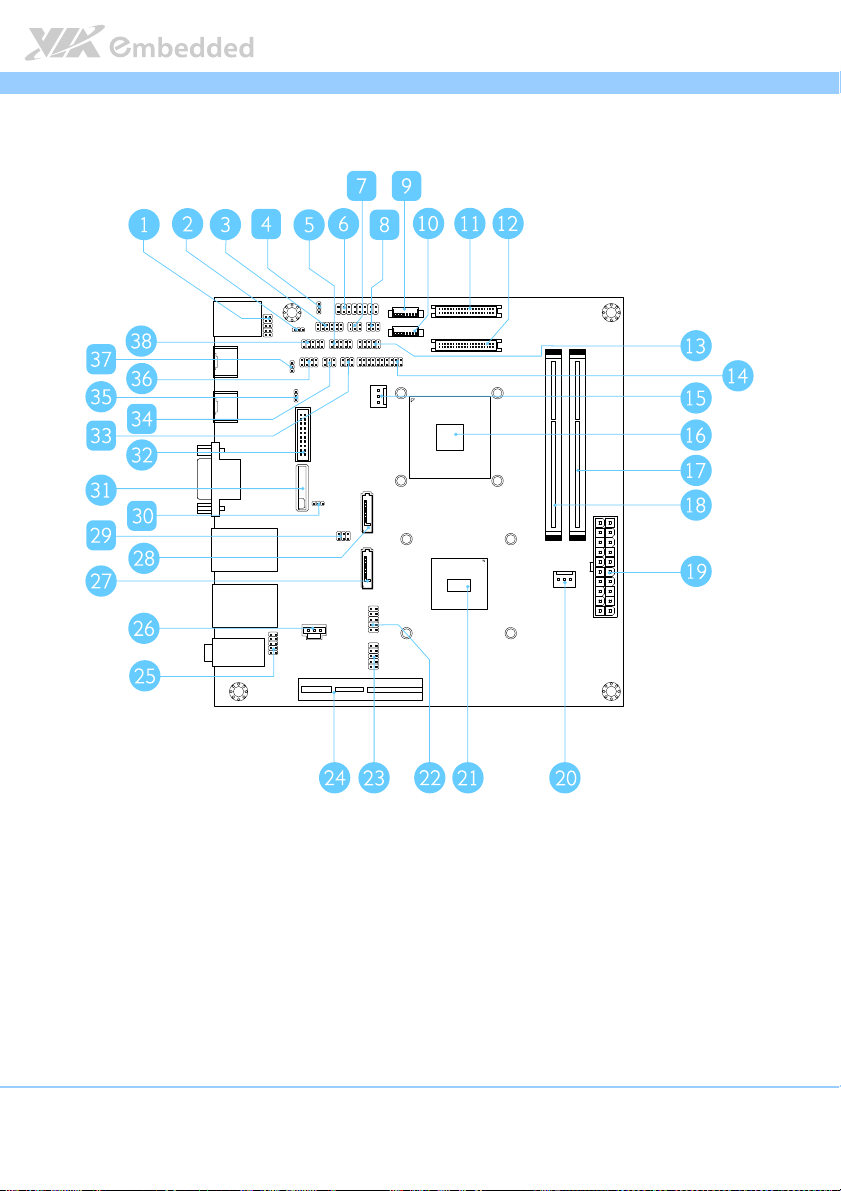

1.3. Layout Diagram

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

Figure

Figure 1111: Layout diagram of the

: Layout diagram of the EPIA

Figure Figure

: Layout diagram of the : Layout diagram of the

EPIA----M920

M920 mainboard

EPIAEPIA

M920M920

mainboard (top view)

mainboard mainboard

(top view)

(top view) (top view)

7

Page 21

EPIA

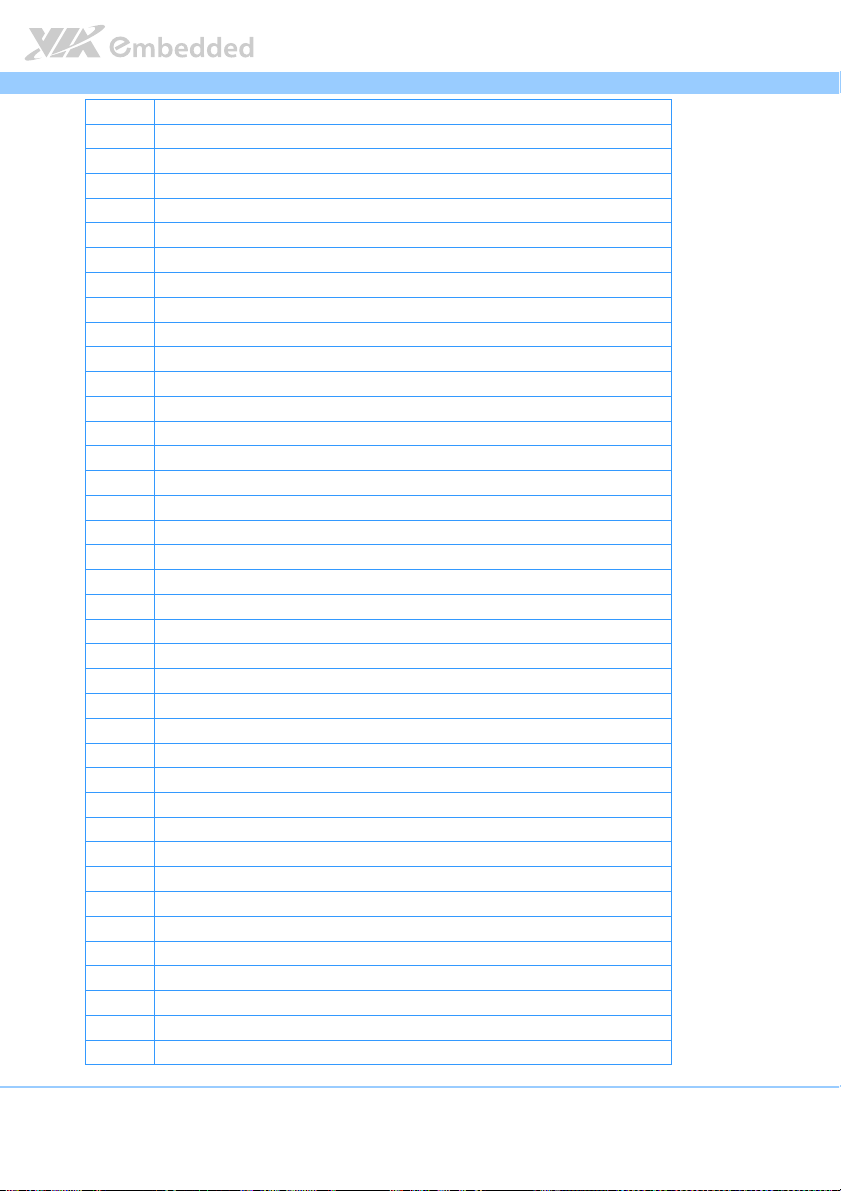

Item

Item Description

ItemItem

1 PS/2 keyboard and mouse pin header (JKBMS)

2 SMBus pin header (SMBUS1)

3 Digital I/O pin headers (DIO1)

4 VDD Power Select jumper (J9)

5 COM4 pin header

6 Front panel pin header (F_PANEL)

7 LVDS1 power select jumper (J14)

8 LVDS2 power select jumper (J15)

9 LVDS inverter connectors (INVERTER2)

10 LVDS inverter connectors (INVERTER1)

11 LVDS connectors (LVDS2)

12 LVDS connectors (LVDS1)

13 COM3 pin header

14 LPC pin header (LPC1)

15 System fan connector (SYSFAN)

16 VIA VX11H chipset

17 Memory slots (SODIMM2)

18 Memory slots (SODIMM1)

19 ATX power supply connector (ATX_POWER2)

20 CPU fan Connector (CPUFAN)

21 VIA Nano X4/ VIA Eden X2 CPU

22 USB pin header (USB_1)

23 USB pin header (USB_2)

24 PCIE x4 slot

25 Front audio pin header (F_AUDIO1)

26 SPDIF connector (SPDIF1)

27 SATA connector (SATA1)

28 SATA connector (SATA2)

29 SATA DOM power select jumper (J12)

30 Clear CMOS jumper (J10)

31 CMOS battery socket (BAT1)

32 USB3.0 Connector (J8)

33 COM3 and COM4 Voltage Select Jumper (J13)

34 COM1 and COM2 Voltage Select Jumper (J11)

35 External Thermal Resister jumper (J7)

36 SPI1 pin header

37 SPI Address Select jumper (J6)

38 COM2 pin header

Description

DescriptionDescription

EPIA----M920

EPIAEPIA

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

1

Page 22

EPIA

EPIA----M920

EPIAEPIA

1.4. Product Dimensions

Figure

Figure 2222: Mounting holes an

: Mounting holes and dimensions of the

Figure Figure

: Mounting holes an: Mounting holes an

d dimensions of the EPIA

d dimensions of the d dimensions of the

EPIA----M920

EPIAEPIA

M920 mainboard

mainboard

M920M920

mainboard mainboard

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

Unit: mm

Figure

Figure 3333:

: External

External I/O

I/O port

port dimensions of the

Figure Figure

: :

External External

dimensions of the EPIA

I/O I/O

portport

dimensions of the dimensions of the

EPIA----M920

M920 mainboard

EPIAEPIA

M920M920

mainboard

mainboard mainboard

2

Page 23

EPIA

EPIA----M920

EPIAEPIA

1.5. Height Distribution

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

Figure

Figure 4444: Height distribution of the

: Height distribution of the EPIA

Figure Figure

: Height distribution of the : Height distribution of the

EPIA----M920

M920 mainboard

EPIAEPIA

M920M920

mainboard (for

mainboard mainboard

(for Qu

(for(for

Quad Core model

ad Core model))))

Qu Qu

ad Core modelad Core model

3

Page 24

EPIA

Figure

Figure 5555: Height distribution of the EPIA

: Height distribution of the EPIA----M920

Figure Figure

: Height distribution of the EPIA: Height distribution of the EPIA

M920 mainboard

mainboard (for

M920M920

mainboard mainboard

(for Dual Core model

Dual Core model))))

(for(for

Dual Core model Dual Core model

EPIA----M920

EPIAEPIA

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

Note:

Note:

Note:Note:

All other heights are under 21.00 mm.

4

Page 25

EPIA

2.

2. I/O Interface

I/O Interface

2.2.

I/O InterfaceI/O Interface

The VIA EPIA-M920 has a wide selection of interfaces integrated into the

board. It includes a selection of frequently used ports as part of the external

I/O coastline.

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.1. External I/O Ports

Figure

Figure 6666: External I/O ports

: External I/O ports

Figure Figure

: External I/O ports: External I/O ports

Item

Item Description

ItemItem

1 PS/2 mouse port

2 HDMI1 port

3 HDMI2 port

4 COM1 port

5 Gigabit Ethernet ports

6 Line-in 3.5 mm TRS jack

7 Line-out 3.5 mm TRS jack

8 PS/2 keyboard port

9 VGA port

10 USB 3.0 ports

11 USB 2.0 ports

12 Microphone 3.5 mm TRS jack

Description

DescriptionDescription

5

Page 26

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

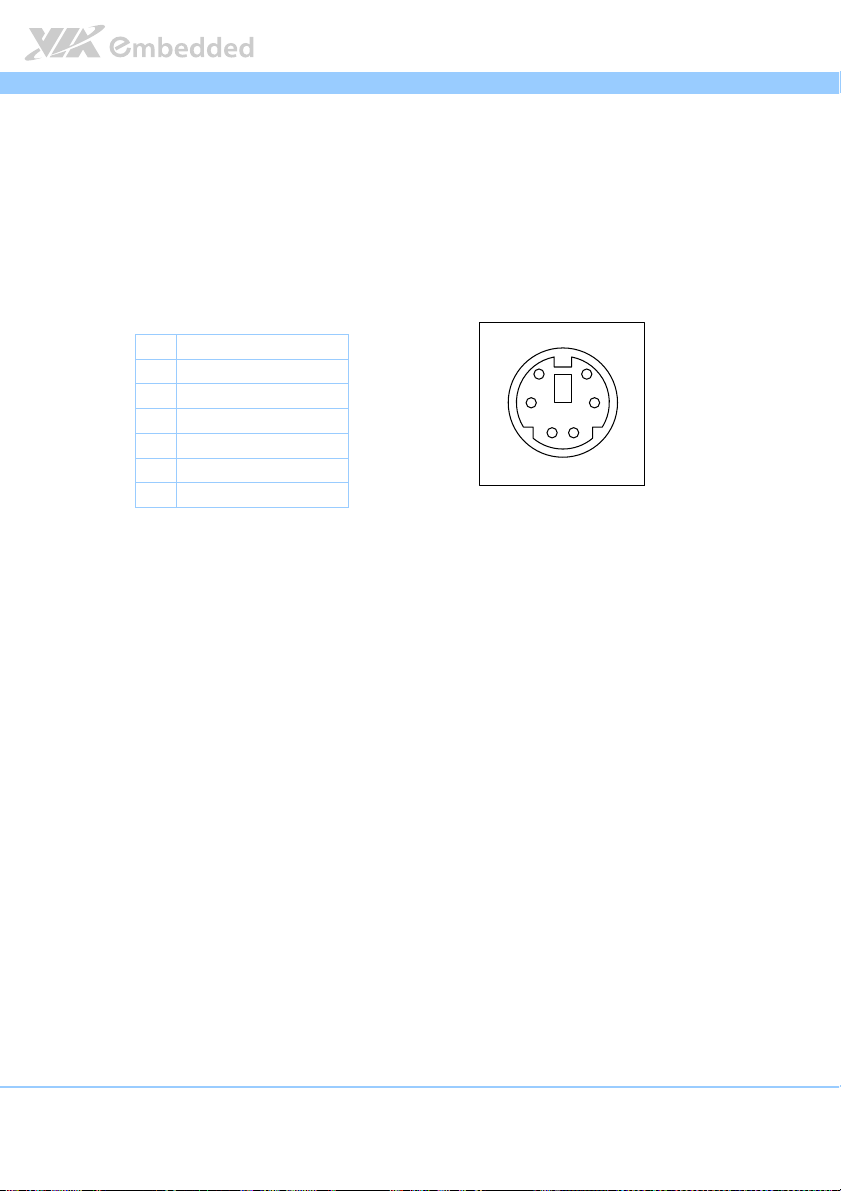

2.1.1. PS/2 Port

The mainboard has two integrated PS/2 ports for keyboard and mouse. Each

port is using the 6-pin Mini-DIN connector. The color purple is used for a PS/2

keyboard while the color green is used for a PS/2 mouse. The pinout of the

PS/2 port are shown below.

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 Data

2 NC

3 Ground

4 +5V

5 Clock

6 NC

Table

Table 1111: PS/2 port pinout

: PS/2 port pinout

TableTable

: PS/2 port pinout: PS/2 port pinout

Figure

Figure 7777:

Figure Figure

: PS/2

PS/2 port pinout diagram

: :

PS/2PS/2

5

6

34

12

port pinout diagram

port pinout diagram port pinout diagram

6

Page 27

EPIA

EPIA----M920

EPIAEPIA

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

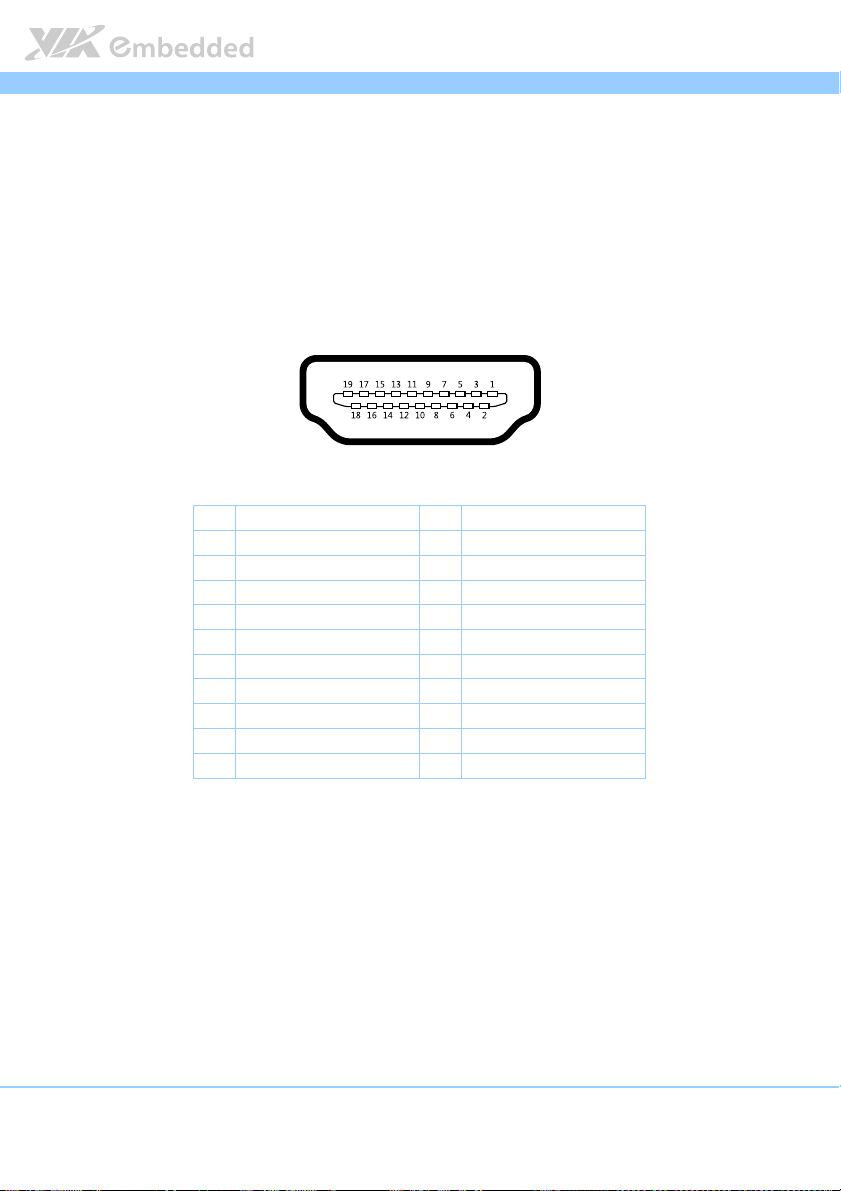

2.1.2. HDMI

®

Port

The integrated 19-pin HDMI® port uses an HDMI® Type A receptacle

®

connector as defined in the HDMI

specification. The HDMI® (High Definition

Multimedia Interface) port is for connecting the high definition video and

digital audio. It allows you to connect the digital video devices which utilize a

high definition video signal. The pinout of the HDMI

®

port is shown below.

Figure

Figure 8888: HDMI

Figure Figure

Ta

Table

ble 2222: HDMI

TaTa

ble ble

®®®®

: HDMI

port pinout diagram

port pinout diagram

: HDMI: HDMI

port pinout diagram port pinout diagram

®®®®

: HDMI

port pinout

port pinout

: HDMI: HDMI

port pinout port pinout

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 TX2+ 2 Ground

3 TX2- 4 TX1+

5 Ground 6 TX1-

7 TX0+ 8 Ground

9 TX0- 10 TXC+

11 Ground 12 TXC-

13 key 14 key

15 DDCSCL 16 DDCSDA

17 Ground 18 +5V

19 Hot Plug Detect

Pin

PinPin

Signal

Signal

SignalSignal

7

Page 28

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

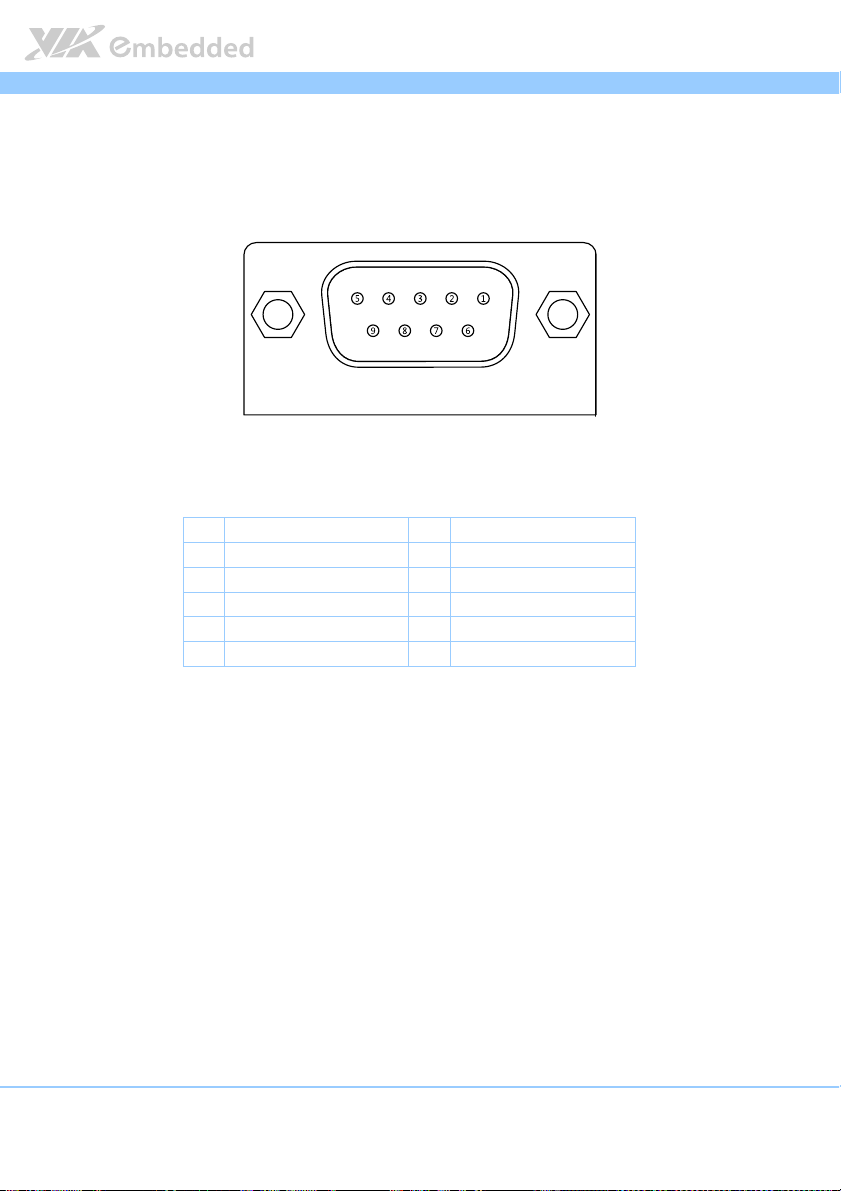

2.1.3. COM Port

The integrated 9-pin COM port uses a male DE-9 connector. The COM

(COM1) port supports the RS-232 standard. The pinout of the COM port is

shown below.

Figure

Figure 9999: CO

: COM port pinout diagram

Figure Figure

Table

Table 3333:

Table Table

M port pinout diagram

: CO: CO

M port pinout diagramM port pinout diagram

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 DCD 6 DSR

2 RxD 7 RTS

3 TxD 8 CTS

4 DTR 9 RI

5 GND

: COM port pinout

COM port pinout

: :

COM port pinoutCOM port pinout

Pin

PinPin

Signal

Signal

SignalSignal

8

Page 29

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

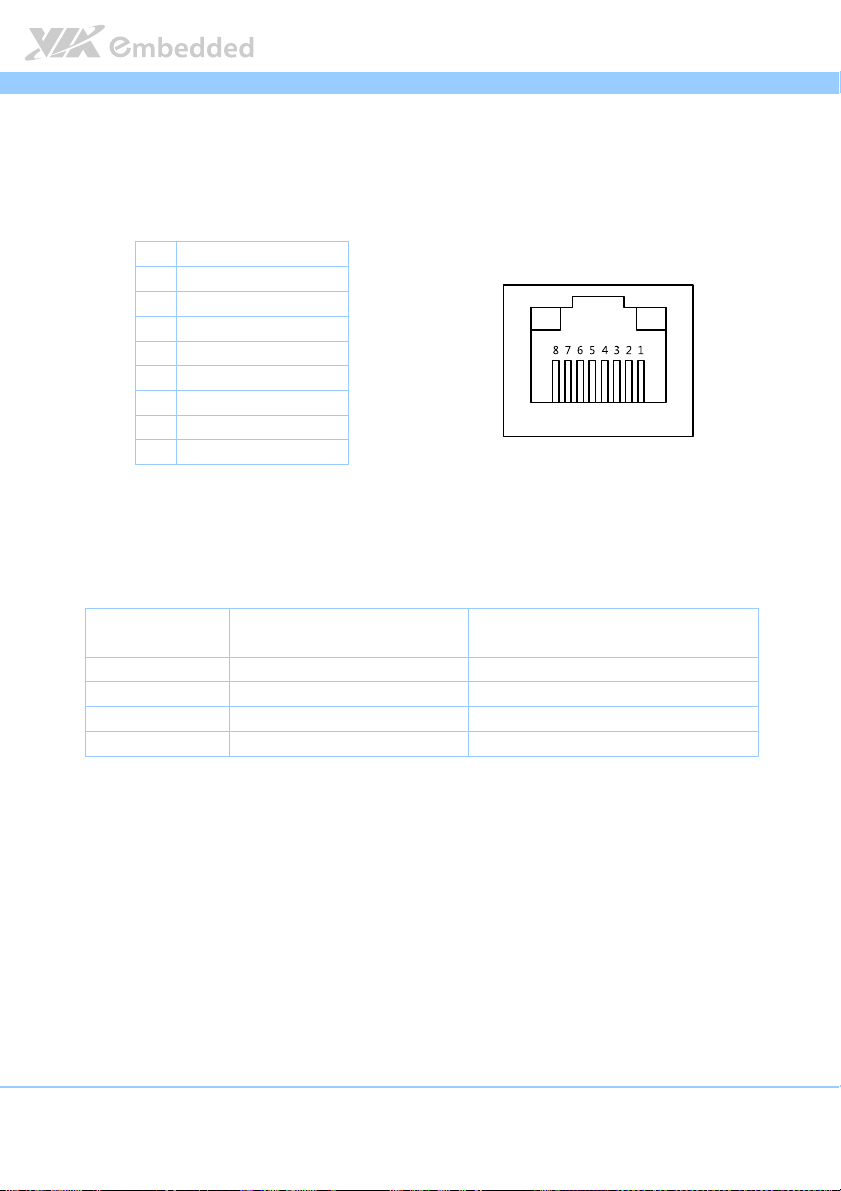

2.1.4. RJ45 LAN port: Gigabit Ethernet

The integrated 8-pin Gigabit Ethernet port is using an 8 Position 8 Contact

(8P8C) receptacle connector (commonly referred to as RJ45). The pinout of

the Gigabit Ethernet port is shown below.

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 Signal pair 1+

2 Signal pair 1-

3 Signal pair 2+

4 Signal pair 3+

5 Signal pair 3-

6 Signal pair 2-

7 Signal pair 4+

8 Signal pair 4-

Table

Table 4444: Gigabit Ethernet port pinout

: Gigabit Ethernet port pinout

Table Table

: Gigabit Ethernet port pinout: Gigabit Ethernet port pinout

Figure

Figure 10

10: Gigabit Ethernet port pinout diagram

Figure Figure

There are two RJ-45 ports and each port has two individual LED indicators

located on the front side to show its Active/Link status and Speed status.

: Gigabit Ethernet port pinout diagram

1010

: Gigabit Ethernet port pinout diagram: Gigabit Ethernet port pinout diagram

Active LED

(Left LED on RJ

(Left LED on RJ----45 connector)

(Left LED on RJ(Left LED on RJ

Link Off Off The LED is always On in Orange color

Speed_10Mbit Flash in Green color The LED is always On in Orange color

Speed_100Mbit Flash in Green color The LED is always On in Green color

Speed_1000Mbit Flash in Green color The LED is always On in Red color

Table

Table 5555: Gigabit Ethernet LED color de

: Gigabit Ethernet LED color definition

Table Table

: Gigabit Ethernet LED color de: Gigabit Ethernet LED color de

Active LED

Active LEDActive LED

45 connector)

45 connector)45 connector)

finition

finitionfinition

Link LED

Link LED

Link LEDLink LED

(Right LED on RJ

(Right LED on RJ----45 connector)

(Right LED on RJ(Right LED on RJ

45 connector)

45 connector)45 connector)

9

Page 30

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

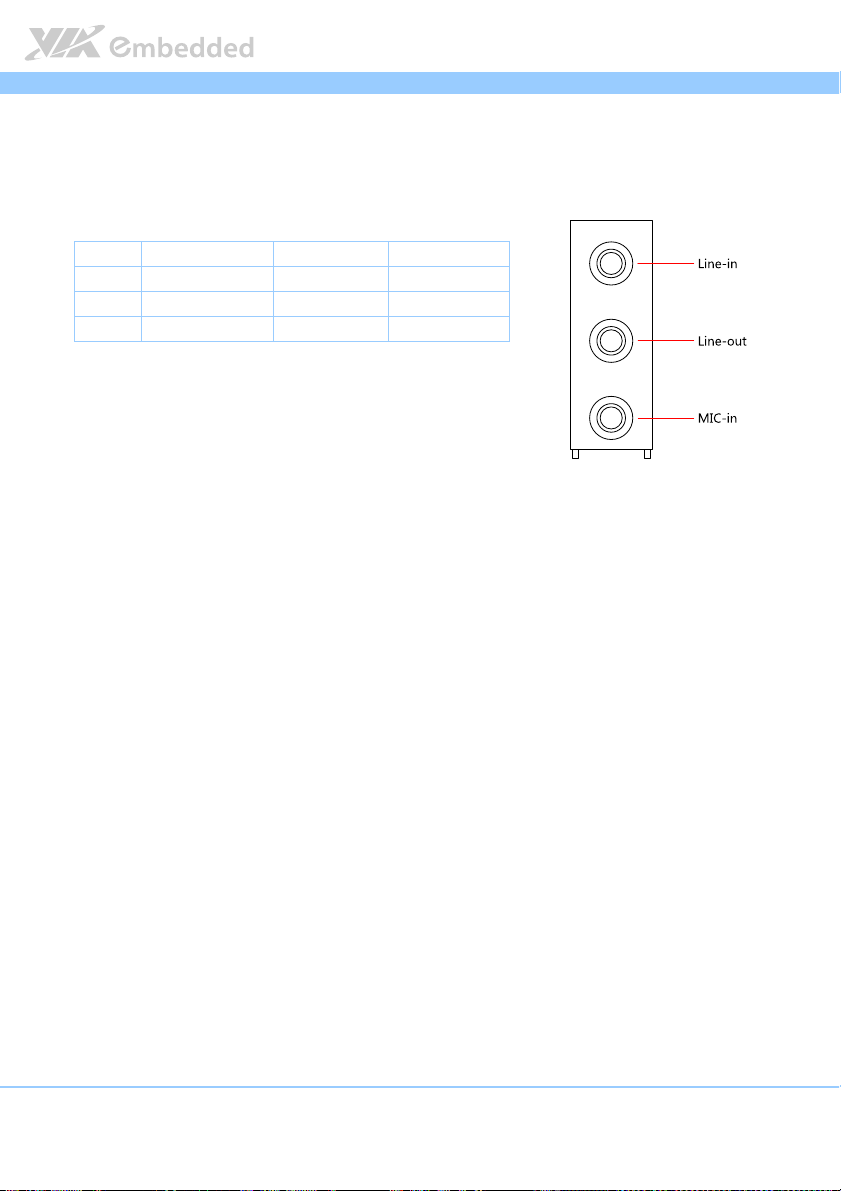

2.1.5. Audio Ports

There are three audio jack receptacles integrated into a single stack on the I/O

coastline. Each receptacle can fit a 3.5 mm Tip Ring Sleeve (TRS) connector to

enable connections to Line-in, Line-out, and MIC-in.

Wiring

Wiring

WiringWiring

Tip Left channel in Left channel Left channel

Ring Right channel in Right channel Right channel

Sleeve Ground Ground Ground

Table

Table 6666: Audio jack receptacle pinout

Table Table

Line

Line----in

in Line

LineLine

inin

: Audio jack receptacle pinout

: Audio jack receptacle pinout: Audio jack receptacle pinout

Line----out

out MIC

LineLine

outout

MIC----in

MICMIC

in

inin

Figure

Figure 11

Figure Figure

11: Audio jack receptacle stack

1111

: Audio jack receptacle stack

: Audio jack receptacle stack: Audio jack receptacle stack

10

Page 31

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.1.6. VGA Port

The integrated 15-pin VGA port uses a female DE-15 connector. The VGA

port is for connecting to analog displays. The pinout of the VGA port is shown

below.

Figure

Figure 12

12: VGA port pinout diagram

Figure Figure

Table

Table 7777: VGA port pinout

Table Table

: VGA port pinout diagram

1212

: VGA port pinout diagram: VGA port pinout diagram

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 RED

2 GREEN

3 BLUE

4 NC

5 Ground

6 Ground

7 Ground

8 Ground

9 +5V

10 NC

11 NC

12 SDA

13 HSync

14 VSync

15 SCL

: VGA port pinout

: VGA port pinout: VGA port pinout

11

Page 32

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.1.7. USB 2.0 Port

There are two integrated USB 2.0 ports in EPIA-M920 mainboard. The USB-

interface port gives complete Plug and Play and hot swap capability for

external devices and it complies with USB UHCI, rev. 2.0. Each USB port is

using the USB Type A receptacle connector. The pinout of the typical USB

port is shown below.

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 +5VSUS

2 Data-

3 Data+

4 Ground

Table

Table 8888: USB port pinout

: USB port pinout

Table Table

: USB port pinout: USB port pinout

Figure

Figure 13

13: USB port pinout diagram

Figure Figure

: USB port pinout diagram

1313

: USB port pinout diagram: USB port pinout diagram

12

Page 33

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.1.8. USB 3.0 Port

The EPIA-M920 mainboard provides two USB 3.0 ports, also known as

SuperSpeed USB. The USB 3.0 port has a maximum data transfer rate up to 5

Gbps and offers a backwards compatible with previous USB 2.0 specifications.

The USB 3.0 port is using the USB Type-A receptacle connector. The pinout of

the typical USB 3.0 port is shown below.

Figure

Figure 14

14: USB

: USB 3333.0 port pinout diagram

Figure Figure

1414

Table

Table 9999: USB 3.0 port pinout

Table Table

.0 port pinout diagram

: USB : USB

.0 port pinout diagram.0 port pinout diagram

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 +5V

2 Data-

3 Data+

4 GND

5 Rx-

6 Rx+

7 GND

8 Tx-

9 Tx+

: USB 3.0 port pinout

: USB 3.0 port pinout: USB 3.0 port pinout

13

Page 34

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2. Onboard Connectors

2.2.1. ATX Power Connector

The mainboard has a 20-pin ATX power connector onboard. The ATX power

connector is labeled as “ATX_POWER1”. The pinout of the ATX power

connector is shown below.

Figure

Figure 15

15: ATX power connector

Figure Figure

Table

Table 10

Table Table

14

: ATX power connector

1515

: ATX power connector: ATX power connector

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 +3.3V 11 +3.3V

2 +3.3V 12 -12V

3 Ground 13 Ground

4 +5V 14 PS_ON

5 Ground 15 Ground

6 +5V 16 Ground

7 Ground 17 Ground

8 PW-OK 18 -5V

9 +5VSUS 19 +5V

10 +12V 20 +5V

10: ATX power connector pinout

: ATX power connector pinout

1010

: ATX power connector pinout: ATX power connector pinout

Pin

PinPin

Signal

Signal

SignalSignal

Page 35

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.2. LVDS panel connectors

The mainboard has two LVDS panel connectors: LVDS1 and LVDS2. LVDS1

connector is controlled by VIA VX11H chipset while the LVDS2 connector is

controlled by VT1636 LVDS transmitter.

Figure

Figure 16

16: LVDS panel connector

Figure Figure

: LVDS panel connector

1616

: LVDS panel connector: LVDS panel connector

15

Page 36

EPIA

Pin

Pin

Signal

Table

Table 11

11: LVDS1

: LVDS1 panel pinout

Table Table

1111

: LVDS1: LVDS1

Signal Pin

PinPin

SignalSignal

M1 GND

2 PVDD1 1 NC

4 PVDD1 3 NC

6 GND 5 GND

8 GND 7 NC

10 -LD1C0 9 NC

12 +LD1C0 11 GND

14 GND 13 NC

16 -LD1C1 15 NC

18 +LD1C1 17 GND

20 GND 19 NC

22 -LD1C2 21 NC

24 + LD1C2 23 GND

26 GND 25 NC

28 -LCLK1 27 NC

30 + LCLK1 29 NC

32 GND 31 GND

34 -LD1C3 33 NC

36 + LD1C3 35 NC

38 LVDSPCLK 37 NC

40 LPDSPD 39 NC

panel pinout

panel pinoutpanel pinout

Pin

PinPin

Signal

Signal

SignalSignal

EPIA----M920

EPIAEPIA

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

16

Page 37

EPIA

EPIA----M920

EPIAEPIA

Pin

Pin

Signal

Table

Table 12

12: LVD

Table Table

1212

: LVDSSSS2

: LVD: LVD

Signal Pin

PinPin

SignalSignal

M1 GND

2 PVDD2 1 -A4_L

4 PVDD2 3 A4_L

6 GND 5 GND

8 GND 7 -A5_L

10 -A0_L 9 A5_L

12 A0_L 11 GND

14 GND 13 -A6_L

16 -A1_L 15 A6_L

18 A1_L 17 GND

20 GND 19 -CLK2_L

22 -A2_L 21 CLK2_L

24 A2_L 23 GND

26 GND 25 -A7_L

28 -CLK1_L 27 A7_L

30 CLK1_L 29 NC

32 GND 31 NC

34 -A3_L 33 NC

36 A3_L 35 NC

38 DVPSPCLK 37 NC

40 DVPSPD 39 NC

2 panel pinout

panel pinout

2 2

panel pinoutpanel pinout

Pin

PinPin

Signal

Signal

SignalSignal

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

17

Page 38

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.3. LVDS Inverter Connector

The mainboard has two inverters for controlling the LVDS panel backlight and

brightness. INVERTER1 corresponds to the LVDS1 panel connector.

INVERTER2 corresponds to the LVDS2 panel connector.

Figure

Figure 17

17: LVDS Inverter connector

Figure Figure

: LVDS Inverter connector

1717

: LVDS Inverter connector: LVDS Inverter connector

18

Page 39

EPIA

Inverter 1

Table

Table 13

13:

: LVDS Inverter connector

Table Table

LVDS Inverter connector pinout

1313

: :

LVDS Inverter connectorLVDS Inverter connector

Inverter 1 Inverter 2

Inverter 1Inverter 1

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 INV1_12 1 IVDD2

2 INV1_12 2 IVDD2

3 BLON1 3 BAKLITE

4 VX11PWM_CTL1 4 VX11PWM_CTL2

5 BLON1 5 BAKLITE

6 BRIGHTNESS1_CTL1 6 BRIGHTNESS2_CTL2

7 GND 7 GND

8 GND 8 GND

pinout

pinout pinout

Inverter 2

Inverter 2Inverter 2

Pin Signal

Signal

PinPin

SignalSignal

EPIA----M920

EPIAEPIA

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

19

Page 40

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.4. Digital I/O pin headers

The mainboard includes one Digital I/O pin header that supports four GPO

and four GPI pins.

Figure

Figure 18

18: Digital I/O pin headers

Figure Figure

Table

Table 14

Table Table

20

: Digital I/O pin headers

1818

: Digital I/O pin headers: Digital I/O pin headers

DIO

DIO 1111

DIO DIO

Pin

Pin

PinPin

1 5V_DIO 2 12V_DIO

3 GPO_37 4 GPI_53

5 GPO_36 6 GPI_52

7 GPO_35 8 GPI_51

9 GPO_34 10 GPI_50

11 GND

14:

: Digital I/O pin headers

Digital I/O pin headers pinout

1414

: :

Digital I/O pin headersDigital I/O pin headers

Signal

Signal Pin

SignalSignal

pinout

pinout pinout

Pin

PinPin

Signal

Signal

SignalSignal

Page 41

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.5. External Thermal Resister

The mainboard supports a pin header (3-pin) that allows the connection of a

temperature sensor cable for detecting the system’s internal air temperature.

The temperature reading can be seen in the BIOS Setup Utility. The pin header

is labeled as “J7”. The pinout of the temperature sensor pin header is shown

below.

Figure

Figure 19

19:

: External Thermal Resister

Figure Figure

Table

Table 15

Table Table

External Thermal Resister

1919

: :

External Thermal ResisterExternal Thermal Resister

J7

J7

J7J7

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 TMPIN2

2 TMPIN2

3 HWMGND

15:

: External thermal resister

External thermal resister pinout

1515

: :

External thermal resister External thermal resister

pinout

pinoutpinout

21

Page 42

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.6. Front Panel Pin Header

The front panel pin header consists of 15 pins in a 16-pin block. Pin 15 is

keyed. The front panel pin header is labeled as “F_PANEL1”. It provides access

to system LEDs, power, reset, system speaker and HDD LED. The pinout of the

front panel pin header is shown below.

Figure

Figure 20

20: Front panel pin header

Figure Figure

: Front panel pin header

2020

: Front panel pin header: Front panel pin header

22

Page 43

EPIA

Pin

Pin

Signal

PinPin

1 +5VDUAL 2 +3.3V

3 +5VDUAL 4 SATA_LED

5 PWR_LED 6 PWR_BTN

7 +5V 8 Ground

9 NC 10 -RST_SW

11 NC 12 Ground

13 SPEAK 14 +5V

15

Table

Table 16

16: Front panel pin header pinout

: Front panel pin header pinout

Table Table

1616

: Front panel pin header pinout: Front panel pin header pinout

Signal Pin

SignalSignal

—

Pin

PinPin

16

Signal

Signal

SignalSignal

-SLEEPLED

EPIA----M920

EPIAEPIA

M920 User Manual

User Manual

M920 M920

User ManualUser Manual

23

Page 44

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.7. SMBus Pin Header

The SMBus pin header consists of three pins that allow connecting the SMBus

devices. Devices communicate with a SMBus host and/or other SMBus devices

using the SMBus interface. It is labeled as “SMBUS”. The pinout of the SMBus

pin header is shown below.

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 SMBCK

2 SMBDT

3 Ground

Table

Table 17

17: SMBus pin header

: SMBus pin header pinout

Table Table

1717

: SMBus pin header: SMBus pin header

pinout

pinout pinout

Figure

Figure 21

Figure Figure

21: SMBus pin header

: SMBus pin header

2121

: SMBus pin header: SMBus pin header

24

Page 45

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.8. CPU and System Fan Connectors

There are two fan connectors on board: one for the CPU and one for the

chassis. The fan connector for the CPU is labeled as “CPUFAN1” and the fan

connector for the system is labeled as “SYSFAN1”. The fans provide variable

fan speeds controlled by the BIOS. The pinout of the fan connectors is shown

below.

CPU fan (CPUFAN1)

CPU fan (CPUFAN1)

CPU fan (CPUFAN1)CPU fan (CPUFAN1)

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 F_I01

2 F_PWM1

3 Ground

System fan (SYSFAN1)

System fan (SYSFAN1)

System fan (SYSFAN1)System fan (SYSFAN1)

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 F_I02

2 F_PWM2

3 Ground

Table

Table 18

18:

: CPU and System

Table Table

CPU and System Fan connector pin

1818

: :

CPU and System CPU and System

Fan connector pinouts

Fan connector pinFan connector pin

outs

outsouts

Figure

Figure 22

Figure Figure

22:

: CPU and System

CPU and System Fan connectors

2222

: :

CPU and System CPU and System

Fan connectors

Fan connectorsFan connectors

25

Page 46

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.9. SATA Connectors

The two SATA connectors on board can support up to 3 Gb/s transfer speeds.

The SATA connectors are labeled as “SATA1” and “SATA2”. The pinout of the

SATA connectors are shown below.

SATA1

SATA1

SATA1SATA1

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 Ground

2 STXP_0

3 STXN_0

4 Ground

5 SRXN_0

6 SRXP_0

7 SATA1_+5V

SATA2

SATA2

SATA2SATA2

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 Ground

2 STXP_1

3 STXN_1

4 Ground

5 SRXN_1

6 SRXP_1

7 SATA2_+5V

Table

Table 19

19: SATA connect

: SATA connector pinouts

Table Table

1919

: SATA connect: SATA connect

or pinouts

or pinoutsor pinouts

Figure

Figure 23

Figure Figure

23: SATA connectors

: SATA connectors

2323

: SATA connectors: SATA connectors

Note:

Note:

Note:Note:

If users want to use the SATA Disk-on-Module flash drive on the board, please use the SATA2 connector.

26

Page 47

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.10. USB 2.0 Pin Headers

The mainboard has two USB 2.0 pin header blocks that support up to four USB

2.0 ports. The pin header blocks are labeled as “USB_1”and “USB_2. The

pinout of the USB pin headers are shown below.

Figure

Figure 24

24: USB pin headers

Figure Figure

: USB pin headers

2424

: USB pin headers: USB pin headers

USB_

USB_1111

USB_USB_

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 +5CDUAL 2 +5CDUAL

3 USBD_T1- 4 USBD_T0-

5 USBD_T1+ 6 USBD_T0+

7 Ground 8 Ground

9

—

Pin

Signal

Signal

PinPin

SignalSignal

10 Ground

USB_

USB_2222

USB_USB_

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 +5CDUAL 2 +5CDUAL

3 USBD_T3- 4 USBD_T2-

5 USBD_T3+ 6 USBD_T2+

7 Ground 8 Ground

9

—

Table

Table 20

20:

: USB pin he

Table Table

USB pin header pinouts

2020

: :

USB pin heUSB pin he

27

Pin

PinPin

10 Ground

ader pinouts

ader pinoutsader pinouts

Signal

Signal

SignalSignal

Page 48

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.11. COM Pin Header for COM2~COM4

There are a total of three COM pin headers on the mainboard. Each COM pin

header supports the RS-232 standard. The pin headers are labeled as “COM2”,

“COM3”, and “COM4”. All of the COM pin headers can support +5V or +12V.

The pinout of the COM pin headers are shown below.

Figure

Figure 25

25: COM pin headers

Figure Figure

Table

Table 21

Table Table

28

: COM pin headers

2525

: COM pin headers: COM pin headers

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 COM_DCD 2 COM_RXD

3 COM_TXD 4 COM_DTR

5 Ground 6 COM_DSR

7 COM_RTS 8 COM_CTS

9 COM_RI 10 —

21: COM pin header pinout

: COM pin header pinout

2121

: COM pin header pinout: COM pin header pinout

Pin

PinPin

Signal

Signal

SignalSignal

Page 49

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.12. PS/2 Keyboard and Mouse Pin Header

The mainboard has a pin header for a PS/2 keyboard and mouse. The pin

header is labeled as “JKBMS”. The pinout of the pin header is shown below.

Figure

Figure 26

26: PS

: PS/2 keyboard and mouse pin header

Figure Figure

Table

Table 22

Table Table

/2 keyboard and mouse pin header

2626

: PS: PS

/2 keyboard and mouse pin header/2 keyboard and mouse pin header

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 VCCE 2 Ground

3 KBCK 4 KBDT

5 EKBCLK 6 EKBDATA

7 MSCK 8 MSDT

9 EMSCLK 10 EMSDATA

22: PS/2 keyboard and mouse pin header pinout

: PS/2 keyboard and mouse pin header pinout

2222

: PS/2 keyboard and mouse pin header pinout: PS/2 keyboard and mouse pin header pinout

Note:

Note:

Note:Note:

When the pin header is not in use, please short pin 3&5, pin 4&6, pin 7&9 and pin 8&10

Pin

PinPin

Signal

Signal

SignalSignal

29

Page 50

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.13. Front Audio Pin Header

In addition to the TRS audio jacks on the external I/O coastline, the mainboard

has a pin header for Line-Out and MIC-In. The pin header is labeled as

“F_AUDIO1”. The pinout of the pin header is shown below.

Figure

Figure 27

27: Front audio pin header

Figure Figure

: Front audio pin header

2727

: Front audio pin header: Front audio pin header

Pin

Pin

Signal

Signal Pin

PinPin

SignalSignal

1 MIC2IN_L 2 AGND

3 MIC2IN_R 4 AGND

5 HPOUTR 6 MIC2_JD

7 F_AUDIO_SENSE 8

9 HPOUTL 10 HPOUT_JD

Table

Table 23

23:

: Front audio pin header pinout

Table Table

Front audio pin header pinout

2323

: :

Front audio pin header pinoutFront audio pin header pinout

30

Pin

PinPin

Signal

Signal

SignalSignal

—

Page 51

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual

User ManualUser Manual

2.2.14. SPI address select

The connector is labeled as “J6”. The pinout of the SPI address select is shown

below.

Figure

Figure 28

28: SPI

: SPI address select

2828

: SPI: SPI

address select

address select address select

Figure Figure

Pin

Pin

Signal

Signal

PinPin

SignalSignal

1 MSPISS0

2 MSPISA

3 MSPISS1

Table

Table 24

24: SP

: SPI address select

Table Table

I address select pinout

2424

: SP: SP

I address selectI address select

pinout

pinout pinout

31

Page 52

EPIA

EPIA----M920

M920 User Manual

EPIAEPIA

M920 M920

User Manual