VIA VT82C686A Datasheet

9,$ 7HFKQRORJLHV

'HOLYHULQJ

9DOXH

97&$

¦6XSHU6RXWK§6RXWK%ULGJH

36,3&

3&,6XSHU,2,QWHJUDWHG3HULSKHUDO&RQWUROOHU

3&&

,

:,7+

,

17(*5$7('6281'%/$67(5

8

/75$

7

17(*5$7('683(5

'0$0

86%&

'

,675,%87('

$&3,(

(03(5$785(

21752//(5

1+$1&('32:(50$1$*(0(17

203/,$17

,2)'&/37&

$67(502'(

.

'0$6

9

2/7$*($1')$1

5HYLVLRQ

)HEUXDU\

3&,

'

,5(&76281'

(<%2$5'&21752//(5

(5,$/

,6$%

72

3&,(,'(&

,543

/8*$1'3/$<

5,'*(

20

$&$

21752//(5

60%

6

3(('021,725,1*

$1'

57&

86$1'

,5

8',2

9,$7(&+12/2*,(6,1&

&RS\ULJKW1RWLFH

&RS\ULJKW 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG 3ULQWHG LQ WKH 8QLWHG 6WDWHV $//5

1R SDUW RI WKLV GRFXPHQW PD\ EH UHSURGXFHG WUDQVPLWWHG WUDQVFULEHG VWRUHG LQ D UHWULHYDO V\VWHP RU WUDQVODWHG LQWR

DQ\ ODQJXDJH LQ DQ\ IRUP RU E\ DQ\ PHDQV HOHFWURQLF PHFKDQLFDO PDJQHWLF RSWLFDO FKHPLFDO PDQXDO RU RWKHUZLVH

ZLWKRXW WKH SULRU ZULWWHQ SHUPLVVLRQ RI 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG

97&$ DQG 6XSHU 6RXWK PD\ RQO\ EH XVHG WR LGHQWLI\ SURGXFWV RI 9,$ 7HFKQRORJLHV ,QF

LD D UHJLVWHUHG WUDGHPDUN RI 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG

70

36

3HQWLXP

:LQGRZV

3&,

$OO WUDGHPDUNV DUH WKH SURSHUWLHV RI WKHLU UHVSHFWLYH RZQHUV

LV D UHJLVWHUHG WUDGHPDUN RI ,QWHUQDWLRQDO %XVLQHVV 0DFKLQHV &RUS

70

3HQWLXP3UR70 3HQWLXP,,70 3HQWLXP,,,70 &HOHURQ70DQG *7/70DUH UHJLVWHUHG WUDGHPDUNV RI ,QWHO &RUS

70

70

LV D UHJLVWHUHG WUDGHPDUN RI WKH 3&, 6SHFLDO ,QWHUHVW *URXS

:LQGRZV 70 :LQGRZV 1770 DQG 3OXJ DQG 3OD\70DUH UHJLVWHUHG WUDGHPDUNV RI 0LFURVRIW &RUS

,*+765(6(59('

'LVFODLPHU1RWLFH

1R OLFHQVH LV JUDQWHG LPSOLHG RU RWKHUZLVH XQGHU DQ\ SDWHQW RU SDWHQW ULJKWV RI 9,$ 7HFKQRORJLHV 9,$ 7HFKQRORJLHV

PDNHV QR ZDUUDQWLHV LPSOLHG RU RWKHUZLVH LQ UHJDUG WR WKLV GRFXPHQW DQG WR WKH SURGXFWV GHVFULEHG LQ WKLV GRFXPHQW

7KH LQIRUPDWLRQ SURYLGHG E\ WKLV GRFXPHQW LV EHOLHYHG WR EH DFFXUDWH DQG UHOLDEOH WR WKH SXEOLFDWLRQ GDWH RI WKLV

GRFXPHQW +RZHYHU 9,$ 7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU DQ\ HUURUV LQ WKLV GRFXPHQW )XUWKHUPRUH 9,$

7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU WKH XVH RU PLVXVH RI WKH LQIRUPDWLRQ LQ WKLV GRFXPHQW DQG IRU DQ\ SDWHQW

LQIULQJHPHQWV WKDW PD\ DULVH IURP WKH XVH RI WKLV GRFXPHQW 7KH LQIRUPDWLRQ DQG SURGXFW VSHFLILFDWLRQV ZLWKLQ WKLV

GRFXPHQW DUH VXEMHFW WR FKDQJH DW DQ\ WLPH ZLWKRXW QRWLFH DQG ZLWKRXW REOLJDWLRQ WR QRWLI\ DQ\ SHUVRQ RI VXFK FKDQJH

2IILFHV

86$ 2IILFH 7DLSHL 2IILFH

0LVVLRQ &RXUW

)UHPRQW &$ &KXQJ&KHQJ 5RDG +VLQ7LHQ

86$ 7DLSHL 7DLZDQ 52&

7HO 7HO

)D[ )D[

2QOLQH6HUYLFHV

+RPH 3DJH

)73 6HUYHU

%%6

http://www.via.com.tw

ftp.via.com.tw

WK

)ORRU 1R

¤RU

http://www.viatech.com

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

R

EVISION HISTORY

Document Release Date Revision Initials

Revision 0.1 2/10/98 Initial release based on 82C596 “Mobile South” Data Sheet revision 0.3 DH

Revision 0.2 3/17/98 Updated features, overview, pins, regs; Added pin list, Sup-IO, HWM, audio DH

Revision 0.3 4/20/98 Revised pinouts, fixed TC, changed reg defs, added regs in funcs 1, 3, & 4: DH

Revision 0.4 4/29/98 Corrected TC, features, pin descriptions, f4/game port regs, removed timing DH

Revision 0.5 5/27/98 Updated feature bullets, pinouts, registers in functions 0-4 and I/O DH

Revision 0.6 5/29/98 Updated registers in functions 1, 3, and 4 DH

Revision 0.72 12/1/98 Changed name to 686A, updated feature bullets, pin names, & register defs DH

Revision 0.8 12/7/9 8 Updated register definitions DH

Revision 0.9 12/9/9 8 Updated register definitions DH

Revision 1.0 1/15/99 Corrected feature bullets, pin typos, ROMCS# description, f0Rx8, f4Rx2 DH

Revision 1.1 4/15/99 Fixed block diagram, pinouts, register descriptions and electrical specs DH

Revision 1.23 5/17/99 Fixed GPI1,5,6, GPO1-3,6, PCS0#, DRQ2/DACK2#, MCCS#, PCS0#,

GPO0/SLOWCLK, GPIOA-D, DACK0-7# IRQ option, FDC on LPT

Fixed SuperIO RxF0-1,F6; FDCIObase+1,Fn0Rx43,59,5B-C,68,74-7F,80,88,

88,8A-F,Fn1Rx43,45,54,Fn2&3Rx8,41,42,Fn4Rx54,D2,PMUIORx0,20,

22,24,28/2A,2C,38,40,42,44-5,HWMIORx28-29,35-38,Fn5Rx6,2C,42,48

Revision 1.24 6/18/99 Changed DRVEN to DRVDEN, moved PME# from W11 to T11

MCCS# on U5, SCIOUT# on U8 for “CF” (opposite prior to “CF”)

Fixed F0 Rx42,74,76, F1 Rx43, F5/6 Rx48, PMU I/O Rx44

Revision 1.3 6/25/99

Revision 1.4 6/25/99 Updated U5/U8 pin defs; fixed Rx74[5,7],76[4-3],77[0],PMUIO Rx44[5,3-1] DH

Revision 1.42 7/7/99 Fixed typo in SUSST1# pin description; Fixed Super-I/O RxF8 table

Revision 1.43 10/7/99 Fixed typo in PDIOR#/SDIOR# pin descriptions & Func 4 Rx42[4] DH

Revision 1.45 12/3/99 Added SCIOUT# to GPIO11 (pin U8), fixed typos in CHAS pin description

Revision 1.5 12/21/99 Changed FDC “OD” pin types to “O”; fixed table 2 ECP port address range

Revision 1.51 1/7/00 Changed silicon version CF to CF/CG (CG same programming / pinout as CF)

Revision 1.52 1/17/00 Added internal I/O APIC pin names; fixed LID name polarity in pin diagram

Revision 1.53 2/8/00 Fixed feature bullet typos, APIC/GPI/GPO pin descriptions, F0 Rx76[4],77[4]

Revision 1.54 2/25/00 Fixed pin direction for APICD0-1 pins (changed from O to IO)

Rev 1.3x created to document CD/CE

Modified F0 Rx59, F1 Rx6,9,34,3C,41,54,71-75,79-7D,C0-C7, F2/3 Rx41-

42,80-84, F4 Rx4C[0], PMU I/O Rx4[0],20-21[1],22-23[1],24-25[1],2C2D[3], HWM IO Rx42[2-1],44[2-1], F5/6 Rx4A-4B, IO Base 0 Rx12[6]

Fixed typos in Serial Port 2 register descriptions, changed to new logo format

Fixed register summary tables: SuperIO Cfg E2; FDC 4, 7

Fixed reg descriptions: SuperIO Cfg E2 & EE defaults; FDCbase+4 & +7;

LPTbase+402; COM1/2 index value references; Com1/2 Divisor offset

Fixed IR description (no 3

Fixed Parallel Port I/O Index, FDC I/O index & Base+7 register description

Fixed typo in Func 4 Rx48 description

Changed Pwr Mgmt I/O Rx44[3-2] (different for CD/DE & CF/CG silicon)

Corrected F0 Rx41[6],58,74[7],77[4], F1 Rx54[5], F2/3 Rx43, F4

Rx4D[3],54[3-2],55[2], PMU IO Rx0[8], added APIC regs

Fixed Func 5/6 AC97 reg summary tables; KBC Ctrl bit-3 changed to reserved

Fixed defaults in register tables for Func 1 Rx40, 41, 43, 45, 50

Added notea to F0 Rx41[3] & Rx45; fixed F1 Rx45[1-0] & misc typos

rd

serial port – muxed on COM2)

(info on version CF removed)

only

VT82C686A

DH

DH

DH

DH

DH

DH

DH

DH

DH

DH

Revision 1.54 February 25, 2000 -i- Revision History

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

T

ABLE OF CONTENTS

VT82C686A

REVISION HISTORY........................................................................................................................................................................I

TABLE OF CONTENTS..................................................................................................................................................................II

LIST OF FIGURES..........................................................................................................................................................................IV

LIST OF TABLES...........................................................................................................................................................................IV

OVERVIEW.......................................................................................................................................................................................4

PINOUTS............................................................................................................................................................................................6

IN DIAGRAM

P

.................................................................................................................................................................................6

IN LISTS

P

IN DESCRIPTIONS

P

........................................................................................................................................................................................7

.........................................................................................................................................................................9

REGISTERS.....................................................................................................................................................................................27

EGISTER OVERVIEW

R

EGISTER DESCRIPTIONS

R

.................................................................................................................................................................27

............................................................................................................................................................39

Legacy I/O Ports...................................................................................................................................................................39

Keyboard Controller Registers.............................................................................................................................................................. 40

DMA Controller I/O Registers.............................................................................................................................................................. 42

Interrupt Controller Registers ............................................................................................................................................................... 43

Timer / Counter Registers..................................................................................................................................................................... 43

CMOS / RTC Registers......................................................................................................................................................................... 44

Super-I/O Configuration Index / Data Registers...............................................................................................................45

Super-I/O Configuration Registers.....................................................................................................................................45

Super-I/O I/O Ports..............................................................................................................................................................48

Floppy Disk Controller Registers.......................................................................................................................................................... 48

Parallel Port Registers........................................................................................................ ................................................................... 49

Serial Port 1 Registers........................................................................................................................................................................... 50

Serial Port 2 Registers........................................................................................................................................................................... 51

SoundBlaster Pro Port Registers.........................................................................................................................................52

FM Registers......................................................................................................................................................................................... 52

Mixer Registers .....................................................................................................................................................................................52

Sound Processor Registers ....................................................................................................................................................................52

Game Port Registers............................................................................................................................................................. 53

PCI Configuration Space I/O...............................................................................................................................................54

Function 0 Registers - PCI to ISA Bridge...........................................................................................................................55

PCI Configuration Space Header.......................................................................................................................................................... 55

ISA Bus Control.................................................................................................................................................................................... 55

Plug and Play Control........................................................................................................................................................................... 59

Distributed DMA / Serial IRQ Control.................................................................................................................................................61

Miscellaneous / General Purpose I/O....................................................................................................................................................62

Function 1 Registers - Enhanced IDE Controller..............................................................................................................68

PCI Configuration Space Header.......................................................................................................................................................... 68

IDE-Controller-Specific Confiiguration Registers................................................................................................................................ 70

IDE I/O Registers.................................................................................................................................................................................. 75

Function 2 Registers - USB Controller Ports 0-1...............................................................................................................76

PCI Configuration Space Header.......................................................................................................................................................... 76

USB-Specific Configuration Registers..................................................................................................................................................77

USB I/O Registers................................................................................................................................................................................. 78

Function 3 Registers - USB Controller Ports 2-3...............................................................................................................79

PCI Configuration Space Header.......................................................................................................................................................... 79

USB-Specific Configuration Registers..................................................................................................................................................80

USB I/O Registers................................................................................................................................................................................. 81

Revision 1.54 February 25, 2000 -ii- Table of Contents

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

VT82C686A

Function 4 Regs - Power Management, SMBus and HWM..............................................................................................82

PCI Configuration Space Header.......................................................................................................................................................... 82

Power Management-Specific PCI Configuration Registers .................................................................................................................. 83

Hardware-Monitor-Specific Configuration Registers ........................................................................................................................... 90

System Management Bus-Specific Configuration Registers................................................................................................................. 90

Power Management I/O-Space Registers ..............................................................................................................................................91

System Management Bus I/O-Space Registers.................................................................................................................................... 100

Hardware Monitor I/O Space Registers .............................................................................................................................................. 103

Function 5 & 6 Registers - AC97 Audio & Modem Codecs............................................................................................107

PCI Configuration Space Header – Function 5 Audio........................................................................................................................ 107

PCI Configuration Space Header – Function 6 Modem...................................................................................................................... 108

Function 5 & 6 Codec-Specific Configuration Registers.................................................................................................................... 109

I/O Base 0 Registers –Audio/Modem Scatter/Gather DMA................................................................................................................ 111

I/O Base 1 Registers – Audio FM NMI Status Registers.................................................................................................................... 115

I/O Base 2 Registers – MIDI / Game Port........................................................................................................................................... 115

Memory Mapped I/O APIC Registers (CG Silicon)............................................................................................................................ 116

Indexed I/O APIC 32-Bit Registers (CG Silicon)............................................................................................................................... 116

FUNCTIONAL DESCRIPTIONS................................................................................................................................................118

OWER MANAGEMENT

P

Power Management Subsystem Overview.......................................................................................................................................... 118

Processor Bus States........................................................................................................................................................................... 118

System Suspend States and Power Plane Control............................................................................................................................... 119

General Purpose I/O Ports...................................................................................................................................................................119

Power Management Events................................................................................................................................................................. 120

System and Processor Resume Events................................................................................................................................................ 120

Legacy Power Management Timers.................................................................................................................................................... 121

System Primary and Secondary Events............................................................................................................................................... 121

Peripheral Events................................................................................................................................................................................ 121

..............................................................................................................................................................118

ELECTRICAL SPECIFICATIONS.............................................................................................................................................122

BSOLUTE MAXIMUM RATINGS

A

HARACTERISTICS

DC C

..............................................................................................................................................................122

...............................................................................................................................................122

PACKAGE MECHANICAL SPECIFICATIONS......................................................................................................................123

Revision 1.54 February 25, 2000 -iii- Table of Contents

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

L

IST OF FIGURES

FIGURE 1. PC SYSTEM CONFIGURATION USING THE VT82C686A.................................................................................5

FIGURE 2. VT82C686A BALL DIAGRAM (TOP VIEW)........................................................................................................... 6

FIGURE 3. VT82C686A PIN LIST (NUMERICAL ORDER) .....................................................................................................7

FIGURE 4. VT82C686A PIN LIST (ALPHABETICAL ORDER)...............................................................................................8

FIGURE 5. STRAP OPTION CIRCUIT.......................................................................................................................................60

FIGURE 6. POWER MANAGEMENT SUBSYSTEM BLOCK DIAGRAM.........................................................................118

FIGURE 8. MECHANICAL SPECIFICATIONS – 352 PIN BALL GRID ARRAY PACKAGE.........................................123

L

IST OF TABLES

TABLE 1. PIN DESCRIPTIONS.....................................................................................................................................................9

TABLE 2. SYSTEM I/O MAP.......................................................................................................................................................27

TABLE 3. REGISTERS..................................................................................................................................................................28

TABLE 4. KEYBOARD CONTROLLER COMMAND CODES ..............................................................................................41

TABLE 5. CMOS REGISTER SUMMARY.................................................................................................................................44

VT82C686A

Revision 1.54 February 25, 2000 -iv- Table of Contents

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

VT82C686A

VT82C686A PSIPC

PCI SUPER-I/O INTEGRATED PERIPHERAL CONTROLLER

PC99 COMPLIANT PCI-TO-ISA BRIDGE

WITH

NTEGRATED HARDWARE SOUNDBLASTER/DIRECT SOUND AC97 AUDIO,

I

U

INTEGRATED SUPER-I/O (FDC, LPT, COM1/2, AND IR),

LTRADMA-33/66 MASTER MODE PCI-EIDE CONTROLLER,

USB C

D

ACPI, E

ONTROLLER, KEYBOARD CONTROLLER, RTC,

ISTRIBUTED DMA, SERIAL IRQ, PLUG AND PLAY,

NHANCED POWER MANAGEMENT, SMBUS, AND

TEMPERATURE, VOLTAGE, AND FAN-SPEED MONITORING

• Inter-operable with VIA and other Host-to-PCI Bridges

−

Combine with VT82C598 for a complete Super-7 (66/75/83/100MHz) PCI / AGP / ISA system (Apollo MVP3)

−

Combine with VT8501 for a complete Super-7 system with integrated 2D / 3D graphics (Apollo MVP4)

−

Combine with VT82C693 for a complete 66 / 100 / 133 MHz Socket-370 or Slot-1 system (Apollo Pro133)

−

Combine with VT8601 for a complete 66 / 100 / 133 MHz Socket-370 or Slot-1 system with integrated 2D / 3D

graphics (Apollo ProMedia)

−

Inter-operable with Intel or other Host-to-PCI bridges for a complete PC99 compliant PCI / AGP / ISA system

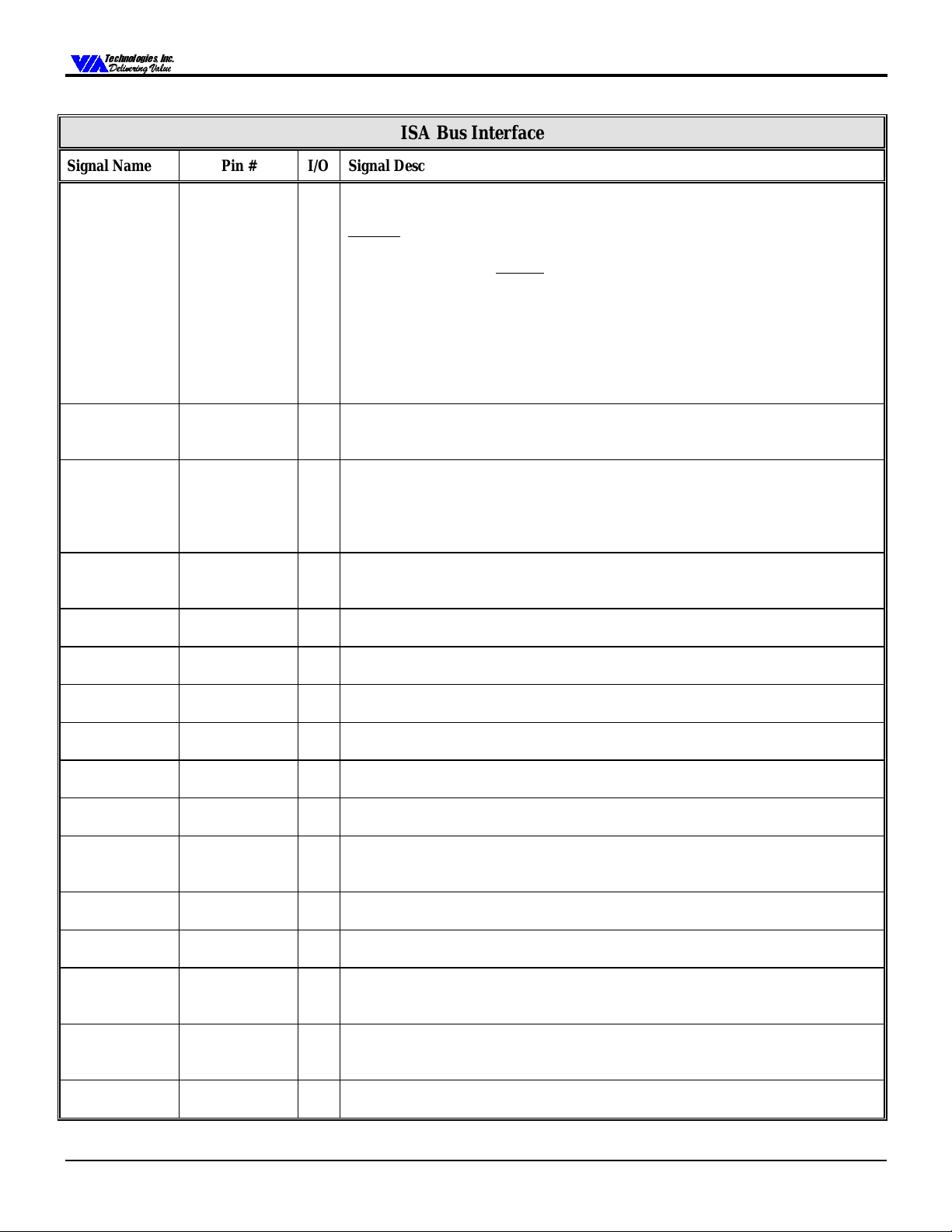

• PCI to ISA Bridge

−

Integrated ISA Bus Controller with integrated DMA, timer, and interrupt controller

−

Integrated Keyboard Controller with PS2 mouse support

−

Integrated DS12885-style Real Time Clock with extended 256 byte CMOS RAM and Day/Month Alarm for ACPI

−

Integrated USB Controller with root hub and four function ports

−

Integrated UltraDMA-33/66 master mode EIDE controller with enhanced PCI bus commands

−

PCI-2.2 compliant with delay transaction and remote power management

−

Eight double-word line buffer between PCI and ISA bus

−

One level of PCI to ISA post-write buffer

−

Supports type F DMA transfers

−

Distributed DMA support for ISA legacy DMA across the PCI bus

−

Serial interrupt for docking and non-docking applica tions

−

Fast reset and Gate A20 operation

−

Edge trigger or level sensitive interrupt

−

Flash EPROM, 4Mb EPROM and combined BIOS support

−

Supports positive and subtractive decoding

Revision 1.54 February 25, 2000 -1- Features

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

• UltraDMA-33 / 66 Master Mode PCI EIDE Controller

−

Dual channel master mode PCI supporting four Enhanced IDE devices

−

Transfer rate up to 33MB/sec to cover PIO mode 4, multi-word DMA mode 2 drives, and UltraDMA-33 interface

−

Increased reliability using UltraDMA-66 transfer protocols

−

Thirty-two levels (doublewords) of prefetch and write buffers

−

Dual DMA engine for concurrent dual channel operatio n

−

Bus master programming interface for SFF-8038i rev.1.0 and Windows-95 compliant

−

Full scatter gather capability

−

Support ATAPI compliant devices including DVD devices

−

Support PCI native and ATA compatibility modes

−

Complete software driver support

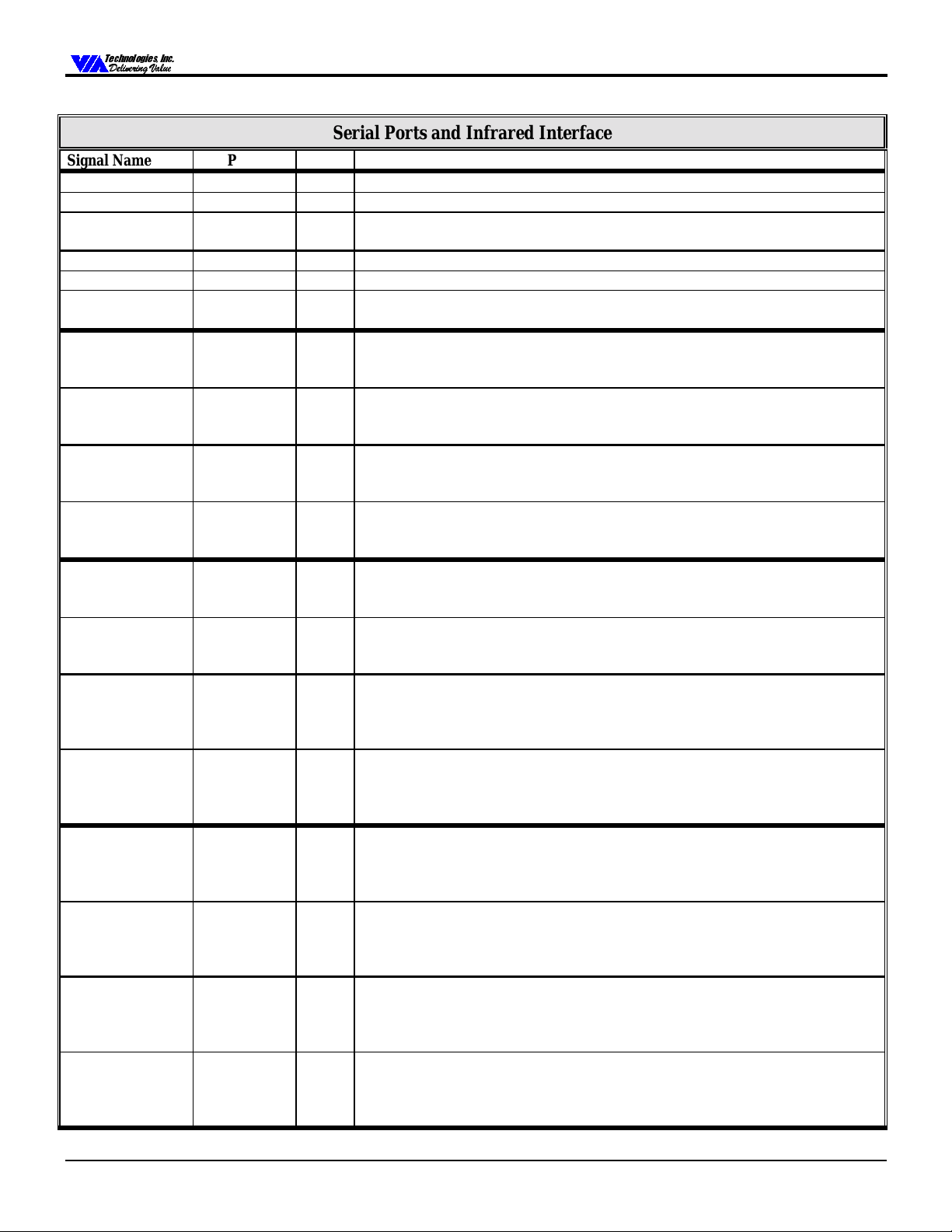

• Integrated Super IO Controller

−

Supports 2 serial ports, IR port, parallel port, and floppy disk controller functions

−

Two UARTs for Complete Serial Ports

Programmable character lengths (5,6,7,8)

Even, odd, stick or no parity bit generation and detection

Programmable baud rate generator

High speed baud rate (230Kbps, 460Kbps) support

Independent transmit/receiver FIFOs

Modem Control

Plug and play with 96 base IO address and 12 IRQ options

−

Infrared-IrDA (HPSIR) and ASK (Amplitude Shift Keyed) IR port multiplexed on COM2

−

Multi-mode parallel port

Standard mode, ECP and EPP support

Plug and play with 192 base IO address, 12 IRQ and 4 DMA options

−

Floppy Disk Controller

16 bytes of FIFO

Data rates up to 1Mbps

Perpendicular recording driver support

Two FDDs with drive swap support

Plug and play with 48 base IO address, 12 IRQ and 4 DMA options

VT82C686A

• SoundBlaster Pro Hardware and Direct Sound Ready AC97 Digital Audio Controller

−

Dual full-duplex Direct Sound channels between system memory and AC97 link

−

PCI master interface with scatter / gather and bursting capability

−

32 byte FIFO of each direct sound channel

−

Host based sample rate co nverter and mixer

−

Standard v1.0 or v2.0 AC97 Codec interface for single or cascaded AC97 Codec’s from multiple vendors

−

Loopback capability for re-directing mixed audio streams into USB and 1394 speakers

−

Hardware SoundBlaster Pro for Windows DOS box and real-mode DOS legacy compatibility

−

Plug and play with 4 IRQ, 4 DMA, and 4 I/O space options for SoundBlaster Pro and MIDI hardware

−

Hardware assisted FM synthesis for legacy compatibility

−

Direct two game ports and one MIDI port interface

−

Complete software driver support for Windows-95/98/2000 and Windows-NT

• Voltage, Temperature, Fan Speed Monitor and Controller

−

Five positive voltage (one internal), three temperature (one internal) and two fan-speed monitoring

−

Programmable control, status, monitor and alarm for flexible desktop management

−

External thermister or internal bandgap temperature sensing

−

Automatic clock throttling with integrated temperature sensing

−

Internal core VCC voltage sensing

−

Flexible external voltage sensing arrangement (any positive supply and battery)

Revision 1.54 February 25, 2000 -2- Features

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

• Universal Serial Bus Controller

−

USB v.1.1 and Intel Universal HCI v.1.1 compatible

−

Eighteen level (doublewords) data FIFO with full scatter and gather capability

−

Root hub and four function ports

−

Integrated physical layer transceivers with optional over-current detection status on USB inputs

−

Legacy keyboard and PS/2 mouse support

• System Management Bus Interface

−

Host interface for processor communications

−

Slave interface for external SMBus masters

• Sophisticated PC99-Compatible Mobile Power Management

−

Supports both ACPI (Advanced Configuration and Power Interface) and legacy (APM) power management

−

ACPI v1.0 Compliant

−

APM v1.2 Compli ant

−

CPU clock throttling and clock stop control for complete ACPI C0 to C3 state support

−

PCI bus cloc k run, Power Management Enable (PME) control, and PCI/CPU clock generator sto p control

−

Supports multiple system suspend types: power-on suspends with flexible CPU/PCI bus reset options,

suspend to DRAM, and suspend to disk (soft-off), all with hardware automatic wake-up

−

Multiple suspend power plane controls and suspend status indicators

−

One idle timer, one peripheral timer and one general purpose timer, plus 24/32-bit ACPI compliant timer

−

Normal, doze, sleep, suspend and conserve modes

−

Global and local device power control

−

System event monitoring with two event classes

−

Primary and secondary interrupt differentiation for individual channels

−

Dedicated input pins for power and sleep buttons, external modem ring indicator, and notebook lid open/close for

system wake-up

−

Up to 12 general purpose input ports and 23 output ports

−

Multiple internal and external SMI sources for flexible power management models

−

One programmable chip select and one microcontroller chip select

−

Enhanced integrated real time clock (RTC) with date alarm, month alarm, and century field

−

Thermal alarm on either external or any combination of three internal temperature sensing circuits

−

Hot docking support

−

I/O pad leakage control

VT82C686A

• Plug and Play Controller

−

PCI interrupts steerable to any interrupt channel

−

Steerable interrupts for integrated peripheral controllers: USB, floppy, serial, parallel, audio, soundblaster, MIDI

−

Steerable DMA channels for integrated floppy, parallel, and soundblaster pro controllers

−

One additional steerable interrupt channel for on-board plug and play devices

−

Microsoft Windows 98TM, Windows NTTM, Windows 95

TM

and plug and play BIOS compliant

• Integrated I/O APIC (Advanced Peripheral Interrupt Controller) (CG Silicon)

• Built-in NAND-tree pin scan test capability

• 0.35um, 3.3V, low power CMOS process

• Single chip 27x27 mm, 352 pin BGA

Revision 1.54 February 25, 2000 -3- Features

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

O

VERVIEW

The VT82C686A PSIPC (PCI Super-I/O Integrated Peripheral Controller) is a high integration, high performance, power-efficient,

and high compatibility device that supports Intel and non-Intel based processor to PCI bus bridge functionality to make a complete

Microsoft PC99-compliant PCI/ISA system. In addition to complete ISA extension bus functionality, the VT82C686A includes

standard intelligent peripheral controllers:

a) Master mode enhanced IDE controller with dual channel DMA engine and interlaced dual channel commands. Dedicated

FIFO coupled with scatter and gather master mode operation allows high performance transfers between PCI and IDE

devices. In addition to standard PIO and DMA mode operation, the VT82C686A also supports the UltraDMA-33 standard to

allow reliable data transfer rates up to 33MB /sec throughput. The VT 82C686A also supports the UltraDMA-66 standard.

The IDE controller is SFF-8038i v1.0 and Microsoft Windows-family compliant.

b) Universal Serial Bus controller that is USB v1.1 and Universal HCI v1.1 compliant. The VT82C686A includes the root hub

with four function ports with integrated physical layer transceivers. The USB controller allows hot plug and play and

isochronous peripherals to be inserted into the system with universal driver support. The controller also implements legacy

keyboard and mouse support so that legacy software can run transparently in a non-USB-aware operating system

environment.

c) Keyboard controller with PS2 mouse support.

d) Real Time Clock with 256 byte extended CMOS. In addition to the standard ISA RTC functionality, the integrated RTC also

includes the date alarm, century field, and other enhancements for compatibility with the ACPI standard.

e) Notebook-class power management functionality compliant with ACPI and legacy APM requirements. Multiple sleep states

(power-on suspend, suspend-to-DRAM, and suspend-to-Disk) are supported with hardware automatic wake-up. Additional

functionality includes event monitoring, CPU clock throttling and stop (Intel processor protocol), PCI b us clock sto p co ntrol,

modular power, clock and leakage control, hardware-based and software-based event handling, general purpose I/O, chip

select and external SMI.

f) Hardware monitoring subs yste m for managing system / motherboard voltage levels, temperatures, and fan speeds

g) Full System Management Bus (SMBus) interface.

h) Two 16550-compatible serial I/O ports with infrared communications port option on the second port.

i) Integrated PCI-mastering dual full-duplex direct-sound AC97-link-compatible sound system. Hardware soundblaster-pro and

hardware-assisted FM blocks are included for Windows DOS box and real-mode DOS compatibility. Loopback capability is

also implemented for directing mixed audio streams into USB and 1394 speakers for high quality digital audio.

j) Two game ports and one MIDI port

k) ECP/EPP-capable parallel port

l) Standard floppy disk drive interface

m) Distributed DMA capability for support of ISA legacy DMA over the PCI bus. Serial IRQ is also supported for docking and

non-docking ap plications.

n) Plug and Play controller that allows complete steerability of all PCI interrupts and internal interrupts / DMA channels to any

interrupt channel. One additional steerable interrupt channel is provided to allow plug and play and reconfigurability of on-

board peripherals for Windows family compliance.

o) Internal I/O APIC (Advanced Programmable Interrupt Controller)

VT82C686A

Revision 1.54 February 25, 2000 -4- Overview

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

VT82C686A

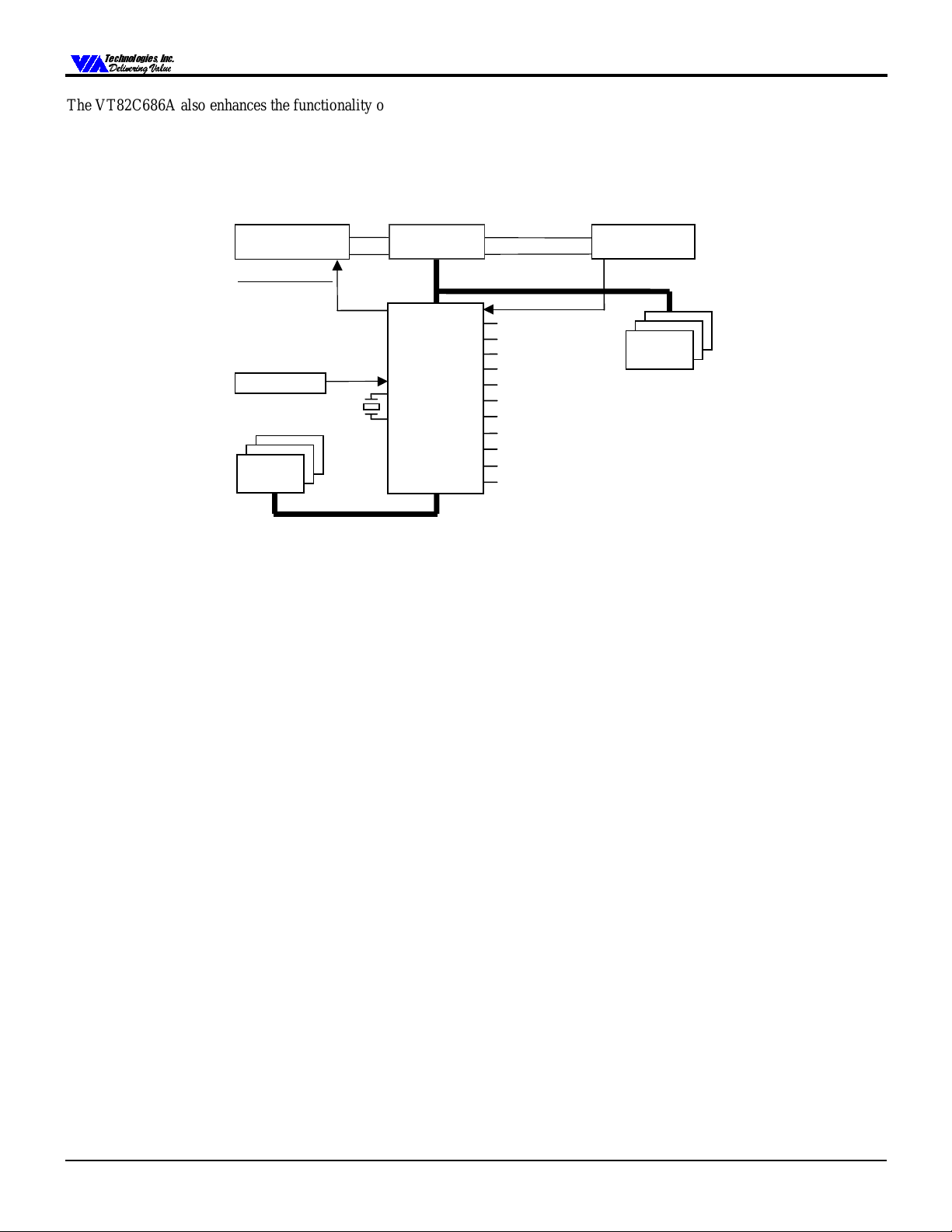

The VT82C686A also enhances the functionality of the standard ISA peripherals. The integrated interrupt controller supports both

edge and level triggered interrupts channel by channel. The integrated DMA controller supports type F DMA in addition to

standard ISA DMA modes. Compliant with the PCI-2.2 specification, the VT82C686A supports delayed transactions and remote

power management so that slower ISA peripherals do not block the traffic of the PCI bus. Special circuitry is built in to allow

concurrent operation without causing dead lock even in a PCI-to-PCI bridge environment. The chip also includes eight levels

(doublewords) of line buffers from the PCI bus to the ISA bus to further enhance overall system performance.

CPU / Cache

Sideband Signals:

Init / CPUreset

IRQ / NMI

SMI / StopClk

FERR / IGNNE

SLP# (Slot-1)

Boot ROM

Expansion

Cards

RTC

Crystal

ISA

CA

CD

North Bridge

VT82C686A

352 BGA

MA/Command

MD

PCI

SMB

USB Ports 0-3

Keyboard / Mouse

MIDI / Game Ports

Parallel Port

Serial Port s 1 and 2

Infrared Comm Port

IDE Primary and Secondary

Floppy Disk Interface

AC97 Lin k

Hardware Monitor Inputs

GPIO, Power Control, Reset

System Memory

DIMM Module ID

Expansion

Figure 1. PC System Configuration Using the VT82C686A

Cards

Revision 1.54 February 25, 2000 -5- Overview

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

P

INOUTS

VT82C686A

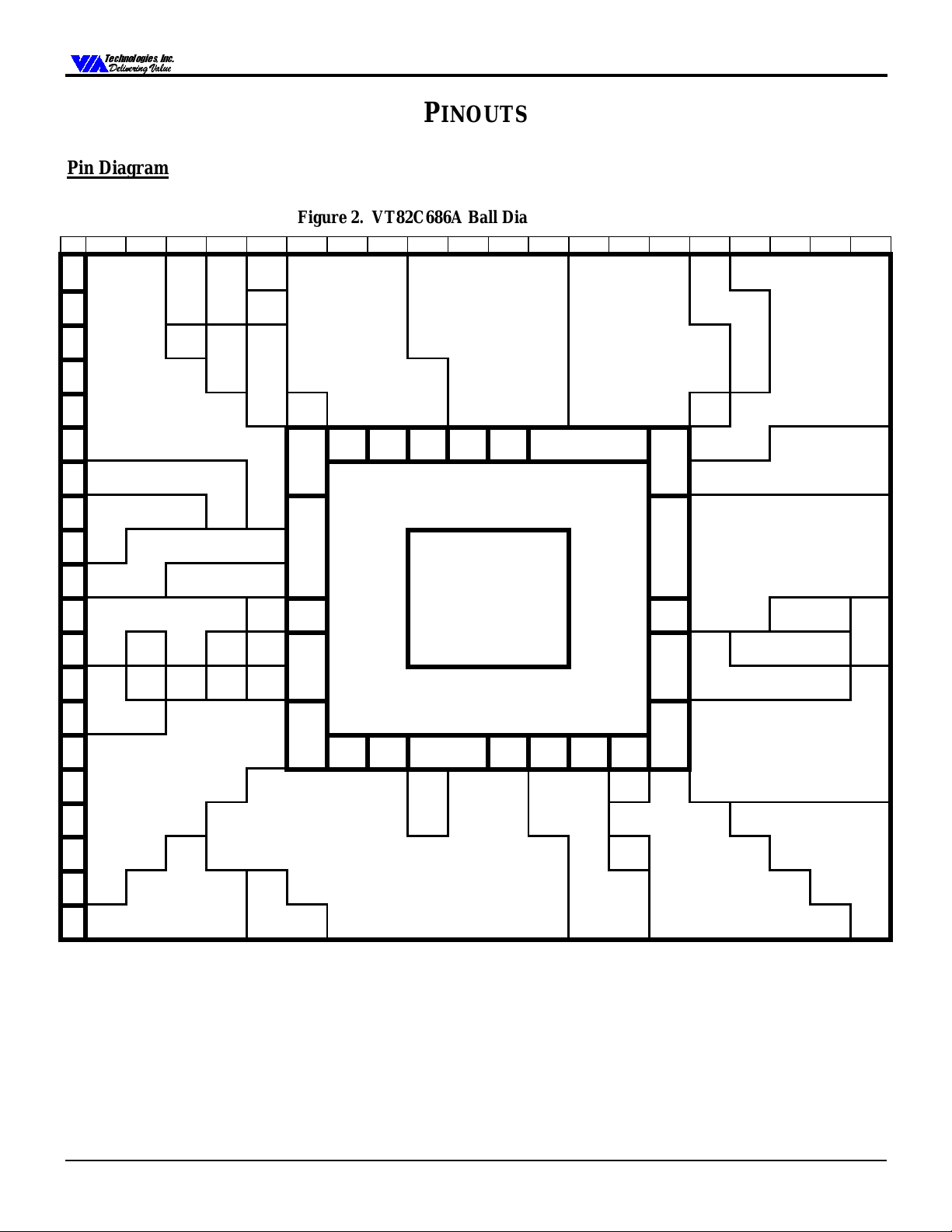

Pin Diagram

Figure 2. VT82C686A Ball Diagram (Top View)

Key1234567891011121314151617181920

R

P3-

W

DS

CTS

DATA#

DS0#DTR2#RXD2RTS1#RXD

MTR1#RI2#DSR2#CTS1#DSR

DIR#

TRK

STEP#

00#

GNDUVCC

GPO0SMB

GPIODSMB

FERR#

CPU

RST#

INTR

CLK#

A20M#IGN

NE#

DCD

DRV

DEN0

MTR0#RTS2#RI1#IR

VCC GND VCC VCC VCC GND

U

VCCSVCC

DATA

CLK

SUSA#SUS

ST1#

SUSB#SMB

ALRT#

SUSC#EXT

SMI#

TXD

DCD

TXD2DTR1#IR

S

SUS

THRM

CLK

PME#

LID

LOW#

RING#

IRQ8#

BTN#

RX

TX

VCCHGND

VCC

FAN

BAT

FAN2V

PCI

STP#VSENS2

PCK

RUN#TSENS1VSENS3

PWR

CPU

STP#TSENS2VSENS4

1#

PD

PD

ERR#

ACK#

1

BUSY

SLCT

VREF

1

SENS1

PD3PD0PCI

PD4P

PD5PD1STR

PE

PD6SLCT

VCC GND

H

GPIOASDD10

SDD7

JBX

GPIOCSDD9

AUTO

INIT#

OBE#

IN#PCLKAD20AD19AD18AD17

JAB2

SDD5

SDD12

ACRS

SDD3

JAX

SYNC

SDD6

SDD11

JBY

SDD8

SDD4

JAY

AD

AD

AD

PIRQ

PIRQD#AD29AD27AD

RST#

PIRQC#AD30C/BE3#ID

FD#

PIRQB#AD23AD22AD

AD16C/BE

DEV

SEL#

AD15AD14AD13AD12AD

AD10AD9AD8C/BE0#AD

AD6AD5AD4AD3AD

AD1AD

PD

CS3#PDA0PDA2PDA1

PD

RDYPDIOR#PDIOW#PDDRQ

PDD0PDD14PDD1PDD13PDD

PDD12PDD3PDD11PDD4PDD

PDD5PDD9PDD6PDD8PDD

JBB2SDCS1#SDCS3#SDA0SDA2

JAB1

SDO

FRM#

2#

STOP# SERR# PAR CBE1#

PREQ#PGNT#

0

SDD1

SDISDA1

SDD13

JBB1

SDD2

SDI2

DACK#

SDD0

BTCKSDIOR#SDIOW#

SDD14

SDD15

MSO

AD

24

SEL

21

I

RDY#TRDY#

11

7

2

PD

CS1#

PD

DACK#

PDD

15

2

10

7

SD

SD

RDY

MSISDDRQ

IOCH

USB

SMEM

A

SMEM

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

AEN

W#

ROM

CS#IOW#

IOR#DACK3#DRQ3USB

DACK1#DRQ

MCS

16#SBHE#

IRQ6

SLPB

TC BALE

RST

DRVLA23LA22LA21LA20

SA19SA18IRQ10IRQ11IRQ

IRQ14DACK0#DRQ0DACK5#SD

DRQ5SD9DACK6#SD10DRQ

SD11DACK7#SD12DRQ7SD

SD14SD15SA17SA16SA15

SA14

SDD14

SA9

SDD9

SA5

SDD5

SA2

SDD2

SA0

SDD0

SD0SD1SD3SD6RTC

RFSH# OSC

1

IRQ5IRQ4IRQ3DACK

SA13

SDD13

SA8

SDD8

SA4

SDD4

SA1

SDD1

SD2SD4SD7RTCX2PWRGDSTP

USB

USB

USB

P0-

USB

USB

CLK

IOCS

16#IOCHK#

DRQ2

SIRQ

SA12

SA11

SDD12

SDD11

SA7

SA6

SDD7

SDD6

SA3

MEM

SDD3

SD5MEM

P1+MSDT

IRQ9B

KB

USB

P2-

P3+

P1-MSCK

KBCKUSB

IRQ

7

2#

CLK

15

8

6

13

SDD15

SA10

SDD10

XDIR INIT SLP#

SOE# SMI# NMI

R#

SPKR

W#

X1

WRT

DATA#WGATE#

DSK

CHG#HDSEL#

DRV

DEN1INDEX#

GND VCC

GND G7 8 9 10 11 12 13 G14 GND

VCC H H VCC

VCC J GND GND GND GND J VCC

VCC K GND GND GND GND K VCC

GND L GND GND GND GND L GND

VCC M GND GND GND GND M VCC

VCC N N VCC

GND P7 8 9 10 11 12 13 P14 GND

GND VCC VCC

RSM

RST#

VBAT

Note: Some of the pins above have alternate functions and alternate names. The table above contains only one name (usually the most often used function), but

the pin lists and pin descriptions contain all names.

Revision 1.54 February 25, 2000 -6- Pinouts

7HFKQRORJLHV ,QF

N

VCC

)

Q

J06PVCC

J09PGN

J10PGN

J

J

J

9

)

5PVCCR10PVCCS

VCC

06PGN

Q

GN

06PGN

9

9

VCCL09PGN

)

Q

GN

5PVCC

)

06PVCC

Q

)

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

VT82C686A

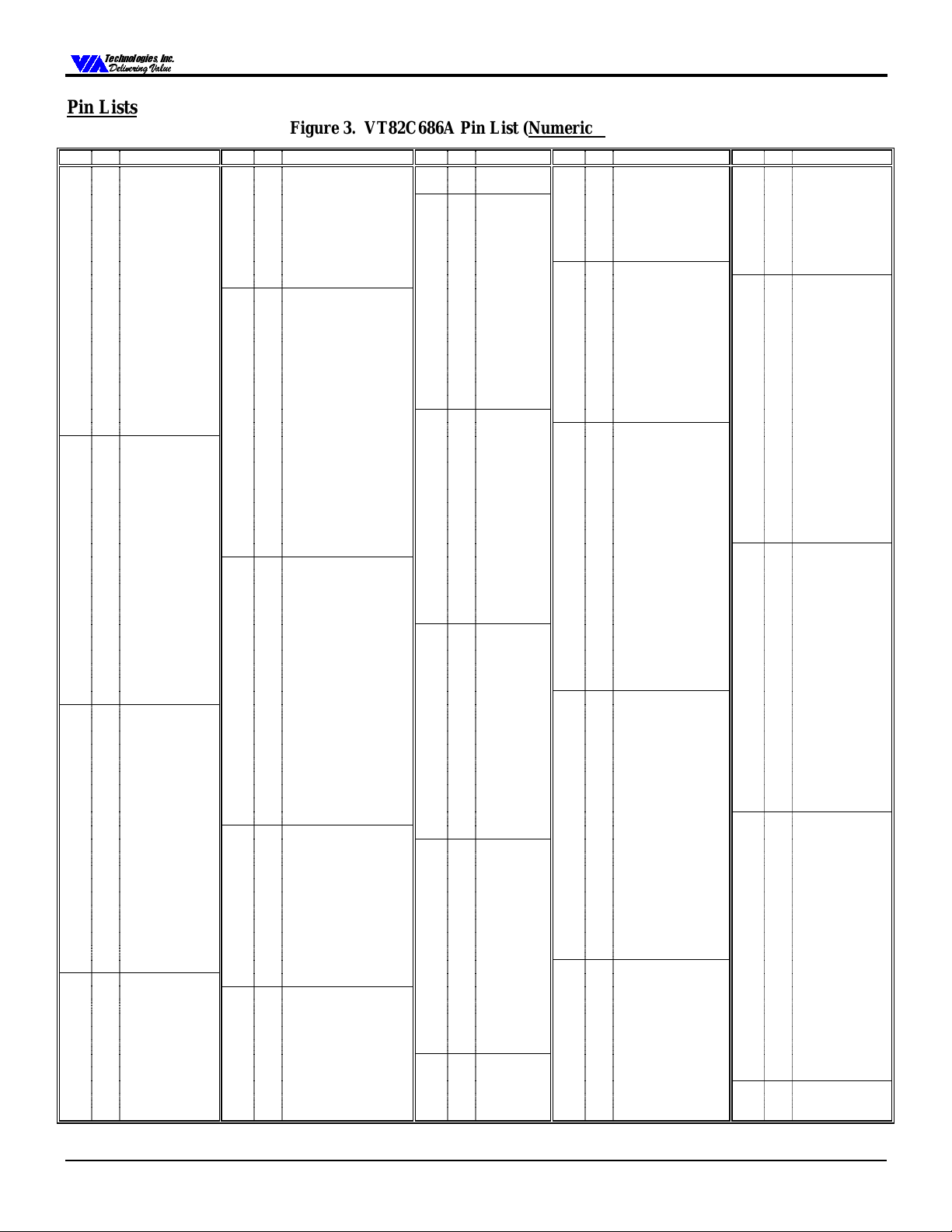

Pin Lists

Figure 3. VT82C686A Pin List (Numerical Order)

PinPin Name PinPin Name PinPin NamePinPin Name PinPin Name

A01 O SMEMR# D12 IO IRRX / GPO15 H19 IO AD12

A02 I IOCHRDY D13 I PE / WDATA# H20 IO AD11

A03 IO USBP0+ D14 IO PD5 J01 O RSTDRV N16 I PDRDY U15 IO SDD05 / RST

A04 IO USBP2+ D15 IO PD1 / TRK00# J02 IO LA23 N17 O PDIOR# U16 IO SDD12 / JBB2

A05 IO KBDT / KBRC D16 IO STROBE# J03 IO LA22 N1 8 O PDIOW# U17 O SDCS1#

A06 I WRTPRT# D17 I PIRQB# J04 IO LA21 N19 I PDDR

A07 O WDATA# D18 IO AD23 J05 IO LA20 N20 IO PDD15 U19 O SDA0

A08 O DS1# D19IO AD22

A09I CTS2# D20 IO AD21

A10 I DCD2# E01 O DACK1# / IDEIRQB

A11 O TXD1 E02 I DRQ1

A12 I DCD1# E03 IO RFSH#

A13 IO PD7 E04 I OSC

A14 IO PD2 / WRTPRT# E05 IO KBCK/A20GATE J16 IO AD10

A15 I ERROR#/HDSL# E06 IO USBP3- J17 IO AD09 P16 IO PDD00 V07 I FERR#

A16 I PIRQA# E07 I TRK00# J18 IO AD08 P17 IO PDD14 V08 OD CPURST

A17 IO AD31 E08 O STEP# J19 IO CBE0# P18 IO PDD01 V09 O SUSA#/O1/APD0

A18 IO AD28 E09 O MTR0# J20 IO AD07 P19 IO PDD13 V10 O SUSST1# / GPO3

A19IO AD26 E10 O RTS2# K01 IO SA1

A20 IO AD25 E11 I RI1# K02 IO SA18 R01 IO SA14 / SDD14 V12 O PCISTP#/GPO5

B01 O SMEMW# E12 O IRTX / GPO14 K03 I IRQ10 R02 IO SA13 / SDD13 V13 I VSENS2 (2.5V

B02 O AEN E13 I SLCT / WGATE# K04 I IRQ11 R03 IO SA12 / SDD12 V14 IO GPIOC(10)/CHAS

B03 IO USBP0- E14 I O PD6 K05 I IRQ15 R04 IO SA11 / SDD11 V15 IO SDD09 / JAX

B04 IO USBP2- E15 IO SLCTIN# / STEP#

B05 IO USBP3+ E16 I PCLK

B06 I RDATA# E17 IO AD20

B07 O WGATE# E18 IO AD19

B08 O DS0# E19 IO AD18

B09ODTR2# E20IOAD17

B10 I RXD2 F01 I MCS16# K16 IO AD06

B11 O RTS1# F02 IO SBHE# K17 IO AD05

B12 I RXD1 F03 I IOCS16# K18 IO AD04

B13 I ACK# / DS1# F04 I IOCHCK# / GPI0 K19 IO AD03

B14 IO PD3 / RDATA# F05 I IRQ7 K20 IO AD02

B15 IO PD0 / INDEX#

B16 O PCIRST#

B17 I PIRQD#

B18 IO AD29

B19 IO AD27

B20 IO AD24

C01 I ROMCS#/KBCS#

C02 IO IOW#

C03 I USBCLK

C04 IO USBP1+

C05 IO MSDT / IRQ12 F16 IO AD16

C06 I DSKCHG# F17 IO CBE2# L16 IO AD01 T07 OD SLP# / GPO7 W18 IO SDD00 / BTCK

C07 O HDSEL# F18 IO FRAME# L17 IO AD00 T08 O GPO0 / SLOWCLK W19 O SDIOR#

C08 O MTR1# F19 IO IRDY# L18 O PREQ# T09 IO SMBDATA W20 O SDIOW#

C09I RI2# F20 IO TRDY# L19I PGNT# T10 O SUSCLK / APICD1 Y01 IO SD00

C10 I DSR2# G01 I IRQ6/I4/SLPBTN# L20 O PDCS1# T11 I THRM / PME# / GI5 Y02 IO SD01

C11 I CTS1# G02 I IRQ5M01IDR

C12 I DSR1# G03 I IRQ4 M02 IO SD09

C13 I BUSY / MTR1# G04 I IRQ3 M03 O DACK6#/UA T14 IO GPIOA/8/GPOWE# Y05 I RTCX1

C14 IO PD4 / DSKCHG# G05 O DACK2#/I13/O25/OC0# M04 IO SD10 T15 IO SDD10 / JAB2

C15 IO PINIT# / DIR#

C16 IO AUTOFD#/DRV0

C17 I PIRQC# G16 IO DEVSEL#

C18 IO AD30 G17 IO STOP#

C19 IO CBE3# G18 I SERR#

C20 I IDSEL G19IO PAR

D01 IO IOR# G20 IO CBE1#

D02 O DACK3#/ACIRQH01 O TC M16 O PDCS3# U03 IO SA03 / SDD3 Y14 I VSENS4 (12V

D03 I DRQ3 H02 O BALE M17 O PDA0 U04 IO MEMR# Y15 IO SDD08 / JAY

D04 IO USBP1- H03 I DRQ2/I12/O24/SQ/OC1 M18 O PDA2 U05 O SOE#/O13/MCCS# Y16 IO SDD04 / SDO

D05 IO MSCK / IRQ1H04IIRQ9 M19 O PDA1 U06 OD SMI# Y17 IO SDD02 / SDI2

D06 O DR VDEN1 H05 O BCLK M20 O PDDACK# U07 OD NMI Y18 IO SDD14 / MSO

D07 I INDEX#

D08 O DIR#

D09O DRVDEN0 H16 IO AD15 N03 IO SD12 U10 I LID / GPI3 / WSC#

D10 O TXD2 H17 IO AD14 N04 I DRQ7U11IBATLOW#/GPI2

D11 O DTR1# H18 IO AD13 N05 IO SD13 U12 IO FAN2/GPIOB(9

F

F07 P VCC

F08 P GNDU

F09 P VCCU

F10 P VCC

F11 P

F12 P

F13 P VCC L10 P GND

F14 P VCC L11 P GND

F15 P GND L12 P GND

G06 P GND

G15 P GND M06 P VCC

H

H15 P VCC

D

DL

11 P GND

12 P GND

15 P VCC P06 P GND

K06 P VCC

K09 P GND R06 P GND

K10 P GND R07 P VCC

K11 P GND R08 P VCC

K12 P GND R09 P VCCS

K1

L01 I IR

L02 O DACK0#/IA R17 IO PDD03 W08 OD INTR

L03 I DRQ0 R18 IO PDD11 W09 O SUSB# / GPO2

L04 O DACK5#/MI R19 IO PDD04 W10 I SMBALRT#/GPI6

L05 IO SD08 R20 IO PDD10 W11 I IRQ8#/GPI1

L15 P GND

M05 I DRQ6 T16 IO PDD05 Y07 OD A20M#

M09 P GND

M10 P GND

M11 P GND

M12 P

M1

N01 IO SD11 U08 IO GPIOD/SO#/MCCS# Y19IO SDD15 / MSI

N02 O DACK7#/UB U09 IO SMBCLK Y20 I SDDR

D

D

14 R16 IO PDD12 W07 OD STPCLK#

D

D

5 T12 I FAN1 Y03 IO SD03

D

06 P

N15 P VCC

P01 IO SD14 U20 O SDA2

P02 IO SD15 V01 IO SA02 / SDD2

P03 IO SA17 V02 IO SA01 / SDD1

P04 IO SA16 V03 IO SD05 / KBIN4

P05 IO SA15 / SDD15 V04 IO MEMW#

P15 P GND

P20 IO PDD02 V11 I R ING# / GPI7

R05 IO SA10 / SDD10 V16 IO SDD03 / SYNC

R11 P

R12 P VCCH

R13 P GNDH

R14 P VCC

R15 P GND

T01 IO SA0

T02 IO SA08 / SDD8 W13 I TSENS1

T03 IO SA07 / SDD7 W14 I VSENS3 (5V

T04 IO SA06 / SDD6 W15 IO SDD06 / JBY

T05 O XDIR/O12/PCS0# W16 IO SDD11 / JAB1

T06 OD INIT W17 IO SDD13 / JBB1

T13 P VREF

T17 IO PDD09 Y08 OD IGNNE#

T18 IO PDD06 Y09 O SUSC#

T19 IO PDD08 Y10 IOD EXTSMI#

T20 IO PDD07 Y11 I PWRBTN#

U01 IO SA05 / SDD5 Y12 O CPUSTP#/GPO4

U02 IO SA04 / SDD4 Y13 I TSENS2

/ SDD

U13 I VSENS1 (2.0V

U14 IO SDD07 / JBX

U18 O SDCS3#

V05 IO SPKR

V06 I RSMRST#

V17 IO SDD01 / SDI

V18 O SDA1

V19 O SDDACK#

V20 I SDRDY

W01 IO SA00 / SDD0

W02 IO SD02

W03 IO SD04 / KBIN3

W04 IO SD07 / KBIN6

W05 O RTCX2

W06 I PWRGD

W12 IO PCKRUN#

Y04 IO SD06 / KBIN5

Y06 P VBAT

Revision 1.54 February 25, 2000 -7- Pinouts

7HFKQRORJLHV ,QF

)

J

J

J

J

J

J

Q

Q

Q

Q

Q

Q

Q

)

)

Q

)

Q

)

Q

Q

Q

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

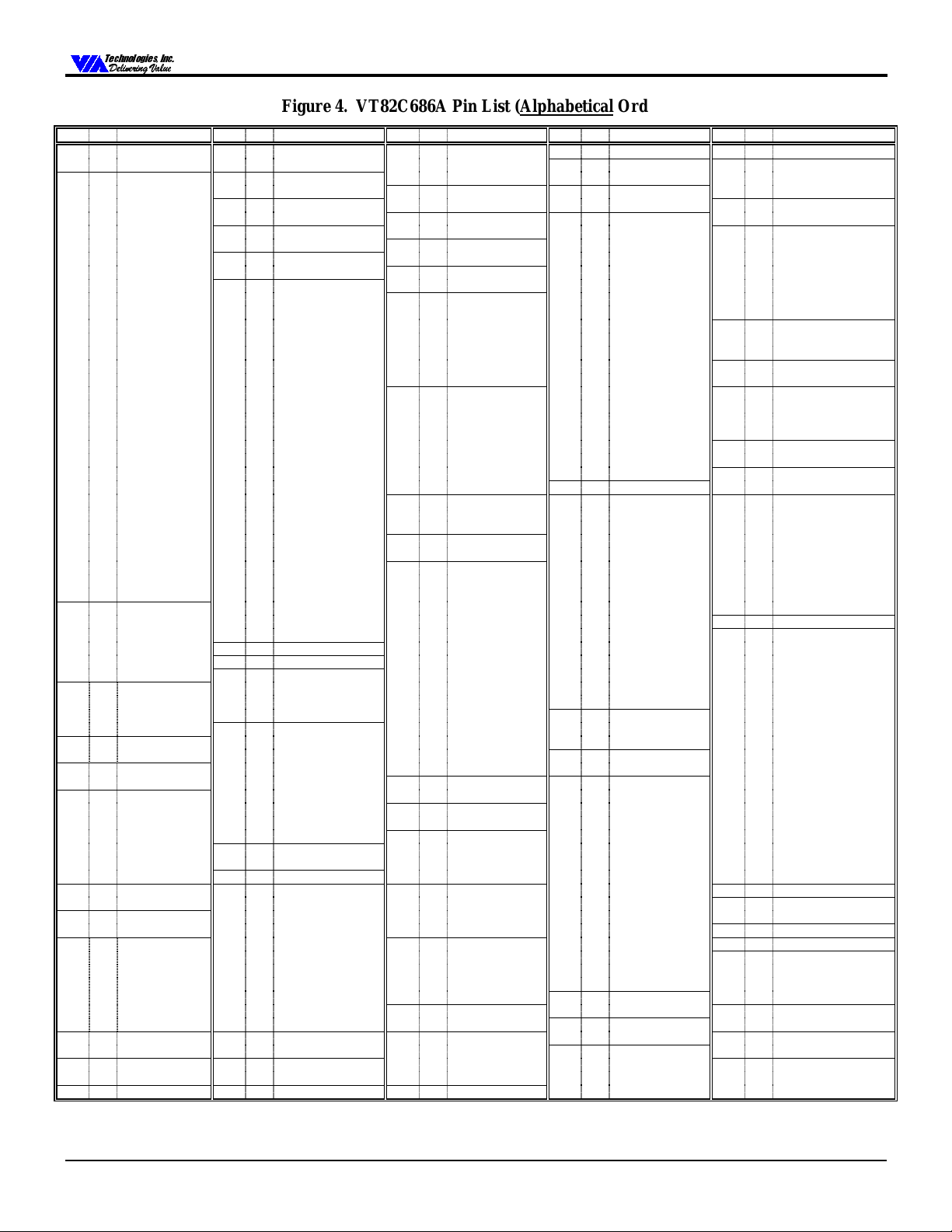

VT82C686A

Figure 4. VT82C686A Pin List (Alphabetical Order)

Pin Pin Name Pin Pin Name Pin Pin Name Pin Pin Name Pin Pin Name

Y07 OD A20M# C12 I DSR1# J04 IO LA21 W05 O RTCX2 T07 OD SLP# / GPO7

B13 I ACK# / DS1# C10 I DSR2# J03 IO LA22 B11 O RTS1# W10 I SMBALRT# / GPI6

L17 IO AD00 D11 O DTR1# J02 IO LA23 E10 O RTS2# U09 IO SMBCLK

L16 IO AD01 B09O DTR2# U10 I LID/GPI3/WSC# B12 I RXD1 T09IO SMBDATA

K20 IO AD02 A15 I ERROR#/HDSEL# F01 I MCS16# B10 I RXD2 A01 O SMEMR#

K19 IO AD03 Y10 IOD EXTSMI# U04 IO MEMR# W01 IO SA00 / SDD0 B01 O SMEMW#

K18 IO AD04 T12 I FAN1 V04 IO MEMW# V02 IO SA01 / SDD1 U06 OD SMI#

K17 IO AD05 U12 IO FAN2/GPIOB(9

K16 IO AD06 V07 I FERR# C05 IO MSDT / IRQ12 U03 IO SA03 / SDD3 V05 IO SPKR

J20 IO AD07 F18 IO FRAME# E09 O MTR0# U02 IO SA04 / SDD4 E08 O STEP#

J18 IO AD08

J17 IO AD09

J16 IO AD10

H20 IO AD11

H19 IO AD12

H18 IO AD13

H17 IO AD14

H16 IO AD15

F16 IO AD16

E20 IO AD17

E19 IO AD18

E18 IO AD19

E17 IO AD20

D20 IO AD21

D19 IO AD22

D18 IO AD23

B20 IO AD24

A20 IO AD25

A19 IO AD26

B19 IO AD27

A18 IO AD28

B18 IO AD29

C18 IO AD30

A17 IO AD31

B02 O AEN

C16 IO AUTOFD#/DR0

H02 O BALE

U11 I BATLOW#/GPI2

H05 O BCLK

C13 I BUSY / MTR1# T14 IO GPIOA(8)/GPOWE# T19 IO PDD08 N05 IO SD13

J19 IO CBE0# V14 IO GPIOC(10)/CHAS T17 IO PDD09 P01 IO SD14

G20 IO CBE1# U08 IO GPIOD/SO#/MCCS R20 IO PDD10 P02 IO SD15

F17 IO CBE2# T08 O GPO0 / SLOWCLK R18 IO PDD11 U19 O SDA0

C19 IO CBE3# C07 O HDSEL# R16 IO PDD12 V18 O SDA1

V08 OD CPURST C20 I IDSEL P19 IO PDD13 U20 O SDA2

Y12 O CPUSTP#/GPO4 Y08 OD IGNNE# P17 IO PDD14 U17 O SDCS1#

C11 I CTS1# D07 I INDEX# N20 IO PDD15 U18 O SDCS3#

A09 I CTS2# T06 OD INIT M20 O PDDACK# W18 IO SDD00 / BTCK

L02 O DACK0#/IDEA W08 OD INTR N19 I PDDR

E01 O DACK1#/IDEB F 04 I IOCHCK# / GPI0 N17 O PDIOR# Y17 IO SDD02 / SDI2

G05 O DAK2#/I13/O25 A02 I IOCHRDY N18 O PDIOW# V16 IO SDD03 / SYNC

D02 O DACK3#/AIRQF03 I IOCS16# N16 I PDRDY Y16 IO SDD04 / SDO

L04 O DACK5#/MIRQD01 IO IOR# D13 I PE / WDATA# U15 IO SDD05 / RST

M03 O DACK6#/USBIA C02 IO IOW# L19 I PGNT# W15 IO SDD06 / JBY

N02 O DACK7#/ USBIB F19 IO IRDY# C15 IO PINIT# / DIR# U14 IO SDD07 / JBX

A12 I DCD1# G04 I IRQ3A16IPIR

A10 I DCD2# G03 I IRQ4D17IPIR

G16 IO DEVSEL# G02 I IRQ5C17IPIR

D08 O DIR# G01 I IRQ6/I4/SLPBTN# B17 I PIRQD# W16 IO SDD1 1 / JAB1

L03 I DRQ0F05IIR

E02 I DRQ1W11IIR

H03 I D2/I12/O24/SQH04 I IRQ9 W06 I PWRGD Y18 IO SDD14 / MSO V13 I VSENS2 (2.2V

D03 I DRQ3K03IIR

M01 I DRQ5K04IIR

M05 I DRQ6L01IIR

N04 I DRQ7K05IIR

D09 O DR VDEN0 D12 IO IRRX / GPO15 V11 I RING# / GPI7 W20 O SDIOW# A06 I WRTPRT#

D06 O DR VDE N1 E12 O IRTX / GPO14 C01 O ROMCS#/KBCS# V20 I SDRDY T05 O XDIR/GPO12/PCS0#

B08 O DS0# E05 IO KBCK / A20GATE V06 I RSMRST# G18 I SERR#

A08 O DS1# A05 IO KBDT / KBRC J01 O RSTDRV E13 I SLCT / WGATE#

C06 I DSKCHG# J05 IO LA20 Y05 I RTCX1 E15 IO SLCTIN#/STEP#

F06 P GND

F11 P GND

F15 P GND

G06 P GND

G15 P GND

09 P GND

10 P GND

11 P GND

12 P GND

K09 P GND

K10 P GND

K11 P GND

K12 P GND

L06 P GND

L09 P GND

L10 P GND

L11 P GND

L12 P GND

L15 P GND

M09 P GND

M10 P GND

M11 P GND

M12 P GND

P06 P GND

P15 P GND

R06 P GND

R15 P GND

R13 P GNDH

F08 P GNDU

7L18OPRE

8# / GPI1 Y11 I PWRBTN# W17 IO SDD13 / JBB1 U13 I VSENS1 (2.0V

10 B06 I RDATA# Y19 IO SDD15 / MSI W14 I VSENS3 (5V

11 E03 IO RFSH# V19 O SDDACK# Y14 I VSENS4 (12V

14 E11 I RI1# Y20 I SDDR

15 C09 I RI2# W19 O SDIOR# B07 O WGATE#

D05 IO MSCK / IRQ1 V01 IO SA02 / SDD2 U05 O SOE#/GPO13/MCCS#

C08 O MTR1# U01 IO SA05 / SDD5 G17 IO STOP#

U07 OD NMI T04 IO SA06 / SDD6 W07 OD STPCLK#

E04 I OSC T0 3 IO SA07 / SDD7 D16 IO STR OBE#

G19 IO PAR T02 IO SA08 / SDD8 V09 O SUSA# / O1 / APICD0

W12 IO PCKRUN# T01 IO SA09 / SDD9 W09 O SUSB# / GPO2

E16 I PCLK R05 IO SA10 / SDD10 Y09 O SUSC#

B16 O PCIRST# R04 IO SA11 / SDD11 T10 O SUSCLK / APICD1

V12 O PCISTP#/GPO5 R03 IO SA12 / SDD12 V10 O SUSST1# / GPO3

B15 IO PD0 / INDEX# R02 IO SA13 / SDD13 H01 O TC

D15 IO PD1 / TRK00# R01 IO SA14 / SDD14 T11 I THRM / PME# / GI5

A14 IO PD2 / WRTPRT# P05 IO SA15 / SDD15 F20 IO TRDY#

B14 IO PD3 / RDATA# P04 IO SA16 E07 I TRK00#

C14 IO PD4 / DSKCHG# P03 IO SA17 W13 I TSENS1

D14 IO PD5 K02 IO SA18 Y13 I TSENS2

E14 IO PD6 K01 IO SA19 A11 O TXD1

A13 IO PD7 F02 IO SBHE# D10 O TXD2

M17 O PDA0 Y01 IO SD00 C03 I USBCLK

M19 O PDA1 Y02 IO SD01 B03 IO USBP0M18 O PDA2 W 02 IO SD02 A03 IO USBP0+

L20 O PDCS1# Y03 IO SD03 D04 IO USBP1M16 O PDCS3# W03 IO SD04 / KBIN3 C04 IO USBP1+

P16 IO PDD00 V03 IO SD05 / KBIN4 B04 IO USBP2-

P18 IO PDD01 Y04 IO SD06 / KBIN5 A04 IO USBP2+

P20 IO PDD02 W04 IO SD07 / KBIN6 E06 IO USBP3-

R17 IO PDD03 L05 IO SD08 B05 IO USBP3+

R19 IO PDD04 M02 IO SD09

T16 IO PDD05 M04 IO SD10

T18 IO PDD06 N01 IO SD11

T20 IO PDD07 N03 IO SD12

V17 IO SDD01 / SDI

A# Y15 IO SDD08 / JAY

B# V15 IO SDD09 / JAX

C# T15 IO SDD10 / JAB2

# U16 IO SDD12 / JBB2

Y06 P VBAT

F07 P VCC

F10 P VCC

F12 P VCC

F13 P VCC

F14 P VCC

H06 P VCC

H15 P VCC

06 P VCC

15 P VCC

K06 P VCC

K15 P VCC

M06 P VCC

M15 P VCC

N06 P VCC

N15 P VCC

R07 P VCC

R08 P VCC

R11 P VCC

R14 P VCC

R12 P VCCH

R09 P VCCS

R10 P VCCS

F09 P VCCU

T13 P VREF

A07 O WDATA#

Revision 1.54 February 25, 2000 -8- Pinouts

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

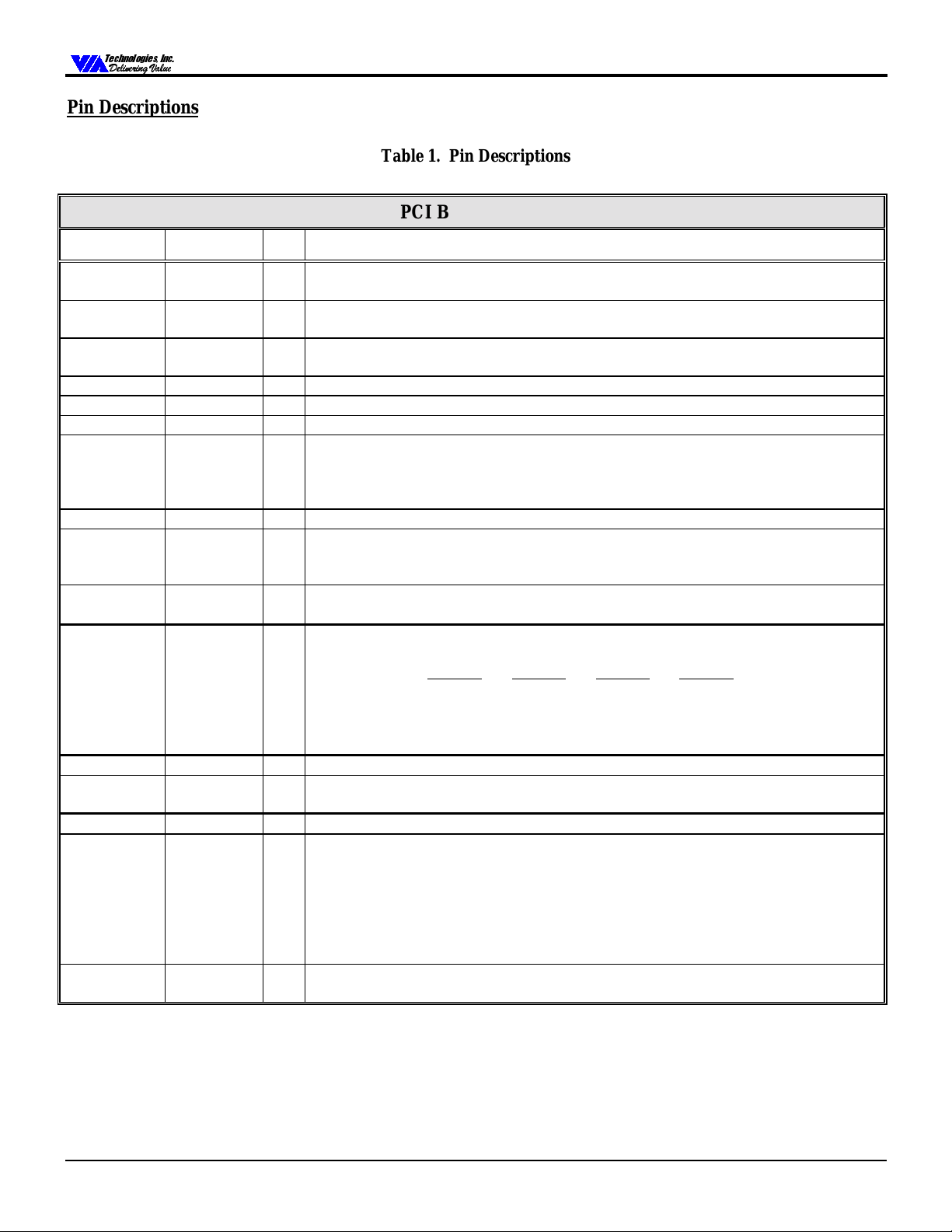

Pin Descriptions

Table 1. Pin Descriptions

PCI Bus Interface

Signal Name Pin # I/O Signal Description

VT82C686A

AD[31:0]

C/BE[3:0]#

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

PAR

SERR#

IDSEL

PIRQA-D#

PREQ#

PGNT#

PCLK

PCKRUN#

PCIRST#

(see pin list) IO

C19, F17,

IO

G20, J19

F18 IO

F19 IO

F20 IO

G17 IO

G16 IO

G19 IO

G18 I

C20 I

A16, D17,

C17, B17

L18 O

L19 I

E16 I

W12 IO

B16 O

Address/Data Bus.

The standard PCI address and data lines. The address is driven with

FRAME# assertion and data is driven or received in following cycles.

Comma n d / B y te En a b l e .

The command is driven with FRAME# assertion. Byte enables

corresponding to supplied or requested data are driven on following clocks.

Frame.

Assertion indicates the address phase of a PCI transfer. Negation indicates that

one more data transfer is desired by the cycle initiator.

Initiator Ready.

Target Ready.

Asserted by the target to request the master to stop the current transaction.

Stop.

Device Select.

Asserted when the initiator is ready for data transfer.

Asserted when the target is ready for data transfer.

The VT82C686A asserts this signal to claim PCI transactions through

positive or subtractive decoding. As an input, DEVSEL# indicates the response to a

VT82C686A-initiated transaction and is also sampled when decoding whether to

subtractively decode the cycle.

A single parity bit is provided over AD[31:0] and C/BE[3:0]#.

Parity.

System Error.

SERR# can be pulsed active by any PCI device that detects a system error

condition. Upon sampling SERR# active, the VT82C686A can be programmed to

generate an NMI to the CPU.

Initialization Device Select.

IDSEL is used as a chip select during configuration read and

write cycles. Connect this pin to AD18 using a 100 Ω resistor.

I

PCI Interrupt Request

. These pins are typically connected to the PCI bus INTA#-

INTD# pins as follows:

PIRQA# PIRQB#

PIRQC# PIRQD#

PCI Slot 1 INTA# INTB# INTC# INTD#

PCI Slot 2 INTB# INTC# INTD# INTA#

PCI Slot 3 INTC# INTD# INTA# INTB#

PCI Slot 4 INTD# INTA# INTB# INTC#

PCI Request.

PCI Grant.

This signal goes to the North Bridge to request the PCI bus.

This signal is driven by the North Bridge to grant PCI access to the

VT82C686A.

PCI Clock.

PCI Bus Clock Run.

PCLK provides timing for all transactions on the PCI Bus.

This signal indicates whether the PCI clock is or will be stopped

(high) or running ( low). The VT82 C686A drives this signal low when the PCI clock is

running (default on r eset) and releases it when it st ops the PCI clo ck. External d evices

may assert this signal low to request that the PCI clock be restarted or prevent it from

stopping. Connect this pin to ground using a 100 Ω resistor if the function is not used.

Refer to the “PCI Mobile Design Guide” and the VIA “Apollo MVP4 Design Guide” for

more details.

PCI Reset.

Active low reset signal for the PCI bus. The VT82C686A will assert this pin

during power-up or from the control register.

Revision 1.54 February 25, 2000 -9- Pinouts

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

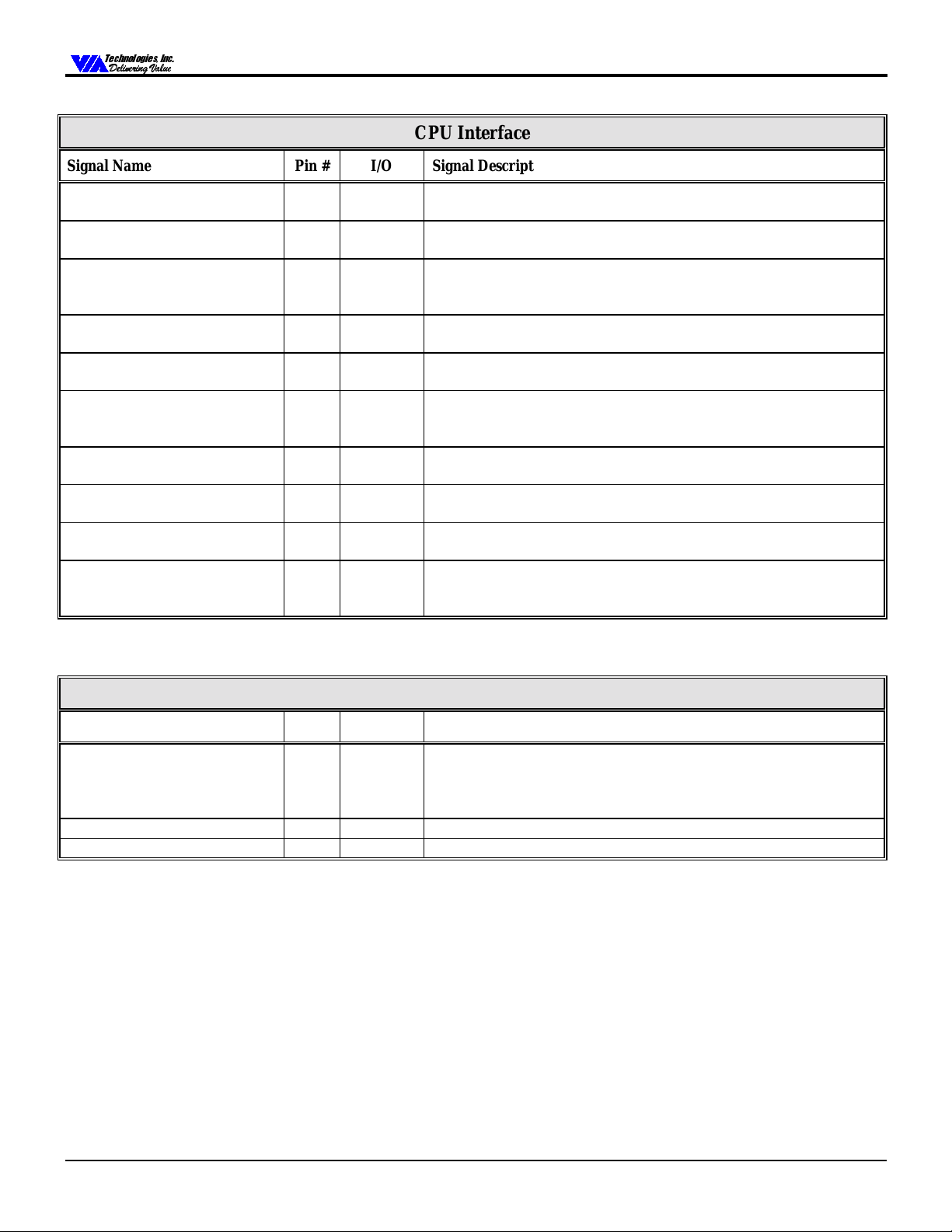

CPU Interface

Signal Name Pin # I/O Signal Description

VT82C686A

CPURST

V8 OD

CPU Reset.

The VT82C686A asserts CPURST to reset the CPU

during power-up.

INTR

W8 OD

CPU Interrupt.

CPU that an interrupt request is pending and needs service.

NMI

U7 OD

Non-Maskable Interrupt.

interrupt to the CPU. The VT82C686A generates an NMI when either

SERR# or IOCHK# is a sse rted.

INIT

T6 OD

Initialization.

The VT82C686A asserts INIT if it detects a shut-down

special cycle on the PCI bus or if a soft reset is initiated by the register

STPCLK#

W7 OD

Stop Clock.

STPCLK# is asserted by the VT82C686A to the CPU to

throttle the processor clock.

SMI#

U6 OD

System Management Interrupt.

VT82C686A to the CPU in response to different Power-Management

events.

FERR#

V7 I

Numerical Coprocessor Error.

error signal on the CPU. Internally generates interrupt 13 if active.

IGNNE#

Y8 OD

Ignore Numeric Error.

pin on the CPU.

SLP#

/ GPO7

T7 OD

(Rx75[7] = 0). Used to put the CPU to sleep. Used with slot-1

Sleep

CPUs only. Not currently used with socket-7 CPUs.

A20M#

Y7 OD

A20 Mask.

Connect to A20 mask input of the CPU to control address

bit-20 generation. Logical combination of the A20GATE input (from

internal or external keyboard controller) and Port 92 bit-1 (Fast_A20).

Note: Connect each of the above signals to 4.7K Ω pullup resistors to VCC3.

INTR is driven by the VT82C686A to signal the

NMI is used to force a non-maskable

SMI# is asserted by the

This signal is tied to the coprocessor

This pin is connected to the “ignore error”

Advanced Programmable Interrupt Controller (APIC)

Signal Name Pin # I/O Signal Description

WSC# (CG)

APICD0 (CG)

APICD1 (CG)

/ GPI3 / LID

/ GPO1 / SUSA#

/ SUSCLK

For programming information, refer to Function 0 Rx74,77, Function 4 Rx54[3-2], and Memory Mapped / Indexed APIC registers.

U10 I / I / I

V9 IO / O / O

T10 IO / O

Write Snoop Complete.

Asserted by the north bridge to indicate that

all snoop activity on the CPU bus initiated by the last PCI-to-DRAM

write is complete and that it is safe to perform an APIC interrupt.

Pin U10 is WSC# if Rx74[7]=1.

APIC Data 0.

APIC Data 1.

Rx74[7]=1.

Rx74[7]=1.

Revision 1.54 February 25, 2000 -10- Pinouts

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

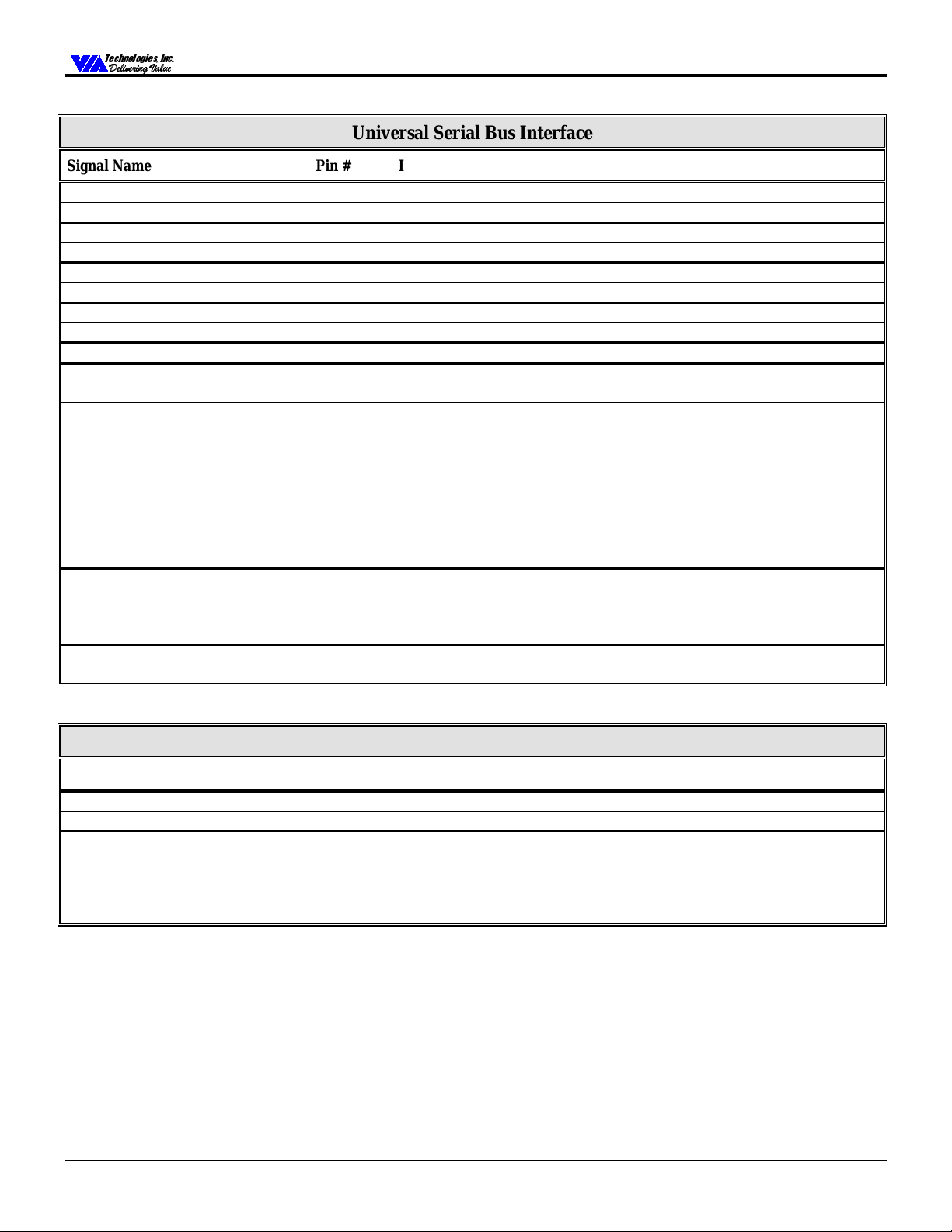

Universal Serial Bus Interface

Signal Name Pin # I/O Signal Description

VT82C686A

USBP0+

USBP0USBP1+

USBP1USBP2+

USBP2USBP3+

USBP3USBCLK

USBOC0#

/ GPI13 / GPO25 /

DACK2# / FDCIRQ

USBOC1#

/ GPI12 / GPO24 /

DRQ2 / FDCDRQ / SERIRQ

USBOC0#

USBOC1#

USBOC2#

USBOC3#

USBIRQA

USBIRQB

(SD2 & RFSH#)

(SD1 & RFSH#)

(SD0 & RFSH#)

(SD3 & RFSH#)

/ DACK6#

/ DACK7#

A3 IO

B3 IO

C4 IO

D4 IO

A4 IO

B4 IO

B5 IO

E6 IO

C3 I

G5 I / I / O

O / I

H3 I / I / O

I / I / I

(W2) I

(Y2) I

(Y1) I

(Y3) I

M3 O

N2 O

USB Port 0 Data +

USB Port 0 Data USB Port 1 Data +

USB Port 1 Data USB Port 2 Data +

USB Port 2 Data USB Port 3 Data +

USB Port 3 Data USB Clock.

USB Port 0 Over Current Detect.

USB Port 1 Over Current Detect.

48MHz clock input for the USB interface

Port 0 is disabled if low.

Port 1 is disabled if this

input is low. Direct inputs are provided for overcurrent

protection for ports 0 and 1 which may be used if the alternate

functions of these two pins are not required. If overcurrent

protection is desired on all four ports ( or it is desired to use the

alternate functions of these two pins), an external buffer may be

used to drive the state of USBOC[3-0]# onto SD[3-0] during ISA

bus refresh cycles (i.e., while ISA bus RFSH# is low, so that

RFSH# may be used as the buffer enable).

USB Port 0 Over Current Detect

USB Port 1 Over Current Detect

USB Port 2 Over Current Detect

USB Port 3 Over Current Detect

USB Interrupt Request A.

USB Interrupt Request B.

Output of internal block.

Output of internal block.

System Management Bus (SMB) Interface (I2C Bus)

Signal Name Pin # I/O Signal Description

SMBCLK

SMBDATA

SMBALRT#

/ GPI6

Revision 1.54 February 25, 2000 -11- Pinouts

U9 IO

T9 IO

W10 I

SMB / I2C Clock.

SMB / I2C Data.

SMB Alert.

(System Management Bus I/O space Rx08[3] = 1)

When the chip is enabled to allow it, assertion generates an IRQ

or SMI interrupt or a power management resume event. The

same pin is used as General Purpose Input 6 whose value is

reflected in Rx48[6] of function 4 I/O space

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

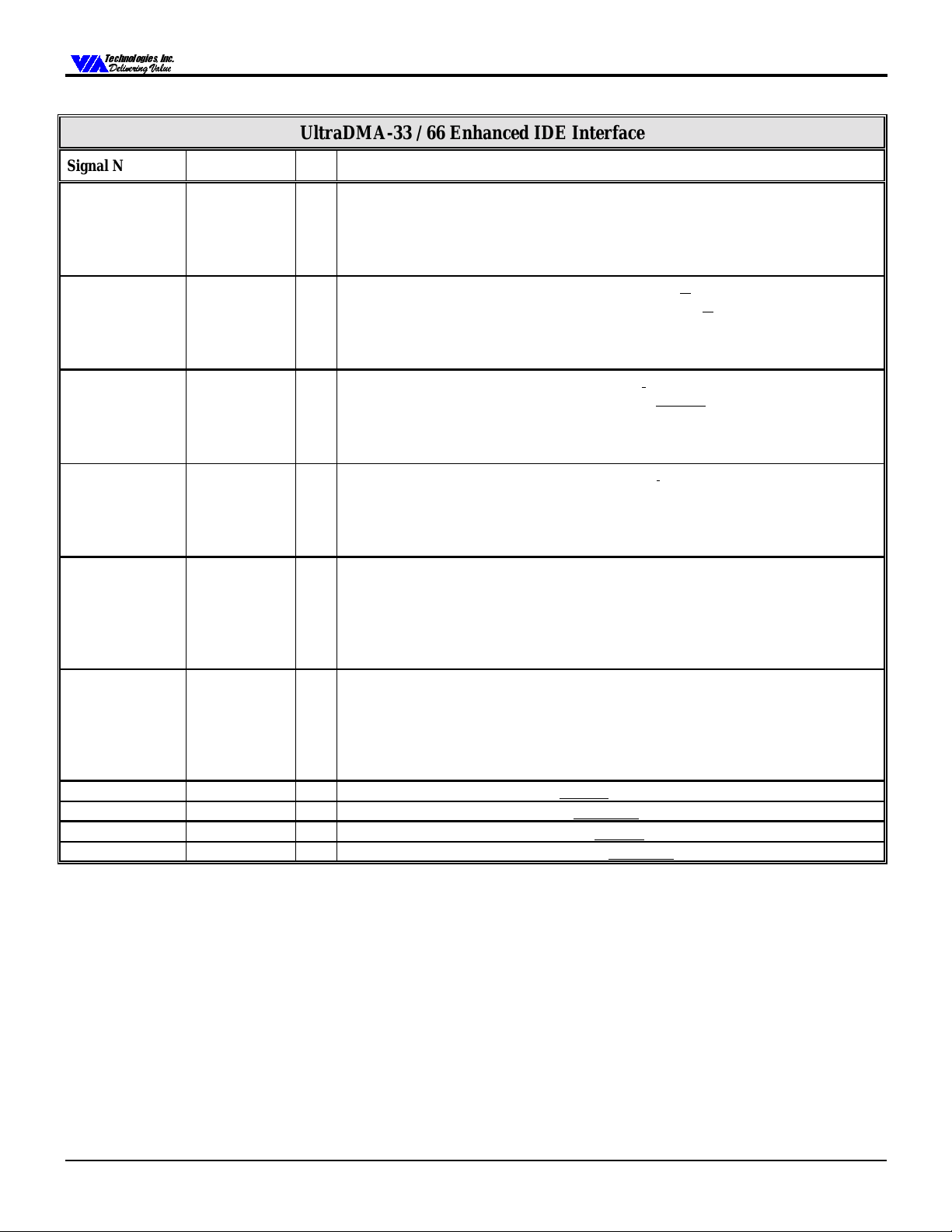

UltraDMA-33 / 66 Enhanced IDE Interface

Signal Name Pin # I/O Signal Description

VT82C686A

PDRDY

/

PDDMARDY /

PDSTROBE

SDRDY

/

SDDMARDY /

SDSTROBE

PDIOR#

/

PHDMARDY /

PHSTROBE

SDIOR#

/

SHDMARDY /

SHSTROBE

PDIOW#

/

PSTOP

SDIOW#

/

SSTOP

PDDRQ

SDDRQ

PDDACK#

SDDACK#

N16 I

V20 I

N17 O

W19 O

N18 O

W20 O

N19 I

Y20 I

M20 O

V19 O

EIDE Mode:

UltraDMA Mode:

Primary I/O Channel Ready.

Primary Device DMA Ready

may assert DDMARDY to pause output transfers

Primary Device Strobe

device may stop DSTROBE to pause input data transfers

EIDE Mode:

UltraDMA Mode:

Secondary I/O Channel Ready.

Secondary Device DMA Ready

device may assert DDMARDY to pause output transfers

Secondary Device Strobe

device may stop DSTROBE to pause input data transfers

EIDE Mode:

UltraDMA Mode:

Primary Device I/O Read.

Primary Host DMA Ready

The host may assert HDMARDY to pause input transfers

Primary Host Strobe

host may stop HSTROBE to pause output data transfers

EIDE Mode:

UltraDMA Mode:

Secondary Device I/O Read.

Secondary Host DMA Ready

may assert HDMARDY to pause input transfers

Host Strobe B

. Output strobe (both ed ges). The host may stop

HSTROBE to pause output data transfers

EIDE Mode:

UltraDMA Mode:

Primary Device I/O Write.

Primary Stop

. Stop transfer: Asserted by the host prior to

initiation of an UltraDMA burst; negated by the host before data

is transferred in an UltraDMA burst. Assertion of STOP by the

host during or after data transfer in UltraDMA mode signals the

termination of the burst.

EIDE Mode:

UltraDMA Mode:

Secondary Device I/O Write.

Secondary Stop

. Stop transfer: Asserted by the host prior to

initiation of an UltraDMA burst; negated by the host before data

is transferred in an UltraDMA burst. Assertion of STOP by the

host during or after data transfer in UltraDMA mode signals the

termination of the burst.

Primary Device DMA Request.

Secondary Device DMA Request.

Primary Device DMA Acknowledge.

Primary channel DMA request

Secondary channel DMA request

Primary channel DMA acknowledge

Secondary Device DMA Acknowledge.

Device ready indicator

. Output flow cont rol. The d evice

. Input data strobe (both edges). The

Device ready indicator

. Output flow control. The

. Input data strobe (both edges). The

Device read strobe

. Primary channel input flow control

. Output data strobe (both edges). The

Device read strobe

. Input flow control. The host

Device write strobe

Device write strobe

Secondary channel DMA acknowledge

.

Revision 1.54 February 25, 2000 -12- Pinouts

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

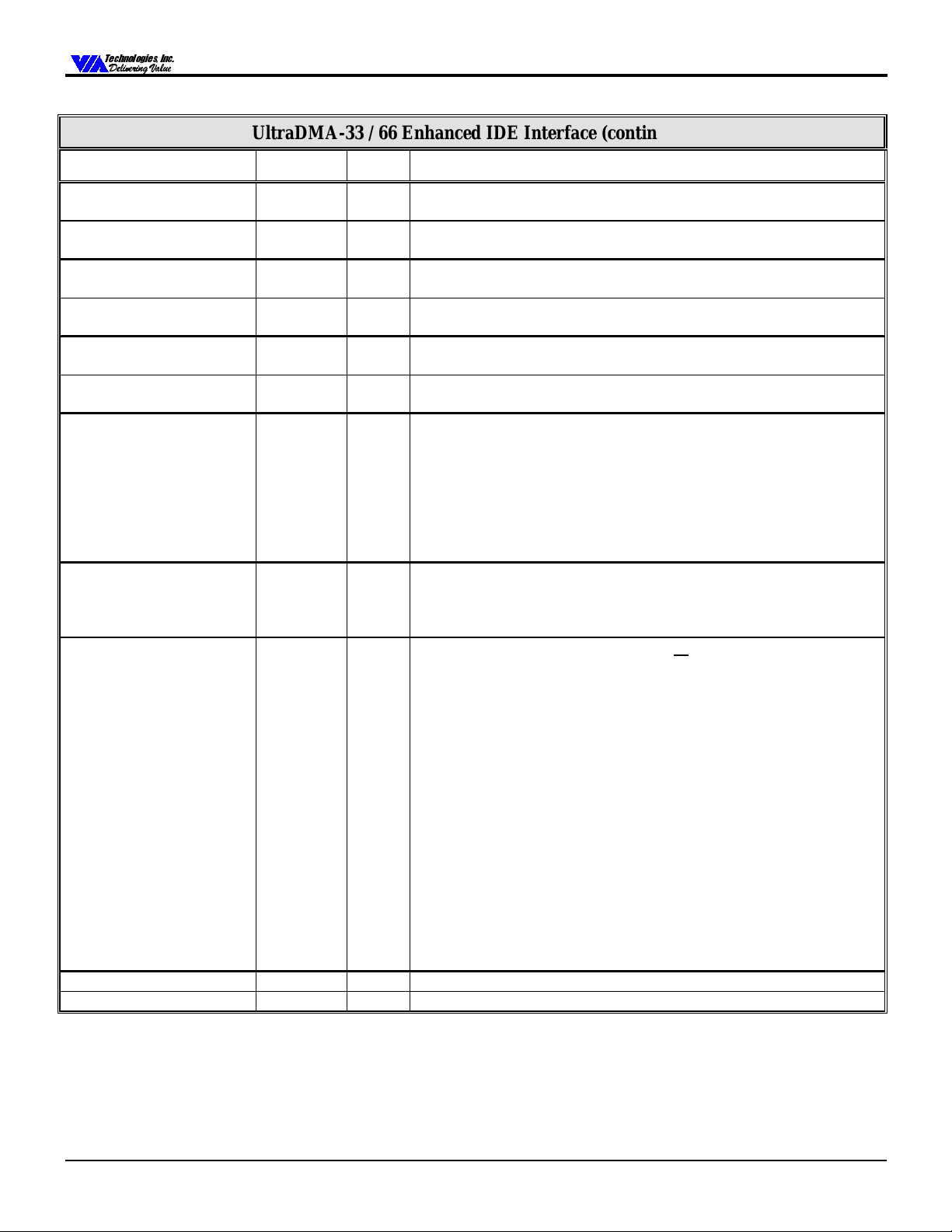

UltraDMA-33 / 66 Enhanced IDE Interface (continued)

Signal Name Pin # I/O Signal Description

VT82C686A

PDCS1#

PDCS3#

SDCS1#

SDCS3#

PDA[2-0]

SDA[2-0]

PDD[15-0]

SDD[15-0]

SDD[15] /

SDD[14] /

SDD[13] /

SDD[12] /

SDD[11] /

SDD[10] /

SDD[9] /

SDD[8] /

SDD[7] /

SDD[6] /

SDD[5] /

SDD[4] /

SDD[3] /

SDD[2] /

SDD[1] /

SDD[0] /

IDEIRQA

IDEIRQB

/ SA[15-0]

,

MSI

,

MSO

/ PDRQB,

JBB1

/ PGNTB,

JBB2

/ PDRQA,

JAB1

/ PGNTA,

JAB2

/ GPO23,

JAX

/ GPO22,

JAY

/ GPI23,

JBX

/ GPI22,

JBY

ACRST

SDOUT

SYNC

SDIN2

SDIN

,

,

,

,

,

BITCLK

/ DACK0#

/ DACK1#

L20 O

M16 O

U17 O

U18 O

M18, M19,

M17

U20, V18,

U19

N20, P17,

P19, R16,

R18, R20,

T17, T19,

T20, T18,

T16, R19,

R17, P20,

P18, P16

P5, R1-R5,

T1-T4, U1-

U3, V1,

V2, W1

Y19,

Y18,

W17,

U16,

W16,

T15,

V15,

Y15,

U14,

W15,

U15,

Y16,

V16,

Y17,

V17,

W18

L2 O

E1 O

O

O

IO

IO

IO / I

IO / O

IO / I

IO / I

IO / I

IO / I

IO / I

IO / I

IO / I

IO / I

IO / O

IO / O

IO / O

IO / I

IO / I

IO / I

Primary Master Chip Select.

This signal corresponds to CS1FX# on

the primary IDE connector.

Primary Slave Chip Select.

This signal corresponds to CS3FX# on the

primary IDE connector.

Secondary Master Chip Select.

This signal corresponds to CS17X# on

the secondary IDE connector.

Secondary Slave Chip Select.

This signal corresponds to CS37X# on

the secondary IDE connector.

Primary Disk Address.

PDA[2:0] are used to indicate which byte in

either the ATA command block or control block is being accessed.

Secondary Disk Address.

SDA[2:0] are used to indicate which byte in

either the ATA command block or control block is being accessed.

Primary Disk Data

Secondary Disk Data

ISA Bus Address only

muxed with ISA Bus Address (Audio Enabled)

(Audio Disabled / Dedicated Secondary IDE

Data) Note: Audio is enabled by strapping the SPKR pin high with

4.7K ohms and disabled by strapping the SPKR pin low with 4.7K ohms.

Secondary Disk Data

AC-Link/Game Ports

(SPKR strap = 0)

(SPKR strap = 1)

or

Secondary Disk Data 15 / Midi Serial In

Secondary Disk Data 14 / Midi Serial Out

Secondary Disk Data 13 / Game Port Joystick B Button 1

Secondary Disk Data 12 / Game Port Joystick B Button 2

Secondary Disk Data 11 / Game Port Joystick A Button 1

Secondary Disk Data 10 / Game Port Joystick A Button 2

Secondary Disk Data 9 / Game Port Joystick A X-axis

Secondary Disk Data 8 / Game Port Joystick A Y-axis

Secondary Disk Data 7 / Game Port Joystick B X-axis

Secondary Disk Data 6 / Game Port Joystick B Y-axis

Secondary Disk Data 5 / AC97 Reset

Secondary Disk Data 4 / AC97 Serial Data Out

Secondary Disk Data 3 / AC97 Sync

Secondary Disk Data 2 / AC97 Serial Data In 2

Secondary Disk Data 1 / AC97 Serial Data In

Secondary Disk Data 0 / AC97 Bit Clock

IDE Interrupt Request A.

IDE Interrupt Request B.

Output of internal block.

Output of internal block.

Revision 1.54 February 25, 2000 -13- Pinouts

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

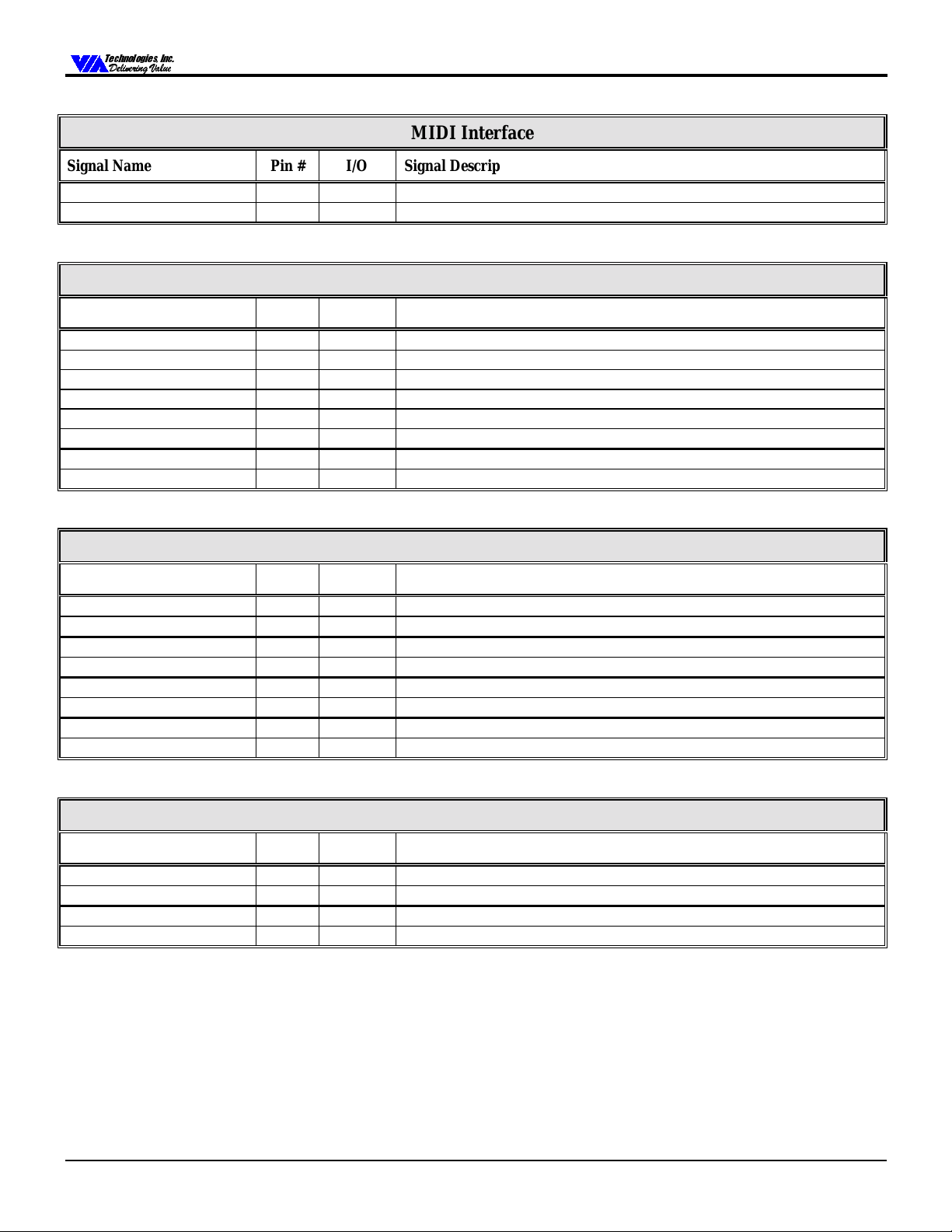

MIDI Interface

Signal Name Pin # I/O Signal Description

VT82C686A

MSI

MSO

/ SDD[15]

/ SDD[14]

Y19 I / IO

Y18 O / IO

MIDI Serial In

MIDI Serial Out

AC97 Audio / Modem Interface

Signal Name Pin # I/O Signal Description

ACRST

SDOUT

SYNC

SDIN2

SDIN

BITCLK

AC97IRQ

MC97IRQB

/ SDD[5]

/ SDD[4]

/ SDD[3]

/ SDD[2]

/ SDD[1]

/ SDD[0]

/ DACK3#

/ DACK5#

U15 O / IO

Y16 O / IO

V16 O / IO

Y17 I / IO

V17 I / IO

W18 I / IO

D2 O

L4 O

AC97 Reset

AC97 Serial Data Out

AC97 Sync

AC97 Serial Data In 2

AC97 Serial Data In

AC97 Bit Clock

AC97 Interrupt Request.

MC97 Interrupt Request.

Game Port Interface

Signal Name Pin # I/O Signal Description

/ SDD[11] / PDRQA

JAB1

/ SDD[10] / PGNTA

JAB2

/ SDD[13] / PDRQB

JBB1

/ SDD[12] / PGNTB

JBB2

/ SDD[9] / GPO23

JAX

/ SDD[8] / GPO22

JAY

/ SDD[7] / GPI23

JBX

/ SDD[6] / GPI22

JBY

See Function 0 Rx77[6]

W16 I / I O / I

T15 I / IO / O

W17 I / I O / I

U16 I / IO / O

V15 I / IO / O

Y15 I / IO / O

U14 I / IO / I

W15 I / I O / I

Joystick A Button 1

Joystick A Button 2

Joystick B Button 1

Joystick B Button 2

Joystick A X-axis

Joystick A Y-axis

Joystick B X-axis

Joystick B Y-axis

/ Secondary Disk Data 15 (SPKR strap = 1)

/ Secondary Disk Data 14 (SPKR strap = 1)

/ Secondary Disk Data 5 (SPKR strap = 1)

/ Secondary Disk Data 4 (SPKR strap = 1)

/ Secondary Disk Data 3 (SPKR strap = 1)

/ Secondary Disk Data 2 (SPKR strap = 1)

/ Secondary Disk Data 1 (SPKR strap = 1)

/ Secondary Disk Data 0 (SPKR strap = 1)

Output of internal block.

Output of internal block.

/ Secondary Disk Data 11 (SPKR strap = 1)

/ Secondary Disk Data 10 (SPKR strap = 1)

/ Secondary Disk Data 13 (SPKR strap = 1)

/ Secondary Disk Data 12 (SPKR strap = 1)

/ Secondary Disk Data 9 (SPKR strap = 1)

/ Secondary Disk Data 8 (SPKR strap = 1)

/ Secondary Disk Data 7 (SPKR strap = 1)

/ Secondary Disk Data 6 (SPKR strap = 1)

PDRQ / PGNT Interface

Signal Name Pin # I/O Signal Description

PDRQA

PGNTA

PDRQB

PGNTB

Revision 1.54 February 25, 2000 -14- Pinouts

/ SDD[11] JAB1

/ SDD[10] / JAB2

/ SDD[13] / JBB1

/ SDD[12] / JBB2

W16 I / I O / I

T15 O / IO / I

W17 I / I O / I

U16 O / IO / I

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

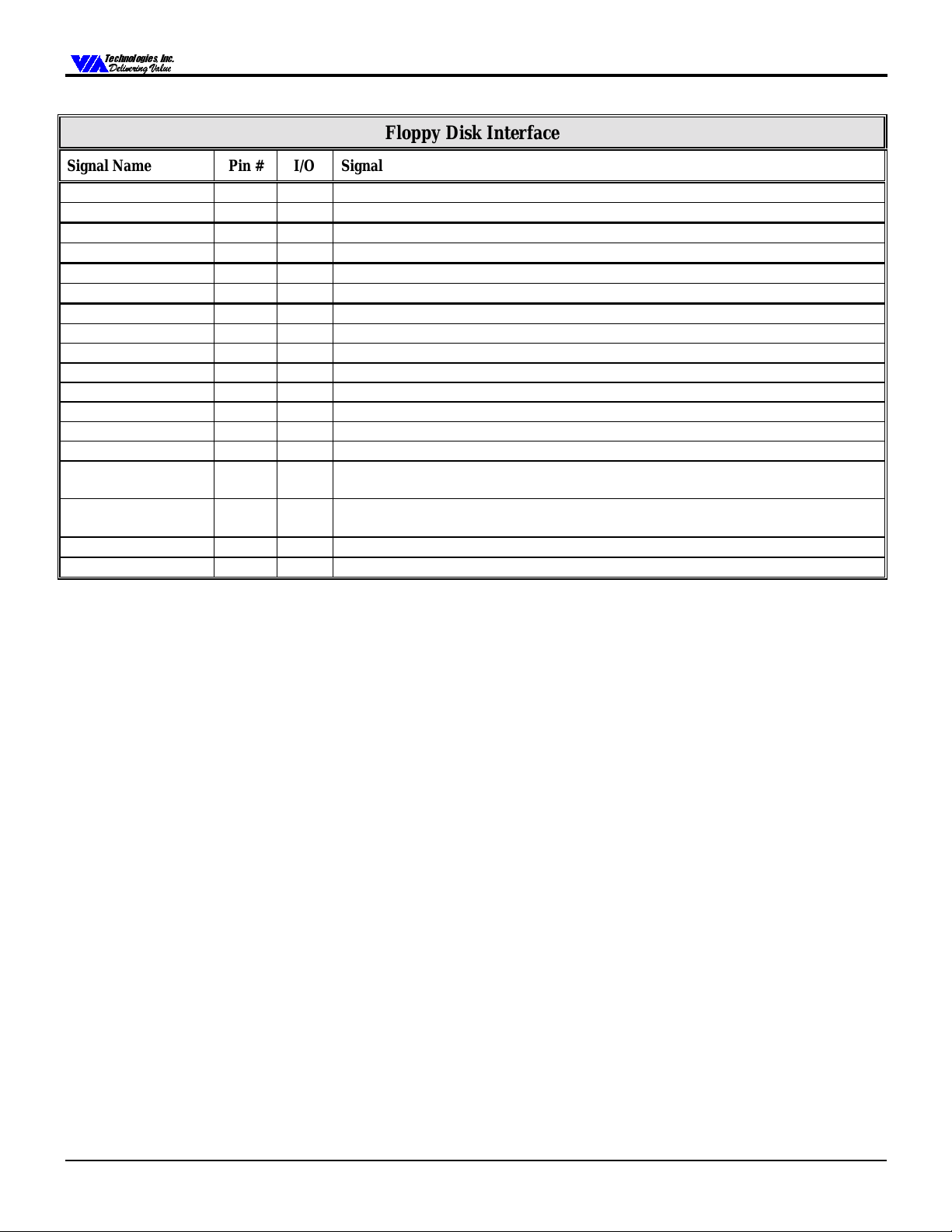

Floppy Disk Interface

Signal Name Pin # I/O Signal Description

VT82C686A

DRVDEN0

DRVDEN1

MTR0#

MTR1#

DS0#

DS1#

DIR#

STEP#

INDEX#

HDSEL#

TRK00#

RDATA#

WDATA#

WGATE#

DSKCHG#

WRTPRT#

FDCIRQ

/ DACK2#

FDCDRQ

/ DRQ2

D9 O

D6 O

E9 O

C8 O

B8 O

A8 O

D8 O

E8 O

D7 I

C7 O

E7 I

B6 I

A7 O

B7 O

C6 I

A6 I

G5 I

H3 I

Drive Density Select 0.

Drive Density Select 1.

Motor Control 0.

Motor Control 1.

Drive Select 0.

Drive Select 1.

Direction.

Step.

Index.

Direction of head movement (0 = inward motion, 1 = outward motion)

Low pulse for each track-to-track movement of the head.

Sense to detect that the head is positioned over the beginning of a track

Head Select.

Track 0.

Sense to detect that the head is positioned over track 0.

Read Data.

Write Data.

Write Gate.

Disk Change.

Select motor on drive 0.

Select motor on drive 1

Select drive 0.

Select drive 1

Selects the side for R/W operations (0 = side 1, 1 = side 0)

Raw serial bit stream from the drive for read operatrions.

Encoded data to the drive for write operations.

Signal to the drive to enable current flow in the write head.

Sense that the drive door is open or the diskette has been changed

since the last drive selection.

Write Protect.

Sense for detection that the diskette is write protected (causes write

commands to be ignor ed)

FDC Interrupt Request.

FDC DMA Request.

Rx75[3] = 1.

Rx75[3] = 1.

Revision 1.54 February 25, 2000 -15- Pinouts

7HFKQRORJLHV ,QF

'HOLYHULQJ 9DOXH

'HOLYHULQJ 9DOXH

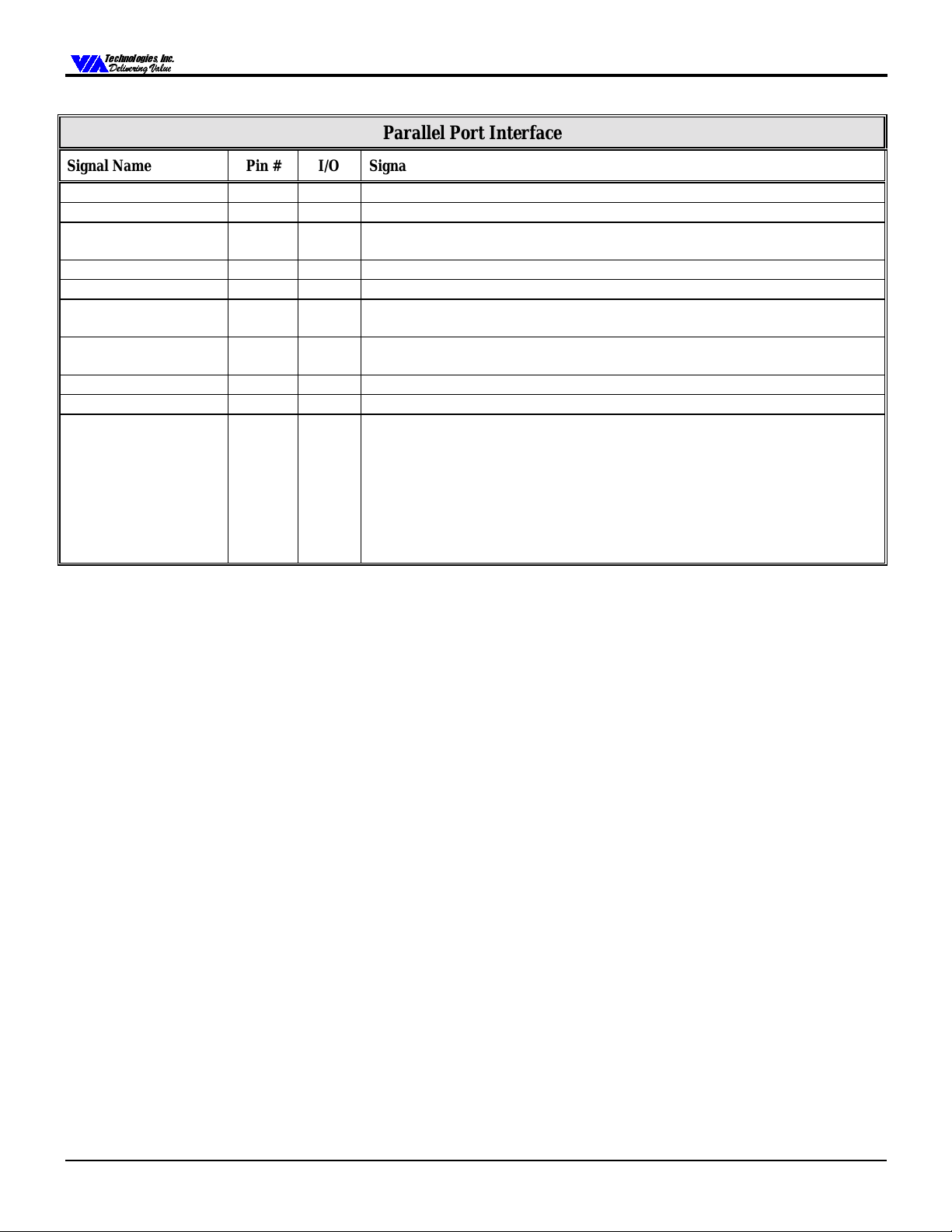

Parallel Port Interface

Signal Name Pin # I/O Signal Description

VT82C686A

PINIT#

/ DIR#

STROBE#

AUTOFD#

/ nc

/ DRVEN0

C15 IO / O

D16 IO / -

C16 IO / O

Initialize.

Strobe.

Output used to strobe data into the printer. I/O in ECP/EPP mode.

Auto Feed.

Initialize printer. Output in standard mode, I/O in ECP/EPP mode.

Output used to cause the printer to automatically feed one line after

each line is printed. I/O pin in ECP/EPP mode.

SLCTIN#

/ WGATE#

SLCT

/ DS1#

ACK#

/ STEP#

E15 IO / O

E13 I / O

B13 I / O

Select In.

Select.

Acknowledge.

Output used to select the printer. I/O pin in ECP/EPP mode.

Status output from the printer. High indicates that it is powered on.

Status output from the printer. Low indicates that it has received

the data and is ready to accept new data

ERROR#

/ HDSEL#

A15 I / O

Status output from the printer. Low indicates an error condition in the

Error.

printer.

/ MTR1#

BUSY

/ WDAT A#

PE

/ nc,

PD7

/ nc,

PD6

/ nc,

PD5

/ DSKCHG#,

PD4

/ RDATA#,

PD3

/ WRTPRT#,

PD2

/ TRK00#,

PD1

/ INDEX#

PD0

C13 I / O