VIA VT82C596B Datasheet

Z

H

FRQQHFW

97&%

6RXWK%ULGJH

3,3&

3&,,QWHJUDWHG3HULSKHUDO&RQWUROOHU

3&&RPSOLDQW3&,WR,6$%ULGJH

ZLWK$&3,(QKDQFHG3RZHU0DQDJHPHQW60%XV

$3,&'LVWULEXWHG'0$6HULDO,543OXJDQG3OD\

8OWUD'0$0DVWHU0RGH3&,(,'(&RQWUROOHU

86%&RQWUROOHU.H\ERDUG&RQWUROOHUDQG57&

5HYLVLRQ

-XQH

9,$7(&+12/2*,(6,1&

&RS\ULJKW1RWLFH

&RS\ULJKW 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG 3ULQWHG LQ WKH 8QLWHG 6WDWHV $//5

1R SDUW RI WKLV GRFXPHQW PD\ EH UHSURGXFHG WUDQVPLWWHG WUDQVFULEHG VWRUHG LQ D UHWULHYDO V\VWHP RU WUDQVODWHG LQWR

DQ\ ODQJXDJH LQ DQ\ IRUP RU E\ DQ\ PHDQV HOHFWURQLF PHFKDQLFDO PDJQHWLF RSWLFDO FKHPLFDO PDQXDO RU RWKHUZLVH

ZLWKRXW WKH SULRU ZULWWHQ SHUPLVVLRQ RI 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG

97&% PD\ RQO\ EH XVHG WR LGHQWLI\ D SURGXFW RI 9,$ 7HFKQRORJLHV ,QF

LV D UHJLVWHUHG WUDGHPDUN RI 9,$ 7HFKQRORJLHV ,QFRUSRUDWHG

70

36

&HOHURQ

:LQGRZV

3&,

$OO WUDGHPDUNV DUH WKH SURSHUWLHV RI WKHLU UHVSHFWLYH RZQHUV

LV D UHJLVWHUHG WUDGHPDUN RI ,QWHUQDWLRQDO %XVLQHVV 0DFKLQHV &RUS

70

3HQWLXP,,70 3HQWLXP,,,70 *7/70 $3,&70 DQG ,QWHO70DUH UHJLVWHUHG WUDGHPDUNV RI ,QWHO &RUS

70

70

LV D UHJLVWHUHG WUDGHPDUN RI WKH 3&, 6SHFLDO ,QWHUHVW *URXS

DQG 3OXJ DQG 3OD\70DUH UHJLVWHUHG WUDGHPDUNV RI 0LFURVRIW &RUS

,*+765(6(59('

'LVFODLPHU1RWLFH

1R OLFHQVH LV JUDQWHG LPSOLHG RU RWKHUZLVH XQGHU DQ\ SDWHQW RU SDWHQW ULJKWV RI 9,$ 7HFKQRORJLHV 9,$ 7HFKQRORJLHV

PDNHV QR ZDUUDQWLHV LPSOLHG RU RWKHUZLVH LQ UHJDUG WR WKLV GRFXPHQW DQG WR WKH SURGXFWV GHVFULEHG LQ WKLV GRFXPHQW

7KH LQIRUPDWLRQ SURYLGHG E\ WKLV GRFXPHQW LV EHOLHYHG WR EH DFFXUDWH DQG UHOLDEOH WR WKH SXEOLFDWLRQ GDWH RI WKLV

GRFXPHQW +RZHYHU 9,$ 7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU DQ\ HUURUV LQ WKLV GRFXPHQW )XUWKHUPRUH 9,$

7HFKQRORJLHV DVVXPHV QR UHVSRQVLELOLW\ IRU WKH XVH RU PLVXVH RI WKH LQIRUPDWLRQ LQ WKLV GRFXPHQW DQG IRU DQ\ SDWHQW

LQIULQJHPHQWV WKDW PD\ DULVH IURP WKH XVH RI WKLV GRFXPHQW 7KH LQIRUPDWLRQ DQG SURGXFW VSHFLILFDWLRQV ZLWKLQ WKLV

GRFXPHQW DUH VXEMHFW WR FKDQJH DW DQ\ WLPH ZLWKRXW QRWLFH DQG ZLWKRXW REOLJDWLRQ WR QRWLI\ DQ\ SHUVRQ RI VXFK FKDQJH

2IILFHV

86$ 2IILFH 7DLSHL 2IILFH

0LVVLRQ &RXUW

)UHPRQW &$ &KXQJ&KHQJ 5RDG +VLQ7LHQ

86$ 7DLSHL 7DLZDQ 52&

7HO 7HO

)D[ )D[

2QOLQH6HUYLFHV

+RPH 3DJH

)73 6HUYHU

%%6

http://www.via.com.tw

ftp.via.com.tw

¤RU

http://www.viatech.com

WK

)ORRU 1R

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

R

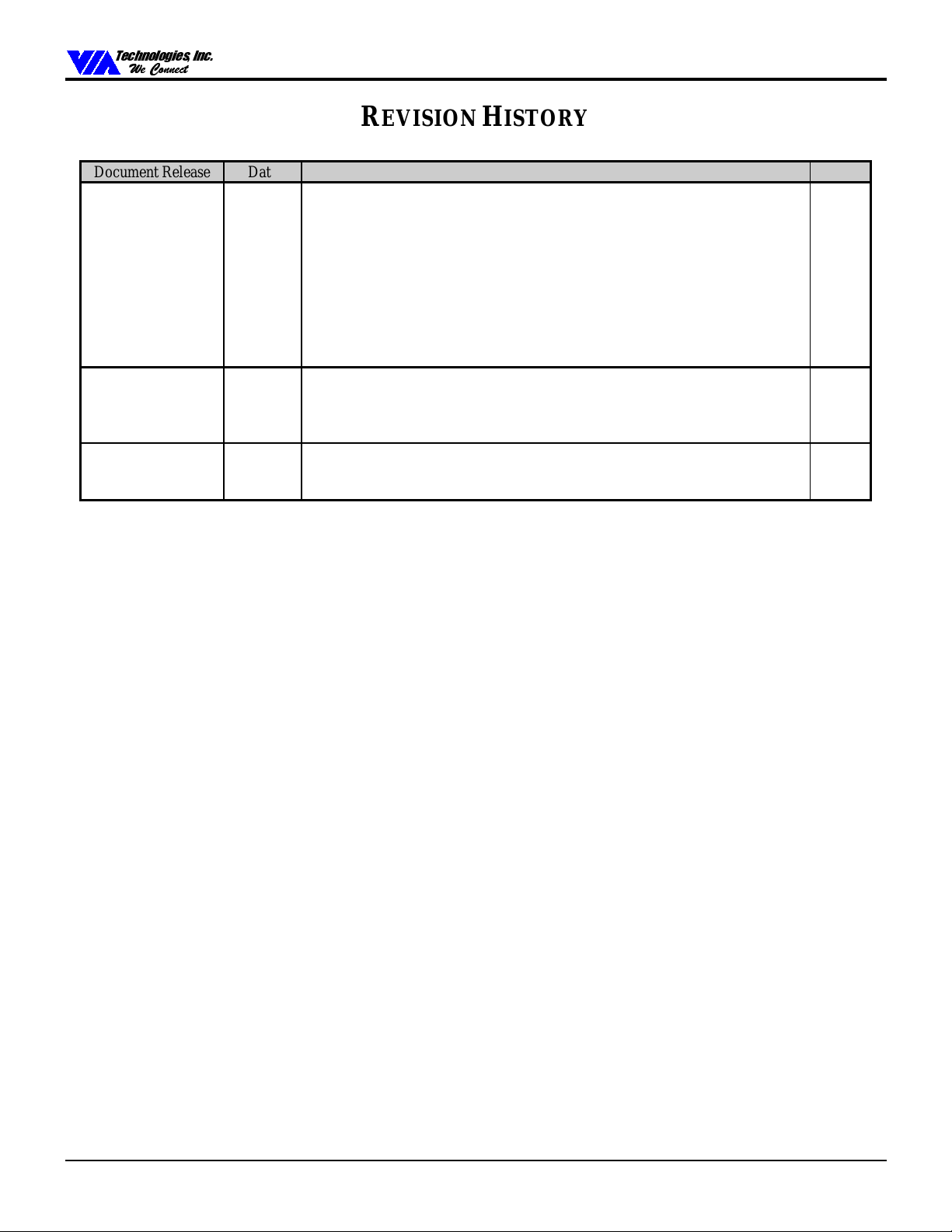

EVISION HISTORY

Document Release Date Revision Initials

Revision 0.1 2/23/99 Initial release based on 82C596A Data Sheet revision 1.1

- Added UltraDMA-66 to feature bullets and overview

- Added integrated APIC (changed H18, K18, J17 pin descriptions)

- Added note to RTC CMOS Register Summary

- Added / changed function 0 Rx42[6], Rx48[7-4], Rx5B[3], Rx5C[7-4, 2],

Rx74[29-24, 8, 1], Rx87-89

- Added / changed function 3 Rx8, Rx4D[2-0], Rx54-55, Rx58-5B, Rx90-91,

RxD2-D6 (80-88 renumbered), PMU I/O Offset 0[11], 20[14, 7-1],

22[14, 7-1], 24[14, 7-1], 28[15-11], 2A[15-11], 2C[11-10], 38[2-1],

44[10-1], 4C[30-0]

Revision 0.2 3/9/99 Updated feature bullets, overview, and pin descriptions

Replaced IDE function 1 with registers from 686B to reflect UltraDMA-66

Added / changed PMU function 3 registers Rx42[7-6, 4], Rx58-5B, PMU I/O

Offset 0[8], 2C[2], 30[10-0], 34[10-0], 38[6, 4-3], 40 (removed)

Revision 0.3 6/17/99 Changed Function 0 Rx42[2-0], 43[5-4], 50 default, 55[3-0], 57[3-0], 58[3-0],

88[5], Function 1 RxD, 42-43, 45[3-2], 54[4-3], 70, 74-75, 78, 7C-7D,

Function 2 Rx41[7-3], Function 3 Rx4C-4F default value

VT82C596B

DH

DH

DH

Revision 0.3 June 17, 1999 -i- Revision History

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

T

ABLE OF CONTENTS

VT82C596B

REVISION HISTORY........................................................................................................................................................................I

TABLE OF CONTENTS..................................................................................................................................................................II

LIST OF FIGURES..........................................................................................................................................................................IV

LIST OF TABLES ...........................................................................................................................................................................IV

OVERVIEW.......................................................................................................................................................................................3

PINOUTS............................................................................................................................................................................................4

REGISTERS.....................................................................................................................................................................................21

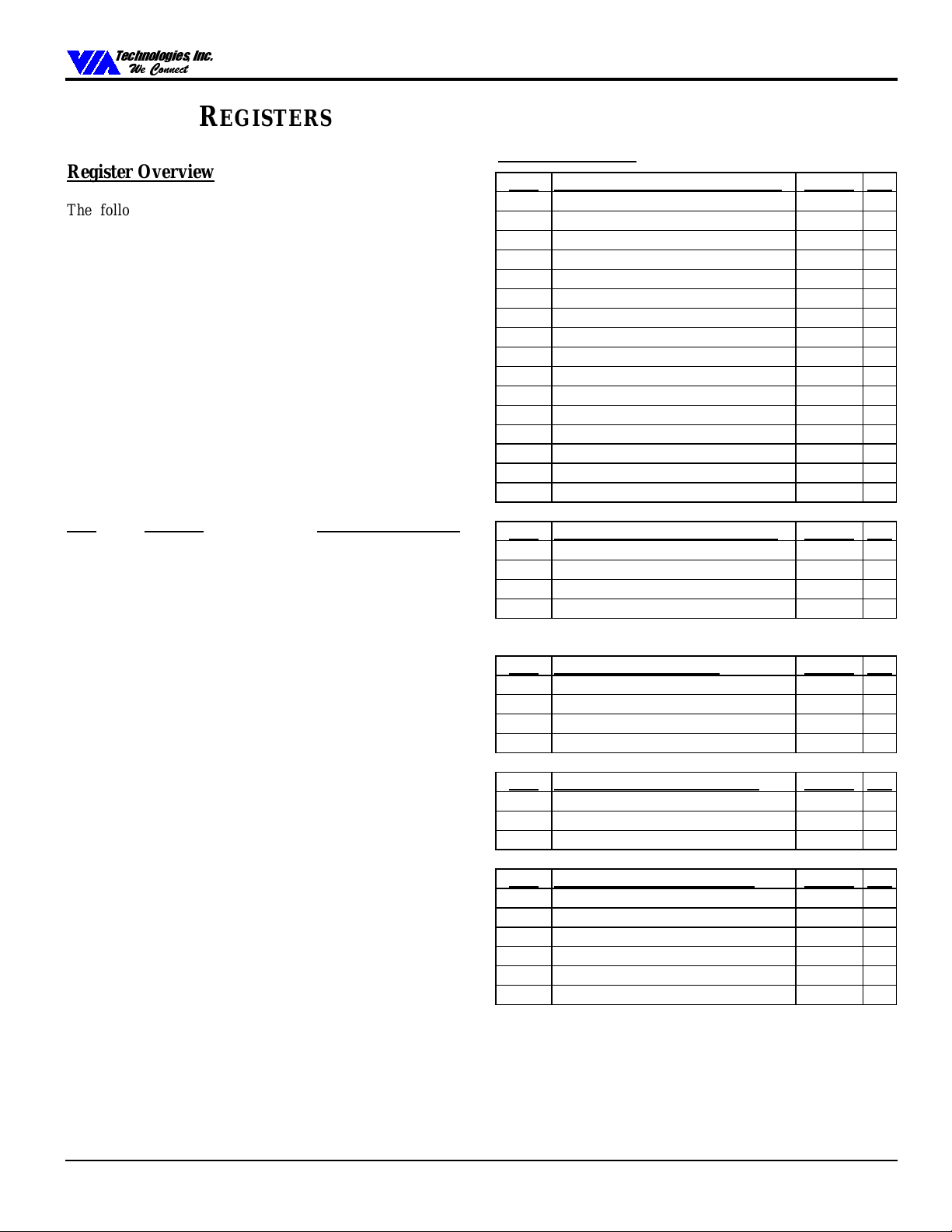

EGISTER OVERVIEW

R

ONFIGURATION SPACE

C

EGISTER DESCRIPTIONS

R

.................................................................................................................................................................21

I/O .......................................................................................................................................................28

............................................................................................................................................................29

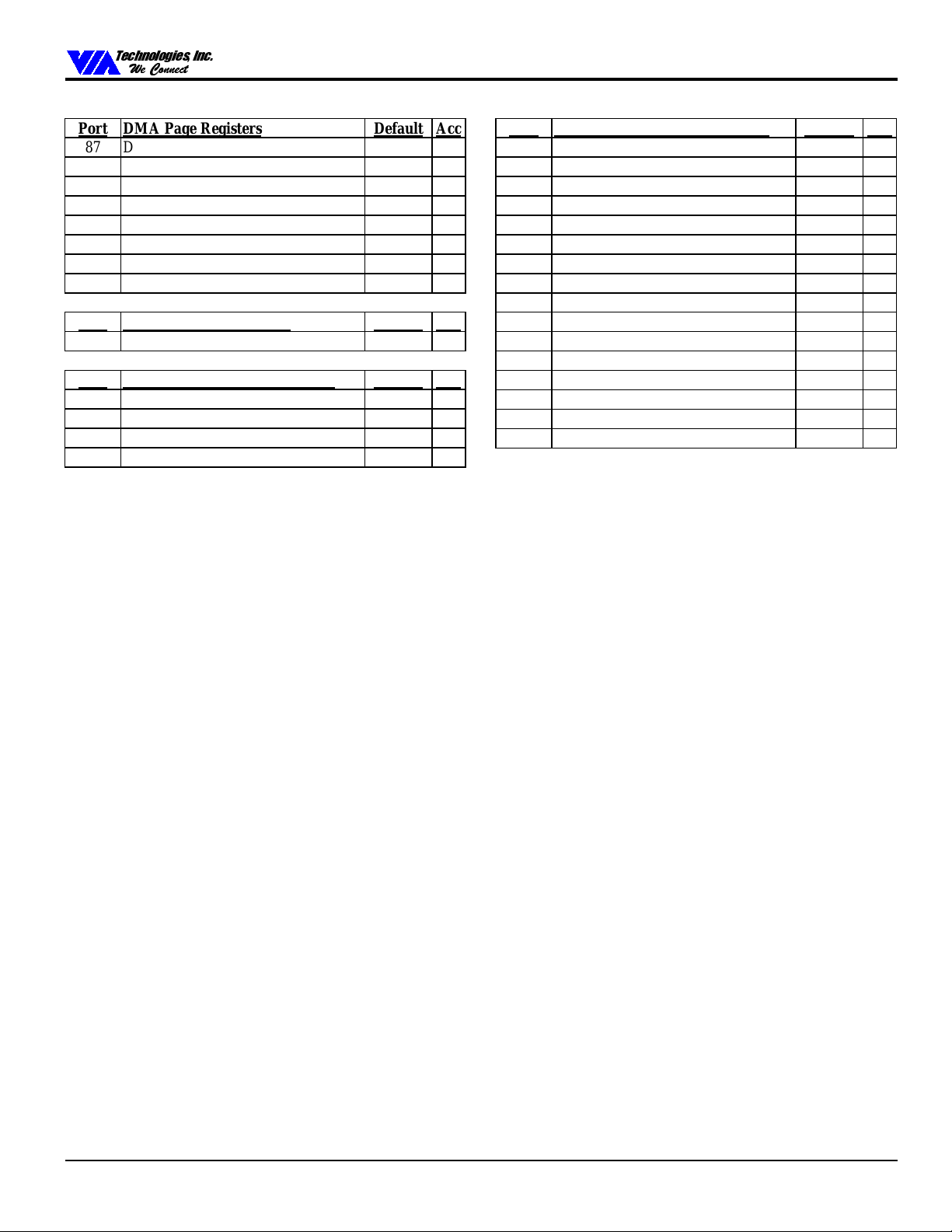

Legacy I/O Ports...................................................................................................................................................................29

Keyboard Controller Registers.............................................................................................................................................................. 30

DMA Controller I/O Registers.............................................................................................................................................................. 32

Interrupt Controller Registers ............................................................................................................................................................... 33

Timer / Counter Registers..................................................................................................................................................................... 33

CMOS / RTC Registers......................................................................................................................................................................... 34

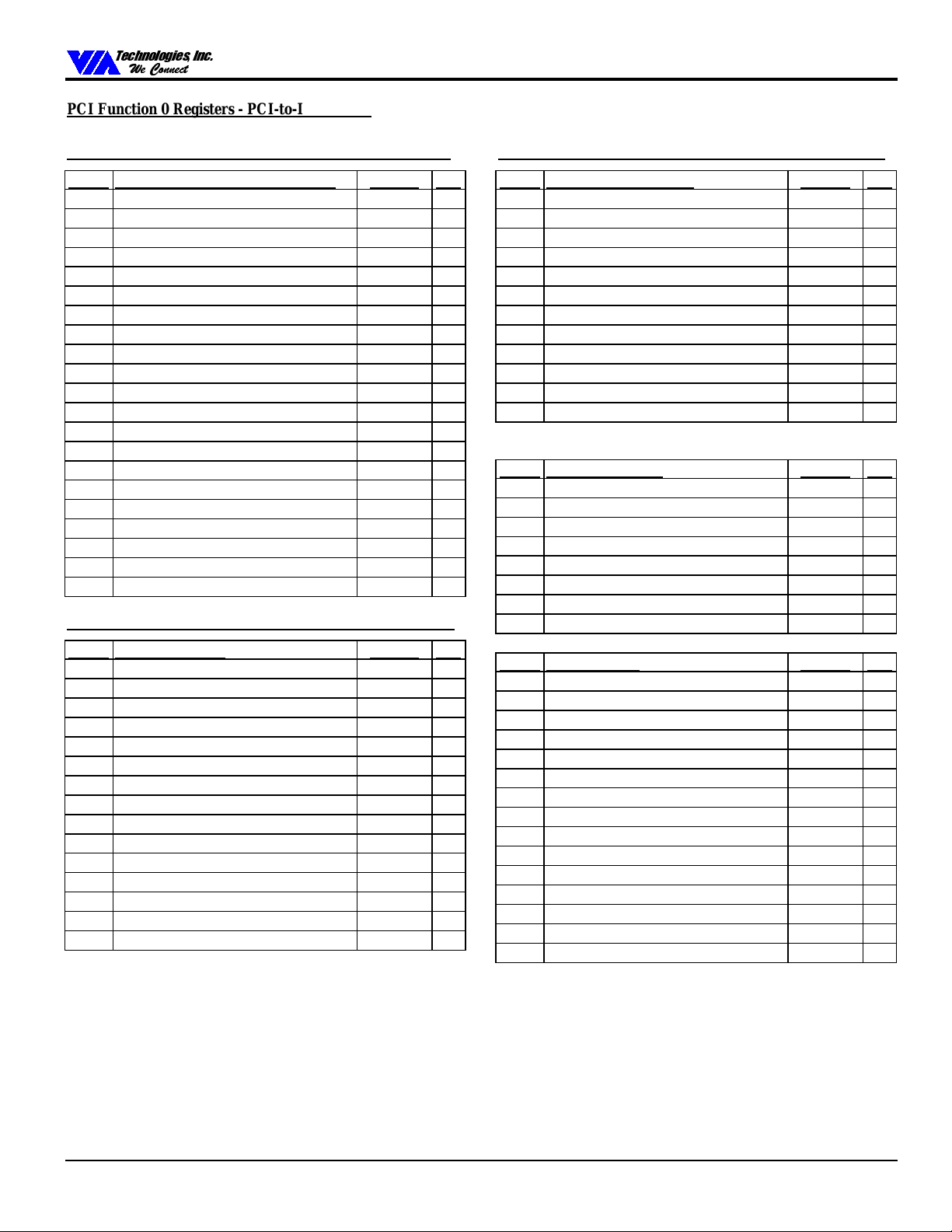

Function 0 Registers - PCI to ISA Bridge...........................................................................................................................35

PCI Configuration Space Header..........................................................................................................................................................35

ISA Bus Control.................................................................................................................................................................................... 36

Plug and Play Control........................................................................................................................................................................... 39

Distributed DMA / Serial IRQ Control................................................................................................................................................. 41

Miscellaneous / General Purpose I/O.................................................................................................................................................... 42

Function 1 Registers - Enhanced IDE Controller..............................................................................................................47

PCI Configuration Space Header..........................................................................................................................................................47

IDE-Controller-Specific Confiiguration Registers................................................................................................................................ 49

IDE I/O Registers.................................................................................................................................................................................. 54

Function 2 Registers - Universal Serial Bus Controller.....................................................................................................55

PCI Configuration Space Header..........................................................................................................................................................55

USB-Specific Configuration Registers.................................................................................................................................................. 56

USB I/O Registers................................................................................................................................................................................. 57

Function 3 Registers - Power Management and SMBus..................................................................................................58

PCI Configuration Space Header..........................................................................................................................................................58

Power Management-Specific PCI Configuration Registers .......................................................................... ........................................ 59

System Management Bus-Specific Configuration Registers................................................................................................................. 65

System Management Bus I/O-Space Registers...................................................................................................................................... 66

Power Management I/O-Space Registers..............................................................................................................................................70

FUNCTIONAL DESCRIPTIONS..................................................................................................................................................78

OWER MANAGEMENT

P

Power Management Subsystem Overview............................................................................................................................................ 78

Processor Bus States............................................................................................................................................................................. 78

System Suspend States and Power Plane Control................................................................................................................................. 79

General Purpose I/O Ports..................................................................................................................................................................... 79

Power Management Events................................................................................................................................................................... 80

System and Processor Resume Events.................................................................................................................................................. 80

Legacy Power Management Timers...................................................................................................................................................... 81

System Primary and Secondary Events................................................................................................................................................. 81

Peripheral Events.................................................................................................................................................................................. 81

................................................................................................................................................................78

ELECTRICAL SPECIFICATIONS...............................................................................................................................................82

Revision 0.3 June 17, 1999 -ii- Table of Contents

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

BSOLUTE MAXIMUM RATINGS

A

HARACTERISTICS

DC C

IMING SPECIFICATIONS

AC T

................................................................................................................................................................82

.................................................................................................................................................82

......................................................................................................................................................83

VT82C596B

PACKAGE MECHANICAL SPECIFICATIONS........................................................................................................................90

Revision 0.3 June 17, 1999 -iii- Table of Contents

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

L

IST OF FIGURES

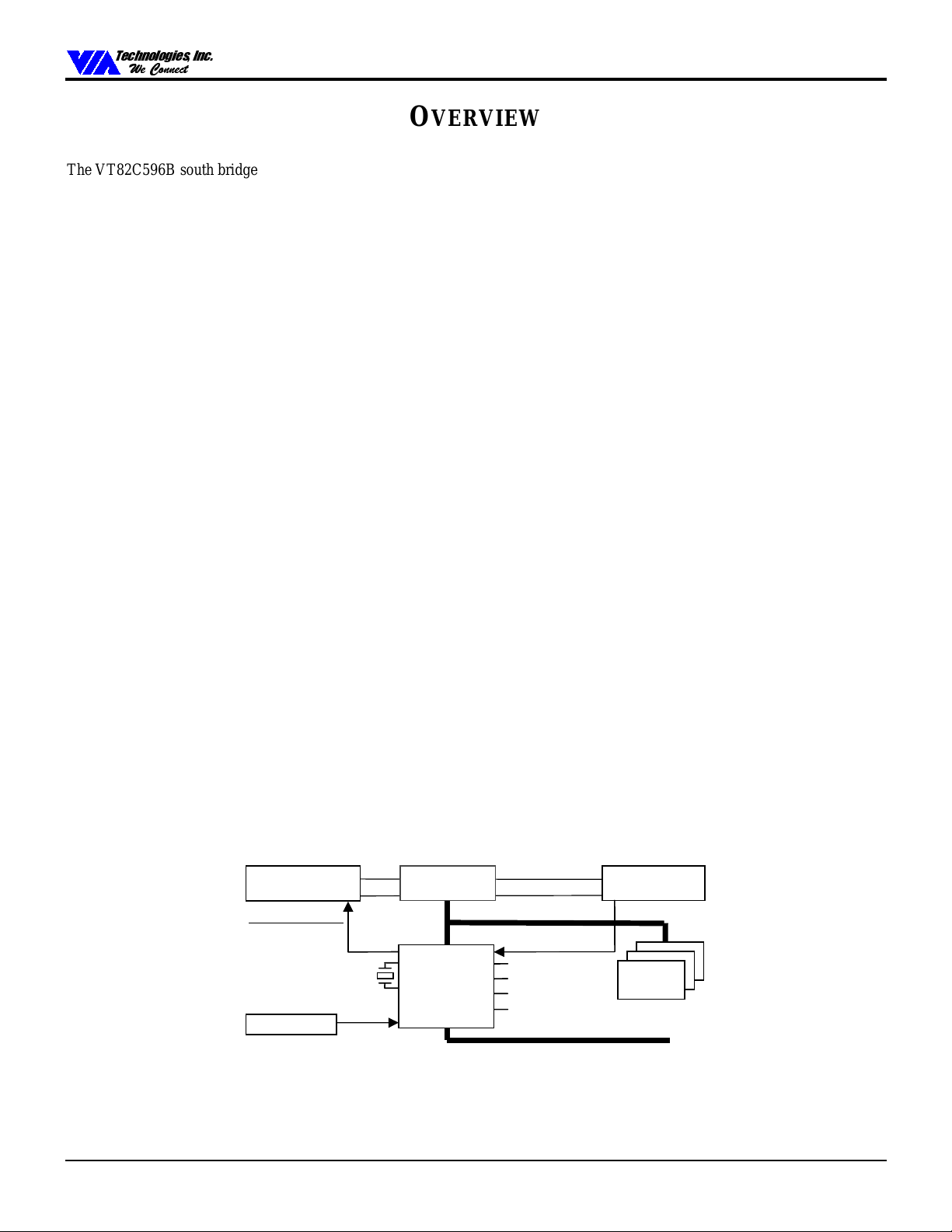

FIGURE 1. PC SYSTEM CONFIGURATION USING THE VT82C596B.................................................................................3

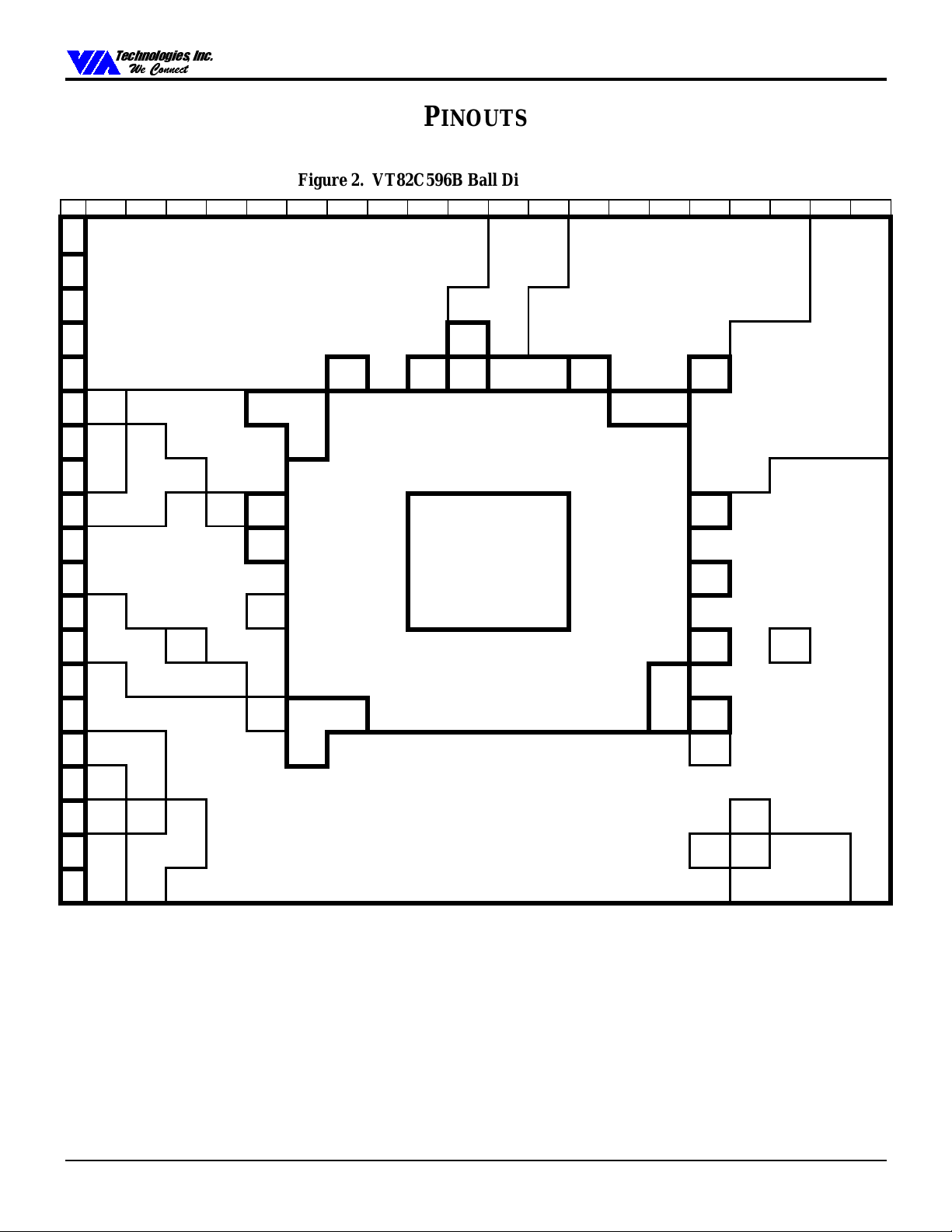

FIGURE 2. VT82C596B BALL DIAGRAM (TOP VIEW)...........................................................................................................4

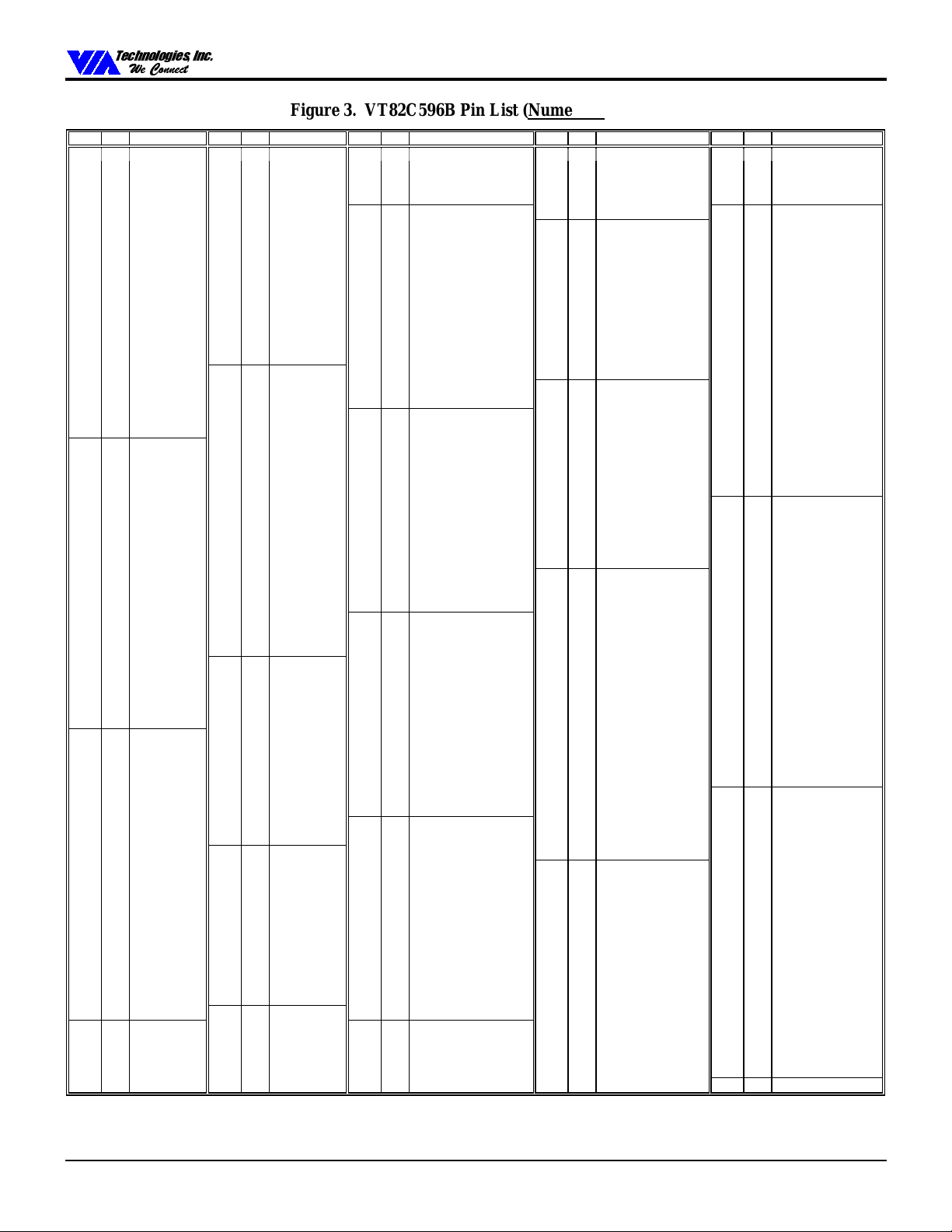

FIGURE 3. VT82C596B PIN LIST (NUMERICAL ORDER)......................................................................................................5

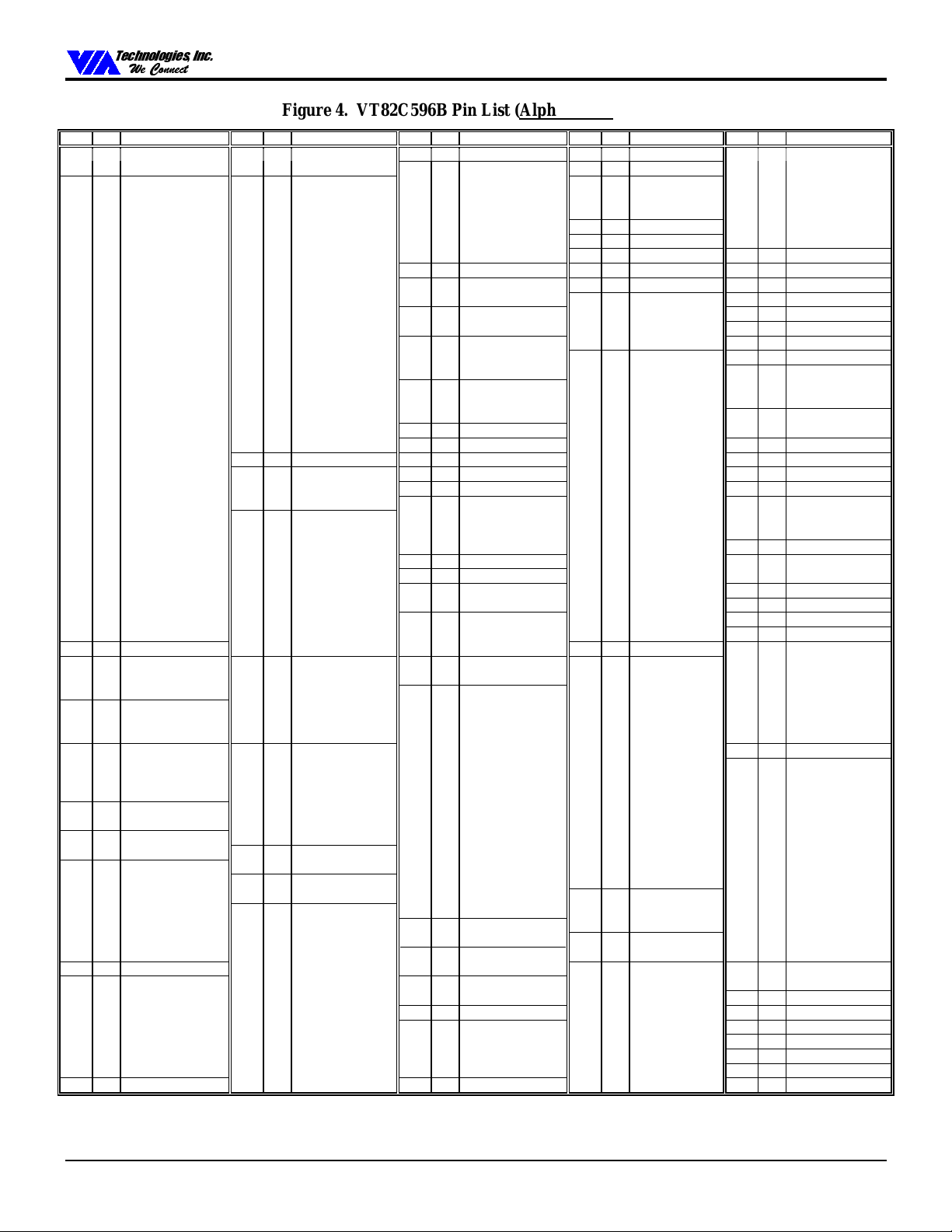

FIGURE 4. VT82C596B PIN LIST (ALPHABETICAL ORDER)............................................................................................... 6

FIGURE 5. STRAP OPTION CIRCUIT.......................................................................................................................................40

FIGURE 6. POWER MANAGEMENT SUBSYSTEM BLOCK DIAGRAM........................................................................... 78

FIGURE 8. ULTRADMA-33 IDE TIMING - DRIVE INITIATING DMA BURST FOR READ COMMAND....................85

FIGURE 9. ULTRADMA-33 IDE TIMING - DRIVE INITIATING BURST FOR WRITE COMMAND............................ 85

FIGURE 10. ULTRADMA-33 IDE TIMING - PAUSING A DMA BURST .............................................................................86

FIGURE 11. ULTRADMA-33 IDE TIMING - DRIVE TERMINATING DMA BURST DURING READ COMMAND....87

FIGURE 12. ULTRADMA-33 IDE TIMING - DRIVE TERMINATING DMA BURST DURING WRITE COMMAND .87

FIGURE 13. ULTRADMA-33 IDE TIMING - HOST TERMINATING DMA BURST DURING READ COMMAND......88

FIGURE 14. ULTRADMA-33 IDE TIMING - HOST TERMINATING DMA BURST DURING WRITE COMMAND...88

FIGURE 15. ULTRADMA-33 IDE TIMING - PIO CYCLE......................................................................................................89

FIGURE 16. MECHANICAL SPECIFICATIONS - 324-PIN BALL GRID ARRAY PACKAGE.........................................90

VT82C596B

L

IST OF TABLES

TABLE 1. PIN DESCRIPTIONS.....................................................................................................................................................7

TABLE 2. SYSTEM I/O MAP.......................................................................................................................................................21

TABLE 3. REGISTERS..................................................................................................................................................................21

TABLE 4. KEYBOARD CONTROLLER COMMAND CODES ..............................................................................................31

TABLE 5. CMOS REGISTER SUMMARY.................................................................................................................................34

TABLE 6. AC CHARACTERISTICS - PCI CYCLE TIMING..................................................................................................83

TABLE 7. AC CHARACTERISTICS - ULTRADMA-33 IDE BUS INTERFACE TIMING..................................................84

Revision 0.3 June 17, 1999 -iv- Table of Contents

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

VT82C596B

VT82C596B PIPC

PCI I

WITH

ACPI, E

APIC, D

U

LTRA

DMA-33/66 M

USB C

Inter-operable with VIA and other Host-to-PCI Bridges

•

−

Combine with VT82C598 (Apollo MVP3) for a complete 66 / 75 / 83 / 100MHz Socket-7 PCI / AGP / ISA system

−

Combine with VT82C693 (Apollo ProPlus) for a complete 66 / 100 MHz Socket-370 or Slot-1 PCI / ISA system

−

Combine with VT82C693A (Apollo Pro133) for a complete 66 / 100 / 133 MHz Skt-370 or Slot-1 PCI / ISA system

PC98 Compliant PCI to ISA Bridge

•

−

Integrated ISA Bus Controller with integrated DMA, timer, and interrupt controller

−

Integrated Keyboard Controller with PS2 mouse support

−

Integrated DS12885-style Real Time Clock with extended 256 byte CMOS RAM and Day/Month Alarm for ACPI

−

Integrated USB Controller with root hub and two function ports

−

Integrated UltraDMA-33/66 master mode EIDE controller with enhanced PCI bus commands

−

PCI-2.1 compliant with delay transaction

−

Eight double-word line buffer between PCI and ISA bus

−

One-level PCI to ISA post-write buffer

−

Supports type F DMA transfers

−

Distributed DMA support for ISA legacy DMA across the PCI bus

−

Sideband signal support for PC/PCI and serial interrupt for docking and non-docking applications

−

Serial Interrupt input

−

Fast reset and Gate A20 operation

−

Edge trigger or level-sensitive interrupts

−

Flash EPROM, 2Mb EPROM and combined BIOS support

−

Supports positive and subtractive decoding

NTEGRATED PERIPHERAL CONTROLLER

PC98 C

OMPLIANT

PCI-TO-ISA B

NHANCED POWER MANAGEMENT

ISTRIBUTED

DMA, S

ERIAL

ASTER MODE

ONTROLLER

, K

EYBOARD CONTROLLER, AND

RIDGE

IRQ, P

LUG AND PLAY

PCI-EIDE C

, SMBUS,

,

ONTROLLER

RTC

,

Universal Serial Bus Controller

•

−

USB v.1.1 and Intel Universal HCI v.1.1 compatible

−

Eighteen level (doublewords) data FIFO with full scatter / gather capabilities

−

Root hub and two function ports

−

Integrated physical layer transceivers with over-current detection status on USB inputs

−

Legacy keyboard and PS/2 mouse support

Advanced Programmable Interrupt Controller (APIC)

•

−

Integrated on-chip

−

Control pins provided for support of optional external APIC

−

Used to extend system interrupt capability

−

PC98 compliant

Revision 0.3 June 17, 1999 -1- Features

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

UltraDMA-33/66 Master Mode PCI EIDE Controller

•

−

Dual channel master mode PCI supporting four Enhanced IDE devices

−

Transfer rate up to 22MB/sec to cover PIO mode 4, multi-word DMA mode 2 drives, and beyond

−

Extension to UltraDMA-33 interface for transfer rates to 33MB/sec

−

Extension to UltraDMA-66 interface for transfer rates to 66MB/sec

−

Thirty-two levels (doublewords) of prefetch and write buffers

−

Dual DMA engine for concurrent dual channe l operation

−

Bus master programming interface for SFF-8038i rev.1.0 and Windows-95 compliant

−

Full scatter gather capability

−

Support ATAPI compliant devices including DVD devices

−

Support PCI native and ATA compatibility modes

−

Complete software driver support

−

Supports glue-less “Swap-Bay” option with full electrical isolation

System Management Bus Interface

•

−

Host interface for processor communications

−

Slave interface for external SMBus masters

Sophisticated PC98-Compatible Mobile Power Management

•

−

Supports both ACPI (Advanced Configuration and Power Interface) and legacy (APM) power management

−

ACPI v1.0 Compliant

−

APM v1.2 Complia nt

−

CPU clock throttling and clock stop control for complete ACPI C0 to C3 state support

−

PCI bus clock run a nd PCI/CPU clock gene rator stop control

−

Supports multiple system suspend types: power-on suspends with flexible CPU/PCI bus reset options,

suspend to DRAM, and suspend to disk (soft-off), all with hardware automatic wake-up

−

Multiple suspend power plane controls and suspend status indicato rs

−

One idle timer, one peripheral timer and one general purpose timer, plus 24/32-bit ACPI compliant timer

−

Normal, doze, sleep, suspend and conserve modes

−

Global and local device power control

−

System event monitoring with two event classes

−

Primary and secondary interrupt differentiation for individual channels

−

Dedicated input pins for power and sleep buttons, external modem ring indicator, and notebook lid open/close for

system wake-up

−

Up to 22 general purpose input ports and 31 output ports

−

Multiple internal and external SMI sources for flexible power management models

−

Two programmable chip selects and one microcontroller chip select

−

Enhanced integrated real time clock (RTC) with date alarm, month alarm, and century field

−

Thermal alarm support

−

Cache SRAM power-down control

−

Hot docking support

−

I/O pad leakage control

VT82C596B

Plug and Play Controller

•

−

PCI interrupts steerable to any interrupt channel

−

Dual interrupt and DMA signal steering for on-board plug and play devices

−

Microsoft Windows 95

Built-in NAND-tree pin scan test capability

•

0.5u, 3.3V, low power CMOS process

•

Single chip 324 pin BGA

•

Revision 0.3 June 17, 1999 -2- Features

TM

and plug and play BIOS compliant

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

O

VERVIEW

VT82C596B

The VT82C596B south bridge is a high integration, high performance, power-efficient, and high compatibility device that supports

PCI / ISA bus bridge functionality to make a complete Microsoft PC98-compliant system. In addition to complete ISA extension

bus functionality, the VT82C596B includes standard intelligent peripheral controllers:

a) Master mode enhanced IDE controller with dual channel DMA engine and interlaced dual channel commands. Dedicated

FIFO coupled with scatter and gather master mode operation allows high performance transfers between PCI and IDE

devices. In addition to standard PIO and DMA mode operation, the VT82C596B also supports the UltraDMA-33 standard to

allow reliable data transfer rate s up to 33 MB /se c thro ughp ut and the Ultra DMA-66 stand ar d fo r 6 6M B/ sec d ata transfer . T he

IDE controller is SFF-8038i v1.0 and Microsoft Windows-95 / 98 / NT compliant.

b) Universal Serial Bus controller that is USB v1.1 and Universal HCI v1.1 compliant. The VT82C596B includes the root hub

with two function ports with integrated physical layer transceivers. The USB controller allows hot plug and play and

isochronous peripherals to be inserted into the system with universal driver support. The controller also implements legacy

keyboard and mouse support so that legacy software can run transparently in a non-USB-aware operating system

environment.

c) Keyboard controller with PS2 mouse support.

d) Real Time Clock with 256 byte extended CMOS. In addition to the standard ISA RTC functionality, the integrated RTC also

includes the date alarm, century field, and other enhancements for compatibility with the ACPI standard.

e) Notebook-class power management functionality compliant with ACPI and legacy APM requirements. Multiple sleep states

(power-on suspend, suspend-to-DRAM, and suspend-to-Disk) are supported with hardware automatic wake-up. Additional

functionality includes event monitoring, CPU clock throttling and stop (Intel processor p rotoco l), PCI b us clock stop control,

modular power, clock and leakage control, hardware-based and software-based event handling, general purpose I/O, chip

select and external SMI.

f) Full System Management Bus (SMBus) interface.

g) Distributed DMA capability for support of ISA legacy DMA over the PCI bus. PC/PCI and Serial IRQ mechanisms are also

supported for docking and non-docking applications.

h) Plug and Play controller that allows complete steerability of all PCI interrupts to any interrupt channel. Three additional

steerable interrupt channels are provided to allow plug and play and reconfigurability of on-board perip herals for Windows

95 compliance.

i) Integrated APIC (see the Win98 Hardware Design Guide)

The VT82C596B also enhances the functionality of the standard ISA peripherals. The integrated interrupt controller supports both

edge and level triggered interrupts channel by channel. The integrated DMA controller supports type F DMA in addition to

standard ISA DMA modes. Compliant with the PCI-2.1 specification, the VT82C596B supports delayed transactions so that

slower ISA peripherals do not block the traffic of the PCI bus. Special circuitry is built in to allow concurrent operation without

causing dead lock even in a PCI-to-PCI bridge environment. The chip also includes eight levels (doublewords) of line buffers from

the PCI bus to the ISA bus to further enhance overall system performance.

CPU / Cache

Sideband Signals:

Init / CPUreset

IRQ / NMI

SMI / StopClk

FERR / IGNNE

Boot ROM

CA

CD

RTC

Crystal

North Bridge

VT82C596B

324 BGA

MA/Command

MD

PCI

I2C (Module ID)

USB

KBC

IDE

GPIO, Power Control, Reset

ISA

System Memory

Expansion

Cards

Figure 1. PC System Configuration Using the VT82C596B

Revision 0.3 June 17, 1999 -3- Overview

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

P

INOUTS

VT82C596B

Figure 2. VT82C596B Ball Diagram (Top View)

Key1234567891011121314151617181920

PCI

A

RST#AD27IDSELAD19

AD31AD26AD23AD18I

B

AD30AD25AD22AD17T

C

AD28CBE3#AD20CBE

D

AD29AD24AD21AD16DEV

E

USB-

F

G

H

J

K

L

M

N

P

R

T

U

V

W

Y

GPO28GPO29

P1+

PIRQD#USB-

GPI18USB

USB

OC0#

KBCS#

/MSDT

RTC-

ALE

REQA#RTC

GNTA#REQB#NC /

A20G/

MSCK

CPU

STP#

SD6SD

IRQ

9

SD

7

RST

DRV

IO

CHK#

SCI#

GPI21GPO0GPO

P0+

USB

P1-

P0-

USB

GPI14NC /

OC1#

ROM

GPI16GPI

CS#

GPI13USB

CLK

CS#XDIR#XOE#

KBCKMCCS#

GNTB#REQC#GNTC#PIRQ

PCI

PIRQA#PIRQ

STP#

IOCH

RDY

3

SMEMW#SA18DRQ3DRQ1SA11IRQ5SA

SD

2

DRQ

SD

2

SD4SD

SD

ZWS# AEN IOR#

5

0

1

FRA

SERR#

ME#

RDY#

RDY#

STOP#

2#

SEL#AD15

GPO

VCC VCC VCC VCC

30

27

GPI19GPI

20

GND

KEYL

USB

VCC

17

USB

PCS0#GPI

15

NC /

KBDT

PCS

1#

C#

NC VCC VCC VCC

B#

IOW#

SMEMR#SA17DACK

SA

16

SA19DACK3#SA14SA12IRQ6SA

AD13AD9AD5AD1PCI

AD12AD8AD4AD0PCI

PAR

CBE1#AD11CBE0#AD3PCK

AD14AD10AD6AD

GND

VCC

VCC

B

CLKSA9

RFSH#

1#

SA15SA13IRQ7SA8DACK2#SA3MCS

2

AD

VCC

7

GND GND GND GND VREF

GND GND GND GND

GND GND GND GND

GND GND GND GND

IRQ3SA4SA1LA23IRQ12LA18DACK

6

7

SA10IRQ4SA5SA2S

RQB#PGNT#SDD6SDD4SDD13SDDRQ

RQC#PREQ#SDD9SDD11SDD1SDIOW#SDA1SDCS1#PDD9PDD6

RUN#

RQA#

BALE

PCI

RQD#SDD7SDD5SDD3SDD14SDIOR#SDA0SDCS3#PDD10PDD5

GND

P

CLKSDD8SDD10SDD2SDD15SDRDYPDD12PDD3PDD11PDD4

PCI

VCC VCC GND

SA0IRQ10LA20DACK0#MEMW#DRQ6DRQ7SUSC#BAT

TC OSC

IOCS

16#LA21

BHE#

16#LA22

SD

D12SDD0

VCC

5#

IRQ14MEMR#DACK

IRQ11LA19DRQ

0

IRQ15LA17DRQ

DACK#

VCC

PD

IOW#PDIOR#PDDRQPDD15PDD0

PDA0PDA2PDA1PD

PD

CS3#PDCS1#

AAK#/

ZZ SPKR

V

BAT

NC

VCC

ALRT#

SUS

LID

VCC

SUS

SD9

6#

DACK

SD

8

5

SDA2PDD8PD

SD

PD

D14PDD1PDD13PDD2

DACK#

RDY

ACS#/

APD0THRM#

STP

APD1

CLK#

ARQ#/

WSC#

IGN

INIT INTR NMI

NE#

RSM

PWRGDCPU

RST#

SMB

NC

SUS

RI#

CLK

CFG1CFG2SMB

SUS

SUS

ST1#

ST2#

SD

TEST#

11

SD13SD

7#

SD10SD12SD

IRQ0

OUT

SER

IRQ

FERR# SLP#

RST

RTCX1RC

GPI

SMI#

1

RTC

CLK

GPO8SMB

DATA

PWR

LOW#

BTN#

SUSB#EXT

SMI#

SUS

15

14

D7

PD

IRQ

1

A20

M#

IN#

X2

A#

IRQ

8#

Note: Some of the pins above have alternate functions and alternate names. The table above contains only one name, but the pin lists and pin descriptions contain

all names.

Revision 0.3 June 17, 1999 -4- Pinouts

7HFKQRORJLHV ,QF

&

Q

Q

:H&RQQHFW

RQQHFW

:H

VT82C596B

Figure 3. VT82C596B Pin List (Numerical Order)

Pin Pin

A01 O PCIRST# D06 IO AD14 H17 O PDCS1#

A02 IO AD27 D07 IO AD10 H18 O APICCS#/D0/GPO13 N17 I SMBALRT# / GPI11 U18 O SUSC# / GPO16

A03 I IDSEL D08 IO AD6 H19 I THRM# / GPI8 N18 - NC U19 I BATLOW# / GPI9

A04 IO AD19 D09 IO AD2 H20 O IRQ0OUT / GPO14 N19 I RTCX1 U20 I PWRBTN#

A05 IO FRAME#

A06 I SERR# D11 I PCLK J02 I USBOC1# P01 IO A20GATE / MSCK V02 I DRQ2

A07 IO AD13 D12 IO SDD8 J03 I GPI14 P02 O GNTB# / GPO10 V03 IO SD0

A08 IO AD9 D13 IO SDD10 J04 I NC / KEYLOCK P03 I REQC# / GPI4 V04 IO SA19

A09 IO AD5 D1 4 IO SDD2

A10 IO AD1 D1 5 IO SDD15

A11 I PCIREQB# D16 I SDRDY

A12 I PGNT# D17 IO PDD12

A13 IO SDD6 D18 IO PDD3

A14 IO SDD4 D19 IO PDD11

A15 IO SDD13 D20 IO PDD4 J17 O APICACK#/D1/GPO12 P19 I GPI1 / PME# V11 I OSC

A16 I SDDR

A17 O SDDACK# E02 IO AD24 J19 I SERIRQ / GPI7 R01 O CPUSTP# / GPO17 V13 IO LA21

A18 O SDA2 E03 IO AD21 J20 I IRQ1 R02 O PCISTP# / GPO18 V14 I IRQ14

A19 IO PDD8 E04 IO AD16 K01 IO KBCS#/GPO26/MSDT R03 IOD PIRQA# V15 IO MEMR#

A20 IO PDD7 E05 IO DEVSEL# K02 O ROMCS# R04 IOD PIRQB# V16 O DACK6#

B01 IO AD31 E06 IO AD15 K03 I GPI16 R05 - NC V17 IO SD11

B02 IO AD26

B03 IO AD23 E08 IO AD7

B04 IO AD18

B05 IO IRDY# E10 I PCIREQA#

B06 O PAR

B07 IO AD12

B08 IO AD8

B09 IO AD4 E14 IO SDD12 K17 O SPKR R20 O RTCX2 W05 IO SA17

B10 IO AD0 E15 IO SDD0 K18 I APICRQ#/WSC#/GPI5 T01 IO SD6 W06 O DACK1#

B11 I PCIREQC#

B12 O PREQ# E17 IO PDD14 K20 OD SLP# T03 IOD IOCHRDY W08 IO SA10

B13 IO SDD9 E18 IO PDD1 L01 O RTCAS / GPO25 T04 IO IOW# W09 I IRQ4

B14 IO SDD11 E19 IO PDD13 L02 I GPI13 / SLPBTN# T05 IO SA16 W10 IO SA5

B15 IO SDD1 E20 IO PDD2 L03 I USBCLK

B16 O SDIOW# F01 IO USBP1+ L04 O PCS0# T07 O BCLK W12 IO SBHE#

B17 O SDA1 F02 O GPO28 L05 I GPI15 T08 IO SA9 W13 I IRQ11

B18 O SDCS1# F03 O GPO29/SCI#

B19 IO PDD9 F04 O GPO30

B20 IO PDD6

C01 IO AD30

C02 IO AD25

C03 IO AD22

C04 IO AD17 F16 O PDIOW# L18 OD INIT T15 O DACK5# W20 O SUSA#

C05 IO TRDY# F17 O PDIOR# L19 OD INTR T16 IO SD9 Y01 I IOCHCK# / GPI0

C06 IO CBE1# F18 I PDDR

C07 IO AD11 F19 IO PDD15 M01 I REQA# / GPI2 T18 O SUSST2# / GPO21 Y 03 I ZWS#

C08 IO CBE0# F20 IO PDD0 M02 O RTCCS# / GPO24 T19 O GPO8 Y04 O AEN

C09 IO AD3 G01 IOD PIRQD# M03 O XDIR# / GPO22 T20 IO SMBDATA Y05 IO IOR#

C10 IO PCKRUN# G02 IO USBP0+ M04 O XOE# / GPO23 U01 I IRQ9 Y06 IO SA15

C11 I PCIREQD# G03 I GPI21 M05 IO NC / KBDT U02 IO SD2 Y07 IO SA13

C12 IO SDD7 G04 O GPO0

C13 IO SDD5 G05 O GPO27

C14 IO SDD3

C15 IO SDD14 G16 O PDA0

C16 O SDIOR# G17 O PDA2 M16 - NC U07 IO SA11 Y12 IO MCS16#

C17 O SDA0 G18 O PDA1 M17 I RSMRST# U08 I IRQ5 Y13 IO LA22 / GPO6

C18 O SDCS3# G19 O PDDACK# M18 I PWRGD U09 IO SA6 Y14 I IRQ15

C19 IO PDD10 G20 I PDRDY M19 OD CPURST U10 O BALE Y15 IO LA17 / GPO1

C20 IO PDD5 H01 I GPI18 M20 OD A20M# U11 IO SA0 Y16 I DRQ5

D01 IO AD28 H02 IO USBP1 - N01 O GNTA# / GPO9 U12 I IRQ10 Y17 IO SD10

D02 IO CBE3 # H03 IO USBP0- N02 I REQB# / GPI3 U13 IO LA20 / GPO4 Y18 IO SD12

D03 IO AD20 H04 I GPI19 N03 IO NC / KBCK U14 O DACK0# Y19 IO SD14

D04 IO CBE2# H05 I GPI20 N04 O M CCS# U15 IO MEMW# Y20 I IRQ8# / GPI6

D05 IO STOP# H16 O PDCS3# N05 O PCS1# U16 I DRQ6

m

Pin Pin

D10 P GND

E01 IO AD29 J18 OD STPCLK# P20 OD SMI# V12 IO IOCS16#

E07 P GND

E09 P VCC K09 P GND R15 P VCC

E11 P VCC K11 P GND

E12 P VCC K12 P GND

E13 P GND

E16 P VCC

F05 P VCC L11 P GND

F06 P VCC L12 P GND

F14 P VCC L16 P VBAT

F15 P VCC

G06 P VCC M11 P GND

m

Pin Pin

J01 I USBOC0# N20 I RCIN# V01 IO SD7

J05 P GNDUSB

J09 P GND

J10 P GND P15 P VCC

J11 P GND

J12 P GND

J16 P VREF

K04 I GPI17

K05 P VCCUSB R07 P VCC

K10 P GND R16 P VCCSUS

K16 O ZZ / GPO19 R19 IO SMBCLK W04 O SMEMR#

K19 I FERR# T02 IO SD3 W07 IO RFSH#

L09 P GND

L10 P GND

L17 OD IGNNE# T14 IO LA18 / GPO2 W19 IO SD15

L20 OD NMI T17 O SUSST1# / GPO20 Y02 IO SD5

M09 P GND

M10 P GND

M12 P GND

m

Pin Pin

N16 P VCCSUS

P04 O GNTC# / GPO11 V0 5 O DACK3#

P05 IOD PIRQC# V06 IO SA14

P16 I LID / GPI10 V08 I IRQ6

P17 O SUSCLK V09 IO SA7

P18 I RI# / GPI12 V10 O TC

R06 P VCC

R17 I CFG1 W02 IO SD4

R18 I CFG2 W03 IO SD1

T06 P VCC

T09 I IRQ3 W14 IO LA19 / GPO3

T10 IO SA4 W15 I DRQ0

T11 IOSA1 W16 IOSD8

T12 IO LA23 / GPO7 W17 O DACK7#

T13 I IRQ12 W18 IO SD13

U03 O SMEMW# Y08 I IRQ7

U04 IO SA18 Y09 IO SA8

U05 I DRQ3 Y10 O DACK2#

U06 I DRQ1Y11IOSA3

m

W01 O RSTDRV

W11 IO SA2

Pin Pin

U17 I DRQ7

V07 IO SA12

V18 I TEST#

V19 O SUSB# / GPO15

V20 IOD EXTSMI#

m

Revision 0.3 June 17, 1999 -5- Pinouts

7HFKQRORJLHV ,QF

&

Q

Q

Q

Q

Q

Q

Q

Q

Q

:H&RQQHFW

RQQHFW

:H

VT82C596B

Figure 4. VT82C596B Pin List (Alphabetical Order)

Pin Pin

P01 IO A20GATE / MSCK K19 I FERR# K01 IO

M20 OD A20M# A05 IO FRAME# Y15 IO LA17 / GPO1 N20 I RCIN# D13 IO SDD10

B10 IO AD00

A10 IO AD01

D09 IO AD02

C09 IO AD03

B09 IO AD04

A09 IO AD05

D08 IO AD06

E08 IO AD07

B08 IO AD08

A08 IO AD09

D07 IO AD10

C07 IO AD11

B07 IO AD12

A07 IO AD13

D06 IO AD14

E06 IO AD15

E04 IO AD16

C04 IO AD17

B04 IO AD18

A04 IO AD19

D03 IO AD20 N01 O GNTA# / GPO9 C10 IO PCKRUN# Y09 IO SA08 D05 IO STOP#

E03 IO AD21 P02 O GNTB# / GPO10 D11 I PCLK T08 IO SA09 J18 OD STPCLK#

C03 IO AD22 P04 O GNTC# / GPO11 E10 I PCIREQA# W08 IO SA10 W20 O SUSA#

B03 IO AD23 P19 I GPI1 / PME# A11 I PCIREQB# U07 IO SA11 V19 O SUSB# / GPO15

E02 IO AD24 L02 I GPI13 / SLPBTN# B11 I PCIREQC# V07 IO SA12 U18 O SUSC# / GPO16

C02 IO AD25 J03 I GPI14 C11 I PCIREQD# Y07 IO SA13 P17 O SUSCLK

B02 IO AD26 L05 I GPI15 A01 O PCIRST# V06 IO SA14 T17 O SUSST1# / GPO20

A02 IO AD27 K03 I GPI16 R02 O PCISTP#/GPO18 Y06 IO SA15 T18 O SUSST2# / GPO21

D01 IO AD28 K04 I GPI17 L04 O PCS0# T05 IO SA16 V10 O TC

E01 IO AD29 H01 I GPI18 N05 O PCS1# W05 IO SA17 V18 I TEST#

C01 IO AD30 H04 I GPI19 G16 O PDA0 U04 IO SA18 H19 I THRM# / GPI8

B01 IO AD31 H05 I GPI20 G18 O PDA1 V04 IO SA19 C05 IO TRDY#

Y04 O AEN G03 I GPI21 G17 O PDA2 W12 IO SBHE# L03 I USBCLK

J17 O APICAK#//D1/O12 G04 O GPO00 H17 O PDCS1# V03 IO SD00 J01 I USBOC0#

H18 O APICCS#/D0/O13 T19 O GPO08 H16 O PDCS3# W03 IO SD01 J02 I USBOC1#

K18 I APICRQ#/WSC#/I5 G05 O GPO27 F20 IO PDD00 U02 IO SD02 H03 IO USBP0U10 O BALE F02 O GPO28 E18 IO PDD01 T02 IO SD03 G02 IO USBP0+

U19 I BATLOW# / GPI9 F03 O GPO29 / SCIOUT# E20 IO PDD02 W02 IO SD04 H02 IO USBP1T07 O BCLK F04 O GPO30 D18 IO PDD03 Y02 IO SD05 F01 IO USBP1+

C08 IO CBE0# A03 I IDSEL D20 IO PDD04 T01 IO SD06

C06 IO CBE1# L17 OD IGNNE# C20 IO PDD05 V01 IO SD07

D04 IO CBE2# L18 OD INIT B20 IO PDD06 W16 IO SD08

D02 IO CBE3# L19 OD INTR A20 IO PDD07 T16 IO SD09

R17 I CFG1 Y01 I IOCHCK# / GPI0 A19 IO PDD08 Y17 IO SD10

R18 I CFG2 T03 IOD IOCHRDY B19 IO PDD09 V17 IO SD11

M19 OD CPURST V12 IO IOCS16# C19 IO PDD10 Y18 IO SD12

R01 O CPUSTP# / GPO17 Y05 IO IOR# D19 IO PDD11 W18 IO SD13

U14 O DACK0# T04 IO IOW# D17 IO PDD12 Y19 IO SD14

W06 O DACK1# B05 IO IRDY# E1 9 IO PDD13 W19 IO SD15

Y10 O DACK2# H20

V05 O DACK3# J20 I IRQ1 F19 IO PDD15 B17 O SDA1

T15 O DACK5# T09 I IRQ3 G19 O PDDACK# A18 O S DA2

V16 O DACK6# W09 I IRQ4 F18 I PDDR

W17 O DACK7# U08 I IRQ5 F17 O PDIOR# C18 O SDCS3#

E05 IO DEVSEL# V08 I IRQ6 F16 O PDIOW# E15 IO SDD00

W15 I DRQ0Y08IIR

U06 I DRQ1Y20IIR

V02 I DRQ2U01IIR

U05 I DRQ3U12IIR

Y16 I DRQ5W13IIR

U16 I DRQ6T13IIR

U17 I DRQ7V14IIR

V20 IOD EXTSMI# Y14 I IRQ15 U20 I PWRBTN# D12 IO SDD08

Referenced to VCCSUS: BATLOW#, CFG1-2, EXTSMI#, GPI1, GPO8, IRQ8#, LID, PWRBTN#, PWRGD, RI#, RSMRST#, SUSA-C#, SUSST1-2#, TEST#

m

Pin Pin

D10 P GND

E07 P GND

E13 P GND

J09 P GND

J10 P GND

J11 P GND

J12 P GND

K09 P GND

K10 P GND

K11 P GND

K12 P GND

L09 P GND

L10 P GND

L11 P GND

L12 P GND

M09 P GND

M10 P GND

M11 P GND

M12 P GND

J05 P GNDUSB

IRQ0OUT / GPO14 E17 IO PDD14 C17 O SDA0

O

7 A12 I PGNT# B15 IO SDD01

8# / GPI6 B12 O PREQ# D14 IO SDD02

9 G20 I PDRDY C14 IO SDD03

10 R03 IOD PIRQA# A14 IO SDD04 M03 O XDIR# / GPO22

11 R04 IOD PIRQB# C13 IO SDD05 M04 O XOE# / GPO23

12 P05 IOD PIRQC# A13 IO SDD06 Y03 I ZWS#

14 G01 IOD PIRQD# C12 IO SDD07 K16 O ZZ / GPO19

m

Pin Pin

T14 IO LA18 / GPO2 M01 I REQA# / GPI2 B14 IO SDD11

W14 IO LA19 / GPO3 N02 I REQB# / GPI3 E14 IO SDD12

U13 IO LA20 / GPO4 P03 I REQC# / GPI4 A15 IO SDD13

V13 IO LA21 / GPO5 W07 IO RFSH# C15 IO SDD14

Y13 IO LA22 / GPO6 P18 I RI# / GPI12 D15 IO SDD15

T12 IO LA23 / GPO7 K02 O ROMCS# A17 O SDDACK#

P16 I LID / GPI10 M17 I RSMRST# A16 I SDDR

N04 O MC CS# W01 O RSTDRV C16 O SDIOR#

Y12 IO MCS16# L01 O RTCAS/GPO25 B16 O SDIOW#

V15 IO MEMR# M02 O RTCCS#/GPO24 J19 I SERIRQ / GPI7

U15 IO MEMW# N19 I RTCX1 A06 I SERR#

J04 I NC / KEYLOCK R20 O RTCX2 D16 I SDRDY

M05 IO NC / KBDT U11 IO SA00 K20 OD SLP#

N03 IO NC / KBCK T11 IO SA01 N17 I SMBALRT#/GPI11

M16 - NC W11 IO SA02 R19 IO SMBCLK

N18 - NC Y11 IO SA03 T20 IO SMBDATA

R05 - NC T10 IO SA04 W04 O SMEMR#

L20 OD NMI W10 IO SA05 U03 O SMEMW#

V11 I OSC U09 IO SA06 P20 OD SMI#

B06 O PAR V09 IO SA07 K17 O SPKR

m

KBCS#/GPO26/MSDT

Pin Pin

M18 I PWRGD B13 IO SDD09

B18 O SDCS1#

m

Pin Pin

L16 P VBAT

E09 P VCC

E11 P VCC

E12 P VCC

E16 P VCC

F05 P VCC

F06 P VCC

F14 P VCC

F15 P VCC

G06 P VCC

P15 P VCC

R06 P VCC

R07 P VCC

R15 P VCC

T06 P VCC

N16 P VCCSUS

R16 P VCCSUS

K05 P VCCUSB

J16 P VREF

m

Revision 0.3 June 17, 1999 -6- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

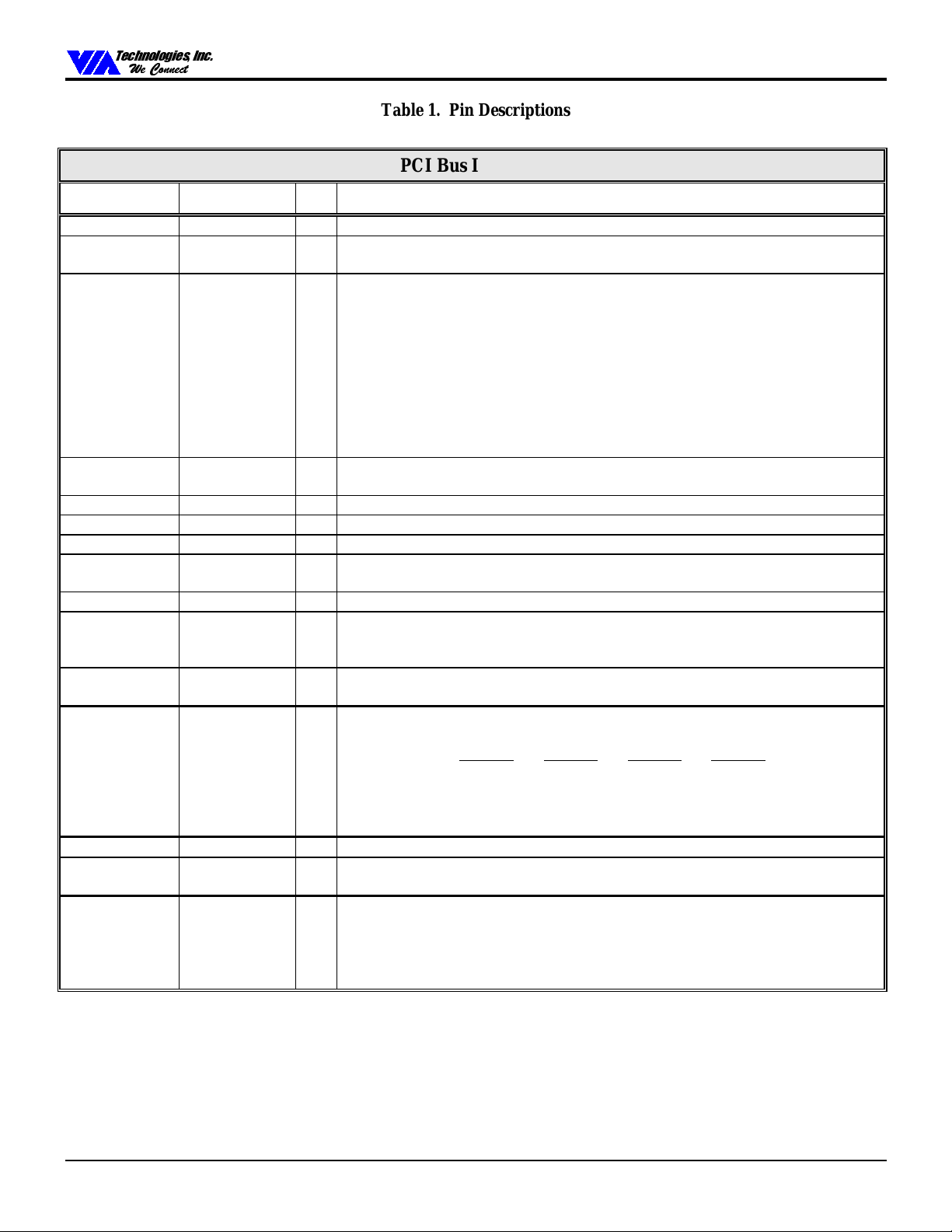

Table 1. Pin Descriptions

PCI Bus Interface

Signal Name Pin # I/O Signal Description

VT82C596B

PCLK

FRAME#

AD[31:0]

C/BE[3:0]#

IRDY#

TRDY#

STOP#

DEVSEL#

PAR

SERR#

IDSEL

PIRQA-D#

PREQ#

PGNT#

PCKRUN#

D11 I

A5 IO

B1, C1, E1,

D1, A2, B2,

C2, E2, B3, C3,

E3, D3, A4,

B4, C4, E4, E6,

D6, A7, B7,

C7, D7, A8,

B8, E8, D8,

A9, B9, C9,

D9, A10, B10

D2, D4, C6, C8 IO

B5 IO

C5 IO

D5 IO

E5 IO

B6 IO

A6 I

A3 I

R3, R4, P5, G1 I

B12 O

A12 I

C10 IO

IO

PCI Clock.

Frame.

that one more data transfer is desired by the cycle initiator.

Address/Data Bus.

with FRAME# assertion and data is driven or received in following cycles.

Comma nd/By te Ena ble.

enables corresponding to supplied or requested data are driven on following clocks.

Initiator Ready.

Target Ready.

Stop.

Device Select.

positive or subtractive decoding.

Parity.

System Error.

error condition. Upon sampling SERR# active, the VT82C596B can be programmed

to generate an NMI to the CPU.

Initialization Device Select.

configuration read and write cycles.

PCI Interrupt Request

INTD# pins as follows:

PCI Slot 1 INTA# INTB# INTC# INTD#

PCI Slot 2 INTB# INTC# INTD# INTA#

PCI Slot 3 INT C# INTD# INTA# INTB#

PCI Slot 4 INTD# INTA# INTB# INTC#

PCI Request.

PCI Grant.

VT82C596B.

PCI Bus Clock Run.

stopped (high) or running (low). The VT82C596B drives this signal low when the

PCI clock is running (de fault on reset) and releases it when it stops the PCI clock.

External devices may assert this signal low to request that the PCI clock be restarted

or prevent it from stopping. Refer to the PCI Mobile Design Guide for more details.

PCLK provides timing for all transactions on the PCI Bus.

Assertion indicates the address phase of a PCI transfer. Negation indicates

The standard PCI address and data lines. The address is driven

The command is driven with FRAME# assertion. Byte

Asserted when the initiator is ready for data transfer.

Asserted when the target is ready for data transfer.

Asserted by the target to request the master to stop the current transaction.

The VT82C596B asserts this signal to claim PCI transactions through

A single parity bit is provided over AD[31:0] and C/BE[3:0]#.

SERR# can be pulsed active by any PCI device that detects a system

IDSEL is used as a chip select during PCI

. These pins are typically connected to the PCI bus INTA#-

PIRQA# PIRQB#

This signal goes to the North Bridge to req uest the PCI bus.

This signal is driven by the North Bridge to grant PCI access to the

This signal indicates whether the PCI clock is or will be

PIRQC# PIRQD#

Revision 0.3 June 17, 1999 -7- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

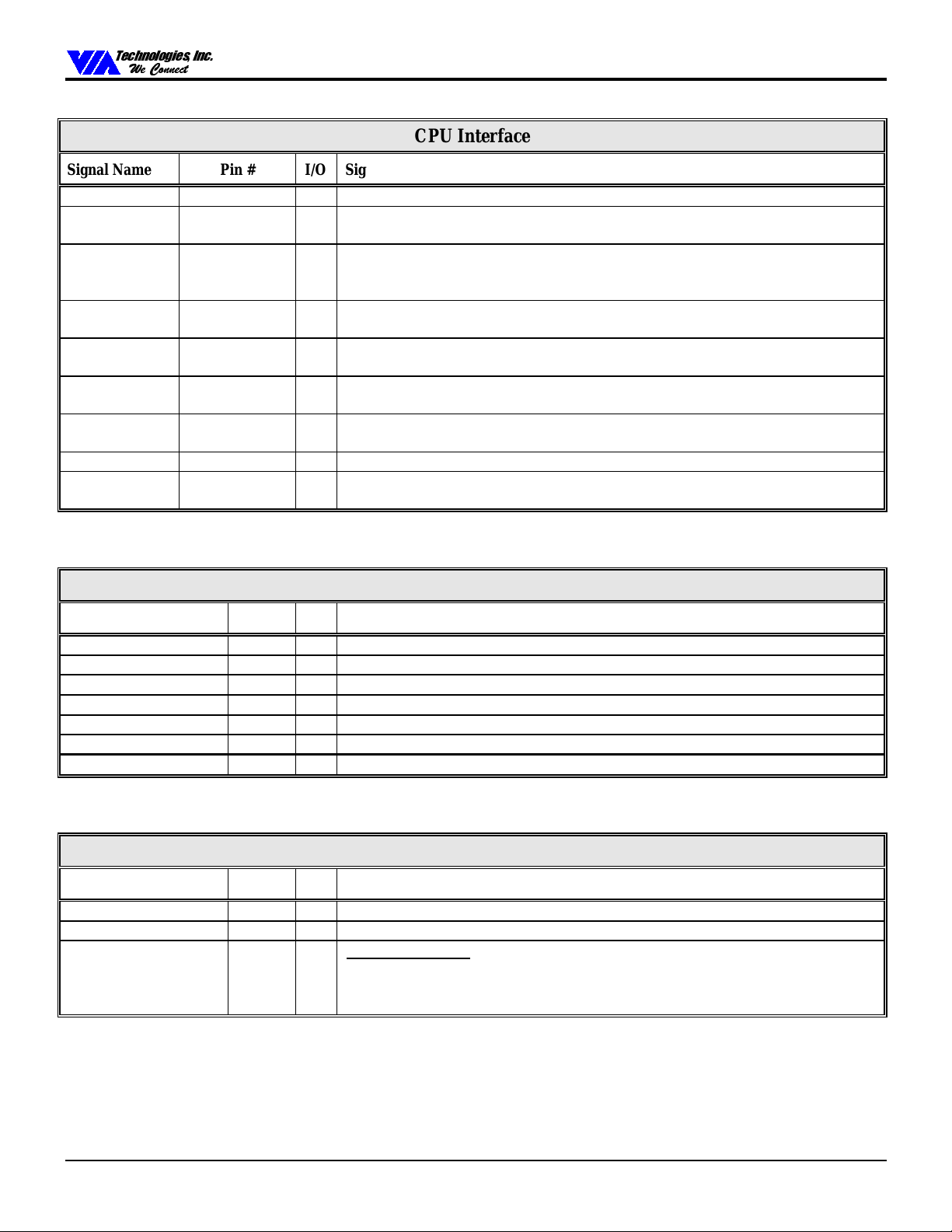

CPU Interface

Signal Name Pin # I/O Signal Description

VT82C596B

CPURST

INTR

NMI

INIT

STPCLK#

SMI#

FERR#

IGNNE#

SLP#

M19 OD

L19 OD

L20 OD

L18 OD

J18 OD

P20 OD

K19 I

L17 OD

K20 OD

CPU Reset.

CPU Interrupt.

interrupt request is pending and needs service.

Non-Maskable Interrupt.

CPU. The VT82C596B generates an NMI when either SERR# or IOCHK# is

asserted.

Initialization.

on the PCI bus or if a soft reset is initiated by the register

Stop Clock.

different Power-Management events.

System Management Interrupt.

in response to different Power-Management events.

Numerical Coprocessor Error.

the CPU. Internally generates interrupt 13 if active.

Ignore Numeric Error.

Sleep.

used with socket-7 CPUs.

The VT82C596B asserts CPURST to reset the CPU during power-up.

INTR is driven by the VT82C596B to signal the CPU that an

The VT82C596B asserts INIT if it detects a shut-down special cycle

STPCLK# is asserted by the VT82C596B to the CPU in response to

Used to put the CPU to sleep. Used with slot-1 CPUs only. Not currently

Universal Serial Bus Interface

Signal Name Pin # I/O Signal Description

USBP0+

USBP0USBOC0#

USBP1+

USBP1USBOC1#

USBCLK

G2 IO

H3 IO

J1 I

F1 I O

H2 IO

J2 I

L3 I

USB Port 0 Data +

USB Port 0 Data USB Port 0 Over Current Detect.

USB Port 1 Data +

USB Port 1 Data USB Port 1 Over Current Detect.

USB Clock.

48MHz clock input for Universal Serial Bus interface

NMI is used to force a non-maskable interrupt to the

SMI# is asserted by the VT82C596B to the CPU

This signal is tied to the coprocessor error signal on

This pin is connected to the “ignore error” pin on the CPU.

Port 0 is disabled if this input is low.

Port 1 is disabled if this input is low.

System Management Bus (SMB) Interface (I2C Bus)

Signal Name Pin # I/O Signal Description

SMBCLK

SMBDATA

SMBALRT#

Revision 0.3 June 17, 1999 -8- Pinouts

/ GPI11

R19 IO

T20 IO

N17 I

SMB / I2C Clock.

SMB / I2C Data.

MultiFunction Pin

SMB Alert.

an IRQ or SMI interrupt or a power management resume event.

General Purpose Input 11.

(Rx74[5] = 0) When the chip is enabled to allo w it, assertion generates

(Rx74[5] = 1) General purpose input.

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

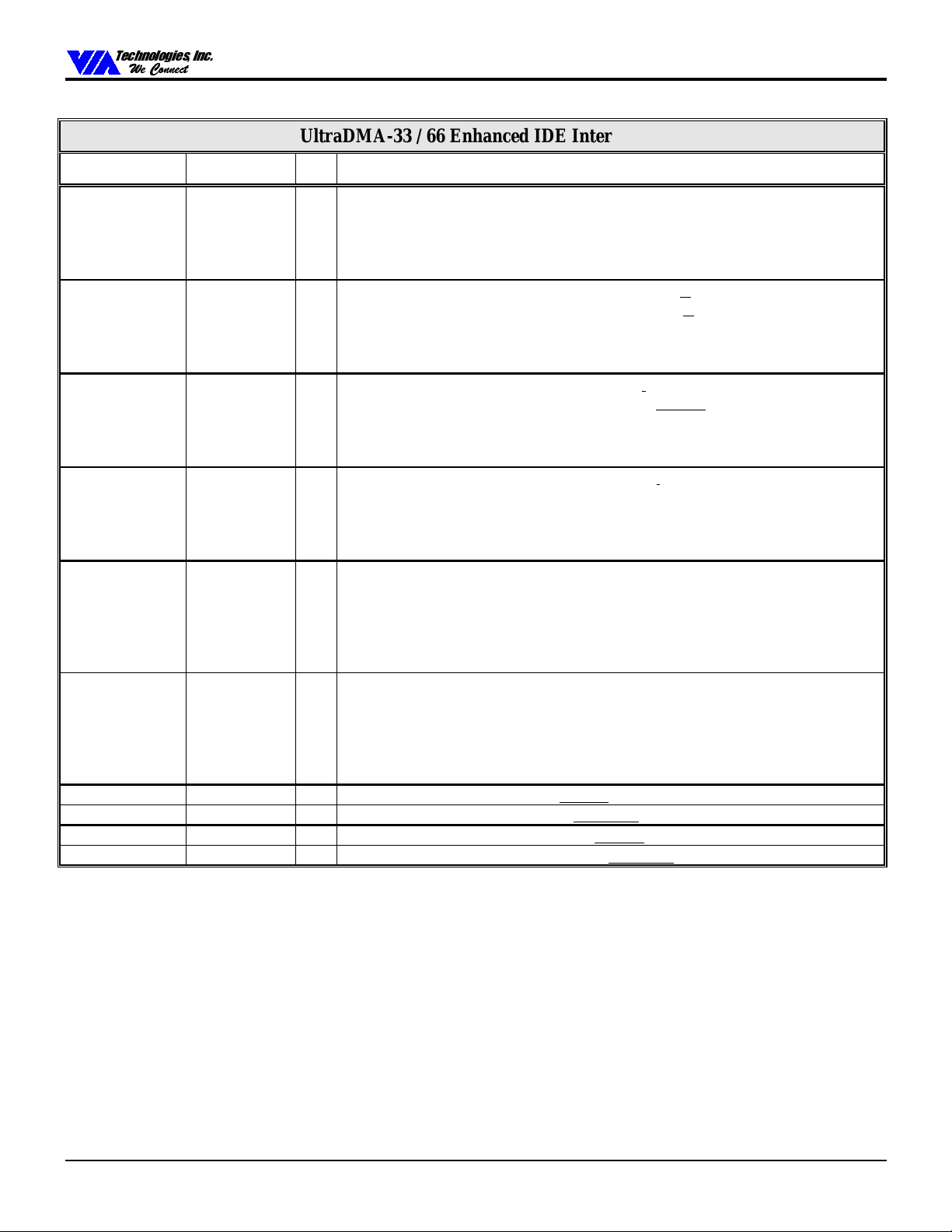

UltraDMA-33 / 66 Enhanced IDE Interface

Signal Name Pin # I/O Signal Description

VT82C596B

PDRDY /

PDDMARDY# /

PDSTROBE

SDRDY /

SDDMARDY# /

SDSTROBE

PDIOR# /

PHDMARDY# /

PHSTROBE

SDIOR# /

SHDMARDY# /

SHSTROBE

PDIOW# /

PSTOP

SDIOW# /

SSTOP

PDDRQ

SDDRQ

PDDACK#

SDDACK#

G20 I

D16 I

F17 O

C16 O

F16 O

B16 O

F18 I

A16 I

G19 O

A17 O

EIDE Mode:

UltraDMA Mode:

EIDE Mode:

UltraDMA Mode:

EIDE Mode:

UltraDMA Mode:

EIDE Mode:

UltraDMA Mode:

EIDE Mode:

UltraDMA Mode:

EIDE Mode:

UltraDMA Mode:

Primary Device DMA Request.

Secondary Device DMA Request.

Primary Device DMA Acknowledge.

Secondary Device DMA Acknowledge.

Primary I/O Channel Ready.

Primary Device DMA Ready

may assert PDDMARDY# to pause output transfers

Primary Device Strobe

device may stop PDSTROBE to pause input data transfers

Secondary I/O Channel Ready.

Secondary Device DMA Ready

device may assert SDDMARDY# to pause output transfers

Secondary Device Strobe

device may stop SDSTROBE to pause input data transfers

Primary Device I/O Read.

Primary Host DMA Ready

The host may assert PHDMARDY# to pause input transfers

Primary Host Strobe

host may stop PHSTROBE to pause output data transfers

Secondary Device I/O Read.

Secondary Host DMA Ready

may assert SHDMARDY# to pause input transfers

Host Strobe B

SHSTROBE to pause output data transfers

Primary Device I/O Write.

Primary Stop

initiation of an UltraDMA burst; negated by the host before data

is transferred in an UltraDMA burst. Assertion of STOP by the

host during or after data transfer in UltraDMA mode signals the

termination of the burst.

Secondary Device I/O Write.

Secondary Stop

initiation of an UltraDMA burst; negated by the host before data

is transferred in an UltraDMA burst. Assertion of STOP by the

host during or after data transfer in UltraDMA mode signals the

termination of the burst.

. Output strobe (both edges). The host may stop

. Stop transfer: Asserted by the host prior to

. Stop transfer: Asserted by the host prior to

Primary channel DMA request

Secondary channel DMA request

Primary channel DMA acknowledge

Device ready indicator

. Output flow control. The device

. Input data strobe (both edges). The

Device ready indicator

. Output flow control. The

. Input data strobe (both edges). The

Device read strobe

. Primary channel input flow control

. Output data strobe (both edges). The

Device read strobe

. Input flow control. The host

Device write strobe

Device write strobe

Secondary channel DMA acknowledge

.

Revision 0.3 June 17, 1999 -9- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

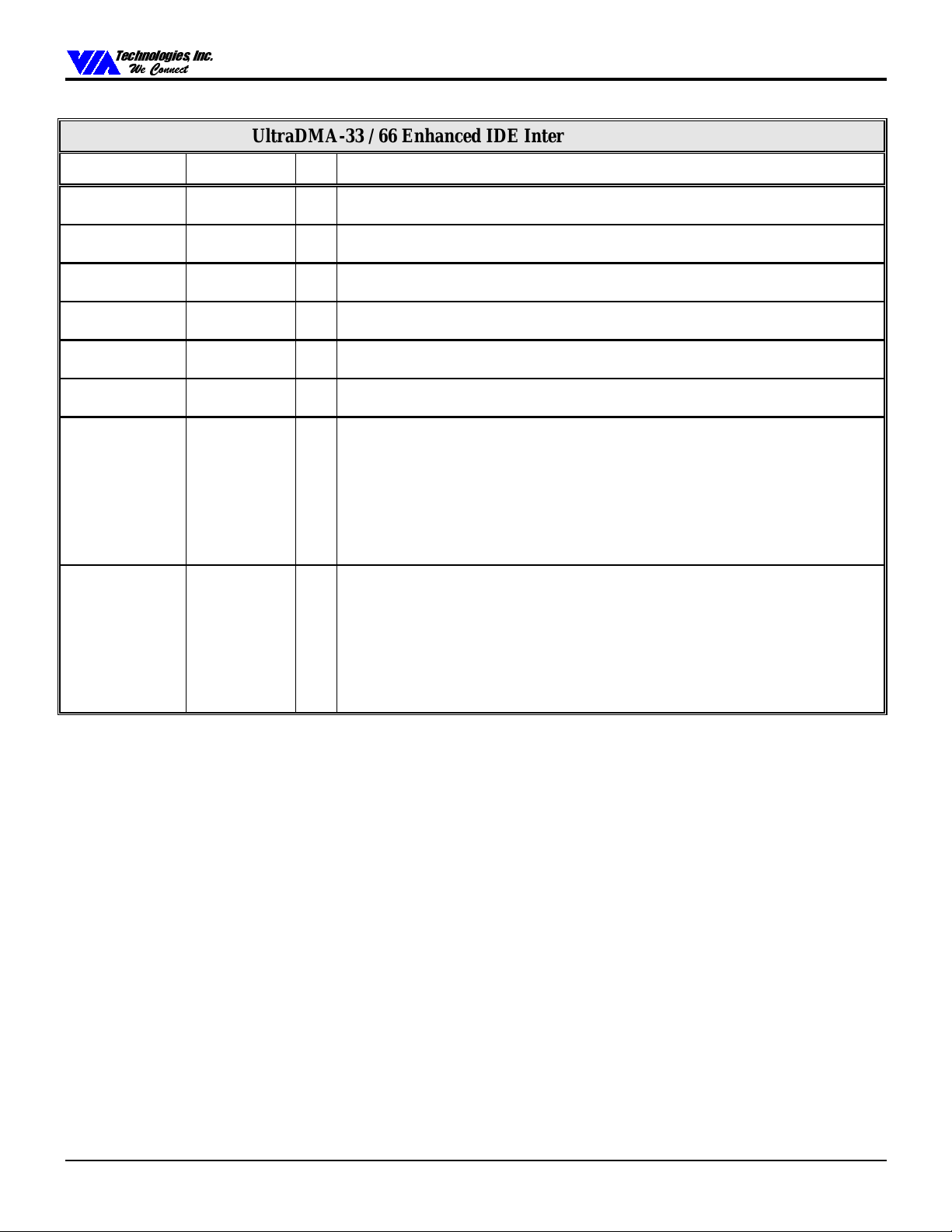

UltraDMA-33 / 66 Enhanced IDE Interface (continued)

Signal Name Pin # I/O Signal Description

VT82C596B

PDCS1#

PDCS3#

SDCS1#

SDCS3#

PDA[2-0]

SDA[2-0]

PDD[15-0]

SDD[15-0]

H17 O

H16 O

B18 O

C18 O

G17, G18,

G16

A18, B17,

C17

F19, E17,

E19, D17,

D19, C19,

B19, A19,

A20, B20,

C20, D20,

D18, E20,

E18, F20

D15, C15,

A15, E14,

B14, D13,

B13, D12,

C12, A13,

C13, A14,

C14, D14,

B15, E15

Primary Master Chip Select.

IDE connector.

Primary Slave Chip Select.

IDE connector.

Secondary Master Chip Select.

secondary IDE connector.

Secondary Slave Chip Select.

IDE connector.

O

Primary Disk Address.

command block or control block is being accessed.

O

Secondary Disk Address.

ATA command block or control block is being accessed.

IO

Primary Disk Data

IO

Secondary Disk Data

This signal corresponds to CS1FX# on the primary

This signal corresponds to CS3FX# on the primary

This signal corresponds to CS17X# on the

This signal corresponds to CS37X# on the secondary

PDA[2:0] are used to indicate which byte in either the ATA

SDA[2:0] are used to indicate which byte in either the

Revision 0.3 June 17, 1999 -10- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

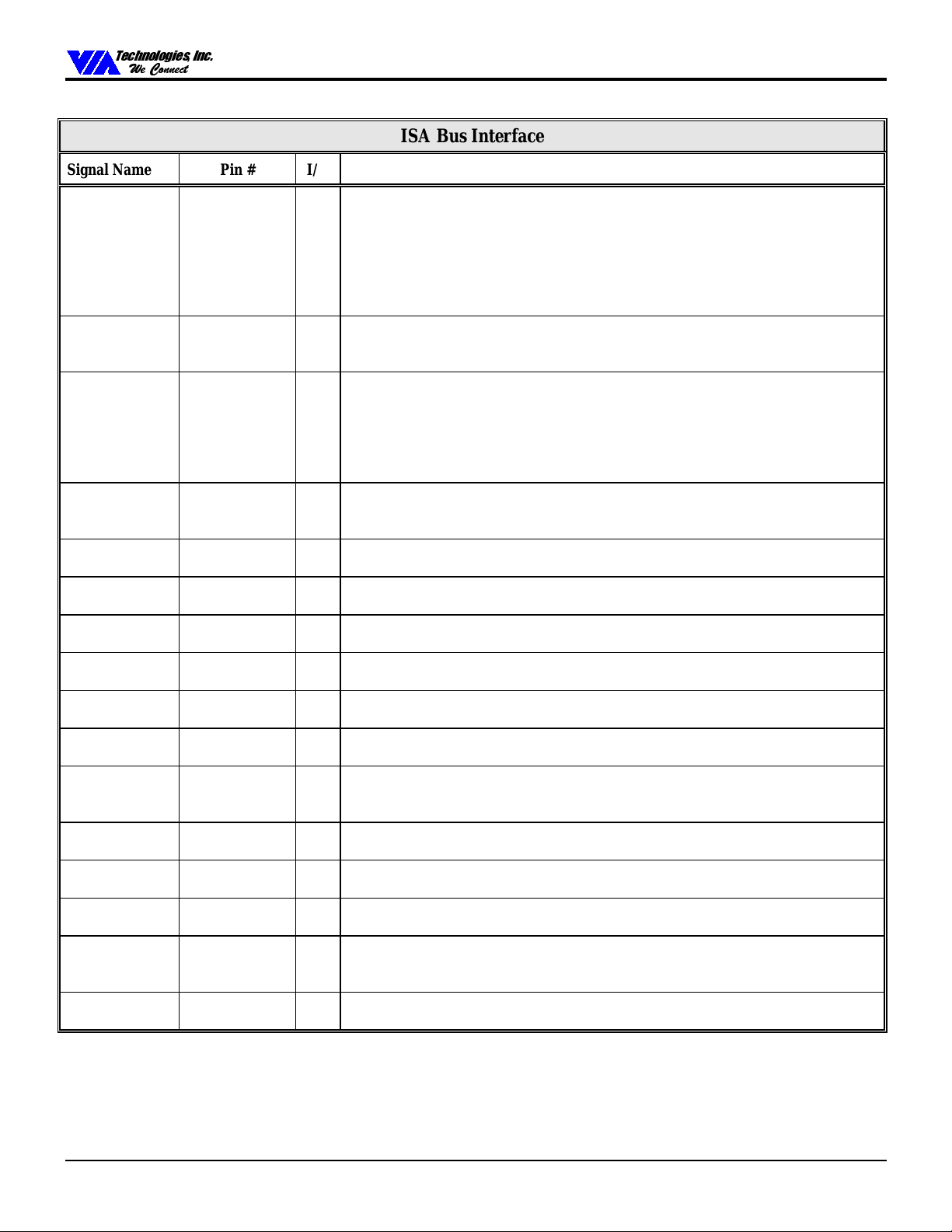

ISA Bus Interface

Signal Name Pin # I/O Signal Description

VT82C596B

SA[19:0]

LA[23:17]

SD[15:0]

SBHE#

IOR#

IOW#

MEMR#

MEMW#

SMEMR#

SMEMW#

BALE

IOCS16#

MCS16#

IOCHCK#

IOCHRDY

ZWS#

V4, U4, W5,

T5, Y6, V6,

Y7, V7, U7,

W8, T8, Y9,

V9, U9, W10,

T10, Y11,

W11, T11, U11

T12, Y13, V13,

U13, W14,

T14, Y15

W19, Y19,

W18, Y18,

V17, Y17, T16,

W16, V1, T1,

Y2, W2, T2,

U2, W3, V3

W12 IO

Y5 IO

T4 IO

V15 IO

U15 IO

W4 O

U3 O

U10 O

V12 IO

Y12 IO

Y1 I

T3 IOD

Y3 I

IO

ISA Address Bus

IO

ISA “Latched” Address Bus

These address lines allow accesses to physical memory on the ISA bus up to

16Mbytes.

IO

ISA Bus Data.

SD7:4 are strap options for keyboard inputs 6:3 (see Function 0 Rx5A)

ISA Byte High Enable.

transferred on the upper byte (SD[15:8]) of the data bus. SBHE# is negated during

refresh cycles.

ISA I/O Read.

that the slave may drive data on to the ISA data bus.

ISA I/O Write.

that the slave may latch data from the ISA data bus.

ISA Memory Read.

that it may drive data onto the ISA data bus.

ISA Memory Write.

that it may latch data from the ISA data bus.

ISA Standard Memory Read.

under 1MB, which indicates that it may drive data onto the ISA data bus

ISA Standard Memory Write.

under 1MB, which indicates that it may latch data from the ISA data bus.

ISA Bus Address Latch Enable.

VT82C596B to indicate that the address (SA[19:0], LA[23:17] and the SBHE#

signal) is valid

ISA 16-Bit I/O Chip Select.

indicate that they support 16-bit I/O bus cycles.

ISA Memory Chip Select 16.

line low to indicate they support 16-bit memory bus cycles.

ISA I/O Channel Check.

an uncorrectable error has occurred for a device or memory on the ISA Bus.

ISA I/O Channel Ready.

assert IOCHRDY low to indicate that additional time (wait states) is required to

complete the cycle.

ISA Zero Wait State.

states are required.

SD[15:0] provide the data path fo r devices residing on the ISA bus.

IOR# is the command to an ISA I/O slave device which indicates

IOW# is the command to an ISA I/O slave device which indicates

MEMR# is the command to a memory slave which indicates

MEMW# is the command to a memory slave which indicates

: The LA[23:17] address lines are bi-directional.

SBHE# indicates, when asserted, that a byte is being

SMEMR# is the command to a memory slave,

SMEMW# is the command to a memory slave,

BALE is an active high signal asserted by the

This signal is driven by I/O devices on the ISA Bus to

ISA slaves that are 16-bit memory devices drive this

When this signal is asserted, it indicates that a parity or

This signal is normally high. Devices on the ISA Bus

Devices on the ISA Bus assert ZWS# to indicate that no wait

Revision 0.3 June 17, 1999 -11- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

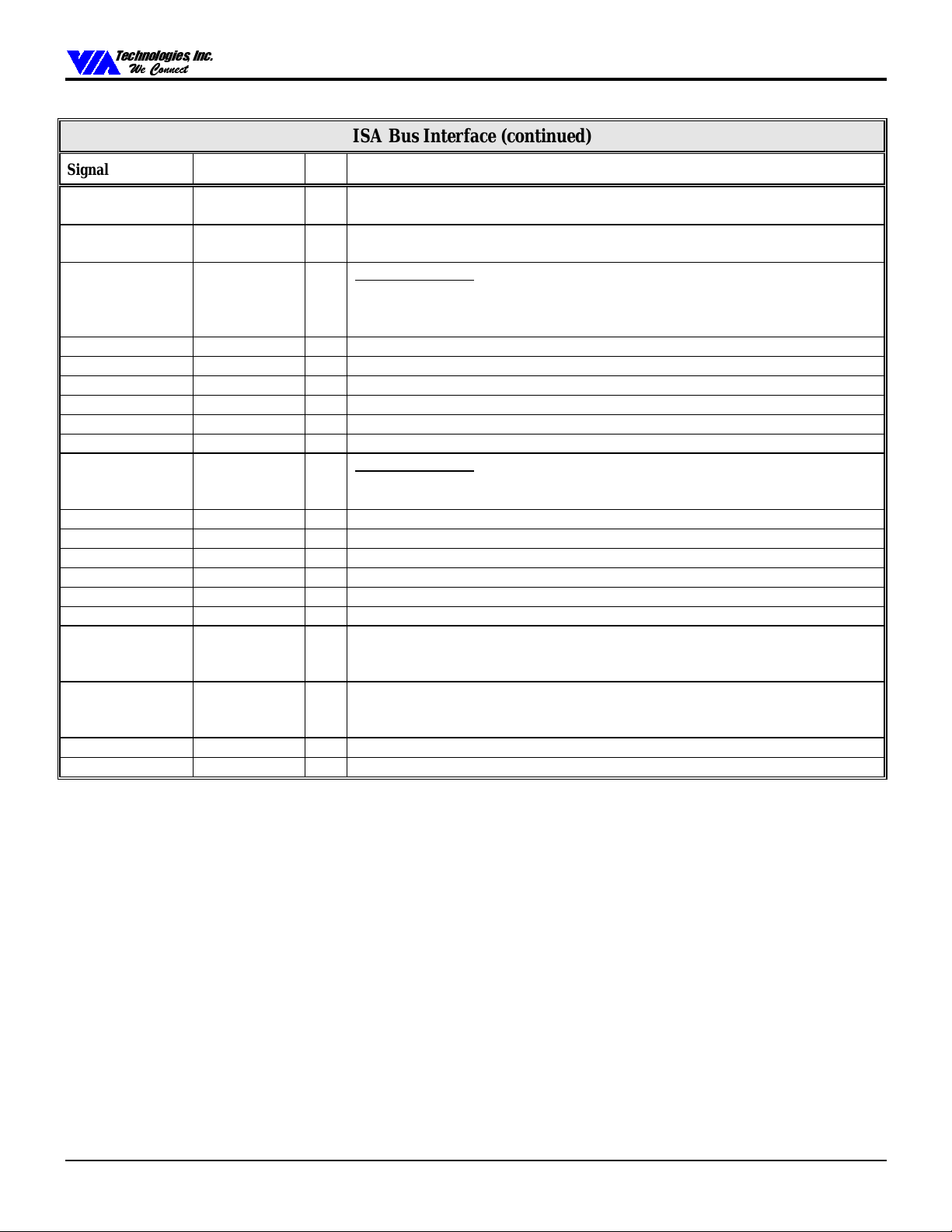

ISA Bus Interface (continued)

Signal Name Pin # I/O Signal Description

VT82C596B

RFSH#

AEN

IRQ0OUT

GPO14

IRQ1

IRQ3

IRQ4

IRQ5

IRQ6

IRQ7

IRQ8#

IRQ9

IRQ10

IRQ11

IRQ12

IRQ14

IRQ15

DRQ7-5, 3-0

DACK7-5, 3-0#

TC

SPKR

/

/ GPI6

W7 IO

Y4 O

H20 O

J20 I

T9 I

W9 I

U8 I

V8 I

Y8 I

Y20 I

U1 I

U12 I

W13 I

T13 I

V14 I

Y14 I

U17, U16,

Y16, U5, V2,

U6, W15

W17, V16,

T15, V5, Y10,

W6, U14

V10 O

K17 O

Refresh.

input RFSH# is driven by 16-bit ISA Bus masters to indicate refresh cycle.

Address Enable.

misinterpreting DMA cycles as valid I/O cycles.

Multifunction Pin

Interrupt Request 1.

Interrupt Request 3.

Interrupt Request 4.

Interrupt Request 5.

Interrupt Request 6.

Interrupt Request 7.

Multifunction Pin

Interrupt Request 9.

Interrupt Request 10.

Interrupt Request 11.

Interrupt Request 12.

Interrupt Request 14.

Interrupt Request 15.

I

DMA Request.

O

Acknowledge.

DMA service has been granted.

Terminal Count.

Speaker Drive.

As an output RFSH# indicates when a refresh cycle is in progress. As an

AEN is asserted during DMA cycles to prevent I/O slaves from

Rx74[7] = 1

Rx74[7] = 0

Rx5A[2] = 0 Internal RTC disabled.

Rx5A[2] = 1 Internal RTC enabled.

Interrupt Request 0 Output.

system timer IRQ0 signal.

General Purpose Output 14

Used to request DMA services from the internal DMA controller.

Used by the internal DMA controller to indicate that a request for

Asserted to DMA slaves as a terminal count indicator.

The output of internal timer/counter 2.

General Purpose Input 6

Reflects the state of the internal

.

Interrupt Request 8

from external RTC

.

Revision 0.3 June 17, 1999 -12- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

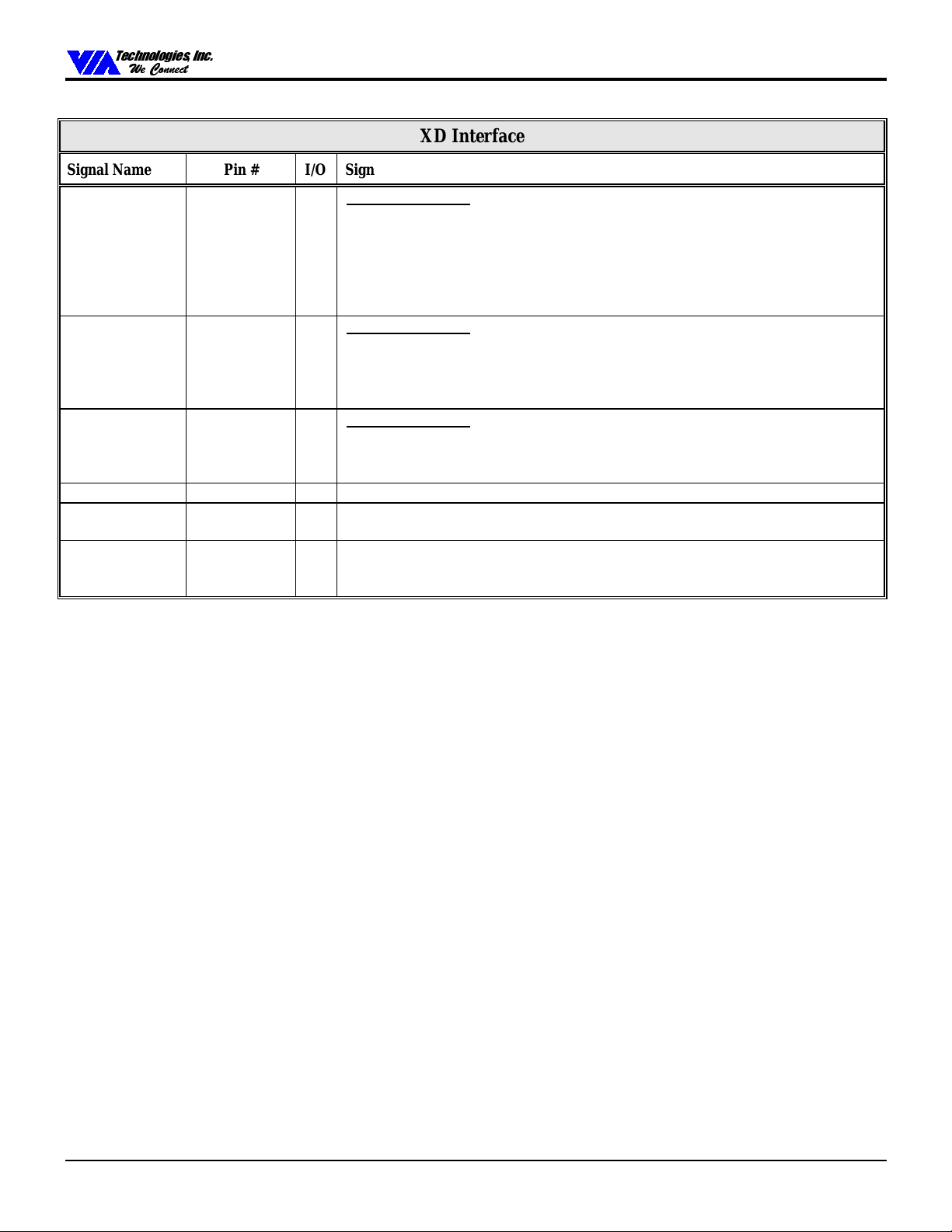

XD Interface

Signal Name Pin # I/O Signal Description

VT82C596B

XDIR#

XOE#

KBCS#

ROMCS#

MCCS#

PCS[1-0]#

/ GPO22

/ GPO23

/ GPO26

M3 O

M4 O

K1 O

K2 O

N4 O

N5, L4 O

MultiFunction Pin

X-Bus Data Direction.

memory read cycles to the programmed BIOS or APIC address space. XDIR# is

tied directly to the direction control of a 74F245 transceiver that buffers the X-Bus

data and ISA-Bus data. SD0-7 connect to the “A” side of the transceiver and

XD0-7 connect to the “B” side. XDIR# high indicates that SD0-7 drives XD0-7.

General Purpose Output 22.

MultiFunction Pin

X-Bus Output Enable.

XOE# is tied directly to the output enable of a 74F245 transceiver that buffers the

X-Bus data and ISA-Bus data (see XDIR# above).

General Purpose Output 23.

MultiFunction Pin

External Keyboard Controller Chip Select.

or write accesses to I/O ports 60h and 64h.

General Purpose Output 26.

ROM Chip Select.

Microcontroller Chip Select.

62h or 66h.

Programmable Chip Selects.

write ISA address ranges. Devices selected by these pins are assumed to be on the XBus (XDIR# and XOE# are enabled).

(Rx75[6]=0) Asserted low for all I/O read cycles and for

(Rx75[6]=1) General purpose output.

(Rx75[6]=0) Asserted low for all decoded X-Bus cycles.

(Rx75[6]=1) General purpose output.

(Rx76[2] = 0) Asserted during read

(Rx76[2]=1) General purpose output.

Chip Select to the BIOS ROM.

Asserted during read or write accesses to I/O ports

Asserted during I/O cycles to programmable read or

Revision 0.3 June 17, 1999 -13- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

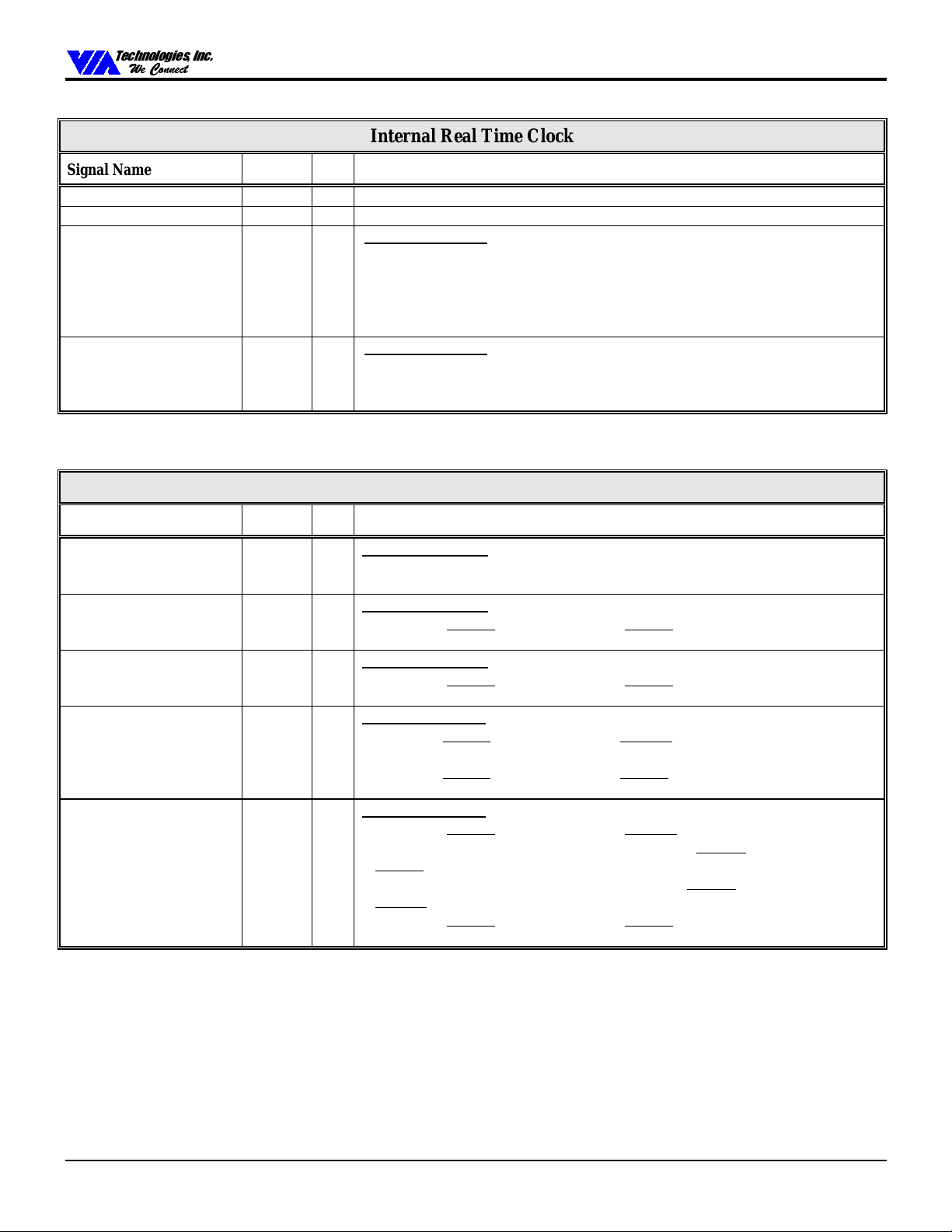

Internal Real Time Clock

Signal Name Pin # I/O Signal Description

VT82C596B

RTCX1

RTCX2

RTCCS#

RTCAS

/ GPO24

/ GPO25

N19 I

R20 O

M2 O

L1 O

RTC Crystal Input

RTC Crystal Output

MultiFunction Pin

External RTC Chip Select.

RTC port 71h. Externally connected to a pair of OR gates (to logically AND

the chip select with IOR# and IOW#) to generate the active-low RTC read and

write commands.

General Purpose Output 24.

MultiFunction Pin

External RTC Address Strobe.

Port 70h.

General Purpose Output 25.

Internal Keyboard Controller

Signal Name Pin # I/O Signal Description

KEYLOCK

/ NC

KBCK

/ NC

KBDT

/ A20GATE

MSCK

/ KBCS# / GPO26

MSDT

/ PIRQ1

J4 I

N3 IO

M5 IO

P1 IO

K1 IO

Extended Function

Rx59[1]=1

Key Lock.

Extended Function

Rx5A[0]=1 (Internal keyboard controller enabled –strapped from XD0)

Keyboard Clock

Extended Function

Rx5A[0]=1 (Internal keyboard controller enabled –strapped from XD0)

Keyboard Data

MultiFunction Pin

Rx5A[1]=0 (internal keyboard controller disabled – strapped from XD1)

Gate A20.

Rx5A[1]=1 (internal keyboard controller enabled

Mouse Clock.

MultiFunction Pin

Rx5A[1]=0 (Internal keyboard controller disabled –strapped from XD1)

Keyboard Controller Chip Select.

enabled) Chip select for external keyboard controller.

General Purpose Output 26

disabled) General purpose output

Rx5A[1]=1 (Internal keyboard controller enabled –strapped from XD1)

Mouse Data.

Input to internal keyboard controller

From optional external keyboard controller

Mouse clock (exte nded function not available on PIIX4)

Mouse data (extended function not available on PIIX4)

: 32.768 KHz crystal or oscillator input.

: 32.768 KHz crystal output

(Rx76[0] = 0) Asserted for read or write accesses to

(Rx76[0] = 1) General purpose output.

(Rx76[1] = 0) Asserted for writes to RTC I/O

(Rx76[1] = 1) General purpose output.

(PIIX4 PIRQ1)

(PIIX4 No Connect)

(PIIX4 No Connect)

–strapped from XD1)

(Rx76[2]=0 external keyboard controller

(Rx76[2]=1 external keyboard controller

Revision 0.3 June 17, 1999 -14- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

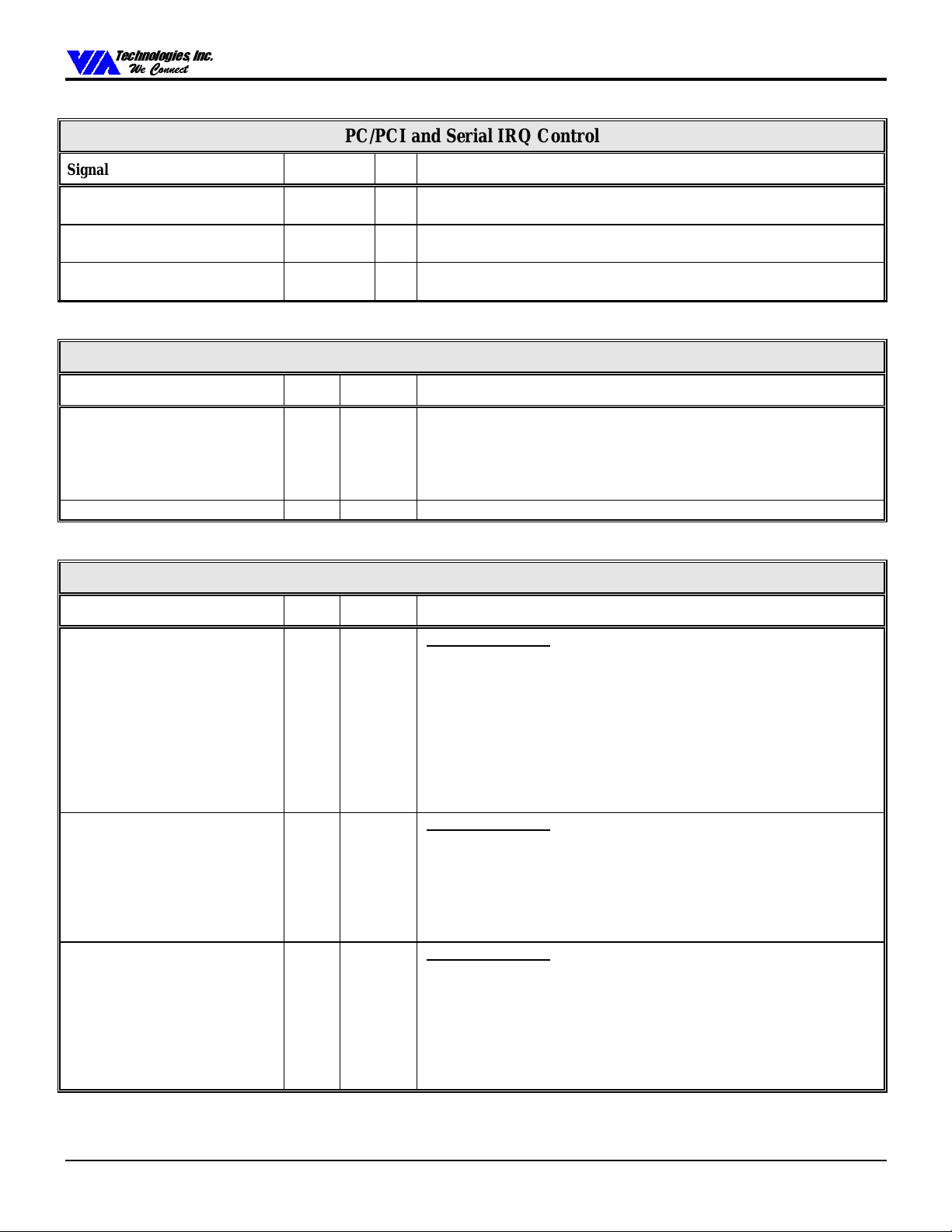

PC/PCI and Serial IRQ Control

Signal Name Pin # I/O Signal Description

VT82C596B

REQ[A-C]#

GNT[A-C]#

SERIRQ

/ GPI7

/ GPI[2-4]

/ GPO[9-11]

M1, N2, P3 I

N1, P2, P4 O

J19 I

PC/PCI DMA Requests.

per the PC/PCI protocol. For GPI functions refer to Rx7D[2-0].

PC/PCI DMA Grants.

PC/PCI protocol. For GPO functions refer to Rx7D[2-0].

Serial Interrupt Request.

Rx68[3].

A20 Control

Signal Name Pin # I/O Signal Description

A20GATE

A20M#

/ MSCK

P1 I

M20 OD

Gate A20:

if used. Logically combined with Port 92 bit-1 (Fast_A20) and output

on the A20M# signal. If the internal keyboard / PS2 mouse co ntroller is

used, this pin becomes the mouse clock input (the A20GATE signal

comes directly from the internal keyboard controller).

A20 Mask.

Gate A20 output from optional external keyboard controller

Connect to A20 mask input of the CPU.

APIC Interface

Signal Name Pin # I/O Signal Description

APICREQ#

APICCS#

APICACK#

/ APICD0 / GPO13

/ WSC# / GPI5

/ APICD1 / GPO12

K18 I / I / I

H18 O / O / O

J17 O / O / O

MultiFunction Pin

Internal APIC Write Snoop Complete.

Asserted by the north bridge to indicate that all snoop activity on the

CPU bus initiated by the last PCI-to-DRAM write is complete and

that it is safe to perform an APIC interrupt.

External APIC Request.

external APIC synchronous to PCICLK prior to sending an interrupt

over the APIC serial bus. This signals the VT82C596B to flush its

internal buffers.

General Purpose Input 5.

MultiFunction Pin

Internal APIC Data 0.

External APIC Chip Select.

VT82C596B drives this signal active to select an external APIC (if

used). This occurs if the external APIC is enabled and a PCI cycle is

detected within the programmed APIC address range.

General Purpose Output 13.

MultiFunction Pin

Internal APIC Data 1.

External APIC Acknowledge.

the VT82C596B to indicate that it internal buffers have been flushed

(in response to APICREQ#). This indicates to the external APIC that

the VT82C596B’s internal buffers have been flushed and that it is OK

for the APIC to send its interrupt.

General Purpose Output 12.

Used by PCI agent to request DMA services

Used to acknowledge DMA services per the

Used with Distributed DMA. For GPI see

(Rx74[7]=1 & Rx74[1]=1)

(Rx74[7]=1 & Rx74[1]=0) Asserted by

(Rx74[7] = 0)

(Rx74[7]=1 & Rx74[1]=1)

(Rx74[7]=1 & Rx74[1]=0) The

(Rx74[7] = 0)

(Rx74[7]=1 & Rx74[1]=1)

(Rx74[7]=1 & Rx74[1]=0) Asserted by

(Rx74[7] = 0)

Revision 0.3 June 17, 1999 -15- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

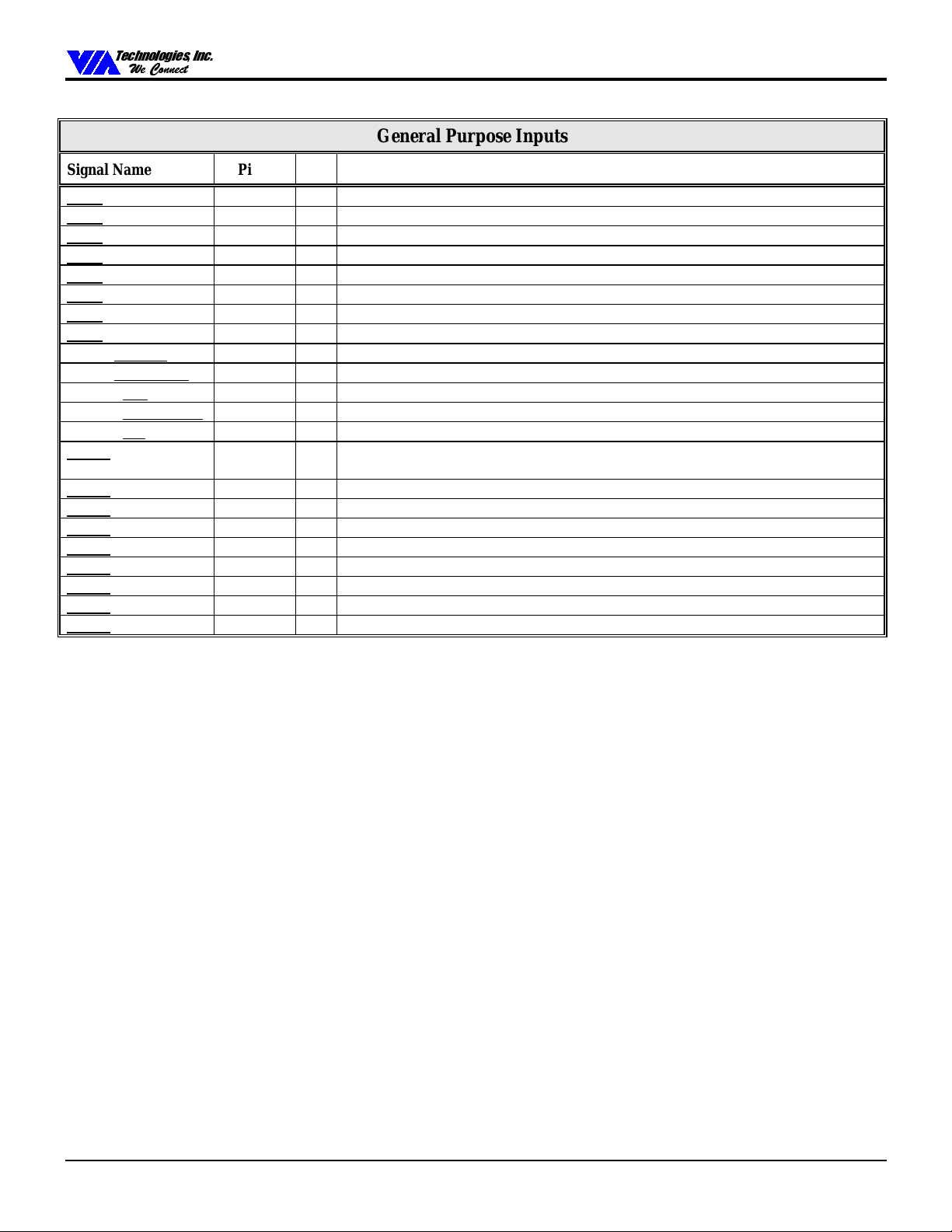

General Purpose Inputs

Signal Name Pin # I/O Signal Description

VT82C596B

/ IOCHCK#

GPI0

/ PME#

GPI1

/ REQA#

GPI2

/ REQB#

GPI3

/ REQC#

GPI4

/ APICREQ#

GPI5

/ IRQ8#

GPI6

/ SERIRQ

GPI7

/ THRM#

GPI8

/ BATLOW#

GPI9

/ LID

GPI10

/ SMBALRT#

GPI11

/ RI#

GPI12

/ SLPBTN#

GPI13

GPI14

GPI15

GPI16

GPI17

GPI18

GPI19

/ PIRQ0

GPI20

/ PIRQ2

GPI21

The underlined name above indicates the default function on power up.

Y1 I

P19 I

M1 I

N2 I

P3 I

K18 I

Y20 I

J19 I

H19 I

U19 I

P16 I

N17 I

P18 I

L2 I

J3 I

L5 I

K3 I

K4 I

H1 I

H4 I

H5 I

G3 I

General Purpose Input 0.

General Purpose Input 1.

General Purpose Input 2.

General Purpose Input 3.

General Purpose Input 4.

General Purpose Input 5.

General Purpose Input 6.

General Purpose Input 7.

General Purpose Input 8.

General Purpose Input 9.

General Purpose Input 10.

General Purpose Input 11.

General Purpose Input 12.

General Purpose Input 13.

register 0 of ACPI I/O Space (Function 3) is enabled

General Purpose Input 14.

General Purpose Input 15.

General Purpose Input 16.

General Purpose Input 17.

General Purpose Input 18.

General Purpose Input 19.

General Purpose Input 20.

General Purpose Input 21.

(Rx74[0] = 0)

(Rx7D[0] = 0)

(Rx7D[1] = 0)

(Rx7D[2] = 0)

(Rx74[7] = 0)

(Rx5A[2] = 1)

(Rx68[3] = 0)

(Rx74[2] = 1)

(Rx74[3] = 1)

(Rx74[4] = 1)

(Rx74[5] = 1)

(Rx74[6] = 1)

Also functions as the ACPI sleep button if bit-9 of

(Rx59[0] = 1) See also Rx55[3:0]

(Rx59[2] = 1) See also Rx58[3:0]

Revision 0.3 June 17, 1999 -16- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

General Purpose Outputs

Signal Name Pin # I/O Signal Description

VT82C596B

GPO0

/ LA17

GPO1

/ LA18

GPO2

/ LA19

GPO3

/ LA20

GPO4

/ LA21

GPO5

/ LA22

GPO6

/ LA23

GPO7

GPO8

/ GNTA#

GPO9

GPO10

GPO11

GPO12

GPO13

GPO14

GPO15

GPO16

GPO17

GPO18

GPO19

GPO20

GPO21

GPO22

GPO23

GPO24

GPO25

GPO26

GPO27

GPO28

GPO29

GPO30

The underlined name above indicates the default function on power up.

/ GNTB#

/ GNTC#

/ APICACK#

/ APICCS#

/ IRQ0OUT

/ SUSB#

/ SUSC#

/ CPUSTP#

/ PCISTP#

/ ZZ

/ SUSST1#

/ SUSST2#

/ XDIR#

/ XOE#

/ RTCCS#

/ RTCAS

/ KBCS#

/ SCIOUT#

G4 O

Y15

T14

W14

U13

V13

Y13

T12

T19 O

N1 O

P2 O

P4 O

J17 O

H18 O

H20 O

V19 O

U18 O

R1 O

R2 O

K16 O

T17 O

T18 O

M3 O

M4 O

M2 O

L1 O

K1 O

G5 O

F2 O

F3 O

F4 O

General Purpose Output 0.

IO General Purpose Output 1.

IO General Purpose Output 2.

IO General Purpose Output 3.

IO General Purpose Output 4.

IO General Purpose Output 5.

IO General Purpose Output 6.

IO General Purpose Output 7.

General Purpose Output 8.

General Purpose Output 9.

General Purpose Output 10.

General Purpose Output 11.

General Purpose Output 12.

General Purpose Output 13.

General Purpose Output 14.

General Purpose Output 15.

General Purpose Output 16.

General Purpose Output 17.

General Purpose Output 18.

General Purpose Output 19.

General Purpose Output 20.

General Purpose Output 21.

General Purpose Output 22.

General Purpose Output 23.

General Purpose Output 24.

General Purpose Output 25.

General Purpose Output 26.

General Purpose Output 27.

General Purpose Output 28.

General Purpose Output 29.

General Purpose Output 30.

Rx74[0] = 0.

Rx74[0] = 0.

Rx74[0] = 0.

Rx74[0] = 0.

Rx74[0] = 0.

Rx74[0] = 0.

Rx74[0] = 0.

F3Rx54[1-0]. Optional 1Hz / 2Hz / 4Hz clock output

Rx7D[0] = 0.

Rx7D[1] = 0.

Rx7D[2] = 0.

Rx74[7] = 0.

Rx74[7] = 0.

Rx74[7] = 0.

Rx75[0] = 1. See also F3Rx54[3].

Rx75[0] = 1. See also F3Rx54[2].

Rx75[1] = 1.

Rx75[2] = 1.

Rx75[3] = 1.

Rx75[4] = 1. See also F3Rx54[4].

Rx75[5] = 1. See also F3Rx54[7].

Rx75[6] = 1.

Rx75[6] = 1.

Rx76[0] = 1.

Rx76[1] = 1.

Rx76[2] = 1.

Rx74[7] = 0.

Revision 0.3 June 17, 1999 -17- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

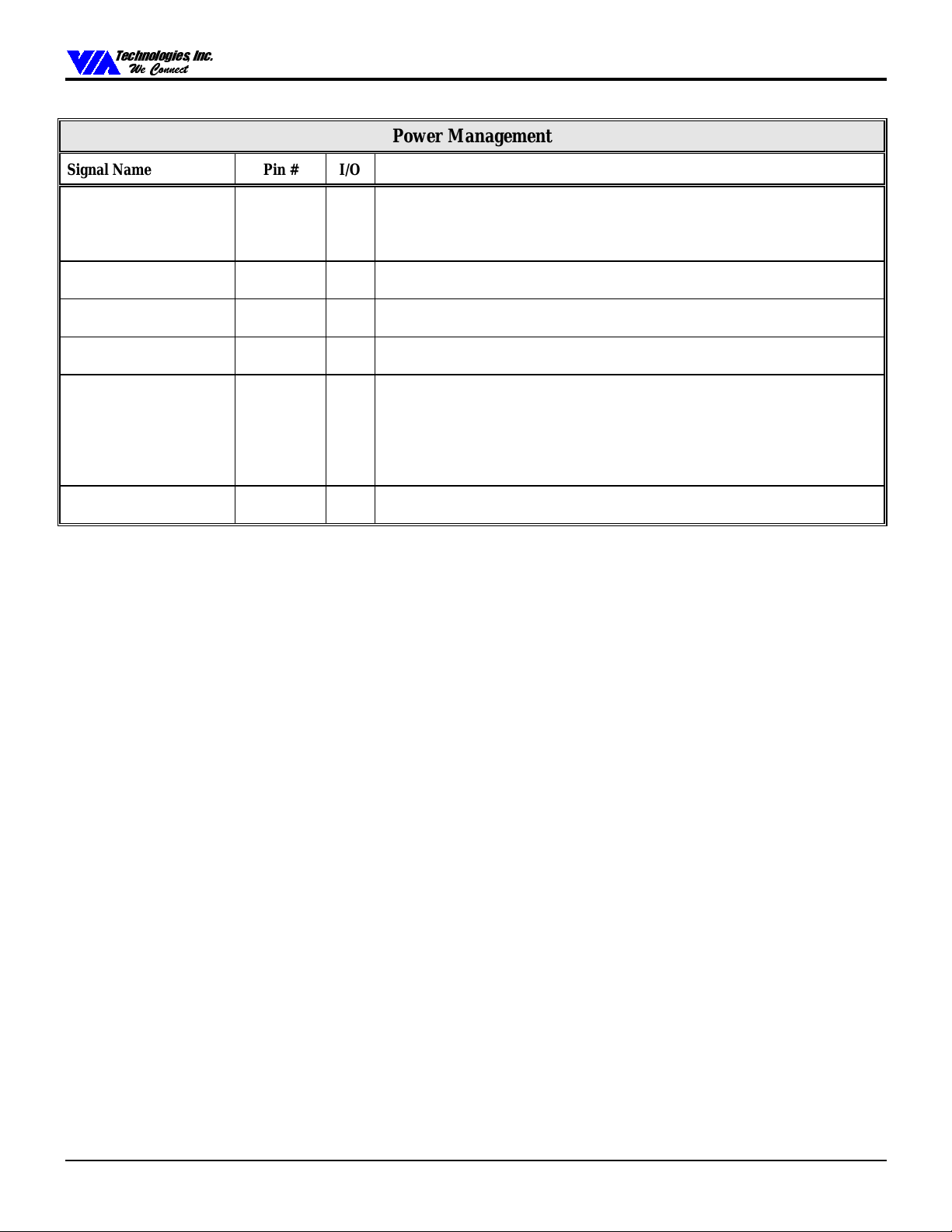

Power Management

Signal Name Pin # I/O Signal Description

VT82C596B

PWRBTN#

SLPBTN#

RCIN#

RSMRST#

EXTSMI#

PCIREQ[A-D]#

/ GPI13

U20 I

L2 I

N20 I

M17 I

V20 IOD

E10, A11,

B11, C11

Power Button.

external system on/off button or switch. The VT82C596B performs a 200us

debounce of this input if Rx40[5] is set to 1. This input is referenced to

VCCSUS.

ACPI Sleep Button.

sleep button if bit-9 of register 0 of ACPI I/O Space (Function 3) is enabled.

Reset CPU.

used) causes an INIT signal to be generated to the CPU.

Resume Reset.

plane and also resets portions of the internal RTC logic.

External System Management Interrupt.

edge on this input causes an SMI# to be generated to the CPU to enter SMI

mode. Once asserted, this pin should be held low for at least four PCICLKs.

The VT82C596B also asserts EXTSMI# in response to SMI# being activated

within the Serial IRQ function. This pin should be connected to an external

pullup.

I

Power Management PCI Requests.

monitor PCI requests for use of the PCI bus.

Used by the Power Management subsystem to monitor an

General purpose input 13, but also functions as the ACPI

This signal from an optional external keyboard controller (if

Resets the internal logic connected to the VCCSUS power

When enabled to allow it, a falling

Used by internal power management to

Revision 0.3 June 17, 1999 -18- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

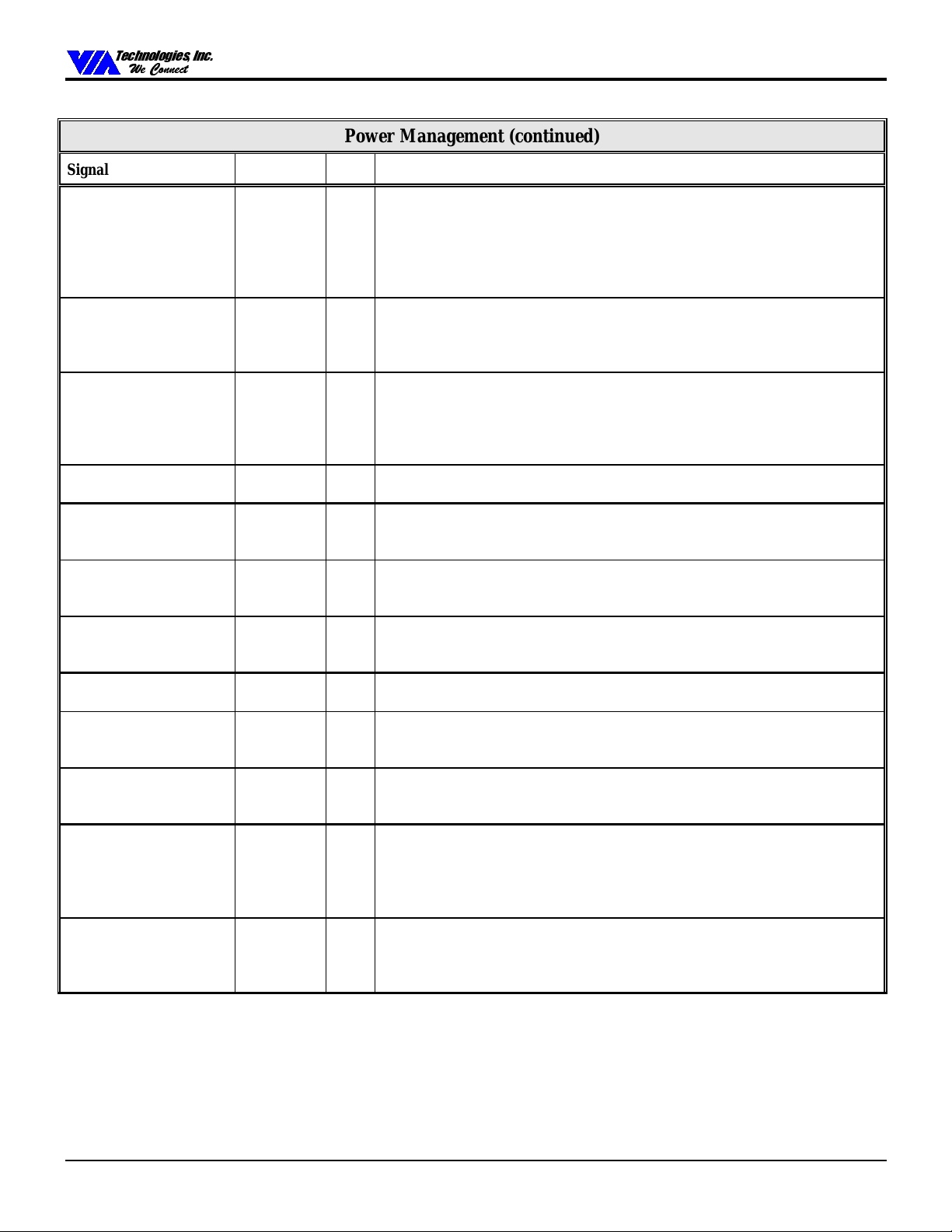

Power Management (continued)

Signal Name Pin # I/O Signal Description

VT82C596B

/ GPI10

LID

/ GPI12

RI#

THRM#

SCIOUT#

CPUSTP#

PCISTP#

/ GPO19

ZZ

SUSA#

/ GPO15

SUSB#

SUSC#

SUSST1#

SUSST2#

/ GPO16

/ GPI8

/ GPO29

/ GPO17

/ GPO18

/ GPO20

/ GPO21

P16 I

P18 I

H19 I

F3 O

R1 O

R2 O

K16 O

W20 O

V19 O

U18 O

T17 O

T18 O

Notebook Computer Display Lid Open / Closed Monitor.

Power Management subsystem to monitor the opening and closing of the

display lid of notebook computers. Can be used to detect either low-to-high

and/or high-to-low transitions to generate an SMI#. The VT82C596B

performs a 200 usec debounce of this input if Rx40[5] is set to 1. May

optionally be programmed as a general purpose input (Rx74[4]=1).

Ring Indicator.

system to be re-activated by a received phone call. This input is referenced to

VCCSUS. May optionally be programmed as a general purpose input

(Rx74[6]=1).

Thermal Detect.

signal initiates hardware Clock Throttling mode. This causes STPCLK# to be

cycled at a preset programmable rate (see Function 3 configuration space

Rx4C). May optionally be programmed as a general purpose input

(Rx74[2]=1).

ACPI System Control Interrupt.

May optionally be programmed as a general purpose output (Rx74[7]=0).

CPU Clock Stop.

outputs. May optionally be programmed as a general purpose output

(Rx75[1]=1).

PCI Clock Stop.

outputs. May optionally be programmed as a general purpose output

(Rx75[2]=1).

L2 Cache SRAM Low Power Mode.

SRAMs during CPU Stop Clock state. May optionally be programmed as a

general purpose output (Rx75[3]=1).

Suspend Plane A Control.

and STD suspend states. Used to control the primary power plane.

Suspend Plane B Control.

suspend states. Used to control the secondary power plane. May optionally be

programmed as a general purpose output (Rx75[0]=1).

Suspend Plane C Control.

state. Used to control the tertiary power plane. May optionally be

programmed as a general purpose output (Rx75[0]=1).

Suspend Status 1.

Apollo MVP3) to provide information on host clock status. Asserted when the

system may stop the host clock, such as Stop Clock or during POS, STR, or

STD suspend states. May optionally be programmed as a general purpose

output (Rx75[4]=1).

Suspend Status 2.

information on system suspend state. Asserted during POS, STR, or STD

suspend states. May optionally be programmed as a general purpose output

(Rx75[5]=1).

May be connected to external modem circuitry to allow the

If the VT82C596B is enabled to allow it, asserting this

Connected to the external APIC if used.

Signals the system clock generator to disable the CPU clock

Signals the system clock generator to disable the PCI clock

Used to power down the L2 Cache

Asserted during po wer management POS, STR,

Asserted during power management STR and STD

Asserted during p ower manage ment ST D susp end

Typically connected to the North Bridge (e.g., VT82C598

Typically connected to other system devices to provide

Used by the

Revision 0.3 June 17, 1999 -19- Pinouts

7HFKQRORJLHV ,QF

&

:H&RQQHFW

RQQHFW

:H

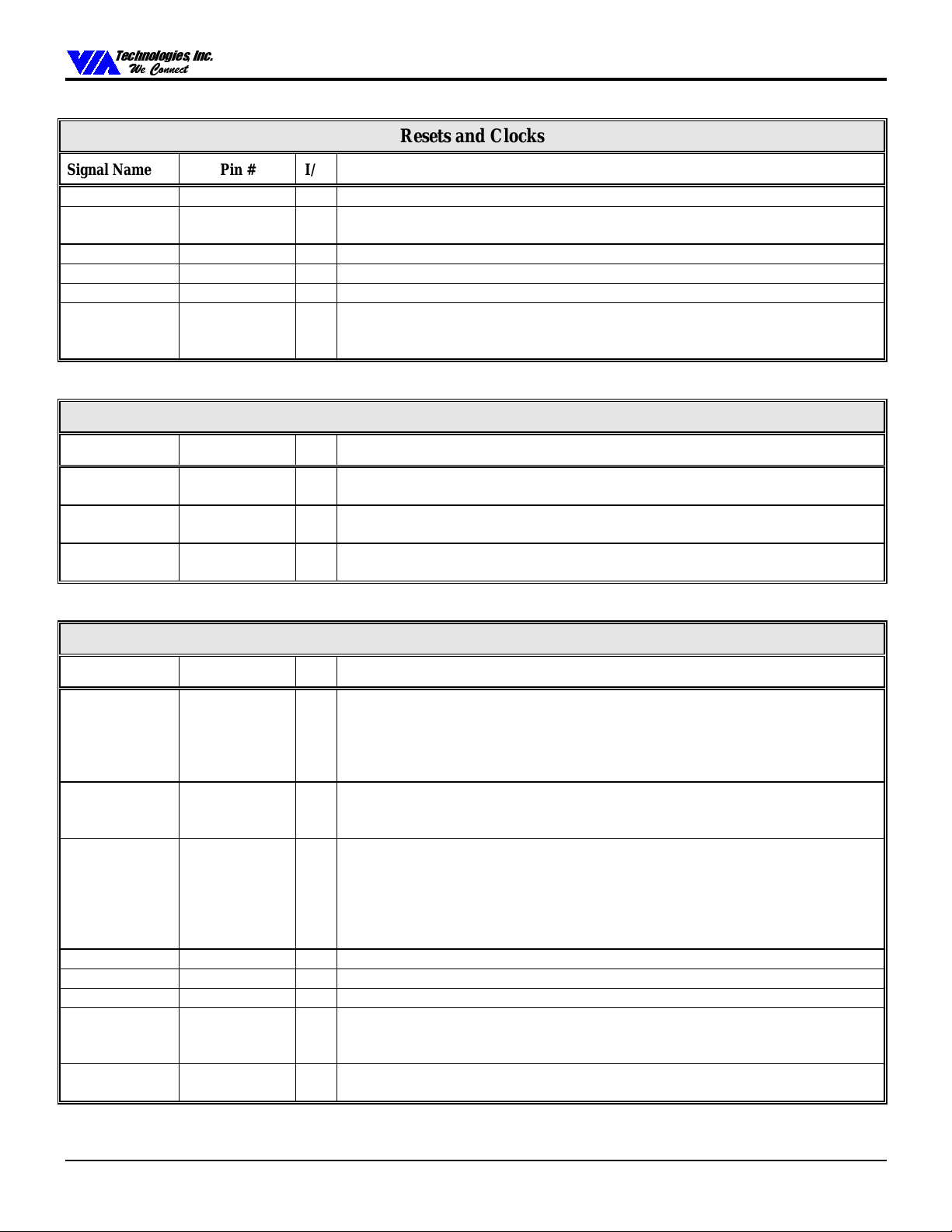

Resets and Clocks

Signal Name Pin # I/O Signal Description

VT82C596B

PWRGD

PCIRST#

RSTDRV

BCLK

OSC

SUSCLK

M18 I

A1 O

W1 O

T7 O

V11 I

P17 O

Power Good.

PCI Reset.

this pin during power-up or from the control register.

Reset Drive.

Bus Clock.

Oscillator.

Suspend Clock.

VT82C598 Apollo MVP3) for DRAM refresh purposes. Stopped during Suspend-to-

Disk and Soft-Off modes.

Connected to the PWRGOOD signal on the Power Supply.

Active low reset signal for the PCI bus. The VT82C596B will assert

Reset signal to the ISA bus.

ISA bus clock.

14.31818 MHz clock signal used by the internal Timer.

32.768 KHz output clock for use by the North Bridge (e.g.,

Configuration and Test

Signal Name Pin # I/O Signal Description

CFG1

CFG2

TEST#

R17 I

R18 I

V18 I

Configuration 1.

the polarity of the INIT and CPURST signals.

Configuration 2.

memory (FFFF0000h-FFFFFFFFh): 0 = Positive decode, 1 = Subtractive decode.

Used to select chip test modes. Pulled up externally to VCCSUS for normal

Test.

operation.

Used to select the CPU type (0=Socket-7, 1=Slot-1). Determines

Used to select the type of decoding for the top 64 Kbytes of

Power and Ground

Signal Name Pin # I/O Signal Description

VCC

VREF

VCCSUS

VBAT

VCCUSB

GNDUSB

GND

NC

E9, E11, E12,

E16, F5, F6,

F14, F15, G6,

P15, R6, R7 ,

R15, T6

J16 P

N16, R16 P

L16 P

K5 P

J5 P

D10, E7, E13,

J9-12, K9-12,

L9-12, M9-12

J4, M5, M16,

N3, N18, R5

P

Core Power.

the mechanical switch on the power supply is turned on and the PWRON signal is