VIA VT82C42 Datasheet

VT82C42

K

EYBOARD CONTROLLER

Preliminary Release

DATE : November 22, 1995

VIA TECHNOLOGIES, INC.

P

RELIMINARY DOCUMENT RELEASE

The material in this document supersedes all previous documentation issued for any of the products

included herein. Please contact VIA Technologies for the latest documentation.

Copyright Notice:

©

Copyright

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or

translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical,

chemical, manual or otherwise without the prior written permission of Via Technologies Incorporated.

The VT82C42 may only be used to identify products of VIA Technologies.

All trademarks are the properties of their respective owners.

1995, Via Technologies Incorporated. Printed in Taiwan. A

LL RIGHTS RESERVED

.

Disclaimer Notice:

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies . VIA

Technologies mak es no warranties, implied or otherwise, in regard to this document and to the products

described in this document. The information pr ovided by this document is believed to be accurate and

reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for

any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or

misuse of the infor mation in this document and for any patent infringem ents that may arise from the use of

this document. The information and pr oduct specifications within this docum ent are subject to change at

any time, without notice and without obligation to notify any person of such change.

Offices:

5020 Brandin Court 8th Floor, No. 533

Fremont, CA 94538 Chung-Cheng Rd., Hsin-Tien

USA Taipei, Taiwan ROC

Tel: (510) 683-3300 Tel: (886-2) 218-5452

Fax: (510) 683-3301 Fax: (886-2) 218-5453

VIA Technologies, Inc.

VT82C42

VT82C42 Keyboard Controller

Date : November 22, 1995

1. General Overview:

The VT82C42 is a compatible direct replacement for the Intel 80C42 BIOS version of the Keyboard

Controller. The VT82C42 is fully implemented by hardware logic so that it has a very fast response capability

for any command issued by the host. In addition to keyboard support, the VT82C42 also offers PS/2 mouse

support. The VT82C42 also offers the Mouse Lock

designed by VIA technologies, which locks the mouse when the keylock function is initiated.

2. Features:

∗

Fully hardware implemented, 0.8µm CMOS Technology.

∗

Very high speed response of A20 GATE & reset.

∗

Support PS2 style mouse.

∗

Compatible with all major BIOS, including AWARD, PHOENIX and AMI.

TM

function (patent pending), a feature exclusively

∗

40 pin PDIP and 44 pin PLCC packages.

3. Function Description:

The internal timer counting is based on an 8Mhz clock input from X1, X2 ( or X2, with X1 connected to

ground). After the deassertion of RESET#, the VT82C4 2 will drive high at pin P 23 and pin P 2 7. After 6 µs (6

x 8 clocks) of driving, the VT82C42 will check on pins T1 & P10; if both pins are low, then the VT82C42

will switch to PS/2 mode. Otherwise, the VT82C42 will remain in AT mode.

If the VT82C42 is in AT mode after the self test, then it will drive P24 and P2 5 low with all other ports high.

If the VT82C42 is in PS/2 mode, then it will drive P24, P25, P 22, and P 27 low with all other ports high. The

VT82C42 will not change its driving value until it receives the command "AA" from the host. When receiving

the command "AA" from the host, the VT82C42 will prepare a "55" in its output buffer and drive P24

(reflecting the internal OBF flag) high within 6 clocks. This response time is the typical active time for

internal IBF flag. After this initialization procedure, the VT82C42 will drive P26 low (AT mode) or drive P26

and P23 low (PS/2 mode) in order for the keyboard and mouse interface to receive data from keyboard or

mouse.

When the keyboard or mouse toggles the interface (KBCLK, KBDATA, MSCLK,MSDATA), the controller

receives data from the serial interface and stores the received data into its internal output buffer. If the

received data is from the keyboard, a scan code translation is executed before the data is sent to the output

buffer. The VT82C42 also raises P24 or P25 to indicate a output buffer full. The host is signaled to issue a

read command to the data port to read the received data out. When the VT82C42 receives data in the normal

mode (pin 25 on DIP40 or pin 28 on PLCC44 parts connected to VCC) and the status of P17 is low, then the

controller will not raise the P24, nor activate its internal OBF flag. It looks like the contro ller will consume the

income data itself. And if the data is from the mouse, the controller will still raise P25 to indicate that data is

coming from mouse. However, if the VT82C42 is in Mouse Lock

PLCC44 parts connected to GND), the data from either keyboard or mouse will be prohibited from sending to

the host.

TM

mode (pin 25 on DIP40 or pin 28 on

-1-

VIA Technologies, Inc.

VT82C42

The host can program the output port (P20-P23 in AT mode, or P20-P21 in PS/2 mode) or in-out port (P10P15 in AT mode, or P12-P15 in PS/2 mode) by issuing a command to the command register on the VT82C42.

The controller will then quickly execute the specified command. Note that P16-P17 is implemented as an

input port only. The host can also transmit data to the keyboard and mouse by issuing a command to the data

register. The data coming to the data register (with A0 = 0, CS# = 0, RD# = 1, and WR# = 0) will be sent to

the keyboard via the keyboard serial interfaces. The data sent to the mouse will be completed by 1) issuing a

D4 command to the command register, 2) then writing the following data byte to the data register (to be sent to

the mouse via mouse serial interface). In either case, the VT82C42 will wait for an acknowledgement from the

keyboard or mouse to complete a transmission. At the same time as the completion of the transmission, the

VT82C42 will raise P24 or P25 (when sending data to mouse) to signal the host of a completion of

transmission. When the controller receives or transmits, the controller does a parity and time-out check. If any

error occurs in the interface or inside the external devices (keyboard or mouse), the controller will reflect that

error in the following status register.

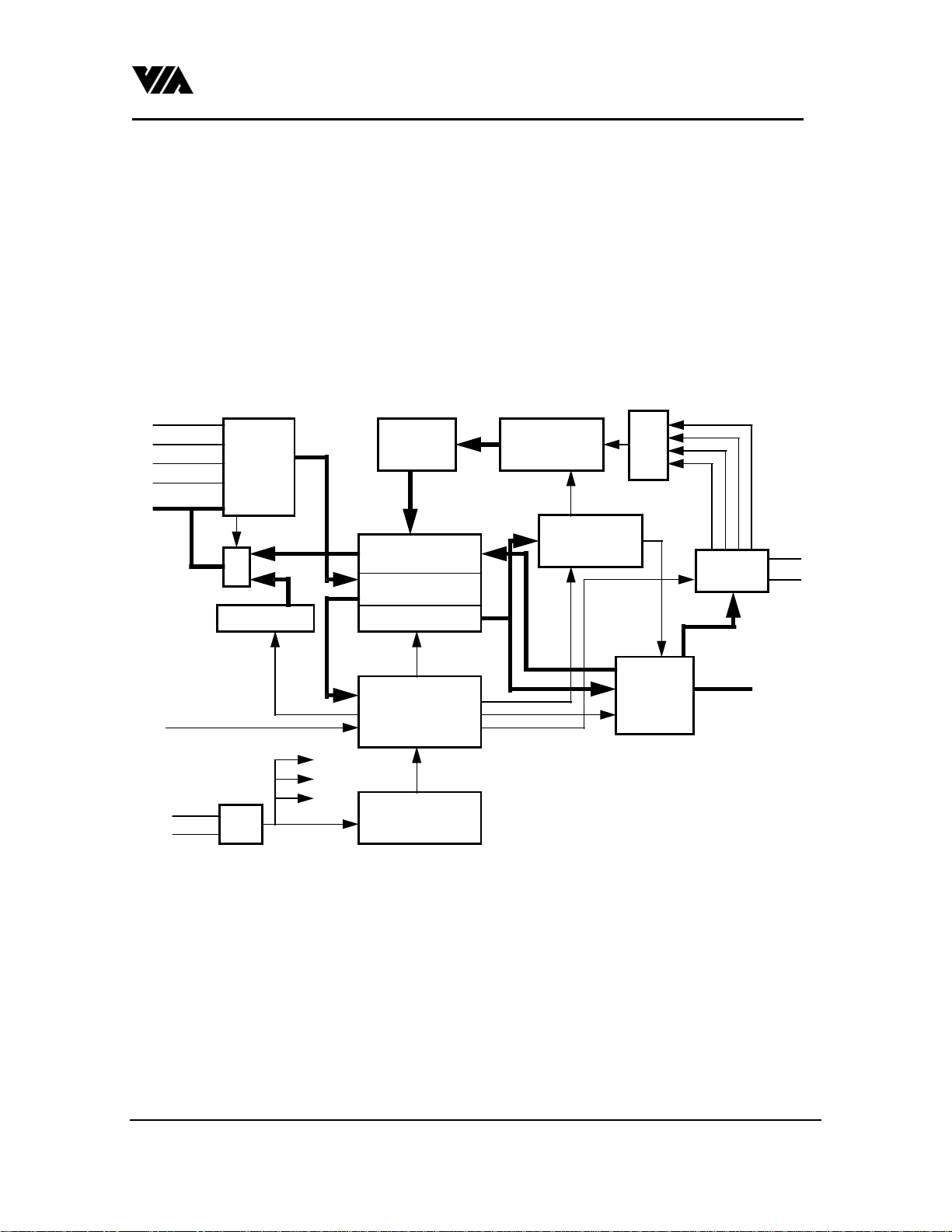

A0

C S

IOR

IOW

D[7: 0]

command

decoder

scan

mappi ng

rece iving u nit

debounci ng

KBCK

KBDT

MSCK

MSDT

RES ET

X1, X2

+

status register

cl ocking

(8 Mhz)

data input buffer

transmitting u nit

command reg ister/

data register

data output buffer

arbitration &

cent r al co ntrol

unit

tim e r

Fig 1. Block Diagram for VT82C42

In/Out

por t buf fer

mode

selector

P[17:10]

P[27:20]

T1

T0

-2-

Loading...

Loading...