Page 1

Data Sheet

VT8231

South Bridge

Revision 2.32

May 10, 2004

VIA TECHNOLOGIES, INC.

Page 2

Copyright Notice:

Copyright © 1999- 2004 VIA Technologies Incorporated. Printed in the United States. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into

any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise

without the prior written permission of VIA Technologies Incorporated.

VT8231 may only be used to identify products of VIA Technologies, Inc.

is a registered trademark of VIA Technologies, Incorporated.

TM

PS/2

Pentium

Windows 95

PCI

All trademarks are the properties of their respective owners.

is a registered trademark of International Business Machines Corp.

TM

, Pentium-ProTM, Pentium-IITM, Pentium-IIITM, CeleronTM,and GTL+TM are registered trademarks of Intel Corp.

TM

TM

is a registered trademark of the PCI Special Interest Group.

, Windows 98TM, Windows NTTM, and Plug and PlayTM are registered trademarks of Microsoft Corp.

Disclaimer Notice:

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies

makes no warranties, implied or otherwise, in regard to this document and to the products described in this document.

The information provided by this document is believed to be accurate and reliable as of the publication date of this

document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA

Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent

infringements that may arise from the use of this document. The information and product specifications within this

document are subject to change at any time, without notice and without obligation to notify any person of such change.

Offices:

USA Office: Taipei Office:

940 Mission Court 8th Floor, No. 533

Fremont, CA 94539 Chung-Cheng Road, Hsin-Tien

USA Taipei, Taiwan ROC

Tel: (510) 683-3300 Tel: (886-2) 218-5452

Fax: (510) 683-3301 or 687-4654 Fax: (886-2) 218-5453

Web: http://www.viatech.com

Web: http://www.via.com.tw

Page 3

VT8231 South Bridge

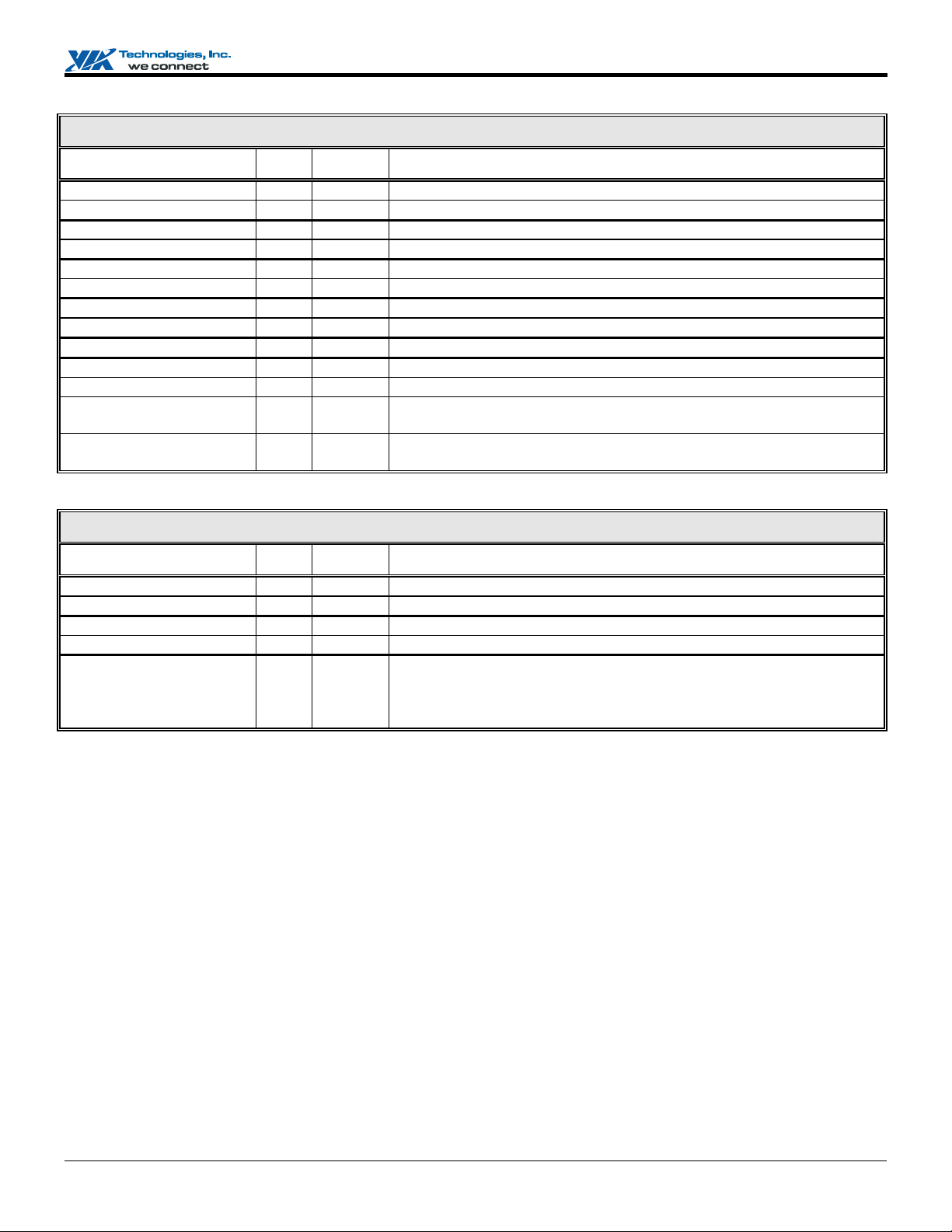

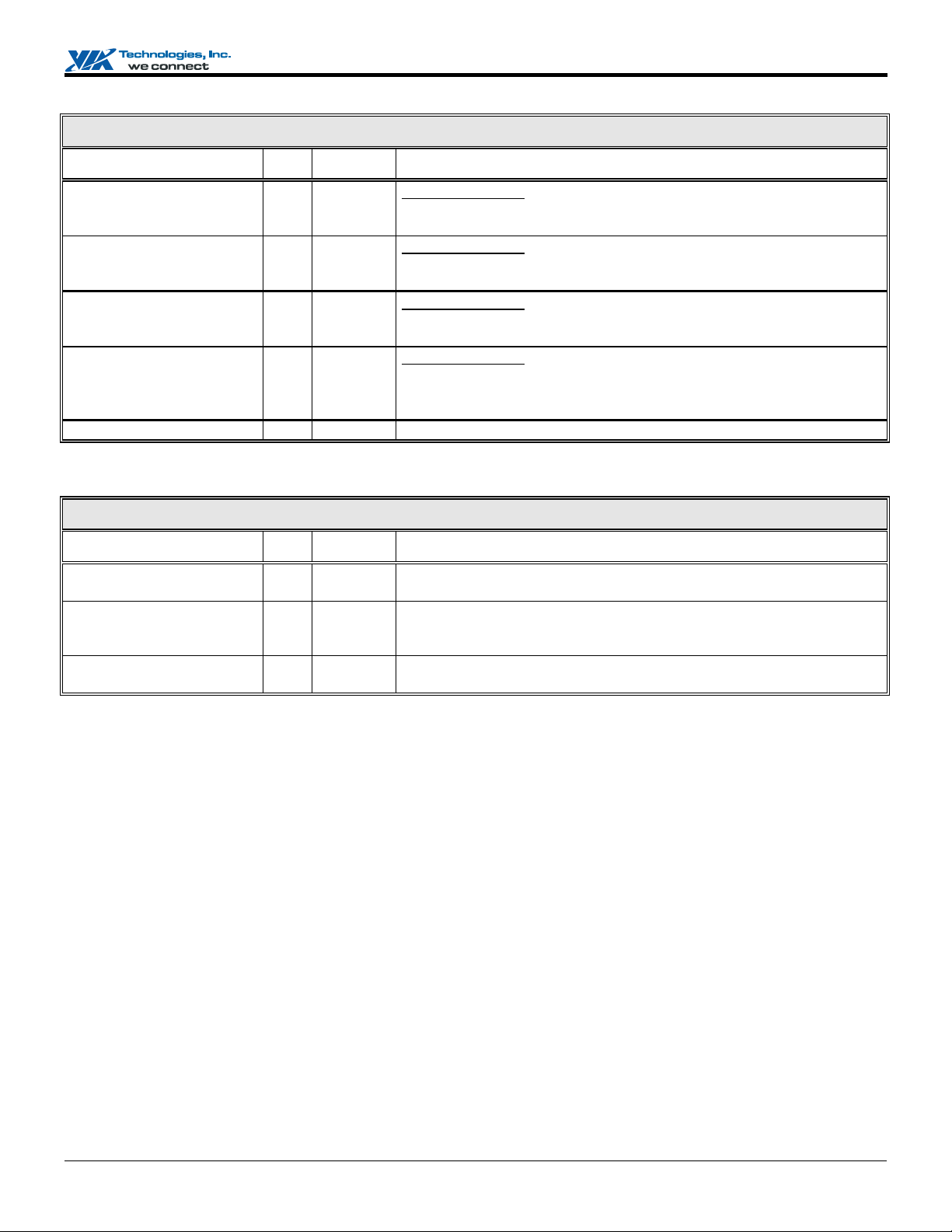

REVISION HISTORY

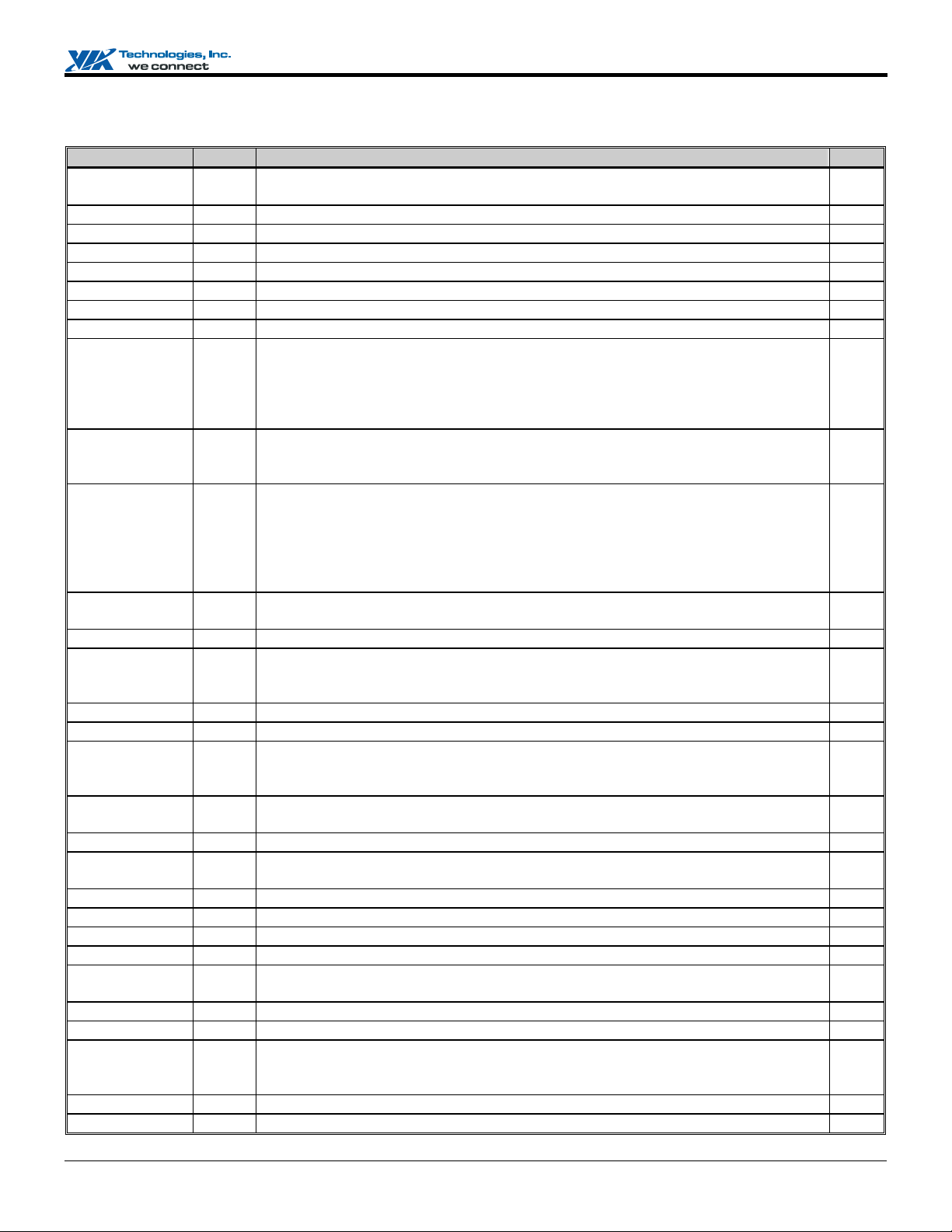

Document Release Date Revision Initials

1.0 5/31/00 Initial public release – removed “NDA Required” watermark

Fixed USBOC2# pin description, F0 Rx40[0], E4[6], PMIO Rx1-0[9], 45[4-0]

1.1 8/1/00 Updated feature bullets, fixed VREF pin direction, updated registers & elec/mech specs DH

1.11 8/22/00 Fixed IDE registers Rx40-45 descriptions and defaults (added Rx42) DH

1.2 11/13/00 Added note to ROMCS# pin description; Updated registers DH

1.3 12/6/00 Removed cover page watermark; Updated pin descriptions, fixed typos DH

1.31 12/11/00 Fixed definition of VCCH and GNDH pins. DH

1.4 1/19/01 Updated copyright notice & table of contents; Fixed pin descriptions and registers DH

1.5 2/1/01 Removed ACSDIN2 & fixed pin descriptions and registers DH

1.6 3/1/01 Removed ATEST and DTEST functions (reserved for internal test purposes)

Fixed GPI10-13 & GPO10-13 pin descriptions and Device 0 F4 RxE5[3-2]

Fixed note under General Purpose Inputs pin description table

Fixed STPCLK# errors in F4 Rx4C[0], PMIO Rx10[9], Rx2C[3]

Changed F5/6 Rx1C-1F to reserved and removed I/O Base 3 registers

1.7 3/19/01 Fixed heading in pin descriptions for UDMA pins

Fixed pin descriptions for JAB1, JBB1, GPI10-13, GPI28-29, GPO8-11

Fixed Device 0 Function 0 Rx40[2], Device 0 Function 4 RxE5[3-2]

1.8 4/30/01 Updated north bridge compatibility list in feature bullets

Added IRQ8# function to GPI1 pin; Added IOCHRDY to LREQ2#/GPI13 pin

Added function summary at beginning of Registers section

Added F0 Rx67[3-2] and added related notes in pin descriptions section

Removed SMB I/O register E;; Removed Temp Reading 3 from HWM I/O registers

Fixed definitions of F1 Rx43[3-0]; 50[28,20,12,4], F4 Rx55[7-6]

1.81 7/2/01 Updated company addresses; Updated Func 0 Rx4C[3:0]

Changed INIT pin to INIT# and added note to pin description

1.82 11/19/01 Fixed LAN Device ID, Elec specs FERR# input voltage; Updated marking specs DH

1.83 2/4/02 Updated logos and legal page formatting; Fixed THRM pin polarity in descriptions

Fixed figure 1 (# of serial ports); Fixed IRRX/IRTX pin descriptions

Fixed register descriptions: Port 71, Func 4 RxE5[5], PMIO Rx4[0]

1.84 2/12/02 Fixed Figure 7 PM Block Diagram to fix pdf print problem; removed “Preliminary” DH

1.85 3/11/02 Updated legal page formatting; Updated JBB1/2 and GPI17 pin descriptions DH

1.9 9/11/02 Removed incorrect register reference from PME# pin description

Fixed Device 0 Func 4 Rx42[4] description; Updated VBAT voltage specs

Added estimated power supply current / power dissipation specs based on test report data

1.91 11/4/02 Updated VIA logos on cover page and page headings to use new VIA corporate logo

Updated LAN Rx74 & added Rx78; fixed typo in electrical specs input voltage table

1.92 11/4/02 Fixed formatting problem in PDF mechanical spec page DH

2.0 11/20/02 Added ACSDIN2-3 functions & removed PCS1#; Updated GPI15, GPIO19 descriptions

Fixed typos in F2-6 Rx0-3; Updated F4 RxE4[5] and E5[7]; Updated LAN registers

2.01 12/19/02 Updated Port 61 (bits 7-6 and 3-2) and Port 92 (bits 7-6 and 3) DH

2.02 2/6/03 Fixed page 51 intro to “Super-I/O/KBC Config Index/Data Regs” step 1 Rx50[2] setting DH

2.1 4/7/03 Fixed EEDI/EEDO pin direction; fixed JEDEC spec reference in mech spec DH

2.2 4/15/03 Updated IDE Rx3C, fixed IDE Rx3D default; fixed IRTX drive DH

2.21 5/22/03 Updated Device 0 Func0 Rx59[3-2], Func4 Rx41[1-0],4C[7-4],4D[6-4], PMIO Rx10[3-0]

Updated electrical specs output pin drive table; Fixed marking specs

2.22 10/2/03 Removed IO Port Port 61 bit 6 and bit 3 VL

2.23 1/6/04 Updated Device 0 Func0 Rx54[3:0] default value VL

2.3 3/16/04 Updated D1F0 Rx6[7:5], 7[7:5], 8[0], 9[0], 0C[4], 0D[1:0], 23-20[7], 43-40[11], 6E[5:3]

and 6F[5:3]

Updated pin name for G13 and G15 in pin diagram and pin descriptons

2.31 5/10/04 Updated Device1 Function 0 Rx8B VL

2.32 9/1/04 Added a lead-free package in Mechanical Specification VL

DH

DH

DH

DH

DH

DH

DH

DH

DH

DH

VL

Revision 2.32, September 1, 2004 -i- Revision History

Page 4

VT8231 South Bridge

TABLE OF CONTENTS

REVISION HISTORY .......................................................................................................................................................................I

TABLE OF CONTENTS.................................................................................................................................................................. II

LIST OF FIGURES .........................................................................................................................................................................IV

LIST OF TABLES ...........................................................................................................................................................................IV

PRODUCT FEATURES.................................................................................................................................................................... 1

OVERVIEW....................................................................................................................................................................................... 5

PINOUTS............................................................................................................................................................................................ 7

PIN DIAGRAM ................................................................................................................................................................................ 7

PIN LISTS ....................................................................................................................................................................................... 8

PIN DESCRIPTIONS....................................................................................................................................................................... 10

REGISTERS..................................................................................................................................................................................... 31

REGISTER OVERVIEW ................................................................................................................................................................. 31

REGISTER DESCRIPTIONS ........................................................................................................................................................... 45

Legacy I/O Ports................................................................................................................................................................... 45

Keyboard Controller I/O Registers........................................................................................................................................................ 46

DMA Controller I/O Registers .............................................................................................................................................................. 48

Interrupt Controller I/O Registers.......................................................................................................................................................... 49

Timer / Counter Registers......................................................................................................................................................................49

CMOS / RTC I/O Registers................................................................................................................................................................... 50

Super-IO / KBC Configuration Index / Data Registers..................................................................................................... 51

Keyboard / Mouse Controller Configuration Registers.................................................................................................... 51

Super-I/O Configuration Registers..................................................................................................................................... 52

Super-I/O I/O Ports.............................................................................................................................................................. 55

Floppy Disk Controller Registers.......................................................................................................................................................... 55

Parallel Port Registers ........................................................................................................................................................................... 56

Serial Port 1 Registers ........................................................................................................................................................................... 57

SoundBlaster Pro Port Registers......................................................................................................................................... 58

FM Registers ......................................................................................................................................................................................... 58

Mixer Registers .....................................................................................................................................................................................58

Sound Processor Registers..................................................................................................................................................................... 58

Game Port Registers............................................................................................................................................................. 59

Fast IR Registers................................................................................................................................................................... 60

PCI Configuration Space I/O .............................................................................................................................................. 67

Device 0 Function 0 Registers - PCI to ISA Bridge ........................................................................................................... 68

PCI Configuration Space Header...........................................................................................................................................................68

ISA Bus Control .................................................................................................................................................................................... 68

PCI Master Arbitration Control............................................................................................................................................................. 70

Miscellaneous Control........................................................................................................................................................................... 71

Function Control.................................................................................................................................................................................... 72

Serial IRQ and PC/PCI DMA Control...................................................................................................................................................72

Plug and Play Control - PCI .................................................................................................................................................................. 73

Miscellaneous Control........................................................................................................................................................................... 74

Programmable Chip Select Control....................................................................................................................................................... 75

Fast IR Control...................................................................................................................................................................................... 75

ISA Decoding Control........................................................................................................................................................................... 76

Device 0 Function 1 Registers - Enhanced IDE Controller............................................................................................... 78

PCI Configuration Space Header...........................................................................................................................................................78

IDE-Controller-Specific Confiiguration Registers ................................................................................................................................ 80

Revision 2.32, September 1, 2004 -ii- Table of Contents

Page 5

VT8231 South Bridge

IDE I/O Registers.................................................................................................................................................................................. 84

Device 0 Function 2 Registers - USB Controller Ports 0-1................................................................................................ 85

PCI Configuration Space Header...........................................................................................................................................................85

USB-Specific Configuration Registers.................................................................................................................................................. 86

USB I/O Registers................................................................................................................................................................................. 87

Device 0 Function 3 Registers - USB Controller Ports 2-3................................................................................................ 88

PCI Configuration Space Header...........................................................................................................................................................88

USB-Specific Configuration Registers.................................................................................................................................................. 89

USB I/O Registers................................................................................................................................................................................. 90

Device 0 Function 4 Regs - Power Management, SMBus and HWM............................................................................... 91

PCI Configuration Space Header...........................................................................................................................................................91

Power Management-Specific PCI Configuration Registers................................................................................................................... 92

Hardware-Monitor-Specific Configuration Registers............................................................................................................................ 99

System Management Bus-Specific Configuration Registers ................................................................................................................. 99

General Purpose I/O Control Registers ............................................................................................................................................... 100

Power Management I/O-Space Registers ............................................................................................................................................ 101

System Management Bus I/O-Space Registers.................................................................................................................................... 110

Hardware Monitor I/O Space Registers............................................................................................................................................... 113

Device 0 Function 5 & 6 Registers - AC97 Audio & Modem Codecs............................................................................. 119

PCI Configuration Space Header – Function 5 Audio......................................................................................................................... 119

PCI Configuration Space Header – Function 6 Modem ......................................................................................................................120

Function 5 & 6 Codec-Specific Configuration Registers ....................................................................................................................121

I/O Base 0 Registers –Audio/Modem Scatter/Gather DMA................................................................................................................ 123

I/O Base 1 Registers – Audio FM NMI Status Registers..................................................................................................................... 127

I/O Base 2 Registers – MIDI / Game Port ........................................................................................................................................... 127

Memory Mapped I/O APIC Registers................................................................................................................................................. 128

Device 1 Function 0 Registers - LAN ................................................................................................................................ 130

PCI Configuration Space Header.........................................................................................................................................................130

LAN-Specific PCI Configuration Registers ........................................................................................................................................ 130

LAN I/O Registers............................................................................................................................................................................... 132

FUNCTIONAL DESCRIPTIONS................................................................................................................................................ 141

POWER MANAGEMENT.............................................................................................................................................................. 141

Power Management Subsystem Overview.......................................................................................................................................... 141

Processor Bus States............................................................................................................................................................................ 141

System Suspend States and Power Plane Control................................................................................................................................ 142

General Purpose I/O Ports................................................................................................................................................................... 142

Power Management Events ................................................................................................................................................................. 143

System and Processor Resume Events................................................................................................................................................. 143

Legacy Power Management Timers .................................................................................................................................................... 144

System Primary and Secondary Events ...............................................................................................................................................144

Peripheral Events................................................................................................................................................................................. 144

ELECTRICAL SPECIFICATIONS ............................................................................................................................................ 145

ABSOLUTE MAXIMUM RATINGS ............................................................................................................................................... 145

DC CHARACTERISTICS ............................................................................................................................................................. 146

POWER CHARACTERISTICS ....................................................................................................................................................... 146

OUTPUT DRIVE .......................................................................................................................................................................... 147

INPUT VOLTAGE ........................................................................................................................................................................ 147

PACKAGE MECHANICAL SPECIFICATIONS...................................................................................................................... 148

Revision 2.32, September 1, 2004 -iii- Table of Contents

Page 6

VT8231 South Bridge

LIST OF FIGURES

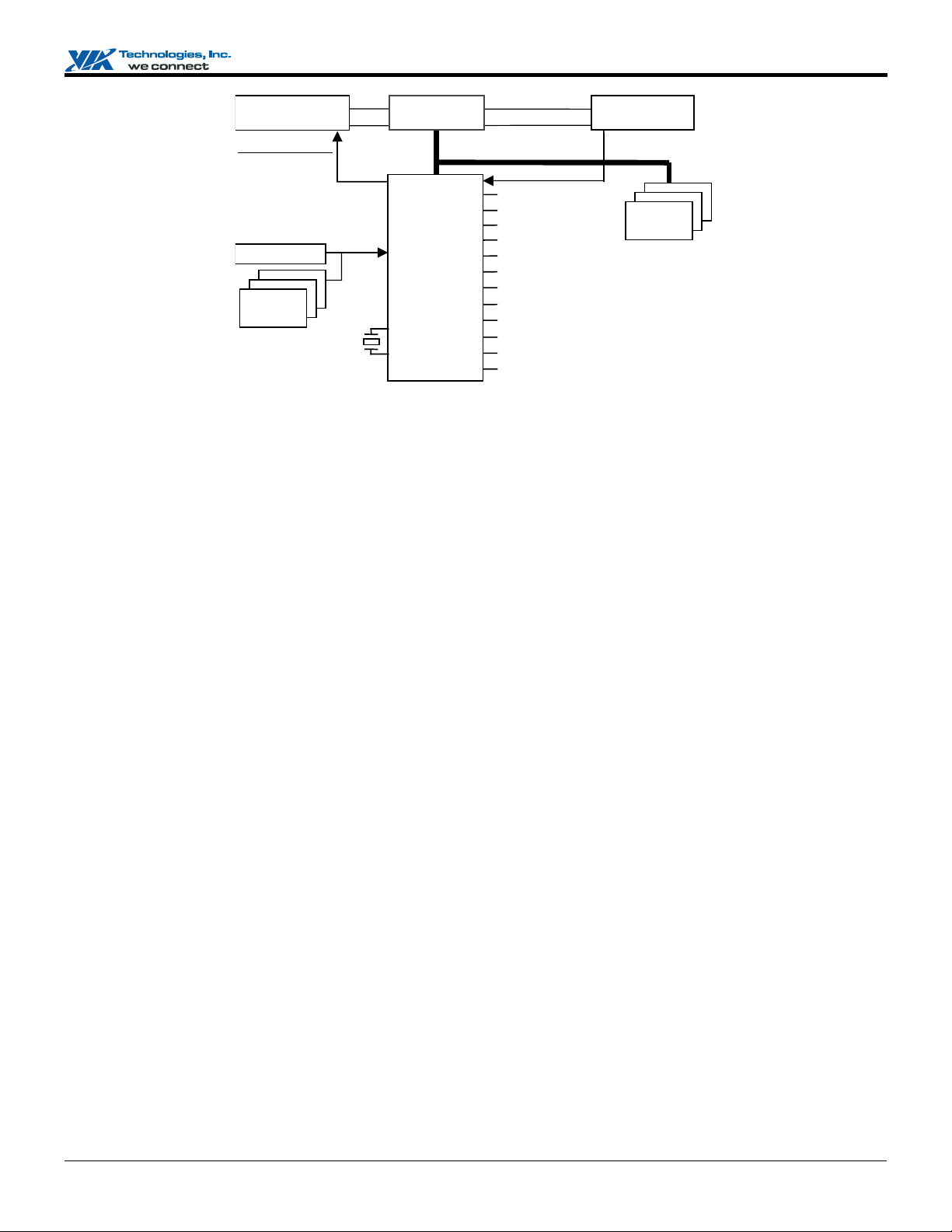

FIGURE 1. PC SYSTEM CONFIGURATION USING THE VT8231 ........................................................................................ 6

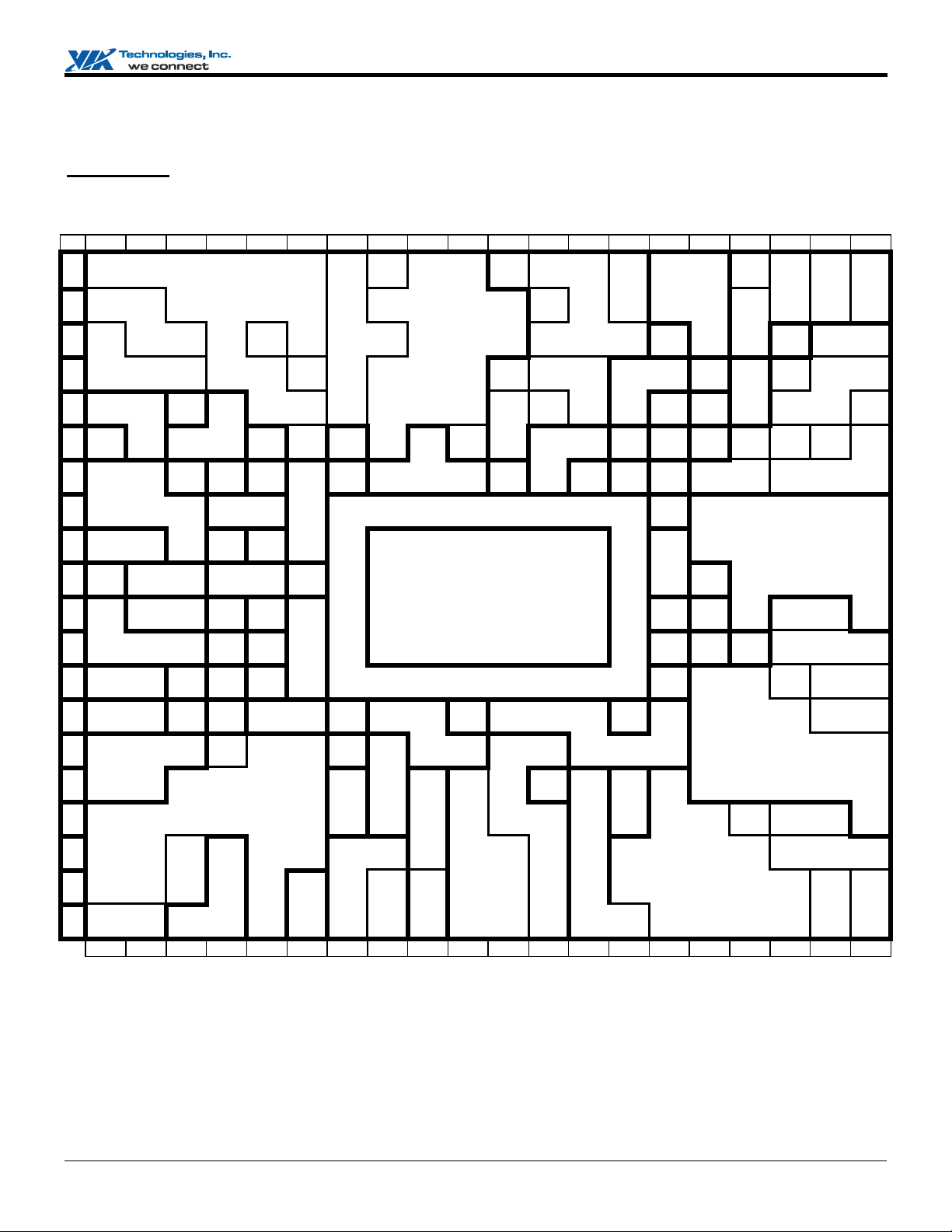

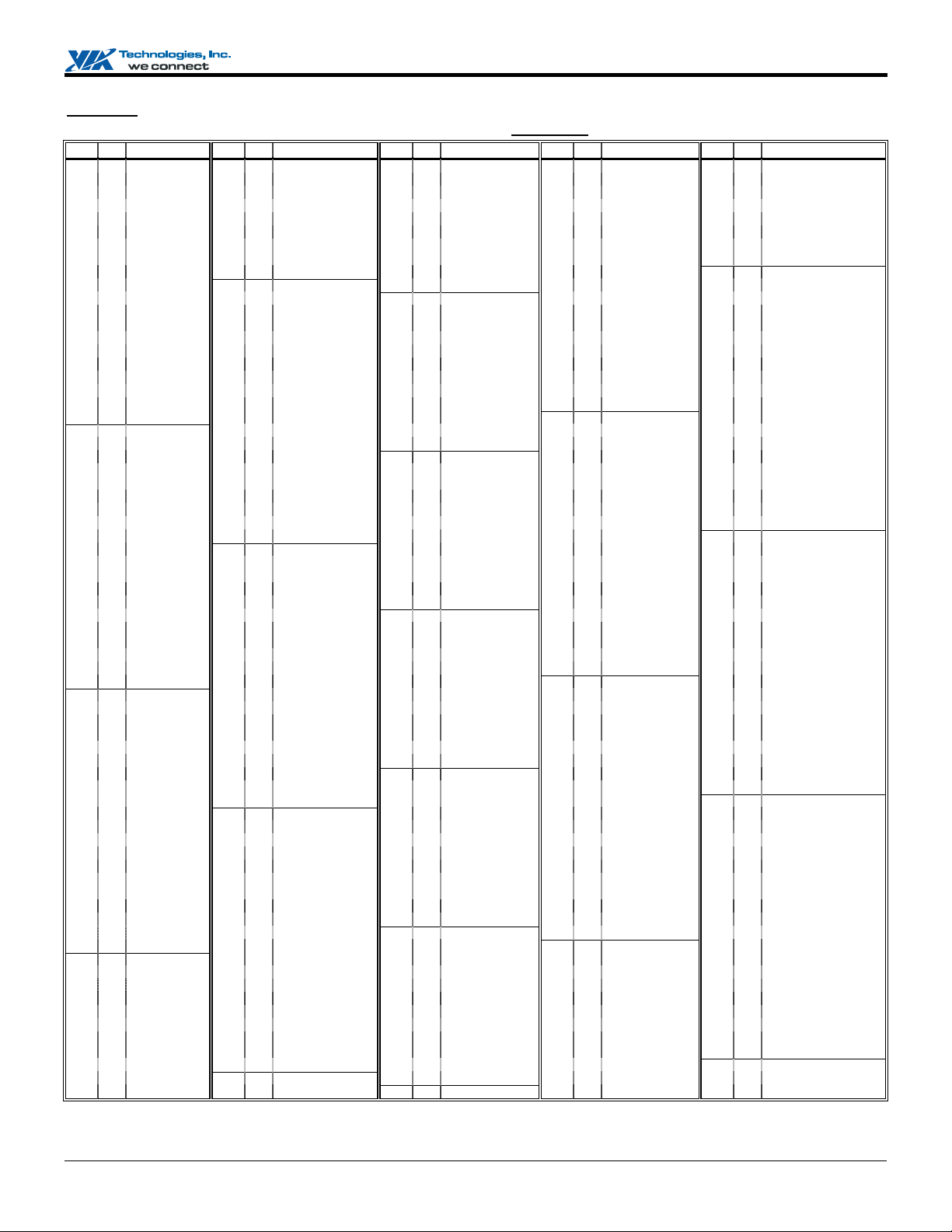

FIGURE 2. VT8231 BALL DIAGRAM (TOP VIEW).................................................................................................................. 7

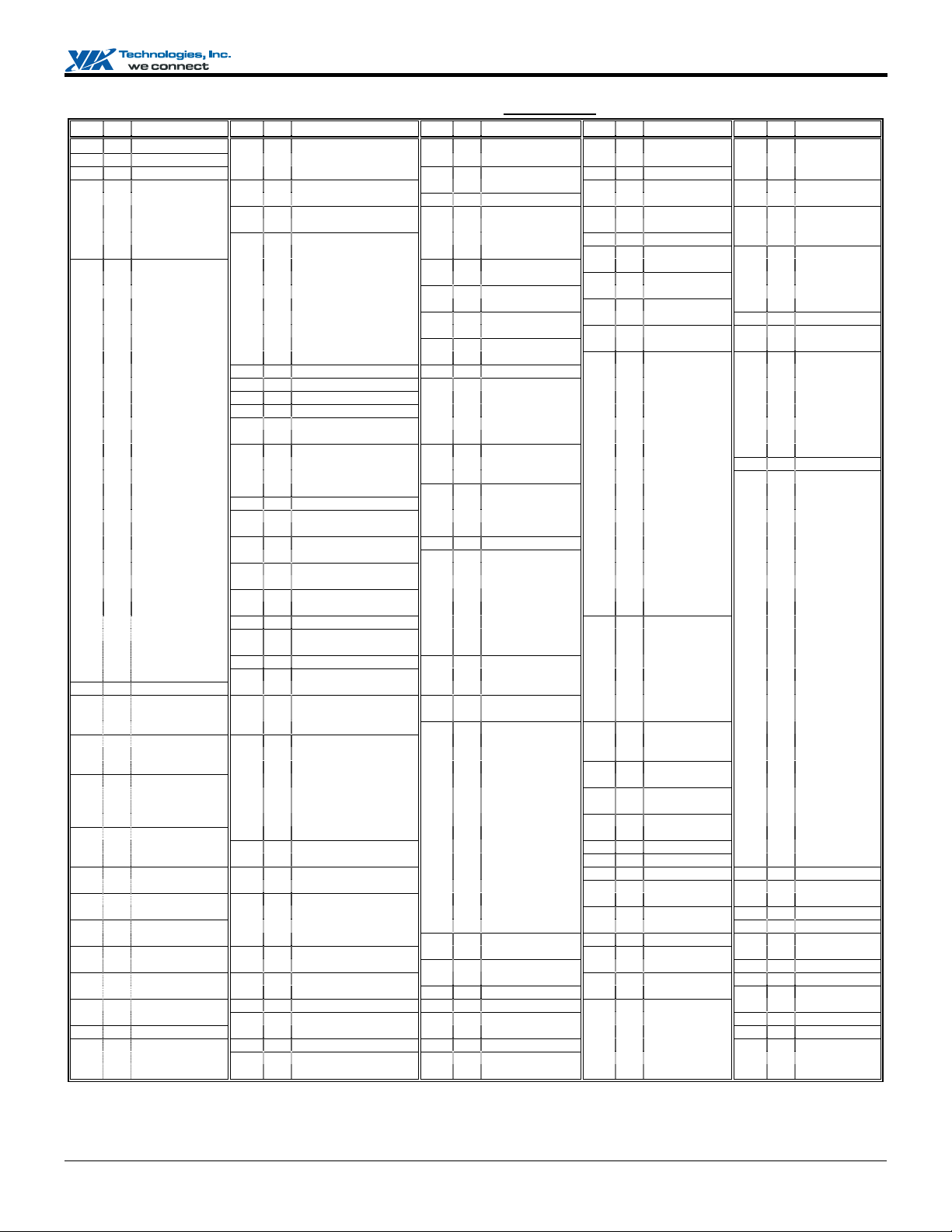

FIGURE 3. VT8231 PIN LIST (NUMERICAL ORDER)............................................................................................................. 8

FIGURE 4. VT8231 PIN LIST (ALPHABETICAL ORDER)...................................................................................................... 9

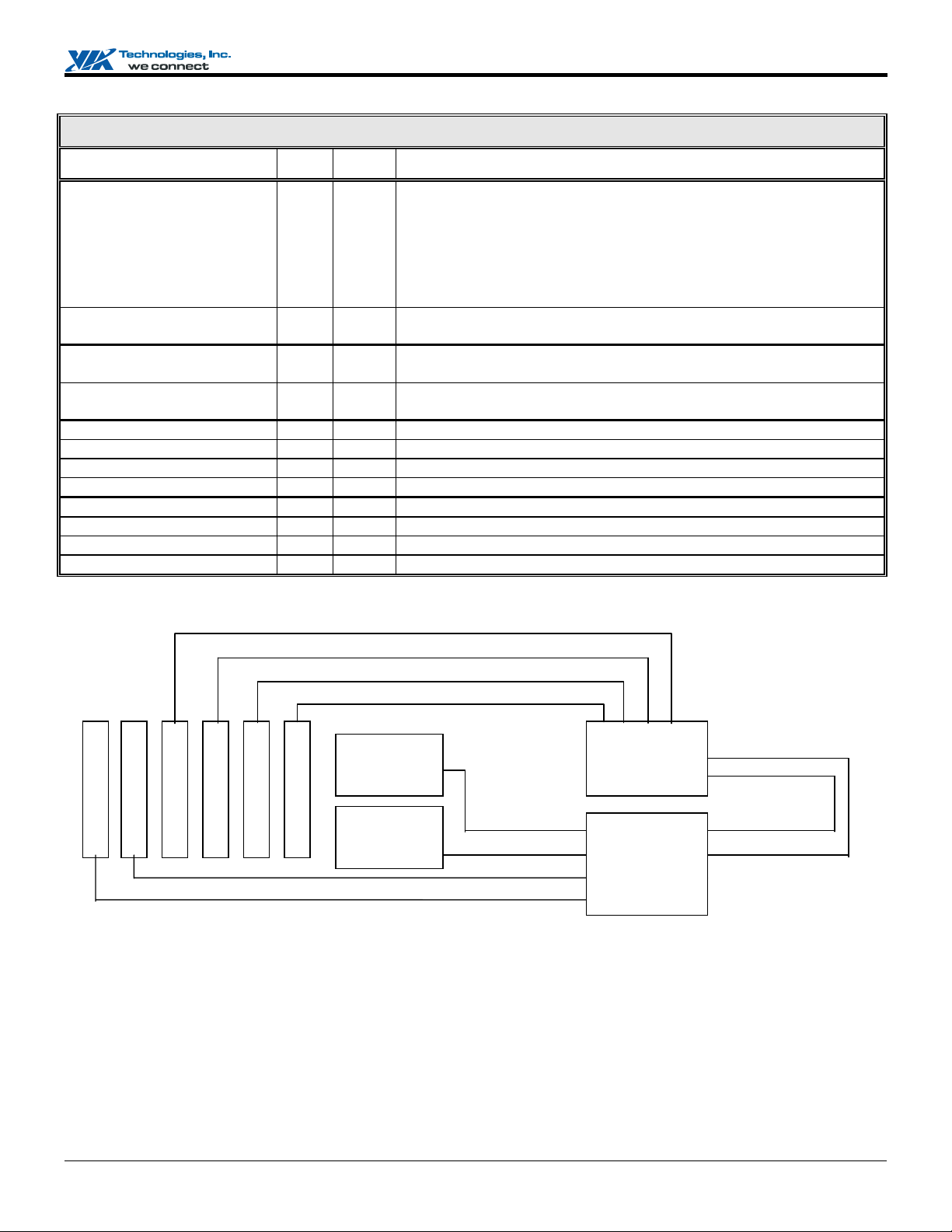

FIGURE 5. PCI REQUEST / GRANT CONNECTIONS USING THE VT8231...................................................................... 11

FIGURE 6. STRAP OPTION CIRCUIT...................................................................................................................................... 13

FIGURE 7. POWER MANAGEMENT SUBSYSTEM BLOCK DIAGRAM......................................................................... 141

FIGURE 9. MECHANICAL SPECIFICATIONS – 376 PIN BALL GRID ARRAY PACKAGE ........................................ 148

LIST OF TABLES

TABLE 1. PIN DESCRIPTIONS .................................................................................................................................................. 10

TABLE 2. MEMORY MAPPED REGISTERS ........................................................................................................................... 31

TABLE 3. FUNCTION SUMMARY............................................................................................................................................. 31

TABLE 4. SYSTEM I/O MAP....................................................................................................................................................... 31

TABLE 5. REGISTERS ................................................................................................................................................................. 32

TABLE 6. KEYBOARD CONTROLLER COMMAND CODES .............................................................................................. 47

TABLE 7. CMOS REGISTER SUMMARY ................................................................................................................................ 50

TABLE 8 - PNP IRQ ROUTING TABLE..................................................................................................................................... 69

TABLE 9 - PNP IRQ ROUTING TABLE..................................................................................................................................... 73

Revision 2.32, September 1, 2004 -iv- Table of Contents

Page 7

VT8231 South Bridge

VT8231

SOUTH BRIDGE

PC99 COMPLIANT

NTEGRATED SUPER-I/O (FDC, LPT, COM, FIR, AND GAME PORT),

I

I

NTEGRATED FAST ETHERNET, LPC, ISA / LPC BIOS ROM,

D

IRECT SOUND AC97 AUDIO AND MC97 MODEM INTERFACE,

NTEGRATED SOUNDBLASTER PRO

I

U

LTRADMA-100/66/33 MASTER MODE EIDE CONTROLLER,

4 P

ORT USB CONTROLLER, KEYBOARD CONTROLLER, RTC,

ERIAL IRQ, SMBUS,

S

P

LUG AND PLAY, ACPI, ENHANCED POWER MANAGEMENT,

T

EMPERATURE, VOLTAGE, AND FAN-SPEED MONITORING

PRODUCT FEATURES

• Inter-operable with VIA and other Host-to-PCI Bridges

− Combine with VT8363A (Apollo KT133A) for a complete Athlon AGP 4x desktop system with 200/266 MHz FSB

− Combine with VT8361 (Apollo KLE133) or VT8365A (Apollo KM133A) for a complete Athlon system with

integrated 2D / 3D graphics

− Combine with VT82C694X (Apollo Pro133A) for a complete 66 / 100 / 133 MHz Socket370 / Slot1 AGP 4x system

− Combine with VT8601A (Apollo PLE133) or VT8605 (Apollo PM133) for a complete Socket370 / Slot1 system

with integrated 2D / 3D graphics

− Combine with VT82C598 (Apollo MVP3) for a complete Super-7 (66 / 75 / 83 / 100 MHz) AGP 2x system

− Combine with VT8501 (Apollo MVP4) for a complete Super-7 system with integrated 2D / 3D graphics

− Inter-operable with Intel or other Host-to-PCI bridges for a complete PC99 compliant PCI / AGP / LPC system

• Integrated Peripheral Controllers

− Integrated Fast Ethernet Controller with 1 / 10 / 100 Mbit capability

− Integrated USB Controller with two root hub and four function ports

− Dual channel UltraDMA-33 / 66 /100 master mode EIDE controller

− AC-link interface for AC-97 audio codec and modem codec

− HSP modem support

− Integrated SoundBlasterPro / DirectSound compatible digital audio controller

− LPC interface for Low Pin Count interface to Super-I/O or ROM

• Integrated Legacy Functions

−

Integrated Keyboard Controller with PS2 mouse support

− Integrated DS12885-style Real Time Clock with extended 256 byte CMOS RAM and Day/Month Alarm for ACPI

− Integrated Bus Controller including DMA, timer, and interrupt controller

− Serial IRQ for docking and non-docking applications

− Flash EPROM, 32Mbit (4Mbyte) EPROM and combined BIOS support

− Fast reset and Gate A20 operation

Revision 2.32, September 1, 2004 -1- Product Features

Page 8

VT8231 South Bridge

• Fast Ethernet Controller

High performance PCI master interface with scatter / gather and bursting capability

−

− Standard MII interface to Ethernet or HomePNA PHYceiver

− 1 / 10 / 100 MHz full and half duplex operation

− Transmit data buffer byte alignment for low CPU utilization

− Separate 2K byte FIFOs for receive and transmit of full Ethernet packets

− Flexible dynamically loadable EEPROM algorithm

− Physical, Broadcast, and Multicast address filtering using hashing function

− Flexible wakeup events: link status change, magic packet, unicast physical address match, predefined pattern match

− Software controllable power down

• UltraDMA-100 / 66 / 33 Master Mode PCI EIDE Controller

− Dual channel master mode PCI supporting four Enhanced IDE devices

− Transfer rate up to 100 MB/sec to cover up to PIO mode 4, multi-word DMA mode 2, and UltraDMA mode 5

− Thirty-two levels (doublewords) of prefetch and write buffers per channel

− Dual DMA engine for concurrent dual channel operation

− Bus master programming interface for SFF-8038i rev.1.0 and Windows-95 / 98 / 2000 compliant

− Full scatter gather capability

− Support ATAPI compliant devices including DVD devices

− Support PCI native and ATA compatibility modes

− Complete software driver support

• Integrated Super IO Controller

− Supports serial port, IR port, parallel port, and floppy disk controller functions

− Serial Port

− Programmable character lengths (5,6,7,8)

− Even, odd, stick or no parity bit generation and detection

− Programmable baud rate generator

− Independent transmit/receiver FIFOs

− Modem Control

− Plug and play with 96 base IO address and 12 IRQ options

− Fast IR (FIR) port

− IrDA 1.0 SIR and IrDA 1.1 FIR compliant

− IR function through the second serial port

− Infrared-IrDA (HPSIR) and ASK (Amplitude Shift Keyed) IR

− Multi-mode parallel port

− Standard mode, ECP and EPP support

− Dynamic and static switch between parallel port pinout and FDC pinout

− Plug and play with 192 base IO address, 12 IRQ and 4 DMA options

− Floppy Disk Controller

− 16 bytes of FIFO

− Data rates up to 1Mbps

− Perpendicular recording driver support

− Two FDDs with drive swap support

− Plug and play with 48 base IO address, 12 IRQ and 4 DMA options

• Low Pin Count (LPC) Bus Interface

Provides connection to external LPC I/O controllers and LPC BIOS ROMs

−

− Enables removal of legacy ISA bus and related pins

− Low pin count interface: two control pins and four address / data pins

Revision 2.32, September 1, 2004 -2- Product Features

Page 9

VT8231 South Bridge

• SoundBlaster Pro Hardware and Direct Sound Ready AC97 Digital Audio Controller

Dual full-duplex Direct Sound channels between system memory and AC97 link

−

− PCI master interface with scatter / gather and bursting capability

− 32 byte FIFO of each direct sound channel

− Host based sample rate converter and mixer

− Standard v1.0 or v2.0 AC97 Codec interface for single or cascaded AC97 Codec’s from multiple vendors

− Loopback capability for re-directing mixed audio streams into USB and 1394 speakers

− Hardware SoundBlaster Pro for Windows DOS box and real-mode DOS legacy compatibility

− Plug and play with 4 IRQ, 4 DMA, and 4 I/O space options for SoundBlaster Pro and MIDI hardware

− Hardware assisted FM synthesis for legacy compatibility

− Direct two game ports and one MIDI port interface

− Complete software driver support for Windows-95/98/2000 and Windows-NT

• MC97 HSP Modem Controller

− PCI bus master interface with scatter / gather and burst capability

− Standard AC97 codec interface for MC or AMC codec

− Wake on ring in APM or ACPI mode through AC97 link

− Supported by most HSP modem vendors

• Universal Serial Bus Controller

− USB v.1.1 and Intel Universal HCI v.1.1 compatible

− Eighteen level (doublewords) data FIFO with full scatter and gather capability

− Root hub and four function ports

− Integrated physical layer transceivers with optional over-current detection status on USB inputs

− Legacy keyboard and PS/2 mouse support

• System Management Bus Interface

− One master / slave SMBus and one slave-only SMBus

− Host interface for processor communications

− Slave interface for external SMBus masters

Revision 2.32, September 1, 2004 -3- Product Features

Page 10

VT8231 South Bridge

• Voltage, Temperature, Fan Speed Monitor and Controller

Five universal input channels for voltage or temperature sensing

−

− Two fan-speed monitoring channels

− Input channel for thermal diode in Intel™ high speed Pentium II™ / Pentium III™ CPUs

− Programmable control, status, monitor and alarm for flexible desktop management

− External thermister or internal bandgap temperature sensing

− Automatic clock throttling with integrated temperature sensing

− Internal core VCC voltage sensing

− Flexible external voltage sensing arrangement (any positive supply and battery)

• Sophisticated PC99-Compatible Mobile Power Management

− Supports both ACPI (Advanced Configuration and Power Interface) and legacy (APM) power management

− ACPI v1.0 Compliant

− APM v1.2 Compliant

− CPU clock throttling and clock stop control for complete ACPI C0 to C3 state support

− PCI bus clock run, Power Management Enable (PME) control, and PCI/CPU clock generator stop control

− Supports multiple system suspend types: power-on suspends with flexible CPU/PCI bus reset options,

suspend to DRAM, and suspend to disk (soft-off), all with hardware automatic wake-up

− Multiple suspend power plane controls and suspend status indicators

− One idle timer, one peripheral timer and one general purpose timer, plus 24/32-bit ACPI compliant timer

− Normal, doze, sleep, suspend and conserve modes

− Global and local device power control

− System event monitoring with two event classes

− Primary and secondary interrupt differentiation for individual channels

− Dedicated input pins for power and sleep buttons, external modem ring indicator, and notebook lid open/close for

system wake-up

− Multiple internal and external SMI sources for flexible power management models

− One programmable chip select and one microcontroller chip select

− Enhanced integrated real time clock (RTC) with date alarm, month alarm, and century field

− Thermal alarm on either external or any combination of three internal temperature sensing circuits

− Hot docking support

− I/O pad leakage control

• Plug and Play Controller

− PCI interrupts steerable to any interrupt channel

− Steerable interrupts for integrated peripheral controllers: USB, floppy, serial, parallel, audio, soundblaster, MIDI

− Steerable DMA channels for integrated floppy, parallel, and soundblaster pro controllers

− One additional steerable interrupt channel for on-board plug and play devices

− Microsoft Windows 2000

BIOS compliant

TM

, Windows 98SETM, Windows 98TM, Windows NTTM, Windows 95

• Built-in NAND-tree pin scan test capability

• 0.30um, 3.3V, low power CMOS process

• Single chip 27x27 mm, 376 pin BGA

TM

and plug and play

Revision 2.32, September 1, 2004 -4- Product Features

Page 11

VT8231 South Bridge

OVERVIEW

The VT8231 South Bridge is a high integration, high performance, power-efficient, and high compatibility device that supports

Intel, AMD, and VIA / Cyrix based processor to PCI bus bridge functionality to make a complete Microsoft PC99-compliant PCI /

LPC system. The VT8231 includes standard intelligent peripheral controllers:

a) Master mode enhanced IDE controller with dual channel DMA engine and interlaced dual channel commands. Dedicated

FIFO coupled with scatter and gather master mode operation allows high performance transfers between PCI and IDE

devices. In addition to standard PIO and DMA mode operation, the VT8231 also supports the UltraDMA-33, 66, and 100

standards to allow reliable data transfer rates up to 100 MB/sec throughput. The IDE controller is SFF-8038i v1.0 and

Microsoft Windows-family compliant.

b) Integrated LAN Fast Ethernet controller (MAC) with Media Independent Interface (MII) to external Ethernet PHY or

HomePNA PHY. The LAN controller operates at 1 / 10 / 100 Mbit/sec transfer rates using either full and half duplex

operation and has separate 2Kbyte FIFOs for receive and transmit of full ethernet packets. The internal high-performance

PCI interface has scatter / gather and bursting capability and can align bytes in the transmit data buffer to reduce CPU

utilization. The LAN interface can perform address filtering on physical, broadcast, and multicast packets. The interface can

also be configured for system wake up on link status change, receipt of magic packet, unicast physical address match on

incoming packets, and predefined pattern match in the incoming data.

c) LPC (Low Pin Count) interface for BIOS ROM plus optional conventional BIOS ROM support

d) Universal Serial Bus controller that is USB v1.1 and Universal HCI v1.1 compliant. The VT8231 includes the root hub with

four function ports with integrated physical layer transceivers. The USB controller allows hot plug and play and isochronous

peripherals to be inserted into the system with universal driver support. The controller also implements legacy keyboard and

mouse support so that legacy software can run transparently in a non-USB-aware operating system environment.

e) Keyboard controller with PS2 mouse support

f) Real Time Clock with 256 byte extended CMOS. In addition to standard RTC functionality, the integrated RTC also

includes the date alarm, century field, and other enhancements for compatibility with the ACPI standard.

g) Notebook-class power management functionality compliant with ACPI and legacy APM requirements. Multiple sleep states

(power-on suspend, suspend-to-DRAM, and suspend-to-Disk) are supported with hardware automatic wake-up. Additional

functionality includes event monitoring, CPU clock throttling and stop (Intel processor protocol), PCI bus clock stop control,

modular power, clock and leakage control, hardware-based and software-based event handling, general purpose I/O, chip

select and external SMI.

h) Hardware monitoring subsystem for managing system / motherboard voltage levels, temperatures, and fan speeds

i) Full System Management Bus (SMBus) interface with one master / slave port and one slave-only port

j) 16550-compatible serial I/O port with “Fast-IR” infrared communications port option.

k) Integrated PCI-mastering dual full-duplex direct-sound AC97-link-compatible sound system. Hardware soundblaster-pro

and hardware-assisted FM blocks are included for Windows DOS box and real-mode DOS compatibility. Loopback

capability is also implemented for directing mixed audio streams into USB and 1394 speakers for high quality digital audio.

l) Game port and MIDI port

m) Standard floppy disk drive interface

n) ECP/EPP-capable parallel port with floppy disk controller pinout option

o) Serial IRQ for docking and non-docking applications

p) Plug and Play controller that allows complete steerability of all PCI interrupts and internal interrupts to any interrupt channel.

One additional steerable interrupt channel is provided to allow plug and play and reconfigurability of on-board peripherals

for Windows family compliance.

Revision 2.32, September 1, 2004 -5- Overview

Page 12

VT8231 South Bridge

CPU / Cache

Sideband Signals:

Init / CPUreset

IRQ / NMI

SMI / StopClk

FERR / IGNNE

SLP# (Slot-1)

Boot ROM

Onboard

LPC I/O

CA

CD

LPC

RTC

Crystal

North Bridge

VT8231

376 BGA

MA/Command

MD

PCI

SMB

USB Ports 0-3

Keyboard / Mouse

MIDI / Game Ports

Parallel Port

Serial Port

Infrared Comm Port

IDE Primary and Secondary

Floppy Disk Interface

AC97 Link

Hardware Monitor Inputs

GPIO, Power Control, Reset

Fast Ethernet Interface

System Memory

DIMM Module ID

Expansion

Cards

Figure 1. PC System Configuration Using the VT8231

Revision 2.32, September 1, 2004 -6- Overview

Page 13

VT8231 South Bridge

PINOUTS

Pin Diagram

Figure 2. VT8231 Ball Diagram (Top View)

Key 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

AD

AD

AD

AD

AD

AD

DEV

CBE

A

30

31

26

24

21

16

SEL#

PINT

PINT

AD

AD

AD

B

B#

A#

28

25

PREQ

PINT

PINT

C

H#

D#

PGNT

PREQ

D

L#

V

E

BAT

JB

F

B1

AC

G

SYNC

AC

H

SDIN0

JA X JB Y AC

J

VREF

K

UIC 5 DTD + DTD - UIC

L

UIC 1 UIC 3 UIC 2 KB

M

KB

N

DT

SUSA

P

#/strap

SMB

R

CK2

SMB

T

DT1

PME#

U

CPU

V

MISS

EXT

W

SMI#

GPIO D GPIO A APIC

Y

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

Note: Some of the pins above have alternate functions and alternate names. The table above contains only one name (usually the most often used function), but the

pin lists and pin descriptions contain all names.

PGNT

L#

PWR

GD

RSM

RST#

AC

RST#

AC

SDIN1

BCLK

FAN 1 FAN2

SLPB#

MS

CK

SUS

B#

SMB

DT2

SMB

ALRT#

LOW#

PWR

BTN#

LID

IRQ8#

SUS

CLK

AD

C#

27

AD

H#

29

RTC

PCI

X1

RST#

INTR

GPI 0 RTC

UDR#

JA

MSI

B1

AC

SUS

C#

AOL

GPI

CK1

BAT

CLK

JB

B2

MSO

JA Y JB

4

CK

MS

DT

CPU

STP#

GPO 0 PCK

PCI

STP#

RST

WSC#

D0

APIC

D1

SDO

SMB

RING # CPU

GPI1

GPIO E APIC

PCS1#

SDIN2

HWM

HWM

RUN#

FERR

AD

23

18 T RDY#

CBE

AD

3#

19 I RDY#

AD

CBE

20

AD

22

X2

JA

B2

GPIO

C

X

GND

VCC

SUS

ST#

VCC

SUS

NMI

#

INIT # STP

A20

M#

SMI#

STOP # AD

2#

AD

SERR # AD

17

FRM#

VCC

GND VCC VCC VCC GND VCC

VCC

VCC

VCC J GND GND GND GND GND GND J VCC

GND K GND GND GND GND GND GND K VCC

VCC L GND GND GND GND GND GND L GND

VCC M GND GND GND GND GND GND M VCC

VCC N7 8 9 10 11 12 13 N14 GND

VCC

SUS

INTR

IGN

NE#

SLP#

CLK# L AD3 L AD0

MCCS

#/strap L AD2 L FRM#

PCS0#

/strap L AD1 L DRQ#

H7 8 9 10 11 12 13 H14 GND

GND VCC VCC GND VCC VCC VCC GND VCC

VCC

IO

W#

IO

R#

AD 9 AD

1#

AD

AD

15

PAR

14

13

AD

11

IR

TX

IR

RX2

IR

RX

AD 4 AD 1 P

10

AD

AD 6 AD 0 PD 1 PD 4 PD 7 USB

12

AD 7 AD 2 PD 0 SLCT

AD 8 AD 3 AUTO

CBE

VCC

VCC VCC

ROM

SPKR

MEM

MEM

CS#

SER

IRQ

R#

W#

0#

HG2#

GPO9

LR1#

GPI12

LG2#

GPO11

LR2#

RDY

LG1#

GPO10

5

ERR#

HR2#

GPI11

HG1#

GPO8

HR1#

STR#

INIT#

FD#

SD 6 SD

SD

7

SD

5

PD 2 PD

6

PD

5

PE DSR# DCD#

IN#

PD

SLCT RXD

3

VCC VCC

GND

LAN

VCC VCC VCC

0

SA17

OSC

/strap

SD

SA

4

18

SA

SD

19

1

LA

SD

20

2

SD

LA

3

21

BUSY RTS# DTR#

ACK# TXD CTS#

RI#

CLK

USB

OC1#

EE

VCC

CK

USB

GND

USB

GND

IRQ

14

IRQ

15

SA5

SDD5

SA9

SDD9

SA16

/strap

VCC

VCC

LAN

SA8

SDD8

SA7

SDD7

SA11

SDD11

SA4

SDD4

SA10

SDD10

VCC

MII

M

CRS M COL

TRK

00#

MTR

1#

VCC

MII

VCC

PLL

GND

PLL

PD

D10

PD

D4

PD

D1

PD

D0

SA6

SDD6

SA2

SDD2

SA12

SDD12

SA3

SDD3

USB

OC0#

USB

P3-

USB

P3+

EE

DO

EE

DI

MTX

CLK

WRT

PRT#

DS

0#

DRV

DEN1

DRV

DEN0

PCI

CLK

PD

D5

PD

D11

PD

D14

PD

D15

SD

DRQ

SA14

SDD14

SA1

SDD1

SA13

SDD13

USB

P0-

USB

P0+

EE

CS#

MD

IO

MRX

D1

MRX

ERR

MTX

D1

DSK

CHG#

STEP#

MTR

0#

PDCS

1#

PD

A1

PD

IOR#

PD

D8

PD

D7

PD

D13

SDCS

1#

SD

A1

SA15

SDD15

SA0

SDD0

USB

USB

P1-

P2-

USB

USB

P1+

P2+

MRX

MD

CLK

CK

MRX

MRX

D3

D2

MRX

MRX

D0

DV

MTX

MTX

ENA

D0

MTX

MTX

D2

D3

HD

R

DATA#

SEL#

W

DATA#W GATE#

DS

DIR#

1#

PDCS

RDY

DRQ

SDCS

IOR#

IOW#

3#

PD

A0

PD

PD

PD

D9

PD

D3

3#

SD

A0

SD

SD

IN

DEX#

PD

A2

PD

DACK#

PD

IOW#

PD

D6

PD

D12

PD

D2

SD

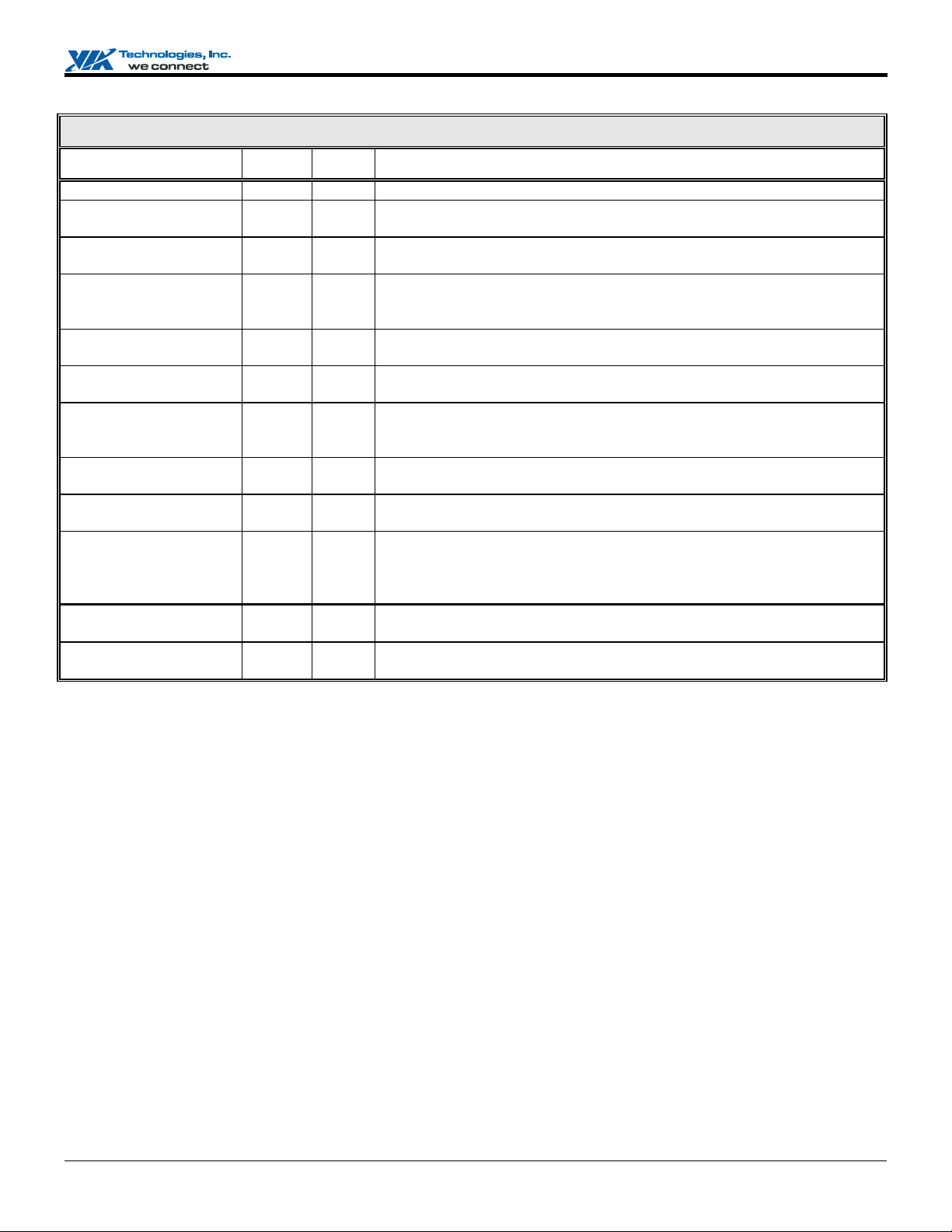

A2

SD

DACK#

SD

RDY

Revision 2.32, September 1, 2004 -7- Pin Diagrams

Page 14

VT8231 South Bridge

Pin Lists

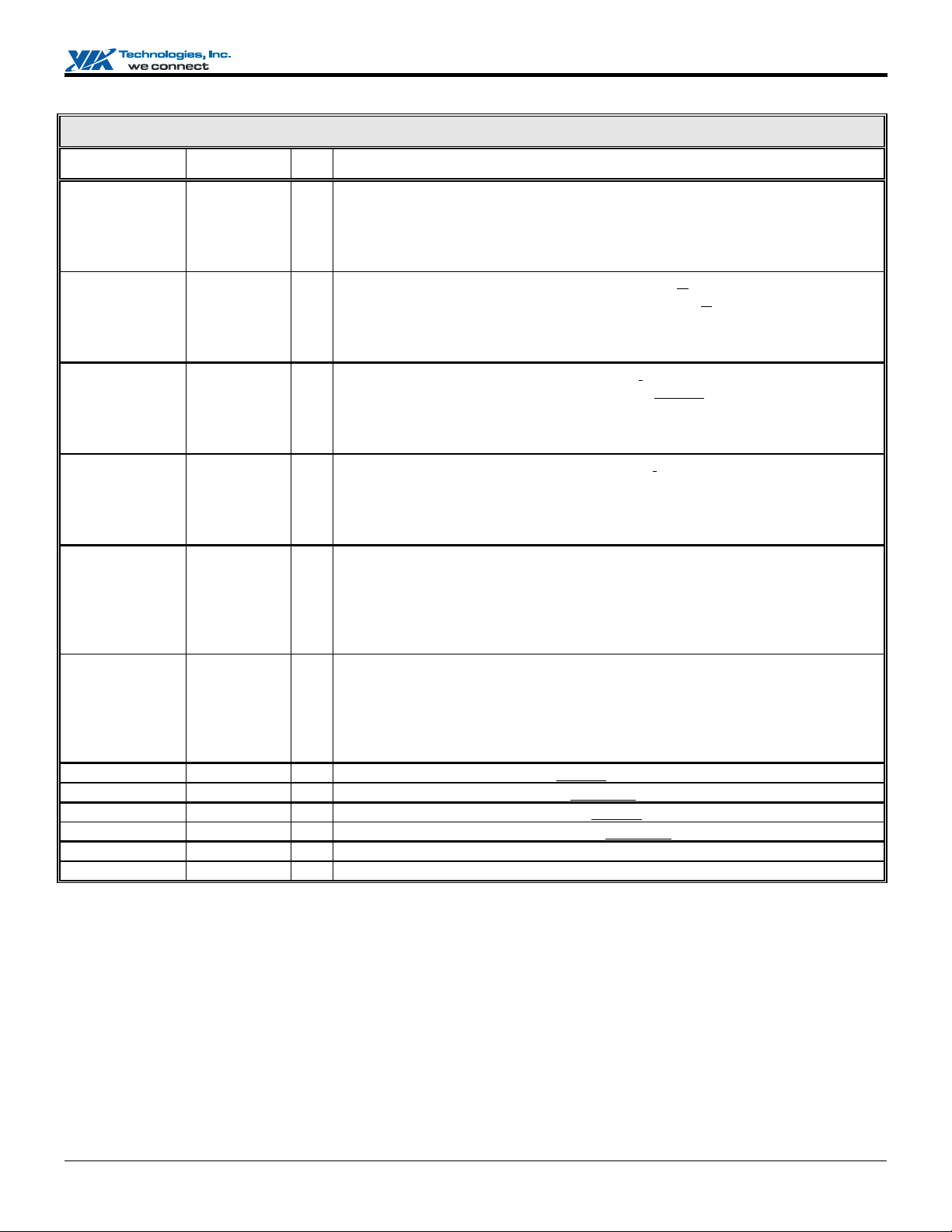

Figure 3. VT8231 Pin List (Numerical Order)

Pin Pin Name Pin Pin Name Pin Pin Name Pin Pin Name Pin Pin Name

A01 IO AD30 D12 IO SLCTIN#/STEP# H03 O ACSDOUT P02 O SUSB# / GPIO2 U13 IO SA18

A02 IO AD31 D13 I PE / WDATA# H04 I JBB2 / GPO13 P03 I AOLGPI/THRM/I17 U14 I IRQ15

A03 IO AD26 D14 I DSR# H05 I JAB2 / GPO12 P04 O CPUSTP# / GPO5 U15 IO SA07 / SDD07

A04 IO AD24 D15 I DCD#

A05 IO AD21 D16 I USBOC1#

A06 IO AD16 D17 I EEDO H16 I TRK00#

A07 IO DEVSEL# D18 IO MDIO H17 I WRTPRT#

A08 IO CBE1# D19 I MRXD3 H18 I DSKCHG#

A09 IO AD09 D20 I MRXD2 H19 O HDSEL#

A10 IO AD05

A11 IO STROBE# E02 I PWRGD J01 I JAX

A12 IO PD2 / WRTPRT# E03 I RTCX1 J02 I JBY

A13 IO PD6 E04 O PCIRST# J03 I ACBITCLK

A14 I BUSY / MTR1# E05 IO AD22 J04 O MSO

A15 O RTS# E06 IO AD17 J05 IO GPIOC/IO25/CHSIO P16 IO PDD04 V07 IO LAD3

A16 O DTR# E07 I SERR#

A17 I USBOC0# E08 IO AD13

A18 IO USBP0- E09 IO AD08 J16 O MTR1# P19 I PDDRQ V10 O LGNT2# / GPO11

A19 IO USBP1- E10 IO AD03 J17 O DS0# P20 O PDIOW# V11 I HREQ2# / GPI11

A20 IO USBP2- E11 IO AUTOFD#/DRV0 J18 O STEP# R01 IO SMBCK2 / GPIO27 V12 IO SD01

B01 I PINTB# E12 IO PD3 / RDATA# J19 O WDATA# R02 IO SMBDT2 / GPIO26 V13 IO SA19

B02 I PINTA# E13 I SLCT/WGATE# J20 O WGATE# R03 IO SMBCK1 V14 IO SA05 / SDD05

B03 IO AD28 E14 I RXD

B04 IO AD25

B05 IO AD23 E16 O EECK K03 I FAN2/SLPB#/IO18 R06 OD INTR V17 IO SA14 / SDD14

B06 IO AD18 E17 O EEDI K04 I JAY

B07 IO TRDY# E18 I MRXD1 K05 I JBX R08 O IRTX / GPO14 V19 O SDA0

B08 IO AD15 E19 I MRXD0

B09 IO AD10 E20 I MRXDV

B10 IO AD04 F01 I JBB1 / GPI29

B11 IO AD01 F02 I RSMRST# K17 O DRVDEN1 R12 IO SD00 W03 IO GPIOE / GPIO31

B12 IO PINIT# / DIR# F03 I INTRUDER#/GPI8 K18 O MTR0#

B13 IO PD5 F04 I GPI0 K19 O DS1#

B14 I ACK# / DS1# F05 O RTCX2 K20 O DIR#

B15 O TXD F06 IO FRAME# L01 AI UIC5 R16 IO PDD01 W07 IO LAD2

B16 I CTS#

B17 IO USBP3- F08 IO AD11 L03 AI DTD- R18 IO PDD07 W09 IO MEMR#

B18 IO USBP0+

B19 IO USBP1+ F10 IO CBE0#

B20 IO USBP2+ F11 I ERROR#/HDSEL#

C01 O PREQH#

C02 I PINTD#

C03 I PINTC#

C04 IO AD27

C05 IO CBE3#

C06 IO AD19 F17 I MTXCLK L20 I INDEX# T07 IO IOW# / GPIO23 W18 IO SA15 / SDD15

C07 IO IRDY# F18 I MRXERR M01 AI UIC1 T08 I IRRX2 / GPIOB W19 O SDIOR#

C08 IO PAR F19 O MTXENA M02 AI UIC3 T09 O ROMCS# / KBCS# W20 O SDDACK#

C09 IO AD12 F20 O MTXD0 M03 AI UIC2 T10 O HGNT2# / GPO9 Y01 IO GPIOD / GPIO30

C10 IO AD06 G01 O ACSYNC M04 IO KBCK / A20G T11 IO SD07 Y02 IO GPIOA / GPIO24

C11 IO AD00 G02 O ACRST#

C12 IO PD1 / TRK00# G03 I JAB1 / GPI28

C13 IO PD4 / DSKCHG# G04 I MSI

C14 IO PD7 G05 O ACSDIN2 / GPIO19

C15 I USBCLK

C16 I RI#

C17 IO USBP3+

C18 O EECS#

C19 I MRXCLK

C20 O MDCK

D01 I PGNTL#

D02 O PREQL#

D03 I PGNTH#

D04 IO AD29

D05 IO AD20 G16 I MCRS

D06 IO CBE2# G17 I MCOL N16 IO PDD10 U07 IO IOR# / GPIO22 Y18 IO SA00 / SDD00

D07 IO STOP# G18 O MTXD1 N17 IO PDD05 U08 I IRRX / GPO15 Y19 O SDIOW#

D08 IO AD14 G19 O MTXD2 N18 O PDIOR# U09 O SPKR Y20 I SDRDY

D09 IO AD07 G20 O MTXD3 N19 I PDRDY U10 I LREQ1# / GPI12

D10 IO AD02 H01 I ACSDIN0 N20 O PDDACK# U11 IO SD05

D11 IO PD0 / INDEX# H02 I ACSDIN1 P01 O SUSA#/GPO1/strapU12 IO SD04

E01 P VBAT

E15 P VCCUSB

F07 P VCC

F09 P VCC

F12 P VCC L15 P GND

F13 P VCC L16 P VCCPLL

F14 P GNDUSB

F15 P VCC

F16 P VCCMII

G06 P VCC

G07 P GND

G08 P VCC

G09 P VCC

G10 P VCC

G11 P GND

G12 P VCC

G13 P GNDLAN

G14 P GND

G15 P VCCLAN N06 P VCC

H06 P VCC P05 P VCCSUS

H15 P GND P06 P VCCSUS

H20 I RDATA#

J06 P VCC

J15 P VCC

K01 O VREF

K02 I FAN1 R05 IO PCKRUN# V16 IO SA02 / SDD02

K06 P GND R09 P VCC

K15 P VCC R10 P VCC

K16 P VCCMII

L02 AI DTD+ R17 IO PDD14 W08 O LFRAME#

L04 AI UIC4 R19 IO PDD09 W10 I LREQ2#/GPI13/OCHRDY

L05 P GNDHWM

L06 P VCC

L17 O DRVDEN0 T04 O PCISTP# / GPO6 W15 IO SA04 / SDD04

L18 O PDCS1# T05 OD NMI W16 IO SA12 / SDD12

L19 O PDCS3# T06 OD IGNNE# W17 IO SA01 / SDD01

M05 P VCCHWM

M06 P VCC

M15 P VCC

M16 P GNDPLL

M17 I PCICLK T16 IO PDD00 Y07 IO LAD1

M18 O PDA1 T17 IO PDD15 Y08 I LDRQ# / GPI15 / SDIN3

M19 O PDA0 T18 IO PDD13 Y09 IO MEMW#

M20 O PDA2 T19 IO PDD03 Y10 O LGNT1# / GPO10

N01 IO KBDT / KBRC T20 IO PDD12 Y11 I HREQ1# / GPI10

N02 IO MSCK / IRQ1 U01 I PME# / GPI6 Y12 IO SD03

N03 O SUSC# / GPO U02 I PWRBTN# Y13 IO LA21/OC3#/IO21

N04 IO MSDT / IRQ12 U03 I RING# / GPI3 Y14 IO SA16 / strap

N05 O SUSST1# / GPO3 U04 OD CPURST Y15 IO SA10 / SDD10

N15 P GND

P07 P GND

P08 P VCC

P09 P VCC

P10 P GND

P11 P VCC

P12 P VCC

P13 P VCC

P14 P GND

P15 P VCC

P17 IO PDD11 V08 IO LAD0

P18 IO PDD08 V09 I SERIRQ

R04 O SLOWCLK / O0 V15 IO SA11 / SDD11

R07 P VCC

R11 IO SD06 W02 O SUSCLK / GPO4

R13 P VCC

R14 P VCC

R15 P VCC

R20 IO PDD06 W11 O HGNT1# / GPO8

T01 IO SMBDT1 W12 IO SD02

T02 I SMBALRT# / GPI7 W13 IO LA20/OC2#/IO20

T03 I BATLOW# / GPI5 W14 IO SA09 / SDD09

T12 I OSC Y03 I APICCLK / GPI9

T13 IO SA17 / strap Y04 O APICD1 / GPO29

T14 I IRQ14 Y05 OD SMI#

T15 IO SA08 / SDD08 Y06 O PCS# / GPO16

U05 I FERR# Y16 IO SA03 / SDD03

U06 OD SLP# / GPO7 Y17 IO SA13 / SDD13

Center GND pins (24 pins): J8-J13, K8-K13, L8-L13, M8-M13

U16 IO SA06 / SDD06

U17 I SDDRQ

U18 O SDCS1#

U19 O SDCS3#

U20 IO PDD02

V01 I CPUMISS / GPI16

V02 I LID / GPI4

V03 I GPI1 / IRQ8#

V04 I WSC# / GPI24

V05 OD INIT#

V06 OD STPCLK#

V18 O SDA1

V20 O SDA2

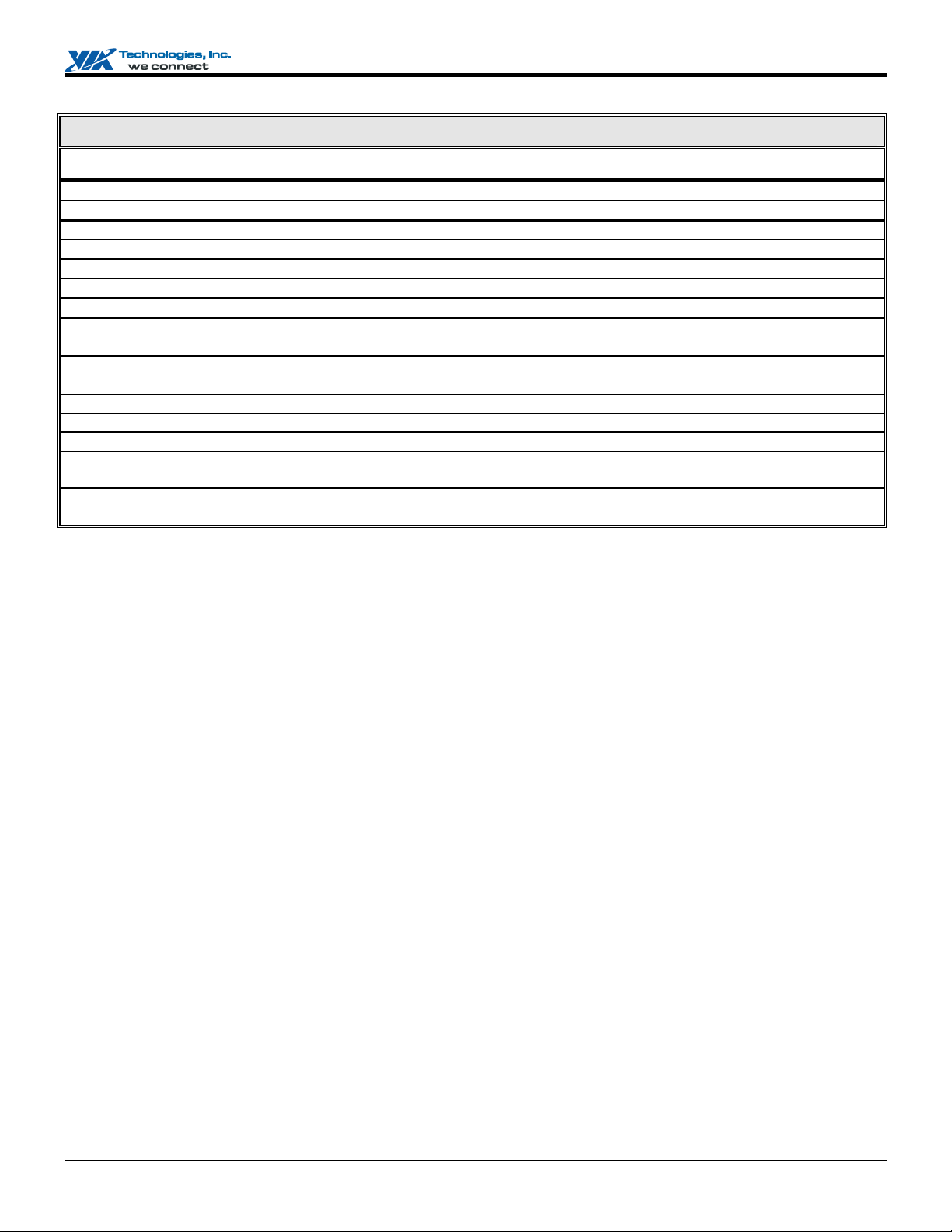

W01 IOD EXTSMI# / GPI2

W04 O APICD0 / GPIO28

W05 OD A20M#

W06 O MCCS#/O17/strap

Revision 2.32, September 1, 2004 -8- Pin Lists

Page 15

VT8231 South Bridge

K

K

K

K

K

K

Q

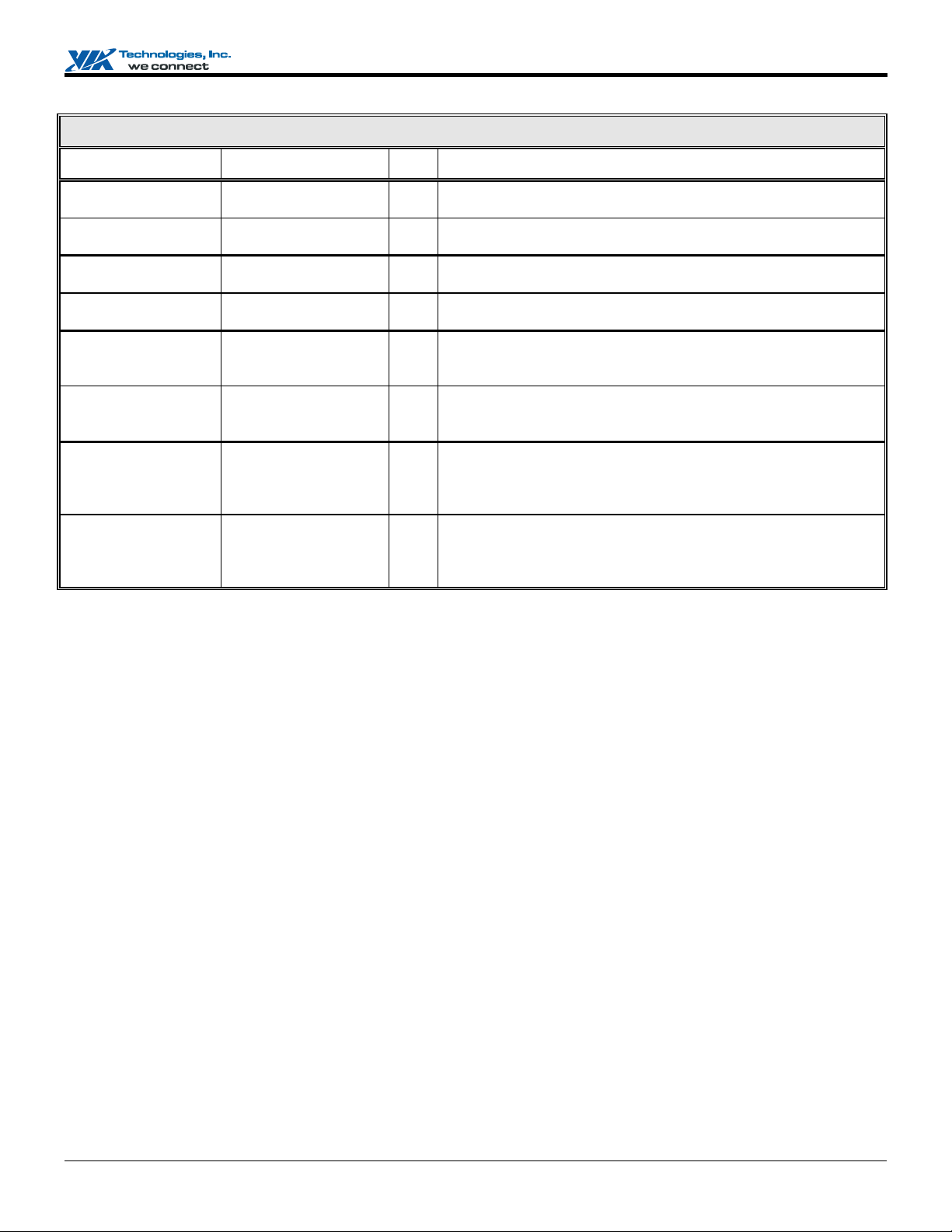

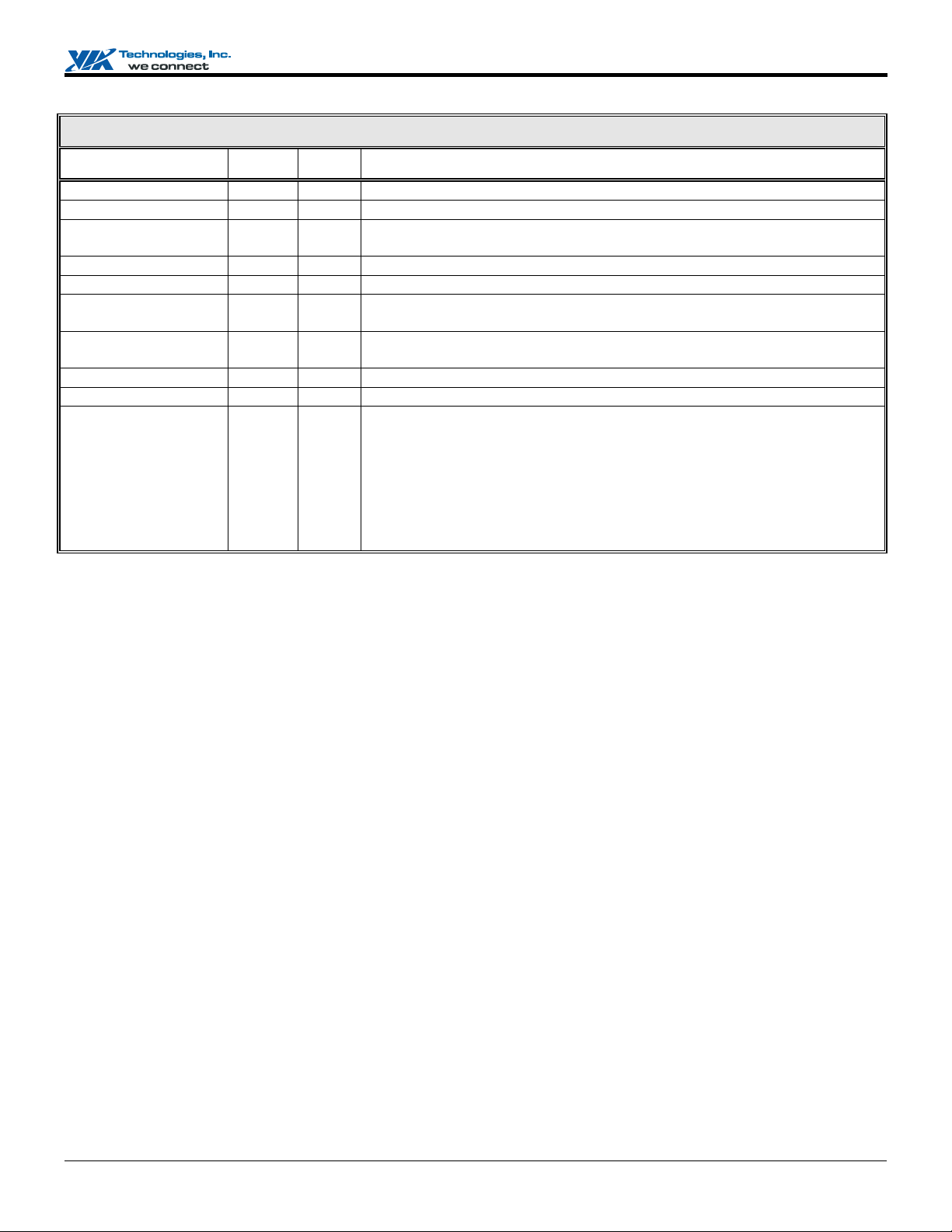

Figure 4. VT8231 Pin List (Alphabetical Order)

Pin Pin Name Pin Pin Name Pin Pin Name Pin Pin Name Pin Pin Name

W05 OD A20M# D17 I EEDO C20 O MDCK C03 I PINTC# P01 O SUSA# / GPO1

J03 I ACBITCLK F11 I ERROR#/HDSEL# D18 IO MDIO C02 I PINTD# P02 O SUSB# / GPO2

B14 I ACK# / DS1# W01 IOD EXTSMI# / GPI2 W09 IO MEMR# U01 I PME# / GPI6 N03 O SUSC#

G02 O ACRST# K02 I FAN1 Y09 IO MEMW# C01 O PREQH# W02 O SUSCL

H01 I ACSDIN0 K03 I FAN2/SLPB#/IO18 C19 I MRXCL

H02 I ACSDIN1 U05 I FERR# E19 I MRXD0 U02 I PWRBTN# B07 IO TRDY#

G05 O ACSDIN2 / GPIO19 F06 IO FRAME# E18 I MRXD1 E02 I PWRGD H16 I TRK00#

H03 O ACSDOUT

G01 O ACSYNC

C11 IO AD00

B11 IO AD01

D10 IO AD02

E10 IO AD03

B10 IO AD04

A10 IO AD05

C10 IO AD06

D09 IO AD07

E09 IO AD08

A09 IO AD09

B09 IO AD10

F08 IO AD11

C09 IO AD12 F04 I GPI0 G20 O MTXD3 V14 IO SA05 / SDD05 B20 IO USBP2+

E08 IO AD13 V03 I GPI1 / IRQ8# F19 O MTXENA U16 IO SA06 / SDD06 B17 IO USBP3D08 IO AD14 Y02 IO GPIOA / GPIO24 T05 OD NMI U15 IO SA07 / SDD07 C17 IO USBP3+

B08 IO AD15 J05 IO GPIOC / GPIO25 T12 I OSC T15 IO SA08 / SDD08

A06 IO AD16 Y01 IO GPIOD / GPIO30 C08 IO PAR W14 IO SA09 / SDD09

E06 IO AD17 W03 IO GPIOE R05 IO PCKRUN# Y15 IO SA10 / SDD10

B06 IO AD18 H19 O HDSEL# M17 I PCICL

C06 IO AD19 W11 O HGNT1# / GPO8 E04 O PCIRST# W16 IO SA12 / SDD12

D05 IO AD20 T10 O HGNT2# / GPO9 T04 O PCISTP# / GPO6 Y17 IO SA13 / SDD13

A05 IO AD21 Y11 I HREQ1# / GPI10 Y06 O PCS# / GPO16 V17 IO SA14 / SDD14

E05 IO AD22 V11 I HREQ2# / GPI11 D11 IO PD0 / INDEX# W18 IO SA15 / SDD15

B05 IO AD23 T06 OD IGNNE# C12 IO PD1 / TRK00# Y14 IO SA16 / strap

A04 IO AD24 L20 I INDEX# A12 IO PD2 / WRTPRT# T13 IO SA17 / strap

B04 IO AD25 V05 OD INIT# E12 IO PD3 / RDATA# U13 IO SA18

A03 IO AD26 R06 OD INTR C13 IO PD4 / DSKCHG# V13 IO SA19

C04 IO AD27 F03 I INTRUDER#/GPI8 B13 IO PD5 R12 IO SD00

B03 IO AD28 U07 IO IOR# / GPIO22 A13 IO PD6 V12 IO SD01

D04 IO AD29 T07 IO IOW# / GPIO23 C14 IO PD7 W12 IO SD02

A01 IO AD30 C07 IO IRDY# M19 O PDA0 Y12 IO SD03

A02 IO AD31 T14 I IRQ14 M18 O PDA1 U12 IO SD04

P03 I AOLGPI/THRM/I17 U14 I IRQ15 M20 O PDA2 U11 IO SD05

Y03 O APICLK / GPI9 U08 I IRRX / GPO15 L18 O PDCS1# R11 IO SD06

W04 O APICD0 / GPIO28 T08 I IRRX2 / GPIOB L19 O PDCS3# T11 IO SD07

Y04 O APICD1 / GPIO29 R08 O IRTX / GPO14 T16 IO PDD00 V19 O SDA0

E11 IO AUTOFD# / DRV0 G03 I JAB1 / GPI28 R16 IO PDD01 V18 O SDA1

T03 I BATLOW# / GPI5 H05 I JAB2 / GPO12 U20 IO PDD02 V20 O SDA2

A14 I BUSY / MTR1# J01 I JAX T19 IO PDD03 U18 O SDCS1#

F10 IO CBE0# K04 I JAY P16 IO PDD04 U19 O SDCS3#

A08 IO CBE1# F01 I JBB1 / GPI29 N17 IO PDD05 W20 O SDDACK#

D06 IO CBE2# H04 I JBB2 / GPO13 R20 IO PDD06 U17 I SDDRQ

C05 IO CBE3# K05 I JBX R18 IO PDD07 W19 O SDIOR#

V01 I CPUMISS / GPI16 J02 I JBY P18 IO PDD08 Y19 O SDIOW#

U04 OD CPURST M04 IO KBCK / A20G R19 IO PDD09 Y20 I SDRDY

P04 O CPUSTP# / GPO5 N01 IO KBDT / KBRC N16 IO PDD10 V09 I SERIRQ

B16 I CTS# W13 IO LA20 / OC2# / GPIO20 P17 IO PDD11 E07 I SERR#

D15 I DCD# Y13 IO LA21 / OC3# / GPIO21 T20 IO PDD12 E13 I SLCT/WGATE#

A07 IO DEVSEL# V08 IO LAD0 T18 IO PDD13 D12 IO SLCTIN#/STEP#

K20 O DIR# Y07 IO LAD1 R17 IO PDD14 R04 O SLOWCLK / O0

L17 O DRVDEN0 W07 IO LAD2 T17 IO PDD15 U06 OD SLP# / GPO7

K17 O DRVDEN1 V07 IO LAD3 N20 O PDDACK# T02 I SMBALRT# / I7

J17 O DS0# Y08 I LDRQ#/ / GPI15 / SDIN3 P19 I PDDR

K19 O DS1# W08 O LFRAME# N18 O PDIOR# R01 IO SMBCK2 / IO27

H18 I DSKCHG# Y10 O LGNT1# / GPO10 P20 O PDIOW# T01 IO SMBDT1

D14 I DSR# V10 O LGNT2# / GPO11 N19 I PDRDY R02 IO SMBDT2 / IO26 J19 O WDATA#

L02 AI DTD+ V02 I LID / GPI4 D13 I PE / WDATA# Y05 OD SMI# J20 O WGATE#

L03 AI DTD– U10 I LREQ1# / GPI12 D03 I PGNTH# U09 O SPKR H17 I WRTPRT#

A16 O DTR# W10 I LREQ2#/GPI13/IOCHRD D01 I PGNTL# J18 O STEP# V04 I WSC# / GPI14

E16 O EECK W06 O MCCS#/O17/strap B12 IO PINIT# / DIR# D07 IO STOP#

C18 O EECS# G17 I MCOL B02 I PINTA# V06 OD STPCLK#

E17 O EEDI G16 I MCRS B01 I PINTB# A11 IO STROBE#

G07 P GND

G11 P GND

G14 P GND

H15 P GND

K06 P GND

L15 P GND

N15 P GND

P07 P GND

P10 P GND

P14 P GND

L05 P GNDHWM

M16 P GNDPLL

G13 P GNDLAN

F14 P GNDUSB

D20 I MRXD2 H20 I RDATA# B15 O TXD

D19 I MRXD3 C16 I RI# M01 I UIC1

E20 I MRXDV U03 I RING# / GPI3 M03 I UIC2

F18 I MRXERR T09 O ROMCS#/KBCS# M02 I UIC3

N02 IO MSCK / IRQ1 F02 I RSMRST# L04 I UIC4

N04 IO MSDT / IRQ12 E03 I RTCX1 L01 I UIC5

G04 I MSI F05 O RTCX2 C15 I USBCL

J04 O MSO A15 O RTS# A17 I USBOC0#

18 O MTR0# E14 I RXD D16 I USBOC1#

J16 O MTR1# Y18 IO SA00 / SDD00 A18 IO USBP0F17 I MTXCL

F20 O MTXD0 V16 IO SA02 / SDD02 A19 IO USBP1G18 O MTXD1 Y16 IO SA03 / SDD03 B19 IO USBP1+

G19 O MTXD2 W15 IO SA04 / SDD04 A20 IO USBP2-

Center GND pins (24 pins): J8-J13, K8-K13, L8-L13, M8-M13

D02 O PREQL# N05 O SUSST1# / GPO3

W17 IO SA01 / SDD01 B18 IO USBP0+

E01 P VBAT

F07 P VCC

V15 IO SA11 / SDD11

R03 IO SMBCK1

F09 P VCC

F12 P VCC

F13 P VCC

F15 P VCC

G06 P VCC

G08 P VCC

G09 P VCC

G10 P VCC

G12 P VCC

H06 P VCC

J06 P VCC

J15 P VCC

K15 P VCC

L06 P VCC

M06 P VCC

M15 P VCC

N06 P VCC

P08 P VCC

P09 P VCC

P11 P VCC

P12 P VCC

P13 P VCC

P15 P VCC

R07 P VCC

R09 P VCC

R10 P VCC

R13 P VCC

R14 P VCC

R15 P VCC

M05 P VCCHWM

F16 P VCCMII

K16 P VCCMII

L16 P VCCPLL

G15 P VCCLAN

P05 P VCCSUS

P06 P VCCSUS

E15 P VCCUSB

K01 O VREF

Revision 2.32, September 1, 2004 -9- Pin Lists

Page 16

VT8231 South Bridge

Pin Descriptions

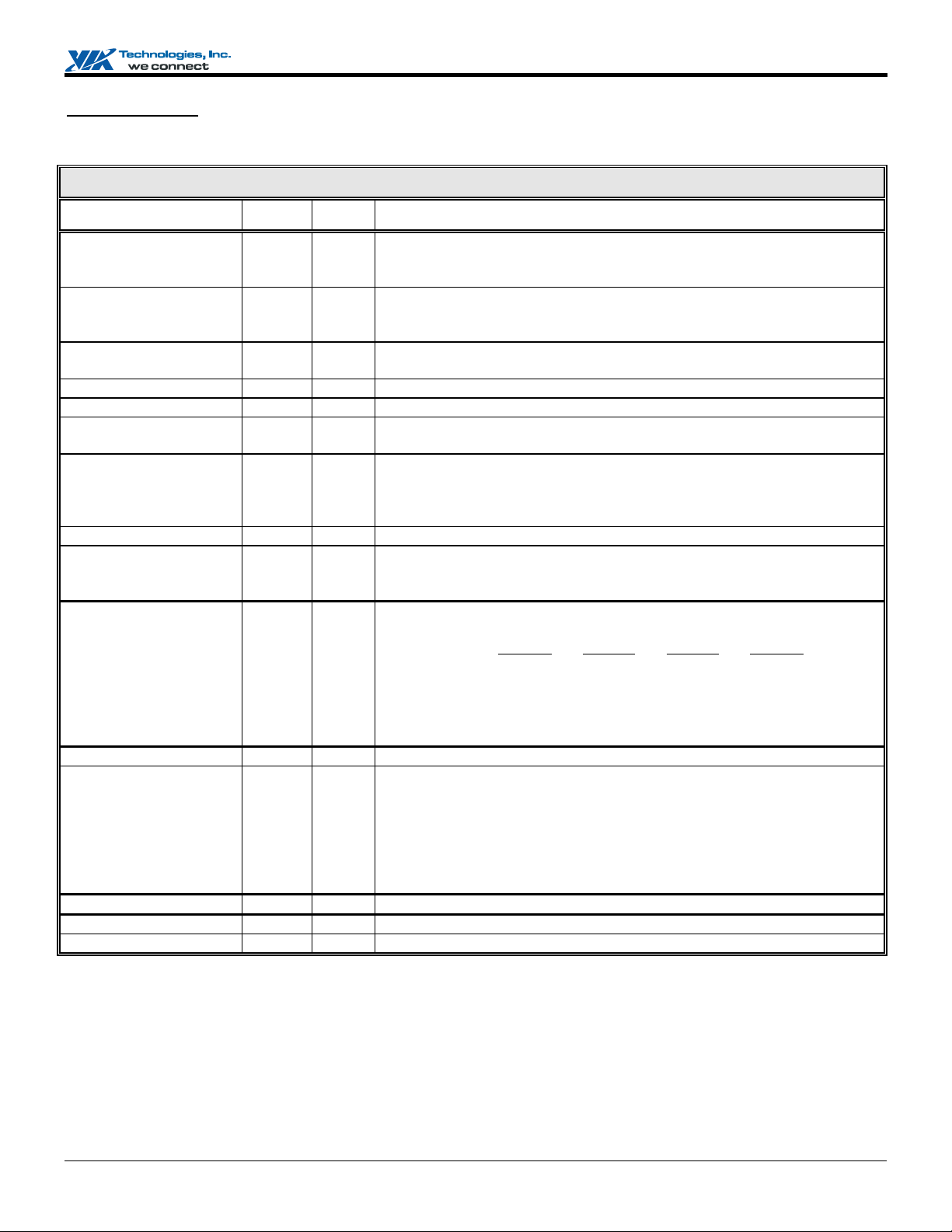

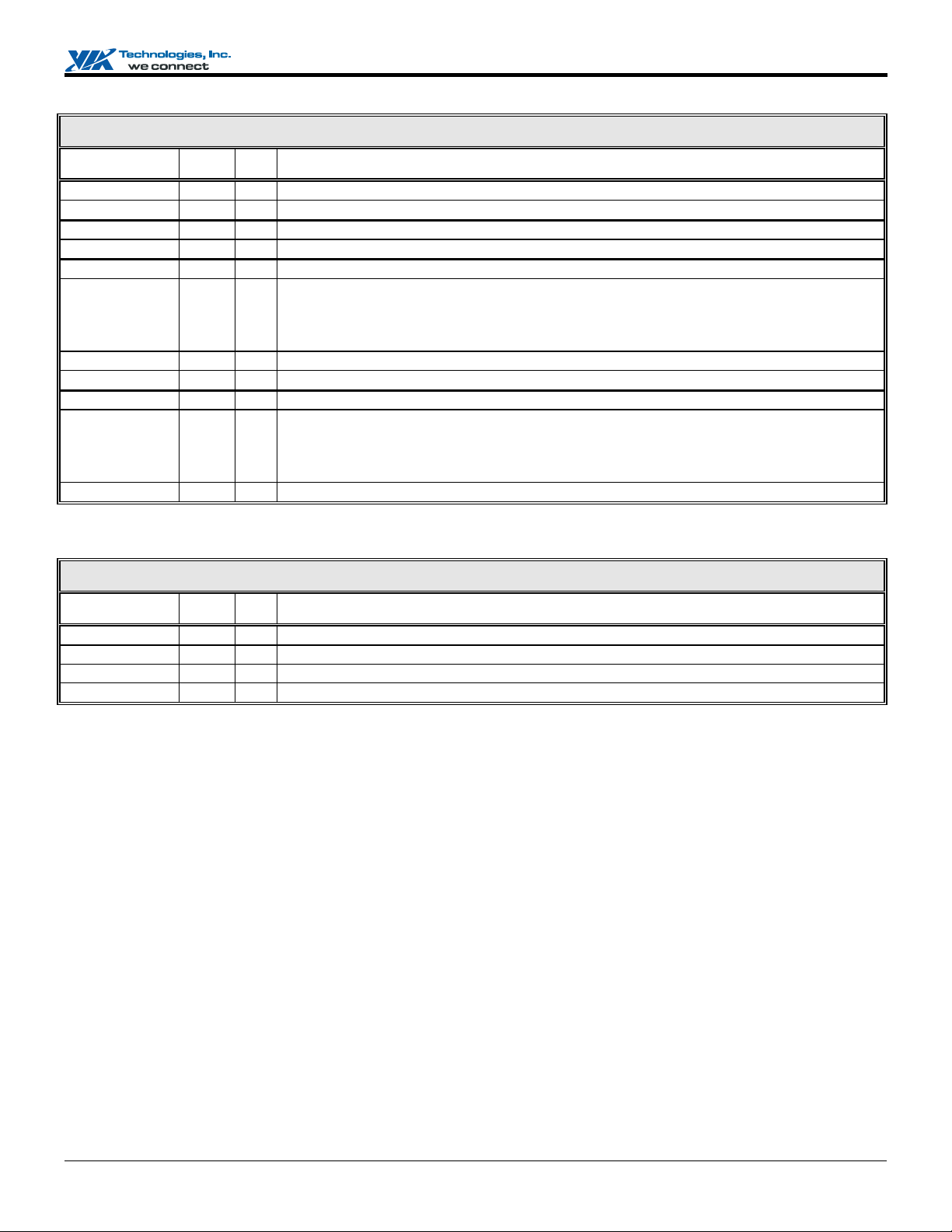

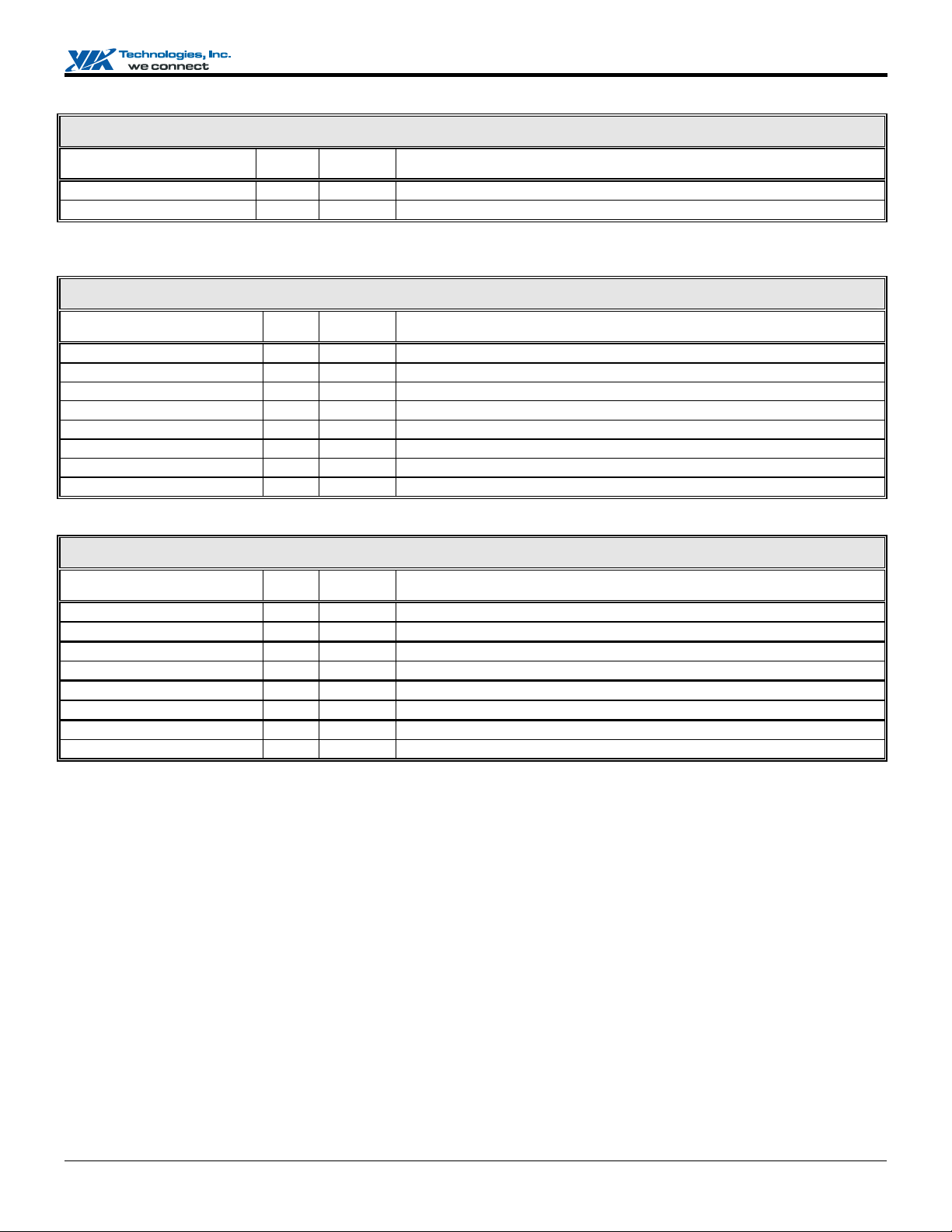

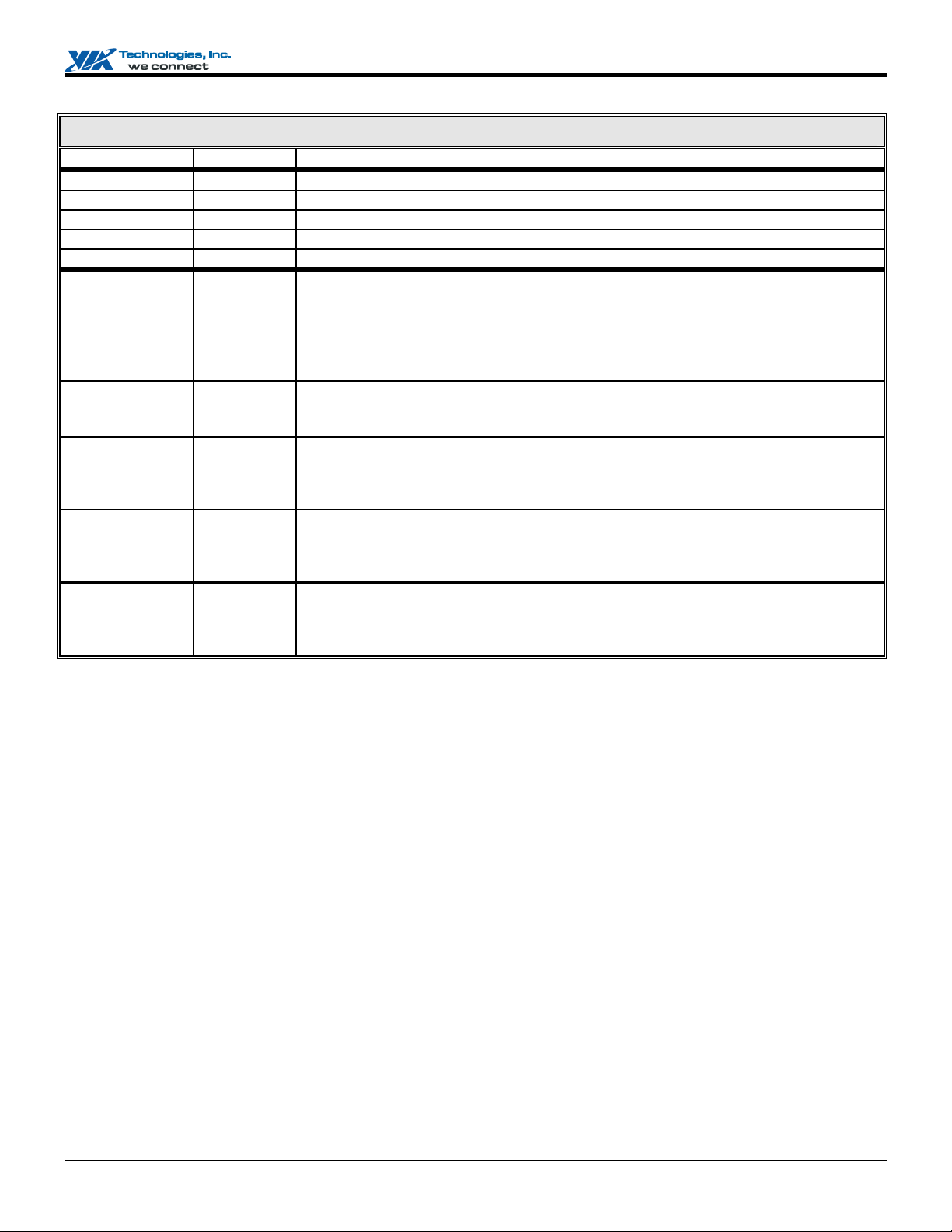

Table 1. Pin Descriptions

PCI Bus Interface

Signal Name Pin # I/O Signal Description

AD[31:0]

C/BE[3:0]#

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

PAR

SERR#

PINTA-D#

PCICLK

PCKRUN#

PCIRST#

PCISTP# / GPO6 T4 O

CPUSTP# / GPO5 P4 O

(see pin

list)

C5, D6,

A8, F10

F6 IO Frame. Assertion indicates the address phase of a PCI transfer. Negation

C7 IO Initiator Ready. Asserted when the initiator is ready for data transfer.

B7 IO Target Ready. Asserted when the target is ready for data transfer.

D7 IO Stop. Asserted by the target to request the master to stop the current

A7 IO Device Select. The VT8231 asserts this signal to claim PCI transactions

C8 IO Parity. A single parity bit is provided over AD[31:0] and C/BE[3:0]#.

E7 I System Error. SERR# can be pulsed active by any PCI device that detects a

B2, B1,

C3, C2

M17 I PCI Clock. PCLK provides timing for all transactions on the PCI Bus.

R5 IO PCI Bus Clock Run. This signal indicates whether the PCI clock is or will be

E4 O

IO Address/Data Bus. The standard PCI address and data lines. The address is

driven with FRAME# assertion and data is driven or received in following

cycles. IDSEL is internally connected to AD28.

IO Command/Byte Enable. The command is driven with FRAME# assertion.

Byte enables corresponding to supplied or requested data are driven on

following clocks.

indicates that one more data transfer is desired by the cycle initiator.

transaction.

through positive or subtractive decoding. As an input, DEVSEL# indicates

the response to a VT8231-initiated transaction and is also sampled when

decoding whether to subtractively decode the cycle.

system error condition. Upon sampling SERR# active, the VT8231 can be

programmed to generate an NMI to the CPU.

I PCI Interrupt Request. These pins are typically connected to the PCI bus

INTA#-INTD# pins as follows:

PINTA#

PCI Slot 1 INTA# INTB# INTC# INTD#

PCI Slot 2 INTB# INTC# INTD# INTA#

PCI Slot 3 INTC# INTD# INTA# INTB#

PCI Slot 4 INTD# INTA# INTB# INTC#

PCI Slot 5 INTA# INTB# INTC# INTD#

stopped (high) or running (low). The VT8231 drives this signal low when the

PCI clock is running (default on reset) and releases it when it stops the PCI

clock. External devices may assert this signal low to request that the PCI clock

be restarted or prevent it from stopping. Connect this pin to ground using a

100 Ω resistor if the function is not used. Refer to the “PCI Mobile Design

Guide” and the VIA “Apollo MVP4 Design Guide” for more details.

PCI Reset.

PCI Stop.

CPU Stop.

PINTB# PINTC# PINTD#

Revision 2.32, September 1, 2004 -10- Pin Descriptions

Page 17

VT8231 South Bridge

PCI Bus Interface (continued)

Signal Name Pin # I/O Signal Description

PREQH#

PGNTH#

PREQL#

PGNTL#

HREQ1# / GPI10 Y11 I / IO High Priority Request 1. Device 0 Function 4 RxE5[3] = 1.

HGNT1# / GPO8 W11 O / IO High Priority Grant 1. Device 0 Function 4 RxE5[3] = 1.

HREQ2# / GPI11 V11 I / IO High Priority Request 2. Device 0 Function 4 RxE5[3] = 1.

HGNT2# / GPO9 T10 O / IO High Priority Grant 2. Device 0 Function 4 RxE5[3] = 1.

LREQ1# / GPI12 U10 I / IO Low Priority Request 1. Device 0 Function 4 RxE5[2] = 1.

LGNT1# / GPO10 Y10 O / IO Low Priority Grant 1. Device 0 Function 4 RxE5[2] = 1.

LREQ2# / GPI13 / IOCHRDY W10 I / IO Low Priority Request 2. Device 0 Func 4 RxE5[2]=1, Func 0 Rx67[3]=0

LGNT2# / GPO11 V10 O / IO Low Priority Grant 2. Device 0 Function 4 RxE5[2] = 1.

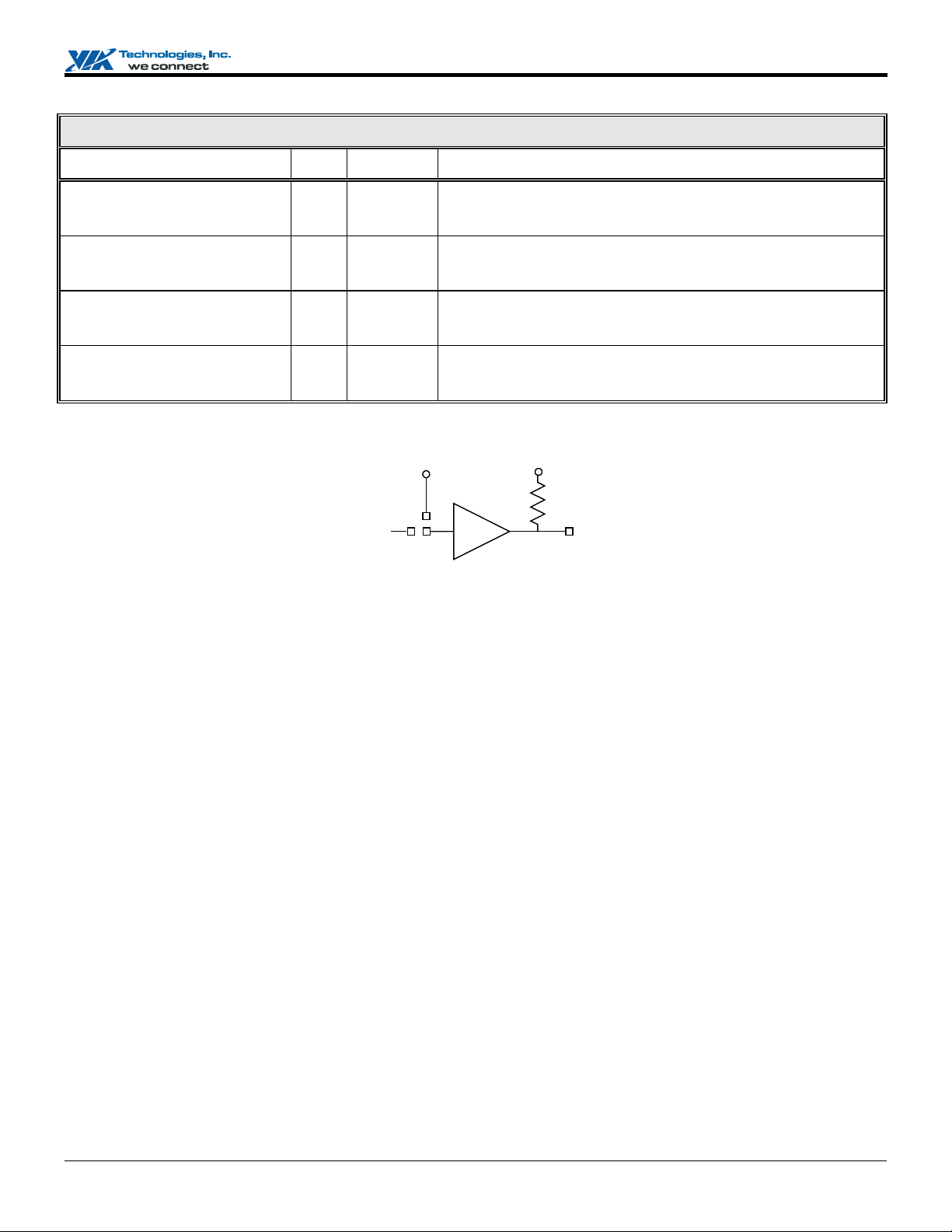

PCI Slot

PCI Slot

PCI Slot

PCI Slot

C1 O PCI Request. This signal goes to the North Bridge REQ4# input to

request the PCI bus for high priority access. The internal LAN requests the

PCI bus using this signal, so if the LAN subsystem is used, this signal must

be connected (one of the H/LREQ/GNT 1 and 2 pairs provided by the

VT8231 may be used to implement the fifth PCI slot if desired). If the

LAN subsystem is not used, PREQH# / PGNTH# may optionally remain

unconnected.

D3 I PCI Grant. This signal is driven by the North Bridge GNT4# signal to

grant high priority PCI access to the VT8231.

D2 O PCI Request. This signal goes to the North Bridge PREQ# input to

request the PCI bus for normal priority access.

D1 I PCI Grant. This signal is driven by the North Bridge PGNT# output to

grant normal priority PCI access to the VT8231.

REQ/GNT 3

REQ/GNT 2

REQ/GNT 1

REQ/GNT 0

PCI Slot

PCI Slot

On-Board

High Priority

PCI Master

On-Board

High Priority

PCI Master

H REQ/GNT 1

H REQ/GNT 2

L REQ/GNT 1

L REQ/GNT 2

VIA

North Bridge

VT8231

South Bridge

REQ/GNT 4

PREQ/GNT

PREQ/GNT L

PREQ/GNT H

Figure 5. PCI Request / Grant Connections Using the VT8231

Revision 2.32, September 1, 2004 -11- Pin Descriptions

Page 18

VT8231 South Bridge

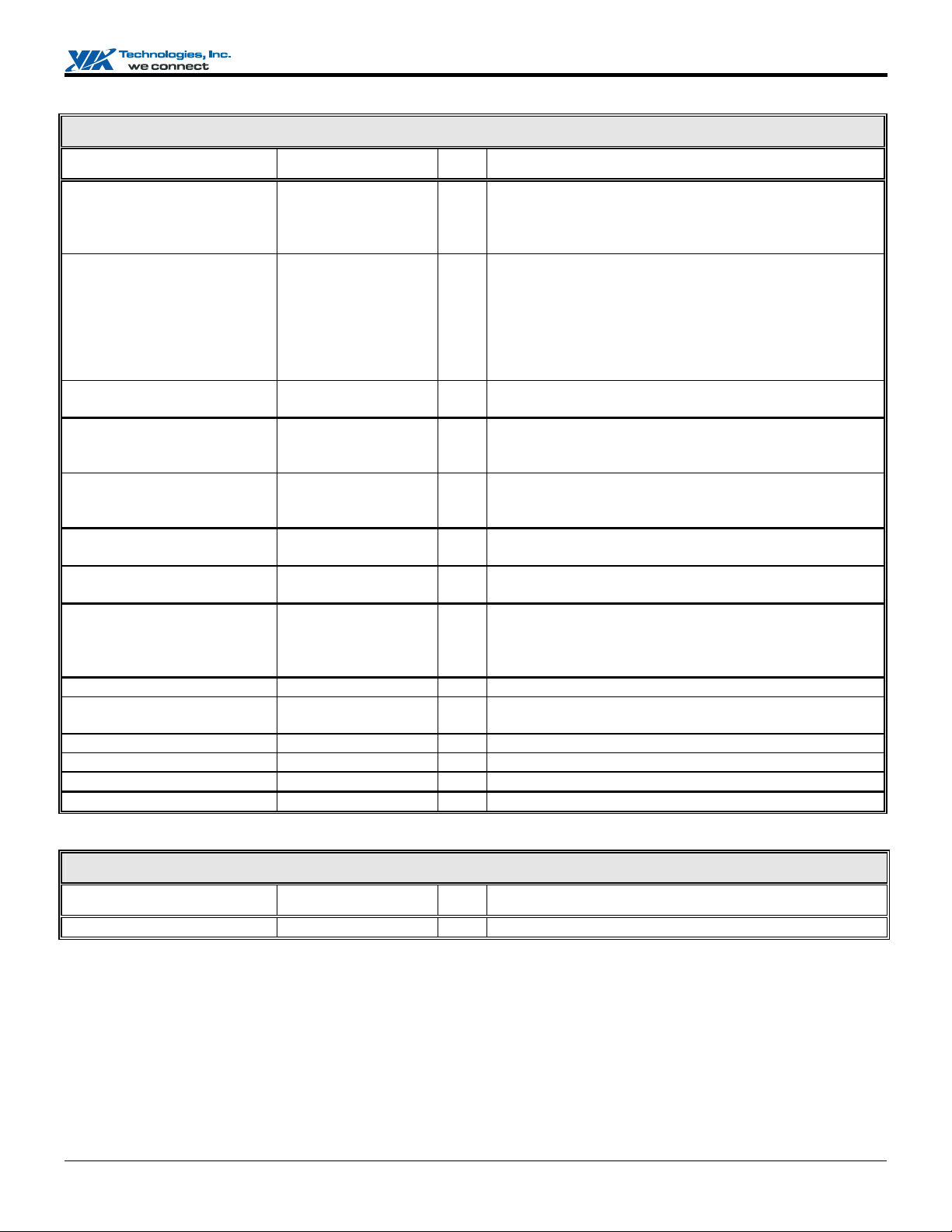

CPU Interface

Signal Name Pin # I/O Signal Description

CPURST

INTR

NMI

INIT#

STPCLK#

SMI#

FERR#

IGNNE#

SLP# / GPO7 U6 OD Sleep (F4 RxE4[4] = 1). Used to put the CPU to sleep. Used with slot-1

A20M#

DTD+

DTD-

Note: Connect each of the above signals to 4.7K Ω pullup resistors to VCC3.

U4 OD CPU Reset. The VT8231 asserts CPURST to reset the CPU during power-up.

R6 OD CPU Interrupt. INTR is driven by the VT8231 to signal the CPU that an

interrupt request is pending and needs service.

T5 OD Non-Maskable Interrupt. NMI is used to force a non-maskable interrupt to

the CPU. The VT8231 generates an NMI when SERR# is asserted.

V5 OD Initialization. The VT8231 asserts INIT# if it detects a shut-down special

cycle on the PCI bus or if a soft reset is initiated by the register. See strap on

SUSA# / GPO1 for polarity selection.

V6 OD Stop Clock. STPCLK# is asserted by the VT8231 to the CPU to throttle the

processor clock.

Y5 OD System Management Interrupt. SMI# is asserted by the VT8231 to the CPU

in response to different Power-Management events.

U5 I Numerical Coprocessor Error. This signal is tied to the coprocessor error

signal on the CPU. Internally generates interrupt 13 if active. A threshold of

1.5V or 2.5V is selectable via Device 0 Function 0 Rx67[2].

T6 OD Ignore Numeric Error. This pin is connected to the “ignore error” pin on the

CPU.

CPUs only. Not currently used with socket-7 CPUs.

W5 OD A20 Mask. Connect to A20 mask input of the CPU to control address bit-20

generation. Logical combination of the A20GATE input (from internal or

external keyboard controller) and Port 92 bit-1 (Fast A20). See Device 0

Function 0 Rx59[1].

L2 Analog I CPU DTD (Thermal Diode) Channel Plus. Connect to cathode of first

external temperature sensing diode.

L3 Analog I CPU DTD (Thermal Diode) Channel Minus. Connect to anode of first

external temperature sensing diode.

Revision 2.32, September 1, 2004 -12- Pin Descriptions

Page 19

VT8231 South Bridge

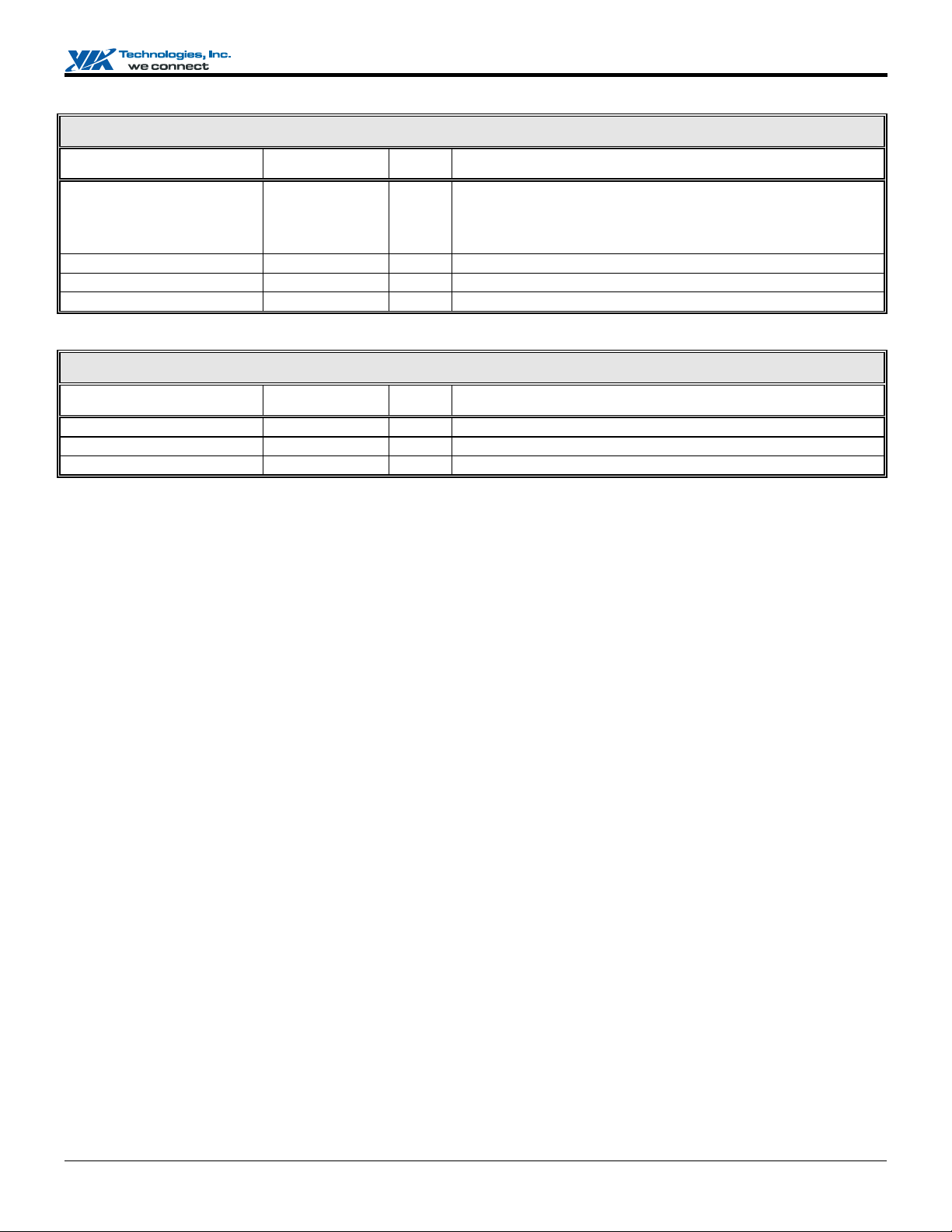

Strap Options

Signal Name Pin # I/O Signal Description

Strap / SUSA# / GPO1 P1 I / O

CPURST / INIT# Polarity

H: Slot-1 / Socket-370 / Slot-A / Socket-A

L: Socket-7

Strap / MCCS# / GPO17 W6 I / O

CPU Frequency Strapping

H: Disable

L: Enable

Strap / SA16 Y14 I / IO

BIOS ROM Interface

H: LPC

L: Conventional

Strap / SA17 T13 I / IO

Auto Reboot

H: Disable (recommended)

L: Enable

Note: External strap option values may be set by connecting the indicated external pin to a 4.7K ohm pullup (for 1 or H) or

driving it low during reset with a 7407 TTL open collector buffer (for 0 or L) as shown in the suggested circuit below:

VCC

7407

RESET#

VCC

4.7K

strap

pin

Figure 6. Strap Option Circuit

Revision 2.32, September 1, 2004 -13- Pin Descriptions

Page 20

VT8231 South Bridge

Advanced Programmable Interrupt Controller (APIC) Interface

Signal Name Pin # I/O Signal Description

WSC# / GPI14 V4 I / I Internal APIC Write Snoop Complete. F0 Rx58[6] = 1.

Asserted by the north bridge to indicate that all snoop activity

on the CPU bus initiated by the last PCI-to-DRAM write is

complete and that it is safe to perform an APIC interrupt.

APICD0 / GPO28 W4 O / O Internal APIC Data 0. F0 Rx58[6] = 1.

APICD1 / GPO29 Y4 O / O Internal APIC Data 1. F0 Rx58[6] = 1.

APICCLK / GPI9 Y3 I / I APIC Clock. F0 Rx58[6] = 1.

Low Pin Count (LPC) Interface

Signal Name Pin # I/O Signal Description

LFRAME#

LDRQ# / GPI15 Y8 I / I LPC Data Request. F0 Rx58[5] = 1 and F4 RxE5[7] = 0.

LAD[3-0]

Note: For LPC control, see Device 0 Function 0 Rx58[5] and Rx59[4-3]

Note: Connect the LPC interface LPCRST# (LPC Reset) signal to PCIRST#

W8 O

V7, W7, Y7, V8 IO

LPC Frame.

LPC Address / Data.

Revision 2.32, September 1, 2004 -14- Pin Descriptions

Page 21

VT8231 South Bridge

LAN Controller - Media Independent Interface (MII)

Signal Name Pin # I/O Signal Description

MCOL

MCRS

MDCK

MDIO

MRXCLK

MRXD[3],

MRXD[2],

MRXD[1],

MRXD[0]

MRXDV

MRXERR

MTXCLK

MTXD[3],

MTXD[2],

MTXD[1],

MTXD[0]

MTXENA

The internal LAN controller uses the high priority PCI bus request / grant pair (PREQH# / PGNTH#) to request PCI bus access

from the chipset north bridge.

G17 I MII Collision Detect. From the external PHY.

G16 I MII Carrier Sense. Asserted by the external PHY when the media is active.

C20 O MII Management Data Clock. Sent to the external PHY as a timing reference for MDIO

D18 IO MII Management Data I/O. Read from the MDI bit or written to the MDO bit.

C19 I MII Receive Clock. 2.5 or 25 MHz clock recovered by the PHY.

D19

D20

E18

E19

E20 I

F18 I MII Receive Error. Asserted by the PHY when it detects a data decoding error.

F17 I MII Transmit Clock. Always active 2.5 or 25 MHz clock supplied by the PHY.

G20

G19

G18

F20

F19 O MII Transmit Enable. Indicates transmit active from the MII port to the PHY.

I

MII Receive Data. Parallel receive data lines driven by the external PHY synchronous with

I

MRXCLK.

I

I

MII Receive Data Valid.

O

MII Transmit Data. Parallel transmit data lines synchronized to MTXCLK.

O

O

O

Serial EEPROM Interface

Signal Name Pin # I/O Signal Description

EECS#

EECK

EEDO

EEDI

C18 O

E16 O

D17 I Serial EEPROM Data Output. Connect to EEPROM Data Out pin.

E17 O Serial EEPROM Data Input. Connect to EEPROM Data In pin.

Serial EEPROM Chip Select.

Serial EEPROM Clock.

Revision 2.32, September 1, 2004 -15- Pin Descriptions

Page 22

VT8231 South Bridge

Universal Serial Bus Interface

Signal Name Pin # I/O Signal Description

USBP0+

USBP0USBP1+

USBP1USBP2+

USBP2USBP3+

USBP3USBCLK

USBOC0#

USBOC1#

USBOC2# / LA20

/ GPI20 / GPO20

USBOC3# / LA21

/ GPI21 / GPO21

For USB interface configuration and control see also Functions 2 and 3 plus Function 0 Rx48[3-2], 4A[1], 4D[1-0], 50[5-4]

B18 IO

A18 IO

B19 IO

A19 IO

B20 IO

A20 IO

C17 IO

B17 IO

C15 I USB Clock. 48MHz clock input for the USB interface

A17 I USB Port 0 Over Current Detect. Port 0 is disabled if this input is low.

D16 I USB Port 1 Over Current Detect. Port 1 is disabled if this input is low

W13 I / IO

/ I / O

Y13 I / IO

/ I / O

USB Port 0 Data +

USB Port 0 Data USB Port 1 Data +

USB Port 1 Data USB Port 2 Data +

USB Port 2 Data USB Port 3 Data +

USB Port 3 Data -

USB Port 2 Over Current Detect. Port 2 is disabled if this input is low.

Device 0 Function 4 RxE4[6] = 0 and Power Management I/O Rx4E[4] = 1

USB Port 3 Over Current Detect. Port 3 is disabled if this input is low.

Device 0 Function 4 RxE4[6] = 0 and Power Management I/O Rx4E[5] = 1

System Management Bus (SMB) Interface (I2C Bus)

Signal Name Pin # I/O Signal Description

SMBCK1

SMBCK2 / GPIO27 R1 IO / IO SMB / I2C Channel 2 Clock†. F4 Rx55[3] = 0.

SMBDT1

SMBDT2 / GPIO26 R2 IO / IO SMB / I2C Channel 2 Data†. F4 Rx55[3] = 0.

SMBALRT# / GPI7 T2 I / I SMB Alert. (System Management Bus I/O space Rx08[3] = 1) When the

For SMB interface configuration and control see also Function 4 Rx54[7], 55[3-2], 56[4], 90-93, D2-D6 plus SMB I/O Rx0-F,

HWM I/O Rx48, and PMIO Rx45[1-0]

† Note: SMBus #2 is a slave-only device used to supply status for external Alert-On-LAN (AOL)

R3 IO

T1 IO

SMB / I2C Channel 1 Clock.

SMB / I2C Channel 1 Data.

chip is enabled to allow it, assertion generates an IRQ or SMI interrupt or a

power management resume event. The same pin is used as General Purpose

Input 6 whose value is reflected in Rx48[6] of function 4 I/O space

Revision 2.32, September 1, 2004 -16- Pin Descriptions

Page 23

VT8231 South Bridge

UltraDMA-33 / 66 / 100 Enhanced IDE Interface

Signal Name Pin # I/O Signal Description

PDRDY /

PDDMARDY /

PDSTROBE

SDRDY /

SDDMARDY /

SDSTROBE

PDIOR# /

PHDMARDY /

PHSTROBE

SDIOR# /

SHDMARDY /

SHSTROBE

PDIOW# /

PSTOP

SDIOW# /

SSTOP

PDDRQ

SDDRQ

PDDACK#

SDDACK#

IRQ14

IRQ15

N19 I EIDE Mode: Primary I/O Channel Ready. Device ready indicator

UltraDMA Mode: Primary Device DMA Ready. Output flow control. The device

may assert DDMARDY to pause output transfers

Primary Device Strobe. Input data strobe (both edges). The

device may stop DSTROBE to pause input data transfers

Y20 I EIDE Mode: Secondary I/O Channel Ready. Device ready indicator

UltraDMA Mode: Secondary Device DMA Ready. O

device may assert DDMARDY to pause output transfers

Secondary Device Strobe. Input data strobe (both edges). The

device may stop DSTROBE to pause input data transfers

N18 O EIDE Mode: Primary Device I/O Read. Device read strobe

UltraDMA Mode: Primary Host DMA Ready. Primary

The host may assert HDMARDY to pause input transfers

Primary Host Strobe. Output data strobe (both edges). The host

may stop HSTROBE to pause output data transfers

W19 O EIDE Mode: Secondary Device I/O Read. Device read strobe

UltraDMA Mode: Secondary Host DMA Ready. Input flow control. The host may

assert HDMARDY to pause input transfers

Host Strobe B. Output strobe (both edges). The host may stop

HSTROBE to pause output data transfers

P20 O EIDE Mode: Primary Device I/O Write. Device write strobe

UltraDMA Mode: Primary Stop. Stop transfer: Asserted by the host prior to

initiation of an UltraDMA burst; negated by the host before data

is transferred in an UltraDMA burst. Assertion of STOP by the

host during or after data transfer in UltraDMA mode signals the

termination of the burst.

Y19 O EIDE Mode: Secondary Device I/O Write. Device write strobe

UltraDMA Mode: Secondary Stop. Stop transfer: Asserted by the host prior to

initiation of an UltraDMA burst; negated by the host before data

is transferred in an UltraDMA burst. Assertion of STOP by the

host during or after data transfer in UltraDMA mode signals the

termination of the burst.

P19 I Primary Device DMA Request. Primary

U17 I Secondary Device DMA Request. Secondary

N20 O Primary Device DMA Acknowledge. Primary

W20 O Secondary Device DMA Acknowledge. Secondary

T14 I

U14 I

Primary Channel Interrupt Request.