VIA VT6304 Datasheet

VIA Technologies, Inc. Preliminary VT6304

VT6304

1394.A 4 PORT PHYSICAL LAYER CHIP

DATA SHEET

(Preliminary)

DATE : June 1, 1999

VIA TECHNOLOGIES, INC.

1

VIA Technologies, Inc. Preliminary VT6304

PRELIMINARY RELEASE

Please contact Via Technologies for the latest documentation.

Copyright Notice:

Copyright © 1998, Via Technologies Incorporated. Printed in Taiwan. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or

translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical,

chemical, manual or otherwise without the prior written permission of Via Technologies Incorporated.

The VT6101/VT6102 may only be used to identify products of Via Technologies.

All trademarks are the properties of their respective owners.

Disclaimer Notice:

No license is granted, implied or otherwise, under any patent or patent rights of Via Technologies. Via

Technologies makes no warranties, implied or otherwise, in regard to this document and to the products

described in this document. The information provided by this document is believed to be accurate and

reliable to the publication date of this document. However, Via Technologies assumes no responsibility for

any errors in this document. Furthermore, Via Technologies assumes no responsibility for the use or misuse

of the information in this document and for any patent infringements that may arise from the use of this

document. The information and product specifications within this document are subject to change at any

time, without notice and without obligation to notify any person of such change.

Offices:

5020 Brandin Court 8th Floor, No. 533

Fremont, CA 94538 Chung-Cheng Rd., Hsin-Tien

USA Taipei, Taiwan ROC

Tel: (510) 683-3300 Tel: (886-2) 218-5452

Fax: (510) 683-3301 Fax: (886-2) 218-5453

Onlines Services:

BBS : 886-2-2186408

FTP : FTP.VIA.COM.TW

HTTP: WWW.VIA.COM.TW

2

VIA Technologies, Inc. Preliminary VT6304

VT6304 IEEE 1394A FOUR PORT CABLE TRANSCEIVER/ARBITER FEATURES

n Supports Provisions of IEEE 1394-1995 Standard for High Performance Serial Bus and the P1394a

Supplement 2.0.

n Full P1394a Supplement Support includes:

n Arbitrated short reset,

n Connection Debounce,

n Multispeed Concatenation,

n Ack Accelerated Arbitration,

n Fly-By Concatenation,

n Programmable Port Disable, Suspend, Resume,

n PHY IDs Do Not Increment Past 63

n Provides Four 1394a Fully Compliant Cable Ports at 100/200/400 Megabits per Second (Mbit/s)

n Single 3.3 V power supply

n Logic Performs Bus Initialization and Arbitration Functions

n Encode and Decode Functions Included for Data-Strobe Bit-Level Encoding

n Incoming Data Resynchronized to Local Clock.

n Data Interface to Link-Layer Controller Provided Through 2/4/8 Parallel Lines at 49.152 MHz

n 24.576 MHZ Crystal Oscillator and PLL Provide TX/RX Data at 100/200/400 Mbps and Link-Layer

Controller Clock at 49.152 MHZ.

n Cable Power Presence Monitoring.

n Programable Node Power Class Information for System Power Management

n Embedded Bus Holder Isolation to Link Layer Controller Interface

n Optional On-chip Resistors to Reduce Component Counts for Electrical Isolation to Link Layer

Controller Interface

n Fully Compliant P1394a 2.0 PHY Map

n Separate TPBIAS for Each Port

n Fully Interoperable with IEEE Std1394-1995 Devices

n Cable Ports Monitor Line Conditions for Active Connection to Remote Node

n Low Power Design for Battery-Powered Applications includes: User Controlled Power-Down via PD,

Automatic Device Power-Down during All Ports Suspended and Link Interface Disabled, Link

Interface Power-Down via Inactive LPS, Automatic Inactive Ports Powered-Down, and Automatic

Inactive Logic Power-Down

n Self Power Up Reset and Pinless PLL to Reduce Component Counts on System

n Low Cost 100-Pin PQFP package

3

VIA Technologies, Inc. Preliminary VT6304

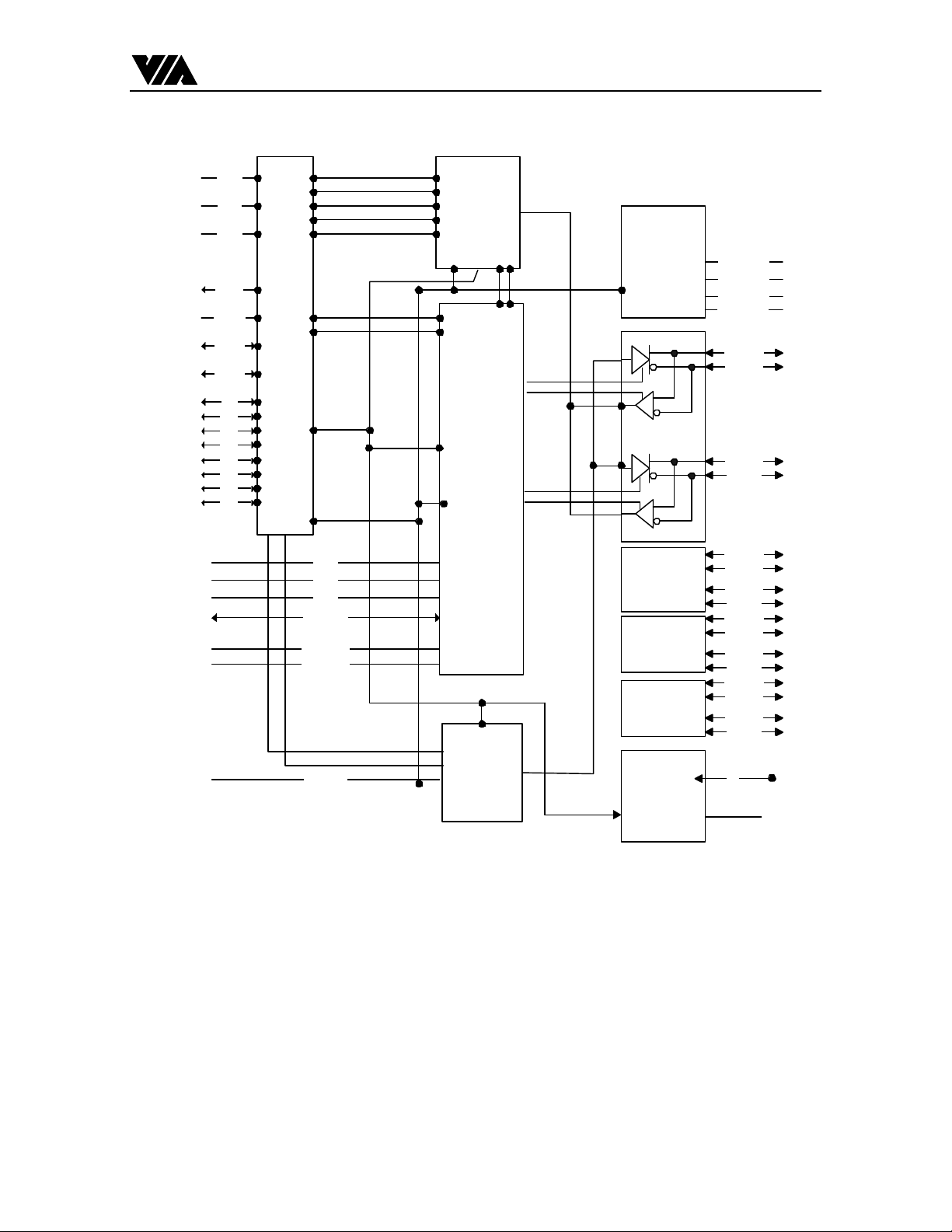

CPS

LPS

ISO\

SYS

CLK

LREQ

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

Link

Interfac

e I/O

PC0

PC1

PC2

C/LKON

TESTM1

TESTM2

Received

Data

Decoder/

Retimer

Arbitration

and Control

State

Machine

Logic

Bias Voltage

and Current

Generator

Cable Port 1

Cable Port 2

Cable Port 3

Cable Port 4

TPBIAS1

TPBIAS2

TPBIAS3

TPBIAS4

TPA1+

TPA1-

TPB1+

TPB1-

TPA2+

TPA2-

TPB2+

TPB2-

TPA3+

TPA3-

TPB3+

TPB3-

TPA4+

TPA4-

TPB4+

TPB4-

n

Transmit

RESET\

Data

Encoder

Figure 1: Functional Block of VT6304

4

Crystal

Oscillator,

PLL System,

and Clock

Generator

XI

XO

VIA Technologies, Inc. Preliminary VT6304

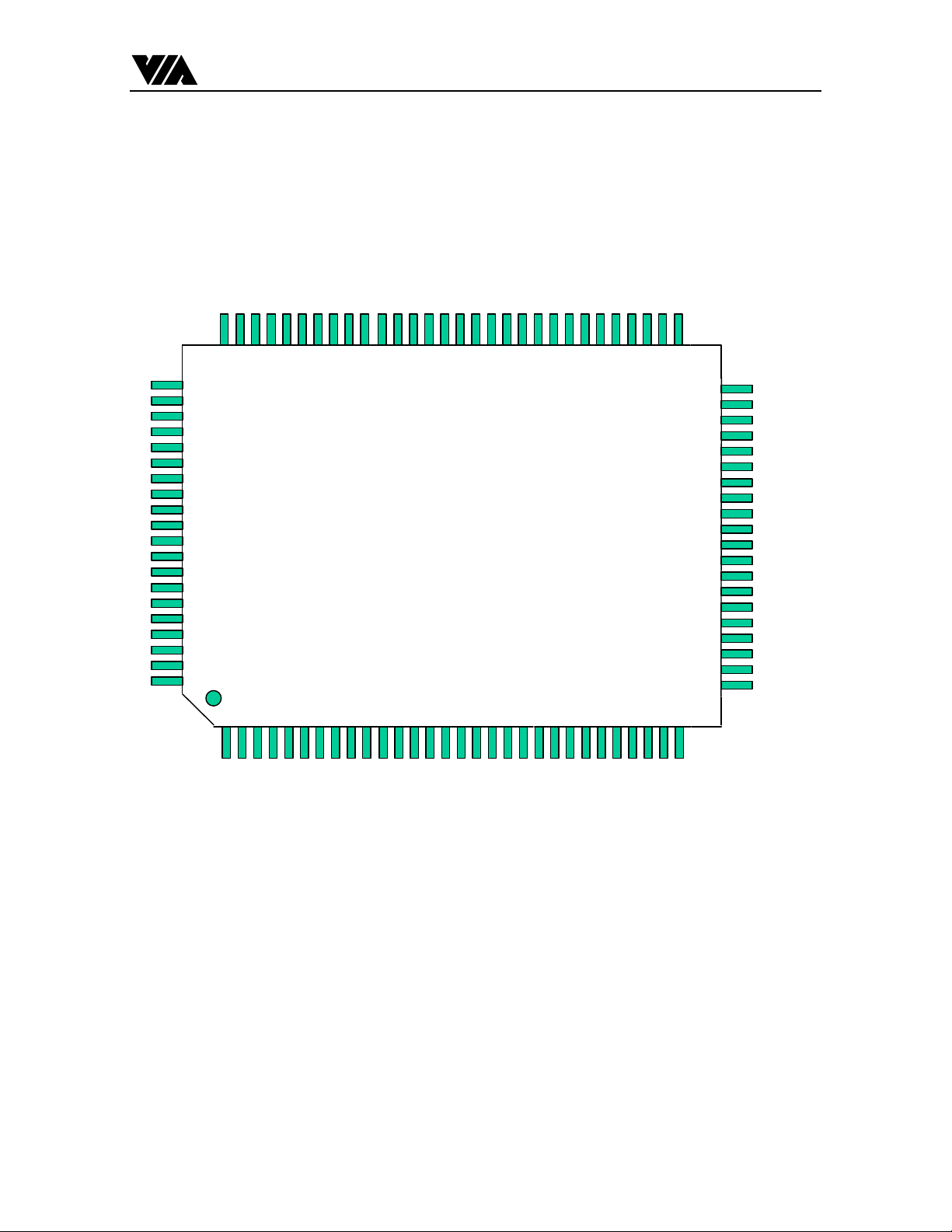

GNDATX2

XTPBIAS1

VDDATX2

VDDARX2

XTPBIAS2

GNDATX3

XTPBIAS3

GNDARX2

Pin Diagram

GNDD5

LINKON

LPS

CMC

VDDDC2

GNDDC2

XCPS

VDDARX0

GNDARX0

XTPB0M

XTPB0P

XTPA0M

XTPA0P

XTPBIAS0

VDDATX0

GNDATX0

GNDATX1

VDDATX1

VDDARX1

GNDARX1

NC

NC

NC

NC

NC

PD

ISO_

4

SCLK

VDDD

4

0

DDD

GNDD

3

1

VDDD

324

D

3

5

D

D

GNDD

2

1

CTL

VDDD

2

LREQ

GNDD

NC

0

6

7

D

CTL

D

80 79 78 77 76 75 74 73 72 7170 69 68 6766 65 64 63 62 6160 59 58 57 5655 54 53 52 51

81

82

83

84

85

86

87

88

89

VT6304

90

91

92

93

94

01/07/99 updated

95

96

97

98

99

100

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1718 19 20 21 22 2324 25 26 27 28 29 30

NC

NC

NC

NC

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

CNA

RESET_

ONCT

TSI

GNDD1

VDDD1

PC0

PC1

PC2

TSO

VDDDC1

GNDDC1

XO

XI

XREXT

GNDAREXT

GNDARX3

VDDARX3

VDDATX3

GNDATX4

NC

NC

NC

NC

NC

XTPB1P

XTPB1M

XTPA1M

XTPA1P

XTPB2P

XTPB2M

XTPA2M

5

XTPA2P

XTPB3P

XTPB3M

XTPA3M

XTPA3P

NC

NCNCNC

NC

VIA Technologies, Inc. Preliminary VT6304

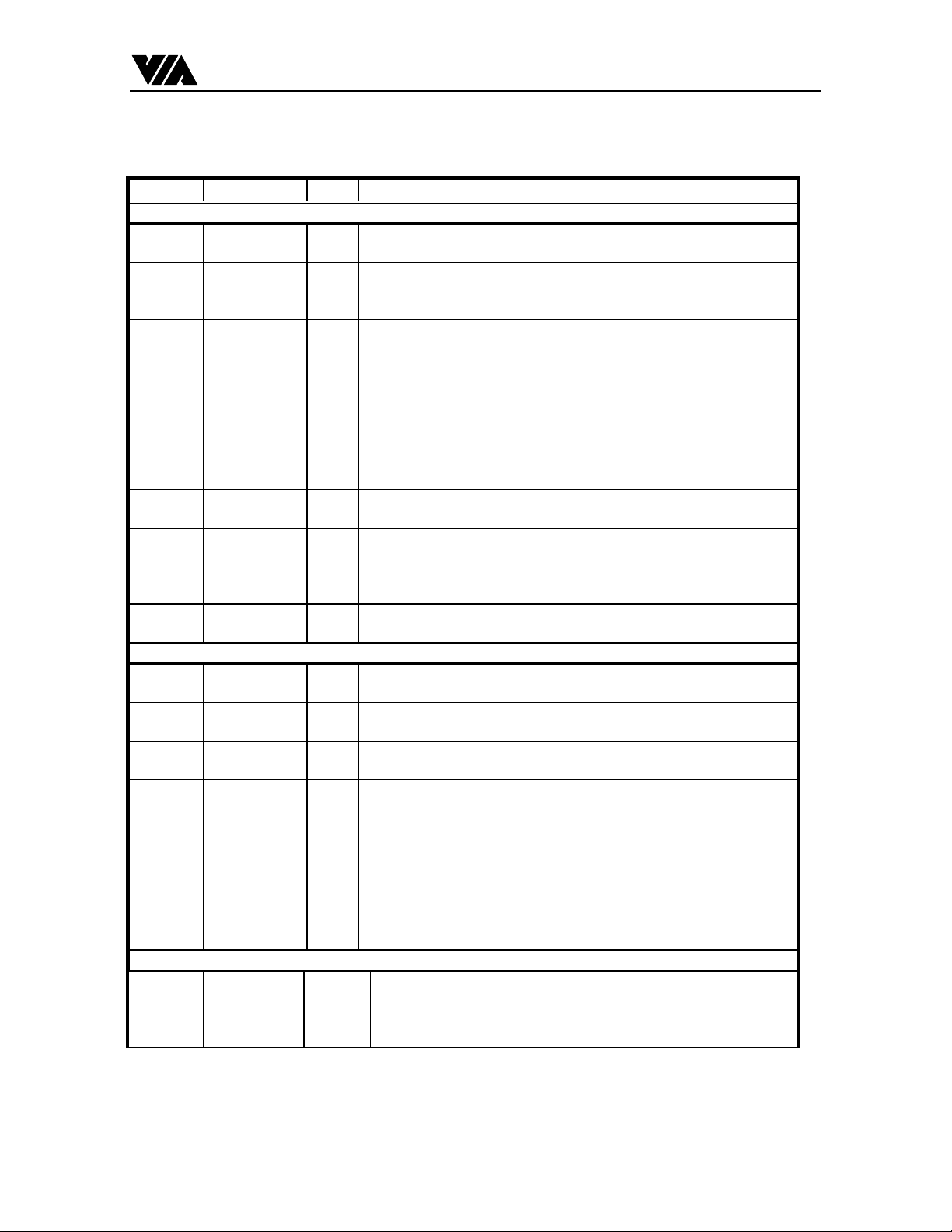

PIN DESCRIPTIONS

No. Name

Link-PHY Interface

82 LINKON O Link on. Indicates the reception of a link-on packet or port event

83 LPS I Link power status. LPS is connected to either the VDD supplying

57 LREQ I Link request. LREQ is an input from the LINK that requests the

74 ISO_ I Link interface isolation control input. This terminal controls the

60, 58 CTL[0-1] I/O Control I/O. the CTLn terminals are bidirectional

70, 69,

68, 66,

65, 64,

62, 61

72 SCLK O System clock. SCLK provides a 49.152 MHZ clock signal, which

Analog Interface

93, 10,

17, 22

92, 9 ,

16, 22

91, 8, 15,21XTPB[0-3]P I/O Twisted-pair cable B differential positive signal pins.

D[0-7] I/O Data I/O. The D terminals are bidirectional and pass data

XTPA[0-3]P I/O Twisted-pair cable A differential positive signal pins.

XTPA[0-3]M I/O Twisted-pair cable A differential negative signal pins.

Type

Description

occurs by asserting a 6.114 MHZ signal.

the LINK or to a pulsed output that is active when the LINK is

powered for the purpose of monitoring the LINK power status.

PHY to perform some service.

operation of output differentiation logic on the CTL[0-1] and

D[0-7] signals. If an optional isolation barrier is implemented

between the VT6304 and LLC the ISO_ pin should be tied low to

enable the differentiation logic. If no isolation barrier is

implemented, the ISO_ should be tied high to disable

differentiation logics.

communications control signals between the PHY and LINK.

between the PHY and LINK.

is synchronized with the data transfers to the LINK.

90, 7, 14,20XTPB[0-3]M I/O Twisted-pair cable B differential negative signal pins.

94, 11,

18, 23

Misc.

87 XCPS I CPS : Cable power status. CPS is normally connected to the

XTPBIAS[0-3]I/O Twisted-pair bias voltage supply. Provide 1.85V (typical) nominal

bias for proper operation of the twisted-pair cable drivers and

receivers, and for signaling to the remote nodes that the cable

connections is active. Hi-impedance during chip reset or power

down. Can be disabled via remote packets or software defined in

P1394a Draft 2.0. Each of these pin must be decoupled with a 1-uF

capacitor to ground.

cable power through a 11 Kohm/1 KOhm volatge divider. This

circuit drivers an internal comparator that detects the presencce

of cable power.

6

VIA Technologies, Inc. Preliminary VT6304

50 CNA O CNA is asserted high when none of the PHY ports are

connected to another active port. This circuit remains active

during the powerdown mode.

84

44, 43, 42

47

41

48 ONCT I On Chip Termination. If the capacitive isolation barrier is

75 PD I Power Down. A logic High on this pin turns off all internal

49 RESET_ I/NC Reset (active low). The reset pin is connected to an internal 10K

38, 37 XI, XO Crystal Crystal Oscillator, 3.3V. These pins connect to a 24.576 MHz

36, 35 XREXT,

Power Supply & Ground

88, 99, 13,

33

89, 100, 25,

24

CMC I Programable Contender/Bus Manager Capable. It specifies in

the Self-ID packet that the node is capable of being a bus

manager.

PC[0-2] I Power Class. These pins are used to set the three

POWER_CLASS bits in the Self-ID packet. They are used to

describe the power consumption and source characteristics of

the node. PC0, 1, 2 are reflected in the Self-ID packet bits 21,

22, 23, respectively.

TSI I Single Self ID packet. If port 4 is unused, i.e, the resistors and

capacitors for port 4 are not implemented, there is no need to

send the 2nd self ID packet, and the system can get benefit by

tying this pin to digital VDD to reduce self ID packet exchange

time.

TSO I Test pin. Tied to VT6304 digital VDD ring for normal

operations.

implemented between the VT6304 and LLC, tie this pin to

VDD will utilize on chip resistors to replace on board 5K

Ohms resistors pair for LREQ, CTL[0:1] and D[0:7] at PHY

side. The resistors for LPS input at PHY side are also replaced

if this pin is tied to VDD. This pin has effects on on-chip

terminations only if ISO_ is tied to ground.

cicuitry except the connection detect circuits, which outputs

the CNA signal.

ohm resistor and an external 0.1 uF capacitor is used for

internal reset generation at power-on. The pin can be left

unconnected to save the external capacitors, and then the reset

time after power-on ranges from 0.5 ms to 2 ms. This pin can

also be driven by an open-drain type driver.

parallel resonant fundamental mode crystal. The optimum

values for the external shnut capacitors are dependent on the

specifications of the cystal used. The resulting frequency

variation is +/- 100 ppm.

I/O Current setting resistor terminals. A resistor of 6.2 KOhm +/-

GNDARE

0.5% is required for internal operating currents generation.

XT

VDDARX supply Analog receiver power. A combination of high-frequency

decoupling capacitors near these pins are suggested. These

pins are seperated from digital power for noise prevention.

GNDARX supply Analog receiver ground. These pins are tied together to the low-

impedance circuit board ground.

7

Loading...

Loading...