Page 1

SERVICE MANUAL

17MB70

1

Page 2

DATE VERSION CHANGE RELEASED BY

14.10.2010 V1.0 Draft Emre YILDIZILI

2

Page 3

İçindekiler

1. INTRODUCTION ............................................................................................................................... 5

2. TUNER .............................................................................................................................................. 6

3. AUDIO AMPLIFIER STAGES .............................................................................................................. 8

A. MAIN AMPLIFIER (TPA3110) ........................................................................................................ 8

B. LINE-OUT and HEAD-PHONE AMPLIFIER STAGE (CXA3813N) ................................................... 11

C. SUBWOOFER AMPLIFIER STAGE (TPA3112) .............................................................................. 12

4. POWER STAGE ............................................................................................................................... 14

5. MICROCONTROLLER(Broadcom) ................................................................................................... 21

6. SATELLITE RECEIVER (Broadcom) .................................................................................................. 24

7. VIDEO BACK-END PROCESSOR (Trident) ....................................................................................... 25

8. FPGA (Spartan-3E) ......................................................................................................................... 27

9. PIXELLENCE II ................................................................................................................................. 28

10. 1Gb F-die DDR2-1066 SDRAM (U41-U42-U8-U9) ...................................................................... 29

11. 32M x 16 bit DDRII Synchronous DRAM (U28-U29) .................................................................. 31

12. 4Gbit NAND Flash Memory (U35) ............................................................................................. 34

13. 128Mbit NAND Flash Memory (U17) ........................................................................................ 36

14. USB Interface ............................................................................................................................. 37

15. CI Interface ................................................................................................................................ 38

16. DVB-C Demodulator .................................................................................................................. 38

17. DVB-C/T2 Demodulator ............................................................................................................. 41

18. LOW POWER&CEC MICROCONTROLLER ................................................................................... 47

19. HDMI SWITCH ............................................................................................................................ 48

20. LNB supply and control IC ......................................................................................................... 53

21. Software Update ....................................................................................................................... 54

22. Troubleshooting ........................................................................................................................ 54

A. No Backlight Problem ............................................................................................................ 54

B. CI Module Problem ............................................................................................................... 57

C. Staying in Stand-by Mode ..................................................................................................... 58

D. IR Problem ............................................................................................................................ 59

E. Keypad Touchpad Problems.................................................................................................. 60

F. USB Problems ....................................................................................................................... 61

G. No Sound Problem ................................................................................................................ 61

3

Page 4

H. Standby On/Off Problem ....................................................................................................... 61

İ. No Signal Problem ................................................................................................................ 62

23. Service Menu Settings ............................................................................................................... 62

24. General Block Diagram .............................................................................................................. 67

4

Page 5

1. INTRODUCTION

17MB70-2 mainboard is based on Broadcom concept IC. This IC combines DVB-T COFDM

terrestrial and PAL/SECAM demodulators, HDMI receivers, a transport processor, a digital

audio processor, graphics processing, Ethernet MAC and PHY, digital processing of analog

video and audio, analog video digitizer and DAC functions, stereo high-fidelity audio DACs,

a 400-MHz dual-threaded MIP processor, and a peripheral control unit providing a variety of

television control functions. This IC also features an advanced video decoder capable of

supporting high-definition AVC, VC-1, and DVB-T MPEG-2 streams.

Main IC Features:

• Advanced multiformat decoder supporting the following:

- H.264/AVC Main and High Profile to Level 4.1 (HD), Level 3.1 (SD)

- HD/SD AVS Jizhun Profile Levels 2.0, 4.0, and 6.0

- VC-1 Advanced Profile @ Level 3, simple and main profiles

- HD/SD MPEG-2 Main Profile at Main and High levels

- MPEG still image decode

- HD DivX® 3.11/4.11/5.x/6x/Home Theater

• 3D/2D OpenGL® ES 1.0- compliant graphics core

• Integrated Video Processing:

- 3D Color management

- Digital, Analog, and Mosquito Noise Reduction

- 1080i motion adaptive deinterlacing with 3:2/2:2 pull-down

- True 10-bit video carried through system

• Dual HDMI 1.3a receivers

• Extensive audio support:

- AAC+ Level 2, AAC-HE

- Dolby® Digital, Dolby Digital Plus, Trusurround XT®

- MPEG I layers 1, 2, and 3 (MP3)

- Windows Media® and Windows Media Pro audio

- Audio DACs, input switch, and equalizer

• Ethernet MAC and PHY

• Integrated DVB-T COFDM terrestrial demodulator:

- Standards compliance: ETSI EN 300 744, Nordig Unified v1.0.3, DTG D-Book 5

compliant

- Excellent Doppler performance

- Active impulse noise suppression

• Integrated PAL/SECAM Demodulator

• PAL decoder with a 3D/2D comb

• Direct PC input support up to 1600 x 1200 UXGA

• Integrated dual-link LVDS transmitters

• Dual USB 2.0

• A 400-MHz 32-bit MIPS dual CPU with two 32-KB instruction caches

and a combined 64-KB data cache with 128-KB L2 cache

Sound system output is supplying 2x8W (10%THD) for stereo 8

Ω speakers

5

Page 6

Supported peripherals are:

• 1 RF input VHF I, VHF III, UHF @ 75Ohm(Common)

• 1 Side AV (CVBS, R/L_Audio)

• 2 SCART socket(Common)

• 1 YPbPr (Common)

• 1 Side S-Video(Common)

• 1 PC input(Common)

• 4 HDMI 1.3 input(Common)

• 1 Common interface(Common)

• 1 Optic S/PDIF output(Common)

• 1 Stereo audio input for PC(Common)

• 1 Subwoofer output(Common)

• 1 Headphone(Common)

• 2 USB(Common)

• 1 Bluray/DVD(Optional)

• 1 Ethernet-RJ45 (Common)

• 1 External Touchpad(Common)

2. TUNER

FT 2112/3/8/9 are newly developed Half-NIM modules designed for both digital

(DVB-T / T2 and DTMB for terrestrial China) and analog TV reception in compliance with

the European ATV standards for analogue, as well as with the terrestrial standard ETS 300

744 for DVB-T and the new terrestrial standard ETS 302 755 for DVB-T2. It consists of a 3band RF tuner, which receives RF signal and down-converts it to an IF frequency of 36MHz

for digital and 38.9MHz for analog IF. The analogue IF output can directly drive a SAW

filter. A digital IF Stage, which consists of one SAW filter & gain-controllable IF that offers a

sufficient output level to be connected directly to an A/D converter.

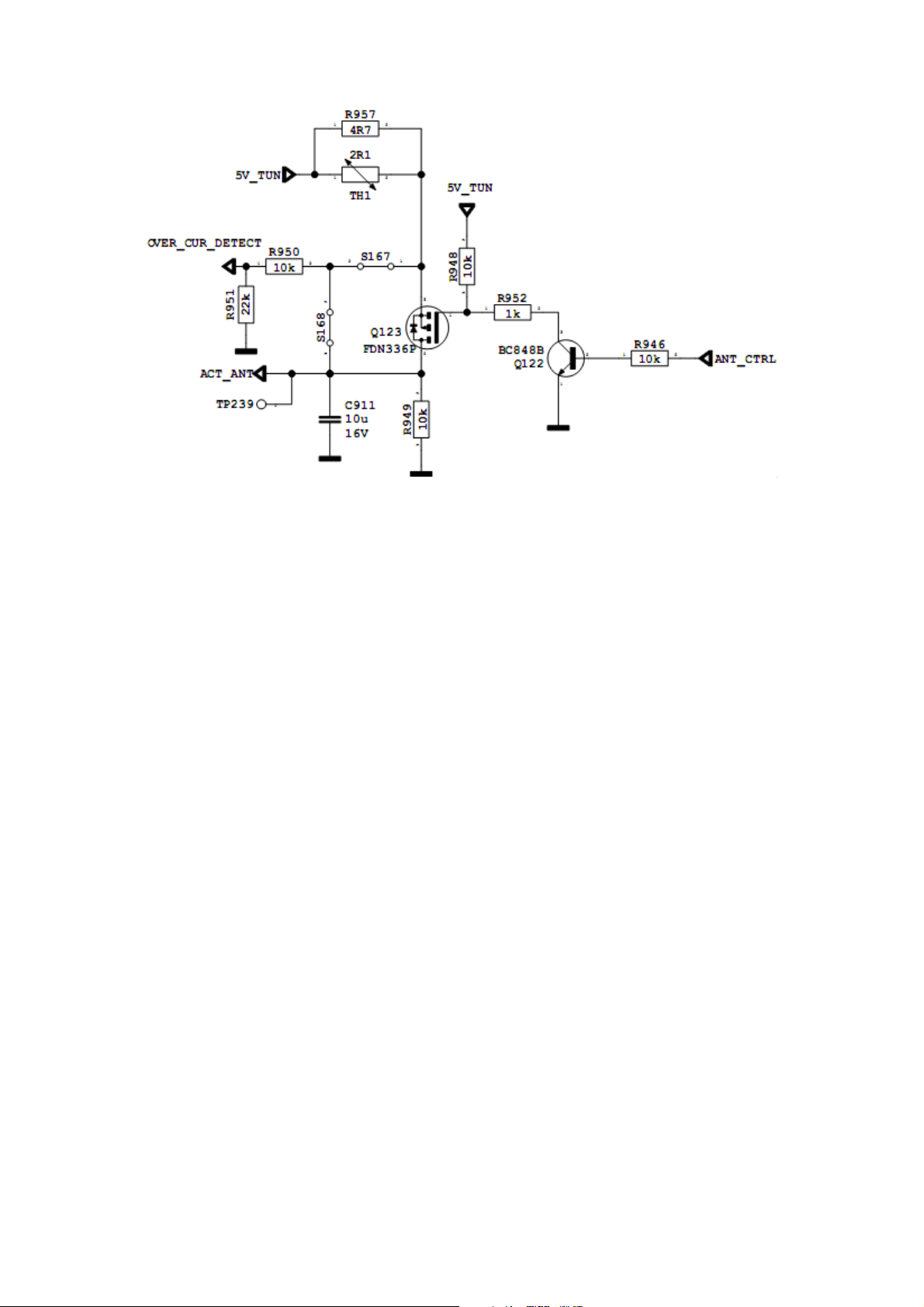

In active antenna option, the following circuit are used. ANT_CTRL pin is controlled by

microcontroller. If ANT_CTRL is low, ANT_PWR will be low. If ANT_CTRL is high,

ANT_PWR will be high. OVER_CUR_DETECT pin is a monitor for short circuit in antenna.

OVER_CUR_DETECT is low, ANT_CTRL will be low, so ANT_PWR will be low. Finally,

short circuit protection is done by circuits and microcontroller.

6

Page 7

Active Antenna Circuit

1.1. Features of FT2112

• Digital DVB-T T2, DTMB & analogue (48.25MHz to 863.25MHz) reception

• Single 5V supply voltage only

• Built-in 5-33V DC-DC converter

• Single power supply to the RF tuner & IF VGA amplifier section

• Bus Control switch-able RF AGC function:

a) Wide Band AGC for optimum strong signal performance

b) Conventional AGC for optimum analog reception

• RF AGC information via I2C Bus

• Tuner power standby mode via I2C Bus

• Small size (56 mm x 29 mm x 10 mm)

• I2C (SDA & SCL) bus control interface

• ROHS compliant

7

Page 8

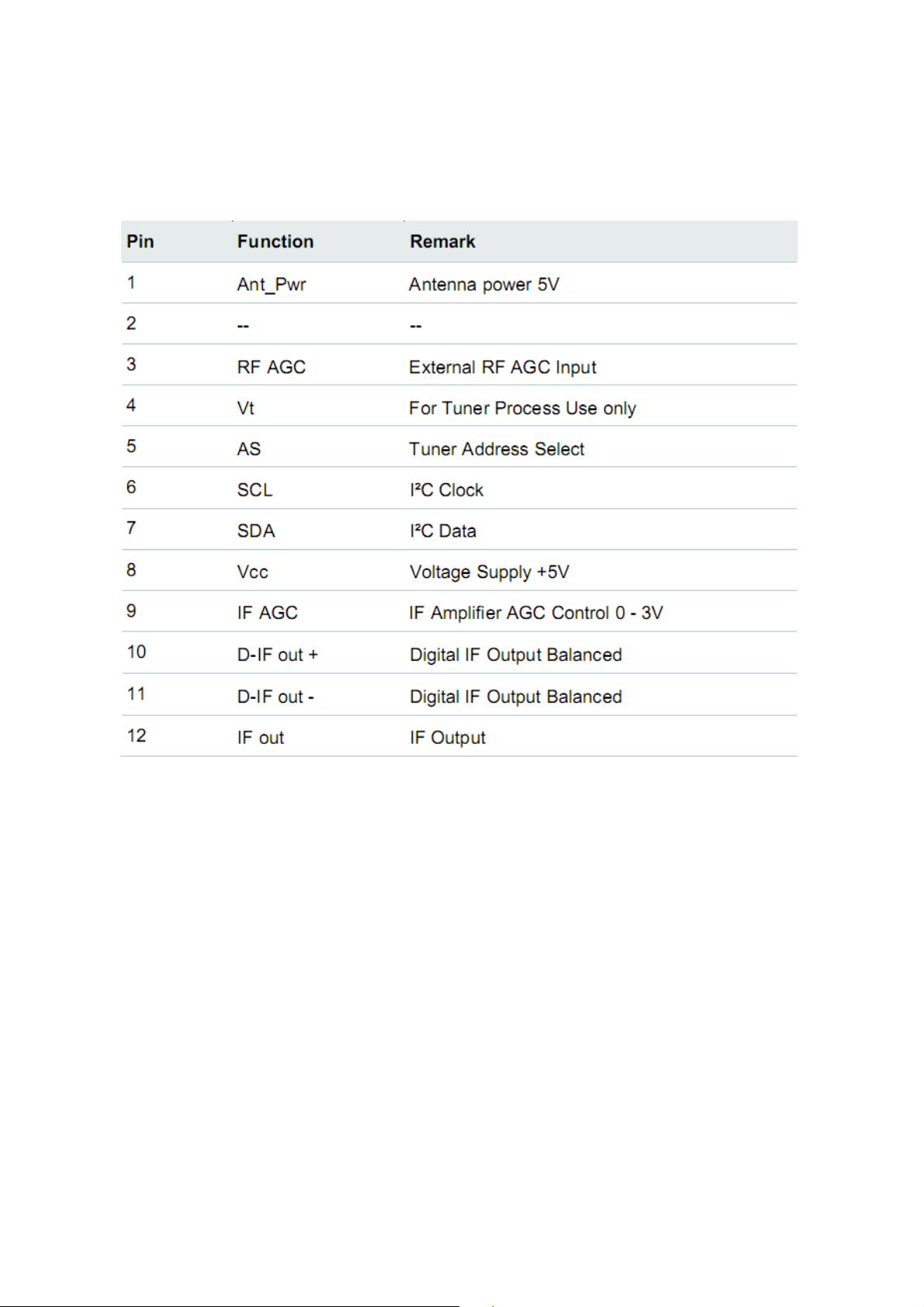

1.2. Tuner Pinning

3. AUDIO AMPLIFIER STAGES

A. MAIN AMPLIFIER (TPA3110)

a. General Description

17MB70 uses TPA 3110 15-W filter-free stereo Class-D audio power amplifier for main

audio output. The TPA3110D2 is a 15-W (per channel) efficient, Class-D audio power

amplifier for driving bridged-tied stereo speakers. Advanced EMI Suppression Technology

enables the use of inexpensive ferrite bead filters at the outputs while meeting EMC

requirements. SpeakerGuard™ speaker protection circuitry includes an adjustable power

limiter and a DC detection circuit. The adjustable power limiter allows the user to set a

"virtual" voltage rail lower than the chip supply to limit the amount of current through the

speaker. The DC detect circuit measures the frequency and amplitude of the PWM signal and

shuts off the output stage if the input capacitors are damaged or shorts exist on the inputs.

8

Page 9

The TPA3110D2 can drive stereo speakers as low as 4

TPA3110D2, 90%, eliminates the need for an external heat sink when playing music. The

outputs are also fully protected against shorts to GND, VCC, and output-to-output. The shortcircuit protection and thermal protection includes an auto-recovery feature.

b. Features

• 15-W/ch into an 8-Ω Loads at 10% THD+N From a 16-V Supply

• 10-W/ch into 8-Ω Loads at 10% THD+N From a 13-V Supply

• 30-W into a 4-Ω Mono Load at 10% THD+N From a 16-V Supply

• 90% Efficient Class-D Operation Eliminates Need for Heat Sinks

• Wide Supply Voltage Range Allows Operation from 8 V to 26 V

• Filter-Free Operation

• SpeakerGuard™ Speaker Protection Includes Adjustable Power Limiter plus DC Protection

• Flow Through Pin Out Facilitates Easy Board Layout

• Robust Pin-to-Pin Short Circuit Protection and Thermal Protection with Auto Recovery

Option

• Excellent THD+N / Pop-Free Performance

Ω. The high efficiency of the

• Four Selectable, Fixed Gain Settings

• Differential Inputs

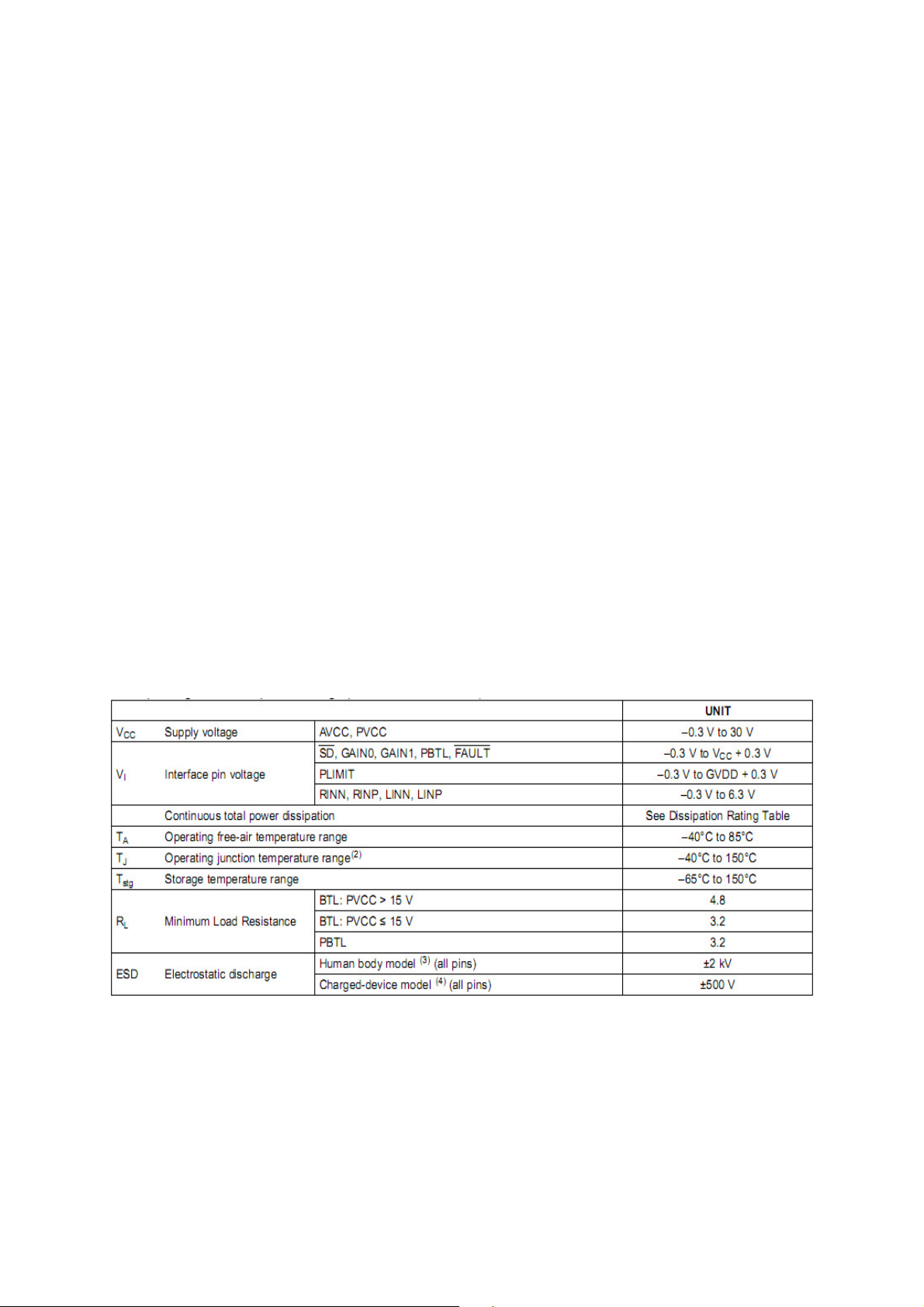

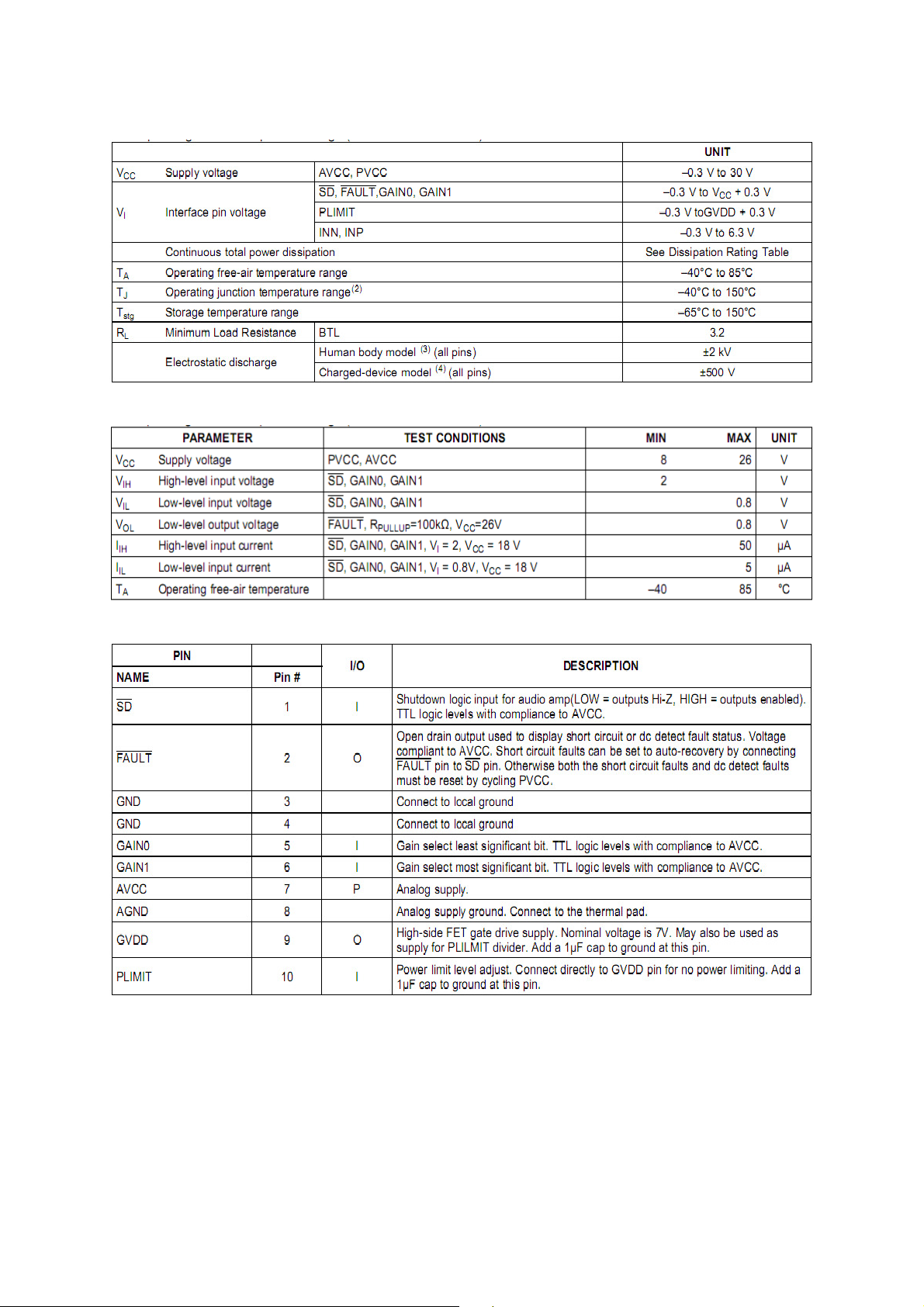

c. Absolute Ratings

9

Page 10

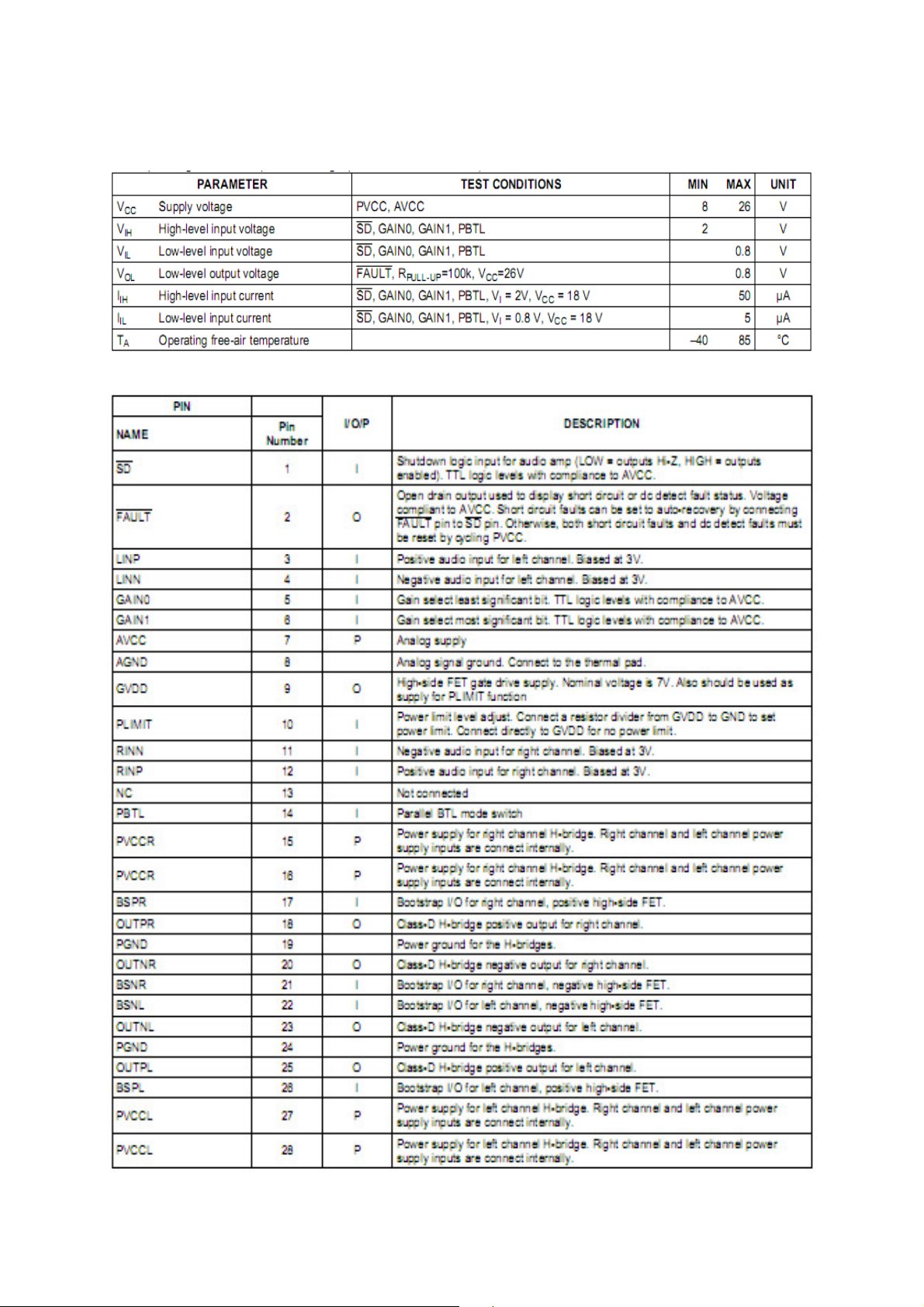

d. Recommended Operating Conditions

e. Pin Functions

10

Page 11

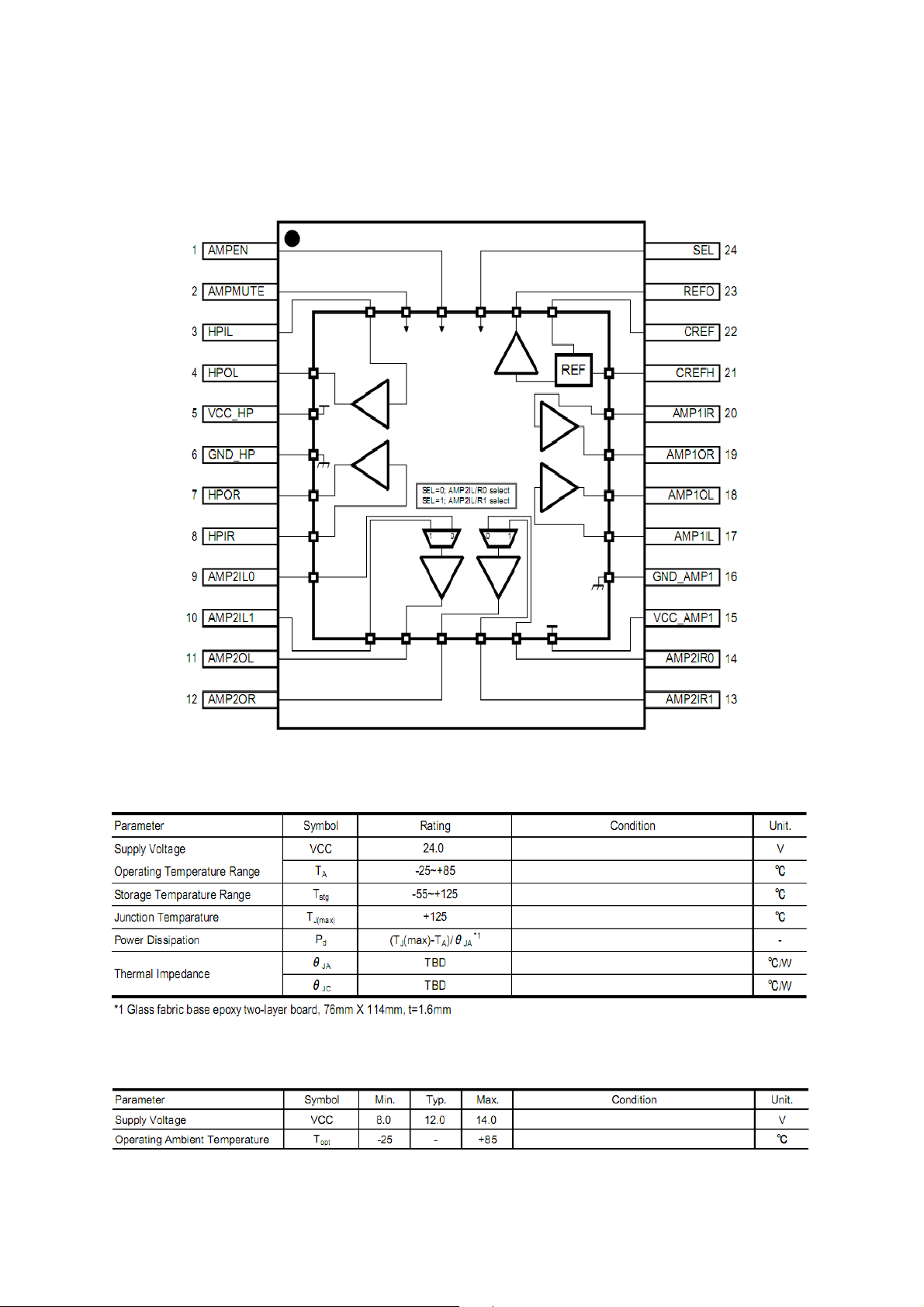

B. LINE-OUT and HEAD-PHONE AMPLIFIER STAGE (CXA3813N)

a. Functional Block Diagram

b. Absolute Ratings

c. Recommended Operating Conditions

11

Page 12

d. Pin Functions

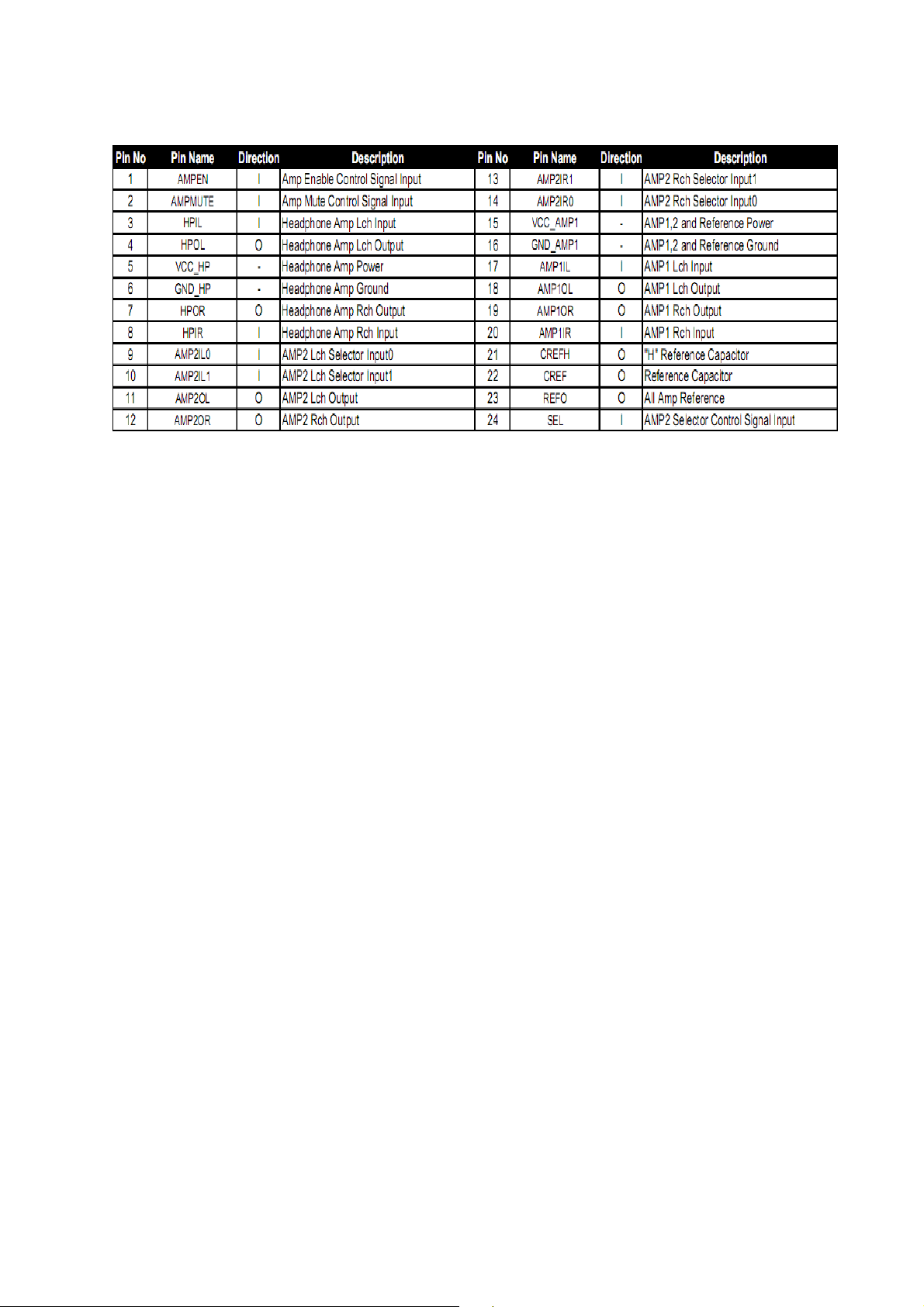

C. SUBWOOFER AMPLIFIER STAGE (TPA3112)

a. General Description

The TPA3112D1 is a 25-W efficient, Class-D audio power amplifier for driving a bridge tied

speaker. Advanced EMI Suppression Technology enables the use of inexpensive ferrite bead

filters at the outputs while meeting EMC requirements. SpeakerGuard speaker protection

system includes an adjustable power limiter and a DC detection circuit. The adjustable power

limiter allows the user to set a "virtual" voltage rail lower than the chip supply to limit the

amount of current through the speaker. The DC detect circuit measures the frequency and

amplitude of the PWM signal and shuts off the output stage if the input capacitors are

damaged or shorts exist on the inputs. The TPA3112D1 can drive a mono speaker as low as

4Ω. The high efficiency of the TPA3112D1, > 90%, eliminates the need for an external heat

sink when playing music. The outputs are fully protected against shorts to GND, VCC, and

output-to-output. The short-circuit protection and thermal protection includes an autorecovery feature.

b. Features

• 25-W into an 8-Ω Load at < 0.1% THD+N Froma 24V Supply

• 20-W into an 4-Ω Load at 10% THD+N From a12-V Supply

• 94% Efficient Class-D Operation into 8-Ω LoadEliminates Need for Heat Sinks

• Wide Supply Voltage Range Allows Operationfrom 8 to 26 V

• Filter-Free Operation

• SpeakerGuard™ Speaker Protection IncludesAdjustable Power Limiter plus DC Protection

• Flow Through Pin Out Facilitates Easy BoardLayout

• Robust Pin-to-Pin Short Circuit Protection andThermal Protection with Auto-Recovery

Option

• Excellent THD+N/ Pop Free Performance

• Four Selectable, Fixed Gain Settings

• Differential Inputs

12

Page 13

c. Absolute Ratings

d. Recommended Operating Conditions

e. Pin Functions

13

Page 14

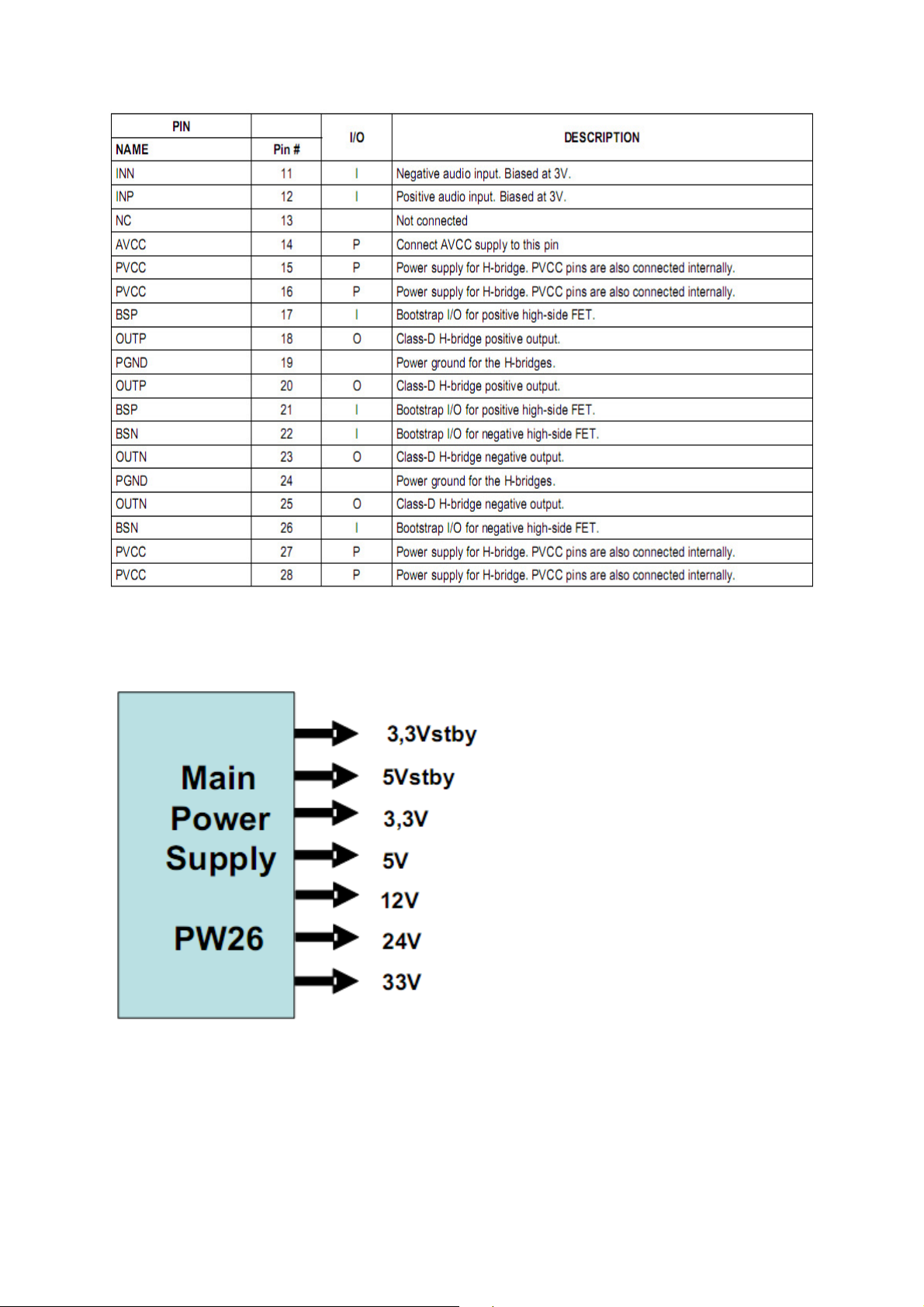

4. POWER STAGE

17MB70 general power managment

block diagram is shown below.

17PW26 power board is used in 32”

17MB70 TV sets.

3,3V stby, 5V stby, 3,3V, 5V, 12V,

24V and 33V can be generated by

PW26.

Below blocks are generated by stepdowns and regulators on MB70

board.

14

Page 15

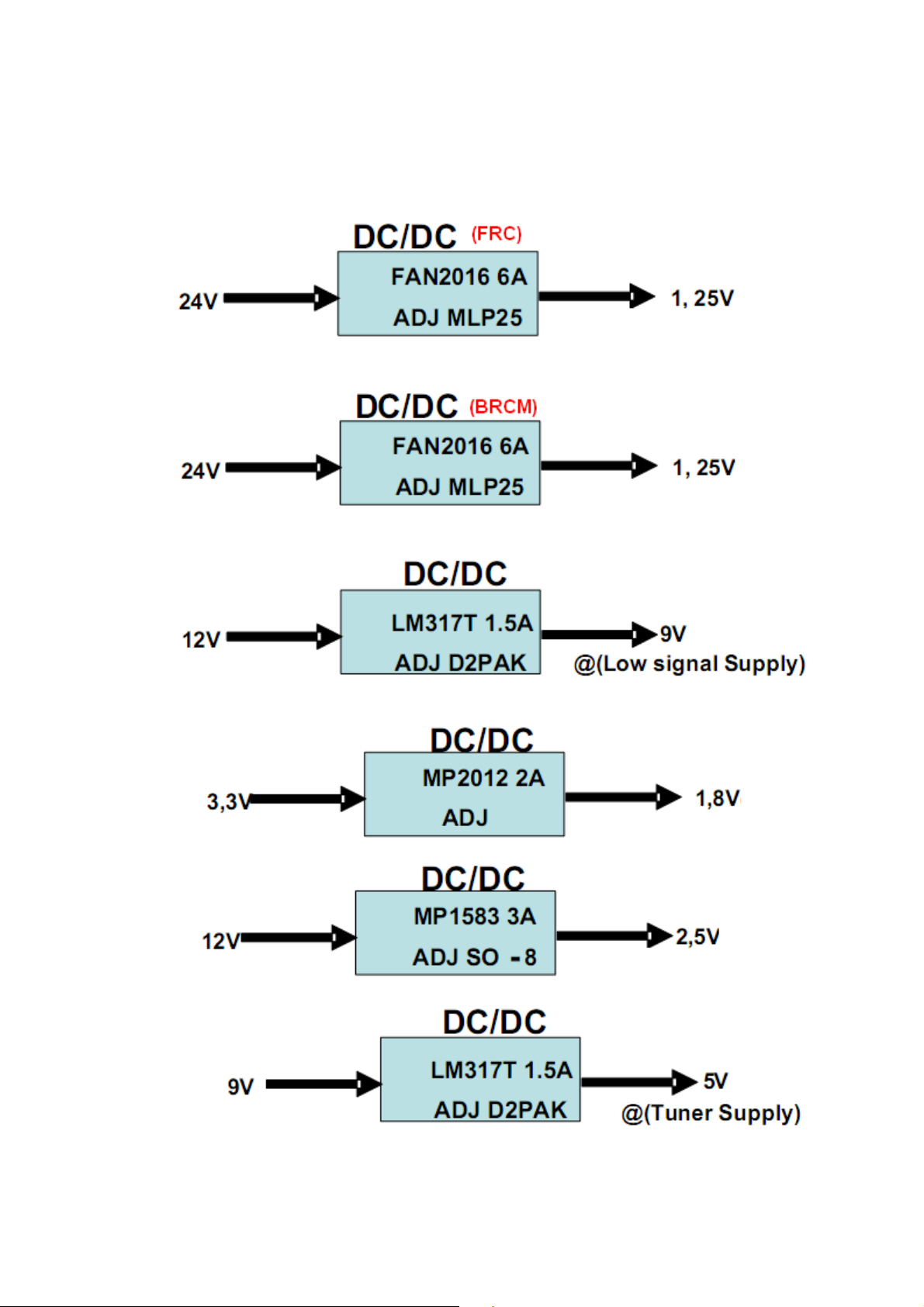

Power Blocks on MB70:

Below blocks are generated by step-downs and regulators on MB70 board.

15

Page 16

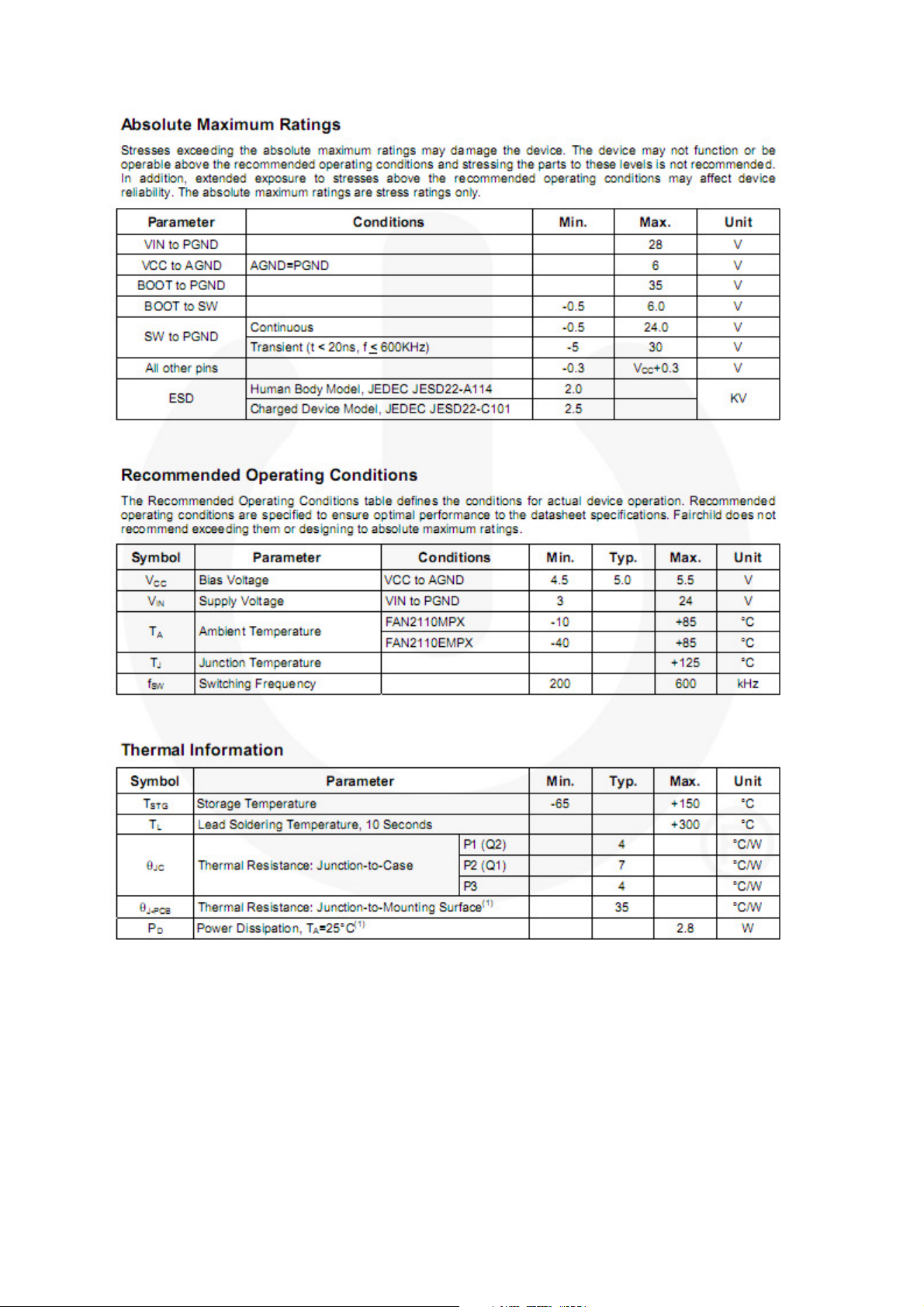

FAIRCHILD FAN2110 (U19-U20)

a) General Description

16

Page 17

17

Page 18

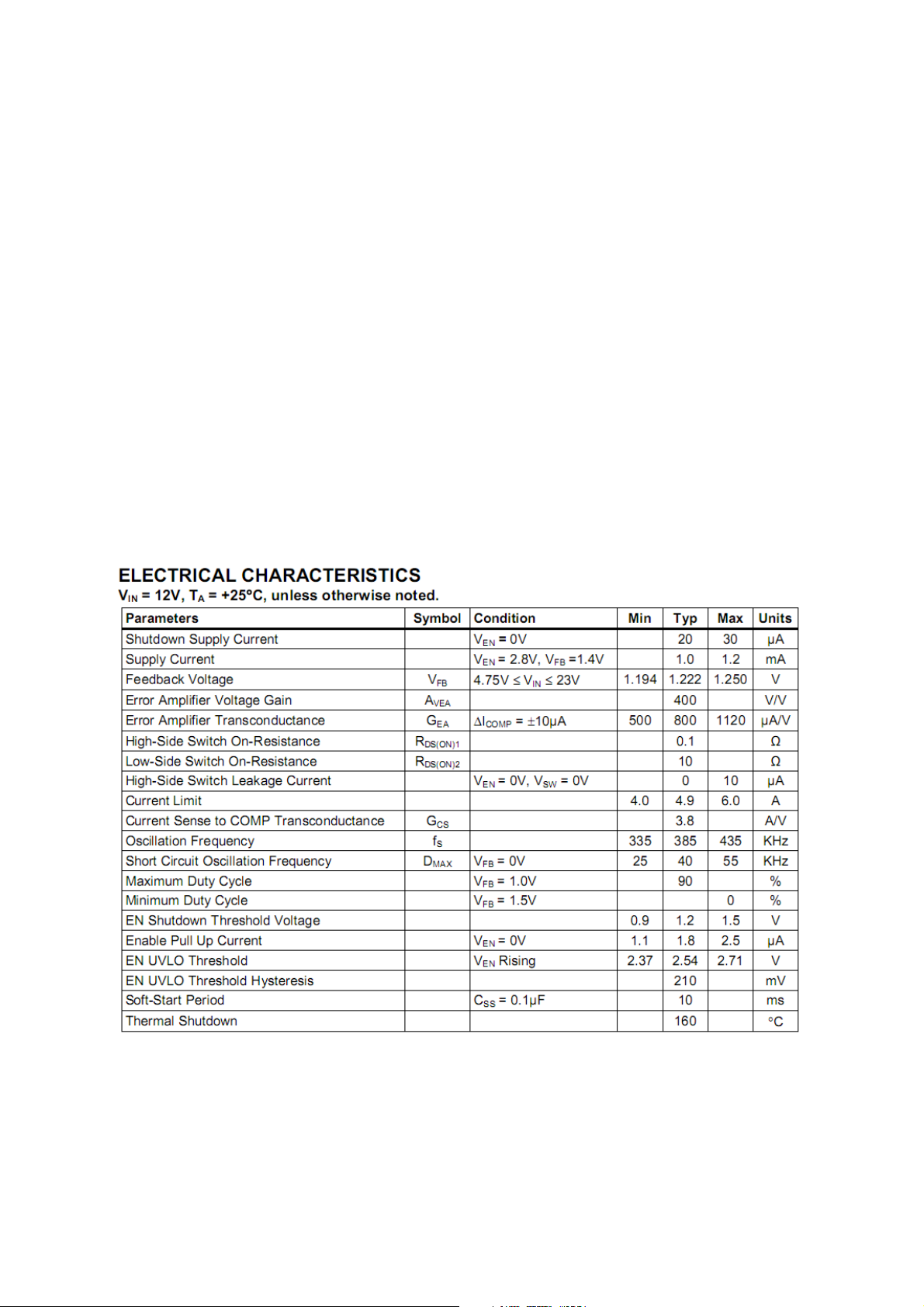

MP1583 (U38)

DESCRIPTION

The MP1583 is a step-down regulator with abuilt-in internal Power MOSFET. It achieves 3A

of continuous output current over a wide input supply range with excellent load and line

regulation.

Current mode operation provides fast transient response and eases loop stabilization.

18

Page 19

Fault condition protection includes cycle-by-cycle current limiting and thermal shutdown. An

adjustable soft-start reduces the stress on the input source at startup. In shutdown mode the

regulator draws 20µA of supply current. The MP1583 requires a minimum number of

external components, providing a compact solution.

FEATURES

• 3A Output Current

• Programmable Soft-Start

• 100m

• Stable with Low ESR Output Ceramic Capacitors

• Up to 95% Efficiency

• 20µA Shutdown Mode

• Fixed 385KHz Frequency

• Thermal Shutdown

• Cycle-by-Cycle Over Current Protection

• Wide 4.75V to 23V Operating Input Range

• Output Adjustable from 1.22V to 21V

• Under-Voltage Lockout

Ω Internal Power MOSFET Switch

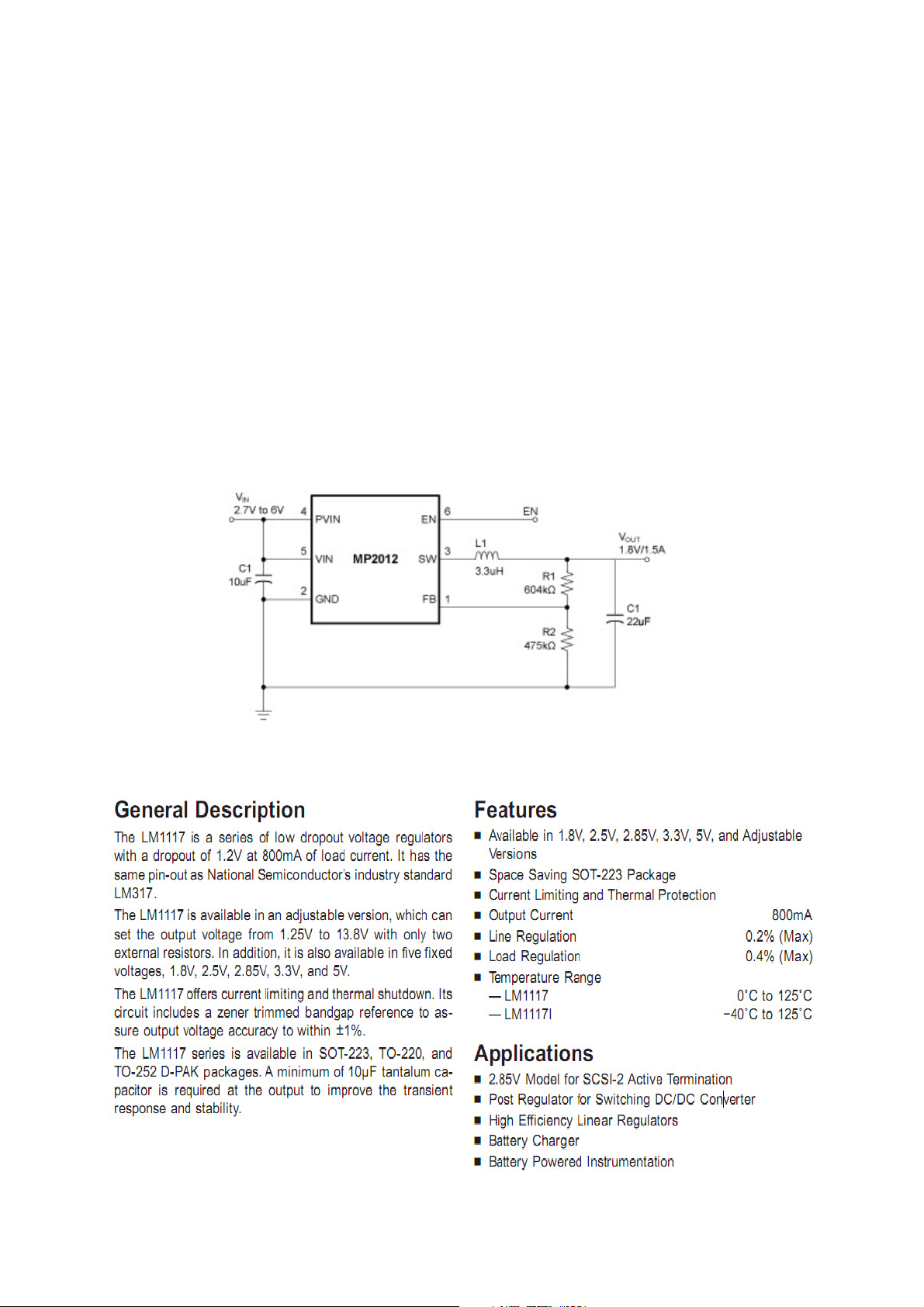

MP2012 (U39)

The MP2012 is a fully integrated, internally compensated 1.2MHz fixed frequency PWM

step-down converter. It is ideal for powering portable equipment that runs from a single cell

Lithium-Ion (Li+) Battery, with an input range from 2.7V to 6V. The MP2012 can provide up

to 1.5A of load current with output voltage as low as 0.8V. It can also operate at 100% duty

19

Page 20

cycle for low dropout applications. With peak current mode control and internal

compensation, the MP2012 is stable with ceramic capacitors and small inductors. Fault

condition protection includes cycle-by-cycle current limiting and thermal shutdown. MP2012

is available in the small 6-pin 3mmx3mm QFN package.

• 2.7-6V Input Operation Range

• Output Adjustable from 0.8V to VIN

µA Max Shutdown Current.

• 1

• Up to 95% Efficiency

• 100% Duty Cycle for Low Dropout Applications

• 1.2MHz Fixed Switching Frequency

• Stable with Low ESR Output Ceramic Capacitors

• Thermal Shutdown

• Cycle-by-Cycle Over Current Protection

• Short Circuit Protection

• Available in 6-pin 3x3mm QFN

LM1117 (U21-U22-U23-U24)

20

Page 21

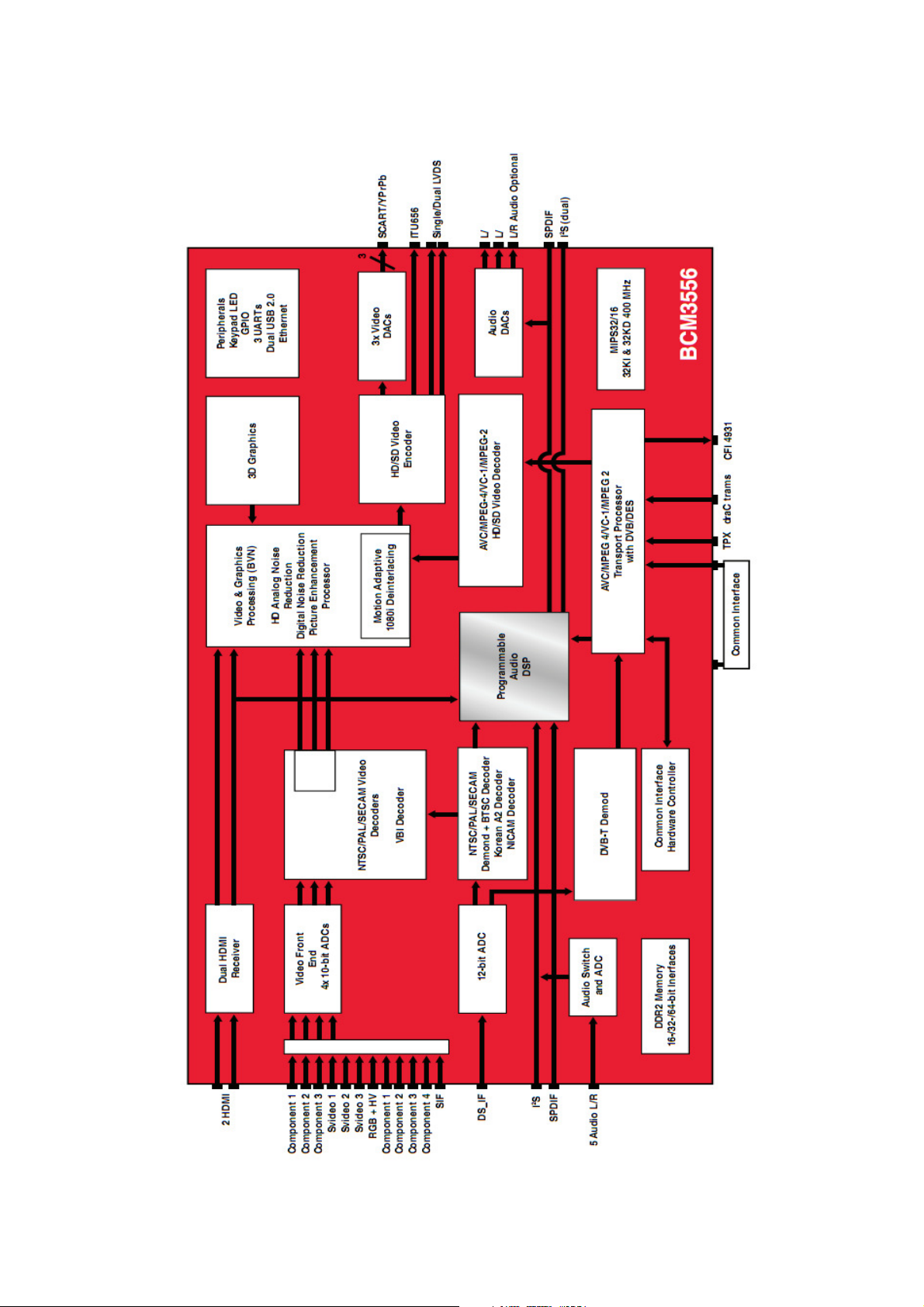

5. MICROCONTROLLER(Broadcom)

BCM3556

a) General Description

The BCM3556 is the next generation of System-on-a-Chip (SoC) Digital Television (DTV)

products from Broadcom® with 1080p60 input and output capability targetedfor the EU

Market. It combines a high level of integration with best-of-class picture quality, enabling TV

manufacturers to reduce overall system cost (BOM) and improve picture quality, all with a

single SoC.

The BCM3556 combines DVB-T COFDM terrestrial and PAL/SECAM demodulators, two

DVI/HDMI receivers, a transport processor, a digital audio processor, 3D/2D graphics

processing, Ethernet MAC and PHY, digital processing of analog video and audio, analog

video digitizer and DAC functions, stereo high-fidelity audio DACs, a 400-MHz dualthreaded MIPS processor, and a peripheral control unit providing a variety of television

control functions. The BCM3556 also features an advanced video decoder

capable of supporting high-definition AVC, VC-1, and DVB-T MPEG-2 streams.

The integration of the DVB-T COFDM terrestrial demodulator reduces the overall cost of the

external tuner module, resulting in cost savings for the customer. The BCM3556also

integrates four 10-bit ADCs with integrated front-end analog muxing that accept four CVBS

inputs, three S-video inputs, three component inputs, one PC input, one full SCART input

with fast blanking, and one Sound IF (SIF) input at the same time without the requirement for

any off-chip muxing ICs. The BCM3556 offers two HDMI 1.3a receivers, a motion adaptive

deinterlacer, HD Analog Noise Reduction, and an analog video decoder with 3D comb for

PAL and Y/C separation for SECAM.

The multiformat video decoder in the BCM3556 is capable of supporting high-definition

AVC, VC-1, and DVB-T MPEG-2 streams. AVC support is up to High Profile Level 4.1.

New tools in the AVC Fidelity Range extensions are supported, including 8x8 transform and

spatial prediction modes and adaptive quantization matrix. The video decoder also supports

high-definition VC-1 (Advanced Profile Level 3, Main, and Simple profiles) and DVBTcompliant MPEG-2, Main Profile at Main and High Levels. The BCM3556 has an advanced

programmable audio processor capable of decoding a broad range of formats including Dolby

Digital, Dolby Digital Plus, AAC 5.1, AAC+ Level 2, AAC+ Level 4, WMA, and MPEG-1

Layer 1, 2, and 3 with simultaneous pass-through support.

The BCM3556 also supports 3D SRS Audio and includes an analog audio decoder for BTSC

and A2 formats. The BCM3556 also integrates an analog audio switch that accepts six stereo

inputs. In addition, the SoC supports SPDIF and I2S inputs. One SPDIF, two I2S, and three

analog audio outputs are available.

The SoC family also has an integrated advanced Picture Enhancement Processor (PEP) to

improve sharpening and perform picture post-processing functions (e.g., autoflesh, green

boost, black and blue stretch). The PEP engine is fully programmable and can be optimized

by the TV manufacturer to meet their respective quality requirements. Also integrated is a

video encoder for NTSC and an advanced 2D/3D graphics for OSD acceleration.

21

Page 22

The BCM3556 supports direct PC inputs up to UXGA 1600x1200 formats with autophase

and automode detection and supports dual LVDS outputs to support 1080p60 panels.

The BCM3556 integrates a 400-MHz 32-bit MIPS dual CPU with two 32-KB

instructioncaches and a combined 64-KB data cache with a 128-KB L2 cache, and a 32-bit

800/1066-MHz DDR2. The BCM3556 also supports an 8-bit external NAND Flash interface

and SPI Flash interface for booting. Integrated peripherals include two USB2.0 ports, three

UARTs, controllers for SPI, BSC, keypad, LED and IR Tx/Rx, and an Ethernet port with

MAC and integrated PHY.

The BCM3556 is available in several package options: WXGA and FHD, PIP and non-PIP, or

MPEG-only and combined AVC/MPEG-2.

b) Features

• Advanced multiformat decoder supporting the following:

- H.264/AVC Main and High Profile to Level 4.1 (HD), Level 3.1 (SD)

- HD/SD AVS Jizhun Profile Levels 2.0, 4.0, and 6.0

- VC-1 Advanced Profile @ Level 3, simple and main profiles

- HD/SD MPEG-2 Main Profile at Main and High levels

- MPEG still image decode

- HD DivX® 3.11/4.11/5.x/6x/Home Theater

• 3D/2D OpenGL® ES 1.0- compliant graphics core

• Integrated Video Processing:

- 3D Color management

- Digital, Analog, and Mosquito Noise Reduction

- 1080i motion adaptive deinterlacing with 3:2/2:2 pull-down

- True 10-bit video carried through system

• Dual HDMI 1.3a receivers

• Extensive audio support:

- AAC+ Level 2, AAC-HE

- Dolby® Digital, Dolby Digital Plus, Trusurround XT®

- MPEG I layers 1, 2, and 3 (MP3)

- Windows Media® and Windows Media Pro audio

- Audio DACs, input switch, and equalizer

• Ethernet MAC and PHY

• Integrated DVB-T COFDM terrestrial demodulator:

- Standards compliance: ETSI EN 300 744, Nordig Unified v1.0.3, DTG D-Book 5

compliant

- Excellent Doppler performance

- Active impulse noise suppression

• Integrated PAL/SECAM Demodulator

• PAL decoder with a 3D/2D comb

• Direct PC input support up to 1600 x 1200 UXGA

• Integrated dual-link LVDS transmitters

• Dual USB 2.0

• A 400-MHz 32-bit MIPS dual CPU with two 32-KB instruction caches and a combined 64

KB data cache with 128-KB L2 cache

22

Page 23

c) BCM3556 - Block Diagram

23

Page 24

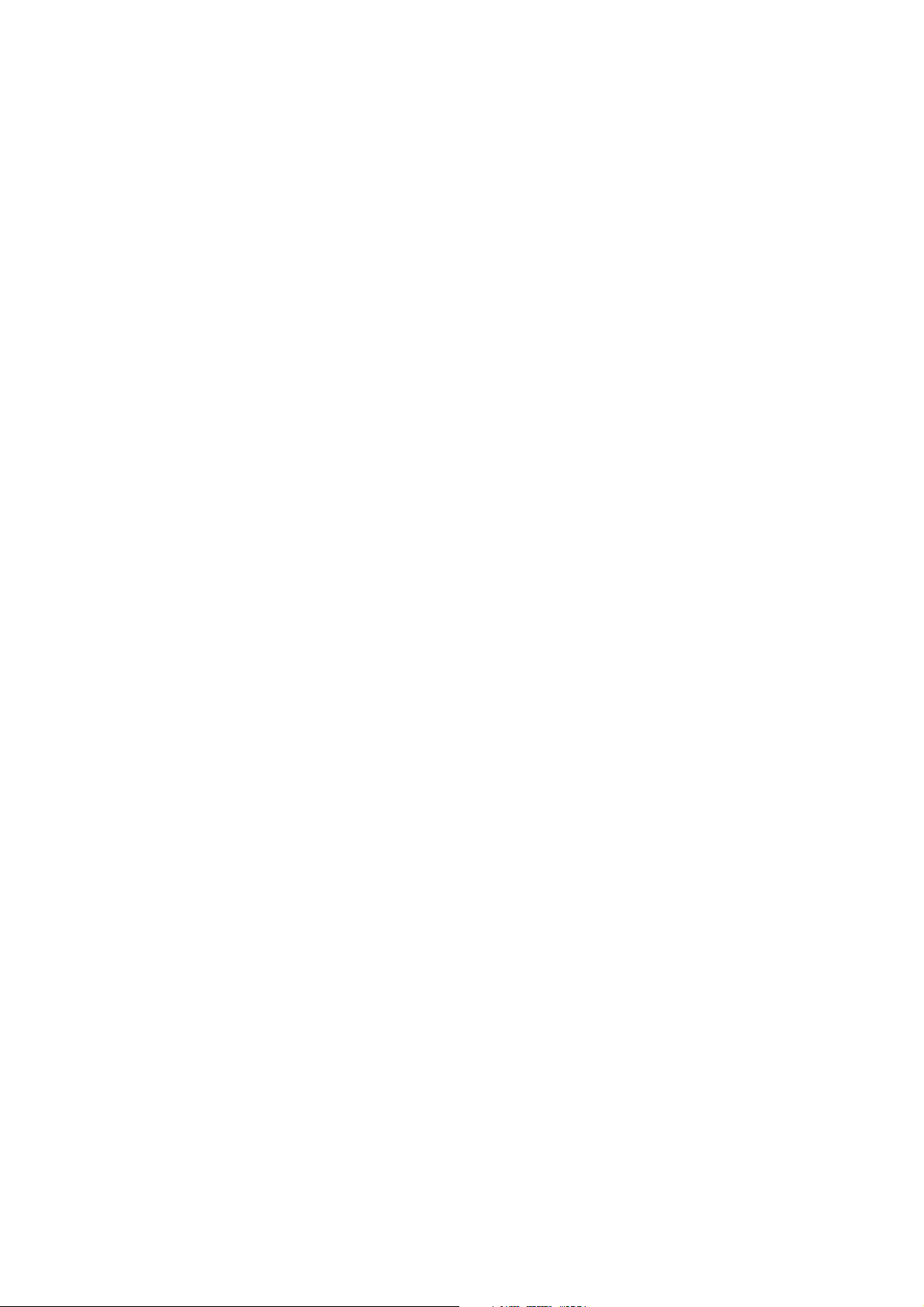

6. SATELLITE RECEIVER (Broadcom)

BCM4505

a) General Description

The BCM4505 is a fully integrated satellite receiver single-chip solution targeted at

multituner advanced modulation satellite receiver systems and ideally suited for new

generation satellite receivers and integrated multifunction Home Media Centers. The

BCM4505 integrates a CMOS tuner and advanced modulation decoder supporting DVB-S2

Broadcast, DVB-S, DIRECTV, and 8PSK Turbo applications. The highly integrated tuner

section is based on existing volume-production Broadcom technologies and a directconversion technology to reduce external components and increase performance.The

BCM4505 is designed to support the full 1-45 Msps DVB operating range with support for

250 to 2150 MHz input frequencies. It contains two 8-bit A/D converters, all-digital variablerate QPSK/8PSK receivers, an advanced modulation LDPC/BCH and Turbo FEC decoder,

and a DVB-S compliant FEC decoder. All required RAM is integrated and all required clocks

are generated on-chip from a single reference crystal. The baseband IQ analog waveforms

from the tuner section are sampled by the integrated 8-bit A/D converters and resampled by

the integrated interpolative digital filter banks.

Optimized soft decisions are then fed into either a DVB-S-compliant FEC decoder, or an

advanced-modulation DVB-S2 LDPC/BCH or Turbo decoder. The final error-corrected

output is delivered in MPEG-2 transport format. The output clock is generated by an on-chip

PLL for low-jitter operation and glueless integration with Broadcom's high definition audio

video subsystems, such as the BCM7401 and the BCM7402. The communication link

sections include an on-chip microcontroller for all system configuration, acquisition, control,

monitoring and diagnostics functions, as well as an integrated DiSEqC 2.x controller for 2way communication with an LNB, and a single FSK transceiver for communication with

ODUs that support multiple LNB configurations over a single coax connection.The

BCM94505 reference design is available for easy system design and testing using the

BCM4505 advanced modulation receiver chip.

b) Features

• Dual direct conversion satellite tuners

• Direct conversion architecture in standard CMOS process

• Supports QPSK and 8PSK demodulation

• Input frequency range: 250 to 2150 MHz

• Integrated 8-bit A/D converters

• Integrated advanced demodulation decoder

• DVB-S2 Broadcast, DVB-S, 8PSK Turbo

• Data Rates:

• DVB-S: 1-45 Msps

• DVB-S2: 1-45 Msps

• 8PSK Turbo: 2-30 Msps

• Code Rates: 1/4, 1/3, 2/5, 1/2,3/5, 2/3, 3/4 , 5/6, 7/8, 8/9, 9/10

• Integrated DiSEqC 2.x transceivers

24

Page 25

• On-chip microcontroller for acquisition and tracking

• 128-pin epLQFP package

c) BCM4505 - Block Diagram

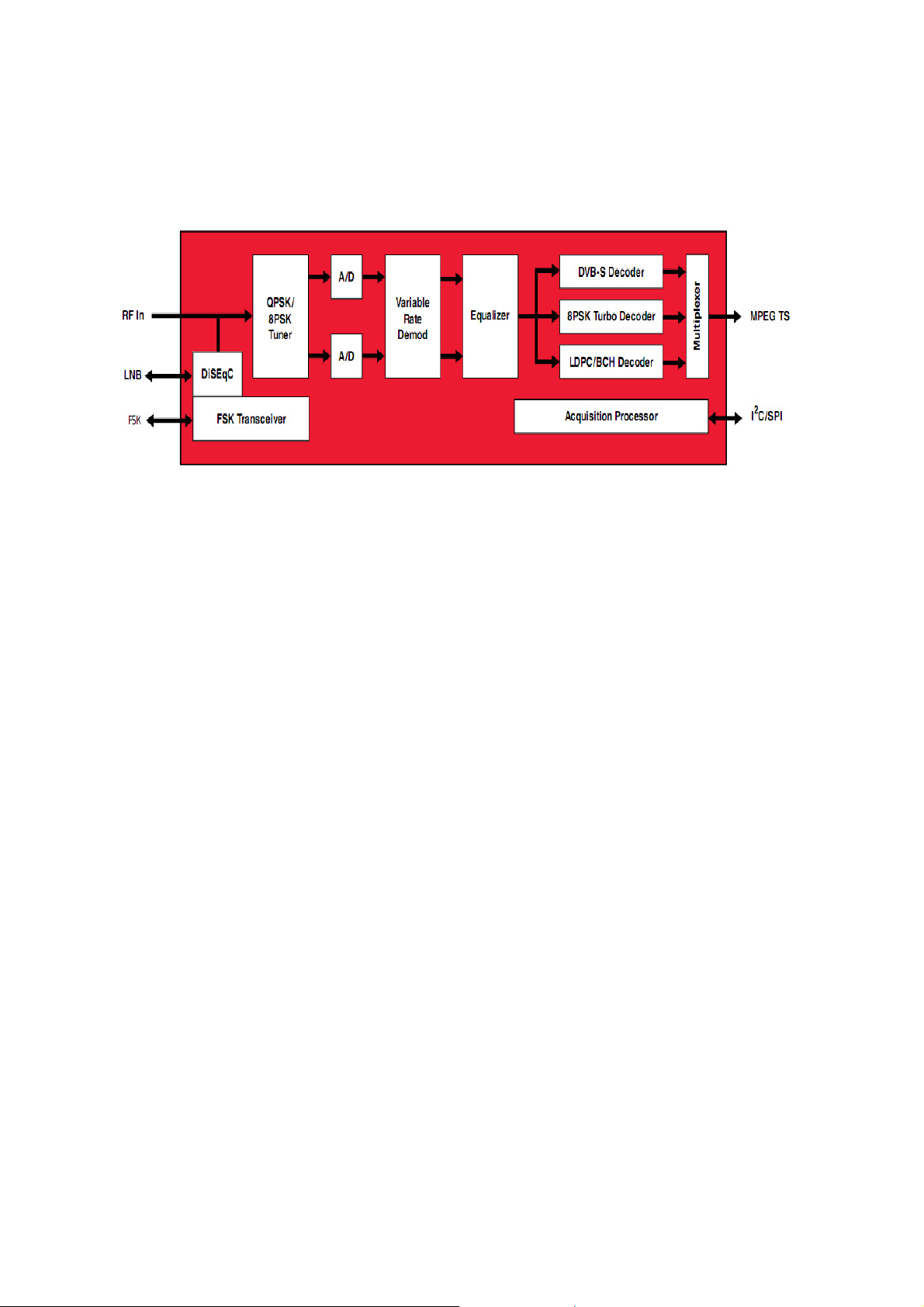

7. VIDEO BACK-END PROCESSOR (Trident)

PNX5120EH

a) General Description

The PNX5120EH is an advanced video picture improvement IC and the world's first solution,

NXP’s Motion Accurate Picture Processing (MAPP), to combine movie judder cancellation,

motion sharpness and vivid color management in a single device. Aimed primarily at digital

and hybrid flat panel televisions in the mid-end and high-end European,Asian and U.S.

consumer markets, it complies with relevant industry standards.LCD TVs represent a huge

and growing market, and the PNX5120EH offers manufacturers a unique combination of

richer color, dynamic motion, sensational sharpness, deep contrast, and full HD resolution.

Moreover, you can easily tailor that balance via the Automatic Picture Control tool (delivered

by NXP as part of a separate System Design-in Toolkit) to meet your own image quality

requirements.

b) Features

• Single 27 MHz crystal clock input for all internal generated clocks

• Three TriMedia TM3271 400 MHz, 32-bit VLIW media-processing cores with:

o five instructions per clock cycle

o 32 kB instruction cache

o 64 kB data cache

• Integrated DDR2 SDRAM controller, 32-bit wide, up to 366 MHz clock (DDR2-800),

supporting 32 MB, 64 MB, 128 MB, and 256 MB single-rank memory configurations

• Separately licensed, the PNX5120EH comes with an easy-to-use System Design-in

Toolkit (SDT), which includes the NXP Picture Quality Tuning Tool, firmware image

containing the NXP proprietary Picture Improvement features, and GPL-licensed UBoot Bootloader software.

25

Page 26

• DDR2-400 to DDR2-800 data rates supported

• PCI/XIO (V2.2) operating at 33 MHz

• Two UARTs

• Two I2C DMA interfaces (100 kHz/400 kHz); the second I2C can be used as a

debugging interface

• 16 GPIO pins

• Five PWM outputs

• Support for 8-bit NOR flash up to 64 MB

• Support for 8-bit/16-bit NAND flash up to 128 MB

c) PNX5120EH - Block Diagram

26

Page 27

8. FPGA (Spartan-3E)

XC3S1200E

a) General Description

The Spartan™-3E family of Field-Programmable Gate Arrays (FPGAs) is specifically

designed to meet the needs of high volume, cost-sensitive consumer electronic applications.

The five-member family offers densities ranging from 100,000 to 1.6 million system gates,

The Spartan-3E family builds on the success of the earlier Spartan-3 family by increasing the

amount of logic per I/O, significantly reducing the cost per logic cell. New features

improve system performance and reduce the cost of configuration. These Spartan-3E

enhancements, combined with advanced 90 nm process technology, deliver more

functionality and bandwidth per dollar than was previously possible, setting new standards in

the programmable logic industry. Because of their exceptionally low cost, Spartan-3E FPGAs

are ideally suited to a wide range of consumer electronics applications, including broadband

access, home networking, display/projection, and digital television equipment. The Spartan3E family is a superior alternative to mask programmed ASICs. FPGAs avoid the high initial

cost, the lengthy development cycles, and the inherent inflexibility of conventional ASICs.

Also, FPGA programmability permits design upgrades in the field with no hardware

replacement necessary, an impossibility with ASICs.

b) Features

• Very low cost, high-performance logic solution for high-volume, consumer-oriented

applications

• Proven advanced 90-nanometer process technology

• Multi-voltage, multi-standard SelectIO™ interface pins

- Up to 376 I/O pins or 156 differential signal pairs

- LVCMOS, LVTTL, HSTL, and SSTL single-ended signal standards

- 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

- 622+ Mb/s data transfer rate per I/O

- True LVDS, RSDS, mini-LVDS, differential HSTL/SSTL differential I/O

- Enhanced Double Data Rate (DDR) support

- DDR SDRAM support up to 333 Mb/s

• Abundant, flexible logic resources

- Densities up to 33,192 logic cells, including optional shift register or distributed

RAM support

- Efficient wide multiplexers, wide logic

- Fast look-ahead carry logic

- Enhanced 18 x 18 multipliers with optional pipeline

- IEEE 1149.1/1532 JTAG programming/debug port

• Hierarchical SelectRAM™ memory architecture

- Up to 648 Kbits of fast block RAM

- Up to 231 Kbits of efficient distributed RAM

• Up to eight Digital Clock Managers (DCMs)

- Clock skew elimination (delay locked loop)

- Frequency synthesis, multiplication, division

- High-resolution phase shifting

- Wide frequency range (5 MHz to over 300 MHz)

27

Page 28

• Eight global clocks plus eight additional clocks per each half of device, plus abundant lowskew routing

• Configuration interface to industry-standard PROMs

- Low-cost, space-saving SPI serial Flash PROM

- x8 or x8/x16 parallel NOR Flash PROM

- Low-cost Xilinx Platform Flash with JTAG

• Complete Xilinx ISE™ and WebPACK™ development system support

• MicroBlaze™ and PicoBlaze™ embedded processor cores

• Fully compliant 32-/64-bit 33 MHz PCI support

• Low-cost QFP and BGA packaging options

- Common footprints support easy density migration

- Pb-free packaging options

9. PIXELLENCE II

a) General Description

PixellenceII IC is a real-time image processing chip. It is mainly a co-processor sitting at the

back of the video ASSP (i.e. concept IC) in a typical TV chassis. PixellenceII gets the picture

that will otherwise be transmitted to the panel in RGB format and applies Vestel patented

image and video processing algorithms to further enhance the picture. After processing, the

video is transmitted to the 50/60 Hz panel serially through LVDS links and in RGB format.

PixellenceII IC supports Full HD (1920x1080) and WXGA (1366x768) resolutions with 10bit or 8-bit processing modes. PixellenceII is also configurable to other common resolutions

such as 1920x1280, 1680x1050, 1440x900, 1280x1024, 1024x768, 1920x1200, 1600x900.

The PixellenceII IC incorporates following Vestel patented algorithms, functions and

interfaces:

Algorithms:

• Skin-tone detection and correction

• Color Saturation

• Dynamic Contrast Enhancement

• Sharpness & CTI

• De-ringing

• De-blocking

• Temporal Noise Reduction

• Spatial Noise Reduction

• Video Analysis Block

Functions:

• Color Space Conversion

• Color Up-sampling, Color Down-sampling

• Gamma Correction

• OSD Detection Logic

• Display Mode Logic

• Logo

28

Page 29

Interfaces:

• I2C

• JTAG

• Dual-Link LVDS Receiver with Spread Spectrum clocking tolerance

• Dual-Link LVDS Transmitter with Spread Spectrum clocking tolerance

• Miscellaneous function signals (8-bit GPO port)

b) Block Diagram

Main blocks of Pix2Frame are LVDS Rx, Tx and pix2_top modules. Major blocks of

pix2_top module are PixellenceII Core video enhancement engine, I2C Slave interface and

embedded Dynamic RAM (eDRAM, 64Mbit) macro.

10. 1Gb F-die DDR2-1066 SDRAM (U41-U42-U8-U9)

Samsung K4T1G084QF

a) Key Features

• JEDEC standard VDD = 1.8V ± 0.1V Power Supply

•VDDQ = 1.8V ± 0.1V

• 533MHz fCK for 1066Mb/sec/pin

• 8 Banks

• Posted CAS

• Programmable CAS Latency: 4, 5, 6, 7

• Programmable Additive Latency: 3, 4, 5. 6

29

Page 30

• Write Latency(WL) = Read Latency(RL) -1

• Burst Length: 4 , 8(Interleave/nibble sequential)

• Programmable Sequential / Interleave Burst Mode

• Bi-directional Differential Data-Strobe (Single-ended data-strobe is an optional feature)

• Off-Chip Driver(OCD) Impedance Adjustment

• On Die Termination

• Special Function Support

- PASR(Partial Array Self Refresh)

- 50ohm ODT

- High Temperature Self-Refresh rate enable

• Average Refresh Period 7.8us at lower than TCASE 85°C, 3.9us at 85°C < TCASE < 95 °C

• All of products are Lead-free, Halogen-free, and RoHS compliant

The 1Gb DDR2 SDRAM is organized as a 16Mbit x 8 I/Os x 8 banks, 8Mbit x 16 I/Os x 8

banks device. This synchronous device achieves high speed double-data-rate transfer rates of

up to 1066Mb/sec/pin (DDR2-1066) for general applications.

The chip is designed to comply with the following key DDR2 SDRAM features such as

posted CAS with additive latency, write latency = read latency - 1, Off-Chip Driver(OCD)

impedance adjustment and On Die Termination. All of the control and address inputs are

synchronized with a pair of externally supplied differential clocks. Inputs are latched at the

crosspoint of differential clocks (CK rising and CK falling). All I/Os are synchronized with a

pair of bidirectional strobes (DQS and DQS) in a source synchronous fashion. The address

bus is used to convey row, column, and bank address information in a RAS/CAS

multiplexing style. For example, 1Gb(x8) device receive 14/10/3 addressing.

The 1Gb DDR2 device operates with a single 1.8V ± 0.1V power supply and 1.8V ± 0.1V

VDDQ.

The 1Gb DDR2 device is available in 60ball FBGA(x8) and 84ball FBGA(x16).

b) Pinning

30

Page 31

c) Electrical Characteristics

11. 32M x 16 bit DDRII Synchronous DRAM (U28-U29)

EtronTech EM68B16CWPA

a) Key Features

• JEDEC Standard Compliant

• JEDEC standard 1.8V I/O (SSTL_18-compatible)

• Power supplies: VDD & VDDQ = +1.8V ± 0.1V

• Operating temperatue: 0 – 85 °C

• Supports JEDEC clock jitter specification

• Fully synchronous operation

• Fast clock rate: 333/400MHz

• Differential Clock, CK & CK#

• Bidirectional single/differential data strobe

-DQS & DQS#

31

Page 32

• 4 internal banks for concurrent operation

• 4-bit prefetch architecture

• Internal pipeline architecture

• Precharge & active power down

• Programmable Mode & Extended Mode registers

• Posted CAS# additive latency (AL): 0, 1, 2, 3, 4, 5

• WRITE latency = READ latency - 1 tCK

• Burst lengths: 4 or 8

• Burst type: Sequential / Interleave

• DLL enable/disable

• Off-Chip Driver (OCD)

-Impedance Adjustment

-Adjustable data-output drive strength

• On-die termination (ODT)

• RoHS compliant

• Auto Refresh and Self Refresh

• 8192 refresh cycles / 64ms

• Package: 84-ball 10x12.5x1.2mm (max) FBGA

- Pb and Halogen Free

The EM68B16C is a high-speed CMOS Double-Data-Rate-Two (DDR2), synchronous

dynamic random-access memory (SDRAM) containing 512 Mbits in a 16-bit wide data I/Os.

It is internally configured as a quad bank DRAM, 4 banks x 8Mb addresses x 16 I/Os The

device is designed to comply with DDR2 DRAM key features such as posted CAS# with

additive latency, Write latency = Read latency -1, Off-Chip Driver (OCD) impedance

adjustment, and On Die Termination(ODT). All of the control and address inputs are

synchronized with a pair of externally supplied differential clocks. Inputs are latched at the

cross point of differential clocks (CK rising and CK# falling) All I/Os are synchronized with a

pair of bidirectional strobes (DQS and DQS#) in a source synchronous fashion. The address

bus is used to convey row, column, and bank address information in RAS #, CAS#

multiplexing style. Accesses begin with the registration of a Bank Activate command, and

then it is followed by a Read or Write command. Read and write accesses to the DDR2

SDRAM are 4 or 8-bit burst oriented; accesses start at a selected location and continue for a

programmed number of locations in a programmed sequence. Operating the four memory

banks in an interleaved fashion allows random access operation to occur at a higher rate than

is possible with standard DRAMs. An auto precharge function may be enabled to provide a

self-timed row precharge that is initiated at the end of the burst sequence. A sequential and

gapless data rate is possible depending on burst length, CAS# latency, and speed grade of the

device.

32

Page 33

b) Pinning

33

Page 34

12. 4Gbit NAND Flash Memory (U35)

ST NAND04G-B2D

a) Key Features

■ High density NAND Flash Memory

– Up to 8 Gbit memory array

– Cost-effective solution for mass storage

applications

■ NAND interface

– x8 or 16x bus width

– Multiplexed address/data

■ Supply voltage: 1.8 V or 3.0 V device

■ Page size

– x8 device: (2048 + 64 spare) bytes

– x16 device: (1024 + 32 spare) words

■ Block size

– x8 device: (128K + 4 K spare) bytes

– x16 device: (64K + 2 K spare) words

■ Multiplane architecture

– Array split into two independent planes

– Program/erase operations can be

performed on both planes at the same time

■ Page read/program

– Random access: 25 µs (max)

– Sequential access: 25 ns (min)

– Page program time: 200 µs (typ)

– Multiplane page program time (2 pages):

200 µs (typ)

■ Copy back program with automatic error

detection code (EDC)

■ Cache read mode

■ Fast block erase

– Block erase time: 1.5 ms (typ)

– Multiblock erase time (2 blocks):

1.5 ms (typ)

■ Status Register

■ Electronic signature

■ Chip Enable ‘don’t care’

■ Serial number option

■ High density NAND Flash Memory

– Up to 8 Gbit memory array

– Cost-effective solution for mass storage

applications

■ NAND interface

– x8 or 16x bus width

– Multiplexed address/data

■ Supply voltage: 1.8 V or 3.0 V device

■ Page size

– x8 device: (2048 + 64 spare) bytes

– x16 device: (1024 + 32 spare) words

■ Block size

– x8 device: (128K + 4 K spare) bytes

– x16 device: (64K + 2 K spare) words

■ Multiplane architecture

– Array split into two independent planes

– Program/erase operations can be

performed on both planes at the same time

■ Page read/program

– Random access: 25 µs (max)

– Sequential access: 25 ns (min)

– Page program time: 200 µs (typ)

– Multiplane page program time (2 pages):

200 µs (typ)

■ Copy back program with automatic error

detection code (EDC)

■ Cache read mode

■ Fast block erase

– Block erase time: 1.5 ms (typ)

– Multiblock erase time (2 blocks):

1.5 ms (typ)

■ Status Register

■ Electronic signature

■ Chip Enable ‘don’t care’

■ Serial number option

34

Page 35

b) Pinning

35

Page 36

13. 128Mbit NAND Flash Memory (U17)

ST NAND128-A

a) Key Features

■ HIGH DENSITY NAND FLASH

MEMORIES

– Up to 1 Gbit memory array

– Up to 32 Mbit spare area

– Cost effective solutions for mass storage

applications

■ NAND INTERFACE

– x8 or x16 bus width

– Multiplexed Address/ Data

– Pinout compatibility for all densities

■ SUPPLY VOLTAGE

– 1.8V device: VDD = 1.7 to 1.95V

– 3.0V device: VDD = 2.7 to 3.6V

■ PAGE SIZE

– x8 device: (512 + 16 spare) Bytes

– x16 device: (256 + 8 spare) Words

■ BLOCK SIZE

– x8 device: (16K + 512 spare) Bytes

– x16 device: (8K + 256 spare) Words

■ PAGE READ / PROGRAM

– Random access: 12µs (max)

– Sequential access: 50ns (min)

– Page program time: 200µs (typ)

■ COPY BACK PROGRAM MODE

– Fast page copy without external

buffering

b) Pinning

■ FAST BLOCK ERASE

– Block erase time: 2ms (Typ)

■ STATUS REGISTER

■ ELECTRONIC SIGNATURE

■ CHIP ENABLE ‘DON’T CARE’

OPTION

– Simple interface with microcontroller

■ SERIAL NUMBER OPTION

■ HARDWARE DATA PROTECTION

– Program/Erase locked during Power

Transitions

■ DATA INTEGRITY

– 100,000 Program/Erase cycles

– 10 years Data Retention

■ RoHS COMPLIANCE

– Lead-Free Components are Compliant

with the RoHS Directive

■ DEVELOPMENT TOOLS

– Error Correction Code software and

hardware models

– Bad Blocks Management and Wear

Leveling algorithms

– File System OS Native reference

software

– Hardware simulation models

36

Page 37

14. USB Interface

USB ports are directly connected concept IC, BCM 3556.

USB ciecuit has 2 main parts:

• Protection IC (U4)

• Over Curent Protection IC (U108-U109)

37

Page 38

15. CI Interface

17MB70 Digital CI ve Smart Card Interface Block diagram:

16. DVB-C Demodulator

Mstar MSB122C

a) Key Features

38

Page 39

b) Block Diagram

c) Pinning

39

Page 40

40

Page 41

17. DVB-C/T2 Demodulator

Sony CXD2820R

a) Key Features

DESCRIPTION

The Sony CXD2820R is a combined DVB-T2, DVB-T and DVB-C demodulator that

conforms to the ETSI EN 302-755 (second generation Terrestrial) ETSI EN 300-744

(Terrestrial) and ETSI EN 300-429 (Cable) standards.

The CXD2820R is a DVB-T2 demodulator offering class-leading performance, optimised

BOM requiring no external memory and low processor overhead. It includes a highly

integrated dual-core DVB-T and DVB-C demodulator which complies with all relevant

European performance standards.

FEATURES DVB-T2

• Supports all DVB-T2 modes, including

• Single and multiple-PLPs

• SISO and MISO transmission

• Simple API

• Fully-automatic acquisition

• Fully-automatic L1-signalling decoding

• Automatic guard-interval detection

• Automatically-calculated constant-rate TS output (using L1

signalling and ISSY)

• Acquisition range ±857kHz

• Stream processor for automatic common- and data-PLP combination

• Null-packet insertion

• Access to channel echo profile and constellation via I2C

FEATURES DVB-C

• Wide symbol range, 0.7 to 7.2Msym/s

• Integrated matched filter 0.15 roll-off factor

• Auto Acquisition controller with fast re-acquisition mode, 15ms typ.

41

Page 42

• Programmable acquisition range ±500kHz

• 2.8us echo cancellation at 7.2Msym/s

• Low impl. loss 0.4dB @ 64QAM and <1.0dB @ 256QAM typ.

• Enhanced channel scanning performance through improved rejection of non-digital signals

• Access to channel SNR, constellation data and dynamic equaliser tap values via I2C

APPLICATIONS

• Set Top Boxes

• IDTV with Digital only or Hybrid Tuner Support

• PC TV

• PVRs and recordable DVD players

• Test equipment

GENERAL FEATURES

• Single, 41MHz crystal (can be shared with CXD2813R analogue demod IC)

• High performance differential signal ADC

• RF power level monitor ADC

• Low IF and high IF (36MHz) mode input

• Fast 400kHz I2C compatible bus interface

• Quiet I2C interface for dedicated tuner control

• Automatic IF AGC and optional programmable

RF AGC/GPIO functions

• Configurable parallel and serial MPEG-2 TS outputs with smoothing buffer

• 3.3V, 2.5V, 1.2V supplies

• Temperature range -20°C to +85°C

• 64 pin exposed-pad LQFP 10mm x 10mm package

• Supplied with full reference design, including software driver, PCB schematic/layouts, GUI

and documentation

b) Block Diagram

42

Page 43

c) Pinning

43

Page 44

44

Page 45

45

Page 46

46

Page 47

18. LOW POWER&CEC MICROCONTROLLER

NEC uPD78F0503

Pinning

47

Page 48

CEC Circuit Design for CEC option:

19. HDMI SWITCH

Silicon Image SiI9287B

a) Key Features

x Four-input, single-output HDMI port processor

x Improved ESD protection on all signals connected to HDMI connector

x Integrated TMDS receiver and transmitter cores capable of receiving and transmitting at

2.25 Gbps:

x InstaPort™ viewing technology

x MHL support

x Supports video resolutions up to 1080p, 60 Hz, 12bit or 720p/1080i, 120 Hz, 12-bit

x Built-in adaptive equalizer provides long cable support even at Deep Color resolutions,

enabling the SiI9287B device to work with noisy signals and many sources, making the sink

devices highly interoperable

x Receiver fully complies with DVI 1.0, HDCP 1.3 and HDMI 1.3a specifications.

48

Page 49

b) Block Diagram

49

Page 50

c) Pinning

50

Page 51

51

Page 52

52

Page 53

20. LNB supply and control IC

ST LNBH23L

a) Key Features

■ Complete interface between LNB and I²C bus

■ Built-in DC-DC converter for single 12 V supply operation and high efficiency (typ. 93%

@0.5 A)

■ Selectable output current limit by external resistor

■ Compliant with main satellite receivers output voltage specification

■ Auxiliary modulation input (EXTM pin) facilitates DiSEqC™ 1.X encoding

■ Accurate built-in 22 kHz tone generator suits widely accepted standards

■ Low-drop post regulator and high efficiency step-up PWM with integrated power NMOS

allow low power losses

■ Overload and over-temperature internal protections with I²C diagnostic bits

■ LNB short circuit dynamic protection

■ +/- 4 kV ESD tolerant on output power pins

Applications

■ STB satellite receivers

■ TV satellite receivers

■ PC card satellite receivers

Description

Intended for analog and digital satellite receivers, the LNBH23L is a monolithic voltage

regulator and interface IC, assembled in QFN32 5 x 5 specifically designed to provide the 13 /

18 V power supply and the 22 kHz tone signalling to the LNB down-converter in the antenna

dish or to the multi-switch box. In this application field, it offers a complete solution with

extremely low component count, low power dissipation together with simple design and I²C

standard interfacing.

53

Page 54

b) Block Diagram

21. Software Update

In MB70 project you can update the main IC software by using USB ports. You can find the

SW update procedure below.

1. Software files should copy directly inside of a flash memory(not in a folder).

2. Put flash memory to the tv when tv is powered off.

3. Power on the and wait. TV will power-up itself.

4. If First Time Installition screen comes, it means software update procedure is succesful.

5. You can check the SW release name from service menu.

22. Troubleshooting

A. No Backlight Problem

Problem: If TV is working, led is normal and there is no picture and backlight on the panel.

Possible couses: Backlight pin, dimming pin, backlight supply, stby on/off pin

54

Page 55

BACKLIGHT_ON/OFF pin should be high when the backlight is ON. R185 must be low

when the backlight is OFF. If it is a problem, please check Q131 and the panel cables.

55

Page 56

Dimming pin should be high or square wave in open position. If it is low, please check S32

for BRCM side and panel or power cables, connectors.

STBY_ON/OFF_NOT should be high for standby condition, please check R203.

56

Page 57

B. CI Module Problem

Problem: CI is not working when CI module inserted.

Possible couses: Supply, suply control pin, detect pins, mechanical positions of pins.

• CI supply should be 5V when CI module inserted. If it is not 5V please check

CI_PWR_CTRL, this pin should be low.

• Please check mechanical position of CI module. Is it inserted properly or not?

• Detect ports should be low. If it is not low please check CI connector pins, CI module

pins.

57

Page 58

C. Staying in Stand-by Mode

Problem: Staying in stand-by mode, no other operation

This problem indicates a short on Vcc voltages. Protect pin should be logic high while normal

operation. When there is a short circuit protect pin will be logic low. If you detect logic low

on protect pin, unplug the TV set and control voltage points with a multimeter to find the

shorted voltage to ground.

58

Page 59

D. IR Problem

Problem: LED or IR not working

Check LED card supply on MB70 chasis.

59

Page 60

E. Keypad Touchpad Problems

Problem: Keypad or Touchpad is not working

Check keypad supply on MB70.

60

Page 61

F. USB Problems

Problem: USB is not working or no USB Detection.

Check USB Supply, It should be nearly 5V. Also USB Enable should be logic high.

G. No Sound Problem

Problem: No audio at main TV speaker outputs.

Check supply voltages of VDD_AUDIO, 8V_VCC and 12V_VCC with a voltage-meter.

There may be a problem in headphone connector or headphone detect circuit (when

headphone is connected, speakers are automatically muted). Measure voltage at HP_DETECT

pin, it should be 3.3v.

H. Standby On/Off Problem

Problem: Device can not boot, TV hangs in standby mode.

There may be a problem about power supply. Check main supplies with a voltage-meter. Also

there may be a problem about SW. Try to update TV with latest SW. Additionally it is good

61

Page 62

to check SW printouts via Teraterm. These printouts may give a clue about the problem. You

can use Scart-1 for terraterm connection.

I. No Signal Problem

Problem: No signal in TV mode.

Check tuner supply voltage; 5V_TUN. Check tuner options are correctly set in Service menu.

Check AGC voltage at RF_AGC pin of tuner.

23. Service Menu Settings

In order to reach service menu, First Press “MENU” buton, then write “4725” by uisng

remote controller.

You can see the service menu main screen below. You can check SW releases by using this

menu. In addition, you can make changes on video, audio etc. by using video settings, audio

settings titles.

62

Page 63

Service Menu Main Screen

63

Page 64

Video Settings

64

Audio Settings

Page 65

Options-1 Menu

65

Options-2 Menu

Page 66

Tuner Settings Menu

66

Source Settings Menu

Page 67

Diagnostic Menu

24. General Block Diagram

67

Page 68

68

Page 69

A

10K

3V3_VCC

3V3_VCC

HDMI_HOTPLUG_IN

B

5V_VCC

HDMIB_HTPLG_OUT

C

1 2 3 4 5 6 7 8

HDMI (SIL9287)

HDMI_TX2P

HDMI_TX2N

HDMI_TX1P

HDMI_TX1N

HDMI_TX0P

HDMI_TX0N

HDMI_TXCP

HDMI_TXCN

R859

4k7

R858

4k7

HDMIB_RX2P

HDMIB_RX2N

HDMIB_RX1P

HDMIB_RX1N

HDMIB_RX0P

HDMIB_RX0N

HDMIB_TXCP

HDMIB_TXCN

HDMIB_SCL

HDMIB_SDA

S128

HDMIB_5V

R259

1k2

100k

R473

AF2

HDMI_RX_0_DATA2_P

AF1

HDMI_RX_0_DATA2_N

AE2

HDMI_RX_0_DATA1_P

AE1

HDMI_RX_0_DATA1_N

AD2

HDMI_RX_0_DATA0_P

AD1

HDMI_RX_0_DATA0_N

AC2

HDMI_RX_0_CLK_P

AC1

HDMI_RX_0_CLK_N

AG1

HDMI_RX_0_CEC_DAT

AB3

HDMI_RX_0_DDC_SCL

Y6

HDMI_RX_0_DDC_SDA

AA6

HDMI_RX_0_HTPLG_IN

AA5

HDMI_RX_0_HTPLG_OUT

AB1

HDMI_RX_1_DATA2_P

AB2

HDMI_RX_1_DATA2_N

AA1

HDMI_RX_1_DATA1_P

AA2

HDMI_RX_1_DATA1_N

Y2

HDMI_RX_1_DATA0_P

Y1

HDMI_RX_1_DATA0_N

W3

HDMI_RX_1_CLK_P

W2

HDMI_RX_1_CLK_N

AA3

HDMI_RX_1_CEC_DAT

V5

HDMI_RX_1_DDC_SCL

V3

HDMI_RX_1_DDC_SDA

V4

HDMI_RX_1_HTPLG_IN

U6

HDMI_RX_1_HTPLG_OUT

P5

EPHY_RDAC

P6

EPHY_VREF

HDMI_RX_0_RESREF

HDMI_RX_1_RESREF

6

U1

BCM3556

EPHY_RDP

EPHY_RDN

EPHY_TDP

EPHY_TDN

HDMIB_5V_PORT

30061090_499R

30061090_499R

W4

P2

P3

N2

N3

R937

510R

R938

510R

ETH_TXP

ETH_TXN

ETH_RXP

ETH_RXN

AC4

R865

10k

BC858B

10k

R864

HDMI_RX_0_VDD2P5

HDMI_RX_1_VDD2P5

10k

Q117

HDMIB_SCL

HDMIB_SDA

HDMIB_HTPLG_OUT

R866

5V_VCC

R861

100R

BLUERAY

HDMIB_RX2P

HDMIB_RX2N

HDMIB_RX1P

HDMIB_RX1N

HDMIB_RX0P

HDMIB_RX0N

HDMIB_TXCP

HDMIB_TXCN

HDMIB_5V

21

12V_VCC

24V_VCC

HDMIB_5V

R1025

10R

21

21

47k

47k

R234

R1020

10R

R1019

10R

47k

R248

R1023

21

R249

F45

330R

F46

330R

10R

R1016

1k

R1022

R1024

10R

R1021

10R

21

R455

10R

R1018

10R

10R

"

CEC

R1017

10R

6

5

4

3

2

1

CN18

CN13

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

CN137

1

3

2

F55

USB_BT_DN

USB_BT_DP

C526

22p

50V

C527

22p

50V

4

330R

3V3_VCC

X4

F29

24MHz

C568

22u

16V

330R

5V_VCC

RESET_IC

1M

R474

C3

16V

100n

3V3D_USB

R381

100R

3V3D_USB

NC

R37

10k

C554

3V3D_USB

1V8_D

3V3D_USB

1u

50V

R427

12k

R569

12k

37

RESET_N

38

VSS_5

39

VDD33CR

40

VDD18_3

41

VSS_6

42

XTAL2

43

XTAL1/CLKIN

44

VDDA18PLL

45

VDDA33PLL

46

ATEST/REG_EN

47

RBIAS

48

VSS_7

10k

R112

35

36

TEST1

CLKIN_EN

VDDA33_1

USBDP0

2

1

C759

3V3A_USB

1p

3V3D_USB

USB_OCD

S41

34

OCS1_N

USBDN0

3

S17

R614

470k

USB_OCD

USB_PWR_EN_1

1V8_D

S55

31

32

33

OCS2_N

PRTPWR1

VDD18_2

U12

USB2503

VSS_1

USBDN1

USBDP1

6

5

4

C758 C760

1p

C389

1u

6V3

30

VSS_4

VDDA33_2

7

3V3A_USB

3V3D_USB

28

29

VBUS_DET

SELF_PWR

USBDP2

USBDN2

9

8

1p

R205

4k7

R204

4k7

R417

47R

47R

R409

25

26

27

CFG_SEL1

SDA/SMBDATA

GR1/NON_REM0

SCL/SMBCLK/CFG_SEL0

GR2/NON_REM1

PRTPWR_POL

GR3/PRTDIS0

VSS_2

USBDN3

USBDP3

12

11

10

3V3D_USB

TEST0

VDD18_1

VSS_3

GANG_EN

PRTPWR2

OCS3_N

PRTPWER3

VDDA33_3

SCL

SDA

24

23

22

21

20

19

18

17

16

15

14

13

1V8_D

R36

10k

R113

10k

3V3D_USB

R111

10k

USB_PWR_EN_2

3V3A_USB

A

B

C

USB_DP1

USB_DM1

F162

330R

C848

220u

10V

F56

330R

USB1_VCC

USB_PWRON_1

USB_PWRFLT_1

USB_DP2

USB_DM2

USB_PWRON_2

USB_PWRFLT_2

21

USB2_VCC

21

USB1_VCC

U4

USB_RREF

50V

100p

R775

4k7

C766

D

USB1_DP

USB1_DN USB_DN

R476

USB_PWR_EN_1 USB_ENABLE

USB_PWR_EN_2 22k

E

CN34

F

5V_VCC

3V3_VCC USB_ENABLE1

USB_ENABLE

22k

R509

USB_SAV_COMMON

4

8

3

7

2

6

1

5

4

3

2

1

CN32

R902

21

4k7

C859

4u7

10V

S115

S116

S117

USB_SAV_COMMON

1

VIN

2

GND

ON ISET

R5

T5

USB_DP

VOUT

U108

FPF2124

USB_MONPLL

USB_MONCDR

C765

10u

10V

5

43

C522

10u

10V

560R

R907

S160

C847

220u

10V

C862

100n

16V

V2

V1

T2

R1

U2

U1

T1

R2

S31

USB2_DP

USB2_DN

USB_ENABLE1

USB_DP

USB_DN

USB_ENABLE

3V3_VCC

USB INTERFACE

R230

6

IO4

5

VDD

AZ099-04S

4 3

U4

IO1

GND

IO2IO3

1

2

10R

R231

10R

R232

10R

R620

10R

21

USB1_DP

21

USB1_DN

21

USB2_DP

21

USB2_DN

F52

C29

330R

16V

100n

C567

22u

16V

Should be close to Pin#45

F53

C32

16V

100n

C547

22u

16V

330R

C31

C327

10u

10V

100n

16V

Should be close to Pin#40

4u7

C860

10V

5V_VCC

R901

3V3_VCC

4k7

21

C119

C525

C30

100n

1u

16V

16V 16V

100n

1

VIN

2

GND

FPF2124

ON ISET

C108

C123

C27

U109

100n

100n

100n

3V3_VCC

2V5_VCC

VOUT

16V

16V

16V

5

43

C120

C121

1V8_D

560R

R908

100n

100n

C861

100n

16V

3V3D_USB

16V

16V

C122

F169

330R

F170

330R

3V3A_USB3V3_VCC

16V

100n

USB2_VCC

47R

R421

R422

47R

100n

47R

16V

Place these resistors

close to STE100P

ETH_TXP

ETH_TXN

ETH_RXP

ETH_RXN

R420

C197

USB1_DN

R423

47R

C199

16V

100n

C477

10n

16V

C198

USB_DP

USB_DN

1

2

3

4

7

6

5

3

4

2

1

TR1

Place these capacitors

16V

close to transformer

100n

USB1_DP

TP167

A0

U40

A1

24LC02

A2

VSS

10

11

14

15

16

USB_BT_DP

5V_VCC

1

VCC

WP

SCL

SDA

98

R342

12

R341

13

8

7

6

5

75R

75R

USB_BT_DN

2 1

TP166

1

1

1

TP169

TP168

C727

BAV70

D37

R778

47R

R777

47R

NVM_WP

3

R340

R344

1n

21

21

75R

75R

1kV

Ethernet lines must be 100ohm differential pairs

VESTEL

SCH NAME :

DRAWN BY :

<DRAWING NAME HERE>

<YOUR NAME HERE>

PROJECT NAME :

HDMIB_5V

21

21

4k7

4k7

R773

R774

HDMIB_SCL

HDMIB_SDA

R776

2 1

47k

1

TX+

2

TX-

3

RX+

4

GND1

5

GND2

6

RX-

7

GND3

8

GND4

Schematic1

3

2

Q108

BC848B

1

JK7

SHEET:

1 1

10-05-2010_10:00

87654321

D

E

F

A3

OF:

AX M

Page 70

1 2 3 4 5 6 7 8

F20

21

330R

Q106

BSH103

3

2

1

21

3

2

21

Q107

BC847B

1

C247

2

100n

1

10V

3V3_VCC

NAND_DATA_0

NAND_DATA_1

NAND_DATA_2

NAND_DATA_3

NAND_DATA_4

NAND_DATA_5

NAND_DATA_6

NAND_DATA_7

C241

2

R329

47k

100n

10V

1

21

2k7

R942

2k7

R941

2k7

R940

2k7

R939

F139

330R

21

4k7

21

C290

10u

10V

BACKLIGHT_DIM

MEGA_DCR_IN

3V3_VCC

R195

EBI_CS0B

NAND_3V3

NAND_3V3

NAND_3V3

TP165

1

CI_PWR

C242

2

100n

1

10V

MEGA_DCR_OUT

S86

PANEL_VCC_ON/OFF

S32

5V_VCC

12V_VCC

NC

S83

R20

2 1

10k

S33

21

F16

60R

F15

60R

F6

60R

2

R174

4k7

C589

220p

50V

R95

2 1

3

1

21

21

21

21

10k

Q18

BC848B

21

R94

2 1

10k

S84

21

3V3_VCC

S9

21

5V_VCC

R172

21

1k

R471

3

2

Q9

BC848B

1

4k7

C590

220p

50V

R181

4k7

21

C588

21

220p

50V

C147

16V

100n

1

21

S8

21

Q25

2

BC858B

3

R479

100R

8

1

3

1

7

6

5 4

Q8

BC848B

R1

2

R2

3

R3

R4

C322

10u

10V

DIMMING

21

2

TP3

1

A

B

PANEL_VCC

6

5

43

21

C662

21

C368

1n

50V

25V

220n

2

33k

R478

R411

21

47R

33k

R475

2 1

3

1

Q6

BC848B

C160

16V

100n

PANEL SUPPLY SWITCH

Q29

FDC642P

2

1

C

3V3_VCC

F7

60R

C5

22u

6V3

C137

100n

16V

C239

330p

50V

NAND_3V3

NAND_WPZ

S59

A

NMIB

U24

T26

T27

U26

U27

V26

V27

V28

R23

T24

T25

R24

T23

U25

V25

W24

U23

V23

V24

P24

N24

NAND_DATA0/EBI_DATA8

NAND_DATA1/EBI_DATA9

NAND_DATA2/EBI_DATA10

NAND_DATA3/EBI_DATA11

NAND_DATA4/EBI_DATA12

NAND_DATA5/EBI_DATA13

NAND_DATA6/EBI_DATA14

NAND_DATA7/EBI_DATA15

NAND_ALE/POD_EBI_DSB

5

U1

NAND_CS0B

SPI_S_MISO

SF_MISO

SF_MOSI

SF_SCK

SF_CSB

NAND_CLE/POD_EBI_TAB

NAND_WEB/POD_EBI_WE0B

NAND_REB/POD_EBI_RDB

NAND_RBB/DS_OVST_CLK

B

BCM3556

RESET_OUTB

RESETB

C

F6

NAND_DATA_0

NAND_DATA_1

NAND_DATA_2

NAND_DATA_3

NAND_DATA_4

NAND_DATA_5

NAND_DATA_6

NAND_DATA_7

NAND_ALE

NAND_CS0B

NAND_CLE

NAND_WEB

NAND_REB

NAND_RBB

C923

100n

16V

R857

3k9

RESET_IC

R375

2 1

100R

NAND_3V3

3V3_STBY

2

10k

1

1

TP54

R1004

RESET_BCM

NAND_CS0B

NAND_3V3

RESET_IC

NAND_3V3

4k7

NAND_REB

R219

R168

NAND_WPZ

S58

3k9

NAND FLASH

1

NC1

2

NC2

3

NC3

4

NC4

5

NC5

6

NC6

NAND_RBB

NAND_CLE

NAND_ALE

NAND_WEB

7

RB

8

R

9

E

10

NC7

11

NC8

12

VDD1

NAND512-A

13

VSS1

14

NC9

15

NC10

16

CL

17

AL

18

W

19

WP

20

NC11

21

NC12

22

NC13

23

NC14

NC15 NC16

U35

NC29

NC28

NC27

NC26

I/O7

I/O6

I/O5

I/O4

NC25

NC24

NC23

VDD2

VSS2

NC22

NC21

NC20

I/O3

I/O2

I/O1

I/O0

NC19

NC18

NC17

48

47

46

45

44

NAND_DATA_7

43

NAND_DATA_6

42

NAND_DATA_5

41

NAND_DATA_4

40

39

38

37

NAND_3V3NAND_3V3

36

35

34

33

32

NAND_DATA_3

31

NAND_DATA_2

30

NAND_DATA_1

29

NAND_DATA_0

28

27

26

2524

5V_VCC

3V3_VCC10k

12V_VCC

21

R330

47k

R13

CI_PWR_CTRL

R377

10k

S3

EBI_RWB

R171

3V3_VCC

2 1

4k7

CI_D0

CI_D1

CI_D2

CI_D3

CI_D4

CI_D5

CI_D6

CI_D7

1

DIR

2

A1

3

A2

4

A3

5

A4

74LCX245

6

A5

7

A6

8

A7

9

A8

GND B8

U2

VCC

OE-

20

19

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

1110

EBI_WE1B

EBI_RWB

EBI_CLK_OUT

EBI_CLK_IN

ABI_TAB

EBI_ADDR13

EBI_ADDR12

EBI_ADDR11

EBI_ADDR10

10

EBI_CSOB

EBI_ADDR9

EBI_ADDR8

EBI_ADDR7

EBI_ADDR6

EBI_ADDR5

EBI_ADDR4

EBI_ADDR3

EBI_ADDR2

EBI_ADDR1

EBI_ADDR0

D

U1

BCM3556

E

F

EBI_ADDR15

EBI_ADDR16

EBI_ADDR17

EBI_ADDR18

EBI_ADDR19

EBI_ADDR20

EBI_ADDR21

EBI_ADDR22

EBI_ADDR23

EBI_ADDR24

EBI_ADDR25

EBI_ADDR14

POD2CHIP_MIVAL

POD2CHIP_MISTRT

POD2CHIP_MDI0

POD2CHIP_MDI1

POD2CHIP_MDI2

POD2CHIP_MDI3

POD2CHIP_MDI4

POD2CHIP_MDI5

POD2CHIP_MDI6

POD2CHIP_MDI7

H26

K23

G28

G27

G24

G25

H27

G26

J27

J28

J26

H28

F27

F26

J25

J24

J23

H25

H24

H23

F25

A28

C28

C27

C26

B28

B27

A27

F24

F23

E25

G23

E24

E23

D25

D24

C25

E27

E26

D28

D27

D26

EBI_RWB

EBI_CS0B

CI_TS_IN_CLK

CI_TS_IN_VALID

CI_TS_IN_SYNC

CI_TS_IN_D0

CI_TS_IN_D1

CI_TS_IN_D2

CI_TS_IN_D3

CI_TS_IN_D4

CI_TS_IN_D5

CI_TS_IN_D6

CI_TS_IN_D7

CI_A14

CI_TS_OUT_VALID

CI_TS_OUT_SYNC

CI_TS_OUT_D0

CI_TS_OUT_D1

CI_TS_OUT_D2

CI_TS_OUT_D3

CI_TS_OUT_D4

CI_TS_OUT_D5

CI_TS_OUT_D6

CI_TS_OUT_D7

S24

R273

33R

1

R1

2

R2

3

R3

R271

R4

33R

8

R1

7

R2

6

R3

R272

R4

33R

1

R1

2

R2

3

R3

R4

47R

2 1

R441

47R

2 1

R443

8

7

6

54

1

2

3

45

8

7

6

54

EBI_WE1B

PC_WAIT_N

CI_A13

CI_A12

CI_A11

CI_A10

CI_A9

CI_A8

CI_A7

CI_A6

CI_A5

CI_A4

CI_A3

CI_A2

CI_A1

CI_A0

CI_CD1

35

1

CN131

3V3D_DVB

21

CI_TS_OUT_D3

4k7

R183

1

47R

R556

8

36

37

2

3

CI_D4

CI_D3

CI_TS_OUT_D4

CI_TS_OUT_D5

CI_TS_OUT_D6

2

3

45

R2

R3R1R4

6

7

38

39

40

4

5

6

CI_D5

CI_D7

CI_D6

21

4k7

CI_TS_OUT_D7

CI_CE2

21

47R

R435

41

42

7

8

CI_A10

CI_CE1

3V3D_DVB

GP23_POD_VS1_N

R211

21

R538

150R

CI_IORD

43

44

9

10

CI_OE

CI_A11

CI_IOWR

CI_TS_IN_SYNC

45

46

11

12

CI_A8

CI_A9

CI_TS_IN_D2

CI_TS_IN_D0

CI_TS_IN_D1

47

48

49

13

14

15

CI_WE

CI_A14

CI_A13

CI_TS_IN_D3

CI_PWRCI_PWR

50

51

16

17

4k7

R177

2 1

3V3D_DVB

CI_TS_IN_D4

52

53

18

19

CI_TS_IN_VALID

4k7

CI_TS_IN_D7

CI_TS_IN_D6

CI_TS_IN_D5

54

55

56

20

21

22

CI_A7

CI_A12

CI_TS_IN_CLK

PC_WAIT_N

3V3D_DVB

GP37_POD2CHIP_MCLKI_VS2_N

21

R212

R539

150R21R192

3V3D_DVB

21

GP19_POD_RST

3V3D_DVB

4k7

21

4k7

R182

R43621R554

57

58

59

60

61

23

24

25

26

27

CI_A5

CI_A6

CI_A4

CI_A2

CI_A3

CI_TS_OUT_D1

CI_TS_OUT_D0

CI_TS_OUT_SYNC

CI_TS_OUT_VALID

8

7

6

R2

63

29

CI_A0

2

64

30

CI_D0

R3R1R4

3

65

31

CI_D1

47R

47R

62

28

CI_A1

1

3V3D_DVB

21

CI_TS_OUT_D2

CI_CD2

4k7

R189

54

66

67

68

32

33

34

CI_D2

21

47R

R410

3V3D_DVB

21

4k7

R213

GP41_DVB_IOIS16_N

GP39_POD_IRQ_N

SMART CARD INTERFACE

123456789

CN14

10V

100n

C279

2

1

2

1

10V

C254

100n

F49

330R

330R

2 1

2 1

5V_VCC

3V3_VCC

GP40_DVB_OE_N

EBI_CS0B

CI_CE2

NAND_WEB

CI_IOWR

NAND_REB

CI_IORD

F50

GP25_SC_CLK

GP26_SC_RST

GP28_SC_VCC

10

TP95

TP94

TP93

TP96

TP97

GP24_SC_IO

GP27_SC_PRES

VESTEL

SCH NAME :

DRAWN BY :

C244

100n

10V

1

1OE-

2

1A1

3

2Y4

4

1A2

5

2Y3

74LCX244

6

1A3

7

2Y2

8

1A4

9

2Y1

GND 2A1

U36

VCC

2OE-

1Y1

2A4

1Y2

2A3

1Y3

2A2

1Y4

20

19

18

17

16

15

14

13

12

1110

NAND_ALE

PROJECT NAME :

<DRAWING NAME HERE>

<YOUR NAME HERE>

2

1

R196

3V3_VCC

CI_CE1

21

4k7

CI_WE

EBI_WE1B

CI_OE

17mb70

07-05-2010_16:06

87654321

3V3_VCC

SHEET:

OF:

2 2

D

E

F

A3

AX M

Page 71

1 2 3 4 5 6 7 8

0.9V

yarısı

A

B

C

D

E

F

DDR01_A00

DDR01_A01

DDR01_A02

DDR01_A03

DDR0_A04

DDR0_A05

DDR0_A06

DDR1_A04

DDR1_A05

DDR1_A06

DDR01_A07

DDR01_A08

DDR01_A09

DDR01_A10

DDR01_A11

DDR01_A12

DDR01_A13

DDR01_BA0

DDR01_BA1

DDR01_BA2

DDR0_DQ00

DDR0_DQ01

DDR0_DQ02

DDR0_DQ03

DDR0_DQ04

DDR0_DQ05

DDR0_DQ06

DDR0_DQ07

DDR0_DQ08

DDR0_DQ09

DDR0_DQ10

DDR0_DQ11

DDR0_DQ12

DDR0_DQ13

DDR0_DQ14

DDR0_DQ15

DDR1_DQ00

DDR1_DQ01

DDR1_DQ02

DDR1_DQ03

DDR1_DQ04

DDR1_DQ05

DDR1_DQ06

DDR1_DQ07

DDR1_DQ08

DDR1_DQ09

DDR1_DQ10

DDR1_DQ11

DDR1_DQ12

DDR1_DQ13

DDR1_DQ14

DDR1_DQ15

9

U1

BCM3556

DDR0_DQS0

DDR0_DQS0B

DDR0_DQS1

DDR0_DQS1B

DDR1_DQS0

DDR1_DQS0B

DDR1_DQS1

DDR1_DQS1B

DDR0_DM0

DDR0_DM1

DDR1_DM0

DDR1_DM1

DDR01_RASB

DDR01_CASB

DDR01_WEB

DDR0_CLK

DDR0_CLKB

DDR1_CLK

DDR1_CLKB

DDR01_CKE

DDR01_ODT

DDR_VREF0

DDR_VREF1

DDR_VDDP1P8_0

DDR_VDDP1P8_1

DDR_COMP

B15

E14

A15

D15

E13

E12

F13

F15

C15

D16

C14

F14

B14

D14

C13

D13

B13

F16

B16

E15

A8

B11

B8

D11

E11

C8

C11

C9

D8

E10

E9

F11

F12

E8

D10

F8

C18

C20

A18

B21

C21

B18

B20

D18

E18

D21

F18

E20

A22

F17

B22

E17

B10

B9

F10

F9

B19

C19

E19

D19

A10

C10

A20

F19

C16

A17

C17

B12

C12

A13

A12

B17

E16

A7

A23

D22

C7

C22

DDR01_A00

DDR01_A01

DDR01_A02

DDR01_A03

DDR0_A04

DDR0_A05

DDR0_A06

DDR1_A04

DDR1_A05

DDR1_A06

DDR01_A07

DDR01_A08

DDR01_A09

DDR01_A10

DDR01_A11

DDR01_A12

DDR01_A13

DDR01_BA0

DDR01_BA1

DDR01_BA2

DDR0_DQ00

DDR0_DQ01

DDR0_DQ02

DDR0_DQ03

DDR0_DQ04

DDR0_DQ05

DDR0_DQ06

DDR0_DQ07

DDR0_DQ08

DDR0_DQ09

DDR0_DQ10

DDR0_DQ11

DDR0_DQ12

DDR0_DQ13

DDR0_DQ14

DDR0_DQ15

DDR1_DQ00

DDR1_DQ01

DDR1_DQ02

DDR1_DQ03

DDR1_DQ04

DDR1_DQ05

DDR1_DQ06

DDR1_DQ07

DDR1_DQ08

DDR1_DQ09

DDR1_DQ10

DDR1_DQ11

DDR1_DQ12

DDR1_DQ13

DDR1_DQ14

DDR1_DQ15

DDR0_DQS0

DDR0_DQS0B

DDR0_DQS1

DDR0_DQS1B

DDR1_DQS0

DDR1_DQS0B

DDR1_DQS1

DDR1_DQS1B

DDR0_DM0

DDR0_DM1

DDR1_DM0

DDR1_DM1

DDR01_RASB

DDR01_CASB

DDR01_WEB

DDR0_CLK

DDR0_CLKB

DDR1_CLK

DDR1_CLKB

DDR01_CKE

DDR01_ODT

D_1V8

R358

240R

R359

C390

DDR01_A12