VESTEL 17MB12 Schematic

TABLE OF CONTENTS

1 INTRODUCTION................................................................................................................... 5

2 TUNER....................................................................................................................................5

2.1 General description of DTT71307: ................................................................................. 5

2.2 Features of DTT71307:............................................................ ....................................... 5

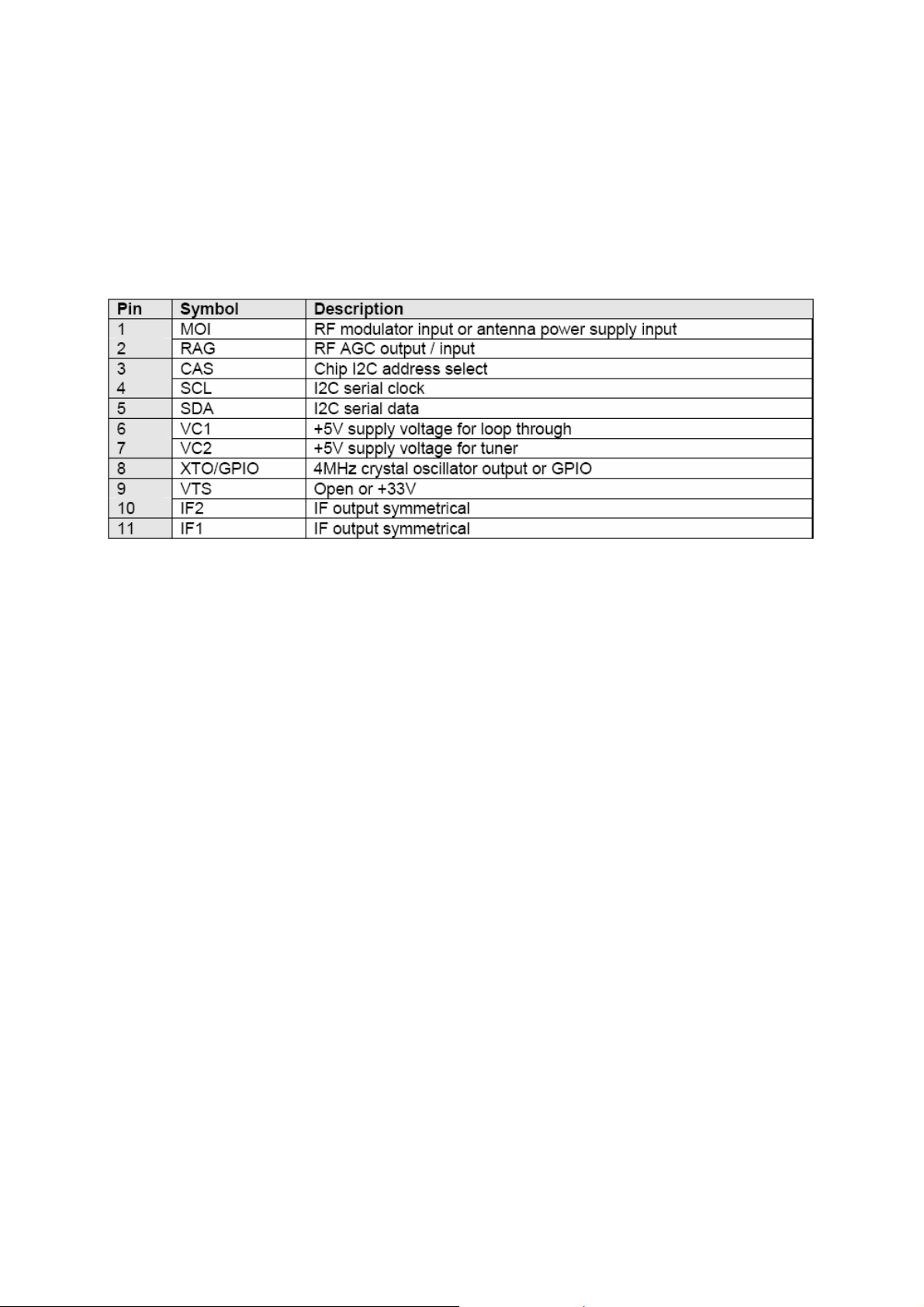

2.3 Pinning: ........................................................................................................................... 6

3 AUDIO AMPLIFIER STAGE WITH TDA8932................................................................... 6

3.1 General Description.........................................................................................................6

3.2 Features...........................................................................................................................6

3.3 Applications .................................................................................................................... 7

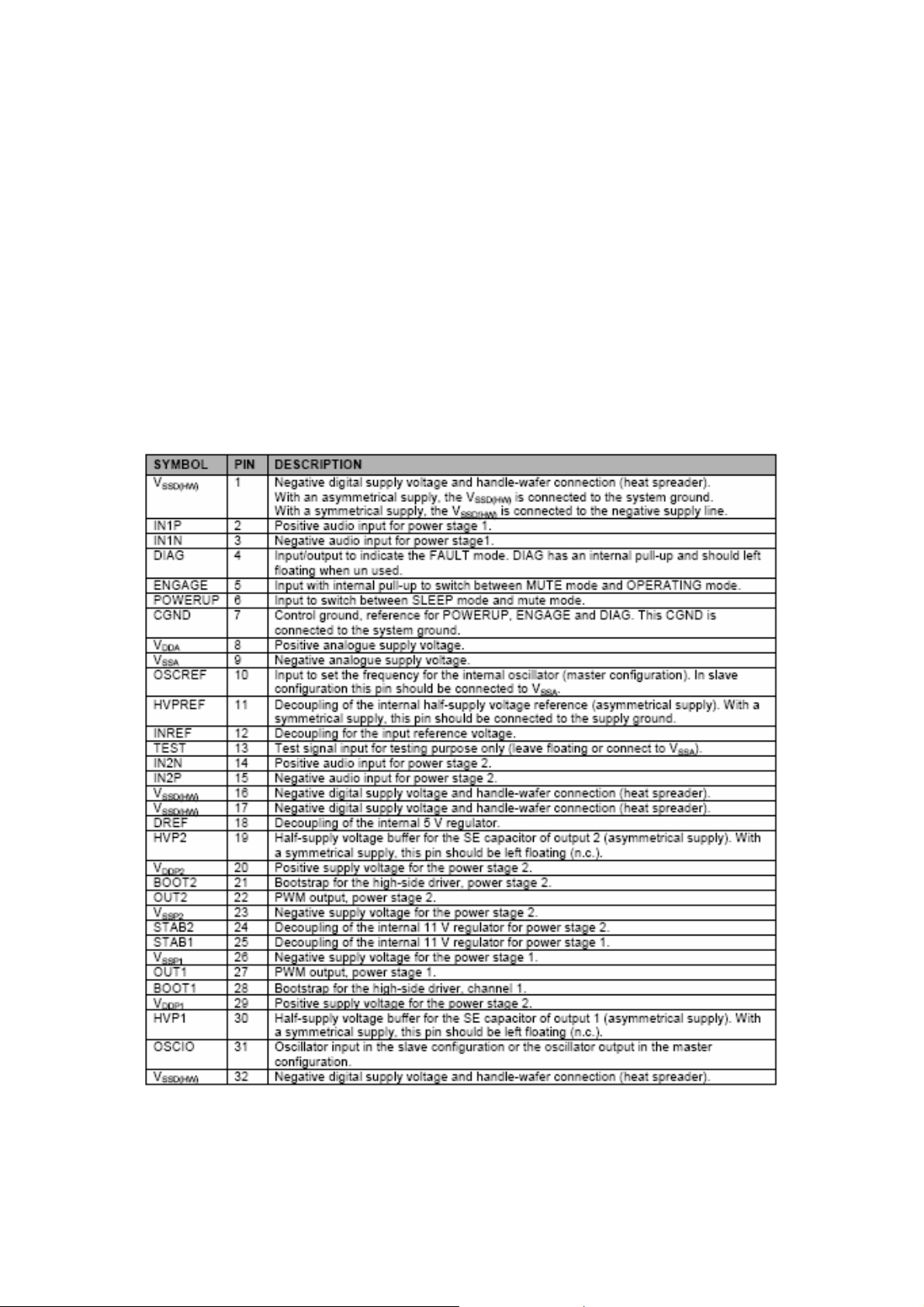

3.4 Pinning ............................................................................................................................7

4 POWER STAGE.....................................................................................................................7

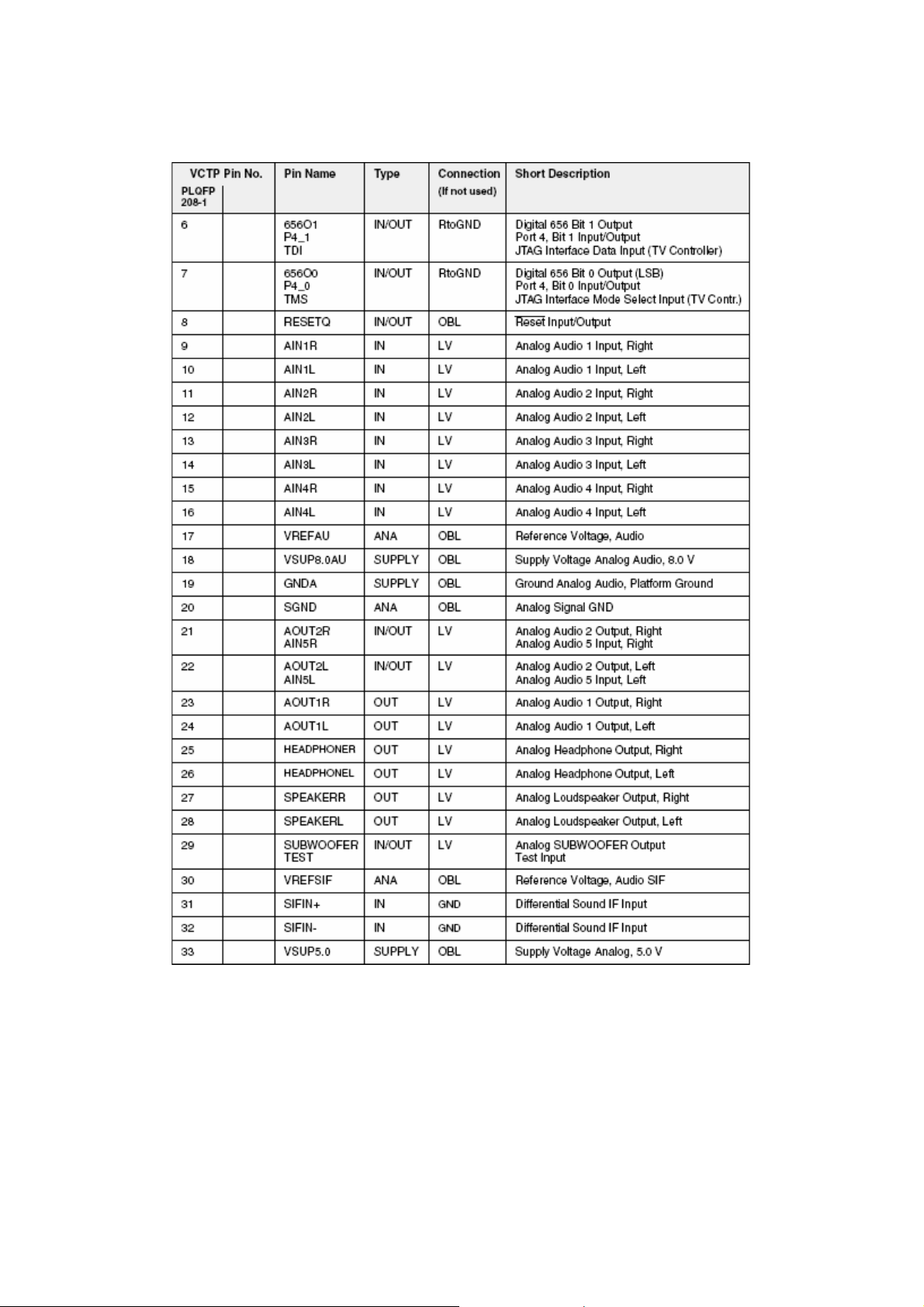

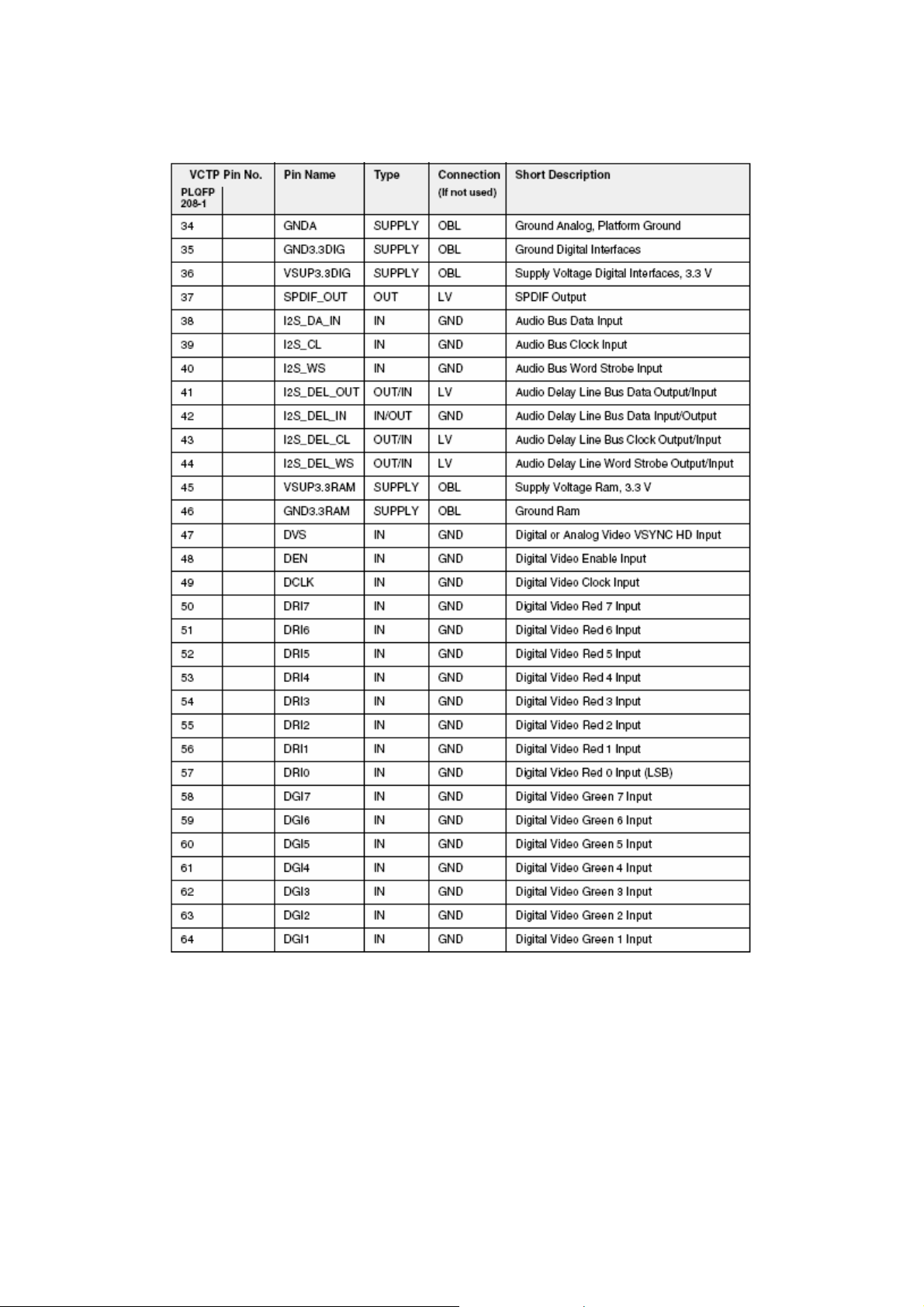

5 MICROCONTROLLER (VCTP) ...........................................................................................8

5.1 General Features..............................................................................................................8

5.1.1 Controller:...............................................................................................................8

5.1.2 Audio:...................................................................................................................... 8

5.1.3 Video:...................................................................................................................... 8

5.2 Multistandard Sound Processor (MSP) Features .......................................................... ..9

5.3 Video Features............................................................................................................... 10

5.4 Controller Features........................................................................................................10

5.5 OSD & Teletext Features...................................... ... ................................ .....................11

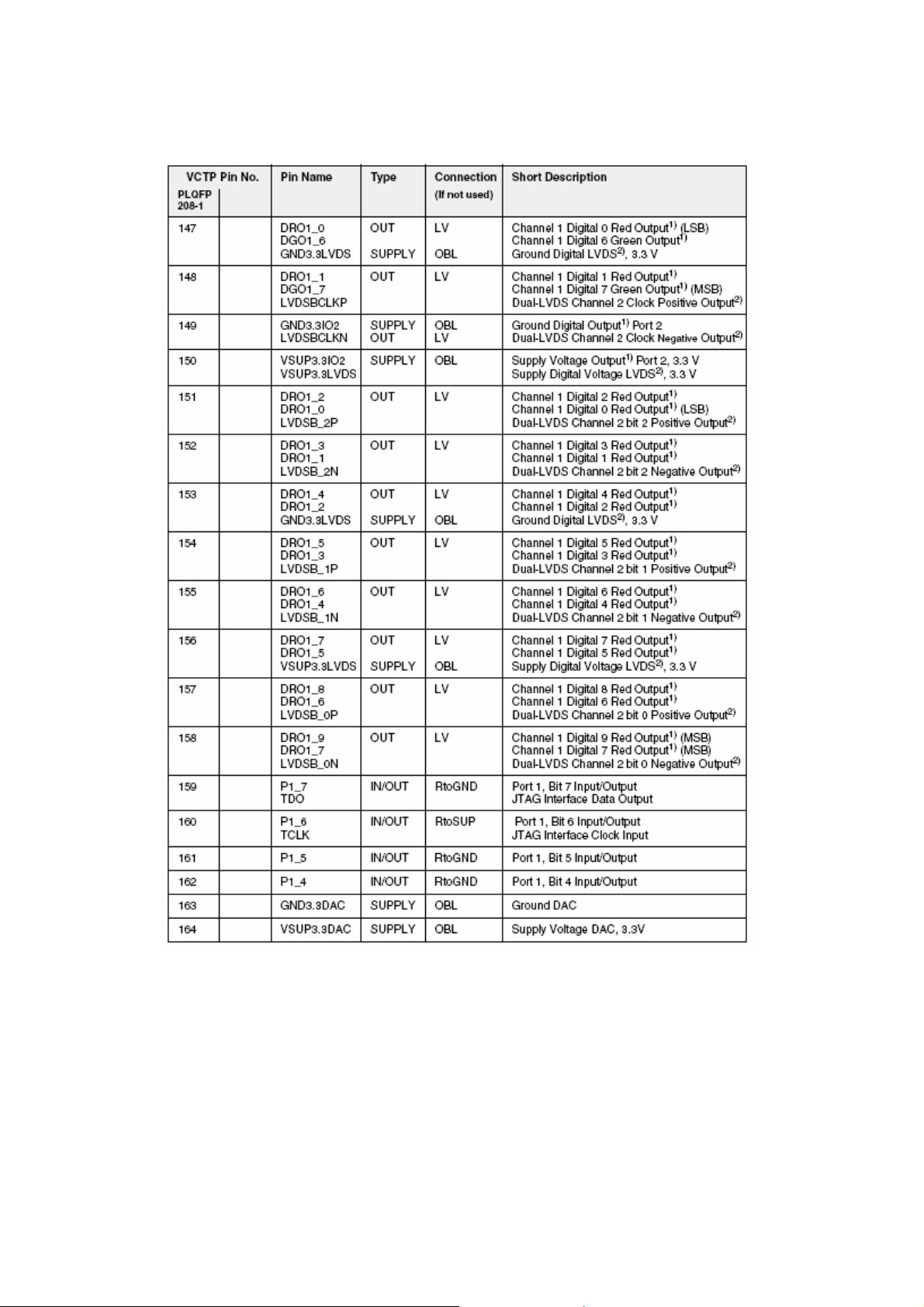

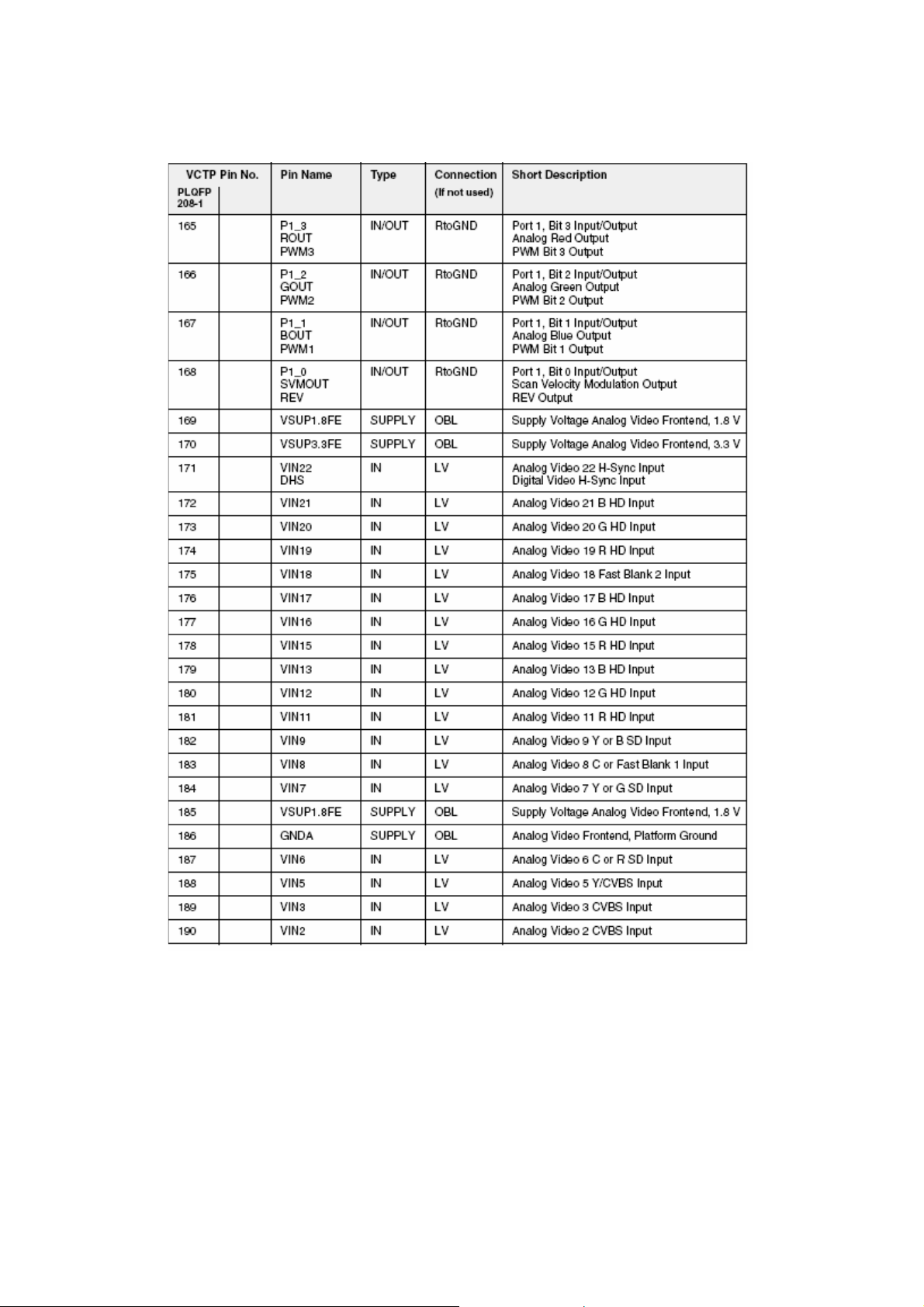

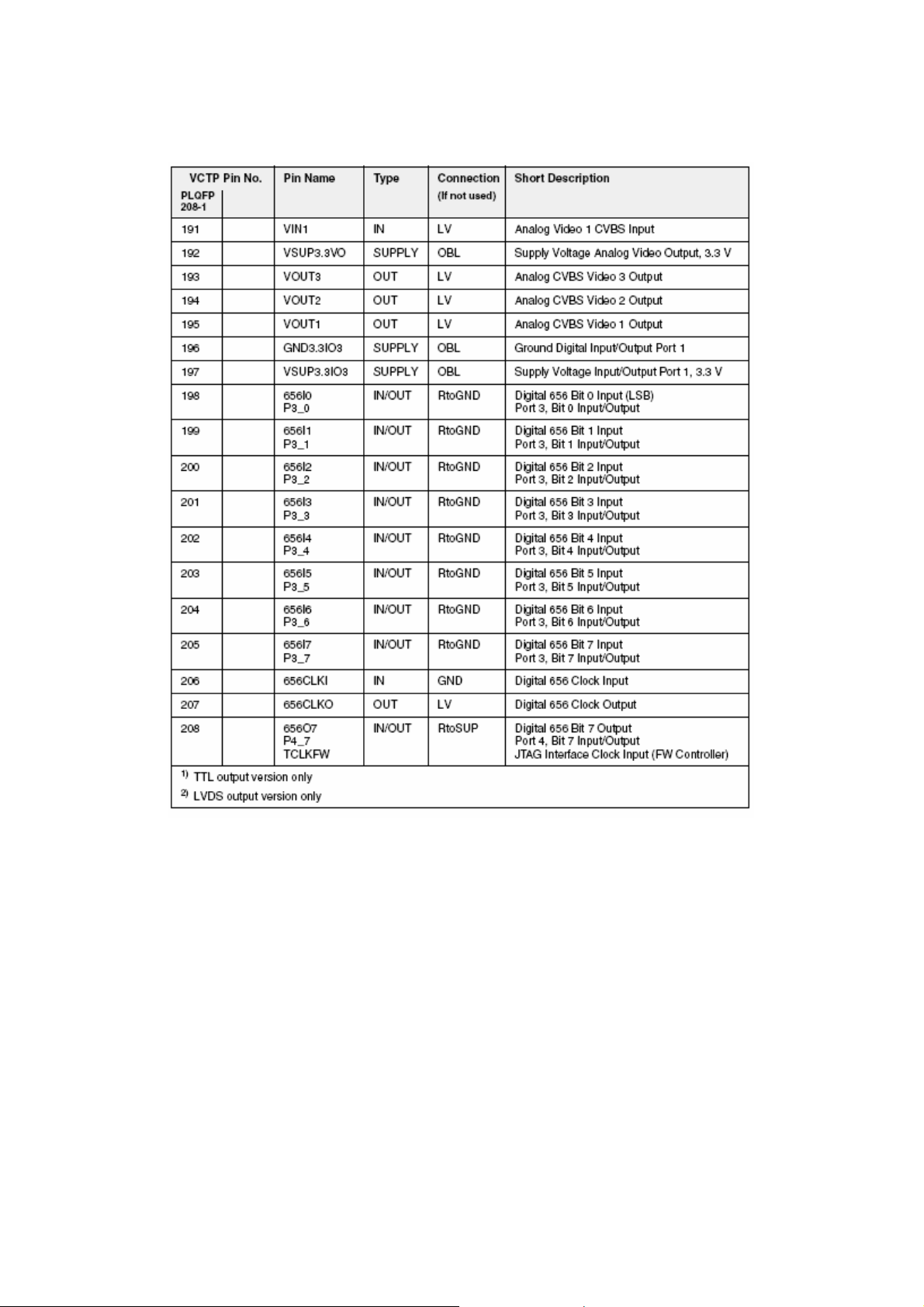

5.6 Port Allocation ..............................................................................................................11

6 DRX 3961A...........................................................................................................................20

6.1 General Desription ........................................................................................................20

6.2 Features.........................................................................................................................20

7 SERIAL 64K I2C EEPROM M24C64WBN6................................................. .....................21

7.1 General Description....................................................................................................... 21

7.2 Features.........................................................................................................................21

7.3 Absolute Maximum Ratings..........................................................................................22

7.4 Pinning ..........................................................................................................................22

8 CLASS AB STEREO HEADPHONE DRIVER TDA7050 .................................................22

8.1 General Description....................................................................................................... 22

8.2 Features.........................................................................................................................22

8.3 Pinning ..........................................................................................................................23

9 SAW FILTER X6966M........................................................................................................23

9.1 Features:........................................................................................................................23

9.2 Pin configuration:..........................................................................................................23

9.3 Frequency response:...................................................................................................... 23

10 MPEG DECODER µPD61115 ......................................................................................... 24

10.1 DESCRIPTION............................................................................................................. 24

10.2 FEATURES...................................................................................................................25

11 DRX 3973D.......................................................................................................................25

11.1 Introduction...................................................................................................................25

11.2 Features......................................................................................................................... 25

11.3 Applications ..................................................................................................................26

12 PI6CX100-27MHz 3.3V VCXO for Set-Top Box Applications ...................................... 26

12.1 Features......................................................................................................................... 26

12.2 Description.................................................................................................................... 26

13 74V1G08...........................................................................................................................27

14 FMS6145...........................................................................................................................27

15 IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM........................................ 28

15.1 LM1117.........................................................................................................................28

15.1.1 General Description...............................................................................................28

15.1.2 Features.................................................................................................................29

15.1.3 Applications ..........................................................................................................29

15.1.4 Absolute Maximum Ratings.................................................................................. 29

15.1.5 Pinning ..................................................................................................................29

15.2 LM1086.........................................................................................................................29

15.2.1 General Description...............................................................................................29

15.2.2 Features.................................................................................................................30

15.2.3 Applications ..........................................................................................................30

15.2.4 Absolute Maximum Ratings.................................................................................. 30

15.2.5 Pinning ..................................................................................................................30

15.3 MP1593......................................................................................................................... 31

15.3.1 General Description...............................................................................................31

15.3.2 Features.................................................................................................................31

15.3.3 Applications ..........................................................................................................31

15.3.4 Absolute Maximum Ratings.................................................................................. 32

15.3.5 Electrical Characteristics....................................................................................... 32

15.3.6 Pinning ..................................................................................................................32

15.4 FDC642P.......................................................................................................................33

15.4.1 General Description...............................................................................................33

15.4.2 Features.................................................................................................................33

15.4.3 Absolute Maximum Ratings.................................................................................. 33

15.4.4 Pinning ..................................................................................................................34

15.5 ANX9021 ......................................................................................................................34

15.5.1 Features.................................................................................................................34

15.6 24LC02.......................................................................................................................... 35

15.6.1 General Description...............................................................................................35

15.6.2 Features.................................................................................................................35

15.6.3 10.6.3 Pinning .......................................................................................................36

15.7 µPA672T....................................................................................................................... 36

15.7.1 General Description...............................................................................................36

15.7.2 Features.................................................................................................................36

15.7.3 Absolute Maximum Ratings.................................................................................. 36

15.7.4 Pinning ..................................................................................................................37

15.8 M74HC4052..................................................................................................................37

15.8.1 General Description...............................................................................................37

15.8.2 Features.................................................................................................................37

15.8.3 Absolute Maximum Ratings.................................................................................. 37

15.8.4 Pinning ..................................................................................................................38

15.9 Max809..........................................................................................................................38

15.9.1 General Description...............................................................................................38

15.9.2 Features.................................................................................................................39

15.9.3 Absolute Maximum Ratings.................................................................................. 39

15.9.4 Pinning ..................................................................................................................40

15.10 24LC21...................................................................................................................... 40

15.10.1 General Description...........................................................................................40

15.10.2 Features.............................................................................................................40

15.10.3 Absolute Maximum Ratings.............................................................................. 40

15.10.4 Pinning ..............................................................................................................41

16 SERVICE MENU SETTINGS.......................... ................................ ................................41

16.1 Video Setup...................................................................................................................41

16.2 AudioSetup....................................................................................................................42

16.3 Options 1....................................................................................................................... 42

16.4 Options 2....................................................................................................................... 43

16.5 Service Scan/Tuning Setup ...........................................................................................44

16.6 External Source Settings ............................................................................................... 44

16.7 Picture Mode.................................................................................................................44

16.8 Reset TV-Set................................................................................................................. 45

17 SOFTWARE UPDATE DESCRIPTION..........................................................................45

2

17.1 Analog Software Update Via I

C..................................................................................45

17.2 Analog Software Update Via UART ............................ ...... .. ...... ..... ... ..... ... ..... ..... ... .....46

18 BLOCK DIAGRAMS.......................................................................................................46

18.1 General Block Diagram.................................................................................................46

18.2 Power Management....................................................................................................... 48

18.3 DRX (IF Demodulator) Block Diagram........................................................................48

18.4 VCT Pro ........................................................................................................................49

18.4.1 General Block Diagram.........................................................................................49

18.4.2 MSP Block Diagram ........................................................... ................................ ..51

18.4.3 Video Processor of VCT 7wxyP Block Diagram................................................ 51

1 INTRODUCTION

17MB12 Main Board is a single board IDTV project, consists of Micronas and NEC

concept. VCT_Pro and Emma2LL are used as controller for TV and IDTV side

respectively. VCT_Pro is capable of handling Audio processing, video processing,

motion adaptive upconversion (MAU), Scaling-Display processing and FPD control

(DPS), unified memory for audio video and Text, 3D comb filter-PC connectivity, OSD

and text processing. Emma2LL is capable of handling MPEG1 and MPEG2 decoding

and provide nearly all the functionality required to realise a high performance and costeffective digital set-top box or integrated digital TV.

TV supports DVB-T reception and following analog receptions PAL, SECAM, NTSC

colour standards and multiple transmission standards as B/G, D/K, I/I’, and L/L’

including German and NICAM stereo.

Sound system output is supplying 2x8W (10%THD) for stereo 8 speakers.

Supported peripherals are:

1 RF input VHF1, VHF3, UHF @ 75Ohm

1 FAV input

2 SCART sockets

1 SVHS input

1 Stereo Headphone input

1 YPbPr

1 PC input

2 HDMI input

1 Stereo audio input for PC and YPbPr

1 Stereo audio output

1 Subwoofer

1 Spdif

2 TUNER

Vertical mounted digital tuner is used in the product, which is suitable for analog

reception with DRX-A. The tuning is available through the digitally controlled I2C bus

(PLL). Below you will find info on the Tuner in use.

2.1 General description of DTT71307:

The DTT 755XX is designed for digital terrestrial reception in VHFIII and UHF,

compliance with the European digital terrestrial standard ETS 300 744. In addition the

tuner covers all analog channels from 44,25 MHz to 863,25 MHz. It is a two band

concept VHF and UHF,with VHF switch between VHF low (VHF I) and VHF high (VHF

III).

2.2 Features of DTT71307:

• VHF I/III/ UHF frequency range

• Antenna loop through (optional)

• Low phase noise

• High level digital IF outputs

• RF-Modulator input for loop through to TV output (optional)

• Wide band AGC

• Indoor Antenna power feed through (optional)

2.3 Pinning:

3 AUDIO AMPLIFIER STAGE WITH TDA8932

3.1 General Description

The TDA8932 device is the high-power version that delivers an output power of 2 x 10

WRMS to 2 x 25 WRMS in a Single Ended (SE) configuration or 10 WRMS to 50 WRMS

in a Bridge Tied Load (BTL) configuration. The TDA8933 device is the low-power

version that delivers an output power of 2 x 5 WRMS to 2 x 15 WRMS in a Single Ended

(SE) configuration or 10 WRMS to 20 WRMS in a Bridge Tied Load (BTL) configuration.

This high efficiency SMA device is designed to operate without a heat sink and has the

flexibility to operate from either an asymmetrical supply or a symmetrical supply with a

wide range (10 V to 36 V or +/-5 V to +/-18 V). The TDA8932/33 device utilizes two

advanced features, respectively the thermal fold back and the cycle-by-cycle current

limiting to avoid audio holes (interruptions) during normal operation.

3.2 Features

• High efficiency Class-D audio amplifier due to a low RDS_ON

• Operates from a wide voltage range 10 V to 36 V (asymmetrical) or +/-5 V to +/-18 V

(symmetrical)

• Maximum power capability:

• TDA8932 is 2 x 25 WRMS maximum in 4 SE without heat sink

• TDA8933 is 2 x 15 WRMS maximum in 8 SE without heat sink

• Cycle-by-cycle current limiting to avoid interruption during normal operation

• Unique Thermal Foldback (TF) to avoid interruption during normal operation

• Integrated Half Supply Voltage (HVP) buffers for reference and SE output capacitance

(asymmetrical supply)

• Internal logic for pop-free power supply on/off cycling

• Low standby-current in SLEEP-mode for power saving regulations

3.3 Applications

• Flat-TV application

• Flat panel monitors

• Multimedia systems

• Wireless speakers

• Micro systems

3.4 Pinning

4 POWER STAGE

The DC voltages required at various parts of the chassis and inverters are provided by a

main power supply unit and power interface board. The main power supply unit is

designed for 24V and 12V DC supply. Power stage which is on-chasis generates +24V

for audio amplifier, 1.8V and 3.3V stand by voltage and 8V, 12V, 5V and 3.3Vsupplies

for other different parts of the chassis.

5 MICROCONTROLLER (VCTP)

5.1 General Features

The VCT 7wxyP is dedicated to high-quality FPD and double-scan TV sets. Modular

design and deep-submicron technology allow the economic integration of features in

LCD/plasma TV and in all classes of double-scan CRT TV sets. The VCT 7wxyP family

is based on approved functional blocks of existing Micronas products for audio and

video.

Each member of the family contains the entire audio, video, up-conversion processing

for 4:3 and 16:9 50/60 Hz progressive or 100/120 Hz interlaced stereo TV sets and the

control/data interface for flat-panel displays. The integrated microcontroller is supported

by a powerful OSD and graphics generator with integrated teletext acquisition.

5.1.1 Controller:

• High-performance 8-bit microcontroller, 8051 compatible

• Up to 512 kByte in system program Flash

• WST, PDC, VPS, and WSS acquisition

• Closed caption and V-chip acquisition

• Up to 10 page on chip teletext memory

• Up to 1000 pages with internal memory

• Up to 30 GPIO

5.1.2 Audio:

• Multistandard TV-sound demodulation:

-All A2/NICAM standards

-BTSC/SAP with DBX

-EIA-J

• Baseband sound processing for loudspeaker channel:

-Volume, bass, treble, loudness, balance

-Spatial effect (e.g. pseudo stereo)

-Micronas AROUND

(Virtual Dolby Surround optional)

-Micronas BASS

-BBE

-SRS WOW

-SRS TruSurround XT

-Lipsync function

5.1.3 Video:

• CVBS, S-VHS, YCrCb and RGB inputs

• HDTV YPrPb and RGB inputs

• ITU656 input

• Linedoubling with vertical detail enhancement (without internal memory)

• State of the art motion adaptive up conversion (with internal memory)

• 4H adaptive comb filter for PAL/NTSC (without internal memory)

• 3D comb filter for PAL/NTSC (with internal memory) (Optional)

• Internal SDR RAM interface

• Powerful horizontal and vertical scaling inclusive

• Nonlinear horizontal scaling “panorama vision”

• picture adaptive image improvements (DCE, LSE, CTI, SCE, NCE)

• non-linear colorspace enhancement (NCE) with 32 programmable slopes and

sections per RGB component (blue stretch, static black stretch, gamma

correction).

• Dynamic contrast enhancement (DCE) (histogram based black stretch with peak

black and activity detection and contrast adaption)

• Luma sharpness enhancement (LSE)

• Color transient improvement (CTI)

• Selective color enhancement (SCE) for skin tone correction, blue and green

stretch

5.2 Multistandard Sound Processor (MSP) Features

The MSP receives the analog Sound IF signal from the tuner and converts it to digital

with its internal SIF-AD converter. The MSP is able to demodulate all TV sound

standards worldwide including the digital NICAM system. TV stereo sound standards

that are unavailable for a specific VCTP version are processed in analog mono sound of

the standard. In that case, stereo or bilingual processing will not be possible.

• Sound IF input

• Worldwide FM/AM-mono sound demodulation

• FM stereo sound demodulation (A2, EIA-J)

• BTSC/SAP demodulation with DBX

• NICAM demodulation

• FM radio & RDS/RBDS demodulation

• Automatic standard detection

• automatic volume correction (AVC)

• Automatic sound select

• Baseband processing for loudspeaker channel:

volume, bass, treble, loudness, balance

-spatial effect (e.g. pseudo stereo)

-Micronas AROUND

-Micronas BASS

-SRS WOW (optional)

-SRS TruSurround XT (optional)

-delayline for lipsync function (shared memory)

-Virtual Dolby Surround (optional)

• 1 I2S input for external ATSC/DVD decoder

• 1 I2S interface for audio delayline

• 1 SPDIF output

• Audio i/o switches

-4 analog stereo line inputs and 2 analog stereo line outputs (configurable 5

analog stereo line inputs and 1 analog stereo line output)

-1 analog stereo loudspeaker output

-1 analog subwoofer output

-1 analog stereo headphone output

5.3 Video Features

The TVT is a Teletext decoder for decoding World System Teletext data, as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide-Screen

Signalling (WSS) data used for PALplus transmissions (line 23). The device also

supports Closed Caption acquisition and decoding.

The TVT provides an integrated general-purpose, fully 8051-compatible microcontroller

with television-specific hardware features. The microcontroller has been enhanced to

provide powerful features such as memory banking, data pointer, additional interrupts,

shared memory access etc.

The TVT has an internal XRAM of 32 KB and a BOOT ROM of 4 KB. For operation the

code is fetched from a 16bit FLASH, which can be addressed up to 1 MByte.

The controller with dedicated hardware does most of the internal TTX acquisition

processing, transfers data to/from external memory interface, and receives/transmits

data via I2C-bus interface. In combination with dedicated hardware, the slicer stores

TTX data in a VBI buffer of 1 KB. The microcontroller firmware performs all the

acquisition tasks (hamming and parity checks, page search, and evaluation of header

control bits) once per field. Additionally, the firmware can provide high-end Teletext

features like Packet-26 handling, FLOF/TOP and list-pages. The interface-to-user

software is optimized for minimal overhead. TVT is realized in deep submicron

technology with 1.8 V supply voltage and 3.3 V I/O (TTL compatible).

• 16 analog video inputs (4xCVBS/Y/C + 3xRGB/YCrCb/YPrPb)

• Video input switch matrix

• 3 analog video outputs (integrated Y+C adder)

• 24-bit RGB/H/V/clk input (e.g. ext. DVI decoder) or 656 8bit input

• 656 8bit input/output (e. g. for external high-end up conversion by FRCA)

• Multi-standard color decoder PAL/NTSC/SECAM including all substandards

• 2D adaptive comb filter for PAL/NTSC with vertical peaking

• 3D-comb filter for PAL/NTSC (Optional)

• Macrovision compliant multi-standard sync processing

• Trilevel sync slicer for HDTV

• Macrovision detection

• High-quality soft mixer controlled by Fast Blank (alpha blending)

• Fastblank monitor via I2C

• Noise measurement

• Letterbox detection (auto-wide)

• Split screen (OSD and video side by side) and AV PIP

5.4 Controller Features

The TVT is a Teletext decoder for decoding World System Teletext data, as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide-Screen

Signalling (WSS) data used for PALplus transmissions (line 23). The device also

supports Closed Caption acquisition and decoding.

The TVT provides an integrated general-purpose, fully 8051-compatible microcontroller

with television-specific hardware features. The microcontroller has been enhanced to

provide powerful features such as memory banking, data pointer, additional interrupts,

shared memory access etc.

• High performance 8-bit microcontroller, 8051 instruction set compatible

• 81 MHz system clock, two machine cycles per instruction

• On-chip debug support (OCDS)

• Up to 512 kByte in system program Flash

• 256 byte on-chip program RAM

• 128 byte on-chip extended stack RAM

• 4-level, 24-input interrupt controller

• Patch module for 16 ROM locations

• Two 16-bit reloadable timers

• Capture compare timer for infrared decoding

• Watchdog timer

• Uart

• Real time clock

• PWM units (2 channels 14-bit, 6 channels 8-bit)

• 8-bit ADC (4 channels)

• I2C bus master/slave interface

• Up to 32 programmable I/O ports

5.5 OSD & Teletext Features

The on-chip display unit for displaying Level 1.5 Teletext data can also be used for

customer-defined onscreen displays.

The TVT has an internal XRAM of 32 KB and a BOOT ROM of 4 KB. For operation the

code is fetched from a 16bit FLASH, which can be addressed up to 1 MByte.

In combination with dedicated hardware, the slicer stores TTX data in a VBI buffer of 1

KB. The microcontroller firmware performs all the acquisition tasks (hamming and parity

checks, page search, and evaluation of header control bits) once per field. Additionally,

the firmware can provide high-end Teletext features like Packet-26 handling, FLOF/TOP

and list-pages. The interface-to-user software is optimized for minimal overhead.

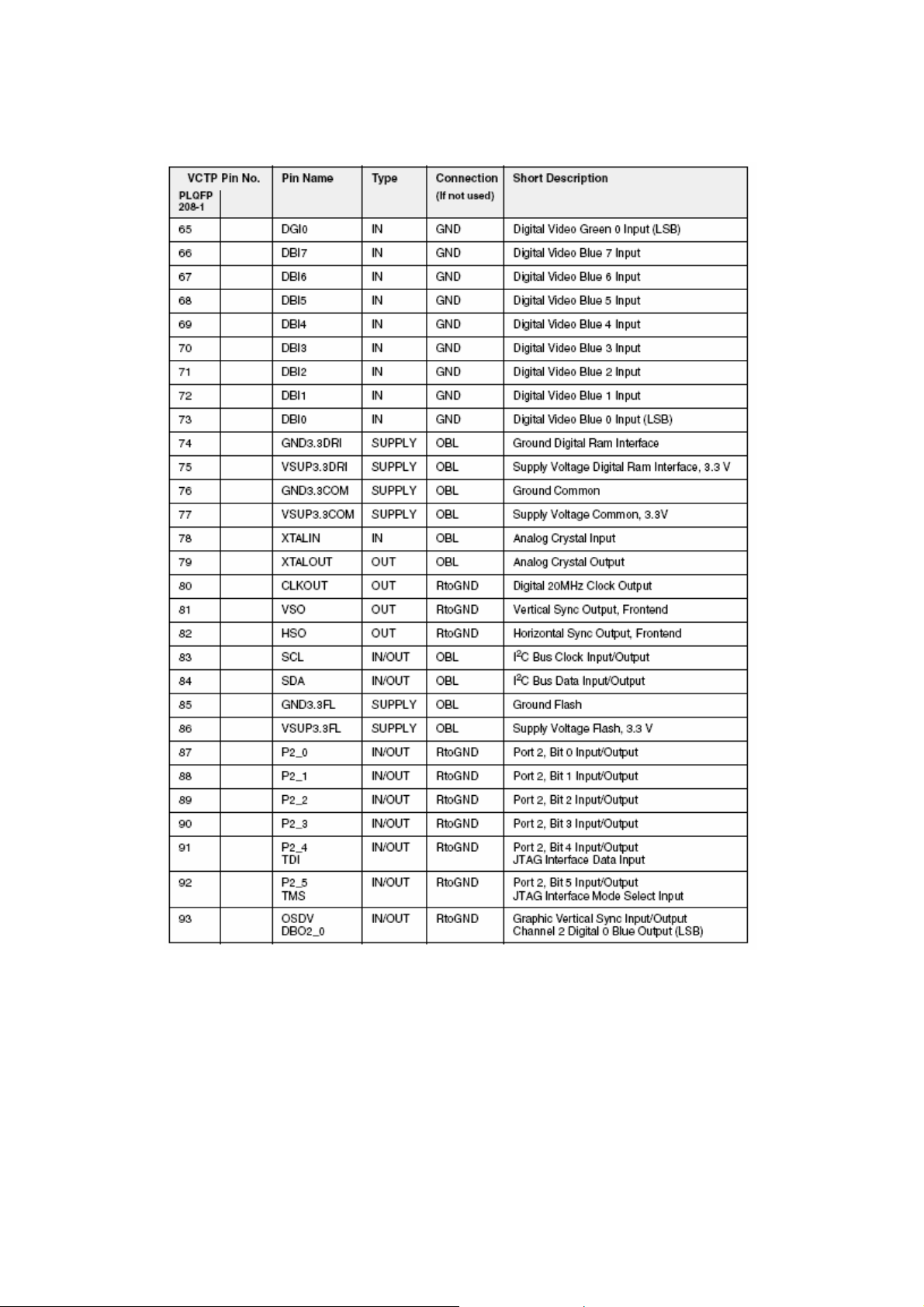

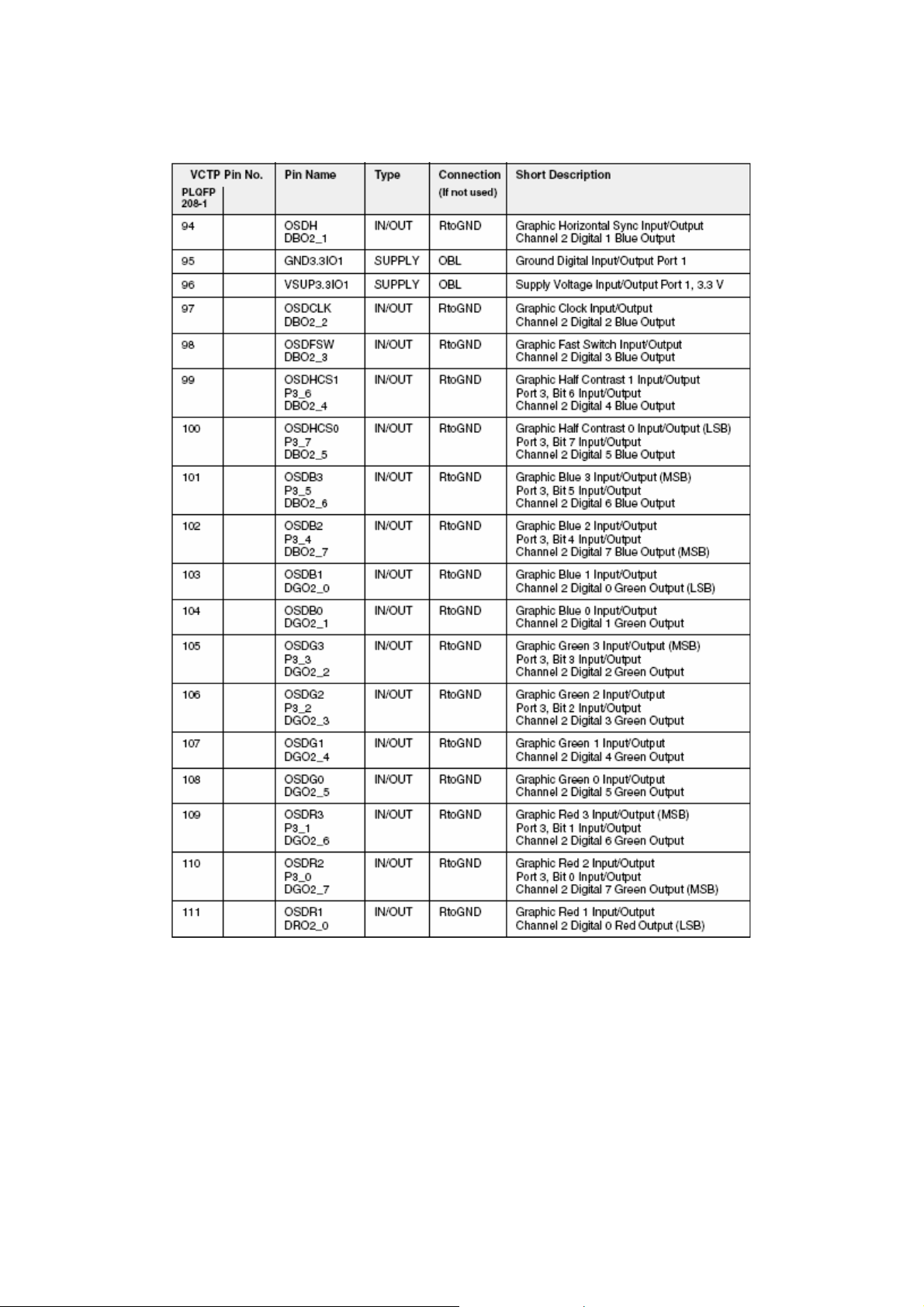

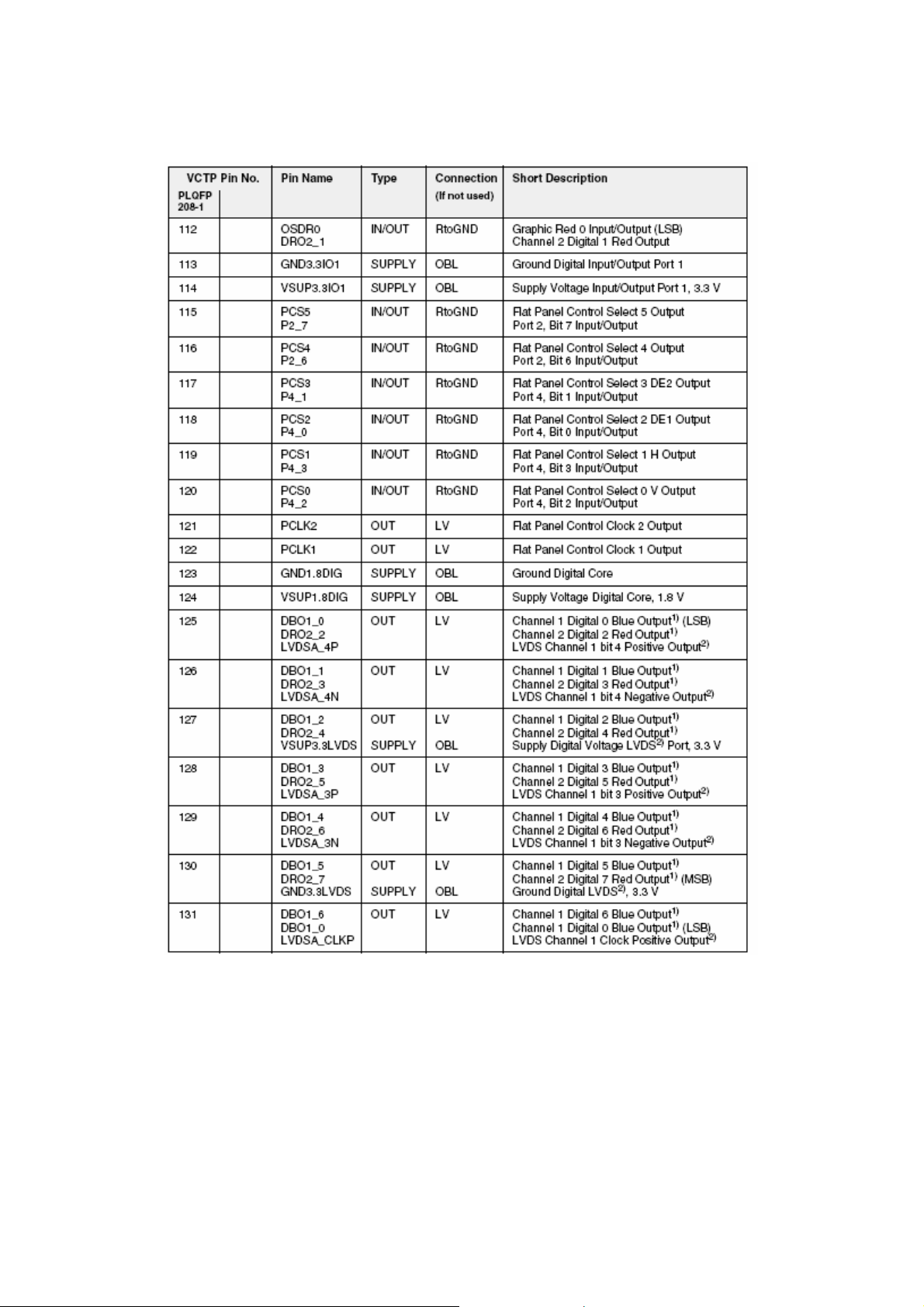

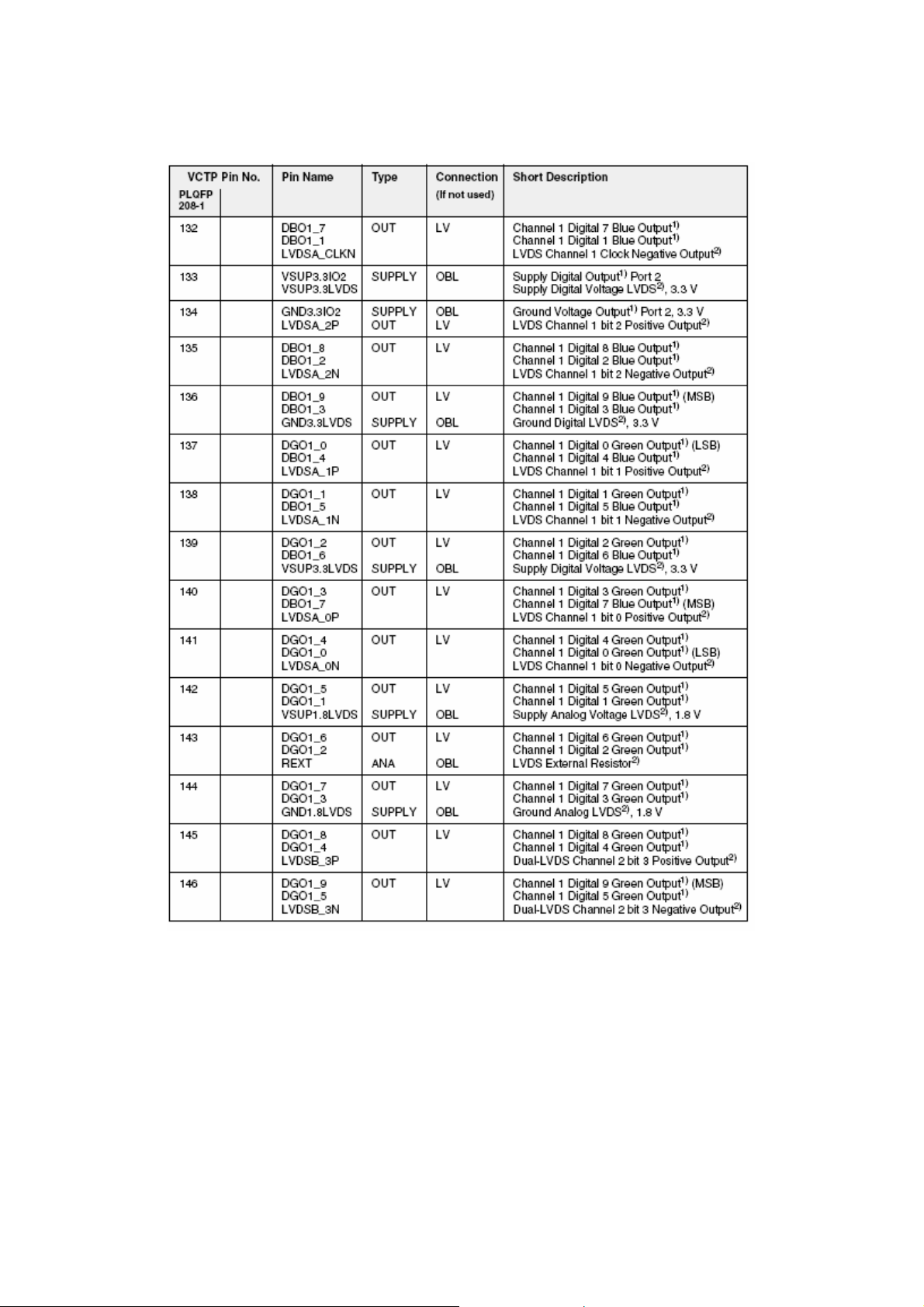

5.6 Port Allocation

6 DRX 3961A

6.1 General Desription

The DSP-based Analog TV IF Demodulator DRX 396xA performs the entire

multistandard Quasi Split Sound (QSS) TV IF processing, AGC, video demodulation,

and generation of the sound IF (SIF), requiring only one SAW filter. The IC is designed

for applications in TV sets, VCRs, PC cards, and TV tuners.

The alignment-free DRX 396xA does not need special external components. All control

functions and status registers are accessible via I2C bus interface.

6.2 Features

• Multistandard QSS IF processing with a single SAW

• Highly reduced amount of external components (no tank circuit, no

potentiometers, no SAW switching)

Loading...

Loading...