Vestel 17MB01-3 Schematic

TFT TV

SERVICE MANUAL

TABLE OF CONTENTS

1. INTRODUCTION ..........................................................................................................................................1

2. TUNER .........................................................................................................................................................1

3. IF PART (DRX 3960A)..................................................................................................................................1

4. MULTI STANDARD SOUND PROCESSOR ................................................................................................2

5. AUDIO AMPLIFIER STAGE WITH TDA7299 ..............................................................................................2

6. POWER ........................................................................................................................................................2

7. MICROCONTROLLER SDA55XX................................................................................................................2

7.1. General Features...................................................................................................................................2

7.2. External Crystal and Programmable Clock Speed ................................................................................2

7.3. Microcontroller Features........................................................................................................................2

7.4. Memory..................................................................................................................................................2

7.5. Display Features....................................................................................................................................2

7.6. ROM Characters....................................................................................................................................3

7.7. Acquisition Features ..............................................................................................................................3

7.8. Ports ......................................................................................................................................................3

8. SERIAL ACCESS CMOS 8K (1024*8) EEPROM ST24C08........................................................................3

9. CLASS AB STEREO HEADPHONE DRIVER TDA1308 .............................................................................3

10. SAW FILTERS ..........................................................................................................................................3

11. IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM ........................................................................4

11.1. TSOP17.. ...........................................................................................................................................4

11.1.1. General Description

11.1.2. Features

11.2. MC34167 ...........................................................................................................................................4

11.2.1. General Description

11.2.2. Features

11.3. LM7808/09 .........................................................................................................................................5

11.3.1. Description

11.3.2. Features

11.4. SDA55XX...........................................................................................................................................5

11.4.1. General description

11.5. ST24C08............................................................................................................................................6

11.5.1. General description

11.5.2. Features

11.6. SST37VF040 .....................................................................................................................................6

11.6.1. Description

11.6.2. Features

11.6.3. Pin Description

11.7. ST24LC21..........................................................................................................................................7

11.7.1. Description

11.7.2. Features

11.7.3. Pin connections

11.8. VPC3230D .........................................................................................................................................8

11.8.1. General Description

11.8.2. Pin Connections and Short Descriptions

11.9. AL300...............................................................................................................................................10

11.9.1. General Description

11.9.2. Features

11.9.3. Pin Definition and Description

11.10. LM1086 ............................................................................................................................................12

11.10.1. Description

11.10.2. Features

11.10.3. Applications

11.10.4. Connection Diagrams

11.11. LM1117 ............................................................................................................................................13

11.11.1. General Description

11.11.2. Features

11.11.3. Applications

........................................................................................................................................4

........................................................................................................................................4

....................................................................................................................................5

........................................................................................................................................5

........................................................................................................................................6

....................................................................................................................................6

........................................................................................................................................6

....................................................................................................................................7

........................................................................................................................................7

......................................................................................................................................10

..............................................................................................................................12

...................................................................................................................................13

...................................................................................................................................13

.....................................................................................................................4

.....................................................................................................................4

.....................................................................................................................5

.....................................................................................................................6

.............................................................................................................................7

............................................................................................................................8

.....................................................................................................................8

..................................................................................8

...................................................................................................................10

..................................................................................................10

............................................................................................................................13

............................................................................................................13

...............................................................................................................13

............................................................................................................................13

i

11.11.4. Connection Diagrams

11.12. TDA7299 ..........................................................................................................................................14

11.12.1. Description

11.12.2. Features

11.12.3. Pin Connection

11.13. DS90C385 .......................................................................................................................................14

11.13.1. General Description

11.13.2. Features

11.13.3. Pin Description

11.14. TDA1308 ..........................................................................................................................................16

11.14.1. General Description

11.14.2. Features

11.14.3. Pinning

11.15. TL431 ...............................................................................................................................................16

11.15.1. Description

11.15.2. Features

11.15.3. Pin Configurations

11.16. AL875...............................................................................................................................................17

11.16.1. General Description

11.16.2. General Features

11.16.3. Pin Definition and Description

11.17. 74HC244A .......................................................................................................................................19

11.17.1. Description

11.17.2. General Features

11.17.3. Pin Description

11.18. ICS1523 ...........................................................................................................................................20

11.18.1. Description

11.18.2. Features

11.19. MC34063 .........................................................................................................................................20

11.19.1. Description

11.19.2. Features

11.19.3. Pin connections

11.20. MSP34X0G ......................................................................................................................................21

11.20.1. Introduction

11.20.2. Features

11.20.3. Pin connections

12. SERVICE MENU SETTINGS..................................................................................................................24

12.1. ADJUST MENU SETTINGS ............................................................................................................24

12.2. OPTIONS MENU SETTINGS ..........................................................................................................26

12.3. APS WSS TEST MENU...................................................................................................................30

13. BLOCK DIAGRAM ..................................................................................................................................31

14. CIRCUIT DIAGRAMS .............................................................................................................................32

..............................................................................................................................14

...................................................................................................................................14

.......................................................................................................................14

...................................................................................................................................15

.......................................................................................................................15

...................................................................................................................................16

.....................................................................................................................................16

..............................................................................................................................16

...................................................................................................................................16

..............................................................................................................................19

.......................................................................................................................19

..............................................................................................................................20

...................................................................................................................................20

..............................................................................................................................20

...................................................................................................................................20

.............................................................................................................................21

...................................................................................................................................21

............................................................................................................14

...............................................................................................................14

...............................................................................................................16

..................................................................................................................17

...............................................................................................................17

....................................................................................................................17

..............................................................................................17

....................................................................................................................19

......................................................................................................................20

......................................................................................................................22

ii

1. INTRODUCTION

TFT TV is a progressive scan flicker free colour television with PC input, driving a XGA panel with 4:3

aspect ratio. The chassis is capable of operation in PAL, SECAM, NTSC (playback) colour standards

and multiple transmission standards as B/G, D/K, I/I’, and L/L´. Sound system output is supplying 2x2W

(10%THD) for left and right outputs of 4Ω speakers. The chassis is equipped with one full SCART, one

front-AV, one SVHS, one D-Sub 15 (PC) input and one line out (left and right) and one HP outputs.

2. TUNER

The hardware and software of the TV is suitable for tuners, supplied by different companies, which are

selected from the Service Menu. These tuners can be combined VHF, UHF tuners suitable for CCIR

systems B/G, H, L, L´, I/I´, and D/K. The tuning is available through the digitally controlled I

(PLL). Below you will find info on one of the Tuners in use.

General description of UV1316:

The UV1316 tuner belongs to the UV 1300 family of tuners, which are designed to meet a wide range of

applications. It is a combined VHF, UHF tuner suitable for CCIR systems B/G, H, L, L’, I and I’. The low

IF output impedance has been designed for direct drive of a wide variety of SAW filters with sufficient

suppression of triple transient.

Features of UV1316:

1. Member of the UV1300 family small sized UHF/VHF tuners

2. Systems CCIR: B/G, H, L, L’, I and I’; OIRT: D/K

3. Digitally controlled (PLL) tuning via I

2

C-bus

4. Off-air channels, S-cable channels and Hyperband

5. World standardised mechanical dimensions and world standard pinning

6. Compact size

7. Complies to “CENELEC EN55020” and “EN55013”

2

C bus

Pinning:

1. Gain control voltage (AGC) : 4.0V, Max: 4.5V

2. Tuning voltage

3. I²C-bus address select : Max: 5.5V

4. I²C-bus serial clock : Min:-0.3V, Max: 5.5V

5. I²C-bus serial data : Min:-0.3V, Max: 5.5V

6. Not connected

7. PLL supply voltage : 5.0V, Min: 4.75V, Max: 5.5V

8. ADC input

9. Tuner supply voltage : 33V, Min: 30V, Max: 35V

10. Symmetrical IF output 1

11. Symmetrical IF output 2

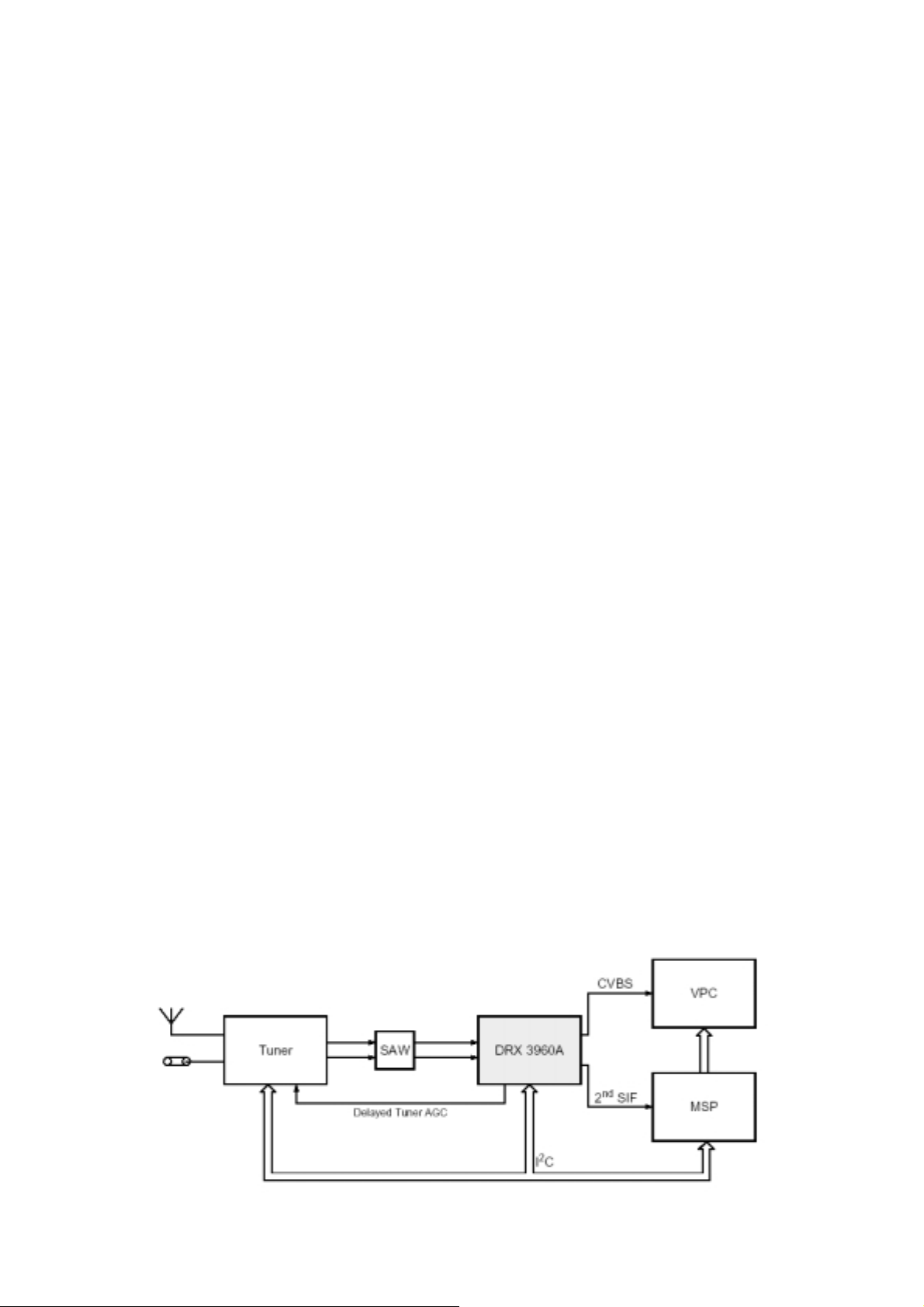

3. IF PART (DRX 3960A)

Tuner output IF signal is pre-filtered with only one 8-MHz channel SAW filter. The entire multi-standard

processing is performed. The Digital Receiver Front-end DRX 3960A performs the entire multi-standard

Quasi Split Sound (QSS) TV IF processing, AGC, video demodulation, and generation of the second

sound IF (SIF). Video and tuner AGC is controlled and adjusted by take over voltage. The alignmentfree DRX 3960A needs no special external components. All control functions and status registers are

accessible via I2C bus interface.

1

4. MULTI STANDARD SOUND PROCESSOR

The MSP 34x0G family of single-chip Multistandard Sound Processors covers the sound processing of

all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound

processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on

a single chip. Signal conforming to the standard by the Broadcast Television Systems Committee

(BTSC). The DBX noise reduction, or alternatively, MICRONAS Noise Reduction (MNR) is performed

alignment free. Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the

FM Stereo Radio standard.

5. AUDIO AMPLIFIER STAGE WITH TDA7299

The TDA7299 is an audio class-AB amplifier assembled in SO package specially designed for sound

cards application. By utilizing two TDA7299, chassis operates as a stereo TV set. TDA7299 has standby feature for low stand-by power consumption by using pin #3. It can deliver 2W without clipping at

9V/4Ω or 12V/8Ω applications.

6. POWER

MC34167 is a power switch regulator, which can output 5V from 12V up to 5A. Utilising a power

MOSFET inside works at a very high efficiency without producing excessive heat. This IC is the main

supply for the voltages used in the main board. Using the pin 5 (stand-by) of IC, TFT TV can have low

stand-by power consumption.

7. MICROCONTROLLER SDA55XX

7.1. General Features

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

• ROM version is used.

7.2. External Crystal and Programmable Clock Speed

• Single external 6MHz crystal, all necessary clocks are generated internally

• CPU clock speed selectable via special function registers.

• Normal Mode 33.33 MHz CPU clock, Power Save mode 8.33 MHz

7.3. Microcontroller Features

• 8bit 8051 instruction set compatible CPU.

• 33.33-MHz internal clock (max.)

• 0.360 ms (min.) instruction cycle

• Two 16-bit timers

• Watchdog timer

• Capture compare timer for infrared remote control decoding

• Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

• ADC (4 channels, 8 bit)

• UART(rxd,txd)

7.4. Memory

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

• UP to 16KByte on Chip Extended RAM (XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

7.5. Display Features

• ROM Character set supports all East and West European Languages in single device

• Mosaic Graphic Character Set

2

• Parallel Display Attributes

• Single/Double Width/Height of Characters

• Variable Flash Rate

• Programmable Screen Size (25 Rows x 33...64 Columns)

• Flexible Character Matrixes (HxV) 12 x 9...16

• Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable

Characters in Enhanced Mode

• CLUT with up to 4096 colour combinations

• Up to 16 Colours per DRCS Character

• One out of 8 Colours for Foreground and Background Colours for 1-bit DRCS and ROM Characters

7.6. ROM Characters

• Shadowing

• Contrast Reduction

• Pixel by Pixel Shiftable Cursor With up to 4 Different Colours

• Support of Progressive Scan and 100 Hz.

• 3 X 4Bits RGB-DACs On-Chip

• Free Programmable Pixel Clock from 10 MHz to 32MHz

• Pixel Clock Independent from CPU Clock

• Multinorm H/V-Display Synchronisation in Master or Slave Mode

7.7. Acquisition Features

• Multistandard Digital Data Slicer

• Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

• Four Different Framing Codes Available

• Data Caption only limited by available Memory

• Programmable VBI-buffer

• Full Channel Data Slicing Supported

• Fully Digital Signal Processing

• Noise Measurement and Controlled Noise Compensation

• Attenuation Measurement and Compensation

• Group Delay Measurement and Compensation

• Exact Decoding of Echo Disturbed Signals

7.8. Ports

• One 8-bit I/O-port with open drain output and optional I 2 C Bus emulation support (Port0)

• Two 8-bit multifunction I/O-ports (Port1, Port3)

• One 4-bit port working as digital or analogue inputs for the ADC (Port2)

• One 2-bit I/O port with secondary function (P4.2, 4.3, 4.7)

• One 4-bit I/O-port with secondary function (P4.0, 4.1, 4.4) (Not available in P-SDIP 52)

8. SERIAL ACCESS CMOS 8K (1024*8) EEPROM ST24C08

The ST24C08 is an 8Kbit electrically erasable programmable memory (EEPROM), organised as 4

blocks of 256*8 bits. The memory is compatible with the I²C standard, two wire serial interface, which

uses a bi-directional data bus and serial clock. The memory carries a built-in 4 bit, unique device

identification code (1010) corresponding to the I²C bus definition. This is used together with 1 chip

enable input (E) so that up to 2*8K devices may be attached to the I²C bus and selected individually.

9. CLASS AB STEREO HEADPHONE DRIVER TDA1308

The TDA1308 is an integrated class AB stereo headphone driver contained in a DIP8 plastic package.

The device is fabricated in a 1 mm CMOS process and has been primarily developed for portable digital

audio applications.

10. SAW FILTERS

X6966M is an 8-MHz SAW Filter which is used for pre-filtering the IF input signal of DRX3960A. The

entire multi-standard processing is performed within this filter which limits the signal bandwidth to 8

MHz and suppresses major parts of the adjacent channels.

3

11. IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM

TSOP17 TDA7299

MC34167 DS90C385

LM7808/09 TDA1308T

SDA55XX TL431

ST24C08 AL875

SST37VF040 74HC244A

ST24LC21 ICS1523

VPC3230D DRX3960A

AL300 MC34063

LM1086 MSP3410G

LM1117

11.1. TSOP17..

11.1.1. General Description

The TSOP17.. – series are miniaturized receivers for infrared remote control systems. PIN diode and

preamplifier are assembled on lead frame, the epoxy package is designed as IR filter. The demodulated

output signal can directly be decoded by a microprocessor. TSOP17.. is the standard IR remote control

receiver series, supporting all major transmission codes.

11.1.2. Features

• Photo detector and preamplifier in one package

• Internal filter for PCM frequency

• Improved shielding against electrical field disturbance

• TTL and CMOS compatibility

• Output active low

• Low power consumption

• High immunity against ambient light

• Continuous data transmission possible (up to 2400 bps)

• Suitable burst length .10 cycles/burst

11.2. MC34167

11.2.1. General Description

The MC34167, MC33167 series are high performance fixed frequency power switching regulators that

contain the primary functions required for dc–to–dc converters. This series was specifically designed to

be incorporated in step–down and voltage–inverting configurations with a minimum number of external

components and can also be used cost effectively in step–up applications.

These devices consist of an internal temperature compensated reference, fixed frequency oscillator

with on–chip timing components, latching pulse width modulator for single pulse metering, high gain

error amplifier, and a high current output switch.

Protective features consist of cycle–by–cycle current limiting, undervoltage lockout, and thermal

shutdown. Also included is a low power standby mode that reduces power supply current to 36 mA.

11.2.2. Features

• Output Switch Current in Excess of 5.0 A

• Fixed Frequency Oscillator (72 kHz) with On–Chip Timing

• Provides 5.05 V Output without External Resistor Divider

• Precision 2% Reference

• 0% to 95% Output Duty Cycle

• Cycle–by–Cycle Current Limiting

• Undervoltage Lockout with Hysteresis

• Internal Thermal Shutdown

• Operation from 7.5 V to 40 V

• Standby Mode Reduces Power Supply Current to 36 mA

• Economical 5–Lead TO–220 Package with Two Optional Leadforms

• Also Available in Surface Mount D

• Moisture Sensitivity Level (MSL) Equals 1

2

PAK Package

4

11.3. LM7808/09

11.3.1. Description

The L7800 series of three-terminal positive regulators is available in TO-220 TO-220FP TO-3 and D 2

PAK packages and several fixed output voltages, making it useful in a wide range of applications.

These regulators can provide local on-card regulation, eliminating the distribution problems associated

with single point regulation. Each type employs internal current limiting, thermal shutdown and safe

area protection, making it essentially indestructible. If adequate heat sinking is provided, they can

deliver over 1A output current. Although designed primarily as fixed voltage regulators, these devices

can be used with external components to obtain adjustable voltages and currents.

11.3.2. Features

• Output Current Up To 1.5 A

• Output Voltages of 5; 5.2; 6; 8; 8.5; 9; 12; 15; 18; 24V

• Thermal Over load protection

• Short Circuit Protection

• Output Transition SOA Protection

11.4. SDA55XX

11.4.1. General description

The SDA55XX is a single chip teletext decoder for decoding World System Teletext data as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide Screen Signalling

(WSS) data used for PAL plus transmissions (Line 23). The device also supports Closed caption

acquisition and decoding. The device provides an integrated general-purpose, fully 8051-compatible

Microcontroller with television specific hardware features. Microcontroller has been enhanced to provide

powerful features such as memory banking, data pointers, and additional interrupts etc. The on-chip

display unit for displaying Level 1.5 teletext data can also be used for customer defined on screen

displays. Internal XRAM consists of up to16 Kbytes. Device has an internal ROM of up to 128 KBytes.

ROMless versions can access up to 1 MByte of external RAM and ROM. The SDA 55XX supports a

wide range of standards including PAL, NTSC and contains a digital slicer for VPS, WSS, PDC, TTX

and Closed Caption, an accelerating acquisition hardware module, a display generator for Level 1.5

TTX data and powerful On screen Display capabilities based on parallel attributes, and Pixel oriented

characters (DRCS).

The 8-bit Microcontroller runs at 360 ns. cycle time (min.). Controller with dedicated hardware does

most of the internal TTX acquisition processing, transfers data to/from external memory interface and

receives/ transmits data via I

2

C-firmware user-interface. The slicer combined with dedicated hardware

stores TTX data in a VBI buffer of 1 Kilobyte. The Microcontroller firmware performs all the acquisition

tasks (hamming and parity-checks, page search and evaluation of header control bits) once per field.

Additionally, the firmware can provide high-end Teletext features like Packet-26-handling, FLOF, TOP

and list-pages. The interface to user software is optimized for minimal overhead. SDA 55XX is realized

in 0.25 micron technology with 2.5 V supply voltage and 3.3 V I/O (TTL compatible). The software and

hardware development environment (TEAM) is available to simplify and speed up the development of

the software and On Screen Display. TEAM stands for TVT Expert Application Maker. It improves the

TV controller software quality in following aspects:

– Shorter time to market

– Re-usability

– Target independent development

– Verification and validation before targeting

– General test concept

– Graphical interface design requiring minimum programming and controller know how.

– Modular and open tool chain, configurable by customer.

5

11.5. ST24C08

11.5.1. General description

The ST24C08 is an 8Kbit electrically erasable programmable memory (EEPROM), organised as 4

blocks of 256 * 8 bits. The memory operates with a power supply value as low as 2.5V. Both Plastics

Dual-in-Line and Plastic Small Outline packages are available.

11.5.2. Features

• Minimum 1 million ERASE/WRITE cycles with over 10 years data retention

• Single supply voltage: 4.5 to 5.5V

• Two wire serial interface, fully I2C-bus compatible

• Byte and Multibyte write (up to 8 bytes)

• Page write (up to 16 bytes)

• Byte, random and sequential read modes

• Self timed programming cycle

PINNING PIN VALUE

1. Write protect enable (Ground) : 0V

2. Not connected (Ground) : 0V

3. Chip enable input (Ground) : 0V

4. Ground : 0V

5. Serial data address input/output : Input LOW voltage: Min: -0.3V, Max: 0.3*Vcc

Input HIGH voltage: Min: 0.7*Vcc, Max: Vcc+1

6. Serial clock : Input LOW voltage: Min: -0.3V, Max: 0.3*Vcc

Input HIGH voltage: Min: 0.7*Vcc, Max: Vcc+1

7. Multibyte/Page write mode : Input LOW voltage: Min: -0.3V, Max: 0.5V

Input HIGH voltage: Min: Vcc-0.5, Max: Vcc+1

8. Supply voltage : Min: 2.5V, Max: 5.5V

11.6. SST37VF040

11.6.1. Description

The SST37VF512/010/020/040 devices are 64K x8 / 128Kx8 / 256K x8 / 512K x8 CMOS, Many-Time

Programmable (MTP), low cost flash, manufactured with SST’s proprietary, high performance CMOS

SuperFlash technology. The split-gate cell design and thick oxide tunneling injector attain better

reliability and manufacturability compared with alternate approaches. The SST37VF512/010/020/040

can be electrically erased and programmed at least 1000 times using an external programmer, e.g., to

change the contents of devices in inventory. The SST37VF512/010/020/040 have to be erased prior to

programming. These devices conform to JEDEC standard pinouts for byte-wide flash memories.

Featuring high performance Byte-Program, the SST37VF512/010/020/040 provide a typical Byte-Program time of 10 µs. Designed, manufactured, and tested for a wide spectrum of applications, these

devices are offered with an endurance of at least 1000 cycles. Data retention is rated at greater than

100 years. The SST37VF512/010/020/040 are suited for applications that require infrequent writes and

low power nonvolatile storage. These devices will improve flexibility, efficiency and performance while

matching the low cost in nonvolatile applications that currently use UV-EPROMs, OTPs, and mask

ROMs.

11.6.2. Features

• Organized as 64K x8 / 128K x8 / 256K x8 / 512K x8

• 2.7-3.6V Read Operation

• Superior Reliability

– Endurance: At least 1000 Cycles

– Greater than 100 years Data Retention

• Low Power Consumption:

– Active Current: 10 mA (typical)

– Standby Current: 2 µA (typical)

• Fast Read Access Time:

– 70 ns

– 90 ns

6

• Latched Address and Data

• Fast Byte-Program Operation:

– Byte-Program Time: 10 µs (typical)

– Chip Program Time:

0.6 seconds (typical) for SST37VF512

1.2 seconds (typical) for SST37VF010

2.4 seconds (typical) for SST37VF020

4.8 seconds (typical) for SST37VF040

• Electrical Erase Using Programmer

– Does not require UV source

– Chip-Erase Time: 100 ms (typical)

• CMOS I/O Compatibility

• JEDEC Standard Byte-wide Flash EEPROM Pinouts

• Packages Available

– 32-lead PLCC

– 32-lead TSOP (8mm x 14mm)

– 32-pin PDIP

11.6.3. Pin Description

Symbol Pin name Functions

1

A

-A

MS

DQ7-D

Q0

CE# Chip Enable

WE# Write Enable To program or erase (WE# = VIL pulse during Program or Erase)

OE# Output Enable To gate the data output buffers during Read operation when low

V

DD

V

SS

NC No Connection Unconnected pins.

Address Inputs To provide memory addresses.

0

Data Input/output To output data during Read cycles and receive input data during Program

cycles. The outputs are in tri-state when OE# or CE# is high.

To activate the device when CE# is low.

Power Supply To provide 3.0V supply (2.7-3.6V)

Ground

1. AMS = Most significant address

A

= A15 for SST37VF512, A16 for SST37VF010, A17 for SST37VF020, and A18 for SST37VF040

MS

11.7. ST24LC21

11.7.1. Description

The ST24LC21 is a 1K bit electrically erasable programmable memory (EEPROM), organized by 8 bits.

This device can operate in two modes: Transmit Only mode and I

the device is in Transmit Only mode with EEPROM data clocked out from the rising edge of the signal

applied on VCLK. The device will switch to the I

2

C bidirectional mode upon the falling edge of the signal

applied on SCL pin. The ST24LC21 can not switch from the I

2

C bidirectional mode. When powered,

2

C bidirectional mode to the Transmit Only

mode (except when the power supply is removed). The device operates with a power supply value as

low as 2.5V. Both Plastic Dual-in-Line and Plastic Small Outline packages are available.

11.7.2. Features

• 1 million Erase/Write cycles

• 40 years data retention

• 2.5V To 5.5V single supply voltage

• 400k Hz compatibility over the full range of supply voltage

• Two wire serial interface I

2

C bus compatible

• Page Write (Up To 8 Bytes)

• Byte, random and sequential read modes

• Self timed programming cycle

• Automatic address incrementing

• Enhanced ESD/Latch up

• Performances

7

11.7.3. Pin connections

DIP Pin connections CO Pin connections

NC: Not connected

Signal names

SDA Serial data Address Input/Output

SCL Serial Clock (I2C mode)

V

cc

V

ss

VCLK Clock transmit only mode

Supply voltage

Ground

11.8. VPC3230D

11.8.1. General Description

The VPC 323xD is a high-quality, single-chip video front-end, which is targeted for 4:3 and 16:9, 50/60Hz and 100/120 Hz TV sets. It can be combined with other members of the DIGIT3000 IC family (such

as DDP 331x) and/or it can be used with 3rd-party products.

The main features of the VPC 323xD are

• high-performance adaptive 4H comb filter Y/C separator with adjustable vertical peaking

• multi-standard colour decoder PAL/NTSC/SECAM including all substandards

• four CVBS, one S-VHS input, one CVBS output

• two RGB/YC

r Cb

component inputs, one Fast Blank (FB) input

• integrated high-quality A/D converters and associated clamp and AGC circuits

• multi-standard sync processing

• linear horizontal scaling (0.25 ... 4), as well as non-linear horizontal scaling ‘Panorama-vision’

• PAL+ preprocessing

• line-locked clock, data and sync, or 656-output interface

• peaking, contrast, brightness, color saturation and tint for RGB/ YC

r C b

and CVBS/ S-VHS

• high-quality soft mixer controlled by Fast Blank

• PIP processing for four picture sizes (1/4, 1/9, 1/16 or 1/36 of normal size) with 8-bit resolution

• 15 predefined PIP display configurations and expert mode (fully programmable)

• control interface for external field memory

2

• I

C-bus interface

• one 20.25-MHz crystal, few external components

• 80-pin PQFP package

11.8.2. Pin Connections and Short Descriptions

NC = not connected

LV = if not used, leave vacant

X = obligatory; connect as described in circuit diagram

SUPPLYA = 4.75...5.25 V, SUPPLYD = 3.15...3.45 V

Pin No.

PQFP

80-pin

1 B1/CB1IN IN VREF Blue1/Cb1 Analog Component Input

2 G1/Y1IN IN VREF Green1/Y1 Analog Component Input

3 R1/CR1IN IN VREF Read1/Cr1 Analog Component Input

4 B2/CB2IN IN VREF Blue2/Cb2 Analog Component Input

Pin Name Type Connection

(if not used)

Short Description

8

5 G2/Y2IN IN VREF Green2/Y2 Analog Component Input

6 R2/CR2IN IN VREF Read2/Cr2 Analog Component Input

7 ASGF X Analog Shield GND

F

8 FFRSTWIN IN LV or GNDDFIFO Reset Write Input

9V

10 V

11 GND

12 GND

SUPCAP

SUPD

D

CAP

OUT X Digital Decoupling Circuitry Supply Voltage

SUPPLYD X Supply Voltage, Digital Circuitry

SUPPLYD X Ground, Digital Circuitry

OUT X Digital Decoupling Circuitry GND

13 SCL IN/OUT X I2C Bus Clock

14 SDA IN/OUT X I2C Bus Data

15 RESQ IN X Reset Input, Active Low

16 TEST IN GND

17 VGAV IN GND

18 YCOEQ IN GND

D

D

D

Test Pin, connect to GND

D

VGAV Input

Y/C Output Enable Input, Active Low

19 FFIE OUT LV FIFO Input Enable

20 FFWE OUT LV FIFO Write Enable

21 FFRSTW OUT LV FIFO Reset Write/Read

22 FFRE OUT LV FIFO Read Enable

23 FFOE OUT LV FIFO Output Enable

24 CLK20 IN/OUT LV Main Clock output 20.25 MHz

25 GND

26 V

SUPPA

PA

OUT X Pad Decoupling Circuitry GND

OUT X Pad Decoupling Circuitry Supply Voltage

27 LLC2 OUT LV Double Clock Output

28 LLC1 IN/OUT LV Clock Output

29 V

30 GND

SUPLLC

LLC

31 Y7 OUT GND

32 Y6 OUT GND

33 Y5 OUT GND

34 Y4 OUT GND

35 GND

36 V

Y

SUPY

37 Y3 OUT GND

38 Y2 OUT GND

39 Y1 OUT GND

40 Y0 OUT GND

41 C7 OUT GND

42 C6 OUT GND

43 C5 OUT GND

44 C4 OUT GND

45 V

46 GND

SUPC

C

47 C3 OUT GND

48 C2 OUT GND

49 C1 OUT GND

50 C0 OUT GND

51 GND

52 V

SY

SUPSY

SUPPLYD X Supply Voltage, LLC Circuitry

SUPPLYD X Ground, LLC Circuitry

Y

Y

Y

Y

Picture Bus Luma (MSB)

Picture Bus Luma

Picture Bus Luma

Picture Bus Luma

SUPPLYD X Ground, Luma Output Circuitry

SUPPLYD X Supply Voltage, Luma Output Circuitry

Y

Y

Y

Y

C

C

C

C

Picture Bus Luma

Picture Bus Luma

Picture Bus Luma

Picture Bus Luma (LSB)

Picture Bus Chroma (MSB)

Picture Bus Chroma

Picture Bus Chroma

Picture Bus Chroma

SUPPLYD X Supply Voltage, Chroma Output Circuitry

SUPPLYD X Ground, Chroma Output Circuitry

C

C

C

C

Picture Bus Chroma

Picture Bus Chroma

Picture Bus Chroma

Picture Bus Chroma (LSB)

SUPPLYD X Ground Sync Pad Circuitry

SUPPLYD X Supply Voltage, Sync Pad Circuitry

53 INTLC OUT LV Interlace Output

54 AVO OUT LV Active Video Output

55 FSY/HC/HSYA OUT LV Front Sync/ Horizontal Clamp Pulse/Front-End

Horizontal Sync Output

56 MSY/HS IN/OUT LV Main Sync/Horizontal Sync Pulse

57 VS OUT LV Vertical Sync Pulse

58 FPDAT/VSYA IN/OUT LV Front End/Back-End Data/Front-End Vertical Sync

Output

59 V

STBYY

SUPPLYA X Standby Supply Voltage

60 CLK5 OUT LV CCU 5 MHz Clock Output

61 NC - LV or GNDDNot Connected

62 XTAL1 IN X Analog Crystal Input

63 XTAL2 OUT X Analog Crystal Output

64 ASGF X Analog Shield GND

65 GND

F

SUPPLYA X Ground, Analog Front-End

F

66 VRT OUTPUT X Reference Voltage Top, Analog

67 I2CSEL IN X I2C Bus Address Select

9

68 ISGND SUPPLYA X Signal Ground for Analog Input, connect to GND

69 V

70 VOUT OUT LV Analog Video Output

71 CIN IN LV Chroma/Analog Video 5 Input

72 VIN1 IN VRT Video 1 Analog Input

73 VIN2 IN VRT Video 2 Analog Input

74 VIN3 IN VRT Video 3 Analog Input

75 VIN4 IN VRT Video 4 Analog Input

76 V

77 GND

78 VREF OUTPUT X Reference Voltage Top, Analog Component Inputs

79 FB1IN IN VREF Fast Blank Input

80 AISGND SUPPLYA X Signal Ground for Analog Component Inputs, connect

SUPF

SUPAI

AI

SUPPLYA X Supply Voltage, Analog Front-End

SUPPLYA X Supply Voltage, Analog Component Inputs Front-End

SUPPLYA X Ground, Analog Component Inputs Front-End

Front-End

to GND

AI

F

11.9. AL300

11.9.1. General Description

The AL300 is designed to enable simple connection from PC’s or video devices to flat panel displays. It

provides LCD/PDP monitor and projector manufacturers with a low-cost, easy solution to bring TV or

PC video to LCD panels. The AL300 is equipped with a high quality zoom engine that automatically

maintains full screen output display, regardless of the resolution of the incoming signal. The input video

can be linearly and independently zoomed in the x and y directions. The AL300 also provides deinterlacing, filtering, and scaling support for interlaced video to be displayed on a LCD panel. Two

integrated On Screen Display (OSD) windows provide overlay of a control menu, text, or caption on the

output display. With the internal OSD RAM, OSD bitmaps of up to 8K pixels are supported. With

optional external user-defined font table ROM, the AL300 OSD functionality is very flexible with font

size and display location; virtually all languages and fonts are supported. Special OSD effects such as

translucency and blinking offer the manufacturer a unique and vivid way of presenting monitor status,

control menu, or other display information. Used with an AL875 (high speed 3-channel ADC with PLL,

100-pin QFP), the AL300 (in 160-pin QFP) offers the best cost-performance and total solution for LCD

monitors or projectors, or other flat panel devices.

11.9.2. Features

• Converts PC’s or TV’s signals for flat panel displays

• Supports active matrix up to 1280x1024 resolution

• De-interlacing support for video inputs

• Automatic screen positioning support

• Fully programmable zoom ratios

• Independent linear zoom in H and V directions

• Supports single and dual pixel per clock panels

• Dithering logic to enhance color resolution for 12-bit or 18-bit panels

• Built-in high speed PLL

• User-definable font table supporting different languages and font sizes

• Two built-in OSD windows

2

• I

C programmable

• No external memory required

• Single 3.3 volt power with 5 volt tolerant I/O

• 160-pin 28x28 mm PQFP package

11.9.3. Pin Definition and Description

Pin Name Type Pin # Note

Video Interface

TVCLK IN (CMOSd) 1

TVHREF IN (CMOSd) 2

TVVS IN (CMOSs) 3

Video Clock from Video Source

Video Horizontal Active Data Reference

This signal is used to indicate valid data of the YUV input.

Video Vertical Sync Signal

10

TVHS IN (CMOSs) 4 Video Horizontal Sync Signal

2

Graphic Interface

GVS IN (CMOSs) 6

GVH IN (CMOSs) 7

GHREF IN (CMOS) 8

Graphic Vertical Sync Signal

Graphic Horizontal Sync Signal

Graphic Horizontal Active Data Reference

GCLK IN (CMOSd) 9 Graphic Input Clock

R/YIN<7:0> IN (CMOS) 11-18

Red Input When in RGB Mode

Y Input When in CCIR601 422 and 444 Modes

G/UVIN<7:0> IN (CMOS) 20-27

Green Input When in RGB Mode

CbCr Input When in CCIR601 422 Mode

Cb Input When in CCIR601 444 Mode

Refer to register #1Bh for details.

BIN<7:0> IN (CMOS) 29-36

Blue Input When in RGB Mode

Cr Input When in CCIR601 444 Mode

Refer to register #1Bh for details.

Host Interface

HOSTCLK OUT (CMOS) 38

Buffered Output of the Clock Input for Host Interface such as a

Micro-controller

XOUT OUT (CMOS) 39

XIN IN (CMOS) 40

Crystal Output

Crystal Input; the frequency provided is for I

output reference timing when input sync signals are missing or

undetectable. Usually in the range of 10~50MHz.

IREQ OUT (CMOS) 41

SCL IN (CMOSs) 42

SDA INOUT

43

Interrupt Request, active high

2

C Serial Clock Input

I

2

I

C Serial Data Input/Output

(COMSsu)

GOUT1 OUT (CMOS) 81

GOUT2 OUT (CMOS) 82

GOUT3 OUT (CMOS) 83

General Purpose Output. Connected to Register 0x1B bit 2

General Purpose Output. Connected to Register 0x1B bit 3

General Purpose Output. Connected to Register 0x1B bit 1

Configuration

PWRDN IN (CMOSd) 46

Power Down

0, Normal Operation

1, Power Down

2

C Bus Slave Address Select

I2CADDR IN (CMOSd) 47

I

0, write address = 70, read address = 71

1, write address = 72, read address = 73

YUVIN IN (CMOSd) 48

YUV Input

0, RGB Format Video Input

1, CCIR YUV Format Video Input

Refer to RIN, GIN, BIN pins

Test1 IN (CMOSd) 49

Test2 IN (CMOSd) 50

Test Pin

Test Pin

Panel/Display Interface

RB<7:0> OUT (CMOS) 52-55,

57-60

Right Pixel of Interleaved Red Output in Dual Pixel Mode

Valid when Register 0x43 bit4 = ‘1’.

Data are output with PCLKB.

For AL300 ver. A, the B data lag A data by 90° (half SCLK).

For AL300 ver. B, A and B data are aligned.

GB<7:0> OUT (CMOS) 62-65,

67-70

Right Pixel of Interleaved Green Output in Dual Pixel Mode

Valid when Register 0x43 bit4 = ‘1’.

Data are output with PCLKB.

For AL300 ver. A, the B data lag A data by 90° (half SCLK).

For AL300 ver. B, A and B data are aligned.

BB<7:0> OUT (CMOS) 72-75,

77-80

Right Pixel of Interleaved Blue Output in Dual Pixel Mode

Valid when Register 0x43 bit4 = ‘1’.

Data are output with PCLKB.

For AL300 ver. A, the B data lag A data by 90° (half SCLK).

For AL300 ver. B, A and B data are aligned.

PCLKA OUT (CMOS) 84

Leading Pixel Clock of Interleaved Video Output for Right data in

Dual Pixel Mode. Polarity is programmable

PCLKB OUT (CMOS) 85

Lagging Pixel Clock of Interleaved Video Output for Right data in

Dual Pixel Mode. Polarity is programmable.

Default PCLKB lags PCLKA by 180° (one SCLK).

SCLK OUT (CMOS) 86

PHS OUT (CMOS) 88

PVS OUT (CMOS) 89

Display Pixel Clock (for single pixel per clock mode)

Panel/Display Hsync. Can be programmed to either polarity.

Panel/Display Vsync. Can be programmed to either polarity.

C sampling and for

11

Loading...

Loading...