VESTEL 11AK53 Service Manual

AK53 (D.O.C)

SERVICE MANUAL

RELEASE DATE: 22.03.2004

PREPARED BY:

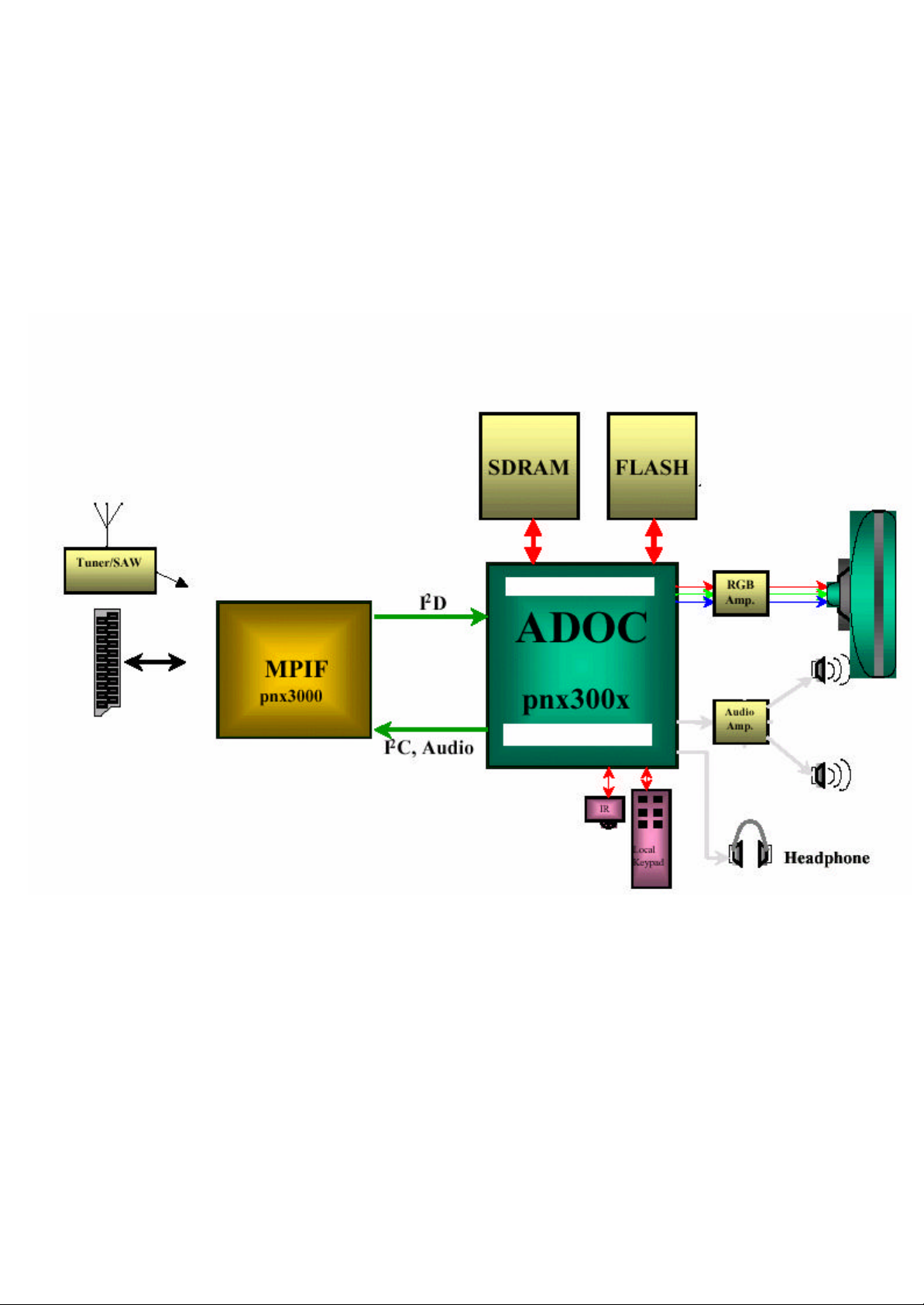

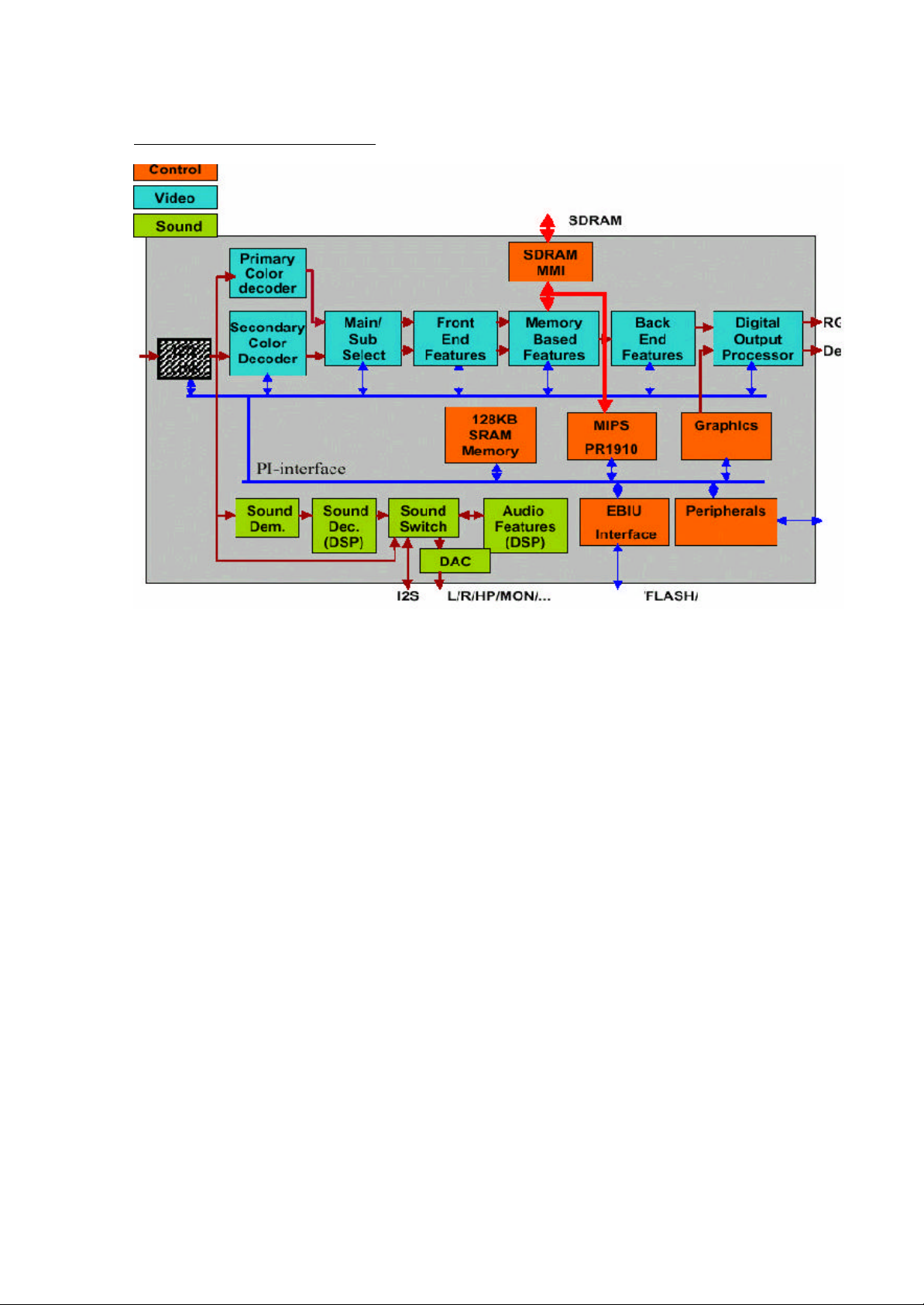

Overall Block Diagram

11AK18 - 100Hz

SCHEMATIC DIAGRAM

TABLE OF CONTENTS

1.INTRODUCTION.......................................................................................................................... 1

2.TUNER SPECIFICATION ............................................................................................................. 1

3.IF/AUDIO&VIDEO SWITCHING/AD CONVERTER PART .............................................................. 2

(PNX3000 (CALLED AS MPIF)) ...................................................................................................... 2

4.DIGITAL TV PROCESSOR (PNX300X (CALLED AS ADOC)) ........................................................ 3

5.SOUND OUTPUT STAGE WITH TDA7480L ................................................................................. 4

6.VERTICAL OUTPUT STAGE WITH STV9379FA& TDA8177F ....................................................... 4

7.VIDEO OUTPUT AMPLIFIER TDA6108JF .................................................................................... 4

8.POWER SUPPLY PART.............................................................................................................. 4

9.SERIAL ACCESS 64K EEPROM .................................................................................................. 5

10.HEADPHONE AMPLIFIER STAGE............................................................................................. 5

11.SAW FILTER SPECIFICATION.................................................................................................. 6

12.IC DESCRIPTIONS .................................................................................................................... 6

12.1.TDA6108JF (IC900) ............................................................................................................. 7

12.1.1.General Description ....................................................................................................... 7

12.1.2.Features........................................................................................................................ 7

12.1.3.Pinning.......................................................................................................................... 7

12.2.HT48RA0A .......................................................................................................................... 8

12.2.1.General Description ....................................................................................................... 8

12.2.2.Features........................................................................................................................ 8

12.2.3.Pin Descriptions............................................................................................................. 8

12.3.PNX3000 (IC400)................................................................................................................. 9

12.3.1.General Description ....................................................................................................... 9

12.3.2.Features........................................................................................................................ 9

12.4.CS51033 (IC 104) ...............................................................................................................13

12.4.1.General Description ......................................................................................................13

12.4.2.Features.......................................................................................................................13

12.4.3.Pin Description .............................................................................................................13

12.5.SDRAM 64MBIT (IC315).....................................................................................................14

12.5.1.General Description ......................................................................................................14

12.5.2.Features.......................................................................................................................14

12.5.3.Pin Description .............................................................................................................14

12.6.FLASH (IC 314) ..................................................................................................................15

12.6.1.General Description ......................................................................................................15

12.6.2.Features .......................................................................................................................15

12.6.3.Pin/Ball Descriptions .....................................................................................................16

12.7.NE56610-29 (RESET IC) (IC 316) ........................................................................................18

12.7.1.General Description ......................................................................................................18

12.7.2.Features.......................................................................................................................18

12.7.3.Pin Description .............................................................................................................18

12.8.STS5PF30L (IC105)............................................................................................................19

12.8.1.Description...................................................................................................................19

12.8.2.Features.......................................................................................................................19

12.9.PNX300X (IC313) ................................................................................................................20

12.9.1.General Description of the Digital One Chip System ........................................................20

12.9.2.Features of the ADOC Processor ...................................................................................21

12.10.M24C64WBN6 (IC309)......................................................................................................26

12.10.1.Features .....................................................................................................................26

12.10.2.Description .................................................................................................................26

12.11.TDA7480L (IC401,IC402)..................................................................................................27

12.11.1.Description .................................................................................................................27

12.11.2.Features .....................................................................................................................27

12.11.3.Pin Functions ..............................................................................................................27

12.12.LM7808 (IC803) ................................................................................................................27

12.12.1.Description .................................................................................................................27

12.12.2.Features .....................................................................................................................27

12.13.TDA8177F & STV9379FA (IC100) .....................................................................................28

i

AK53 D.O.C. Service Manual 22/03/2004

12.13.1.Description .................................................................................................................28

12.13.2.Features .....................................................................................................................28

12.13.3.Pin connections ...........................................................................................................28

12.13.4.Block Diagram ............................................................................................................28

12.14.TCET1102G (IC801) ..........................................................................................................29

12.14.1.Description .................................................................................................................29

12.14.2.Applications ................................................................................................................29

12.14.3.Features .....................................................................................................................29

12.15.MC44608 (IC804)..............................................................................................................30

12.15.1.Description .................................................................................................................30

12.15.2.General Features ........................................................................................................30

12.15.3.Pin Connections..........................................................................................................30

12.16.TL431 (Q816) ...................................................................................................................32

12.16.1.Description .................................................................................................................32

12.16.2.Features .....................................................................................................................32

12.16.3.Pin Configurations.......................................................................................................32

12.17.TFMS5360........................................................................................................................32

12.17.1.Description .................................................................................................................32

12.17.2.Features .....................................................................................................................32

13.AK53 CHASSIS MANUAL ADJUSTMENTS PROCEDURE ........................................................33

13.1.PRELIMINARY...................................................................................................................33

13.2.SYSTEM VOLTAGE ADJUSTMENTS..................................................................................33

13.3.AFC ADJUSTMENTS .........................................................................................................33

13.4.FOCUS ADJUSTMENTS .....................................................................................................33

13.5.SCREEN ADJUSTMENT (VG2 ALIGNMENT) ......................................................................33

13.6.AGC (AUTOMATIC GAIN CONTROL) .................................................................................33

14.AK53 CHASSIS PRODUCTION SERVICE MODE ADJUSTMENTS ............................................34

14.1.OPTIONS ...........................................................................................................................34

14.2.GEOMETRY.......................................................................................................................36

14.2.1.EW ALIGNMENT ..........................................................................................................36

14.3.VIDEO ALIGNMENTS .........................................................................................................44

14.3.1.VIDEO ADJUST............................................................................................................44

14.3.1.1.WHITE DRIVE........................................................................................................45

14.3.1.2.MIN BRIGHTNESS .................................................................................................45

14.3.1.3.MIN CONTRAST ....................................................................................................45

14.3.2.COLOR ADJUSTMENT.................................................................................................46

14.3.2.1.Y DEL SEC BG, Y DEL SEC DK, Y DEL SEC L, Y DEL SEC AV :.............................46

14.3.2.2.Y DEL PAL BG, Y DEL PAL DK, Y DEL PAL I, Y DEL PAL M, Y DEL PAL AV: .......46

14.3.2.3.VIDDEC QTHR, VIDDEC STHR ..............................................................................46

14.4.SOUND RELATED OPTIONS..............................................................................................47

14.5.FACTORY SETTINGS ........................................................................................................48

15.MENU LANGUAGES ................................................................................................................49

16.BLOCK DIAGRAM....................................................................................................................50

17.CIRCUIT DIAGRAMS ................................................................................................................51

ii

AK53 D.O.C. Service Manual 22/03/2004

1.INTRODUCTION

11AK53 is a 100Hz color television DIGITAL ONE CHIP SYSTEM (DOC) capable of driving 28”4:3/16:9

SF/RF, 29”4:3 real flat, 32” 16:9 SF/RF, 33”4:3 and 34‘ 4:3 real flat picture tubes.

The chassis is capable of operation in PAL, SECAM, NTSC (playback) color standards and multiple

transmission standards as B/G, D/K, I/I’, and L/L´.

Sound system output is supplying 2x10W (10%THD) for left and right outputs of 8ohm speakers.

TV supports the level 1.5 teletext standard. It is possible to decode transmissions including high

graphical data.

The chassis is equipped with two full EuroScarts, one SCART for AV input/output, one front -AV input,

one back-AV input, one headphone output, one SVHS input (via SCART and SVHS connector), two

external speaker outputs (left and right), one audio line output.

2.TUNER SPECIFICATION

The hardware and software of the TV is suitable for tuners, supplied by different compani es, which are

selected from the Service Menu. These tuners can be combined VHF, UHF tuners suitable for CCIR

systems B/G, H, L, L´, I/I´, and D/K. The tuning is available through the digitally controlled I2C bus

(PLL). Below you will find info on one of the Tuners in use.

General description of UV1316 MK3(Philips) /CTF55XX (Thomson):

UV1316 MK3 (Philips) /CTF55XX (Thomson) tuners, which are designed to meet a wide range of

applications are PLL tuners; It is a combined VHF, UHF tuner suitable for CCIR systems B/G, H, L, L’, I

and I’. The low IF output impedance has been designed for direct drive of a wide variety of SAW filters

with sufficient suppression of triple transient.

Features of Tuner:

1. Those tuners are small sized UHF/VHF tuners

2. Systems CCIR: B/G, H, L, L’, I and I’; OIRT: D/K

3. Digitally controlled (PLL) tuning via I2C-bus

4. Off-air channels, S-cable channels and Hyperband

5. World standardized mechanical dimensions and world standard pinning

6. Compact size

7. Complies to “CENELEC EN55020” and “EN55013”

Pinning:

1. Gain control voltage (AGC) : 4.0V, Max: 4.5V

2. Tuning voltage

3. I²C-bus address select : Max: 5.5V

4. I²C-bus serial clock : Min:-0.3V, Max: 5.5V

5. I²C-bus serial data : Min:-0.3V, Max: 5.5V

6. Not connected

7. PLL supply voltage : 5.0V, Min: 4.75V, Max: 5.5V

8. ADC input

9. Tuner supply voltage* : 33V, Min: 30V, Max: 35V

10. Symmetrical IF output 1

11. Symmetrical IF output 2

*33V is obtained from FBT of large signal board.

1

AK53 D.O.C. Service Manual 22/03/2004

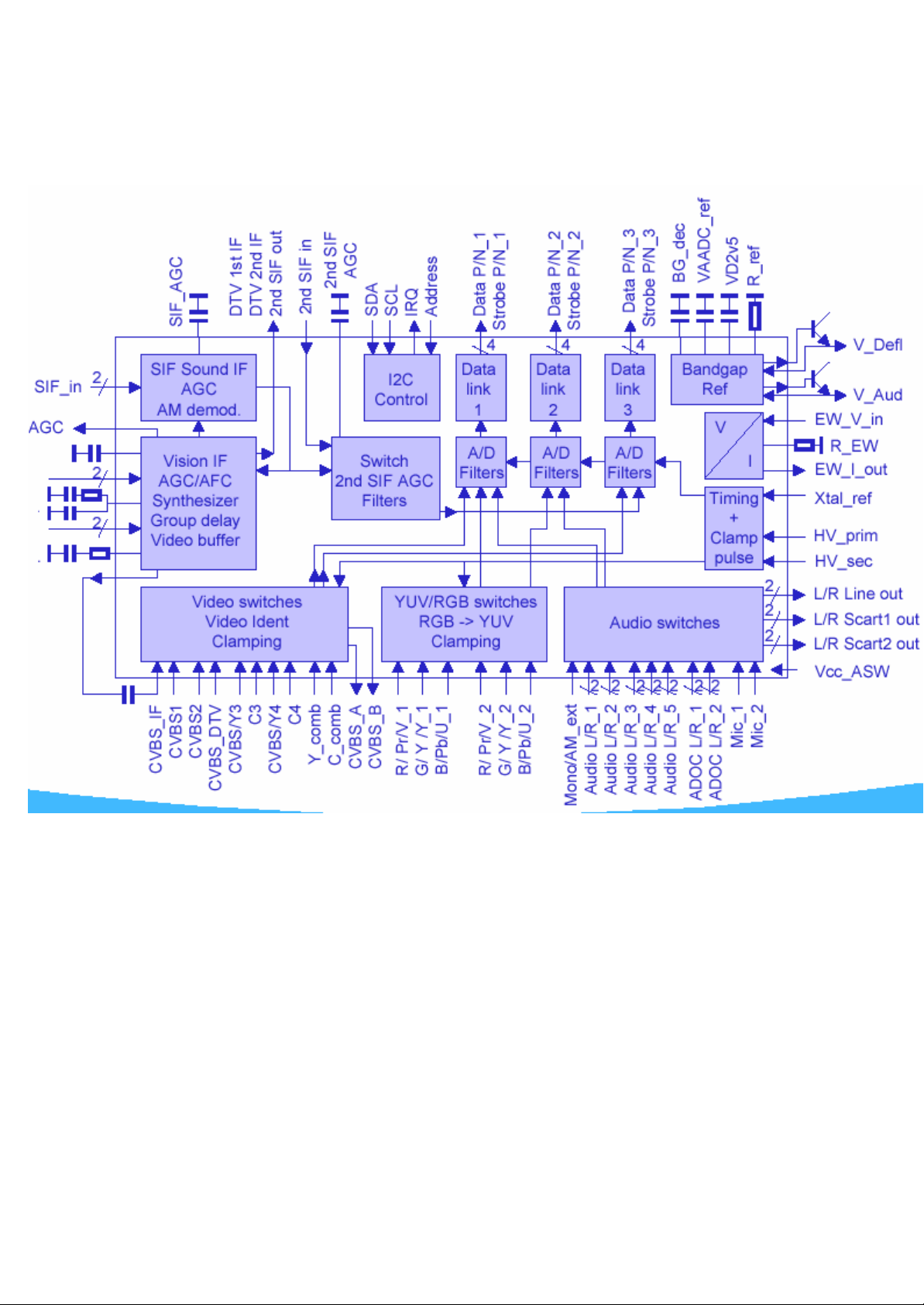

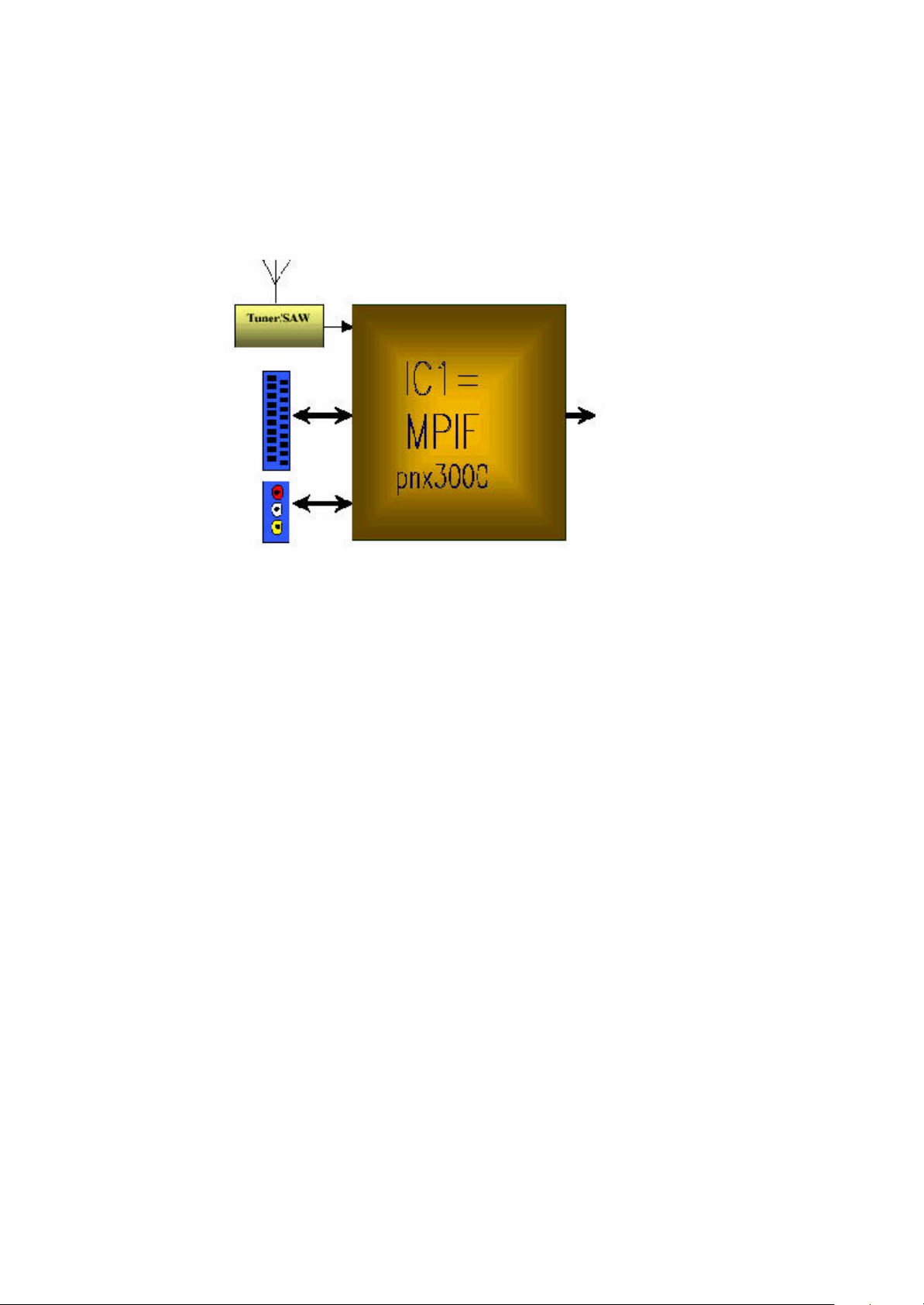

3.IF/AUDIO&VIDEO SWITCHING/AD CONVERTER PART

(PNX3000 (CALLED AS MPIF))

MPIF IC consists of following OVERALL blocks;

(1)-Video/Audio switching

(2)-IF processing

(3)-A/D conversion for digital TV (DTV) processor (ADOC-PNX300X)

Main building blocks:

_ Vision PLL-IF, auto-calibrated, selectable IF frequency, 4 selectable AGC time constants, built-in

sound trap and selectable group delay. The demodulated CVBS signal is fed outside for use with

SCART.

_ Synthesizer mode, meant for down mixing of DTV signals to a suitable 2nd IF which can be handled

by a digital DTV decoder. Using a suitable SAW filter at the input the synthesizer mode can also be

used to downmix FM radio frequencies from the Tuner to a suitable 2nd IF frequency for the FM

demodulator.

_ Two Video IF inputs, selectable by internal switch to ena ble use of optimized SAW filters

_ Sound QSS IF, demodulated 2nd SIF can be either from SIF input (QSS) or Video IF (intercarrier).

The Sound IF also contains an AM demodulator for SECAM L/L'

_ CVBS and Y/C crossbar switch, with 2 video outputs for furthe r processing in the Digital TV Signal

Processor after A/D conversion and 2 selectable video outputs which are available on output pins for

external connections

2

AK53 D.O.C. Service Manual 22/03/2004

_ Two YUV / RGB inputs, which can handle also YPrPb and sync on Y for DVD players Also 2Fh YUV /

RGB signals can be handled by the A/D converters.

_ An audio stereo crossbar switch with two outputs (one stereo, one stereo or mono) for further

processing in the processor after A/D conversion and three stereo outputs for external connections.

Extra inp uts are provided to enable also the selection of demodulated RF sound (mono, NICAM, 2CS)

from the Digital TV Signal Processor for use on external connections.

_ Low pass filtering and A/D conversion. The audio and video sampling clocks use the same reference

so it is possible to interleave video and audio data into one serial data stream.

_ For control, I 2 C control is built-in with a selectable address.

_ Auxiliary building blocks which perform some functions which have typical better performance in

analogue design environment than in digital and are used by the Digital TV Signal Processor:

- Reference voltage for vertical deflection and audio ADC's

- Voltage to current conversion of the E/W

The set -up with an analogue and a digital part has the following advantages:

_ High frequent parts (IF) can be included in the concept

_ Less A/D and D/A converters needed for source switching

_ Better performance for AD converters (realized in analogue design environment, more accurate, less

tolerance)

_ Critical items like reference voltages can be realized in the analogue environment

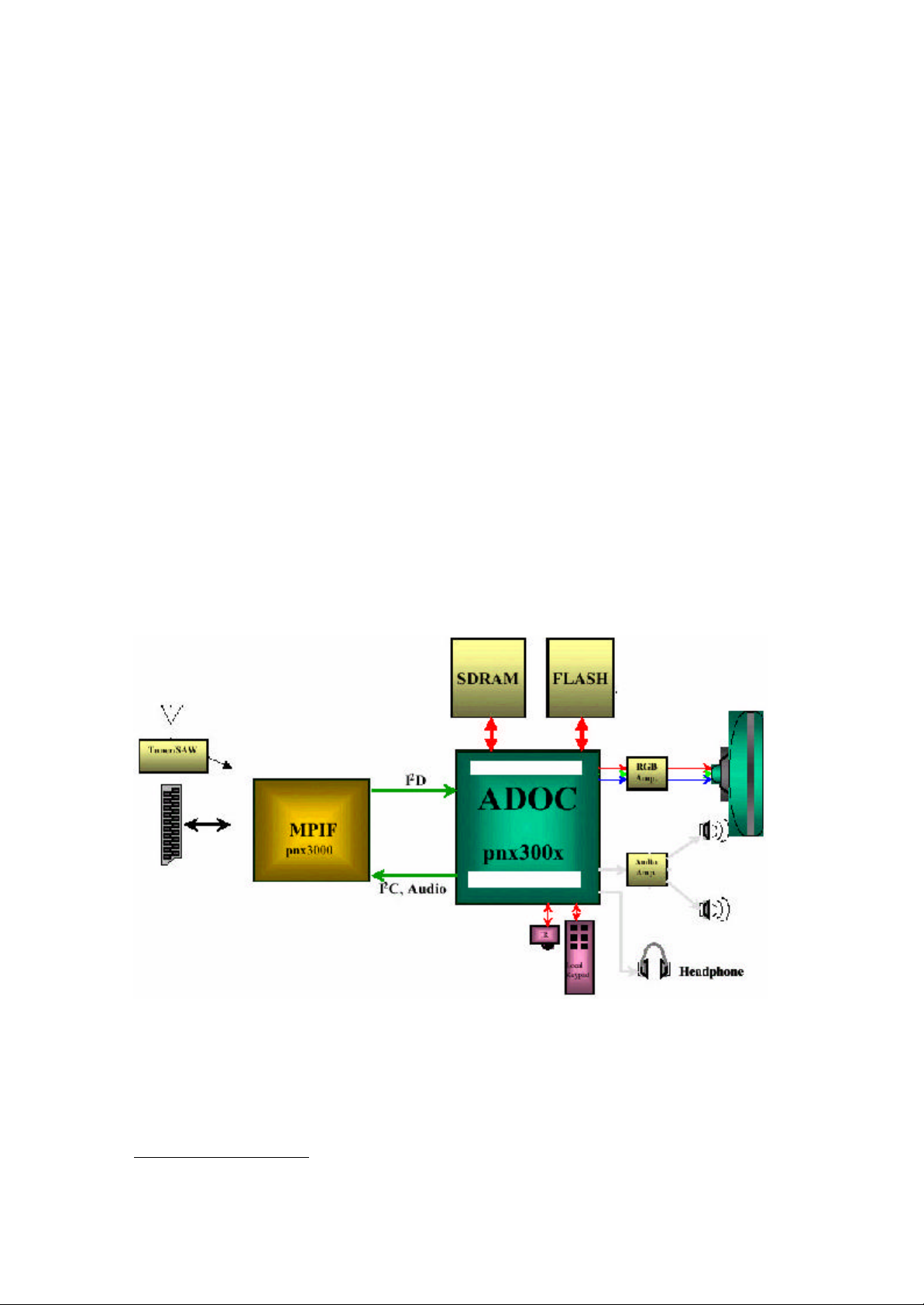

4.DIGITAL TV PROCESSOR (PNX300X (CALLED AS ADOC))

The DOC system serves the TV functionality for small signal processing of audio, video, VBI services,

graphics and control. This chip implements all TV functions in digital technology. PNX300X is the digital

TV processor which consists of;

? TV video processor

? TV deflection processor

? TV audio processor

? TV microcontroller

As it is shown in the below block diagram ADOC gets the digital signal which is converted by MPIF and

processed in its own blocks and controls the overall system by I2C and the software programme is

downloaded into a flash memory which tells microcontroller within ADOC about the software

management and the output of ADOC turns into RGB, Main/Headphone audio right/left.

Then RGB output of ADOC is processed into a RGB preamplifier circuit to get enough gain for the video

output amplifier TDA6108JF (in CRT board)

Highlight points of ADOC:

(1)-Digital (I2D) data link is connected from MPIF to ADOC with a swing of about 300mV. The data rate

is 594Mbit/s.

(2)-Only one crystal is used in overall system which is 13.5MHZ.

3

AK53 D.O.C. Service Manual 22/03/2004

Functional block diagram of ADOC:

5.SOUND OUTPUT STAGE WITH TDA7480L

The TDA7480L is an audio class-D amplifier assembled in Power DIP package specially designed for

high efficiency applications mainly for TV and Home Stereo sets.

Mute stand-by function of the audio amplifier can be described as the following; the pin 12

(MUTE/STAND-BY) controls the amplifie r status by two different thresholds, referred to ground. When

Vpin 12 voltage is lower than 0.7V the amplifier is in Stand-by mode and the final stage generators are

off. When Vpin 12 is higher than 4V, the amplifier is in play mode.

The TDA7480L is a 10W+10W stereo sound amplifier with mute/stand -by facility. MUTE control signal

coming from microcontroller (when it is at high level) activates the mute function. IC is muted when

mute pin is at low level (pin12). MUTE pin can also be activated via an external pop-noise circuitry in

order to eliminate pop noise when TV is turned off. Just after the TV is turned off, this circuit switches

the IC to stand-by mode by pulling the mute pin voltage to ground.

6.VERTICAL OUTPUT STAGE WITH STV9379FA& TDA8177F

The IC STV9379FA& TDA8177F is the vertical deflection booster circuit. Two supply voltages, +14V

and –14V are needed to scan the inputs VERT+ and VERT-, respectively. And a third supply voltage,

+60V for the flyback limiting is needed. The vertical deflection coil is connected in series between the

output and feedback to the input.

7.VIDEO OUTPUT AMPLIFIER TDA6108JF

The TDA6108JF includes three video output amplifiers is intended to drive the three cathodes of a color

picture tube.

8.POWER SUPPLY PART

In Large Signal Board

The DC voltages required at various parts of the chassis are provided by an SMPS transformer

controlled by the IC MC44608, which is designed for driving, controlling and protecting switching

transistor of SMPS. The transformer generates 135V for FBT input, +/-14V for audio amplifier, 8V, 12V,

V8Stby ( needed for step down converted for small signal board) and 5V supplies for other different

parts of the chassis.

4

AK53 D.O.C. Service Manual 22/03/2004

An optocoupler is used to control the regulation of line voltage and stand-by power consumption. There

is a regulation circuit in secondary side. This circuit produces a control voltage according to the

changes in 135V DC voltage, via an optocoupler (TCET 1102G) to pin3 of the IC.

During the switch on period of the transistor, energy is stored in the transformer. During the switch off

period energy is fed to the load via secondary winding. By varying switch-on time of the power

transistor, it controls each portion of energy transferred to the second side such that the output voltage

remains nearly independent of load variations.

In Small Signal Board

V8Stby and +5V is switched by a discrete circuit to make power consumption effective.

? When supply switch port of ADOC IC is HIGH +5V ? 3.3V via IC103 regulator

? When supply switch port of A DOC IC is LOW V8Stby ? 3.3V via IC103 regulator

V8Stby is used to get +5V, which is available in Stby.

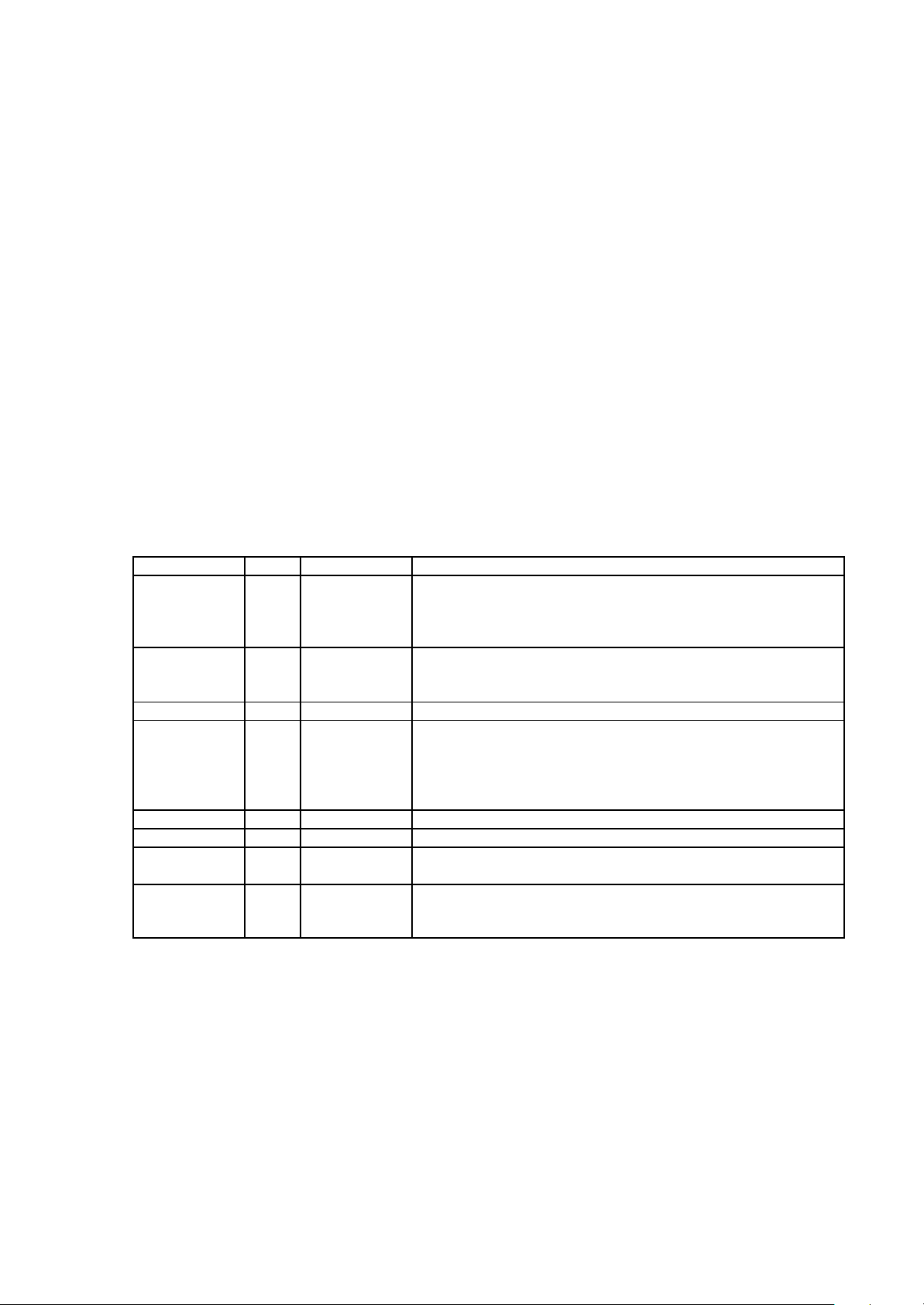

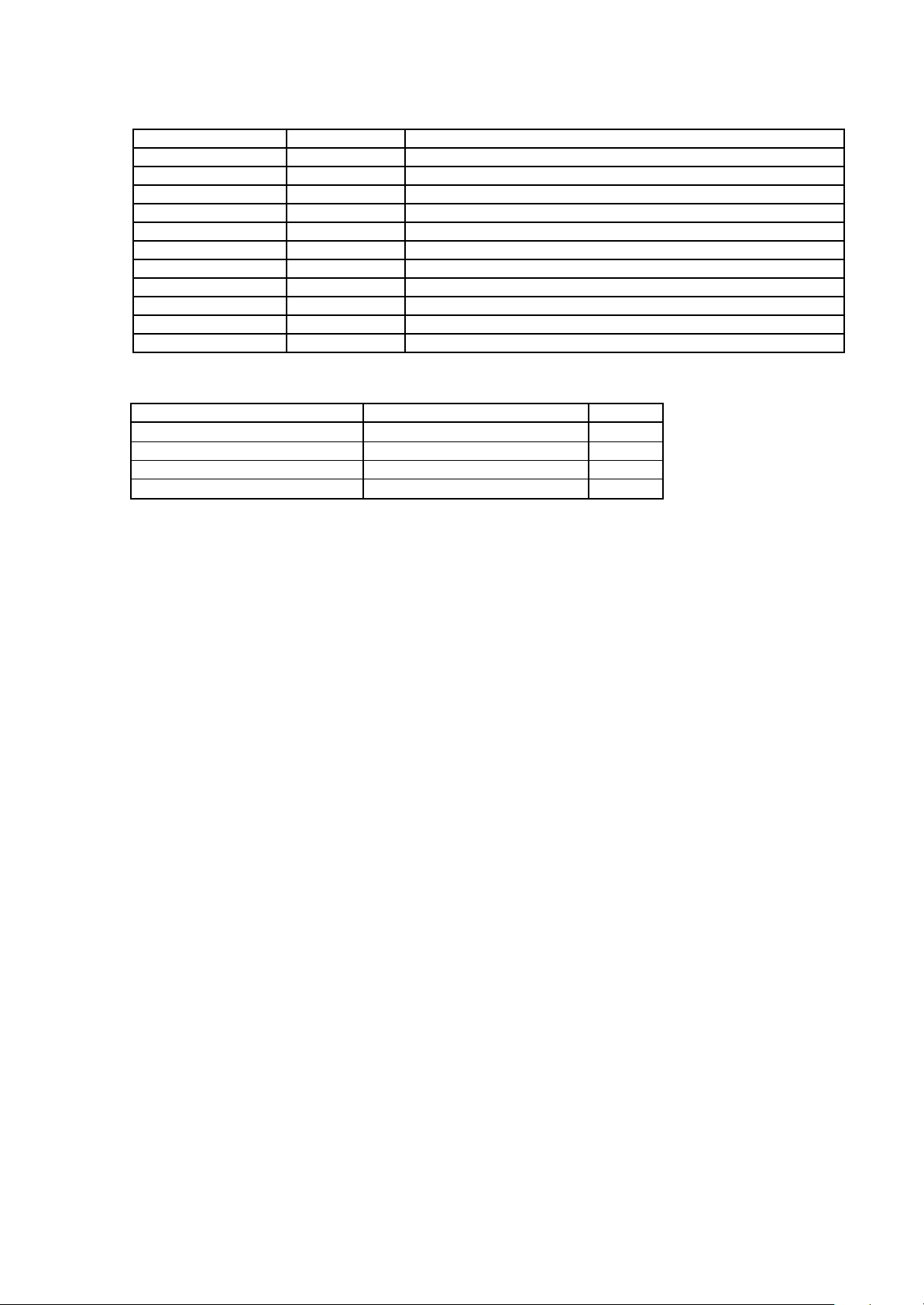

Supply Voltages Available/Not-Available In Stand-by, IC Requirement, Supply Location

Supply In Stby available? Where? For Which ? NOTE

135V (B+) NO large signal board FBT depends on

CRT

14V-A NO large signal board IC401,IC402(Audio

amplifier)

(-)14V-A NO large signal board IC401,IC402(Audio

amplifier)

14V NO large signal board Horizontal drive transistor

8V NO small signal board

5V NO small signal board

V8stby YES large signal board Step down IC and for s+5V

1.8V YES small signal board IC313 (ADOC)

3.3V YES small signal board

12V NO small signal board CRT board (IC900)

5V YES small signal board LED/IR

Vert Sup+ (14V) NO large signal board Vertical IC (IC100)

Vert Sup- (14V)

33V NO large signal board Tuner (TU200,TU850)

Important Microcontroller Ports For Supplying

Port State Function

On/Off low normal operation

On/Off high stand by mode

NO large signal board Vertical IC (IC100)

IC400 (MPIF)/Headphone discrete

circuit/RGB pre amplifiers/audio saw

filter(Z401)

IC400 (MPIF),Tuner(TU200,TU850)

IC313

(ADOC),IC309(EEPROM),IC316(Reset IC)

9.SERIAL ACCESS 64K EEPROM

M24C64WBN6, is the 64Kbit electrically erasable programmable memo ry. The memory is compatible

with the I2C standard, two wire serial interface, which uses a bi-directional data bus and serial clock.

10.HEADPHONE AMPLIFIER STAGE

This stage is designed with discrete components (no IC is used for this purpose)

5

AK53 D.O.C. Service Manual 22/03/2004

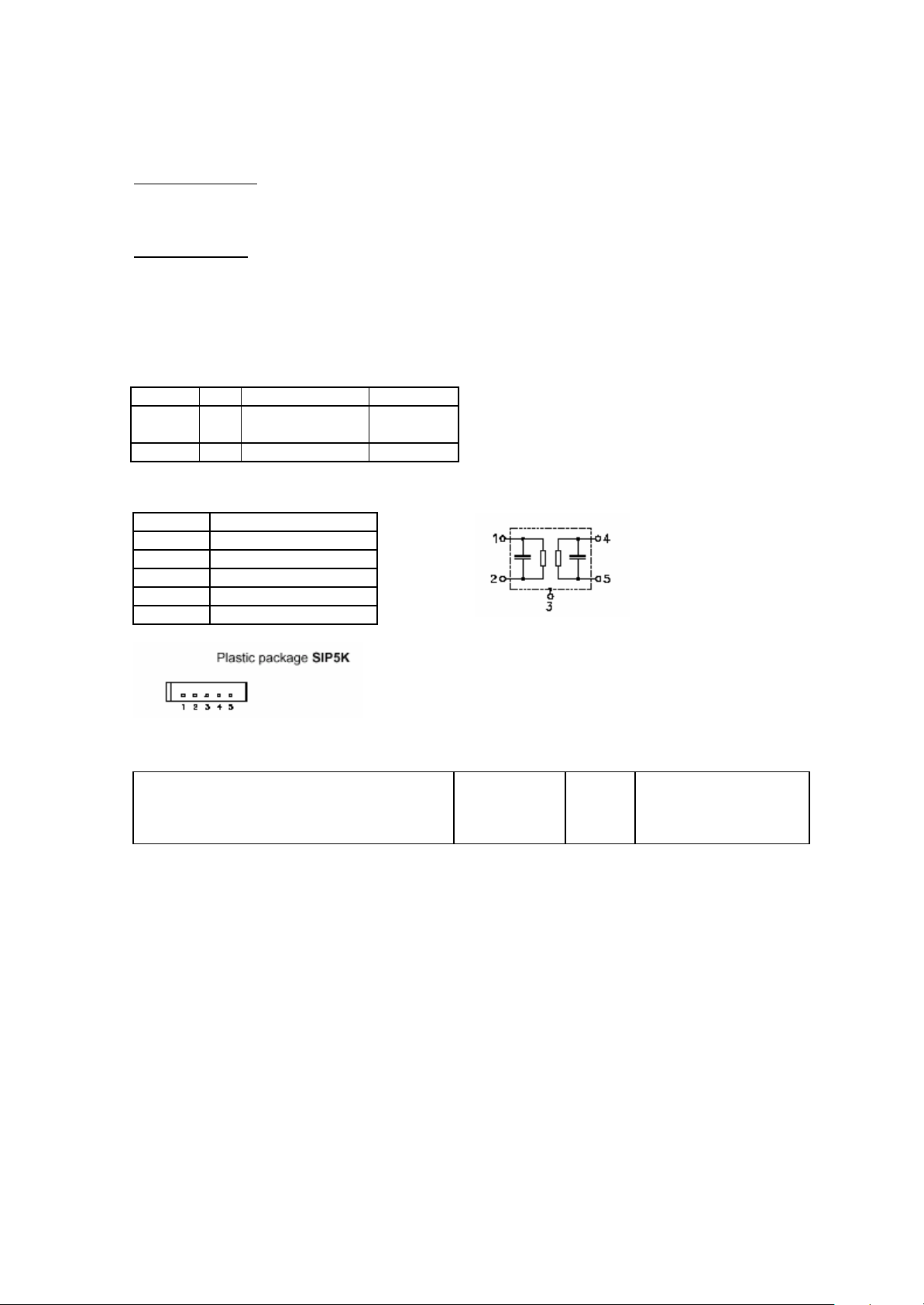

11.SAW FILTER SPECIFICATION

Two groups of saw filters are used from EPCOS

For picture (Z400)

? Pal Secam BG DK L L’?K3953M

? Pal Secam BG I I’ ?K3953M

For sound(Z401)

? Pal Secam BG DK L L’?K9656M

? Pal Secam BG I I’ ?K9356

For sound saw filter it needs to be switched between L’ and other standards for K3953M, a port signal

coming from PNX300X(ADOC) called SEL_L/L’ is used for this purpose to make pin2 of audio saw filter

ground or not.

port state Q404 Standard

SEL_L/L' High Shorted to

ground

SEL_L/L' Low open BG,DK,I,L

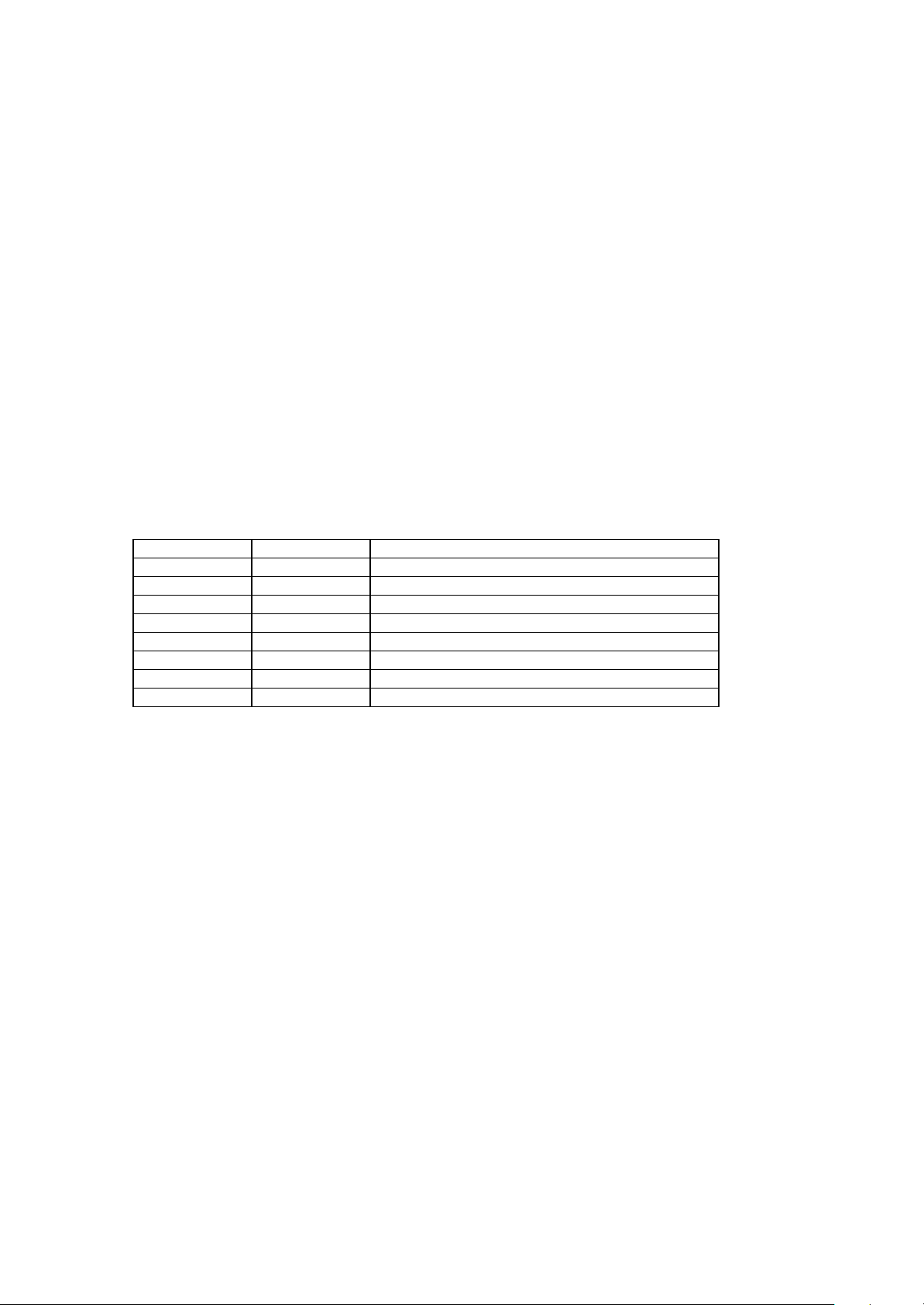

Pin Configuration

Pin No Definition

1 Input

2

3

4

5

Input - ground

Chip carrier - ground

Output

Output

L'

Maximum ratings for saw filters

Operable temperature range TA

Storage temperature range T

DC voltage VDC

AC vo ltage Vpp

–25/+65 °C

stg

12.IC DESCRIPTIONS

In following chapters you can find details of ICs used in the chassis and the SS B(Small signal board)

TDA6108JF HT48RA0A

PNX3000 CS51033

SDRAM 64MBIT FLASH 32 MBIT

NE56610-29 STS5PF30L

PNX300X M24C64WBN6

TDA7480L LM7808

TDA8177&STV9379FA TCET1102G

MC44608 TL431

TFMS5360

6

AK53 D.O.C. Service Manual 22/03/2004

12.1.TDA6108JF (IC900)

12.1.1.General Description

The TDA6108JF includes three video output amplifiers in one plastic DIL-bent-SIL 9-pin medium power

(DBS9MPF) package (SOT111-1), using high-voltage DMOS technology, and is intended to drive the three

cathodes of a color CRT directly. To obtain maximum performance, the amplifier should be used with blackcurrent control.

12.1.2.Features

• Typical bandwidth of 9.0 MHz for an output signal of 60 V (p-p)

• High slew rate of 1850 V/ms

• No external components required

• Very simple application

• Single supply voltage of 200 V

• Internal reference voltage of 2.5 V

• Fixed gain of 51

• Black-Current Stabilization (BCS) circuit

• Thermal protection

12.1.3.Pinning

SYMBOL PIN DESCRIPTION

V

1 inverting input 1

i(1)

V

2 inverting input 2

i(2)

V

3 inverting input 3

i(3)

GND 4 ground (fin)

Iom 5 black current measurement output

VDD 6 supply voltage

V

7 cathode output 3

oc(3)

V

8 cathode output 2

oc(2)

V

9 cathode output 1

oc(1)

7

AK53 D.O.C. Service Manual 22/03/2004

12.2.HT48RA0A

12.2.1.General Description

The HT48RA0A is an 8-bit high performance RISC-like microcontroller specifically designed for multiple

I/O product applications. The device is particularly suitable for use in products such as infrared remote

controllers and various subsystem controllers. A HALT feature is included to reduce power

consumption.

12.2.2.Features

• Operating voltage: 2.2V~3.6V

• Ten bidirectional I/O lines

• Six Schmitt trigger input lines

• One carrier output (1/2 or 1/3 duty)

• On-chip crystal and RC oscillator

• Watchdog Timer

• 1K_14 program EPROM

• 32_8 data RAM

• HALT function and wake-up feature reduce power consumption

• 62 powerful instructions

• Up to 1_s instruction cycle with 4MHz system clock

• All instructions in 1 or 2 machine cycles

• 14-bit table read instructions

• One-level subroutine nesting

• Bit manipulation instructions

• 20-pin/24-pin SOP package

12.2.3.Pin Descriptions

Pin Name I/O Code Option Description

PB0, PB1 I/O Wake-up

or None

PC0/REM O Level or

Carrier

VDD - - Positive power supply

OSC2

OSC1

VSS - - Negative power supply, ground

RES I - Schmitt trigger reset input. Active low.

PB2~PB7 I Wake-up

PA0~PA7 I/O - Bidirectional 8-bit input/output port with pull -high resistors.

I/O Crystal

or RC

or None

2-bit bidirectional input/output lines with pull -high resistors.

Each bit can be determined as NMOS output or Schmitt

trigger input by software instructions. Each bit can also be

configured as wake-up input by code option.

Level or carrier output pin

PC0 can be set as CMOS output pin or carrier output pin by

code option.

OSC1, OSC2 are connected to an RC network or a crystal

(determined by code option) for the internal system clock. In

the case of RC operation, OSC2 is the output terminal for

1/4 system clock

(NMOS open drain output).

6-bit Schmitt trigger input lines with pull-high resistors. Each

bit can be configured as a wake-up input by code option.

Each bit can be determined as NMOS output or Schmitt

trigger input by software instructions.

8

AK53 D.O.C. Service Manual 22/03/2004

12.3.PNX3000 (IC400)

12.3.1.General Description

The PNX3000 is an analog front end for digital video processors. It contains an IF circuit for both analog

and digital broadcast signals, and input selectors and A to D converters for analog video and audio

signals. The digital output signals are made available via three serial data links.

The IC has a supply voltage of 5V. The supply voltage of the analog audio part can be 5V or 8V,

depending on the maximum signal amplitudes that are required.

12.3.2.Features

• Multi-standard vision IF circuit with alignment -free PLL demodulator without external components

• Internal (switchable) time-constant for the IF-AGC circuit

• DTV IF circuit for gain control of digital broadcast TV signals.

• Sound IF amplifier with separate AGC circuit for quasi split sound

• IF circuit can also be used for intercarrier sound

• Analog demodulator for AM sound

• Integrated sound trap and group delay correction

• Video ident function detects the presence of a video signal

• Video source selector with 4 external CVBS or YC inputs and 2 analog CVBS outputs with

independent source selection for each output

• Two linear inputs for 1fH or 2fH RGB signals with source selector. The RGB signals are converted to

YUV before A to D conversion. Both inputs can also be used as YPB PR input for DVD or set top box

• Integrated anti-alias filters for video A to D converters

• Four 10-bit video A to D converters for the conversion of CVBS, YC, YUV and down mixed sound IF

signals

• Up to three different A to D converted video channels are simultaneous available (e.g. CVBS and YC

and YUV)

• Audio source selector with 5 stereo inputs for analog audio and two microphone inputs

• Two microphone amplifiers with adjustable gain

• Three analog audio outputs for SCART and Line out with independent source selection for each

output

• Four 1-bit audio sigma delta A to D converters for the conversion of audio and microphone signals

• Three serial data link transmitters for interfacing with the digital video processor. The bit rate is 594

Mbits/sec per data link

• Voltage to current converter for driving of external East-West power amplifier

• I2C-bus transceiver with selectable slave address and maskable interrupt output

9

AK53 D.O.C. Service Manual 22/03/2004

SYMBOL PIN DESCRIPTION

CVBS2 1 CVBS2 input

VAUDO 2 DC output voltage for supply of audio DACs in digital decoder

VAUDS 3 sense voltage for audio DACs supply

CVBS/Y3 4 external CVBS/Y3 input

C3 5 external CHROMA3 input

GND_VSW 6 ground video switch

BGDEC 7 bandgap decoupling

CVBS/Y4 8 external CVBS/Y3 input

C4 9 external CHROMA3 input

fuse

GND_FILT

CVBS_DTV

RREF

VCC_FILT

YCOMB

CCOMB 16 C signal from 3D Comb filter

AMEXT

TESTPIN3

CVBSOUTA

VDEFLO

VDEFLS

CVBSOUTB

fuse

TESTPIN2

R1/PR1 /V1 25 R1/PR1 /V1 input

G1/Y1/Y1 26 G1/Y1/Y1 input

B1/PB1 /U1 27 B1/PB1 /U1 input

VCC_RGB 28 supply voltage RGB matrix (5V)

GND_RGB

R2/PR2 /V2

G2/Y2/Y2

B2/PB2 /U2

fuse

GND_VADC

VCC_VADC

EWVIN

EWIOUT

REW

ADR

XREF

fuse

IRQ

SDA

SCL

HV_SEC

HV_PRIM

VD2V5

GND_DIG

VCC_DIG

STROBE3N

STROBE3P

DATA3N

DATA3P

fuse

STROBE2N 55 strobex negative datalink2

STROBE2P 56 strobex positive datalink2

DATA2N 57 data positive datalink2

10

11

12

13

14

15

17

18

19

20

21

22

23

24

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

fused lead

ground filters

input for CVBS encoded signal from DTV decoder

reference current input

supply voltage filters (5V)

Y signal from 3D Comb filter

external AM mono input

test pin 3 (leave open)

CVBS or Y+CHROMA output A

DC output voltage for supply of deflection DACs in digital decoder

sense voltage for deflection DACs supply

CVBS or Y+CHROMA output B

fused lead

test pin 2 (connect to ground)

ground RGB matrix

R2/PR2 /V2 input

G2/Y2/Y2 input

B2/PB2 /U2 input

fused lead

ground video ADCs

supply voltage video ADCs (5V)

East-West input voltage

East-West output current

East-West voltage to current conversion resistor

I2C address selection

XTAL reference frequency input

fused lead

interrupt request output

I2C serial data input/output

I2C serial clock input

horizontal and vertical sync input for secondary video channel

horizontal and vertical sync input for primary video channel

decoupling of internal digital supply voltage

digital ground

digital supply voltage (5V)

strobex negative datalink3

strobex positive datalink3

data positive datalink3

data positive datalink3

fused lead

10

AK53 D.O.C. Service Manual 22/03/2004

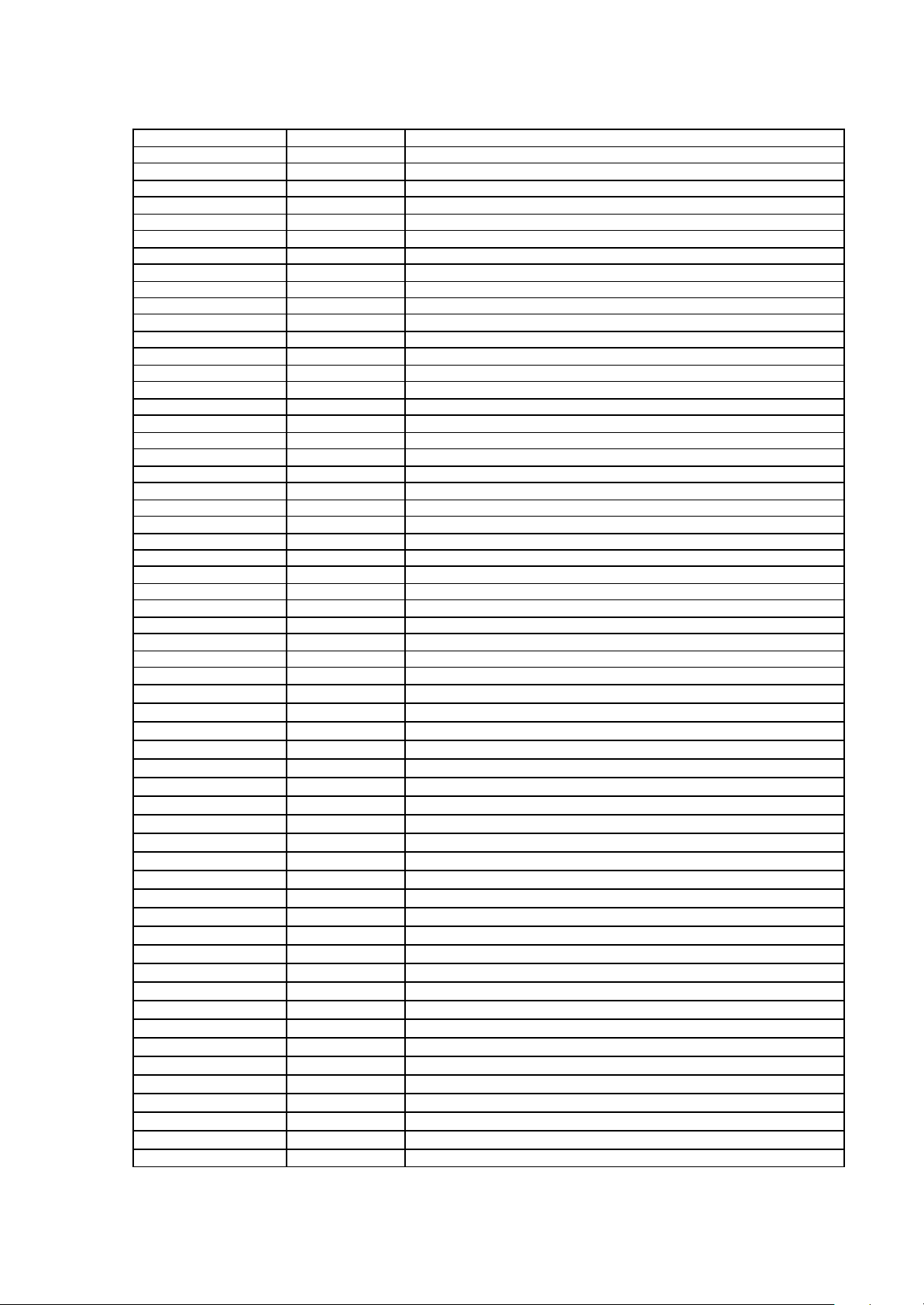

DATA2P 58 data positive datalink2

GND_I2D 59 ground datalinks

STROBE1N 60 strobex negativ e datalink1

STROBE1P 61 strobex positive datalink1

DATA1N 62 data negative datalink1

DATA1P 63 data positive datalink1

VCC_I2D 64 supply voltage datalinks (5V)

SCART2R 65 audio output for SCART 2 right

SCART2L 66 audio output for SCART 2 left

LINER 67 audio line output right

LINEL 68 audio line output left

SCART1R 69 audio output for SCART1 right

SCART1L 70 audio output for SCART1 left

fuse 71 fused lead

DSNDR2 72 audio signal from digital decoder right 2

DSNDL2 73 audio signal fro m digital decoder left 2

DSNDR1 74 audio signal from digital decoder right 1

DSNDL1 75 audio signal from digital decoder left 1

GND_AADC 76 ground audio ADCs

VCC_AADC 77 supply voltage audio ADCs (5V)

fuse 78 fused lead

R4 79 right input audio 4

L4 80 left input audio 4

R3 81 right input audio 3

L3 82 left input audio 3

R2 83 right input audio 2

L2 84 left input audio 2

R1 85 right input audio 1

L1 86 left input audio 1

GND2_ASW 87 ground audio switch

VCC2_ASW 88 supply voltage audio switch (audio output buffers, 5V or 8V)

VAADCREF 89 decoupling of reference voltage for audio ADCs

VAADCN 90 0V reference voltage for audio ADCs (GND)

VAADCP

MIC2N

MIC2P

MIC1N

MIC1P

fuse

GND1_ASW

VCC1_ASW

SIFINP

SIFINN

SIFAGC

DTVIFAGC

DTVIFINP

DTVIFINN

TUNERAGC

fuse

VIFINP

VIFINN

DTVIFPLL

VCC_IF

VIFPLL

GND1_IF

2NDSIFEXT

2NDSIFAGC

GND2_IF

DTVOUTP

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

full scale reference voltage for audio ADCs (5V)

microphone input 2 neg

microphone input 2 pos

microphone input 1 neg

microphone input 1 pos

fused lead

ground audio switch

supply voltage audio switch (audio input buffers, 5V or 8V)

sound IF input positive

sound IF input negative

control voltage for SIF AGC

control voltage for DTV IF AGC

DTV IF input positive

DTV IF input negative

tuner AGC output

fused lead

vision IF input positive

vision IF input negative

loop filter DTVIF PLL demodulator

supply voltage IF circuit (5V)

loop filter VIF PLL demodulator

ground IF circuit

2ndSIF input

2ndSIF AGC capacitor

ground IF circuit

DTV output positive

11

AK53 D.O.C. Service Manual 22/03/2004

DTVOUTN

VCC_SUP

fuse

CVBSOUTIF

GND_SUP

VCC1_VSW

CVBS0

TESTPIN1

VCC2_VSW

CVBS1

R5

L5

117

118

119

120

121

122

123

124

125

126

127

128

DTV output negative

supply of supply circuit (5V)

fused lead

CVBS output of IF circuit

ground of supply circuit

supply of video switch (5V)

CVBS0 input (to be used for CVBS from IF part)

test pin 1 (connect to ground)

supply of video switch (5V)

CVBS1 input

right input audio 5

left input audio 5

Important pins need to be checked in case of troubleshooting

Signal Measure Value

CVBS/RGB Input voltage Input pins 1Vpk-pk

CVBS Output voltage Output pins 2 Vpk -pk

Maximum input audio voltage Input pins 2 Vrms

Maximum output audio voltage Output pins 2 Vrms

12

AK53 D.O.C. Service Manual 22/03/2004

12.4.CS51033 (IC 104)

12.4.1.General Description

The CS51033 is a switching controller for use in dc –dc converters. It can be used in the buck topology

with a minimum number of external components. The CS51033 consists of a 1.0 A power driver for

controlling the gate of a discrete P –channel transistor, fixed frequency oscillator, short circuit protection

timer, programmable Soft Start, precision reference, fast output voltage monitoring comparator, and

output stage driver logic with latch.

The high frequency oscillator allows the use of small inductors and output capacitors, minimizing PC

board area and systems cost. The programmable Soft Start reduces current surges at start up. The

short circuit protection timer significantly reduces the PFET duty cycle to approximately 1/30 of its

normal cycle during short circuit conditions.

The CS51033 is available in an 8–Lead SO package.

12.4.2.Features

• 1.0 A Totem Pole Output Driver

• High Speed Oscillator (700 kHz max)

• No Stability Compensation Required

• Lossless Short Circuit Protection

• 2.0% Precision Reference

• Programmable Soft Start

• Wide Ambient Temperature Range:

Industrial Grade: –40°C to 85°C

Commercial Grade: 0°C to 70° C

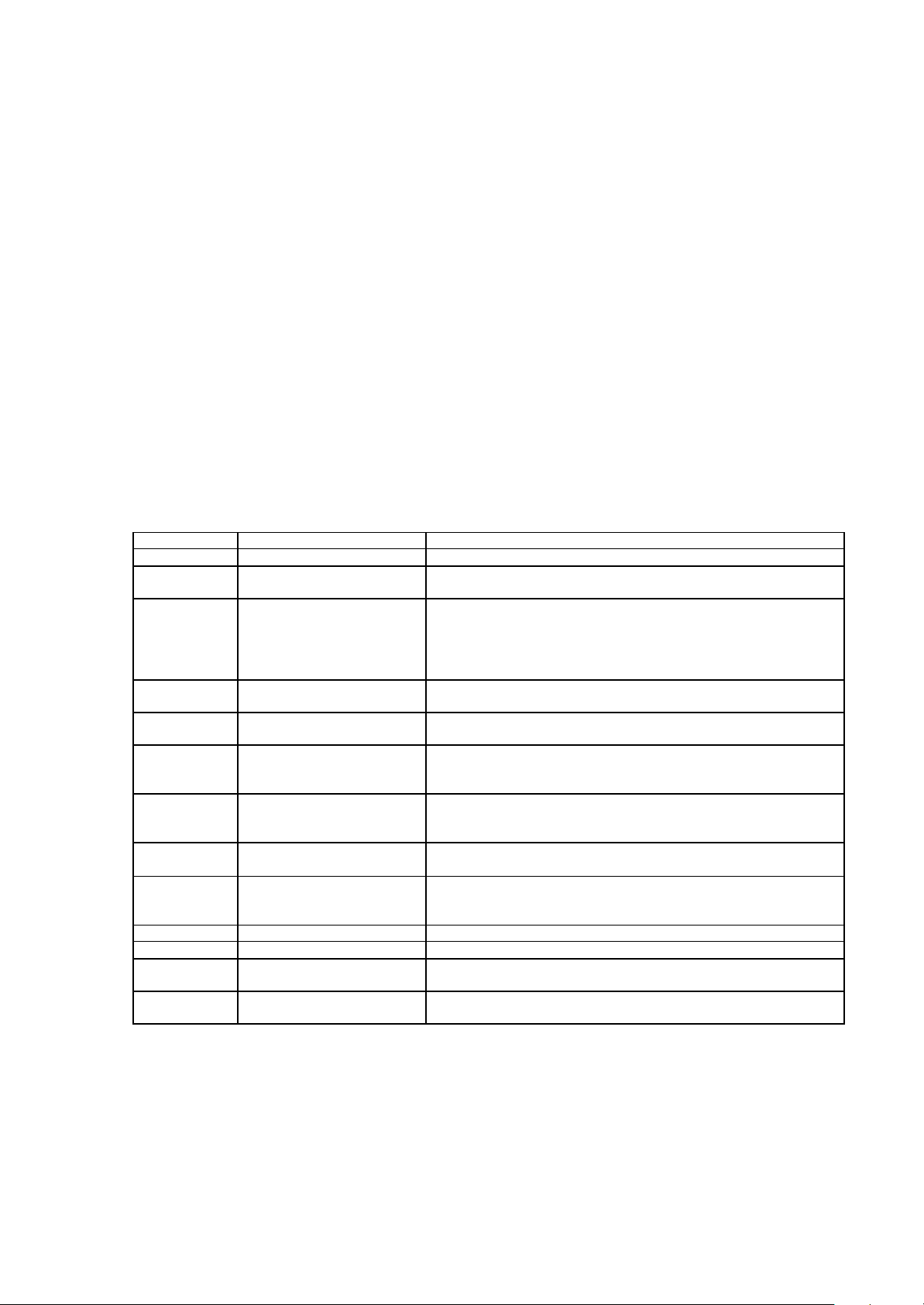

12.4.3.Pin Description

PIN NUMBER PIN SYMBOL FUNCTION

1 V

2 P

3 C

Driver pin to gate of external PFET.

GATE

Output power stage ground connection.

GND

Oscillator frequency programming capacitor.

OSC

4 GND Logic ground.

5 VFB Feedback voltage input .

6 V

Logic supply voltage.

CC

7 CS Soft Start and fault timing capacitor.

8 VC Driver supply voltage.

13

AK53 D.O.C. Service Manual 22/03/2004

12.5.SDRAM 64MBIT (IC315)

12.5.1.General Description

Please note that in the following explanation one of the SDRAM alternative is used.

The K4S641632D is 67,108,864 bits synchronous high data rate Dynamic RAM organized as 4 x

1,048,576 words by 16 bits, fabricated with SAMSUNG¢s high performance CMOS technology.

Synchronous design allows precise cycle control with the use of system clock I/O transactions are

possible on every clock cycle. Range of operating frequencies, programmable burst length and

programmable latencies allow the same device to be useful for a variety of high bandwidth, high

performance memory system applications.

12.5.2.Features

• JEDEC standard 3.3V power supply

• LVTTL compatible with multiplexed address

• Four banks operation

• MRS cycle with address key programs

-. CAS latency (2 & 3)

-. Burst length (1, 2, 4, 8 & Full page)

-. Burst type (Sequential & Interleave)

• All input s are sampled at the positive going edge of the system clock

• Burst read single -bit write operation

• DQM for masking

• Auto & self refresh

• 64ms refresh period (4K cycle)

12.5.3.Pin Description

PIN NAME INPUT FUNCTION

CLK System clock Active on the positive going edge to sample all inputs.

CS Chip select Disables or enables device operation by masking or enabling all

inputs except CLK, CKE and L(U)DQM

CKE Clock enable Masks system clock to freeze operation from the next clock

cycle.

CKE should be enabled at least one cycle prior to new

command.

Disable input buffers for power down in standby.

A0 ~ A11 Address Row/column addresses are multiplexed on the same pins.

BA0 ~ BA1 Bank select address Selects bank to be activated during row address latch time.

RAS Row address strobe Latches row addresses on the positive going edge of the CLK

CAS Column address strobe Latches column addresses on the positive going edge of the

WE Write enable Enables write operation and row precharge.

L(U)DQM Data input/output mask Makes data output Hi-Z, tSHZ after the clock and masks the

DQ0 ~ 15 Data input/output Data inputs/outputs are multiplexed on the same pins.

VDD/VSS Power supply/ground Power and ground for the input buffers and the core logic.

VDDQ/VSSQ Data output power/ground Isolated power supply and ground for the output buffers to

N.C/RFU No connection

/reserved for future use

Row address : RA0 ~ RA11, Column address : CA0 ~ CA7

Selects bank for read/write during column address latch time.

with RAS low.

Enables row access & precharge.

CLK with CAS low.

Enables column access.

Latches data in starting from CAS, WE active.

output.

Blocks data input when L(U)DQM active.

provide improved noise immunity.

This pin is recommended to be left No Connection on the device.

14

AK53 D.O.C. Service Manual 22/03/2004

12.6.FLASH (IC 314)

12.6.1.General Description

The MT28F128J3 is a nonvolatile, electrically block-erasable (Flash), programmable memory

containing 134,217,728 bits organized as 16,777,218 bytes (8 bits) or 8,388,608 words (16 bits). This

128Mb device is organized as one hundred twenty-eight 128KB erase blocks.

The MT28F640J3 contains 67,108,864 bits organized as 8,388,608 bytes (8 bits) or 4,194,304 words

(16 bits). This 64Mb device is organized as sixty-four 128KB erase blocks.

Similarly, the MT28F320J3 contains 33,554,432 bits organized as 4,194,304 bytes (8 bits) or 2,097,152

words (16 bits). This 32Mb device is organized as thirty-two 128KB erase blocks.

These three devices feature in-system block locking. They also have comm on Flash interface (CFI) that

permits software algorithms to be used for entire families of devices. The software is deviceindependent, JEDEC ID-independent with forward and backward compatibility.

Additionally, the scalable command set (SCS) allows a single, simple software driver in all host systems

to work with all SCS-compliant Flash memory devices. The SCS provides the fastest system/device

data transfer rates and minimizes the device and system-level implementation costs.

To optimize the processor-memory interface, the device accommodates VPEN, which is switchable

during block erase, program, or lock bit configuration, or hard-wired to VCC, depending on the

application. VPEN is treated as an input pin to enable erasing, programming, and block locking. When

VPEN is lower than the VCC lockout voltage (VLKO), all program functions are disabled. Block erase

suspend mode enables the user to stop block erase to read data from or program data to any other

blocks. Similarly, program suspend mode enables the us er to suspend programming to read data or

execute code from any unsuspended blocks.

VPEN serves as an input with 2.7V, 3.3V, or 5V for application programming. VPEN in this Q-Flash _

family can provide data protection when connected to ground. This pin also enables program or erase

lockout during power transition.

Micron’s even -sectored Q-Flash devices offer individual block locking that can lock and unlock a block

using the sector lock bits command sequence.

Status (STS) is a logic signal output that gives an additional indicator of the internal state machine

(ISM) activity by providing a hardware signal of both status and status masking. This status indicator

minimizes central processing unit (CPU) overhead and system power consumption. In the default

mode, STS acts as an RY/BY# pin. When LOW, STS indicates that the ISM is performing a block

erase, program, or lock bit configuration. When HIGH, STS indicates that the ISM is ready for a new

command.

Three chip enable (CE) pins are used for enabling and disabling the device by activating the device’s

control logic, input buffer, decoders, and sense amplifiers.

BYTE# enables the device to be used in x8 or x16 read/write mode; BYTE# = 0 selects an 8-bit mode,

with address A0 selecting between the LOW and HIGH by te, while BYTE# = 1 selects a 16-bit mode.

When BYTE# = 1, A1 becomes the lowest-order address line with A0 being a no connect.

RP# is used to reset the device. When the device is disabled and RP# is at Vcc, the standby mode is

enabled. A reset time (t RWH) is required after RP# switches HIGH until outputs are valid. Likewise, the

device has a wake time (t RS) from RP# high until writes to the command user interface (CUI) are

recognized. When RP# is at GND, it provides write protection, resets the ISM, and clears the status

register.

A variant of the MT28F320J3 also supports the new security block lock feature for additional code

security. This feature provides an OTP function for the device. (Contact factory for availability.)

The MT28F320J3 and the MT28F640J3 are manufactured using the 0.18µm process technology, and

the MT28F128J3 is manufactured using the 0.15µm process technology.

12.6.2.Features

• x8/x16 organization

• One hundred twenty-eight 128KB erase blocks (128Mb)

Sixty-four 128KB erase blocks (64Mb)

Thirty-two 128KB erase blocks (32Mb)

•VCC, VCCQ, and VPEN voltages:

2.7V to 3.6V VCC operation

2.7V to 3.6V, or 5V VPEN application programming

• Interface Asynchronous Page Mode Reads:

150ns/25ns or 120ns/25ns read access time (128Mb)

120ns/25ns or 115ns/25ns read access time (64Mb)

110ns/25ns read access time (32Mb)

• Manufacturing ID (ManID)

Intel® (0x89h)

15

AK53 D.O.C. Service Manual 22/03/2004

Loading...

Loading...