VESTEL 11AK52 TABLE OF CONTENTS

TABLE OF CONTENTS

1.INTRODUCTION ....................................................................................................................................1

2.TUNER....................................................................................................................................................1

3.IF PART (TDA9885/86).......................................................................................................................... 1

4.VIDEO SWITCH TEA6415 .....................................................................................................................2

5.MULTI STANDARD SOUND PROCESSOR..........................................................................................2

6.SOUND OUTPUT STAGE WITH TDA7480L.........................................................................................2

7.VERTICAL OUTPUT STAGE WITH TDA8177F....................................................................................2

8.VIDEO OUTPUT AMPLIFIER TDA6109................................................................................................3

9.POWER SUPPLY (SMPS) .....................................................................................................................3

10.MICROCONTROLLER SDA5550........................................................................................................3

10.1.General Features..........................................................................................................................3

10.2.External Crystal and Programmable Clock Speed ...................................................................3

10.3.Microcontroller Features.............................................................................................................3

10.4.Memory..........................................................................................................................................3

10.5.Display Features ..........................................................................................................................3

10.6.ROM Characters...........................................................................................................................4

10.7.Acquisition Features....................................................................................................................4

10.8.Ports ..............................................................................................................................................4

11.SERIAL ACCESS 32K EEPROM ........................................................................................................4

12.CLASS AB STEREO HEADPHONE DRIVER TDA1308....................................................................4

13.SAW FILTERS......................................................................................................................................4

14.IC DESCRIPTIONS ..............................................................................................................................5

14.1.TDA6109........................................................................................................................................5

14.1.1.General Description ..............................................................................................................5

14.1.2.Features..................................................................................................................................5

14.1.3.Pinning....................................................................................................................................5

14.2.27W401..........................................................................................................................................6

14.2.1.Description.............................................................................................................................6

14.2.2.Features..................................................................................................................................6

14.2.3.Connections...........................................................................................................................6

14.3.24LC32A........................................................................................................................................7

14.3.1.Description.............................................................................................................................7

14.3.2.Features..................................................................................................................................7

14.3.3.Pin Descriptions....................................................................................................................7

14.4.SDA5275........................................................................................................................................8

14.4.1.Features..................................................................................................................................8

14.4.2.Pin Definition and functions.................................................................................................8

14.5.DRAM 4MX4..................................................................................................................................9

14.5.1.General Description ..............................................................................................................9

14.5.2.Features................................................................................................................................10

14.5.3.Pin Assignment ...................................................................................................................10

14.6.SDA9400......................................................................................................................................10

14.6.1.General Description ............................................................................................................10

14.6.2.Features................................................................................................................................10

14.6.3.Pin Definition .......................................................................................................................11

14.7.LM317T........................................................................................................................................12

14.7.1.Description...........................................................................................................................12

14.7.2.Features................................................................................................................................12

14.8.DDP3310......................................................................................................................................12

14.8.1.Description...........................................................................................................................12

14.8.2.Features................................................................................................................................12

14.8.3.Pin connection and short descriptions.............................................................................13

14.9.SDA5550......................................................................................................................................14

14.9.1.General definition................................................................................................................14

14.9.2.Features................................................................................................................................15

14.10.TEA6415C..................................................................................................................................16

14.10.1.General Description ..........................................................................................................16

14.10.2.Features..............................................................................................................................16

14.10.3.Pinning................................................................................................................................16

14.11.VPC3230D .................................................................................................................................17

i

14.11.1.General Description ..........................................................................................................17

14.11.2.Pin Connections and Short Descriptions .......................................................................17

14.12.TDA1308T..................................................................................................................................19

14.12.1.General Description ..........................................................................................................19

14.12.2.Features..............................................................................................................................19

14.12.3.Pinning................................................................................................................................19

14.13.MSP34X1G (MSP3411G)..........................................................................................................19

14.13.1.Description.........................................................................................................................19

14.13.2.Features..............................................................................................................................20

14.13.3.Pin connections.................................................................................................................20

14.14.TL431.........................................................................................................................................22

14.14.1.Description.........................................................................................................................22

14.14.2.Features..............................................................................................................................22

14.14.3.Pin Configurations ............................................................................................................22

14.15.TDA9885/86...............................................................................................................................22

14.15.1.Introduction........................................................................................................................22

14.15.2.Features..............................................................................................................................22

14.15.3.Pin Configurations ............................................................................................................23

14.16.LM7808......................................................................................................................................23

14.16.1.Description.........................................................................................................................23

14.16.2.Features..............................................................................................................................23

14.17.TDA8177F..................................................................................................................................24

14.17.1.Description.........................................................................................................................24

14.17.2.Features..............................................................................................................................24

14.17.3.Pin connections.................................................................................................................24

14.17.4.Block Diagram ...................................................................................................................24

14.18.LM1086......................................................................................................................................24

14.18.1.Description.........................................................................................................................24

14.18.2.Features..............................................................................................................................24

14.18.3.Applications.......................................................................................................................25

14.18.4.Connection Diagrams .......................................................................................................25

14.19.MC44608....................................................................................................................................25

14.19.1.Description.........................................................................................................................25

14.19.2.General Features...............................................................................................................25

14.19.3.Pin Connections................................................................................................................26

14.20.TCET1102G...............................................................................................................................26

14.20.1.Description.........................................................................................................................26

14.20.2.Applications.......................................................................................................................26

14.20.3.Features..............................................................................................................................26

14.21.TDA7480L..................................................................................................................................27

14.21.1.Description.........................................................................................................................27

14.21.2.Features..............................................................................................................................27

14.21.3.Pin Functions.....................................................................................................................27

14.22.SAA3010T..................................................................................................................................27

14.22.1.Description.........................................................................................................................27

14.22.2.Features..............................................................................................................................28

14.22.3.Pinning................................................................................................................................28

15.AK52 CHASSIS MANUAL ADJUSTMENTS PROCEDURE.............................................................29

15.1.PRELIMINARY.............................................................................................................................29

15.2.SYSTEM VOLTAGE ADJUSTMENTS........................................................................................29

15.3.AFC ADJUSTMENTS..................................................................................................................29

15.4.FOCUS ADJUSTMENTS.............................................................................................................29

15.5.SCREEN ADJUSTMENTS..........................................................................................................29

15.6.IF ADJUSTMENT FOR L’ MODE................................................................................................29

16.AK52 CHASSIS PRODUCTION SERVICE MODE ADJUSTMENTS ...............................................29

16.1.PRELIMINARY.............................................................................................................................30

16.2.H/V (HORIZONTAL AND VERTICAL GEOMETRY ALIGNMENTS)..........................................30

16.3.VIDEO ALIGNMENTS.................................................................................................................33

16.4.SERVICE ALIGNMENTS.............................................................................................................34

17.BLOCK DIAGRAM.............................................................................................................................36

18.CIRCUIT DIAGRAMS.........................................................................................................................37

ii

1.INTRODUCTION

11AK52 is a 100Hz flicker free colour television capable of driving 28”4:3/16:9, 32” 16:9, 33”4:3 and

29”4:3 real flat picture tubes.

The chassis is capable of operation in PAL, SECAM, NTSC (playback) colour standards and multiple

transmission standards as B/G, D/K, I/I’, and L/L´.

Sound system output is supplying 2x10W (10%THD) for left and right outputs of 8ohm speakers.

TV supports the level 1.5 teletext standard. It is possible to decode transmissions including high

graphical data.

The chassis is equipped with two full EuroScarts, one SCART for AV input/output, one front-AV input,

one back-AV input, one headphone output, one SVHS input (via SCART and SVHS connector), two

external speaker outputs (left and right).

2.TUNER

The hardware and software of the TV is suitable for tuners, supplied by different companies, which are

selected from the Service Menu. These tuners can be combined VHF, UHF tuners suitable for CCIR

systems B/G, H, L, L´, I/I´, and D/K. The tuning is available through the digitally controlled I

(PLL). Below you will find info on one of the Tuners in use.

General description of UV1316:

The UV1316 tuner belongs to the UV 1300 family of tuners, which are designed to meet a wide range of

applications. It is a combined VHF, UHF tuner suitable for CCIR systems B/G, H, L, L’, I and I’. The low

IF output impedance has been designed for direct drive of a wide variety of SAW filters with sufficient

suppression of triple transient.

Features of UV1316:

1. Member of the UV1300 family small sized UHF/VHF tuners

2. Systems CCIR: B/G, H, L, L’, I and I’; OIRT: D/K

3. Digitally controlled (PLL) tuning via I

2

C-bus

4. Off-air channels, S-cable channels and Hyperband

5. World standardized mechanical dimensions and world standard pinning

6. Compact size

7. Complies to “CENELEC EN55020” and “EN55013”

2

C bus

Pinning:

1. Gain control voltage (AGC) : 4.0V, Max: 4.5V

2. Tuning voltage

3. I²C-bus address select : Max: 5.5V

4. I²C-bus serial clock : Min:-0.3V, Max: 5.5V

5. I²C-bus serial data : Min:-0.3V, Max: 5.5V

6. Not connected

7. PLL supply voltage : 5.0V, Min: 4.75V, Max: 5.5V

8. ADC input

9. Tuner supply voltage : 33V, Min: 30V, Max: 35V

10. Symmetrical IF output 1

11. Symmetrical IF output 2

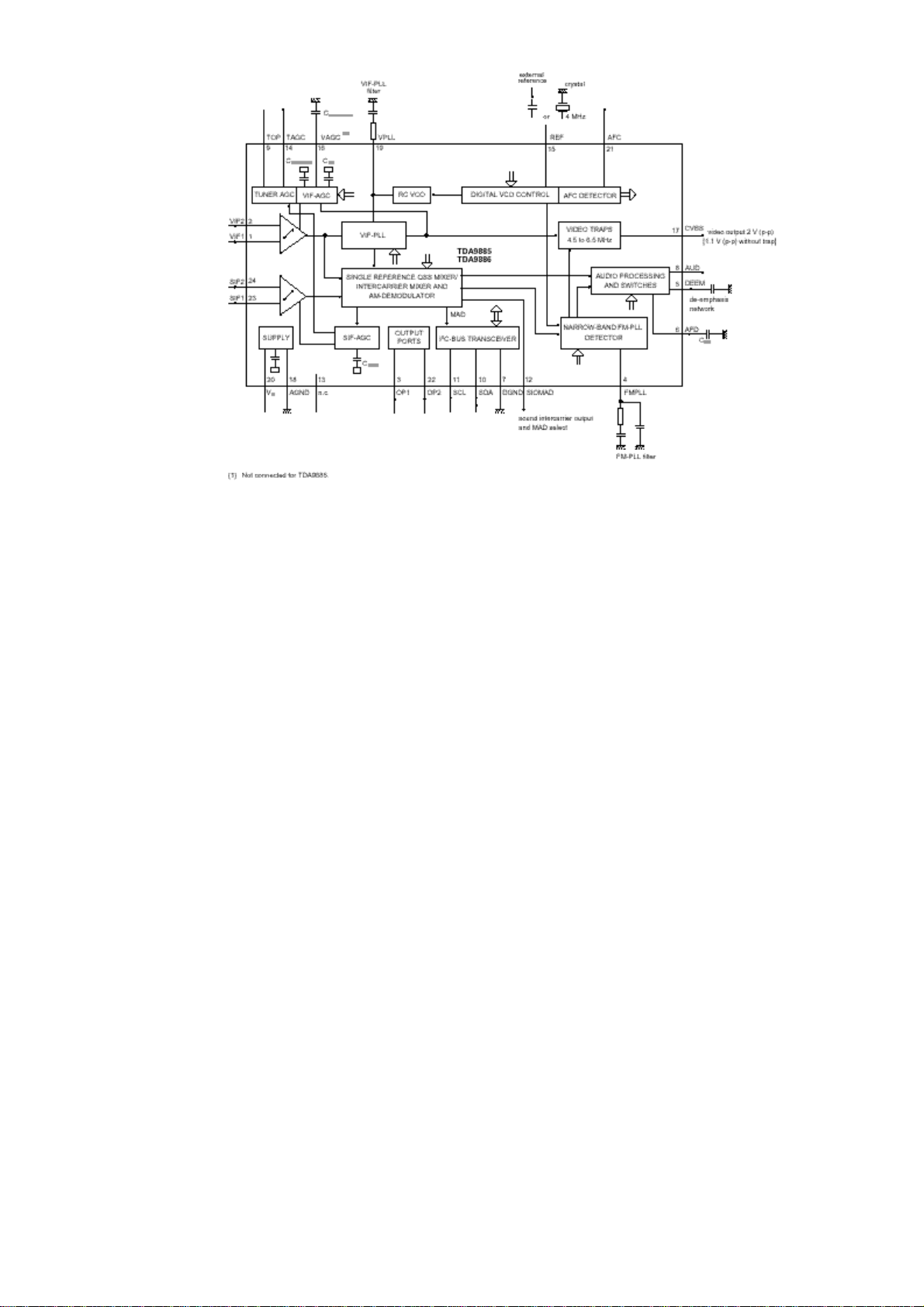

3.IF PART (TDA9885/86)

The TDA9885 is an alignment-free single standard (without positive modulation, only PAL) vision and sound

IF signal PLL.

The TDA9886 is an alignment-free multistandard (PAL, SECAM and NTSC) vision and sound IF signal PLL

Both devices can be used for TV, VTR, PC and set-top box applications.

The following figure shows the simplified block diagram of the integrated circuit.

The integrated circuit comprises the following functional blocks:

VIF amplifier, Tuner and VIF-AGC, VIF-AGC detector, Frequency Phase-Locked Loop (FPLL) detector, VCO

and divider, Digital acquisition help and AFC, Video demodulator and amplifier, Sound carrier trap, SIF

amplifier, SIF-AGC detector, Single reference QSS mixer, AM demodulator, FM demodulator and acquisition

help, Audio amplifier and mute time constant, I

voltage stabilizer.

2

C-bus transceivers and MAD (module address), Internal

1

4.VIDEO SWITCH TEA6415

In case of three or more external sources are used, the video switch IC TEA6415 is used. The main

function of this device is to switch 8 video-input sources on the 6 outputs.

Each output can be switched on only one of each input. On each input an alignment of the lowest level

of the signal is made (bottom of sync. top for CVBS or black level for RGB signals).

Each nominal gain between any input and output is 6.5dB.For D2MAC or Chroma signal the alignment

is switched off by forcing, with an external resistor bridge, 5VDC on the input. Each input can be used

as a normal input or as a MAC or Chroma input (with external Resistor Bridge). All the switching

possibilities are changed through the BUS. Driving 75ohm load needs an external resistor. It is possible

to have the same input connected to several outputs.

5.MULTI STANDARD SOUND PROCESSOR

The MSP34x1G family of single-chip Multi-standard Sound Processors covers the sound processing of

all analog TV-Standards worldwide, as well as the NICAM digital sound standards. The full TV sound

processing, starting with analog sound IF signal-in, down to processed analog AF-out, is performed on

a single chip. Signal conforming to the standard by the Broadcast Television Systems Committee

(BTSC).

The DBX noise reduction, or alternatively, MICRONAS Noise Reduction (MNR) is performed alignment

free. Other processed standards are the Japanese FM-FM multiplex standard (EIA-J) and the FM

Stereo Radio standard.

6.SOUND OUTPUT STAGE WITH TDA7480L

The TDA7480L is an audio class-D amplifier assembled in Power DIP package specially designed for

high efficiency applications mainly for TV and Home Stereo sets.

Mute stand-by function of the audio amplifier can be described as the following; the pin 12

(MUTE/STAND-BY) controls the amplifier status by two different thresholds, referred to ground. When

Vpin 12 voltage is lower than 0.7V the amplifier is in Stand-by mode and the final stage generators are

off. When Vpin 12 is higher than 4V, the amplifier is in play mode.

The TDA7480L is a 10W+10W stereo sound amplifier with mute/stand-by facility. MUTE control signal

coming from microcontroller (when it is at high level) activates the mute function. IC is muted when

mute pin is at low level (pin12). MUTE pin can also be activated via an external pop-noise circuitry in

order to eliminate pop noise when TV is turned off. Just after the TV is turned off, this circuit switches

the IC to stand-by mode by pulling the mute pin voltage to ground.

7.VERTICAL OUTPUT STAGE WITH TDA8177F

The IC TDA8177F is the vertical deflection booster circuit. Two supply voltages, +12V and -12V are

needed to scan the inputs VERT+ and VERT-, respectively. And a third supply voltage, +60V for the

flyback limiting are needed. The vertical deflection coil is connected in series between the output and

feedback to the input.

2

8.VIDEO OUTPUT AMPLIFIER TDA6109

The TDA6109 includes three video output amplifiers in order to drive the three cathodes of a colour

picture tube directly. To obtain maximum performance, the amplifier is used with black-current control.

9.POWER SUPPLY (SMPS)

The DC voltages required at various parts of the chassis are provided by an SMPS transformer

controlled by the IC MC44608, which is designed for driving, controlling and protecting switching

transistor of SMPS. The transformer generates 135V for FBT input, +/-14V for audio amplifier, 8V stand

by voltage and 8V, 12V and 5V supplies for other different parts of the chassis.

An optocoupler is used to control the regulation of line voltage and stand-by power consumption. There

is a regulation circuit in secondary side. This circuit produces a control voltage according to the

changes in 135V DC voltage, via an optocoupler (TCET 1102G) to pin3 of the IC.

During the switch on period of the transistor, energy is stored in the transformer. During the switch off

period energy is fed to the load via secondary winding. By varying switch-on time of the power

transistor, it controls each portion of energy transferred to the second side such that the output voltage

remains nearly independent of load variations.

10.MICROCONTROLLER SDA5550

10.1.General Features

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

• ROM version is used.

10.2.External Crystal and Programmable Clock Speed

• Single external 6MHz crystal, all necessary clocks are generated internally

• CPU clock speed selectable via special function registers.

• Normal Mode 33.33 MHz CPU clock, Power Save mode 8.33 MHz

10.3.Microcontroller Features

• 8bit 8051 instruction set compatible CPU.

• 33.33-MHz internal clock (max.)

• 0.360 ms (min.) instruction cycle

• Two 16-bit timers

• Watchdog timer

• Capture compare timer for infrared remote control decoding

• Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

• ADC (4 channels, 8 bit)

• UART (rxd, txd)

10.4.Memory

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

• UP to 16KByte on Chip Extended RAM (XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

10.5.Display Features

• ROM Character set supports all East and West European Languages in single device

• Mosaic Graphic Character Set

• Parallel Display Attributes

• Single/Double Width/Height of Characters

• Variable Flash Rate

• Programmable Screen Size (25 Rows x 33...64 Columns)

• Flexible Character Matrixes (HxV) 12 x 9...16

• Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable

Characters in Enhanced Mode

• CLUT with up to 4096 colour combinations

• Up to 16 Colours per DRCS Character

• One out of 8 Colours for Foreground and Background Colours for 1-bit DRCS and ROM Characters

3

10.6.ROM Characters

• Shadowing

• Contrast Reduction

• Pixel by Pixel Shiftable Cursor With up to 4 Different Colours

• Support of Progressive Scan and 100 Hz.

• 3 X 4Bits RGB-DACs On-Chip

• Free Programmable Pixel Clock from 10 MHz to 32MHz

• Pixel Clock Independent from CPU Clock

• Multinorm H/V-Display Synchronization in Master or Slave Mode

10.7.Acquisition Features

• Multi-standard Digital Data Slicer

• Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

• Four Different Framing Codes Available

• Data Caption only limited by available Memory

• Programmable VBI-buffer

• Full Channel Data Slicing Supported

• Fully Digital Signal Processing

• Noise Measurement and Controlled Noise Compensation

• Attenuation Measurement and Compensation

• Group Delay Measurement and Compensation

• Exact Decoding of Echo Disturbed Signals

10.8.Ports

• One 8-bit I/O-port with open drain output and optional I

2

C Bus emulation support (Port0)

• Two 8-bit multifunction I/O-ports (Port1, Port3)

• One 4-bit port working as digital or analogue inputs for the ADC (Port2)

• One 2-bit I/O port with secondary function (P4.2, 4.3, 4.7)

• One 4-bit I/O-port with secondary function (P4.0, 4.1, 4.4) (Not available in P-SDIP 52)

11.SERIAL ACCESS 32K EEPROM

24LC32 is the 32Kbit electrically erasable programmable memory. The memory is compatible with the

2

I

C standard, two wire serial interface, which uses a bi-directional data bus and serial clock.

12.CLASS AB STEREO HEADPHONE DRIVER TDA1308

The TDA1308 is an integrated class AB stereo headphone driver contained in a DIP8 plastic package.

The device is fabricated in a 1 mm CMOS process and has been primarily developed for portable digital

audio applications.

13.SAW FILTERS

K3953M:

Standard

B/G, D/K, I, L/L’

Features

TV IF video filter with Nyquist slopes at 33,90 MHz and 38,90 MHz

Constant group delay

Suitable for CENELEC EN 55020

Terminals

Tinned CuFe alloy

Pin configuration

1 Input

2 Input - ground

3 Chip carrier - ground

4 Output

5 Output

K3958M:

Standard

B/G, D/K, I, L/L’

Features

TV IF video filter with Nyquist slopes at 33.90 MHz and 38.90 MHz

Constant group delay

Terminal and Pin configuration are the same with

K3953M

4

K9356M:

Standard

B/G, D/K, I, L

Features

TV IF audio filter with pass band for sound carriers at 32,40 MHz (D/K, L), 32,90 MHz (I) and 33,40 MHz

(B/G)

Terminal and Pin configuration are the same with

K3953M

K9656M:

Standard

B/G, D/K, I, L/L’

Features

TV IF audio filter with two channels

Channel 1 (L’) with one pass band for sound carriers at 40,40 MHz (L’) and 39,75 MHz (L’- NICAM)

Channel 2 (B/G, D/K, L, I) with one pass band for sound carriers between 32,35 MHz and 33,40 MHz

Terminal and Pin configuration are the same with

K3953M

14.IC DESCRIPTIONS

TDA6109 27W401

24LC32 SDA5275

DRAM 4MX4 SDA9400

LM317T DDP3310

SDA5550 TEA6415

VPC3230D TDA1308T

MSP3411G TL431

TDA9885/86 LM7808

TDA8177F LM1086

MC44608 TCET1102G

TDA7480L SAA3010T

14.1.TDA6109

14.1.1.General Description

The TDA6109JF includes three video output amplifiers in one plastic DIL-bent-SIL 9-pin medium power

(DBS9MPF) package (SOT111-1), using high-voltage DMOS technology, and is intended to drive the three

cathodes of a colour CRT directly. To obtain maximum performance, the amplifier should be used with blackcurrent control.

14.1.2.Features

· Typical bandwidth of 9.0 MHz for an output signal of 60 V (p-p)

· High slew rate of 1850 V/ms

· No external components required

· Very simple application

· Single supply voltage of 200 V

· Internal reference voltage of 2.5 V

· Fixed gain of 51

· Black-Current Stabilization (BCS) circuit

· Thermal protection

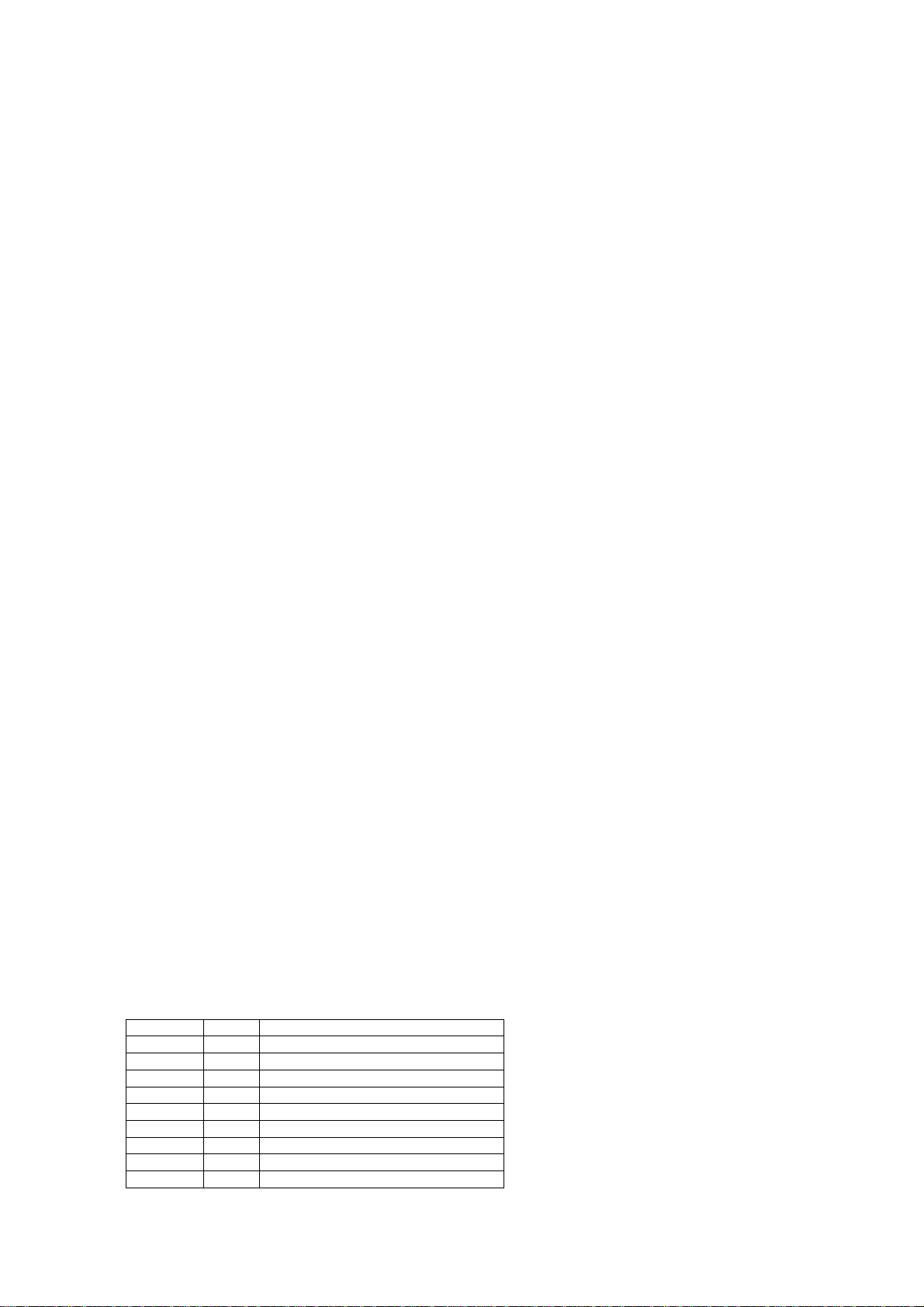

14.1.3.Pinning

SYMBOL PIN DESCRIPTION

V

i(1)

V

i(2)

V

i(3)

GND 4 ground (fin)

I

om

V

DD

V

oc(3)

V

oc(2)

V

oc(1)

1 inverting input 1

2 inverting input 2

3 inverting input 3

5 black current measurement output

6 supply voltage

7 cathode output 3

8 cathode output 2

9 cathode output 1

5

14.2.27W401

14.2.1.Description

The M27W401 is a low voltage 4 Mbit EPROM offered in the two ranges UV (ultra violet erase) and

OTP (one time programmable). It is ideally suited for microprocessor systems requiring large data or

program storage and is organized as 524,288 by 8 bits. The M27W401 operates in the read mode with

a supply voltage as low as 2.7V at –40 to 8C temperature range. The decrease in operating power

allows either a reduction of the size of the battery or an increase in the time between battery recharges.

The FDIP32W (window ceramic frit-seal package) has a transparent lid, which allows the user to expose the chip to ultraviolet light to erase the bit pat-tern. A new pattern can then be written to the device

by following the programming procedure. For application where the content is programmed only one

time and erasure is not required, the M27W401 is offered in PDIP32, PLCC32 and TSOP32 (8x20 mm)

packages.

14.2.2.Features

2.7V to 3.6v Low voltage in Read Operation

Access time:

–70ns at V

–80ns at V

Pin Compatible with M27C4001

Low Power Consumption:

–1mA max Standby Current

– 15mA max Active Current at 5MHz

Programming Time 10ms/byte

High Reliability CMOS Technology

– 2,000V ESD Protection

– 200mA Latchup Protection Immunity

Electronic Signature

– Manufacturer Code: 20h

– Device Code: 41h

= 3.0V to 3.6V

CC

= 2.7V to 3.6V

CC

14.2.3.Connections

DIP connections LCC Connections TSOP Connections

6

Signal Names

A0-A18 Address Inputs

Q0-Q7 Data Outputs

Chip Enable

G Output Enable

V

pp

V

cc

V

ss

Program Supply

Supply Voltage

Ground

14.3.24LC32A

14.3.1.Description

The Microchip Technology Inc. 24LC32A is a 4K x 8 (32K bit) Serial Electrically Erasable PROM

capable of operation across a broad voltage range (2.5V to 6.0V). It has been developed for advanced,

low power applications such as personal communications or data acquisition. The 24LC32A also has a

page-write capability of up to 32 bytes of data. The 24LC32A is capable of both random and sequential

reads up to the 32K boundary. Functional address lines allow up to eight 24LC32A devices on the

same bus, for up to 256K bits address space. Advanced CMOS technology and broad voltage range

make this device ideal for low-power/ low-voltage, nonvolatile code and data applications. The

24LC32A is available in the standard 8-pin plastic DIP and both 150 mil and 200 mil SOIC packaging.

14.3.2.Features

• Single supply with operation down to 2.5V

• Maximum write current 3 mA at 6.0V

• Standby current 1 mA max at 2.5V

• 2-wire serial interface bus, I 2 CÔ compatible

• 100 kHz (2.5V) and 400 kHz (5V) compatibility

• Self-timed ERASE and WRITE cycles

• Power on/off data protection circuitry

• Hardware write protect

• 1,000,000 Erase/Write cycles guaranteed

• 32 byte page or byte write modes available

• Schmitt trigger filtered inputs for noise suppression

• Output slope control to eliminate ground bounce

• 2 ms typical write cycle time, byte or page

• Up to eight devices may be connected to the same bus for up to 256K bits total memory

• Electrostatic discharge protection > 4000V

• Data retention > 200 years

• 8-pin PDIP and SOIC packages

• Temperature ranges

• Commercial (C): 0°C to +75°C

• Industrial (I): -40°C to +85°C

14.3.3.Pin Descriptions

A0, A1, A2 Chip Address Inputs

The A0..A2 inputs are used by the 24LC32A for multiple device operation and conform to the 2-wire bus

standard. The levels applied to these pins define the address block occupied by the device in the

address map. A particular device is selected by transmitting the corresponding bits (A2, A1, A0) in the

control byte.

SDA Serial Address/Data Input/Output

This is a Bi-directional pin used to transfer addresses and data into and data out of the device. It is an

open drain terminal, therefore the SDA bus requires a pull up resistor to V

CC (typical 10 k for 100 kHz,

2 k for 400 kHz) For normal data transfer SDA is allowed to change only during SCL low. Changes

during SCL HIGH are reserved for indicating the START and STOP conditions.

SCL Serial Clock

This input is used to synchronize the data transfer from and to the device.

7

WP

This pin must be connected to either V

SS or VCC. If tied to VSS, normal memory operation is enabled

(read/write the entire memory 000-FFF). If tied to VCC, WRITE operations are inhibited. The entire

memory will be write-protected. Read operations are not affected.

W

CC

+2.5V to 6V Power Supply

SS

W

Ground

14.4.SDA5275

14.4.1.Features

• Single chip teletext IC

• Analog CVBS-input with onchip clamping circuitry

• Slicer

• Supports level 1, 2.5 and 3.5 ETSI teletext standard

• Stores up to 14 teletext pages on chip

• Stores up to 2048 teletext pages with external 16 M memory

• SDA 5275: full level 2.5 processing

• Analog RGB-output

• 41 Latin script languages

• 12 ´ 10 character size

• Parallel display attributes

• 64 from 4096 colors selectable

• Enhanced flash modes

• Dynamically redefinable character set (DRCS, PCS)

• Pixel graphics

• Full screen display (64 ´ 32 or 80 ´ 24 character positions)

• Horizontal and vertical scrolling

• Graphic cursors

• 4:3 and 16:9 display

• Multinorm display (50/60/100/120 Hz)

• RISC-processor

• Firmware downloadable

2

• I

C / 3 wire UART-interface (1 Mbit/s)

• Independent clocks for acquisition and display

• Tools for greatly simplified software development

• 24-Kbyte on-chip reconfigurable DRAM

• 44160-bit character ROM

• One external crystal for all standards

14.4.2.Pin Definition and functions

Pin No. P-LCC-68-1 Symbol Function

1 INTQ Interrupt request output to ext. controller

2 CLK-IO System clock input/output

3 TCSQ/FLD Composite sync output/ field output

4 VS/VCS Vertical sync input/output

5 HS Horizontal sync input/output

6 XOUT 20.5-MHz crystal oscillator output

7 XIN 20.5-MHz crystal oscillator input

8 GPO General purpose output

9 TM Test pin, leave open or connect VSS

10 CVBS CVBS-video signal input

11 VDD1 + 5 V digital supply

12 VDDA + 5 V analog supply

13 VSSA1 Analog ground

14 N.C. Not connected

15 N.C. Not connected

16 VDD2 + 5 V digital supply

17 RES Chip reset

18 N.C. Not connected

8

19 N.C. Not connected

20 N.C. Not connected

21 VDD3 + 5 V digital supply

22 N.C. Not connected

23 VREF + 3 V reference voltage input

24 N.C. Not connected

25 VDD4 + 5 V digital supply

26 A8 External DRAM-address

27 A7 External DRAM-address

28 A6 External DRAM-address

29 A5 External DRAM-address

30 A4 External DRAM-address

31 A3 External DRAM-address

32 A2 External DRAM-address

33 A1 External DRAM-address

34 A0 External DRAM-address

35 A9 External DRAM-address

36 A10 External DRAM-address

37 A11 External DRAM-address

38 RASQ Row address strobe (DRAM)

39 WEQ Write enable (DRAM)

40 D1 External DRAM-data

41 D0 External DRAM-data

42 D2 External DRAM-data

43 D3 External DRAM-data

44 VSS4 0 V digital supply

45 CASQ Column address strobe

46 N.C. Not connected

47 N.C. Not connected

48 N.C. Not connected

49 VSS3 0 V digital supply

50 N.C. Not connected

51 N.C. Not connected

52 N.C. Not connected

53 N.C. Not connected

54 N.C. Not connected

55 VSS2 0 V digital supply

56 VBB Substrate bias voltage N.C.* (depends on version)

57 N.C. Not connected

58 VSSA2 Analog ground

59 RGB-GND RGB-ground

60 VSS1 0 V digital supply

61 R Analog red display output

62 G Analog green display output

63 B Analog blue display output

64 BLAN Blanking signal open drain output

65 CORQ Contrast reduction open drain output

66 SCL Bi-directional I2C Bus clock port

67 SDA Bi-directional I2C Bus data port

68 I2CEN I2C Bus enable

14.5.DRAM 4MX4

14.5.1.General Description

The 4 Meg x 4 DRAM is a randomly accessed, solid-state memory containing 16,777,216 bits

organized in a x4 con-figuration. RAS# is used to latch the row address (first 11 bits for 2K and first 12

bits for 4K). Once the page has been opened by RAS#, CAS# is used to latch the column address

latter 11 bits for 2K and

the latter 10 bits for 4K, address pins A10 and A11 are “don’t care”). READ and

WRITE cycles are selected with the WE# input. A logic HIGH on WE# dictates READ mode, while a

logic LOW on WE# dictates WRITE mode. During a WRITE cycle, data-in (D) is latched by the falling

edge of WE# or CAS#, whichever occurs last. An EARLY WRITE occurs when WE# is taken LOW prior

to CAS# falling. A LATE WRITE or READ-MODIFY-WRITE occurs when WE# falls after CAS# is taken

LOW. During EARLY WRITE cycles, the data outputs (Q) will remain High-Z regardless of the state of

OE#. During LATE WRITE or READ-MODIFY-WRITE cycles, OE# must be taken HIGH to disable the

9

(the

data outputs prior to applying input data. If a LATE WRITE or READ-MODIFY-WRITE is attempted

while keeping OE# LOW, no write will occur, and the data outputs will drive read data from the

accessed location. The four data inputs and the four data outputs are routed through four pins using

common I/O, and pin direction is controlled by WE# and OE#.

14.5.2.Features

• Industry-standard x4 pin out, timing, functions and packages

• State-of-the-art, high-performance, low-power CMOS silicon-gate process

• Single power supply (+3.3V ±0.3V or +5V ±10%)

• All inputs, outputs and clocks are TTL-compatible

• Refresh modes: RAS#-ONLY, HIDDEN and CAS#-BEFORE- RAS# (CBR)

• Optional Self Refresh (S) for low-power data retention

• 11 row, 11 column addresses (2K refresh) or 12 row, 10 column addresses (4K refresh)

• Extended Data-Out (EDO) PAGE MODE access cycle

• 5V-tolerant inputs and I/Os on 3.3V devices

14.5.3.Pin Assignment

Top View

*NC on 2K refresh and A11 on 4K refresh options. Note: The “#” symbol indicates signal is active LOW.

14.6.SDA9400

14.6.1.General Description

The SDA9400 is a new component of the Micronas MEGAVISION ® IC set in a 0.35µm embedded

DRAM technology (frame memory embedded). The SDA9400 is pin compatible to the SDA9401 (field

memory embedded). The SDA9400 comprises all main functionalities of a digital feature box in one

monolithic IC. The scan rate conversion to 100/120 Hz interlaced (50/60 Hz progressive) is based on a

motion adaptive algorithm. The scan rate converted picture can be vertically expanded. The SDA9400

has a free running mode, therefore features like scan rate conversion to e.g. 70, 75 Hz with joint lines or

multiple picture display (e.g. tuner scan) are possible. Due to the frame based signal processing, the

noise reduction has been greatly improved. Furthermore separate motion detectors for luminance and

chrominance have been implemented. For automatic controlling of the noise reduction parameters a

noise measurement algorithm is included, which measures the noise level in the picture or in the

blanking period. In addition a spatial noise reduction is implemented, which reduces the noise even in

the case of motion. The input signal can be compressed horizontally and vertically with a certain

number of factors. Therefore split screen is supported. Beside these additional functions like coloured

background, windowing and flashing are implemented.

14.6.2.Features

• Two input data formats

- 4:2:2 luminance and chrominance parallel (2 x 8 wires)

- ITU-R 656 data format (8 wires)

10

• Two different representations of input chrominance data

- 2‘s complement code

- Positive dual code

• Flexible input sync controller

• Flexible compression of the input signal

- Digital vertical compression of the input signal (1.0, 1.25, 1.5, 1.75, 2.0, 3.0, 4.0)

- Digital horizontal compression of the input signal (1.0, 2.0, 4.0)

• Noise reduction

- Motion adaptive spatial and temporal noise reduction (3D-NR)

- Temporal noise reduction for luminance frame based or field based

- Temporal noise reduction for chrominance field based

- Separate motion detectors for luminance and chrominance

- Flexible programming of the temporal noise reduction parameters

- Automatic measurement of the noise level (5-bit value, readable by I²C bus)

• 3-D motion detection

- High performance motion detector for scan rate conversion

- Global motion detection flag (readable by I²C bus)

- Movie mode and phase detector (readable by I²C bus)

• TV mode detection by counting line numbers (PAL, NTSC, readable by I²C bus)

• Embedded memory

- 5 Mbit embedded DRAM core for field memories

- 192 kbit embedded DRAM core for line memories

• Flexible clock and synchronization concept

- Decoupling of the input and output clock system possible

• Scan rate conversion

- Motion adaptive 100/120 Hz interlaced scan conversion

- Motion adaptive 50/60 Hz progressive scan conversion

- Simple static interlaced and progressive conversion modes for 100/120 Hz interlaced or 50/60 Hz

progressive scan conversion: e.g. ABAB, AABB, AA*B*B, AAAA, BBBB, AB, AA*

- Simple progressive scan conversion with joint lines:

50 Hz -> 60, 70, 75 Hz progressive

60 Hz -> 70, 75 Hz progressive

- Large area and line flicker reduction

• Flexible digital vertical expansion of the output signal (1.0, ... [1/32] ..., 2.0)

• Flexible output sync controller

- Flexible positioning of the output signal

- Flexible programming of the output sync raster

- External synchronization by backend IC possible

(e.g. split screen for one TV channel with joint lines and one PC VGA channel)

• Signal manipulations

- Insertion of coloured background

- Vertical and/or horizontal windowing with four different speed factors

- Flash generation (for supervising applications, motion flag readable by I²C bus)

- Still frame or field

- Support of split screen applications

- Multiple picture display - Tuner scan (4 and 16 times for 4:3, 12 times for 16:9 tubes)

- Support of multi picture display with PIP or front-end processor with integrated scaler

(e.g. 9 times display of PIP pictures, picture tracking, random pictures, still-in-moving picture, movingin-still picture)

• I²C-bus control (400 kHz)

• P-MQFP-64 package

• 3.3 V ± 5% supply voltage

14.6.3.Pin Definition

Pin No. Name Type Description

2,8,24,42,55 VSS1 S Supply voltage ( V SS = 0 V )

9,25,41,56 VDD1 S Supply voltage ( V DD = 3.3 V )

36,52,58 VSS2 S Supply voltage ( V SS = 0 V )

35,51,53,57,59 VDD2 S Supply voltage ( V DD = 3.3 V )

43,..,50 YIN0...7 I/TTL Data input Y (see input data format)

31,..,34;37,...,40 UVIN0...7 I/TTL Data input UV (for 4:2:2 parallel, see input data format)

11

PD (for CCIR 656, see input data format)

30 RESET I/TTL System reset. The RESET input is low active. In order to ensure

correct operation a "Power On Reset" must be performed. The

RESET pulse must have a minimum duration of two clock periods

of the system clock CLK1.

23 HIN I/TTL

PD

22 VIN I/TTL

PD

29 SYNCEN I/TTL Synchronization enable input

21 SDA I/O I2C-Bus data line (5V ability)

20 SCL I I I2C-Bus clock line (5V ability)

54 CLK1 I/TTL System clock 1

17,..,10 UVOUT0...7 O/TTL Data output UV (see output data format)

7,..,3;1;64;63 YOUT0...7 O/TTL Data output Y (see output data format)

62 HREF O/TTL Horizontal active video output

61 VOUT/

VEXT

60 HOUT/

HEXT

18 INTERLACED O/TTL Interlace signal for AC coupled vertical deflection

28 X1 / CLK2 I/TTL Crystal connection / System clock 2

27 X2 O/AN Crystal connection

26 CLKOUT O/TTL Clock output (depends on I²C parameters CLK11EN, CLK21EN,

19 TEST I/TTL Test input, connect to V SS for normal operation

I/O/

TTL

I/O/

TTL

H-Sync input

(only for full CCIR 656)

V-Sync input

(only for full CCIR 656)

EXSYN=0 (I²C-bus parameter): V-Sync output

EXSYN=1: External V-Sync input for output part

EXSYN=0 (I²C-bus parameter): H-Sync output

EXSYN=1: External H-Sync input for output part

FREQR)

14.7.LM317T

14.7.1.Description

The LM317T is an adjustable 3 terminal positive voltage regulator capable of supplying in excess of 1.5

amps over an output range of 1.25 to 37 volts. This voltage regulator is exceptionally easy to use and

requires only two external resistors to set the output voltage. Further, it employs internal current limiting,

thermal shutdown and safe area compensation, making it essentially blow–out proof. The LM317

serves a wide variety of applications including local, on card regulation. This device can also be used to

make a programmable output regulator, or by connecting a fixed resistor between the adjustment and

output, the LM317 can be used as a precision current regulator.

14.7.2.Features

• Output Current in Excess of 1.5 A

• Output Adjustable between 1.2 V and 37 V

• Internal Thermal Overload Protection

• Internal Short Circuit Current Limiting Constant with Temperature

• Output Transistor Safe–Area Compensation

• Floating Operation for High Voltage Applications

• Available in Surface Mount D

2

PAK, and Standard 3–Lead Transistor Package

• Eliminates Stocking many Fixed Voltages

14.8.DDP3310

14.8.1.Description

The DDP 3310B is a single-chip digital Display and Deflection Processor designed for high-quality

back-end applications in 100/120-Hz TV sets with 4:3 or 16:9 picture tubes. The IC can be combined

with members of the DIGIT 3000 IC family (VPC 32xx, TPU 3040), or it can be used with third-party

products. The IC contains the entire digital video component and deflection processing and all analog

interface components.

14.8.2.Features

Video processing

– linear horizontal scaling (0.25 … 4)

– non-linear horizontal scaling “panorama-vision”

– dynamic peaking

12

– soft limiter (gamma correction)

– color transient improvement

– programmable RGB matrix

– picture frame generator

– two analog RGB/Fast-Blank inputs. The DDP 3310B is a single-chip digital Display and Deflection

Processor designed for high-quality back-

Deflection processing

– scan velocity modulation output

– high-performance H/V deflection

– EHT compensation for vertical / East/West

– soft start/stop of H-Drive

– vertical angle and bow

– differential vertical output

– vertical zoom via deflection

– horizontal and vertical protection circuit

– adjustable horizontal frequency for VGA/SVGA display

Miscellaneous

– selectable 4:1:1/ 4:2:2 YC

r C b input

– selectable 27/ 32-MHz line-locked clock input

– crystal oscillator for horizontal protection

– automatic picture tube adjustment (cutoff, white-drive)

– single 5-V power supply

– hardware for simple 50/60-Hz to 100/ 120-Hz conversion (display frequency doubling)

2

– two I

C-controlled PWM outputs

– beam current limiter

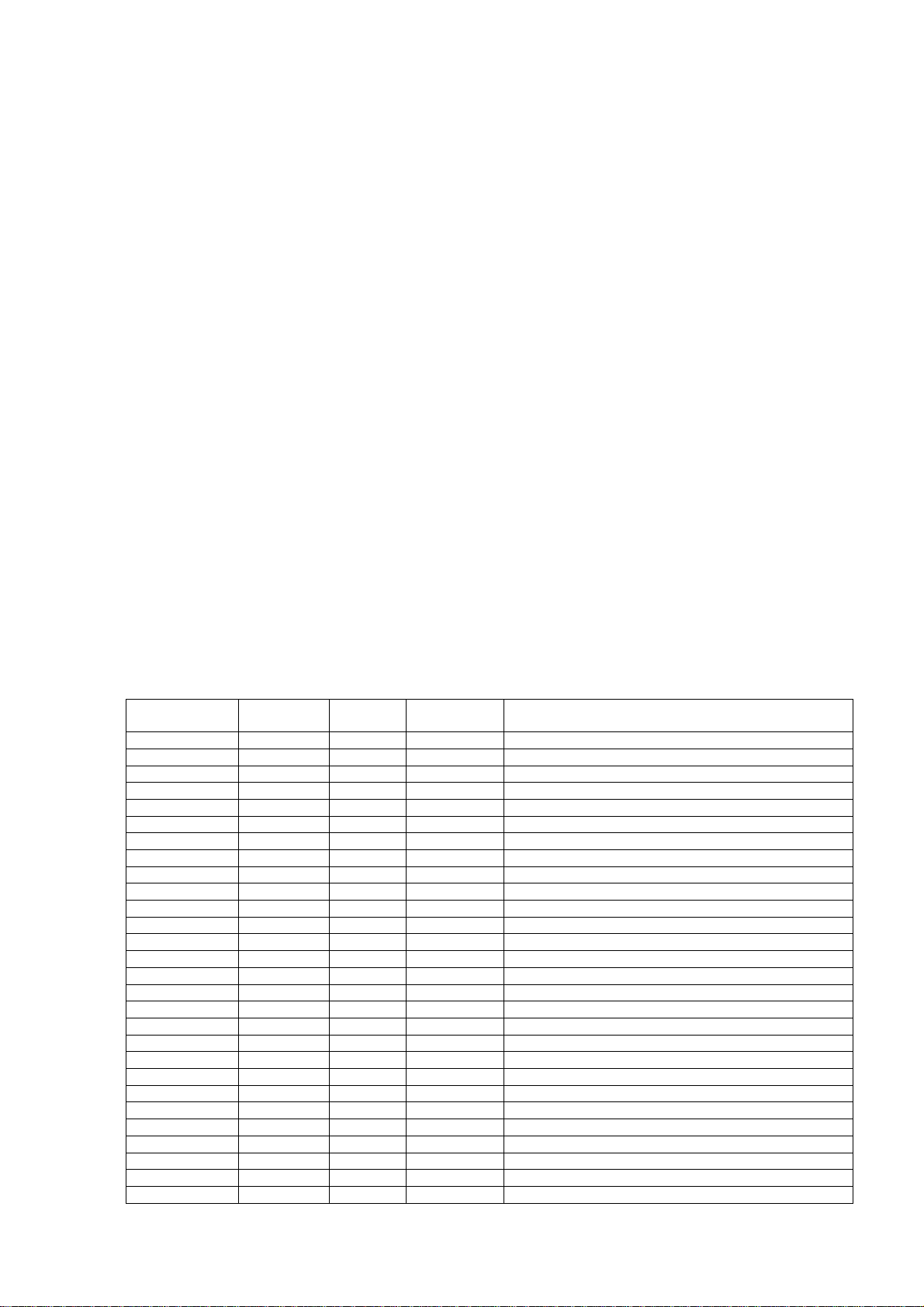

14.8.3.Pin connection and short descriptions

NC = not connected LV = if not used, leave vacant

X = obligatory; connect as described in circuit diagram IN = Input

OUT = Output SUPPLY = Supply Pin

Pin no

PLCCK 68 pin

1 VSUPP SUPPLY X Supply voltage, Output pin driver

2 GNDP SUPPLY X Ground, Output pin driver

3 VS2 IN GNDD Additional VSYNC input

4 FIFORRD OUT LV FIFO Read counter reset

5 FIFORD OUT LV FIFO Read Enable

6 FIFOWR OUT LV FIFO Write Enable

7 FIFORWR OUT LV FIFO Write counter reset

8 HOUT OUT X Horizontal Drive Output

9 HFLB IN Hout Horizontal Flyback Input

10 SAFETY IN GNDO Safety Input

11 VPROT IN GNDO Vertical protection Input

12 FREQSEL IN X Selection of H-Drive Frequency Range

13 CM1 IN X Clock select 40.5 or 27/32 MHz

14 CMO IN X Clock select 27/32 MHz

15 RSW2 OUT LV Range Switch2, Measurement ADC

16 RSW1 IN/OUT LV Range Switch1, Measurement ADC

17 SENSE IN GNDO Sense ADC Input

18 GNDM SUPPLY X Ground, MADC Input

19 VERT+ OUT GNDO Differantial Vertical Sawtooth Output

20 VERT- OUT GNDO Differantial Vertical Sawtooth Output

21 EW OUT GNDO Vertical Parabola Output

22 XREF IN X Reference Input for RGB DACs

23 SVM OUT VSUPO Scan Velocity Modulation

24 ROUT OUT VSUPO Analog Output Red

25 GOUT OUT VSUPO Analog Output Green

26 BOUT OUT VSUPO Analog Output Blue

27 GNDO SUPPLY X Ground, Analog Back-end

28 VSUPO SUPPLY X Supply Voltage, Analog Back-end

Pin name Type Connection

(if not used)

Short description

13

29 VRD/BCS IN X DAC Reference, Beam Current Safety

30 FBLIN1 IN GNDO Fast-Blank1 Input

31 RIN1 IN GNDO Analog Red1 Input

32 GIN1 IN GNDO Analog Green1 Input

33 BIN1 IN GNDO Analog Blue1 Input

34 FBLIN2 IN GNDO Fast-Blank2 Input

35 RIN2 IN GNDO Analog Red2 Input

36 GIN2 IN GNDO Analog Green2 Input

37 BIN2 IN GNDO Analog Blue2 Input

38 TEST IN GNDD Test Pin

39 RESQ IN X Reset Input, active low

40 PWM1 OUT LV I2C-controlled DAC

41 PWM2 OUT LV I2C-controlled DAC

42 HCS IN GNDD Half-contrast

43 C0 IN GNDD Picture Bas Chroma (LSB)

44 C1 IN GNDD Picture Bas Chroma

45 C2 IN GNDD Picture Bas Chroma

46 C3 IN GNDD Picture Bas Chroma

47 C4 IN GNDD Picture Bas Chroma

48 C5 IN GNDD Picture Bas Chroma

49 C6 IN GNDD Picture Bas Chroma

50 C7 IN GNDD Picture Bas Chroma (MSB)

51 VSUPD SUPPLY X Supply Voltage, Digital Circuitry

52 GNDD SUPPLY X Ground, Digital Circuitry

53 LLC2 IN X System Clock Input (27/32/40.5 MHz)

54 Y0 IN GNDD Picture Bas Luma (LSB)

55 Y1 IN GNDD Picture Bas Luma

56 Y2 IN GNDD Picture Bas Luma

57 Y3 IN GNDD Picture Bas Luma

58 Y4 IN GNDD Picture Bas Luma

59 Y5 IN GNDD Picture Bas Luma

60 Y6 IN GNDD Picture Bas Luma

61 Y7 IN GNDD Picture Bas Luma (MSB)

62 LLC1 IN VSUPD Single Line-Locked Clock Input (13.5/16 MHz)

63 HS IN X Horizontal Sync Input

64 VS IN GNDD Vertical Sync Input

65 XTALK2 OUT X Analog Crystal Output (5-MHz Security Clock)

66 XTALK1 IN X Analog Crystal Input (5-MHz Security Clock)

67 SDA IN/OUT X I2C-Bus Data

68 SCL IN/OUT X I2C-Bus Clock

14.9.SDA5550

14.9.1.General definition

The SDA5550M is a single chip teletext decoder for decoding World System Teletext data as well as

Video Programming System (VPS), Program Delivery Control (PDC), and Wide Screen Signalling

(WSS) data used for PAL plus transmissions (Line 23). The device provides an integrated generalpurpose, fully 8051-compatible Microcontroller with television specific hardware features.

Microcontroller has been enhanced to provide powerful features such as memory banking, data

pointers, and additional interrupts etc. The on-chip display unit for displaying Level 1.5 teletext data can

also be used for customer defined on screen displays. Internal XRAM consists of up to 17 Kbytes. This

device can support external memory up to 1Mbyte ROM and RAM.TVTEXT Controller contains a data

slicer for VPS, WSS, PDC and TXT, an acceleration acquisition hardware module, a display generator

for Level 1.5 TXT and powerful On screen Display capabilities based on parallel attributes, and pixel

oriented characters (DRCS). The 8 bit Microcontroller operates at 360nsec cycle time (min). Controller

with dedicated hardware does most of the internal TXT acquisition processing, transfer data to/from

external memory interface and receives/transmits data via I

realized in 0.25 micron technology with 2.5V supply voltage and 3.3V I/O compatible. The IC produces

the following input or output control signals; AGC_CON, MODE_SW, L / L’, PIP_MODS, PIP_SEL,

ON/OFF (stand-by), SC1..3_IN_AV (pin 8 information from 3 SCARTs), AFC, MUTE (to mute audio

output IC), I

2

CEN.

14

2

C-firmware user interface. SDA5550M is

14.9.2.Features

General

• Feature selection via special function register

• Simultaneous reception of TTX, VPS, PDC, and WSS (line 23)

• Supply Voltage 2.5 and 3.3 V

External Crystal and Programmable clock speed

Single external 6MHz crystal, all necessary clocks are generated internally

CPU clock speed selectable via special function registers.

Normal Mode 33.33 MHz CPU clock, Power Save mode 8.33 MHz

Microcontroller Features

• 8bit 8051 instruction set compatible CPU.

• 33.33-MHz internal clock (max.)

• 0.360ms (min.) instruction cycle

• Two 16-bit timers

• Watchdog timer

• Capture compare timer for infrared remote control decoding

• Pulse width modulation unit (2 channels 14 bit, 6 channels 8 bit)

• ADC (4 channels, 8 bit)

• UART

Memory

• Non-multiplexed 8-bit data and 16 … 20-bit address bus (ROMless Version)

• Memory banking up to 1Mbyte (Romless version)

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

• UP to 16KByte on Chip Extended RAM (XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

Display Features

• ROM Character Set Supports all East and West European Languages in single device

• Mosaic Graphic Character Set

• Parallel Display Attributes

• Single/Double Width/Height of Characters

• Variable Flash Rate

• Programmable Screen Size (25 Rows x 33...64 Columns)

• Flexible Character Matrixes (HxV) 12 x 9...16

• Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable

Characters in Enhanced Mode

• CLUT with up to 4096 color combinations

• Up to 16 Colors per DRCS Character

• One out of Eight Colors for Foreground and Background Colors for 1-bit DRCS and ROM Characters

• Shadowing

• Contrast Reduction

• Pixel by Pixel Shiftable Cursor With up to 4 Different Colors

• Support of Progressive Scan and 100 Hz.

• 3 X 4Bits RGB-DACs On-Chip

• Free Programmable Pixel Clock from 10 MHz to 32MHz

• Pixel Clock Independent from CPU Clock

• Multinorm H/V-Display Synchronization in Master or Slave Mode

15

Loading...

Loading...