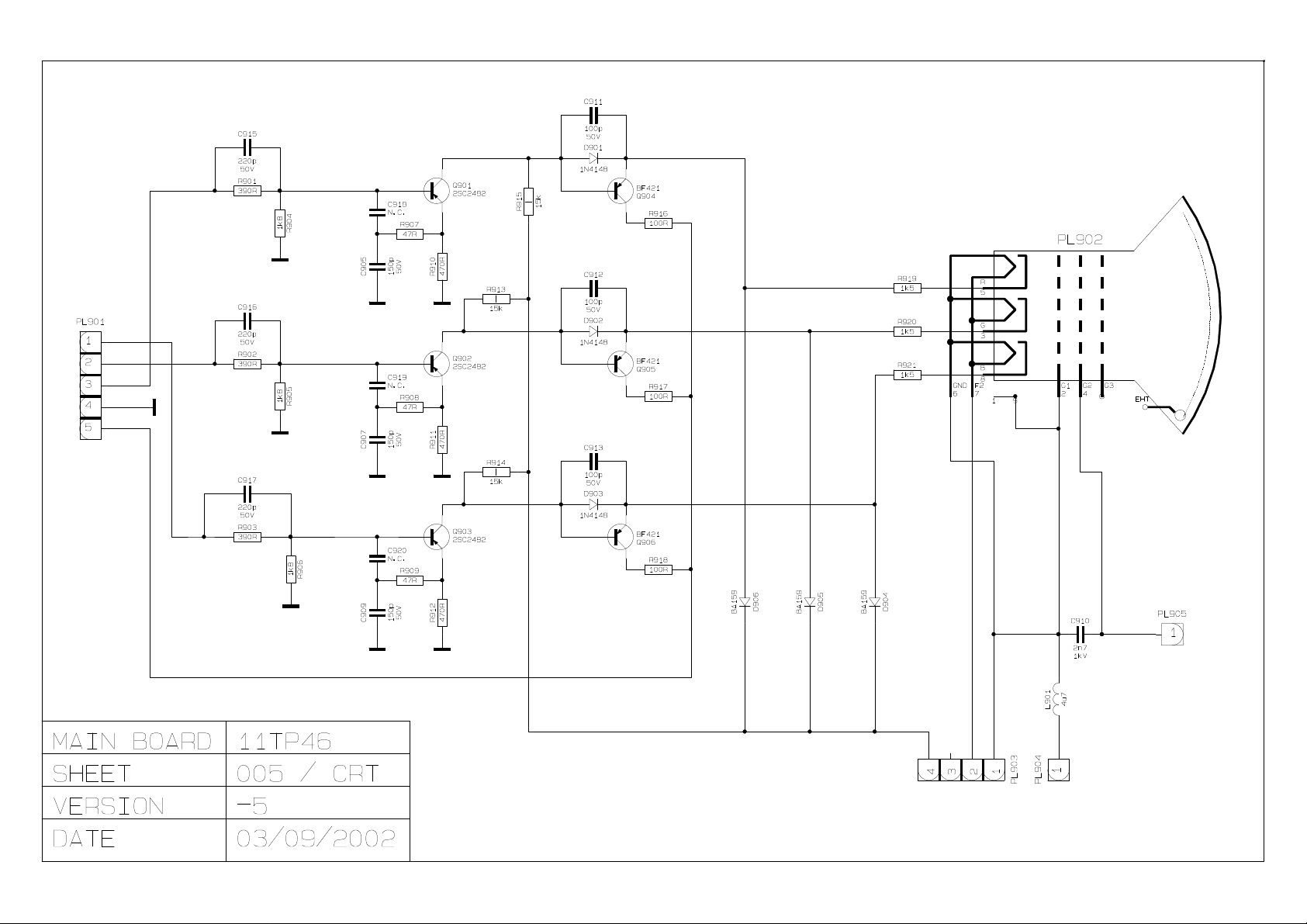

VESTEL 11AK46 Schematics 5

A

B

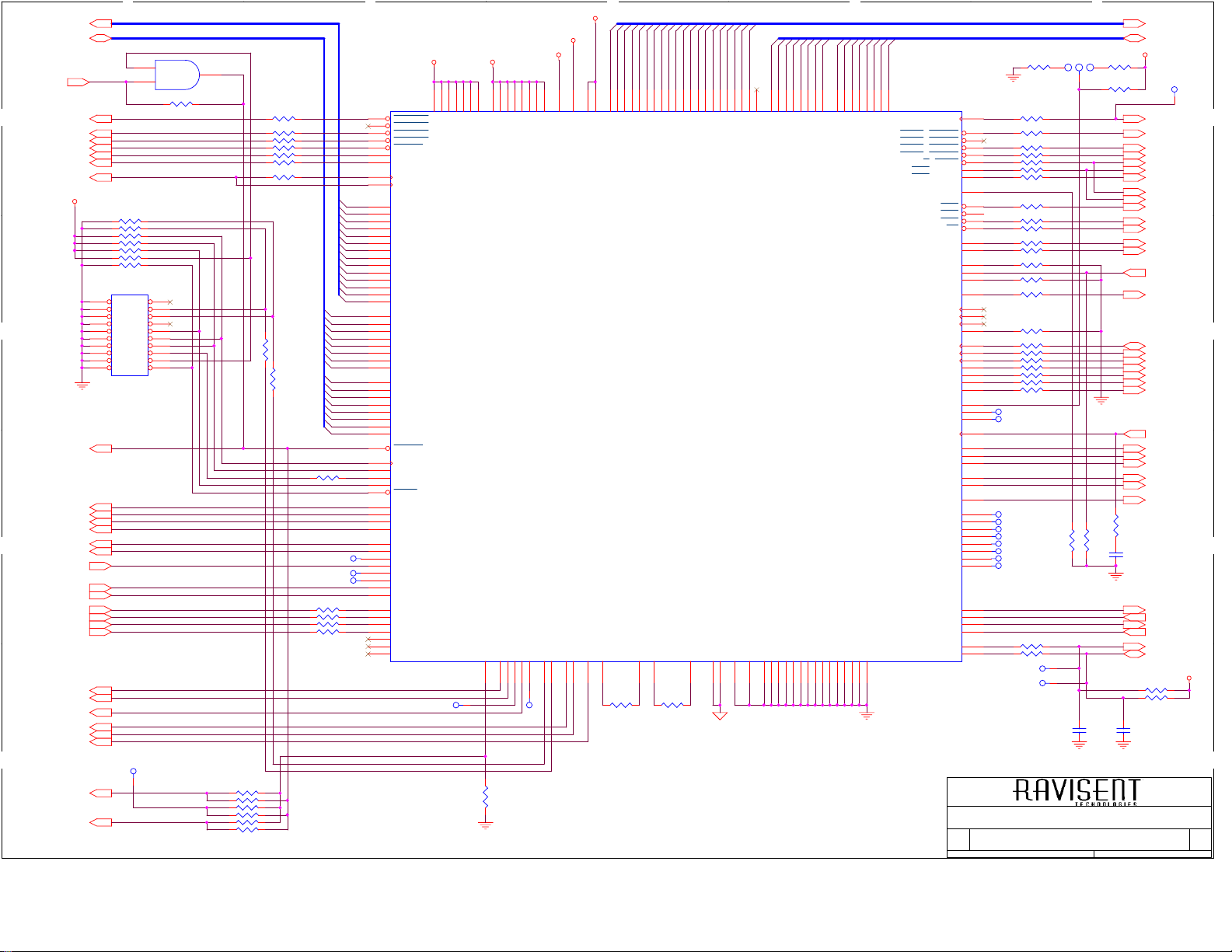

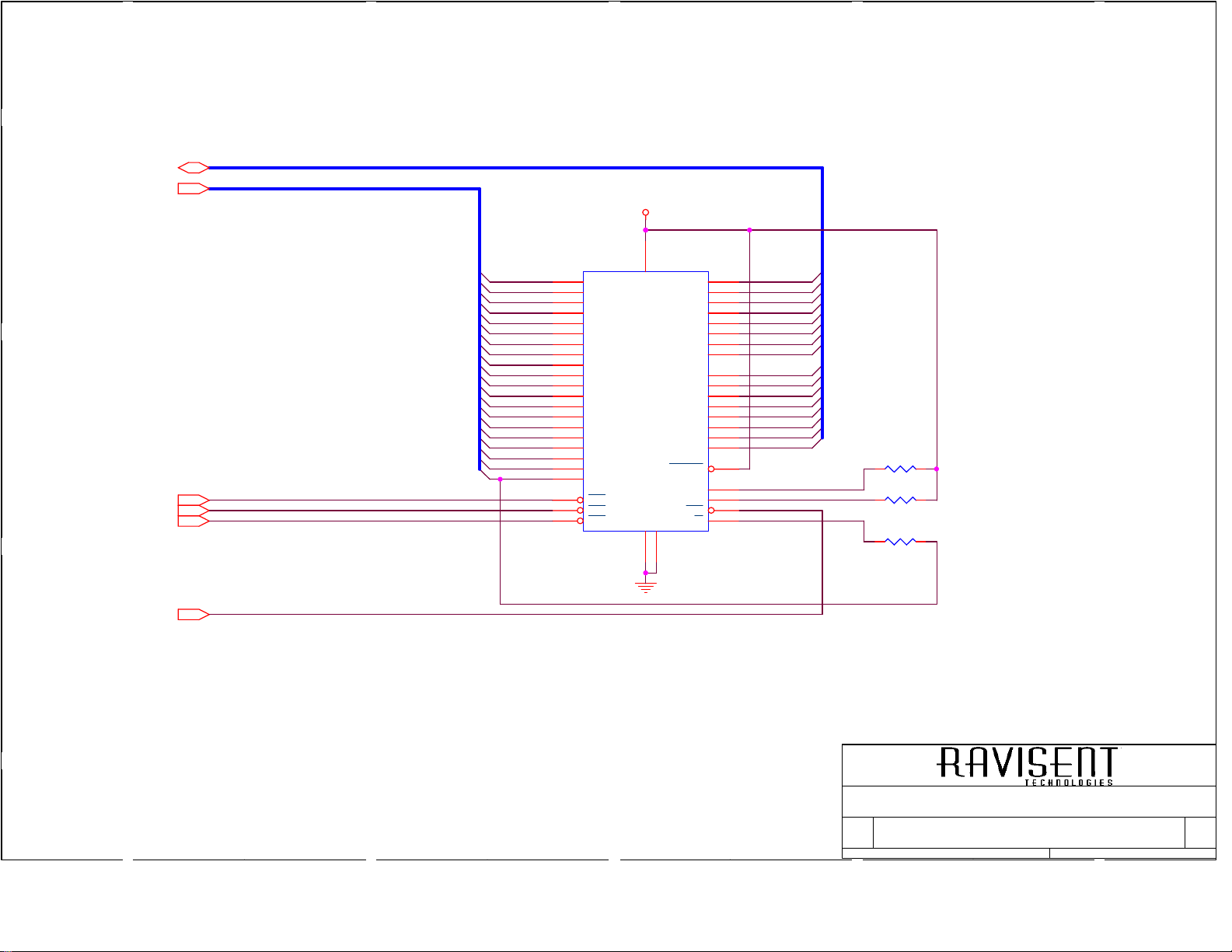

Production - STi5508/80

C

REV DESCRIPTION APPROVAL

1.0

INITIAL RELEASE

D

E

DATE

4 4

3 3

2 2

1 1

A

DECMEM

05-DECMEM

FRONT PANEL

14-FRONT PANEL

AUDIO OUT

11-AUDIO OUT

VIDEO OUT

12-VIDEO OUT

SEEPROM RST

20-SEEPROM RST

EXTPLL

09-EXTPLL

MA[0..13]

MD[0..15]

SMICLK

#SMICS0

#SMIRAS

#SMICAS

#SMIWE

SMIDQML

SMIDQMU

FPDATA

#BPRESET

SPDIF_OUT

DAC_PCMCLK

DAC_SCLK

DAC_LRCLK

DAC_DATA0

DAC_DATA1

DAC_DATA2

DAC_DATA

BPPIO0

BPPIO1

BPPIO2

BPPIO3

STANDBY

CHROMA

POWERON

#BPRESET

PCMCLK

PIXCLK

AUDCLK

FPCLK

FPSTB

FPIR

SCL

SDA

SCL

SDA

RED

GREEN

BLUE

LUMA

CVBS

SCL

SDA

B

MA[0..13] ADR[0..20]

MD[0..15] DATA[0..15]

ML

MD

MC

STi5508

MA[0..13]

MD[0..15]

SMICLK

#SMICS0

#SMIRAS

#SMICAS

#SMIWE

SMIDQML

SMIDQMU

FPCLK

FPDATA

FPSTB

FPIR

#BPRESET

SPDIF_OUT

DAC_SCLK

DAC_LRCLK

DAC_DATA0

DAC_DATA1

DAC_DATA2

DAC_DATA

BPPIO0

BPPIO1

BPPIO2

BPPIO3

RED

GREEN

BLUE

CHROMA

LUMA

CVBS

POWERON

ML

MD

MC

PIXCLK

AUDCLK

02-5508

ADR[0..20]

DATA[0..15]

#SDRAS

#SDCAS

#FERESET

#ATAPI_WR

#ATAPI_RD

C

RAMCLK

#SDCS0

#SDWE

DQML

DQMH

#CE3

#OE

#WE

#RESET

RTS

CTS

TXD

RXD

#CE1

R/#W

FEINT

OPEN

CLOSE

#SENSE

#PUSH

DATA

BCLK

FLAG

SYNC

SCL

SDA

SYSMEM

ADR[0..20]

DATA[0..15]

RAMCLK

#SDCS0

#SDRAS

#SDCAS

#SDWE

DQML

DQMH

04-SYSMEM

FLASHROM

ADR[0..20]

DATA[0..15]

#CE3

#OE

#WE

#RESET

03-FLASHROM

RS232

RTS

CTS

TXD

RXD

10-RS232

FRONTEND

ADR[0..20]

DATA[0..15]

#FERESET

#CE1

R/#W

#ATAPI_WR

#ATAPI_RD

FEINT

OPEN

CLOSE

#SENSE

#PUSH

DATA

BCLK

FLAG

SYNC

SCL

SDA

06-FRONTEND

POWER

22-POWER

I²C Add.:

E²PROM 0xA0

RTC/WD 0xDE

NV-MEM 0xAE

TVM502 0x30

D

THESE SCHEMATICS ARE PROPRIETARY AND CONFIDENTIAL

INFORMATION OF RAVISENT Technologies Inc.

(c) RAVISENT Technologies Inc.

Title

Production - Overview of Decoder Board

Size Document Number Rev

A3

101559

Date: Sheet

of

116Tuesday, December 26, 2000

E

1.1

A

MA[0..13]

MD[0..15]

POWERON

4 4

#SMICS0

#SMIRAS

#SMICAS

#SMIWE

SMIDQML

SMIDQMU

SMICLK

VCC3

3 3

#RESET

BPPIO0

BPPIO1

BPPIO2

BPPIO3

2 2

OPEN

CLOSE

FPIR

#SENSE

#PUSH

DATA

BCLK

FLAG

SYNC

MC

MD

ML

FPCLK

FPDATA

FPSTB

1 1

MA[0..13]

MD[0..15]

1

2

#SMICS0

#SMIRAS

#SMICAS

#SMIWE

SMIDQML

SMIDQMU

SMICLK

R19 10K

R21 10K

R23 10K

R24 10K

R26 10K

R28 10K

R29 10K

J1

12

34

56

78

910

1112

1314

1516

1718

1920

HEADER2X10

SHROUDED

BPPIO0

BPPIO1

BPPIO2

BPPIO3

OPEN

CLOSE

FPIR

#SENSE

#PUSH

DATA

BCLK

FLAG

SYNC

MC

MD

ML

FPCLK

FPDATA

FPSTB

TP12

#JTAG_RESET

U1

TC4S81F

R3 NS

TRIGIN

TRIGOUT

#RESET

4

R4 0R0

R6 0R0

R8 0R0

R9 0R0

R11 0R0

R13 0R0

R16 0R0

R36 75R

R41 75R

TDO

R45 56R

R49 220R

R50 220R

R51 220R

R52 220R

TP6

TP7

TP8

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

TCK

TDI

TMS

#TRST

B

VCC3

U2

74

SMICS0

75

SMICS1

76

SMIRAS

77

SMICAS

78

SMIWE

79

SMIDQML

80

SMIDQMU

95

SMICLKOUT

82

SMICLKIN

69

SMIADR0

68

SMIADR1

67

SMIADR2

SMIADR3

58

SMIADR4

59

SMIADR5

60

SMIADR6

61

SMIADR7

62

SMIADR8

63

SMIADR9

70

SMIADR10

71

SMIADR11

72

SMIADR12

73

SMIADR13

84

SMIDATA0

85

SMIDATA1

86

SMIDATA2

SMIDATA3

88

SMIDATA4

89

SMIDATA5

90

SMIDATA6

91

SMIDATA7

92

SMIDATA8

93

SMIDATA9

97

SMIDATA10

98

SMIDATA11

99

SMIDATA12

100

SMIDATA13

101

SMIDATA14

102

SMIDATA15

124

RESET

113

TCK

112

TDI

111

TDO

110

TMS

109

TRST

205

PARA_REQ/PIO2_1

201

PARA_SYNC/PIO1_5

206

PARA_STR/PIO2_2

196

PARA_DVALID/PIO1_2

6

PARA_DATA0/PIO3_0

7

PARA_DATA1/PIO3_1

8

PARA_DATA2/PIO3_2

9

PARA_DATA3/CAP0/PIO3_3

10

PARA_DATA4/CAP1/PIO3_4

11

PARA_DATA5/CAP2/PIO3_5

12

PARA_DATA6/PIO3_6

13

PARA_DATA7/PIO3_7

16

B_DATA

17

B_BCLK

18

B_FLAG

19

B_SYNC

20

B_WCLK/NRSS_CLK

21

B_V4/NRSS_IN

22

NRRS_OUT

STi5508

or STi5580

#SOFT_RESET

TP5

4

VDD3

47

VDD3

C

+2V5-DENC

+2V5-PCM

+2V5-PLL

+2V5

81

VDD3

107

VDD3

136

VDD3

159

VDD3

184

VDD3

14

37

64

VDD2_5

VDD2_5

94

119

149

VDD2_5

VDD2_5

VDD2_5

198

171

VDD2_5

VDD2_5

VDD2_5

485023

122

VDD_PLL

VDD_PCM

ADR1

ADR2

161

162

30

ADR1

VDD_RGB

VDD_YCC

ADR3

163

ADR2

ADR4

ADR5

164

165

ADR3

ADR4

ADR6

ADR7

166

167

ADR5

ADR6

ADR9

ADR8

168

169

ADR7

ADR8

ADR10

ADR11

170

173

ADR9

ADR10

ADR11

ADR12

ADR14

ADR13

174

175

176

ADR12

ADR13

ADR16

ADR15

177

178

ADR14

ADR15

ADR16

ADR19

ADR17

ADR18

179

180

181

ADR17

ADR18

ADR20

182

183

ADR19

ADR20

ADR21

DATA1

DATA0

DATA2

141

142

143

DATA1

DATA0

DATA3

DATA4

144

145

DATA2

DATA3

DATA4

DATA5

DATA6

14665147

DATA5

ST Microelectronics

STi5508/80

PIO0_0

189

186

PIO0_3

PIO0_5

PIO0_4

191

192

190

TP11

PIO0_6

PIO0_7

193

20287203

PIO1_6

PIO1_7

204

PIO2_5

PIO2_0

1

3

PIO2_7

V_REF DAC RGB

I_REF DAC RGB

V_REF DAC YCC

28

29

356636

R57

20K0

1%

20K0

1%

R58

VSS_YCC

VSS_RGB

I_REF DAC YCC

24

31

VSS_PCM

VSS_PLL

49

123

VSSOEVSS

VSS

VSS

VSS

38

15596

VSS

VSS

83

108

DATA8

DATA7

148

151

DATA7

DATA6

VSS

VSS

VSS

137

121

1502199

D

DATA9

DATA10

152

153

DATA8

DATA9

VSS

VSS

172

160

DATA13

DATA11

DATA12

DATA14

DATA15

154

155

156

157

158

RAMCLK

CAS1/SDCS0

RAS1/SDCS1

DATA11

DATA12

DATA10

DATA13

DATA14

DATA15

RAS0/SDRAS

CAS0/SDCAS

R/W/SDWE

BE0/DQML

BE1/DQMH

ATAPI_RD/PIO0_1

ATAPI_WR/PIO0_2

SPDIF_OUT

ADC_PCMCLK

ADC_SCLK

ADC_LRCLK

ADC_DATA

DAC_PCMCLK

DAC_SCLK

DAC_LRCLK

DAC_DATA0

DAC_DATA1

DAC_DATA2

PIO2_6/DAC_DATA

PWM1/BOOTFROMROM

PWM0/HSYNC

PWM2/VSYNC

PIXCLK _27Mhz

CVBS_OUT

YUV0/PIO4_0

YUV1/PIO4_1

YUV2/PIO4_2

YUV3/PIO4_3

YUV4/PIO4_4

YUV5/PIO4_5

YUV6/PIO4_6

YUV7/PIO4_7

PIO2_3

PIO2_4

PIO1_3/TXD2

PIO1_4/RXD2

PIO1_1/SCL

VSS

VSS

VSS

PIO1_0/SDA

185

WAIT

CE1

CE2

CE3

IRQ0

IRQ1

IRQ2

R_OUT

G_OUT

B_OUT

Y_OUT

C_OUT

R5

118

R7

140

138

R10

135

R12

139

R14

130

R15

128

R17

129

131

R18

134

133

R20

132

R22

117

R25

187

R27

188

R32

127

FEINT

126

R30

125

R31

57

106

103

104

R35

105

55

R37

R38

51

R39

56

R40

52

R42

53

R43

54

R44

BOOTFROMROM

115

116

114

PIXCLK

120

RED

27

GREEN

26

BLUE

25

LUMA

32

CHROMA

33

CVBS

34

39

40

41

42

43

44

45

46

RTS

207

CTS

208

TXD

197

RXD

200

R53

195

R54

194

TP31

TP32

TP33

TP34

TP35

TP36

TP37

TP38

TP39

TP40

TP9

TP10

R1

10K

0R0

0R0

0R0

0R0

0R0

0R0

0R0

33R

33R

33R

33R

33R

10K

10K

33R

10K

33R

33R

33R

33R

33R

33R

33R

33R

33R

E

ADR[0..20]

DATA[0..15]

JUMPER3

10K

R47

10K

C2

47pF

R347

R48

10K

SCL

SDA

R2

10K

R46

75R

C1

47pF

R55

R56

C3

47pF

VCC3

ADR[0..20]

DATA[0..15]

TP1JP1

RAMCLK

#SDCS0

#SDRAS

#SDCAS

#SDWE

DQML

DQMH

R/#W

#WE

#CE1

#CE3

#OE

#ATAPI_RD

#ATAPI_WR

FEINT

SPDIF_OUT

AUDCLK

DAC_SCLK

DAC_LRCLK

DAC_DATA0

DAC_DATA1

DAC_DATA2

DAC_DATA

PIXCLK

RED

GREEN

BLUE

LUMA

CHROMA

CVBS

RTS

CTS

TXD

RXD

SCL

SDA

VCC

4K7

4K7

#FERESET

#BPRESET

Ravisent Proprietary Information

#FERESET

#AUXRESET

#BPRESET

A

R59 0R0

R61 NS

R62 0R0

R63 NS

R64 NS

R65 0R0

R60

10K

B

C

D

Title

Production - STi5508 Core

Size Document Number Rev

A3

101559

Date: Sheet

of

216Tuesday, December 26, 2000

E

1.1

A

B

C

D

E

Firmware Flash ROM

4 4

DATA[0..15]

ADR[0..20]

3 3

#CE3

#OE

#WE

2 2

#RESET

DATA[0..15]

ADR[0..20]

#CE3

#OE

#WE

VCC-FLASH

ADR1

ADR2

ADR3

ADR4

ADR5

ADR6

ADR7

ADR8

ADR9

ADR10

ADR11

ADR12

ADR13

ADR14

ADR15

ADR16

ADR17

ADR18

ADR19

ADR20

FLASH_1024KX16

or FLASH_512x16

100ns

TSOP48

25

24

23

22

21

20

19

18

48

17

16

26

28

11

8

7

6

5

4

3

2

1

9

U3

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18/NC

A19/NC

CE

OE

WE

37

DQ0

DQ1

VCC

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15/A-1

BYTE

VPP

#WP

RP

VSS

VSS

RB

272946

31

33

35

38

40

42

44

30

32

34

36

39

41

43

45

47

13

14

12

15

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

#RESET

R66

0R0

R67

0R0

R68

NS-0R0

INSTALL ZERO OHM

RESISTORS FOR INTEL

AND MICRON FLASH

SUPPORT. DO NOT

INSTALL FOR OTHER

VENDORS.

ZERO OHM RESISTOR

REQUIRED FOR SOME

16MB DEVICES A19 ON PIN 15

1 1

Title

Production - FLASH ROM Memory

Ravisent Proprietary Information

A

Size Document Number Rev

A4

Date: Sheet of

B

C

101599

D

316Tuesday, December 26, 2000

E

1.1

A

B

C

D

E

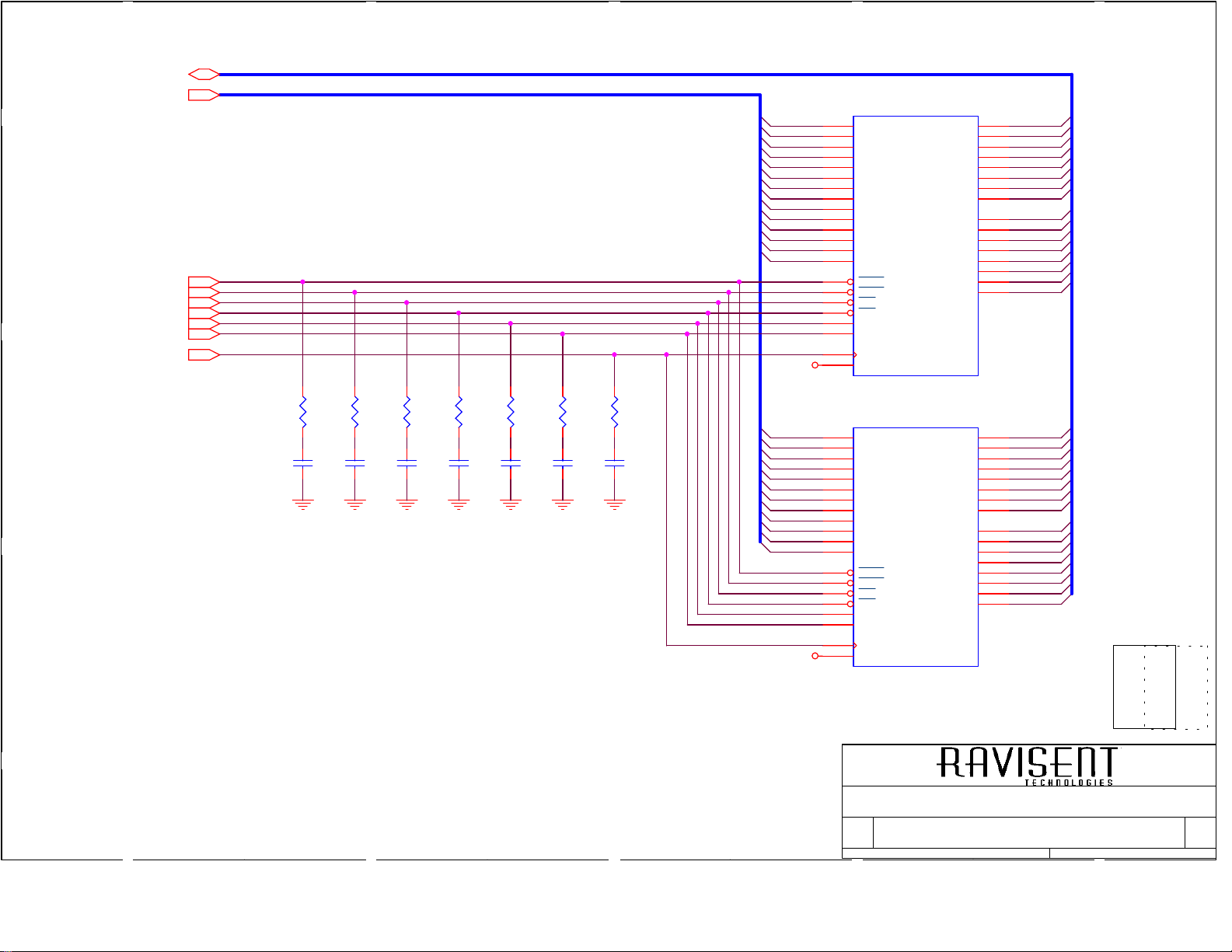

Dedicated System Memory (Optional)

DATA[0..15]

ADR[0..20]

4 4

#SDRAS

#SDCAS

#SDWE

#SDCS0

3 3

DQML

DQMH

RAMCLK

2 2

DATA[0..15]

ADR[0..20]

#SDRAS

#SDCAS

#SDWE

#SDCS0

DQML

DQMH

RAMCLK

R69

75R

C4

47pF

R70

75R

C5

47pF

R71

75R

C6

47pF

R72

75R

C7

47pF

R73

75R

C8

47pF

R74

75R

C9

47pF

R75

75R

C10

47pF

ADR1

ADR2

ADR3

ADR4

ADR5

ADR6

ADR7

ADR8

ADR9

ADR10

ADR11

ADR12

ADR15

ADR16

VCC3

ADR1

ADR2

ADR3

ADR4

ADR5

ADR6

ADR7

ADR8

ADR9

ADR10

ADR11

ADR12

VCC3

U20/1

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

21

A12_BA1

20

A13_BA0

18

RAS

17

CAS

16

WE

19

CS

15

LDQM

39

UDQM

38

CLK

37

CKE

SDRAM_4MX16

125MHz

3.3V

U20/2

21

A0

22

A1

23

A2

24

A3

27

A4

28

A5

29

A6

30

A7

31

A8

32

A9

20

A10

19

A11

17

RAS

16

CAS

15

WE

18

CS

14

LDQM

36

UDQM

35

CLK

34

CKE

NS-SDRAM_1MX16

125MHz

3.3V

TSOP(II)50_400

2

D0

4

D1

5

D2

7

D3

8

D4

10

D5

11

D6

13

D7

42

D8

44

D9

45

D10

47

D11

48

D12

50

D13

51

D14

53

D15

TSOP(II)54

2

D0

3

D1

5

D2

6

D3

8

D4

9

D5

11

D6

12

D7

39

D8

40

D9

42

D10

43

D11

45

D12

46

D13

48

D14

49

D15

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

Overlap footprints

of /1 and /2 parts

1 1

Title

Production - System DRAM Memory

Size Document Number Rev

A4

Date: Sheet of

101599

D

416Tuesday, December 26, 2000

E

1.1

Ravisent Proprietary Information

A

Note:

- place RC termination close to U5

- route SDCLK as short as possible

- 125MHz SDRAMs are required

B

C

A

B

C

D

E

Decoder / SMI Memory

4 4

MD[0..15]

MA[0..13]

3 3

#SMIRAS

#SMICAS

#SMIWE

#SMICS0

SMIDQML

SMIDQMU

SMICLK

MD[0..15]

MA[0..13]

#SMIRAS

#SMICAS

#SMIWE

#SMICS0

SMIDQML

SMIDQMU

SMICLK

R76

75R

R77

75R

R78

75R

R79

75R

R80

75R

R81

75R

R82

75R

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

VCC3

U4

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

21

A12_BA1

20

A13_BA0

18

RAS

17

CAS

16

WE

19

CS

15

LDQM

39

UDQM

38

CLK

37

CKE

SDRAM_4MX16

125MHz

3.3V

TSOP(II)54

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

2

4

5

7

8

10

11

13

42

44

45

47

48

50

51

53

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

ROUTE SMICLK IN A LOOP FROM

2 2

C11

47pF

C12

47pF

C13

47pF

C14

47pF

C15

47pF

C16

47pF

C17

47pF

5508 PIN 95 TO SDRAM THEN BACK

TO 5508 PIN 82

1 1

Title

Production - Decoder SDRAM Memory

Size Document Number Rev

A4

Date: Sheet of

101599

D

516Tuesday, December 26, 2000

E

1.1

Ravisent Proprietary Information

A

Note:

- place RC termination close to U6

- route SDCLK as short as possible

- 125MHz SDRAMs are required

B

C

A

B

C

D

E

4 4

ADR[0..20]

#FERESET

3 3

#CE1

R/#W

#ATAPI_WR

#ATAPI_RD

SCL

SDA

OPEN

CLOSE

#SENSE

#PUSH

ADR[0..20]

#FERESET

#CE1

R/#W

#ATAPI_WR

#ATAPI_RD

#FERESET

SCL

SDA

OPEN

CLOSE

#SENSE

#PUSH

2 2

ATAPI

ADR[0..20] DATA[0..15]

#FERESET

#CE1

R/#W

#ATAPI_WR

07-ATAPI

TVM502

#FERESET

SCL

SDA

OPEN

CLOSE

#SENSE

#PUSH

08-TVM502

FEINT

FEINT#ATAPI_RD

DATA

BCLK

FLAG

SYNC

DATA[0..15]

FEINT

DATA

BCLK

FLAG

SYNC

FEINT

DATA[0..15]

FEINT

DATA

BCLK

FLAG

SYNC

1 1

Title

Production - Front End Options

Size Document Number Rev

Ravisent Proprietary Information

A

A4

Date: Sheet

B

C

101599

D

of

616Tuesday, December 26, 2000

E

1.1

Loading...

Loading...