Vestel 11AK25 Service Manual

CONTENTS

Contents ................................................................................................................................................................................... 1

Safety Precautions ................................................................................................................................................................... 2

TV Set switched off .................................................................................................................................................................. 2

Measurements .......................................................................................................................................................................... 2

PERI-TV SOCKET ................................................................................................................................................................... 2

SCART 1 ................................................................................................................................................................................... 2

SCART 2 ................................................................................................................................................................................... 2

INTRODUCTION ...................................................................................................................................................................... 2

SMALL SIGNAL PART WITH TDA884X .................................................................................................................................. 2-3

TUNER...................................................................................................................................................................................... 4

VIDEO SWITCH TEA6415C .................................................................................................................................................... 4

SOUND OUTPUT STAGE TDA2614/TDA2615/TDA2616Q ....................................................................................................... 5

VERTICAL OUTPUT STAGE WITH TDA8351/TDA8356 ........................................................................................................... 5

VIDEO OUTPUT AMPLIFIER TDA6107Q .................................................................................................................................... 5

POWER SUPPLY (SMPS) .......................................................................................................................................................... 5

MICROCONTROLLER SDA545X OTP ....................................................................................................................................... 5

SERIAL ACCESS CMOS 8K (1024*8) EEPROM ST24C08 ................................................................................................... 6

CLASS AB STEREO HEADPHONE DRIVER TDA1308 ............................................................................................................. 6

SAW FILTERS ........................................................................................................................................................................... 6

IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM ............................................................................................................. 7

TDA8840/TDA8842/TDA8844 ............................................................................................................................................ 6-7

PLL ..................................................................................................................................................................................... 8

TEA6415C .......................................................................................................................................................................... 8

TDA2614/TDA2615 ............................................................................................................................................................ 9

TDA6107Q .......................................................................................................................................................................... 10

MC44604 ............................................................................................................................................................................ 10

SDA545X ............................................................................................................................................................................ 11

ST24C08 ............................................................................................................................................................................. 12

TDA1308 ............................................................................................................................................................................ 13

G1965M .............................................................................................................................................................................. 13

AK25 CHASSIS MANUAL ADJUSTMENT PROCEDURE ........................................................................................................... 13

For Option Settings ............................................................................................................................................................................ 13

OPTION 00 ........................................................................................................................................................................................ 1 4

OPTION 01 ........................................................................................................................................................................................ 1 4

OPTION 02 ........................................................................................................................................................................................ 1 4

OPTION 03 ........................................................................................................................................................................................ 1 4

OPTION 04 ........................................................................................................................................................................................ 1 4

OPTION 05 ........................................................................................................................................................................................ 1 4

OPTION 06 ........................................................................................................................................................................................ 1 4

OPTION 07 ........................................................................................................................................................................................ 14- 1 5

OPTION 08 ........................................................................................................................................................................................ 1 5

OPTION 09 ........................................................................................................................................................................................ 1 6

OPTION 10 ........................................................................................................................................................................................ 1 6

OPTION 11 ........................................................................................................................................................................................ 1 6

OPTION 12 ........................................................................................................................................................................................ 16- 1 7

OPTION 13 ........................................................................................................................................................................................ 1 7

OPTION 14 ........................................................................................................................................................................................ 1 7

OPTION 15 ........................................................................................................................................................................................ 1 7

OPTION 16 ........................................................................................................................................................................................ 1 8

OPTION 17 ........................................................................................................................................................................................ 1 8

OPTION 18 ........................................................................................................................................................................................ 1 8

OPTION 19 ........................................................................................................................................................................................ 1 8

OPTION 20 ........................................................................................................................................................................................ 1 9

OPTION 21 ........................................................................................................................................................................................ 1 9

OPTION 22 ........................................................................................................................................................................................ 1 9

OPTION 23 ........................................................................................................................................................................................ 1 9

OPTION 24 ........................................................................................................................................................................................ 1 9

OPTION 25 ........................................................................................................................................................................................ 2 0

OPTION 26 ........................................................................................................................................................................................ 2 0

OPTION 27 ........................................................................................................................................................................................ 2 0

OPTION 28 ........................................................................................................................................................................................ 2 0

OPTION 29 ........................................................................................................................................................................................ 2 0

OPTION 30 ........................................................................................................................................................................................ 2 1

AK25 CHASSIS ADJUST SETTING

ADJUST 00-24 ................................................................................................................................................................................... 21

AK25 TECHNICAL FEATURES AND DIFFERENCES ...................................................................................................................... 22

GENERAL BLOCK DIAGRAM OF CHASSIS AK25 ............................................................................................................................ 2 3

1

DO NOT CHANGE ANY MODULE UNLESS THE SET IS SWITCH OFF

The mains supply side of the switch mode power supply transformer is live.

Use an isolating transformer.

The receivers fulfill completely the safety requirements.

Safety precautions:

Servicing of this TV should only be carried out by a qualified person.

- Components marked with the warning symbol on the circuit diagram are critical for safety and must only be replaced with an identical

component.

- Power resistor and fusable resistors must be mounted in an identical manner to the original component.

- When servicing this TV, check that the EHT does not exceed 28kV.

TV Set switched off:

Make short-circuit between HV-CRT clip and CRT ground layer.

Short C804 (150mF) before changing IC802 or other components in primary side of SMPS.

Measurements:

Voltage readings and oscilloscope traces are measured under following conditions.

Antenna signal 60dB from colourbar generator. (100% white, 75% colour saturation)

Brightness, contrast, colour set for a normal picture.

Mains supply, 220VAC, 50Hz.

PERI-TV SOCKET

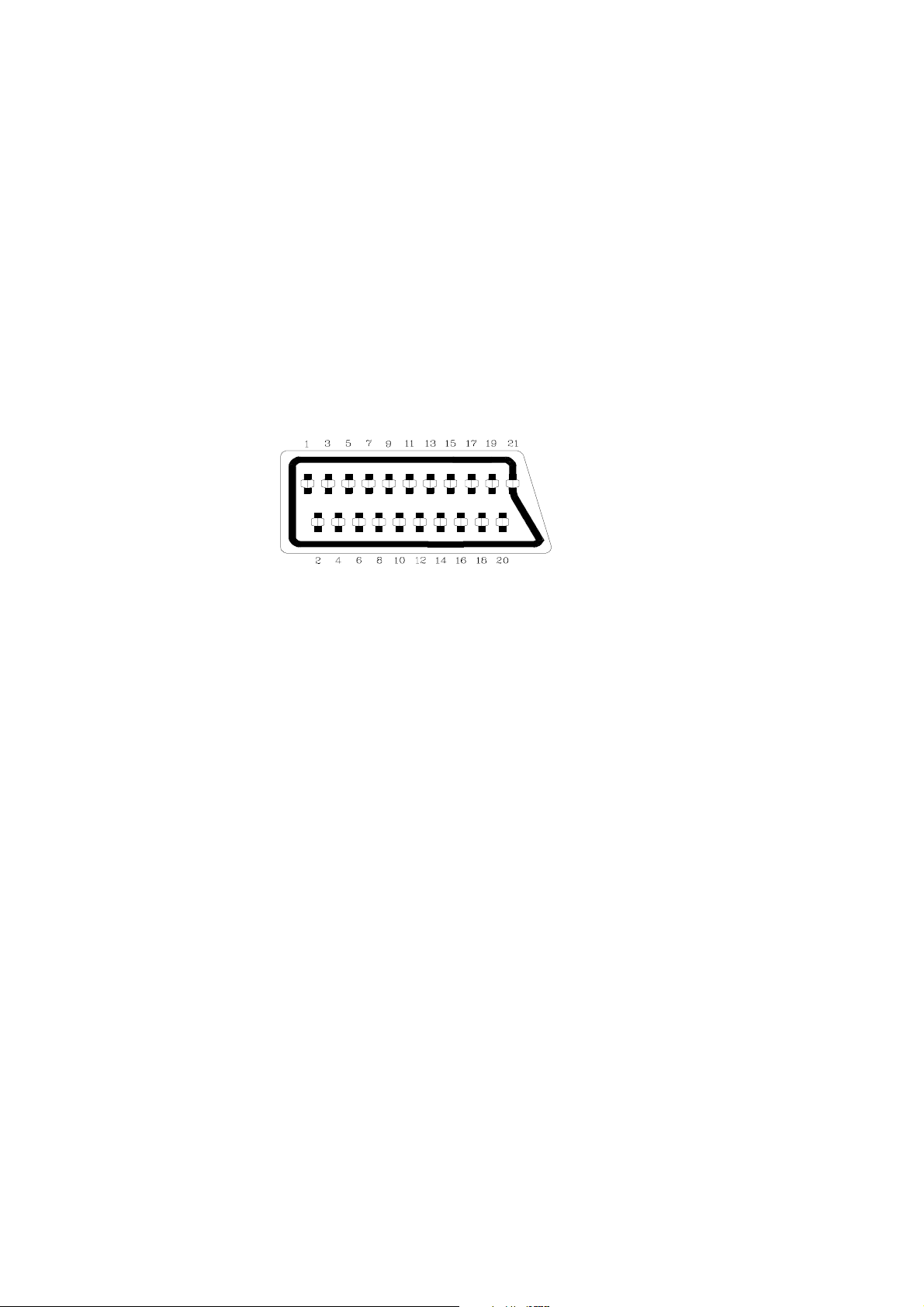

SCART 1 (SC050) SCART 2 (SC051)

1 Audio right output 0.5Vrms / 1K 1 Audio right output 0.5Vrms / 1K

2 Audio right input 0.5Vrms / 10K 2 Audio right input 0.5Vrms / 10K

3 Audio left output 0.5Vrms / 1K 3 Audio left output 0.5Vrms / 1K

4 Ground AF 4 Ground AF

5 Ground Blue 5 Ground Blue

6 Audio left input 0.5Vrms / 10K 6 Audio left input 0.5Vrms / 10K

7 Blue input 0.7Vpp / 75ohm 7 Blue input 0.7Vpp / 75ohm

8 AV switching input 0-12VDC /10K 8 AV switching input 0-12VDC /10K

9 Ground Green 9 Ground Green

10 - 10 11 Green input 0.7Vpp / 75ohm 11 12 - 12 13 Ground Red 13 Ground Red

14 Ground Blanking 14 Ground Blanking

15 Red input 0.7Vpp / 75ohm 15 16 Blanking input 0-0.4VDC, 1-3VDC / 75ohm 16 17 Ground CVS output 17 Ground CVS output

18 Ground CVS input 18 Ground CVS input

19 CVS output 1Vpp / 75ohm 19 CVS output 1Vpp / 75ohm

20 CVS input 1Vpp / 75ohm 20 CVS input 1Vpp / 75ohm

21 Ground 21 Ground

1. INTRODUCTION

11AK25 is a 90ø chassis capable of driving 14-20-21 tubes at appropriate currents.

The chassis is capable of working in both PAL and SECAM. The sound system is capable of giving 6watts

RMS output into a load of 8ohms.

One 8 page simple TELETEXT, TOPTEXT and FASTEXT is provided.

The chassis is equipped with 21-pin scart connectors which can accept via scart the SVHS format from VCRs so equipped.

. SMALL SIGNAL PART WITH TDA884X

The TDA8840/8842 combine all small signal functions required for a colour TV receiver, except tuning.

2.1. Vision IF amplifier

The IF-amplifier contains 3 AC-coupled control stages with a total gain control range which is higher than 66dB.

The sensitivity of the circuit is comparable with that of modern IF-IC s. The video signal is demodulated by means of a PLL

carrier regenerator. This circuit contains a frequency detector and a phase detector. The AFC output is obtained by using the

VCO control voltage of the PLL and can be read via the I²C-bus. For fast search tuning systems the window of

the AFC can be increased with a factor 3. The setting is realised with the AFW bit.

Depending on the type the AGC-detector operates on top-sync level (single standard versions) or on top sync and top

white-level (multi standard versions). The demodulation polarity is switched via the I²C-bus. The AGC detector time-constant capacitor

is connected externally. This mainly because of the flexibility of the application. The time-constant of the AGC system during positive

modulation is rather long to avoid visible variations of the signal amplitude. To improve the speed of the AGC system a circuit has

2

been included which detects whether the AGC detector is activated every frame period. When during 3 frame periods no action is

detected the speed of the system is increased. For signals without peak white information the system switches automatically to a

gated black level AGC. Because a black level clamp pulse is required for this way of operation the circuit will only switch to black level

AGC in the internal mode.

The circuits contain a video identification circuit which is independent of the synchronisation circuit. Therefore search tuning is

possible when the display section of the receiver is used as a monitor. The ident output is supplied to the tuning system via

the I²C-bus. The video ident circuit can be made less sensitive by means of the STM bit. This mode can be used during search

tuning to avoid that the tuning system will stop at very weak input signals.

2.2. Video Switches

The circuits have two CVBS inputs (internal and external CVBS) and Y/C input. When the Y/C input is not required the Y input can be

used as third CVBS input. The selection of the various sources is made via the I²C-bus. The circuit has one CVBS output.

2.3. Sound Circuit

The sound band pass and trap filters have to be connected externally. The filtered intercarrier signal is fed to a limiter circuit

and is demodulated by means of a PLL demodulator. This PLL circuit tunes itself automatically to the incoming carrier signal

so that no adjustment is required.

The volume is controlled via the I²C-bus. The deemphasis capacitor has to be connected externally. The non-controlled audio

signal can be obtained from this pin. The FM demodulator can be muted via the I²C-bus. This function can be used to switch-off

the sound during a channel change so that high output peaks are prevented. The TDA8840/8842 contain an automatic volume

levelling (AVL) circuit which automatically stabilises the audio output signal to a certain level which can be set by the viewer by means

of the volume control. This function prevents big audio output fluctuations due to variations of the modulation depth of the transmitter.

The AVL function can be activated via the I²C-bus.

2.4. Synchronisation circuit

The sync seperator is preceded by a controlled amplifier which adjusts the sync pulse amplitude to a fixed level. These pulses are fed

to the slicing stage which is operating at 50% of the amplitude. The separated sync pulses are fed to the first phase detector and to the

coincidence detector. This coincidence detector is used to detect whether the line oscillator is synchronised and can also be used for

transmitter identification. The first PLL has a very high statical steepness so that the phase of the picture is independent of the line

frequency.

The horizontal output signal is generated by means of an oscillator which is running at twice the line frequency. Its frequency is divided

by 2 to lock the first control loop to the incoming signal. The time-constant of the loop can be forced by the I²C-bus (fast or slow).

If required the IC can select the time-constant depending on the noise content of the incoming video signal.

To protect the horizontal output transistor, the horizontal drive is immediately switched off when a power-on-reset is detected.

The drive signal is switched-on again when the normal switch-on procedure is followed.

Via the I²C-bus, adjustments can be made of the horizontal and vertical geometry. The vertical sawtooth generator drives the

vertical output drive circuit which has a differrential output current. For the EW drive a single ended current output is available.

When the horizontal scan is reduced to display 4 : 3 pictures on a 16 : 9 picture tube an accurate video blanking can be switched on

to obtain well defined edges on the screen.

Overvoltage conditions can be detected via the EHT tracking pin.When an overvoltage condition is detected the horizontal output

drive signal will be switched-off via the slow stop procedure but it is also possible that the drive is not switched-off and that just a

protection indication is given in the I²C-bus output byte. The choice is made via the input bit PRD.

2.5. Chroma and Luminance processing

The circuits contain a chroma bandpass and trap circuit. The filters are realised by means of gyrator circuits and they are

automatically calibrated by comparing the tuning frequency with the X-tal frequency of the decoder.

The luminance delay line and the delay for the peaking circuit are also realised by means of gyrator circuits.

The centre frequency of the chroma bandpass filter is switchable via the I²C-bus so that the performance can be optimised for

front-end signals and external CVBS signals.

During SECAM reception the centre frequency of the chroma trap is reduced to get a better suppression of the SECAM

carrier frequencies.

2.6. Colour Decoder

The decoder contains an alignment-free X-tal oscillator, a killer circuit and two colour difference demodulators. The 90° phase shift for

the reference signal is made internally.

The IC contains an automatic colour limiting (ACL) circuit which prevents that oversaturation occurs when signals with a high

chroma-to-burst ratio are received. The ACL circuit is designed such that it only reduces the chroma signal and not the burst signal.

This has the advantage that the colour sensitivity is not affected by this function.

The base-band delay line is integrated in the PAL/SECAM IC s.

The demodulated colour difference signals are internally supplied to the delay line. The matrixed signals are externally available.

The colour difference matrix switches automatically between

PAL/SECAM and NTSC, however, it is also possible to fix the matrix in the PAL standard.

Which colour standard the IC can decode depends on the external X-tals. The X-tal to be connected to pin 34 must have a frequency

of 3.5 MHz (NTSC-M, PAL-M or PAL-N) and pin 35 can handle X-tals with a frequency of 4.4 and 3.5 MHz. To prevent calibration

problems of the horizontal oscillator the external switching between the 2 X-tals should be carried out when the oscillator is forced to

pin 35. For a reliable calibration of the horizontal oscillator it is very important that the X-tal indication bits (XA and XB) are not

corrupted. For this reason the X-tal bits can be read in the output bytes so that the software can check the I²C-bus transmission.

2.7. RGB output circuit and black-current stabilisation

The colour-difference signals are matrixed with the luminance signal to obtain the RGB-signals. The TDA 884X device has one linear

RGB input. This RGB signal can be controlled on contrast and brightness.

The output signal has an amplitude of about 2 volts black-to-white at nominal input signals and nominal settings of the controls.

To increase the flexibility of the IC it is possible to insert OSD and/or teletext signals directly at the RGB outputs.

This insertion mode is controlled via the insertion input (pin 26 in the S-DIP 56- and pin 38 in the QFP-64 level). This blanking action

at the RGB outputs has some delay which must be compansated externally.

To obtain an accurate biasing of the picture tube a Continuous Cathode Calibration circuit has been developed.

This function is realised by means of a 2-point black level stabilisation circuit.

When the TV receiver is switched-on, the RGB output signals are blanked and the black current loop will try to set the right picture

tube bias levels.Via the AST bit a choice can be made between automatic start-up or a start-up via the m-processor.

3

3. TUNER

Either a PLL tuner is used as a tuner.

Channel coverage of PLL:

BAND

Low Band E2 to C 48.25 to 82.25 (1) S01 to S08 69.25 to 154.25

Mid Band E5 to E12 175.25 to 224.25 S09 to S38 161.25 to 439.25

High Band E21 to E69 471.25 to 855.25 (2) S39 to S41 447.25 to 463.25

(1). Enough margin is available to tune down to 45.25 MHz.

(2). Enough margin is available to tune up to 863.25 MHz.

OFF-AIR CHANNELS CABLE CHANNELS

CHANNELS FREQUENCY CHANNELS FREQUENCY

RANGE (MHz) RANGE (MHz)

Noise Typical Max. Gain Min. Typical Max.

Low band : 5dB 9dB All channels : 38dB 44dB 52dB

Mid band : 5dB 9dB Gain Taper (of-air channels) : - - 8dB

High band : 6dB 9dB

4.VIDEO SWITCH TEA6415C

In case of three or more external sources are used, the video switch IC TEA6415C is used. The main function of this device is to switch

8 video input sources on the 6 outputs.

Each output can be switched on only one of each input. On each input an alignment of the lowest level of the signal is made (bottom

of sync. top for CVBS or black level for RGB signals).

Each nominal gain between any input and output is 6.5dB.For D2MAC or Chroma signal the alignment is switched off by forcing, with

an external resistor bridge, 5VDC on the input. Each input can be used as a normal input or as a MAC or Chroma input (with external

resistor bridge). All the switching possibilities are changed through the BUS.

Driving 75ohm load needs an external resistor.

It is possible to have the same input connected to several outputs.

Sound IF Input:

The sound IF amplifier consists of three AC-coupled differential amplifier stages each with approximately 20dB gain.

At the output of each stage is a multiplier for gain controlling. The overall control range is approximately -6 to +60dB and the

frequency response (-3dB) of the IF amplifier is approximately 6 to 70MHz. The steepness of gain control is approximately 10mV/dB.

IF AGC:

The automatic gain control voltage to maintain the AM demodulator output signal at a constant level is generated by a mean

level detector.The AGC-detector charges and discharges the capacitor at pin 3 controlled by the output signal of the

AM-demodulator compared to an internal reference voltage.The maximum charge/discharge current is approximately 5 mA.

AM-demodulator

The IF amplifier output signal is fed to a limiting amplifier (two stages) and to a multiplier circuit.

However the limiter output signal (which is not any more AM modulated) is also fed to the multiplier, which provides AM

demodulation (in phase demodulation). After lowpass filtering (fg @ 400kHz) for carrier rejection and buffering,

the demodulator output signal is present at pin 6.

Audio Switch

This circuit is an operational amplifier with three input stages and internal feedback network determining gain (0dB) and

frequency response (fg @ 700kHz). Two of the input stages are connected to pin 7 and pin 9, the third input stage to an

internal reference voltage. Controlled by the switching pins 10 and 12, one of the three input stages can be activated and a

choice made between two different AF signals or mute state. The selected signal is present at pin 8. The decoupling capacitors

at the input pins are needed, because the internally generated bias voltage for the input stages must not be influenced

by the application in order to avoid DC-plop in case of switching.

Reference Circuit:

This circuit is a band gap stabiliser in combination with a voltage regulation amplifier, which provides an internal reference voltage

of about 3.6V nearly independent from supply voltage and temperature. This reference voltage is filtered by the capacitor at

pin 4 in order to reduce noise. It is used as a reference to generate all important voltages and currents of the circuit.

For application in 12V power supply concepts, there is an internal voltage divider in combination with a Darlington transistor in

order to reduce the supply voltage for all IC function blocks to approximately 6V.

Description of the demodulator and decoder section:

SIF Input:

Two input pins are provided, SIF1 e.g. for terrestrial TV and SIF2 e.g. for a satellite tuner. The selected signal is passed through an

AGC circuit and then digitized by an 8-bit ADC operating at 24.576MHz.

AGC:

The gain of the AGC amplifier is controlled from the ADC output by means of a digital control loop employing hysteresis.

The AGC has a fast attack behaviour to prevent ADC overloads and slow decay behaviour AGC oscillations.

For AM demodulation AGC must be switched off.

Mixer

The digitized input signal is fed to the mixers, which mix one or both input sound carriers down to zero IF. A 24-bit control word for

each carrier sets the required frequency.

4

FM and AM Demodulation

An FM or AM input signal is fed via a band-limiting filter to a demodulator that can be used for either FM or AM demodulation.

Apart from the standard (fixed) de-emphasis characteristic, an adaptive de-emphasis is available for encoded satellite programs.

A stereo decoder recovers the left and right signal channels from the demodulated sound carriers.

FM Identification:

The identification of the FM sound mode is performed by AM synchronous demodulation of the pilot signal and narrow-band

detection of the identification frequencies. The result is available via the I²C-bus interface.

NICAM Demodulation:

The NICAM signal is transmitted in a DQPSK code at a bit rate of 728 kbit/s. The NICAM demodulator performs DQPSK

demodulation and feeds the resulting bitstream and clock signal onto the NICAM decoder and, for evaluation purposes, to PCLK

(pin 1) and NICAM (pin 2).

NICAM Decoder:

The device performs all decoding functions in accordance with the EBU NICAM 728 specification. After locking to the frame

alignment word, the data is descrambled by applying the defined pseudo-random binary sequence; the device will then synchronise

to the periodic frame flag bit C0.

The status of the NICAM decoder can be read out from the NICAM status register by the user. The OSB bit indicates that the

decoder has locked to the NICAM data. The VDSP bit indicates that the decoder has locked to the NICAM data and that the

data is valid sound data.

5. SOUND OUTPUT STAGE TDA2614/TDA2615

TDA2614 is used as the AF output amplifier for mono applications. It is supplied by ±12VDC coming from a separate winding in the

SMPS transformer. An output power of 2*6W (THD=0.5%) can be delivered into an 8ohm load.

TDA2615 is used as the AF output amplifier for stereo applications. It is supplied by

±12VDC coming from a separate winding in the SMPS transformer. An output power of 2*6W (THD=0.5%)

can be delivered into an 8ohm load.

6. VERTICAL OUTPUT STAGE WITH TDA8356

The TDA8356 vertical deflection circuit can be used in 90° deflection systems with field frequencies from

50 up to 120Hz. With its bridge configuration the deflection output can be DC coupled with few external components.

Only a single supply voltage for the scan and a second supply for the flyback are needed.

The drive voltage is amplified by an amplifier and fed to two amplifiers, one is inverting and the other is a non inverting amplifier.

The outputs (pins 7 and 4) are connected to the series connection of the vertical deflection coil and feedback resistor Rsense

(R702//R703). The voltage across Rsense is fed via pin 9 to correction amplifier, to obtain a deflection current which is proportional

to the drive voltage. The supply voltage for the TDA8356 is 15VDC at pin 3. The supply voltage generator has a separate

supply voltage of 45VDC at pin 6.

7. VIDEO OUTPUT AMPLIFIER TDA6107Q

The TDA6107Q consists of three monolithic video output amplifiers. The amplifier can be seen as an operational amplifier

with negative feedback.

The advantage of negative feedback is that the amplifier characteristics do not play an important role up to certain frequencies.

The internal flash diodes protect the amplifiers against flash over in the picture tube.

The only protections required at the cathode outputs are a flash resistor and a sparkgap.

The TDA6107Q has an internal thermal protection circuit which gives a decrease of the slew rate at high temperatures.

Furthermore, the device needs only one power supply voltage (Vdd).

In contrast to previous types of DMOS video amplifiers, all the external resistors (Rf, Ri and Ra) are integrated, so the gain is fixed

and saves 9 resistors.

Furthermore, the reference voltage is integrated, it saves a resistor divider and a decoupling capacitor. So, the replacement

value of the TDA6107Q is very high.

The TDA6107Q is provided with a black current data pin. Since TDA884X is used as drive device, no adjustments are required

for gain and black setting, as the TDA884X has I²C white point adjustment and black current set-up.

8. POWER SUPPLY (SMPS)

The DC voltages required at various parts of the chassis are provided by an SMPS transformer controlled by the IC MC44604

which is designed for driving, controlling and protecting switching transistor of SMPS. The transformer produces 150/115V for

FBT input, ±14V for audio output IC, S+5V for microcontroller, +15V for vertical output (field scan) and +33V for tuner and some

other ICs and transistors.

9. MICROCONTROLLER SDA545XOTP

The device is TV TEXT tuning and control system based on the SDA 525X TV TEXT microcontroller. It is designed for a low

cost mono TV-SET with analogue picture and sound control. Neverthless the system offers an on screen display (OSD) and

IR remote control of all functions.

SDA545X has the following features:

- Display of program number, channel number, TV standard, analogue values, sleep timer, parental control, and mute is done by

OSD.

- Single LED for IR active, standby and on mode indication.

- 1 Control line to select external source.

- 3 Control lines for TV standard selection.

- Frequency synthesis tuning (62.5 kHz steps)

- 192 step fine tuning

- Channels corresponding to standards B/G, OIRT, L and I (I+)

- Mono sound control by analogue voltage

- System configuration with service mode

5

10. SERIAL ACCESS CMOS 8K (1024*8) EEPROM ST24C08

The ST24C08 is a 8Kbit electrically erasable programmable memory (EEPROM), organised as 4 blocks of 256*8 bits.

The memory is compatible with the I²C standard, two wire serial interface which uses a bi-directional data bus and serial clock.

The memory carries a built-in 4 bit, unique device identification code (1010) corresponding to the I²C bus definition.

This is used together with 1 chip enable input (E) so that up to 2*8K devices may be attached to the I²C bus and selected individually.

11. CLASS AB STEREO HEADPHONE DRIVER

The TDA1308 is an integrated class AB stereo headphone driver contained in a DIP8 plastic package.

The device is fabricated in a 1 mm CMOS process and has been primarily developed for portable digital audio applications.

16. SAW FILTERS

Saw filter type : Model:

G1965M : PAL-SECAM B/G MONO

G3962M : PAL-SECAM B/G GER&NIC STEREO, PAL I NIC STEREO, INT-1

G1984 : PAL-SECAM B/G GER&NIC STEREO INT-2

J1951M : PAL-I MONO

J3950M : PAL-I NIC STEREO

J1956M : PAL-I MONO

K2955M : PAL-SECAM B/G-D/K MONO, PAL-SECAM B/G-D/K-I, MONO, PAL-SECAM B/G-D/K-L MONO

K2958M : PAL-SECAM B/G-D/K (38) MONO

K2962M : PAL-SECAM B/G-L/L MONO

G3957M : PAL-SECAM B/G-L/L GER&NIC BG/L STEREO

K6256K : PAL-SECAM B/G-D/K-I-L/L MONO, PAL-SECAM B/G-D/K-I, L/L GER&NIC BG/L STEREO,

PAL-SECAM B/G-D/K-I-L/L I, NICAM STEREO, PAL-SECAM B/G-D/K-I-L/L GER&NIC I-B/G-L, STEREO

K6259K : PAL-SECAM B/G-D/K-I-M/N (EURO) MONO

M1963M : PAL M/N MONO, NTSC M MONO, PAL M/N-NTSC M MONO

IC DESCRIPTIONS AND INTERNAL BLOCK DIAGRAM

n TDA8840/8842

n TUNER

n TEA6415C

n TDA2614/2615

n TDA8356

n TDA6107Q

n MC44604

n SDA545X

n ST24C08

n TDA1308

TDA1308

TDA8840/8842

The TDA884X is IýC-bus controlled single chip TV processor which is intended to be applied in PAL, NTSC, PAL/NTSC and

multi-standard television receivers. These IC s are nearly pin compatible with the TDA837X TV processors but have a higher

degree of integration because the delay line (TDA4665 function) and the SECAM decoder have been integrated. In addition to

these functions some additional features have been added like Continuous Cathode Calibration (2-point black current loop

which results in an accurate biasing of the 3 guns), adjustable luminance delay time, blue stretching and dynamic skin tone control.

Features:

n Vision IF circuit with PLL demodulator

n Alignment-free multi-standard FM sound demodulator (4.5 MHz to 6.5 MHz)

n Audio switch

n Flexible source selection with CVBS switch and Y(CVBS)/C input so that a comb filter can be applied

n Integrated chrominance trap circuit

n Integrated luminance delay line

n Asymmetrical peaking in the luminance channel with a noise coring function

n Black stretching of non-standard CVBS or luminance signals

n Integrated chroma band-pass filter with switchable center frequency

n Blue stretch circuit which offsets colours near white towards blue

n RGB control circuit with Continuous Cathode Calibration and white point adjustment

n Linear RGB inputs and fast blanking

n Possibility to insert a blue black option when no video signal is available

n Horizontal synchronisation with two control loops and alignment-free horizontal oscillator

n Vertical count-down circuit

n Vertical driver optimised for DC-coupled vertical output stages

n IýC-bus control of various functions

n Low dissipation (850 mW)

Functional Differences between the 8840/8842 :

6

IC VERSION (TDA) 8840 8842

Multi-standard IF X

Automatic Volume Limiting X X

PAL Decoder X X

SECAM Decoder X

NTSC Decoder X

Dynamic Skin Control

Colour Matrix PAL/NTSC (Japan) X

Colour Matrix NTSC Japan/USA

YUV interface

Base-band delay line X X

Adjustable luminance delay time

Horizontal geometry

Horizontal and vertical zoom

Vertical scroll

PINNING PIN VALUE

1. Sound IF input : 1mVrms

2. External audio input : 500mVrms

3. IF demodulator tuned circuit 1

4. IF demodulator tuned circuit 2

5. IF-PLL loop filter : Min:32-Max:60 MHz

6. IF video output : 4.7V (Negative Modulation), 2V (Positive Modulation)

7. Serial clock input : Low level max:1.5 V, High level min 3.5V

8. Serial data input/output : Low level max:1.5 V, High level min 3.5V

9. Bandgap decoupling

10. Chrominance input (S-VHS) : 1Vpp, Max:1.4Vpp

11. External CVBS/Y input : 1Vpp, Max:1.4Vpp

12. Main supply voltage 1 : 8V, Min:7.2V, Max:8.8V

13. Internal CVBS input : 1Vpp, Max:1.4Vpp

14. Ground 1

15. Audio output : 700mVrms, Min:500mVrms, Max:900mVrms

16. SECAM PLL decoupling

17. External CVBS input : Vpp, Max:1.4Vpp

18. Black-current input : Amplitude of low reference current : 8mA

Amplitude of high reference current : 20mA

19. Blue output : 2Vpp

20. Green output : 2Vpp

21. Red output : 2Vpp

22. Beam current limiter input/V-guard input

23. Red input for insertion : 0.7Vpp, Max:0.8Vpp

24. Green input for insertion : 0.7Vpp, Max:0.8Vpp

25. Blue input for insertion : 0.7Vpp, Max:0.8Vpp

26. RGB insertion input : Max:0.3V

27. Luminance input : 1.4Vpp

28. Luminance output : 1.4Vpp

29. (B-Y) signal output : 1.05Vpp

30. (R-Y) signal output : 1.05Vpp

31. (B-Y) signal input : 1.05Vpp

32. (R-Y) signal input : 1.05Vpp

33. Subcarrier reference output : 3.58/4.43 MHz

34. 3.58 MHz crystal connection

35. 4.43/3.58 MHz crystal connection

36. Loop filter phase detector

37. 2nd

supply voltage 1 : 8V, Min:7.2V, Max:8.8V

38. CVBS output : 1Vpp, Max:1.4Vpp

39. Decoupling digital supply : 1.8V

40. Horizontal output : Max: 0.3V

41. Flyback input/sandcastle output : Min:100ma, Max:300mA

42. Phase-2 filter : 150 ms/ms

43. Phase-1 filter : ±0.9 kHz, Max: ±1.2 kHz

44. Ground 2

45. East-west drive output

46. Vertical drive A output : 0.95mA

47. Vertical drive B output : 0.95mA

48. IF input 1

49. IF input 2

50. EHT/overvoltage protection input : Min:1.2V, Max : 2.8V

51. Vertical sawtooth capacitor : 3Vpp

52. Reference current input : 3Vpp

53. AGC decoupling capacitor

54. Tuner AGC output : Max:9V (Maximum tuner AGC

output voltage), 300mV (Output saturation voltage)

55. Audio deemphasis : 500mVrms

56. Decoupling sound demodulator

7

Loading...

Loading...