Page 1

ReferenceReference

ManualManual

VL-12CT96

VL-12CT97

VL-12CT98

Analog & Digital Input/Output

Card for the STD 32 Bus

Page 2

ii VL-12CT96/7 Analog & Digital I/O Card

Page 3

Table of Contents

Table of Contents

1. Overview

Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

2. Configuration

Jumper Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

VL-12CT96/7 Jumper Block Locations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

VL-12CT96/7 Jumper Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

Board Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

8-Bit Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

16-Bit Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

IOEXP Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Data Bus Width. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

Analog Input Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Single Ended Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

Pseudo-Differential Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

Differential Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Current Loop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-11

Input Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

Settling Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Low Pass Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-13

Input Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-14

Analog Output Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Output Voltage Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Output Local/Remote Sense. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-15

Output Current Loop Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

Output Voltage Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

5B01 Analog Signal Conditioning Rack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Digital Input/Output Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Rack Power Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-17

Digital I/O Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Edge Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

Interrupt Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-19

3. Installation

Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Signal Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

Priority Chain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

External Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

J1 — Analog Input Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

J2 — Analog Output Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

J3 — Digital I/O Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

VL-12CT96/7 Analog & Digital I/O Card iii

Page 4

Table of Contents

4. Registers

Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

I/O Port Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Analog Input Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Analog InputWrite Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

Channel Select Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

Convert Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Clear Flags Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Analog Input Read Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

Analog Input Data Low Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Analog Input Data High Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

Analog Input Data Representation (VL-12CT96, 12-Bit) . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Analog Input Data Representation (VL-12CT97, 16-Bit) . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

Analog Output Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

Analog Output Data Low Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

Analog Output Data High Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

Analog Output Data Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

Parallel Port Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Signal Direction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Parallel Port Data High Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

Parallel Port Data Low Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

5. Operation

Analog Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Polled Mode Analog Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

Interrupt Mode Analog Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

Analog Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Digital I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Signal Direction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

Signal Inversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Digital Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Interrupt Mode Digital Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

Digital Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

System Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

6. Software Examples

Analog Input Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

Analog Input Interrupt Mode Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

Analog Output Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

Parallel Port Code Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

Parallel Port Interrupt Mode Code Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

7. Calibration

Analog Input Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

Analog Output Calibration (Voltage Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

Analog Output Calibration (Current Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

8. Reference

STD 80 Bus Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

STD 32 Bus Pinout Extension . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-2

VL-12CT96/7 Parts Placement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

VL-12CT96/7 Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

VL-12CT96/7 Parts List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

iv VL-12CT96/7 Analog & Digital I/O Card

Page 5

Overview

Overview

This manual details the installation and operation of VersaLogic’s VL-12CT96 and VL-12CT97

multifunction I/O cards. The VL-12CT96/7 cards include analog input, analog output, digital I/O, and

extended temperature operation. The VL-12CT96 has a 12-bit analog input converter, while the VL12CT97 has a 16-bit converter.

Introduction

The VL-12CT96/7 provides 16 single-ended, or 8 differential analog input channels (12-bit resolution

for the VL-12CT96 or 16-bit resolution for the VL-12CT97). Four of the input channels may optionally

be configured for current loop input. The cards feature fast 10 µs conversion times, and on-board DC

to DC converters (requires +5 volt supply only). They operate with input ranges of ±5 volts or ±10 volts

(also ±50 mv or ±100 mv on the VL-12CT96). They can accommodate input signals in single-ended,

differential, or pseudo-differential configurations. Throughput up to 100KHz may be realized on these

cards.

The VL-12CT96/7 cards also include two 12-bit analog output channels. These channels may be

jumpered for ±5 volt or ±10 volt output at 5 ma. One channel may optionally be converted to a 4-20

ma output.

In addition to the analog sections, these cards also include 16 digital I/O lines. These digital lines

feature open-collector outputs with readback and are compatible with optically isolated modular I/O

racks.

Features

Analog Input:Analog Input:

•

Analog Input:

Analog Input:Analog Input:

8 Differential or 16 Single-Ended Input Channels

12-bit (VL-12CT96) or 16-bit (VL-12CT97) Resolution

±5V and ±10V Input Ranges

±50 mv and ±100 mv optional range on the VL-12CT96

Current Loop Input Option (4 channels)

Selectable Low Pass Filter

10 Microsecond Conversion Time

Auto Channel Increment Mode

Interrupt Support

5B01 Compatible Pinout

Analog Output:Analog Output:

•

Analog Output:

Analog Output:Analog Output:

2 Output Channels

12-bit Resolution

Independent ±5V and ±10V Output Ranges

Current Loop Option (1 Channel)

Digital Input/Output:Digital Input/Output:

•

Digital Input/Output:

Digital Input/Output:Digital Input/Output:

16 Channel Opto 22 Compatible

Interrupt Support

Opto 22 Compatible Pinout

TTL Compatible

Extended Temperature OperationExtended Temperature Operation

•

Extended Temperature Operation

Extended Temperature OperationExtended Temperature Operation

STD 32 (8- or 16-Bit Data), STD 80, STD Z80 CompatibleSTD 32 (8- or 16-Bit Data), STD 80, STD Z80 Compatible

•

STD 32 (8- or 16-Bit Data), STD 80, STD Z80 Compatible

STD 32 (8- or 16-Bit Data), STD 80, STD Z80 CompatibleSTD 32 (8- or 16-Bit Data), STD 80, STD Z80 Compatible

VL-12CT96/7 Analog & Digital I/O Card 1-1

Page 6

Overview

Specifications

Specifications are typical at 25°C with 5.0V supply unless otherwise noted.

Size:Size:

Size: Meets all STD & STD 32 Bus mechanical specifications

Size:Size:

Storage Temperature:Storage Temperature:

Storage Temperature: –40°C to +85°C

Storage Temperature:Storage Temperature:

Free Air Operating Temperature:Free Air Operating Temperature:

Free Air Operating Temperature: –25°C to +85°C

Free Air Operating Temperature:Free Air Operating Temperature:

Power Requirements:Power Requirements:

Power Requirements: 5V ±5% @ 485 mA typ.

Power Requirements:Power Requirements:

Analog Input:Analog Input:

Analog Input:

Analog Input:Analog Input:

16 single ended or 8 differential channels

±50 mv, ±100 mv, ±5V, ±10V ranges

Resolution:

VL-12CT96: 12-bit, no missing codes

VL-12CT97: 16-bit, no missing codes

Accuracy (±5V or ±10V ranges):

VL-12CT96: ±0.022%

VL-12CT97: ±0.003%

10 µs conversion time

5 µs or 10µs settling time

±35 volt input overvoltage protection

.6 x 108 Ω input impedance

2.5 µA input bias current

±12 volt common-mode range

89 dB common-mode rejection (gain=1)

Analog Output:Analog Output:

Analog Output:

Analog Output:Analog Output:

2 channels

±5V or ±10V ranges

1 optional current loop output

15 µs settling time

Resolution: 12-bit

Accuracy: ±0.024%

5 ma maximum output current (per channel)

Digital I/O:Digital I/O:

Digital I/O:

Digital I/O:Digital I/O:

16 lines

Open collector

.7V maximum @ 12 ma low level output

Analog Temperature Coefficients:Analog Temperature Coefficients:

Analog Temperature Coefficients:

Analog Temperature Coefficients:Analog Temperature Coefficients:

Gain ±25 ppm/°C of FSR

Offset ±10 ppm/°C of FSR

Addressing: Addressing:

Addressing: I/O, 8- or 16-bits plus IOEXP

Addressing: Addressing:

Mapping: Mapping:

Mapping: 16-byte block on any 16-byte boundary

Mapping: Mapping:

Bus Compatibility:Bus Compatibility:

Bus Compatibility:

Bus Compatibility:Bus Compatibility:

STD Z80: Full compliance, all bus speeds

STD 80: Full compliance, all bus speeds

STD 32: I/O slave, SA16, SA8-I, IX

Specifications are subject to change without notice.

1-2 VL-12CT96/7 Analog & Digital I/O Card

Page 7

Configuration

Configuration

Jumper Options

Various options available on the VL-12CT96/7 cards are selected using removable jumper blocks

(shorting plugs). Features are selected or deselected by installing or removing the jumpers as noted.

The terms “In” or “Jumpered” are used to indicate an installed plug; “Out” or “Open” are used to indicate

a removed plug.

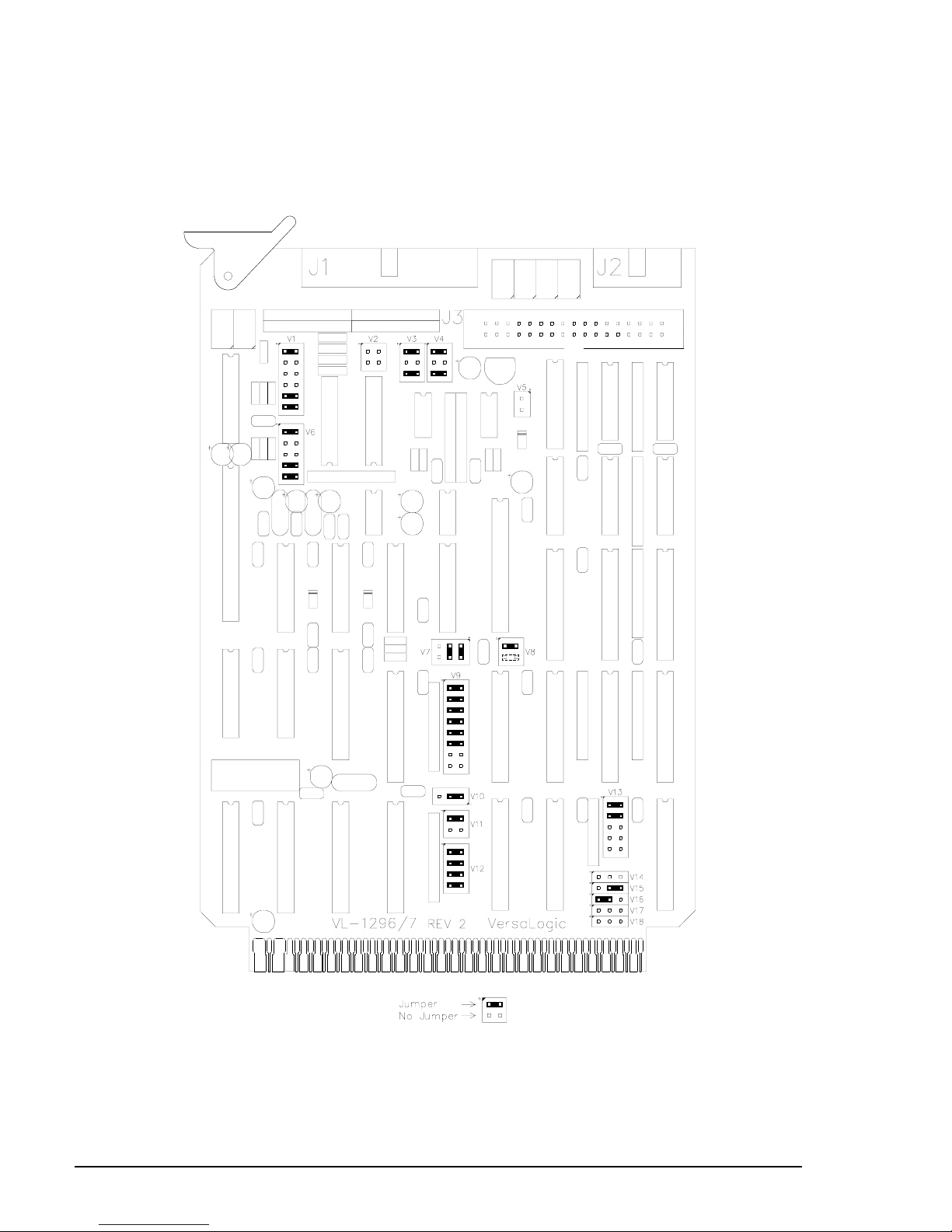

Figure 2-1 shows the jumper block locations on the VL-12CT96/7 card. The figures indicate the position

of the jumpers as shipped from the factory.

VL-12CT96/7 Analog & Digital I/O Card 2-1

Page 8

Configuration — Jumper Block Locations

VL-12CT96/7 Jumper Block Locations

Figure 2-1. Jumper Block Locations for VL-12CT96/7

2-2 VL-12CT96/7 Analog & Digital I/O Card

Page 9

Configuration — Jumper Options

VL-12CT96/7 Jumper Options

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

DescriptionDescription

Description

DescriptionDescription

V1[1-2] Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Single Ended 2-8

In –Single-Ended or Pseudo-Differential

Out – Differential

V1[3-4] Input Gain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Normal 2-12

In – x100

Out – Normal

V1[5-6] Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Single Ended 2-8

In – Pseudo-Differential

Out – Single-Ended or Differential

V1[7-8] Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Single Ended 2-8

In – Differential

Out – Single-Ended or Pseudo-Differential

V1[9-10] Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Single Ended 2-8

In – Single-Ended

Out – Differential or Pseudo-Differential

V1[11-12] Differential Bias Resistor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . In Circuit 2-10

In –In Circuit

Out – Disconnected

V2[1-2] Analog Loopback (Channel 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Independent 2-16

In –Connects DAC 0 output to ADC 0 input for diagnostic loopback

Out – Circuits operate independently

V2[3-4] Analog Loopback (Channel 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Independent 2-16

In –Connects DAC 1 output to ADC 1 input for diagnostic loopback

Out – Circuits operate independently

V3[1-2] DAC Channel 0 Remote Sense (IR Drop Compensation) . . . . . . . . . . . . . . . . . . . . . Local sense 2-15

In –Local sense (no compensation)

Out – Remote sense

V3[3-4] Channel 0 Output Range (±5 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V 2-15

In –±5 Volts

Out – ±10 Volts

V3[5-6] Channel 0 Output Range (±10 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V 2-15

In –±10 Volts

Out – ±5 Volts

V4[1-2] DAC Channel 1 Remote Sense (IR Drop Compensation) . . . . . . . . . . . . . . . . . . . . . Local Sense 2-15

In –Local sense (no compensation)

Out – Remote sense

V4[3-4] Channel 1 Output Range (±5 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V 2-15

In –±5 Volts

Out – ±10 Volts

V4[5-6] Channel 1 Output Range (±10 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V 2-15

In –±10 Volts

Out – ±5 Volts

V5 Opto-22 I/O Rack Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . External 2-17

In –I/O rack power provided locally

Out – I/O rack power provided externally

V6[1-8] Input Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V 2-12

[1-2] & [7-8] In – ±10 Volts

[3-4] & [5-6] In – ±5 Volts

V6[9-10] Input Low Pass Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Enabled 2-13

In – Enabled

Out – Disabled

V7[1-2] Input Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Single Ended 2-8

In –Single-Ended or Pseudo-Differential

Out – Differential

V7[3-4] 5 µs Settling Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Enabled 2-13

In – Enabled

Out – Disabled

V7[5-6] 10 µs Settling Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled 2-13

In – Enabled

Out – Disabled

V8[1-2] Data Bus Width . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-Bit 2-14

In –8-Bit Data Bus

Out – 16-Bit Data Bus

V8[3-4] Analog Input Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Varies 2-14

In –16-Bit Resolution (VL-12CT97 only)

Out – 12-Bit Resolution (VL-12CT96 only)

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

PagePage

Page

PagePage

VL-12CT96/7 Analog & Digital I/O Card 2-3

Page 10

Configuration — Jumper Options

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

DescriptionDescription

Description

DescriptionDescription

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

PagePage

Page

PagePage

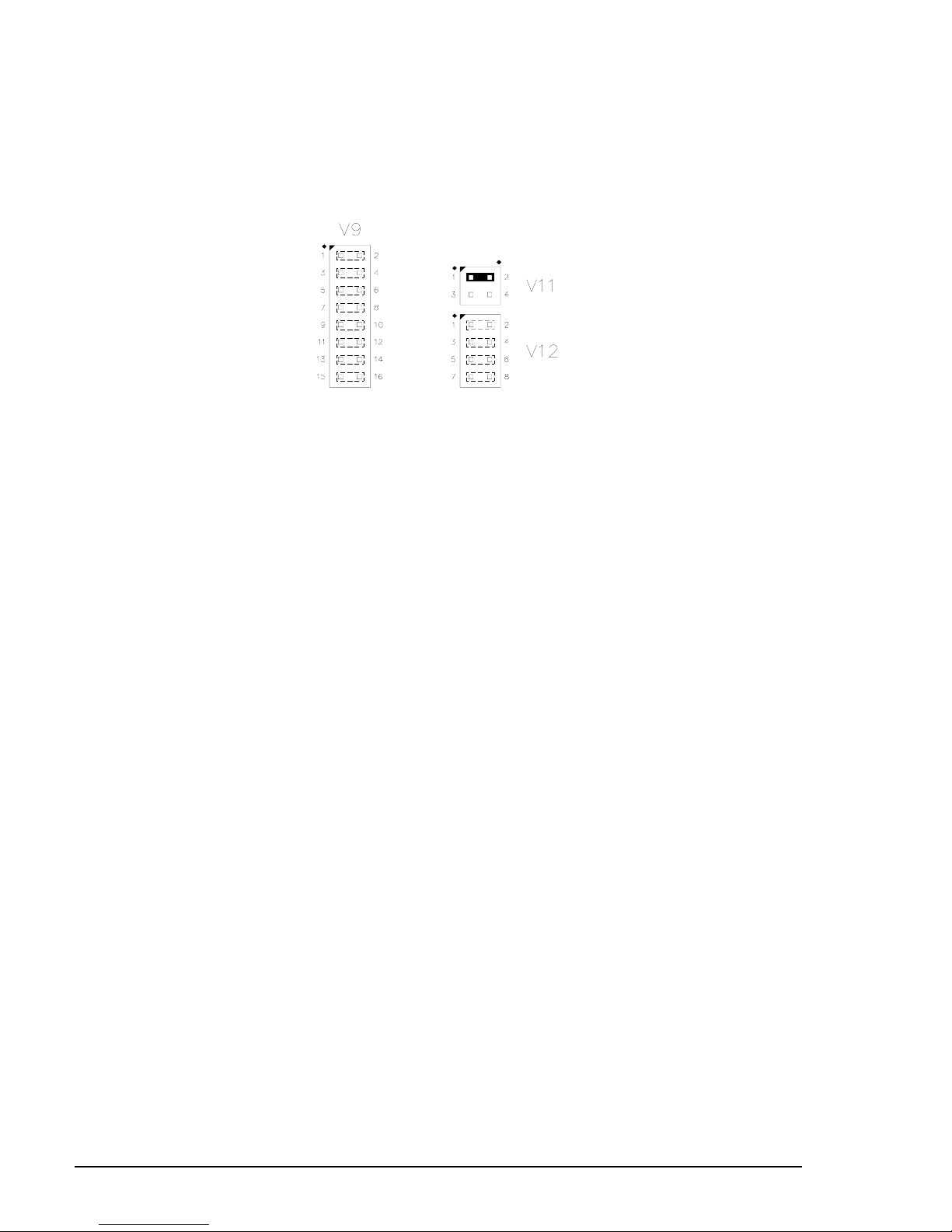

V9 Board Address (A8 – A15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0300H 2-6

[1-2] = In – A15 Decoded Low [1-2] = Out – A15 Decoded High

[3-4] = In – A14 Decoded Low [3-4] = Out – A14 Decoded High

[5-6] = In – A13 Decoded Low [5-6] = Out – A13 Decoded High

[7-8] = In – A12 Decoded Low [7-8] = Out – A12 Decoded High

[9-10] = In – A11 Decoded Low [9-10] = Out – A11 Decoded High

[11-12] = In – A10 Decoded Low [11-12] = Out – A10 Decoded High

[13-14] = In – A9 Decoded Low [13-14] = Out – A9 Decoded High

[15-16] = In – A8 Decoded Low [15-16] = Out – A8 Decoded High

V10 IOEXP Select. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IOEXP Ignored 2-7

[1-2] = In – Board responds to IOEXP high and low (IOEXP ignored)

[2-3] = In – Board responds to IOEXP low

[Both] = Out – Board responds to IOEXP high

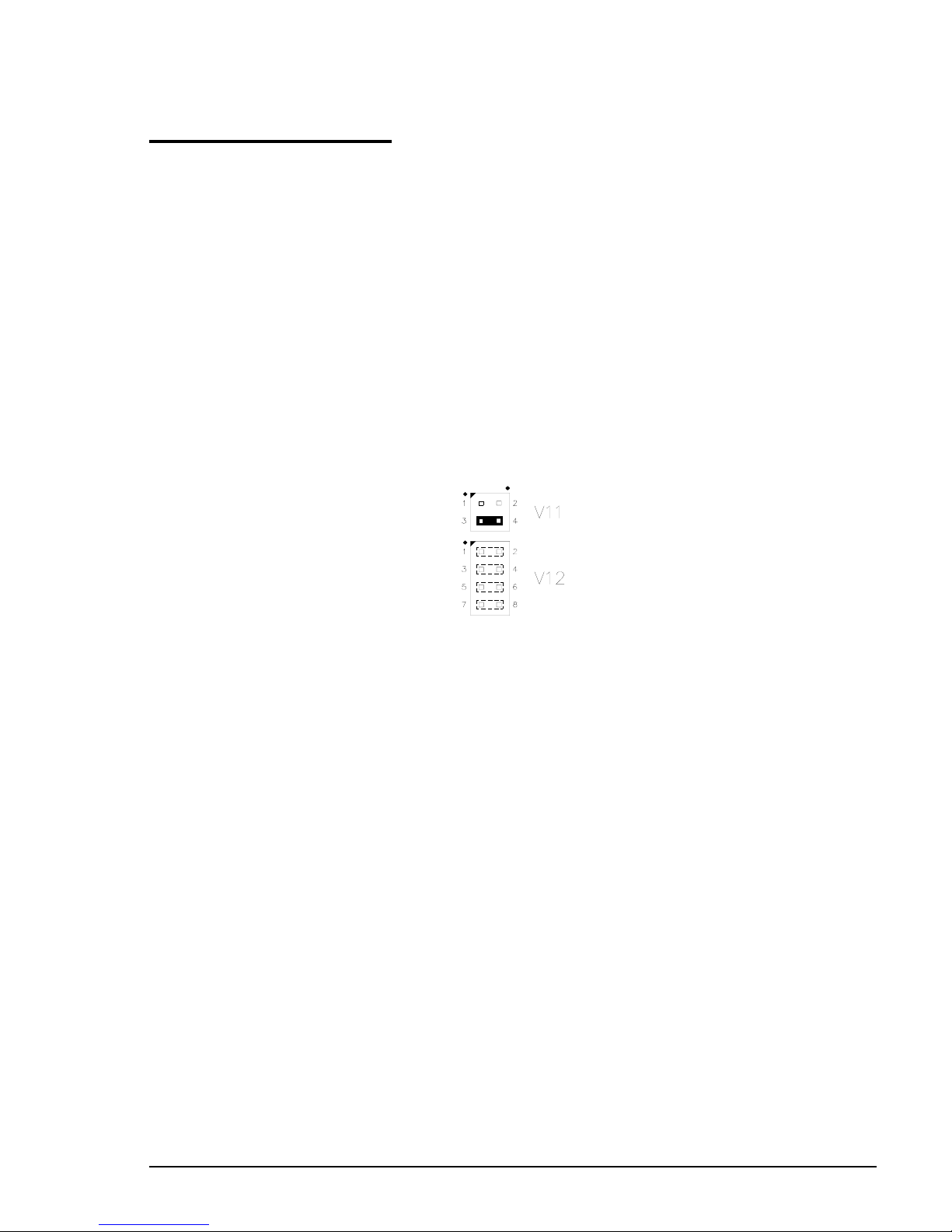

V11 Address Mode Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-Bit 2-5

[1-2] = In – 16-Bit Address Decoding

[3-4] = In – 8-Bit Address Decoding

V12 Board Address (A4 – A7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0300H 2-5

[1-2] = In – A7 Decoded Low [1-2] = Out – A7 Decoded High

[3-4] = In – A6 Decoded Low [3-4] = Out – A6 Decoded High

[5-6] = In – A5 Decoded Low [5-6] = Out – A5 Decoded High

[7-8] = In – A4 Decoded Low [7-8] = Out – A4 Decoded High

V13[1-2] Parallel Port Interrupt Edge Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Rising Edge Only 2-18

In –Rising Edge Only

Out – Rising and Falling Edges

V13[3-4] Parallel Port Interrupt Select (Module 0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Enabled 2-18

In –Activity on Module 0 (J3 Pin 31) generates interrupt request

Out – Disabled

V13[5-6] Parallel Port Interrupt Select (Module 1). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled 2-18

In –Activity on Module 1 (J3 Pin 29) generates interrupt request

Out – Disabled

V13[7-8] Parallel Port Interrupt Select (Module 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled 2-18

In –Activity on Module 2 (J3 Pin 27) generates interrupt request

Out – Disabled

V13[9-10] Parallel Port Interrupt Select (Module 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled 2-18

In –Activity on Module 3 (J3 Pin 25) generates interrupt request

Out – Disabled

V14[1-2] Use STD Bus IRQx to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . Disabled 2-19

In –Connects parallel port interrupt circuitry to STD Bus IRQx (E47)

Out – Frees IRQx to be used for other purposes

V14[2-3] Use STD Bus IRQx to carry ADC conversion complete interrupt. . . . . . . . . . . . . . . . Disabled 2-19

In –Connects ADC interrupt circuitry to STD Bus IRQx (E47)

Out – Frees IRQx to be used for other purposes

V15[1-2] Use STD Bus IRQ* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . Disabled 2-19

In –Connects parallel port interrupt circuitry to STD Bus IRQ* (P44)

Out – Frees IRQ* to be used for other purposes

V15[2-3] Use STD Bus IRQ* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . . Enabled 2-19

In –Connects ADC interrupt circuitry to STD Bus IRQ* (P44)

Out – Frees IRQ* to be used for other purposes

V16[1-2] Use STD Bus IRQ1* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . Enabled 2-19

In –Connects parallel port interrupt circuitry to STD Bus IRQ1* (P37)

Out – Frees IRQ1* to be used for other purposes

V16[2-3] Use STD Bus IRQ1* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . Disabled 2-19

In –Connects ADC interrupt circuitry to STD Bus IRQ1* (P37)

Out – Frees IRQ1* to be used for other purposes

V17[1-2] Use STD Bus IRQ2* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . Disabled 2-19

In –Connects parallel port interrupt circuitry to STD Bus IRQ2* (P50)

Out – Frees IRQ2* to be used for other purposes

V17[2-3] Use STD Bus IRQ2* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . Disabled 2-19

In –Connects ADC interrupt circuitry to STD Bus IRQ2* (P50)

Out – Frees IRQ2* to be used for other purposes

V18[1-2] Use STD Bus IRQ3* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . Disabled 2-19

In –Connects parallel port interrupt circuitry to STD Bus IRQ3* (E67)

Out – Frees IRQ3* to be used for other purposes

V18[2-3] Use STD Bus IRQ3* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . Disabled 2-19

In –Connects ADC interrupt circuitry to STD Bus IRQ3* (E67)

Out – Frees IRQ3* to be used for other purposes

Figure 2-2. VL-12CT96/7 Jumper Functions

2-4 VL-12CT96/7 Analog & Digital I/O Card

Page 11

Configuration — Board Addressing

Board Addressing

The VL-12CT96/7 card supports both 8- and 16-bit I/O addressing. 8-bit addressing is used with most

8-bit processors (Z80, 8085, 6809, etc.) which provide 256 I/O addresses. 16-bit addressing can be used

with 16-bit processors (i.e. 8088, 80188, etc.) to decode up to 65536 I/O port addresses.

Both 8- and 16-bit addressing can be extended (capacity doubled) using the IOEXP signal which is

decoded on board.

As shipped, the board is configured for 16-bit addressing with a board address of hex 0300. The card

occupies sixteen consecutive I/O addresses (0300H to 030FH). Twelve of these addresses are mapped

to control, data, and status registers, the remaining four are inaccessible. See the I/O Port Mapping

section on page 4-1 for further information.

8-Bit Addressing

To configure the board for an 8-bit I/O address, refer to the figure below. Use the table to select the

jumpering for the appropriate upper hex digit of the desired starting address (i.e., “3” and “0” = hex

address 30). Note: the lower digit is always “0.”

V12 V12 V12 V12 Upper Lower

1-2 3-4 5-6 7-8 Digit Digit

XXXX0 Always “0”

XXX—1

XX—X2

XX——3

X—XX 4

X—X—5

X——X 6

X——— 7

—XXX8

—XX—9

—X—XA

—X——B

——X X C

——X—D

———X E

————F

X = Jumper installed

—= Jumper removed

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V12 Board Address (A4 – A7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0300H (16-Bit)

DescriptionDescription

Description

DescriptionDescription

[1-2] = In – A7 Decoded Low [1-2] = Out – A7 Decoded High

[3-4] = In – A6 Decoded Low [3-4] = Out – A6 Decoded High

[5-6] = In – A5 Decoded Low [5-6] = Out – A5 Decoded High

[7-8] = In – A4 Decoded Low [7-8] = Out – A4 Decoded High

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

VL-12CT96/7 Analog & Digital I/O Card 2-5

Figure 2-3. 8-Bit Address Jumpers

Page 12

Configuration — Board Addressing

16-Bit Addressing

To configure the board for a 16-bit I/O address refer to the figure below. Use the table to select the

jumpering for the appropriate four hex digits of the desired starting address (i.e., “1” and “2” and “3”

and “0” = hex address 1230). Note: the lower digit is always “0.”

V9 V9 V9 V9 Upper V9 V9 V9 V9 2nd V12 V12 V12 V12 3rd Lower

1-2 3-4 5-6 7-8 Digit 9-10 11-12 13-14 15-16 Digit 1-2 3-4 5-6 7-8 Digit Digit

XXXX0 XXXX0 XXXX0 Always “0”

XXX—1 XXX—1 XXX—1

XX—X2 XX—X2 XX—X2

XX——3 XX——3 XX——3

X—XX 4 X—X X 4 X—XX 4

X—X—5 X—X—5 X—X—5

X——X 6 X——X6 X——X 6

X——— 7 X———7 X——— 7

—XXX8 —XXX8 —XXX8

—XX—9 —XX—9 —XX—9

—X—XA —X—X A —X—XA

—X——B —X——B —X——B

——X X C ——X X C ——X X C

——X—D ——X—D ——X—D

———X E ———X E ———X E

————F ———— F ————F

X = Jumper installed

-- = Jumper removed

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V9 Board Address (A8 – A15) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0300H

V12 Board Address (A4 – A7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0300H

DescriptionDescription

Description

DescriptionDescription

[1-2] = In – A15 Decoded Low [1-2] = Out – A15 Decoded High

[3-4] = In – A14 Decoded Low [3-4] = Out – A14 Decoded High

[5-6] = In – A13 Decoded Low [5-6] = Out – A13 Decoded High

[7-8] = In – A12 Decoded Low [7-8] = Out – A12 Decoded High

[9-10] = In – A11 Decoded Low [9-10] = Out – A11 Decoded High

[11-12] = In – A10 Decoded Low [11-12] = Out – A10 Decoded High

[13-14] = In – A9 Decoded Low [13-14] = Out – A9 Decoded High

[15-16] = In – A8 Decoded Low [15-16] = Out – A8 Decoded High

[1-2] = In – A7 Decoded Low [1-2] = Out – A7 Decoded High

[3-4] = In – A6 Decoded Low [3-4] = Out – A6 Decoded High

[5-6] = In – A5 Decoded Low [5-6] = Out – A5 Decoded High

[7-8] = In – A4 Decoded Low [7-8] = Out – A4 Decoded High

Figure 2-4. 16-Bit Address Jumpers

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

2-6 VL-12CT96/7 Analog & Digital I/O Card

Page 13

Configuration — Board Addressing/Data Bus Width

IOEXP Signal

The IOEXP (I/O expansion) signal on the STD Bus is normally used to select between two different I/

O banks or maps. It can be used to double the number of available I/O addresses in the system (by

selecting between two banks of I/O boards). The IOEXP signal is usually controlled by (or jumpered

to ground on) the system CPU card.

A low IOEXP signal usually selects the standard or normal I/O map. A high IOEXP signal usually

selects the secondary or alternate I/O map. Boards that ignore (or do not decode) IOEXP will appear

in both I/O maps.

As shipped the IOEXP jumper is configured to ignore the IOEXP signal. The board will be addressed

whether the IOEXP signal is high or low. It can be jumpered for two other modes as shown below.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V10 IOEXP Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . IOEXP Ignored

DescriptionDescription

Description

DescriptionDescription

[1-2] = In – Board responds to IOEXP high and low (IOEXP ignored)

[2-3] = In – Board responds to IOEXP low

[Both] = Out – Board responds to IOEXP high

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-5. IOEXP Options

Data Bus Width

The VL-12CT96/7 provides both 8-bit and 16-bit data paths to the bus. The 8-bit mode is compatible

with STD 80, STD Z80, and STD 32 bus specifications. The 16-bit mode is used only when operating

the card in an STD 32 card cage.

In 8-bit mode, the register map for the VL-12CT96/7 is a superset of the Analog Devices RTI-1265 board.

In 16-bit mode, the registers are remapped to even addresses for efficient I/O access. This allows the

full A/D data word to be read in a single bus cycle. See the I/O Port Mapping section on page 4-1 for

further information.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V8[1-2] Data Bus Width. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-Bit

DescriptionDescription

Description

DescriptionDescription

In – 8-Bit Data Bus

Out – 16-Bit Data Bus

VL-12CT96/7 Analog & Digital I/O Card 2-7

Figure 2-14. Data Bus Width Jumper

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Page 14

Configuration — Analog Input

Analog Input Configuration

The VL-12CT96/7 board accommodates 16 single-ended or 8 differential input channels.

Input Mode

The board can be configured for three types of analog inputs: differential, single-ended, or pseudodifferential. All inputs connected to the board must be of the same type.

When operated in differential mode, four channels can be configured to accept 4-20ma current loop

input.

Typical connections for the three input modes are shown in the figures below. Since ground loops

(current flowing between various equipment ground lines) affect analog measurements made with

reference to ground, careful attention should be paid to the ground connections shown. In particular,

the STD Bus power supply logic ground line should never be connected to earth ground when operating

in the differential or pseudo-differential modes.

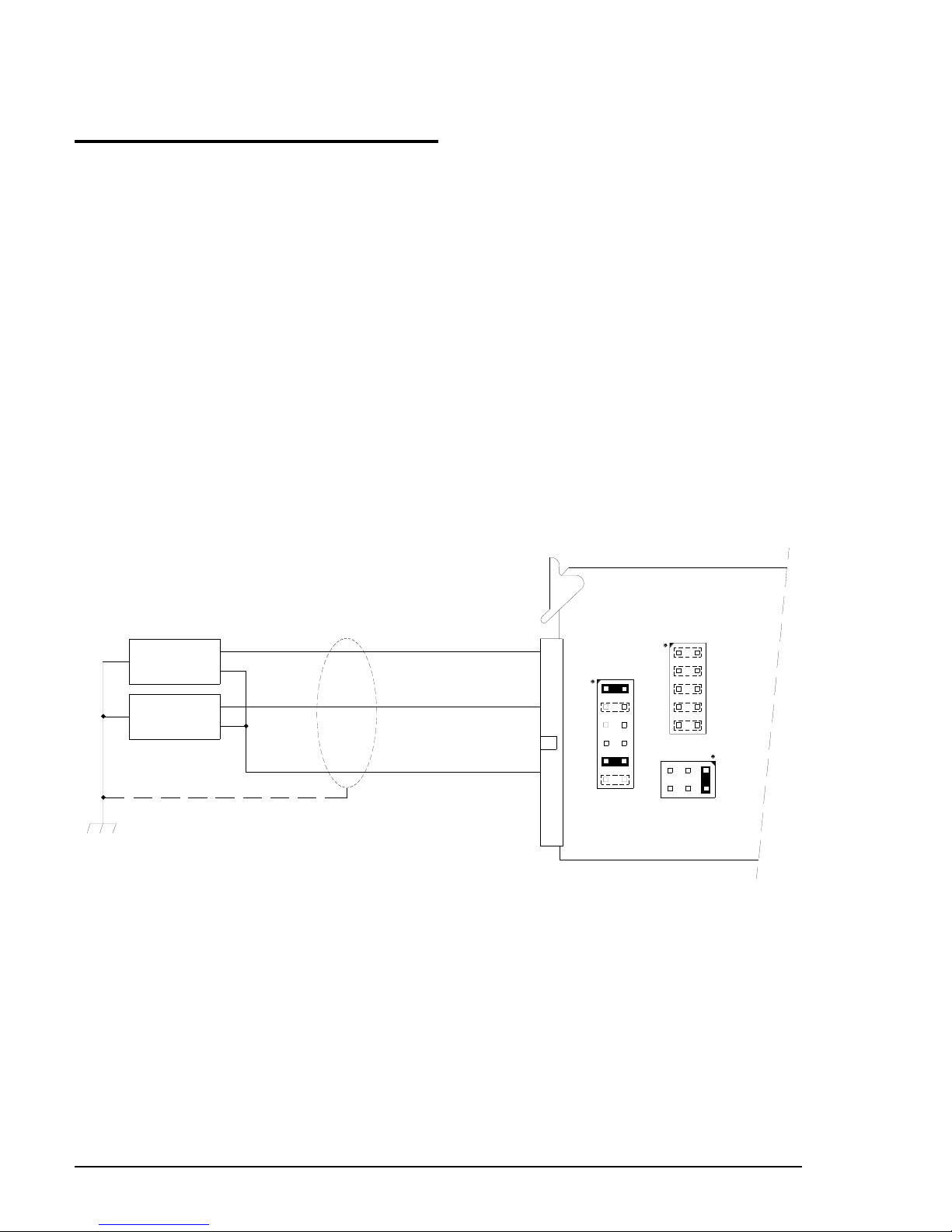

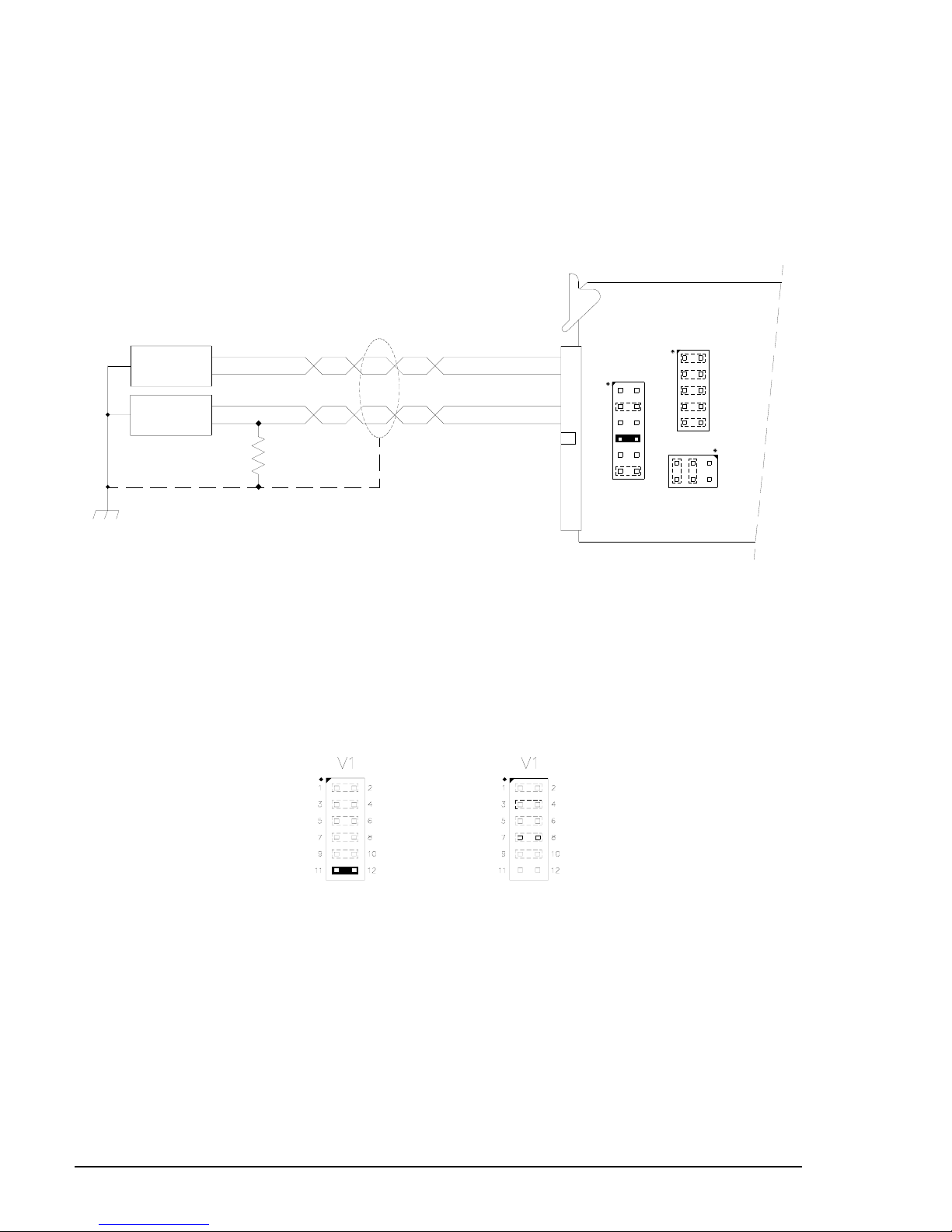

Single Ended Mode

Single-ended mode is used for signals that are referenced to a common ground. It is normally used only

for higher level signals on short distance runs (less than 10 feet). 16 input channels are available in

single-ended mode.

OPTIONAL

V0

V1

VL-12CT96

VL-12CT97

+

-

+

-

CHANNEL 0

CHANNEL 1

AGND

1

V1

1

3

5

5

7

9

9

11

As Shipped

V6

1

3

5

2

7

4

9

6

8

10

12

2

4

6

8

10

5

3

1

V7

2

4

6

Figure 2-6. Single Ended Input Mode

2-8 VL-12CT96/7 Analog & Digital I/O Card

Page 15

Configuration — Analog Input

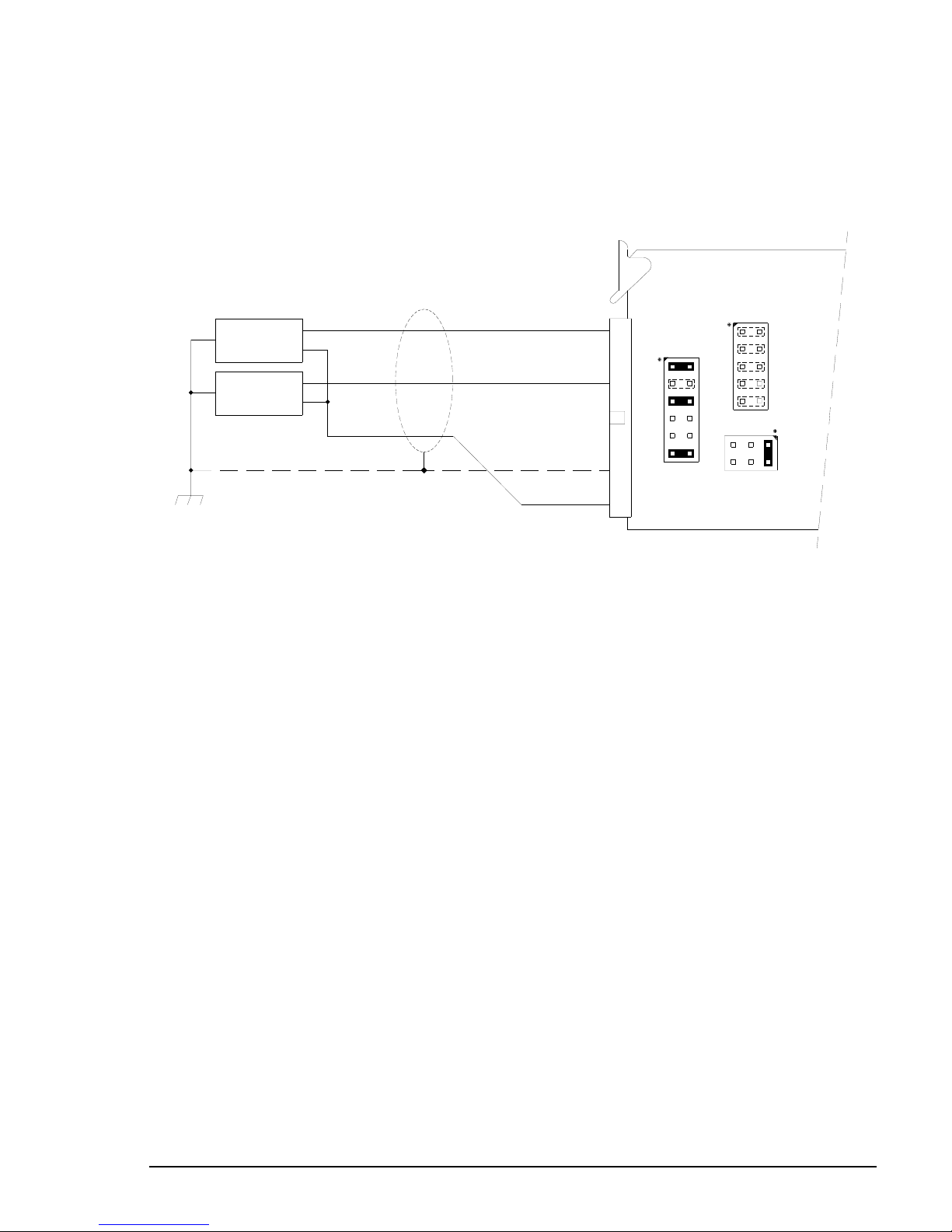

Pseudo-Differential Mode

Pseudo-differential mode is used for signals that are not referenced to ground, but are all connected

to a single common return line. This mode can provide most of the advantages of full differential input

while requiring fewer total wires. 16 input channels are available in pseudo-differential mode. This

mode is used when connecting to a 5B01 signal conditioning rack.

VL-12CT96

VL-12CT97

OPTIONAL

V0

V1

+

CHANNEL 0

-

+

CHANNEL 1

-

AGND

P.D. SENSE

Figure 2-7. Pseudo-Differential Input Mode

25

V6

1

V1

1

3

5

5

7

9

11

1

3

5

7

4

9

6

8

10

12

9

2

4

62

8

10

5

3

1

V7

2

4

6

VL-12CT96/7 Analog & Digital I/O Card 2-9

Page 16

Configuration — Analog Input

Differential Mode

Differential mode is used for signals that are not referenced to a common ground point. Each input

signal is represented as a voltage difference between two signal conductors (usually twisted wires), and

is presented to the board as a (+) and (–) pair. Differential mode reduces the effects of electromagnetically induced noise and ground currents in electrically noisy environments. It is especially useful in

eliminating the effects of common mode noise generated on input lines over longer distances. Eight

input channels are available in differential mode.

VL-12CT96

VL-12CT97

V6

1

2

3

4

5

2

4

6

8

10

12

6

7

8

9

10

5

3

1

V7

2

4

6

OPTIONAL

V0

V1

+

-

CHANNEL 0

+

-

SEE

TEXT

CHANNEL 1

+

1

-

2

+

5

-

4

V1

1

3

5

7

9

11

Figure 2-8. Differential Input Mode

Note that in full differential operation a return path must be provided for the bias currents of the input

amplifier. An on-board 1M Ω resistor is provided for this purpose. Jumper V1[11-12] should be

inserted.

In noisy electrical environments, the bias resistor should be located in close proximity to the voltage

source. Jumper V1[11-12] should be removed under these conditions.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

DescriptionDescription

Description

DescriptionDescription

V1[11-12] Differential Bias Resistor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . In Circuit

In – In Circuit

Out – Disconnected

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-9. Bias Resistor

2-10 VL-12CT96/7 Analog & Digital I/O Card

Page 17

Configuration — Analog Input

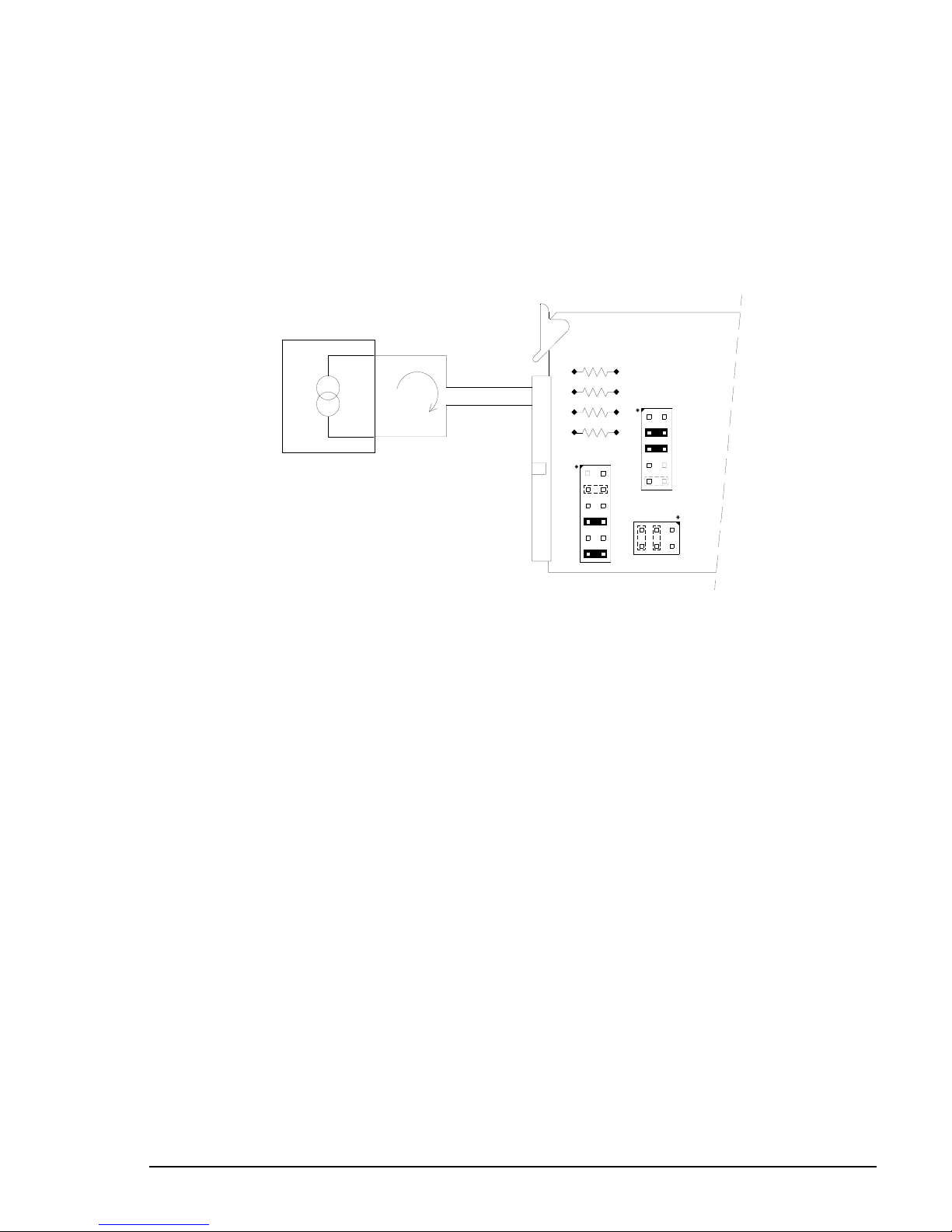

Current Loop Mode

In addition to voltage mode inputs, the VL-12CT96/7 can accept up to four 4-20 ma current loop inputs.

Channels 0 through 3 can be converted to current-loop input by installing 200 to 250 Ω, ¼W, 0.1%

precision resistors in locations R4 through R7 respectively.

The board must be jumpered for differential mode, and the input range should be jumpered for ±5V

operation when using current loop inputs. A signal proportional to the 4-20 ma current is developed

across the precision resistors. This voltage is applied to the VL-12CT96/7 as a differential-mode signal,

and is converted into digital values.

VL-12CT96

+

I

LOOP

CHANNEL 0

1

2

-

VL-12CT97

R4

R5

R6

R7

V1

1

3

5

7

9

11

V6

1

2

3

4

5

6

7

2

4

6

8

10

12

8

9

10

5

3

1

V7

2

4

6

Figure 2-10. Current Loop Input Mode

VL-12CT96/7 Analog & Digital I/O Card 2-11

Page 18

Configuration — Analog Input

Input Range

The board may be operated with an input range of ±5 volts, ±10 volts, ±50 mv, or ±100 mv. To achieve

the maximum digital resolution and to prevent saturation, the range which most closely matches the

input signal should be chosen. All channels operate with the same input range.

As shipped the board is configured for ±10 volt operation. It can be jumpered for other ranges as shown

below.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V1[3-4] Input Gain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Normal

V6[1-8] Input Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V

DescriptionDescription

Description

DescriptionDescription

In – x100

Out – Normal

[1-2] & [7-8] In – ±10 Volts

[3-4] & [5-6] In – ±5 Volts

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-11. Input Range Jumper

2-12 VL-12CT96/7 Analog & Digital I/O Card

Page 19

Configuration — Analog Input

Settling Time

The VL-12CT96/7 board inserts a short delay between the time a channel is selected and time the A/

D conversion begins. The delay allows the multiplexer and associated circuitry to properly settle for

a more accurate reading.

The settling delay starts when the Channel Select register is written to by software, or when the Data

High register is read (in auto increment mode). After channel selection (during the settling time), the

A/D conversion cycle can be started by writing to the Convert register; however, the A/D converter is

not triggered until the delay time elapses. The time delay is not inserted when one channel is read

repeatedly.

The standard 5 µS delay (as shipped) is used for ±5V or ±10V input ranges. The longer 10 µS settling

delay is needed for the ±50 mv or ±100 mv input ranges.

Settling delay times can be selected as indicated in the figure below.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V7[3-4] 5 µS Settling Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Enabled

V7[5-6] 10 µS Settling Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

DescriptionDescription

Description

DescriptionDescription

In – Enabled

Out – Disabled

In – Enabled

Out – Disabled

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-12. Settling Time Jumpers

Low Pass Filter

A 1 MHz low pass filter between the instrumentation amplifier and the A/D convertor can be selected

as shown in the figure below. This filter is used to reject high frequency noise and is normally enabled.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

DescriptionDescription

Description

DescriptionDescription

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

V6[9-10] Input Low Pass Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Enabled

In – Enabled

Out – Disabled

VL-12CT96/7 Analog & Digital I/O Card 2-13

Figure 2-13. Low Pass Filter Jumper

Page 20

Configuration — Analog Input

Input Resolution

The VL-12CT96 provides 12 bits of resolution (4096 digital counts). For correct operation, jumper V8[34] should be removed. The VL-12CT97 provides 16 bits of resolution (65536 counts) for applications

which require finer resolution. For correct operation, jumper V8[3-4] should be inserted.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V8[3-4] Analog Input Resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Varies

DescriptionDescription

Description

DescriptionDescription

In – 16-Bit Resolution (VL-12CT97 only)

Out – 12-Bit Resolution (VL-12CT96 only)

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-15. Input Range Selection

Analog Output Configuration

The VL-12CT96/7 board accommodates two analog output channels. Both output channels are singleended and are referenced to analog ground. The digital data format is two’s complement.

2-14 VL-12CT96/7 Analog & Digital I/O Card

Page 21

Configuration — Analog Output

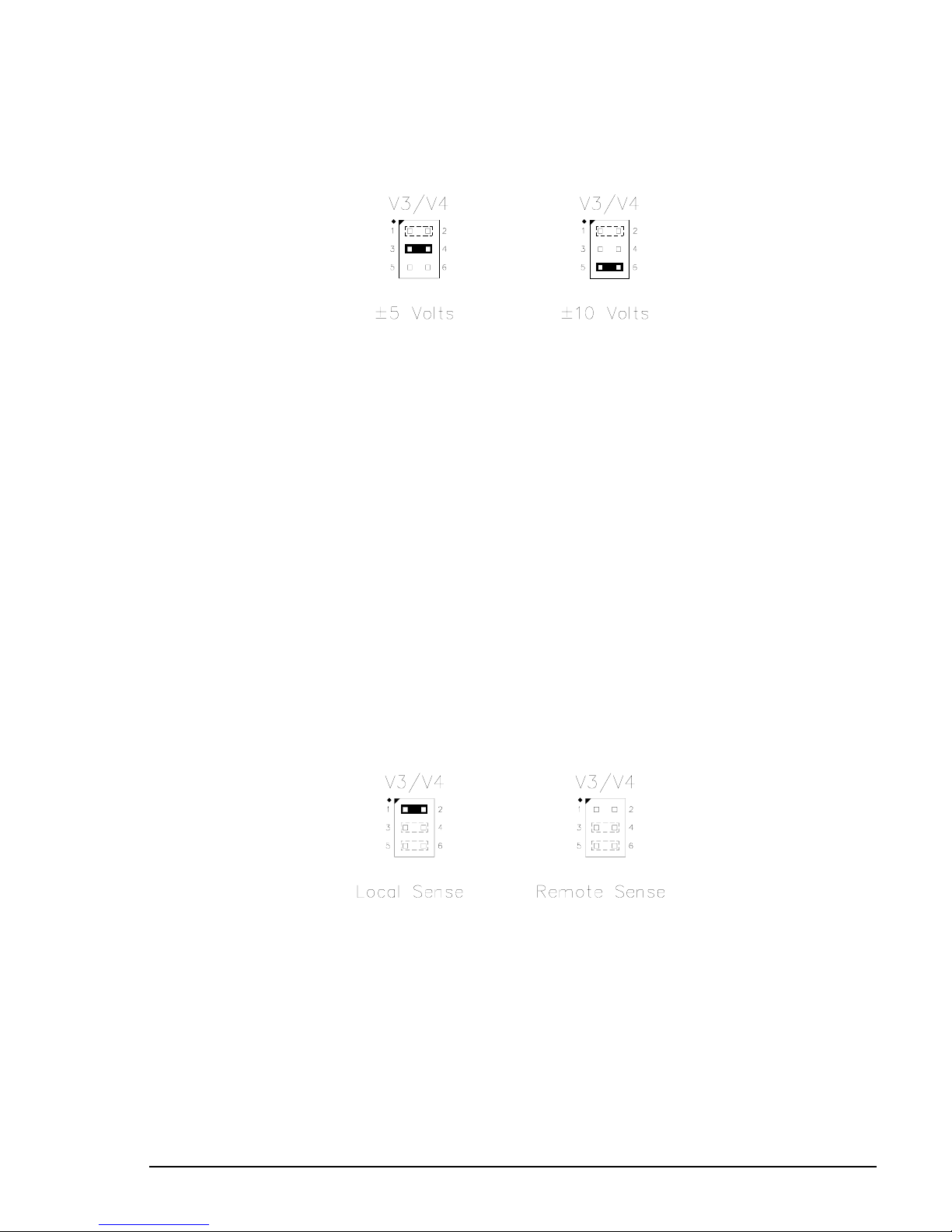

Output V oltage Range

Each output channel can be configured independently to produce output voltage ranges of ±5 volts, or

±10 volts as shown below.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V3[3-4] Channel 0 Output Range (±5 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V

V3[5-6] Channel 0 Output Range (±10 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V

V4[3-4] Channel 1 Output Range (±5 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V

V4[5-6] Channel 1 Output Range (±10 Volt Selection) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±10V

DescriptionDescription

Description

DescriptionDescription

In – ±5 Volts

Out – ±10 Volts

In – ±10 Volts

Out – ±5 Volts

In – ±5 Volts

Out – ±10 Volts

In – ±10 Volts

Out – ±5 Volts

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-16. Output Voltage Range

Output Local/Remote Sense

When a load is driven over a long cable, the resistance of the wire can cause a voltage drop to occur. This

can result in erroneous signal levels at the remote end of the line. The VL-12CT96/7 board can compensate

for this drop (up to 3 volts of loss) by measuring the voltage at the far end of the line through a separate

sense line.

Each channel can be jumpered for local sense (voltage measured at the card edge, no sense wire used),

or remote sense (voltage measured at the destination, sense wire required).

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V3[1-2] DAC Channel 0 Remote Sense (IR Drop Compensation). . . . . . . . . . . . . . . . . . . . . . . . . . Local sense

V4[1-2] DAC Channel 1 Remote Sense (IR Drop Compensation). . . . . . . . . . . . . . . . . . . . . . . . . . Local sense

DescriptionDescription

Description

DescriptionDescription

In – Local sense (no compensation)

Out – Remote sense

In – Local sense (no compensation)

Out – Remote sense

VL-12CT96/7 Analog & Digital I/O Card 2-15

Figure 2-17. Remote Sense Jumpers

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Page 22

Configuration — Analog Output

Output Current Loop Option

Channel 0 can optionally be configured to produce current loop output in the range of 4 to 20 mA.

Normally this is a factory installed option. Contact VersaLogic for further information.

Note: When using the 4-20 mA option, channel 0 must be configured for ±10 volt output range.

An external loop power source between 15 and 30 volts must be connected to J1 pin 5 (LP0) as shown

below. This power source must be capable of providing 25 mA of current.

VL-12CT96

VL-12CT97

CHANNEL 0

0 to +10V

J2

5

~

5

~

mA

4 to 20 mA

6

4

R

LOAD

EXTERNAL LOOP

POWER SOURCE

+15V TO +30V

Figure 2-18. Current Loop Connection

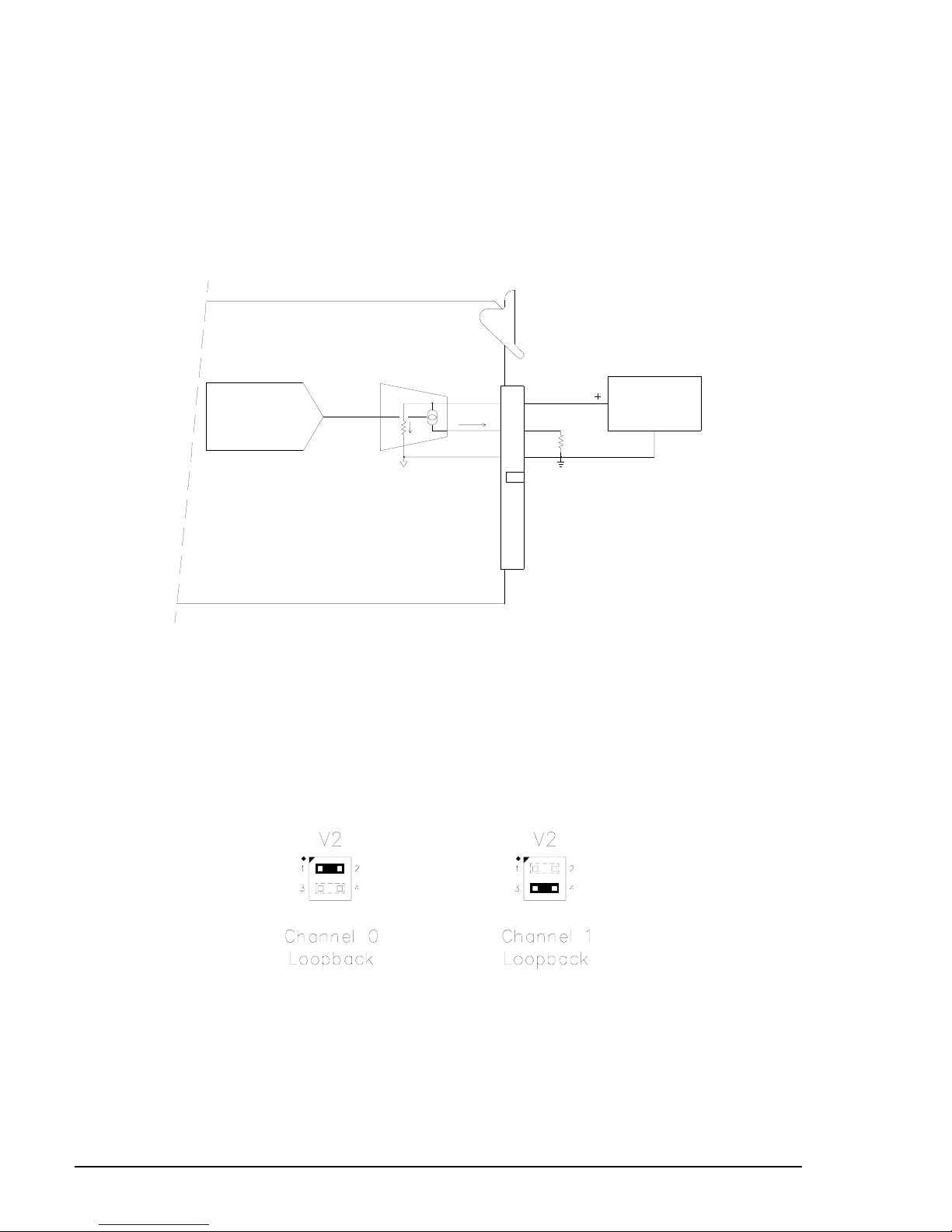

Output Voltage Loopback

The output channels can be connected to their corresponding input channels for a direct readback of

the voltage. The looped back output channels are also available on J1 for user and 5B01 rack

connections.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V2[1-2] Analog Loopback (Channel 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Independent

V2[3-4] Analog Loopback (Channel 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Independent

DescriptionDescription

Description

DescriptionDescription

In – Connects DAC 0 output to ADC 0 input for diagnostic loopback

Out – Circuits operate independently

In – Connects DAC 1 output to ADC 1 input for diagnostic loopback

Out – Circuits operate independently

Figure 2-19. Analog Output Loopback

2-16 VL-12CT96/7 Analog & Digital I/O Card

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Page 23

Configuration — 5B01 Rack/Digital Input/Output

5B01 Analog Signal Conditioning Rack

When using a 5B01 series analog signal conditioning rack connected to J1, the input mode should be

set to Pseudo-Differential mode and the input range should be set to ±5V. The output channels can

be connected to the 5B01 rack using the Output Voltage Loopback jumpers, and should be configured

for ±5V output.

Digital Input/Output Configuration

This card has 16 digital I/O lines that can be independantly programmed as inputs or outputs. The

I/O connector is compatible with 8 and 16 position modular I/O racks.

Rack P ower Contr ol

The VL-12CT96/7 board includes provisions for powering the external I/O rack assembly with +5 volts

at 500 ma.

When jumper V5 is installed, the I/O rack power line (I/O rack pin 49) is connected directly to +5 volts

on the STD Bus. If the I/O rack is powered by a separate external supply, either a jumper from the

I/O rack or the V5 jumper must be removed.

Note that the +5 volt power output from the VL-12CT96/7 card can be shorted to ground if the connector

is not correctly oriented at either end of the interface cable. The use of keys in the connectors, or very

clear markings on the connectors, is recommended to prevent backwards connection of the cable.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V5 Opto-22 I/O Rack Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . External

DescriptionDescription

Description

DescriptionDescription

In – I/O rack power provided by VL-12CT96/7

Out – I/O rack power provided externally

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-20. Rack Power Control Jumper

VL-12CT96/7 Analog & Digital I/O Card 2-17

Page 24

Configuration — Digital Input/Output

Digital I/O Interrupts

Up to four parallel port signals can be selected by jumper V13 to trigger an interrupt request when the

logic state on these signals changes state.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V13[3-4] Parallel Port Interrupt Select (Module 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Enabled

V13[5-6] Parallel Port Interrupt Select (Module 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

V13[7-8] Parallel Port Interrupt Select (Module 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

V13[9-10] Parallel Port Interrupt Select (Module 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

DescriptionDescription

Description

DescriptionDescription

In – Activity on Module 0 (J3 Pin 31) generates interrupt request

Out – Disabled

In – Activity on Module 1 (J3 Pin 29) generates interrupt request

Out – Disabled

In – Activity on Module 2 (J3 Pin 27) generates interrupt request

Out – Disabled

In – Activity on Module 3 (J3 Pin 25) generates interrupt request

Out – Disabled

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Figure 2-21. Digital Interrupts

Edge Selection

Two edge options are available: single edge, and double edge mode. Single edge mode generates an

interrupt when any of the selected input signals (at connector J3) switches from high-to-low. Double

edge mode generates an interrupt on both high-to-low and low-to-high transitions.

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V13[1-2] Inte rr u pt Edge Selector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Rising Edge Only

DescriptionDescription

Description

DescriptionDescription

In – Rising Edge Only

Out – Rising and Falling Edges

Figure 2-22. Digital Interrupt Edge Select

2-18 VL-12CT96/7 Analog & Digital I/O Card

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

Page 25

Configuration — Interrupt

Interrupt Configuration

Jumpers V14 through V18 connect the interrupt request signals from the VL-12CT96/7 card to five

STD Bus interrupt request lines. The choice of which jumper position to choose depends upon the

capabilities of the CPU or interrupt controller used in the system.

If an STD 32 Slot X interrupt controller is used, interrupts are requested on the dedicated slot specific

signal IRQx (E47).

JumperJumper

Jumper

JumperJumper

BlockBlock

Block

BlockBlock

V14[1-2] Use STD Bus IRQx to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

V14[2-3] Use STD Bus IRQx to carry ADC conversion complete interrupt. . . . . . . . . . . . . . . . . . . . Disabled

V15[1-2] Use STD Bus IRQ* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

V15[2-3] Use STD Bus IRQ* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . . . . . . Enabled

V16[1-2] Use STD Bus IRQ1* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . . . . Enabled

V16[2-3] Use STD Bus IRQ1* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . . . . . Disabled

V17[1-2] Use STD Bus IRQ2* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

V17[2-3] Use STD Bus IRQ2* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . . . . . Disabled

V18[1-2] Use STD Bus IRQ3* to carry parallel port interrupt signal . . . . . . . . . . . . . . . . . . . . . . . . . Disabled

V18[2-3] Use STD Bus IRQ3* to carry ADC conversion complete interrupt . . . . . . . . . . . . . . . . . . . Disabled

DescriptionDescription

Description

DescriptionDescription

In – Connects parallel port interrupt circuitry to STD Bus IRQx (E47)

Out – Frees IRQx to be used for other purposes

In – Connects ADC interrupt circuitry to STD Bus IRQx (E47)

Out – Frees IRQx to be used for other purposes

In – Connects parallel port interrupt circuitry to STD Bus IRQ* (P44)

Out – Frees IRQ* to be used for other purposes

In – Connects ADC interrupt circuitry to STD Bus IRQ* (P44)

Out – Frees IRQ* to be used for other purposes

In – Connects parallel port interrupt circuitry to STD Bus IRQ1* (P37)

Out – Frees IRQ1* to be used for other purposes

In – Connects ADC interrupt circuitry to STD Bus IRQ1* (P37)

Out – Frees IRQ1* to be used for other purposes

In – Connects parallel port interrupt circuitry to STD Bus IRQ2* (P50)

Out – Frees IRQ2* to be used for other purposes

In – Connects ADC interrupt circuitry to STD Bus IRQ2* (P50)

Out – Frees IRQ2* to be used for other purposes

In – Connects parallel port interrupt circuitry to STD Bus IRQ3* (E67)

Out – Frees IRQ3* to be used for other purposes

In – Connects ADC interrupt circuitry to STD Bus IRQ3* (E67)

Out – Frees IRQ3* to be used for other purposes

AsAs

As

AsAs

ShippedShipped

Shipped

ShippedShipped

VL-12CT96/7 Analog & Digital I/O Card 2-19

Figure 2-23. Interrupt Configuration Options

Page 26

2-20 VL-12CT96/7 Analog & Digital I/O Card

Page 27

Installation

Installation

Handling

** CAUTION **** CAUTION **

** CAUTION ** The VL-12CT96/7 card uses chips which are sensitive to static electricity discharges.

** CAUTION **** CAUTION **

Normal precautions, such as discharging yourself, work stations, and tools to ground before touching

the board should be taken whenever the board is handled. The board should also be protected during

shipment or storage by placing it in a pink anti-static bag (such as the one it was received in).

Installation

The VL-12CT96/7 card can be installed in any slot of an STD Bus card cage, excluding Slot X in STD

32 cages.

Signal Levels

The STD Bus interface on the VL-12CT96/7 card is compatible with TTL and CMOS bus level signals.

Connector J1 is the analog input connector. All signals are analog level signals. The maximum non-

destructive input voltage applied to any of the inputs is ±35V with power on (±20V with power off). Each

analog channel presents a minimum input impedance of 1 x 108 Ω.

Connector J2 is the analog output connector. All signals are analog level signals. The voltage outputs

can provide up to 5 ma each. The optional current loop output requires an external +15V to +30V power

supply capable of providing 25 ma of current.

Connector J3 is the digital input/output connector. Each circuit is an open collector driver with a 10K

Ω pull up resistor to +5V. Input gates are attached to each output signal for read-back. The open

collector driver must be in the off state to use a channel for input purposes. External equipment

attached to connector J3 must be able to sink 500 µA @ 5V per channel. The maximum non-destructive

input voltage applied to any channel is +5V.

All logic levels are referenced to digital ground on the same connector.

Priority Chain

The VL-12CT96/7 card does not use the STD Bus priority interrupt chain signals PCO and PCI;

however, because PCI is connected to PCO on board, the card can be installed between cards using the

chain.

VL-12CT96/7 Analog & Digital I/O Card 3-1

Page 28

Installation — External Connections

External Connections

J1, J2 and J3 are unlatched header type connectors. External connections to the VL-12CT96/7 can be

made with standard cable assemblies, or with the following mating connectors:

Connector Mating Connector

J1 26-pin socket type connectors such as 3M #3399-6626

J2 10-pin socket type connectors such as 3M #3473-6610

J3 34-pin socket type connectors such as 3M #3414-6634

Figure 3-1. Mating Connectors

Figure 3-2. I/O Connector Physical Pin Locations

3-2 VL-12CT96/7 Analog & Digital I/O Card

Page 29

J1 — Analog Input Connector

Installation — External Connections

J1 Pin Differential Pesudo-Differential

1 Channel 0+ Channel 0

2 Channel 0– Channel 8

3 Analog Ground Analog Ground

4 Channel 1– Channel 9

5 Channel 1+ Channel 1

6 Analog Ground Analog Ground

7 Channel 2+ Channel 2

8 Channel 2– Channel 10

9 Analog Ground Analog Ground

10 Channel 3– Channel 11

11 Channel 3+ Channel 3

12 Analog Ground Analog Ground

13 Channel 4+ Channel 4

14 Channel 4– Channel 12

15 Analog Ground Analog Ground

16 Channel 5– Channel 13

17 Channel 5+ Channel 5

18 Analog Ground Analog Ground

19 Channel 6+ Channel 6

20 Channel 6– Channel 14

21 Analog Ground Analog Ground

22 Channel 7– Channel 15

23 Channel 7+ Channel 7

24 Analog Ground Analog Ground

25 PD PD

26 N/C N/C

Single Ended or

Figure 3-3. J1 – Analog Input Connector Pinout

Channel 0 to 15. Analog voltages are applied to these inputs for A/D conversion. In single-ended

configuration, these inputs are referenced to Analog Ground. In pseudo-differential configuration,

these inputs are considered “high side” (+) inputs and are referenced to PD.

Channel 0+ to 7+. Differential “high side” voltages are applied to these inputs for A/D conversion. Each

input is referenced to a corresponding differential “low side” (–) input.

Channel 0– to 7–. Differential “low side” voltages are applied to these inputs for A/D conversion. Each

input is referenced to a corresponding differential “high side” (+) input.

PD — Pseudo Differential “Low Side”. All “low side” (–) pseudo-differential analog voltages are connected

together and brought to this pin for differential reference.

Analog Ground. This signal is the on-board analog ground. In single-ended mode, all analog inputs are

referenced to this signal. In differential mode, a return path for the input bias currents of the on-board

instrumentation amplifiers may be connected to this pin. The use of multiple ground connections is

recommended to maintain a high degree of signal integrity.

N/C — No Connection. This signal is not connected to on-board circuitry. It has no function on the

VL-12CT96/7.

VL-12CT96/7 Analog & Digital I/O Card 3-3

Page 30

Installation — External Connections

J2 — Analog Output Connector

J2 Pin Signal Name Function

1 AGND Analog Ground

2 DA0V Channel 0 Voltage Output

3 DA0S Channel 0 Sense

4 AGND Analog Ground

5 LP0 Channel 0 Loop Power

6 DA0I Channel 0 Current Output

7 AGND Analog Ground

8 DA1V Channel 1 Voltage Output

9 DA1S Channel 1 Sense

10 AGND Analog Ground

Figure 3-4. J2 – Analog Output Connector Pinout

DA0V, DA1V — Channel 0 & 1 Voltage Output. Analog voltage outputs referenced to analog ground. Each

signal can source or sink up to 5 mA.

DA0S, DA1S — Channel 0 & 1 Sense. Remote sense inputs. Used to compensate for the voltage drop which

occurs when using long cables.

LP0 — Channel 0 Loop Power. External +15V to +30V power input. Used to provide loop power for

current loop mode.

DA0I — Channel 0 Current Output. Current loop output from channel 0.

AGND — Analog Ground. This signal is the on-board analog ground. All signals on J2 are referenced

to this signal. The use of multiple Analog Ground signals is recommended to maintain a high degree

of signal integrity.

3-4 VL-12CT96/7 Analog & Digital I/O Card

Page 31

J3—Digital I/O Connector

Installation — External Connections

J3 Pin Signal Name

1 MOD15*

2 Digital Ground

3 MOD14*

4 Digital Ground

5 MOD13*

6 Digital Ground

7 MOD12*

8 Digital Ground

9 MOD11*

10 Digital Ground

11 MOD10*

12 Digital Ground

13 MOD9*

14 Digital Ground

15 MOD8*

16 Digital Ground

17 MOD7*

18 Digital Ground

19 MOD6*

20 Digital Ground

21 MOD5*

22 Digital Ground

23 MOD4*

24 Digital Ground

25 MOD3*

26 Digital Ground

27 MOD2*

28 Digital Ground

29 MOD1*

30 Digital Ground

31 MOD0*

32 Digital Ground

33 Power

34 Digital Ground

MOD0* – MOD15*. Opto 22 bidirectional interface signals. Each signal is an open collector driver with

a 10ΚΩ pull up resistor to +5V. Input gates are attached to each signal for read-back. The open collector

driver must be in the off state to use a channel for input purposes.

used to manipulate these signals.

Power. +5V power output. When jumper V5 is installed, up to 500 mA can be drawn from this +5V

output to power the Opto 22 interface rack or other external equipment. If the I/O rack is powered by

a separate external supply, the power jumper on the I/O rack or the V5 jumper must be removed.

Digital ground. All signals on connector J3 are referenced to these digital ground connections. The use

of all ground connections is recommended to maintain a high degree of signal integrity.

VL-12CT96/7 Analog & Digital I/O Card 3-5

Figure 3-5. J3 – Digital I/O Connector Pinout

Registers PARLO and PARHI are

Page 32

3-6 VL-12CT96/7 Analog & Digital I/O Card

Page 33

Registers

Registers

Introduction

This section includes information about registers, control and status bits, and data formats. It focuses

primarily on the individual registers, the bits contained within them, and their functional descriptions.

I/O Port Mapping

The VL-12CT96/7 uses one of two I/O port maps depending upon whether the data bus is configured

for 8-bit or 16-bit operation. In 8-bit mode, registers are mapped to correspond with Analog Device’s

RTI-1265 board. In 16-bit mode, the data registers are moved to an even address boundary to facilitate

efficient single-cycle reading of the A/D data.

8-Bit Mode 8-Bit Mode 16-Bit Mode 16-Bit Mode As Shipped

Input Port Output Port Input Port Output Port Port Address Address

— DAC1HI — DAC1HI Board Address + 15 030FH

— DAC1LO — DAC1LO Board Address + 14 030EH

— DAC0HI — DAC0HI Board Address + 13 030DH

— DAC0LO — DAC0LO Board Address + 12 030CH

PARHI PARHI PARHI PARHI Board Address + 11 030BH

PARLO PARLO PARLO PARLO Board Address + 10 030AH

— CLRFLG — CLRFLG Board Address + 9 0309H

————Board Address + 8 0308H

————Board Address + 7 0307H

————Board Address + 6 0306H

— — ADCHI — Board Address + 5 0305H

ADCHI — ADCLO — Board Address + 4 0304H

ADCLO — — — Board Address + 3 0303H

— CONVERT — CONVERT Board Address + 2 0302H

— SELECT — SELECT Board Address + 1 0301H

STATUS CONTROL STATUS CONTROL Board Address + 0 0300H

Figure 4-1. I/O Port Addresses

VL-12CT96/7 Analog & Digital I/O Card 4-1

Page 34

Registers — Analog Input Registers

Analog Input Registers

The following table lists the functions assigned to each read and write register.

Write Registers Functions Page

CONTROL Interrupt, Auto-trigger, Auto increment, Scan range limit 4-2

SELECT Selects A/D channel to convert 4-4

CONVERT

CLRFLG

PARLO Parallel Port Data Low (Opto 22 Modules 8-15) 4-12

PARHI Parallel Port Data High (Opto 22 Modules 0-7) 4-12

DAC0LO D/A Channel 0 Data Low 4-10

DAC0HI D/A Channel 0 Data High 4-10

DAC1LO D/A Channel 1 Data Low 4-10

DAC1HI D/A Channel 1 Data High 4-10

Read Registers Functions Page

STATUS Busy, Done, Settling Delay, Interrupt status bits 4-6

ADCLO A/D Data Low 4-7

ADCHI A/D Data High 4-7

1

Data insensitive. Any value may be written to this port.

1

1

Triggers A/D conversion 4-5

Clears Done bit 4-5

Figure 4-2. Read and Write Register Functions

Analog Input Write Register s

Control Register

CONTROL — 0300H

7 6 5 4 3 2 1 0

D7D6D5D4D3D2D1D

Figure 4-3. Control Register

The Control register is a write register used to configure the operating mode of the VL-12CT96/7.

D7 — Not Used. This bit has no function on the VL-12CT96/7.

D6, D5 — Scan Range Limit. These two bits define and restrict the number of channels scanned in auto-

increment mode. This allows for faster throughput when only eight or four analog signals are

connected. A “1” bit in D6 or D5 forces a “0” on the multiplexer address lines MA3 or MA2 respectively.

Values other than those listed will cause channels to be skipped in groups. A board reset selects (00)

so that applications which do not use auto-increment mode are not restricted to a limited set of

channels.

0

D6 D5 Scan Range C omment

0 0 0 to 15 All 16 channels

1 0 0 to 7 Restricted range

1 1 0 to 3 Restricted range

4-2 VL-12CT96/7 Analog & Digital I/O Card

Figure 4-4. Scan Range Limit

Page 35

Registers — Analog Input Registers

(00)—Channels 0 to 15. This selection does not restrict the number of channels accessed in auto-

increment mode. (00) should be selected for applications which do not use auto-increment mode.

(10)—Channels 0 to 7. This selection causes the first eight channels to be accessed in auto-increment

mode. Channels 0 through 7 are accessed in sequence, and then repeated (modulo 8 restriction of

the value contained in the SELECT register).

(11)—Channels 0 to 3. This selection causes the first four channels to be accessed in auto-increment

mode. Channels 0 through 3 are accessed in sequence, and then repeated (modulo 4 restriction of

the value contained in the SELECT register).

D4 — Auto Increment Enable. Setting this bit to “1” places the VL-12CT96/7 in auto-increment mode. In

this mode the SELECT register increments by one after the ADCHI register is read, allowing the next

channel in sequence to be converted. The SELECT register will increment to a maximum value set

by the Scan Range Limit (bits D6 and D5 of this register) and then repeat starting again with channel

0. A settling delay set by jumper V7 is inserted after each increment. Resetting this bit to “0” disables

auto-increment mode, allowing the SELECT register to retain its value. Auto-increment is disabled

upon board reset. Auto-increment is compatible with manual and auto-trigger modes.

Before selecting auto-increment mode, the initial channel to be converted (usually channel 0) should

be selected by writing to the SELECT register.

D3 — Auto Trigger Enable. Setting this bit to “1” places the VL-12CT96/7 in auto-trigger mode. In this

mode a new A/D conversion is triggered immediately after the ADCHI register is read, eliminating the

need to trigger a conversion by writing to the CONVERT register.

There are two ways to trigger an A/D conversion: writing to the CONVERT register or reading the

ADCHI register (if auto-trigger is enabled).

To use auto-triggering, set this bit to “1,” start the first A/D “manually” by writing to the CONVERT

register, wait until Done, then read the ADCLO and ADCHI registers. From this point on, just wait

until Done and read data.

D2 — Not Used. This bit has no function on the VL-12CT96/7.

D1 — Parallel Port Interrupt Enable. Setting this bit to “1” enables parallel port interrupts. In this mode

an interrupt request is sent to the CPU when specific parallel port signal conditions are met as

determined by jumper V13. Reset this bit to “0” to disable interrupt requests from the parallel port.

See page 5-4 for further information about operating the parallel port with interrupts. An interrupt

software example is shown on page 6-8.

D0 — A/D Interrupt Enable. Setting this bit to “1” enables A/D interrupts. In this mode an interrupt

request is sent to the CPU when the A/D conversion is complete. Reset this bit to “0” to disable interrupt

requests from the A/D converter. See page 5-2 for further information about operating the A/D

converter with interrupts. An interrupt software example is shown on page 6-2.

VL-12CT96/7 Analog & Digital I/O Card 4-3

Page 36

Registers — Analog Input Registers

Channel Select Register

SELECT — 0301H

7 6 5 4 3 2 1 0

D7D6D5D4D3D2D1D

0

Figure 4-5. Channel Select Register

The SELECT register is a write register used to select the analog channel number to perform an A/D

conversion on. A word-wide output instruction to the SELECT register (out dx,ax) also writes into the

CONVERT register causing channel addressing and triggering with one CPU instruction.

D7, D6, D5, D4 — Not Used. These bits have no function on the VL-12CT96/7.

D3, D2, D1, D0 — Channel Address. These bits select the analog channel to use for A/D conversion. In

auto-increment mode, the channel address changes after each A/D conversion. In all other cases the

value remains static.

Note: The Scan Range Limit bits in the Control register affect the number stored in this register. See

page 4-2 for further information.

A settling delay set by jumper V7 is inserted whenever this register changes.

D3 D2 D1 D0 Selected Channel

0000Channel 0

0001Channel 1

0010Channel 2

0011Channel 3

0100Channel 4

0101Channel 5

0110Channel 6

0111Channel 7

1000Channel 8

1001Channel 9

1010Channel 10

1011Channel 11

1100Channel 12

1101Channel 13

1110Channel 14

1111Channel 15

Figure 4-6. Channel Selection Codes

4-4 VL-12CT96/7 Analog & Digital I/O Card

Page 37

Registers — Analog Input Registers

Convert Register

CONVERT — 0302H

7 6 5 4 3 2 1 0

D7D6D5D4D3D2D1D

0

Figure 4-7. Convert Register

The CONVERT register is a write register which, when written to, triggers (starts) an A/D conversion.

It is data insensitive; any value written to the CONVERT register will produce a trigger.

There are two ways to trigger an A/D conversion: writing to the CONVERT register or reading the

ADCHI register (if auto-trigger is enabled).

A word-wide output instruction to the SELECT register (out dx,ax) also writes into the CONVERT

register causing channel addressing and triggering with one CPU instruction.

D7-D0 — Not Used. These bits have no function on the VL-12CT96/7. Any value written triggers an A/

D conversion.

Clear Flags Register

CLRFLG — 0309H

7 6 5 4 3 2 1 0

D7D6D5D4D3D2D1D

0

Figure 4-8. Clear Flags Register

The CLRFLG register is a write register which, when written to, clears the Done bit in the STATUS

register. It is data insensitive; any value written to the CLRFLG register will clear Done.

D7-D0 — Not Used. These bits have no function on the VL-12CT96/7. Any value written will cause the

Done bit in the STATUS register to be cleared.

VL-12CT96/7 Analog & Digital I/O Card 4-5

Page 38

Registers — Analog Input Registers

Analog Input Read Registers

Status Register

STATUS — 0300H

7 6 5 4 3 2 1 0

D7D6D5D4D3D2D1D

0

Figure 4-9. Status Register

The STATUS register is a read register which contains the status of the VL-12CT96/7. It can be read

at any time to determine if an A/D conversion is complete, or if a parallel port interrupt is pending.

D7 — Busy. This bit is set to “1” when an A/D conversion is currently in progress. This bit comes directly

from the A/D converter BUSY signal and resets to “0” automatically when the A/D conversion is

complete.

D6 — Done. This bit is set to “1” when an A/D conversion has completed. It indicates that data is

available to be read from the ADCLO and ADCHI registers. When interrupts are enabled, the A/D

interrupt request signal goes active when Done is set.