Page 1

Y8K

Dynamic

Memory

Board

-----,

I

.~

(!

.,~Ci:O=t

~=tAi'l-iC

I

inc.

Page 2

DYNAMIC MEMORY BOARD

:opyright

Revision

February

1979

7,

Vector

3

1979

Graphic

Inc.

Page 3

Copyright

1979

by

Vector

Graphic

Inc.

The

at

on

revi

revision

the

t

he

sed.

Revision

bottom

Title

3 -

number

of

each

page

2/7/78

Revision

and

date

page.

corresponds

of

The

Numbers

release

revision

to

that

of

each

number

of

the

page

and

page

!1erein

date

most

of

r

Page 4

The

48K

Dynamic

faults

and

including

merchantability.

INC.,

customer,

contain

the

48K

will,

repair

defects

1.

Dynamic

2.

defect

claimed

3.

GRAPHIC,

GRAPHIC,

repair

INC.,

INC.,

or

replacement

RAM

Board

without

any

any

implied

warranty,

warranty

However,

for

a

period

or

replace

in

materials

Such

defect

RAM

Board

in

left

VECTOR GRAPHIC,

The

within

48K

to

Dynamic

at

customer's

confirm

ten

if

(10)

found

REPAIR

sold

the

above

of

ninety

any

48K

or

workmanship,

material

the

INC.,

days

RAM

Board

the

to

AGREEMDIT

hereunder

either

of

notwithstanding,

(90)

Dynamic

or

workmanship

VECTOR

is

after

is

expense,

alleged

be

in

order.

is

expressed

fitness

days

RAM

provided:

GRAPHIC,

given

its

promptly

for

defect,

sold

for

"as

intended

following

Board

existed

INC.,

notice

discoverYi

returned

examination

and

is",

or

VECTOR

delivery

that

is

at

factory;

of

the

for

subsequent

with

implied,

use

GRAPHIC,

found

the

time

precise

to

VECTOR

by

VECTOR

all

or

to

to

Repair,

workmanship

forth

expense,

Buyer's

or

correction.

after

in

addition

INC.,

for

required

correction

expiration

INC.,

and

the

GRAPHIC,·

VECTOR

replacement

which

above

will

provided

expense,

expiration

to

the

the

repair

first

rate.

thereafter.

of

defects

of

the

will

submit

VEc'rOR GRAPW'::,

written

estirn:::lce

INC.,

GRAPHIC,

VECTOR GRAPHIC,

correct

returned

its

prior

Repair

GRAPHIC,

any

option

to

Agreement

48K

with

also

commencing

INC.

wi

are

be

performed

the

to

VECTOR

In

performing

of

the

cost

At

hour,

period

to

Buyer a written

INC.,

of

sj

gned

INC.,

INC. I shall

Dynamic

approval

require

work.

void

thin

ten

or

correction

discovered

48K

GRAPHIC,

period

of

the

and

$18.00

Prior

in

material

for

will

charges

by

to

commence

RAM

to

prepayment

if

the

(10)

of

after

by

VECTOR GRAPHIC,

Dynamic

RAM

INC.,

any

repair,

set

forth

parts

present

the

time

per

to

commencing

or

no-cost-to-Buyer

estimate

not

commence

has

been

duly

authorized

with

have

Board

proceed,

no

until

obligation

and

of

enclosed

days

of

any

defects

expiration

Board

for

such

replacement

above,

then-current

the

applicable

hour

for

any

workmanship

repairs,

of

repa.ir

returned

representative

the

the

written

VECTOR

the

estimated

card

end

is

not

consumer

is

returned,

repair,

Buyer

every

repair,

the

by

repair

to

GRAPHIC,

returned

purchase.

1n

material

of

the

period

INC.,

at

Buyer's

also

replacement

or

correction

will

be

charged

VECTOR GRAPHIC,

rate

hour

is

of

$35.00

work

replacement

discovered

v~CTOR

expected

until

such

Buyer

after

GRAPHIC,

charges,

time

to

VECTOR

authorizing

work

repair,

estimate

repair

involved.

replace

has

INC.

I may

charges

to

been

VECTOR

or

set

at

or

as

or

at

Page 5

Vector

Graphic

Section

48K

Dynamic

RAM

Rnn~~

TABLE OF CONTENTS

1

1.

II.

III.

rrable

of

Introduction

1.1

1.2

Theory

of

2.1

2.2

User's

Guicle...................................

3.1

3.2

3.3

3.4

3.5

Contents.

•.

Description

Description

Operation

The

48K

Board

The

Refresh

Modifications

Z-80

Board

3.1.

3.1.

The

READY

Using

Address

Memory

D~lA

of

Test.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

the

of

of

Board

this

•••

Manual.

.................................

1

2

Li

.......

the

Circuitry

Feature

to

the

•••••.•.••..••

Refresh

Reset

ne

•••••••

II

......

Board.

Circuitry.

•••..••.••.••••.

of

the

48K

Board

Signal.

Z-80

Board

and

the

. . . . . . . . .

•..

••.•

••••

. • • 4

• • • 8

••

••

1

2

. 2

2

3

3

.6

.6

.6

'7

.8

.8

.8

IV.

V.

VI.

Spec:.fications

Memory

Schematic

Chip

•••.••••••••••

.•••••

Locations

•.

..10

.11

••

12

nevision

2

1/12/78

Page 6

Vector

Graphic

48K

Dynamic

R.AN

Board

I.

INTRODUCTION

2

!~_l_~Description

The

bytes

It

(Minor

Guide",

beginning

The

Vector

of

can

be

modifications

Vector

Graphic

random

used

below.).

at

OOOOH.

Graphic

Lreakthrough

cumbining

the

refresh

boards

power.

board,

In

3ddition

Board

was

given

It

features

Accepted

supply,

cost

Other

rather

has

design

und

compact

provisions

considerably

to

proven

during

bypass.

of

access

in

ANY

in

cost

inexpensive

dynamic

than

the

the

above

to

design

a

gridded

practice

the

Board

48K

Dynamic

memory,

S-lOO

may

It

be

occupies

48R

effectiveness.

of

the

more,

memory

built

features,

be

remarkably

of

the

ground

was

Memory

using

bus

computer

necessary.

the

Dynamic

dynamic

Z-80

CPU.

take

boards

in

features

the

reliable.

board

plane

observed

24

Memory

memory

up

use

Vector

to

in

Board

16K

dynamic

using

See

lower

This

chips

The

most

more

space,

complex

of

the

the

elimination

designed

structuring

provides

memory

a

Z-80

Section

48K

Board

is

accomplished

of

wi

III,

memory,

is

th

recent

and

support

Z-80.

Graphic

Dynamic

Considerable

to

reduce

grounds,

49,152

8-bit

chips.

CPU

board.

"User's

i.e.

clearly

the

use

static

require-more

logic

on

Memory

attention

of

noise.

noise.

power

a

by

of

RAM

the

1.2

This

Description

manual

Dynamic

operation,

the

board

are

not

provides

Memory

and

is

not

included.

of

the

Board,

information

sold

a

a

as

more

Manual

general

detailed

on

a

kit,

description

how

to

assembly

discussion

use

and

information

of

test

the

of

the

Vectcr

the

board.

and

theory

parts

Graphic

of

Since

list

ru;vision

1 -

1/3/7tl

Page 7

3

2.1

'i'

h

eVe

The

c

provisions

support

1\

Inemory

address

14

address

logic

over

multiplexing

arr~

applied

lines

signal

d,)wn a

does

have

on

chain

the

1.

Generates

2.

Disables

48K

tor

G

of

reference

AO-AIS.

bits

to

had

SMEMR

following

block

strobe

chips.

Board

rap

the

circuitry

must

7

address

the

time

or

of

inverters

a

which

latches

U39,

II.

THEORY

Circuitry

h i c 4 8 K D Y n

Z-80

cycle

Each

be

CPU

on

board,

the

beC]ins

of

supplied

inputs.

chip

a

things

low

to

write

going

is

the

a

tri

address

settle,

signal

in

U13

in

order:

RAS

selected

address

state

OF OPERATION

ami c Me

which

board.

with

the

memory

to

the

Initially

inputs

the

in

MWRITE.

to

initiate

strobe

by

U35

bits

driver.

In 0 r y

the

chips

chips.

by

CPU

for

and

Boa

r d

greatly

CPU

contains

the

low

U39.

board

This

a

timing

the

~ates

internally

use s the

simplifies

board

This

is

order

After

issues

signal

sequence

appropriate

Ull

and

in

sending

16K

done

7

addresses

the

a

memory

propagates

U23.

the

ref

res

bits,

by

time

address

read

which

memory

This

memory

h

the

the

so

3.

Enables

chips.

4.

Generates

chip

a

If

the

cycle

U43

bus

i)

the

in

enables

to

be

DO

bus

of

the

discriminate

The

principal

nee

d

tor

lwcessary

charge

will

the

must

same

l:hip

128

stored

gradually

dielectric.

be

location.

designers,

row

U38,

a

in

the

memory

to

enable

to

write

write

read

is

ch

cycle.

is

a

the

by

buffered

ips.

the

read

bus

the

The

a(Jainst

diff:ccence

e f

res

h

the

because

on

each

a

leak

In

periodically

This

by

executing

addresse~;

within

applying

low

going

chips

the

data

into

cycle

driver

CPU.

by

74

LS244

noi~:e.

br",tween

d a t a s

bi

t

capacitor

away

order

due

to

read

is

out,

accomplished,

a 2

the

-

CAS

strobe

and

initiates

output

the

or

Ml

U41

If

U40

to

the

and

chips

,;tdtic

tor e din

of

da

ta

in

to

the

restore

amplified,

a m

millisecona

high

order

drivers

selected

cycle,

place

cycle

made

have

is

each

finite

the

thanks

only

which

a

timing

if

memory

the

the

is

a

available

Schmi

dnd

a d y n a

represen

memory

insulation

amplitude

and

memory

interval.

7

address

latches

it

is

logic

memory

write

t t t r

dynamic

IT,

i c

HI

ted

"cell".

written

to

the

cycle

lines

the

sequence

a

read

location

associated

data

cycle,

at

the

i9ge

r i

memory

e

In

0 r y . T

by

an

resistance

of

the

back

ingenuity

for

In

other

addresses

cycle,

if

on

data

data

npu

elec t ric

This

charge,

each

dynamic

to

the

in

the

it

with

the

input

ts

is

th(:

his

charge

in

the

of

bf

or

is

Dl

on

to

is

of

it

the

the

](C'vision

- J

1l/7B

Page 8

Vector

Graphic

4~K

Dynamic

PAM

RORrd

4

mel1lory

boards,

complicated

cycles

2.2

with

The

Fortunately,

by

including

incremented

count

when

a

must

RFSH

on

the

signal

be

reclocked

the

memory

0enerate

refresh

There

will

1.

2.

are

be

if

if

priority

CPU

Refresh

the

a 7

every

the

address

address

on

initiated.

by

the

chips.

a

RAS

cycle.

several

interrupted

the

CPU

a

DMA

without

this

is

access

Feature

designers

bit

Ml

bus

bus

is

pin

66

The

system

The

strobe

conditions

which

is

held

dev

ice

generating

done

resolving

cycles.

of

of

refresh

cycle

during

idle.

of

the

timing

clock

output

which

could

in

takes

the

using

the

Z-80

the

and

by

every

The

bus

of

to

satisfy

of

is

under

result

a

wait

control

necessary

counters,

circuitry

Board

Z-80

counter

designing

Vector

to

indicate

this

U23

applied

which

state

provided

in

Ml

cycle

Graphic

signal

the

pin

to

the

in

loss

for

of

the

refresh

to

for

the

the

that

is

timing

8

is

all

normal

of

2

mS

bus

multiplexers

interleave

this

chip

chip

at

Z-80

a

a

to

point

board

ref

modified

requirements

combined

chips

refresh

memory

or

longer.

f.or

more

signals.

refresh

requirement

which

output

in

outputs

resh

by

in

cyc

U24

Ull

during

sequence

data.

than

and

is

the

time

le

and

of

to

the

2

mS

1.

if

the

Condition

occu-

HI.

L'l'

prog

occur

in

since

1

a

system

ram

operaticn.

boards,

which

micro-seconds

Guide,"

for

programmers.

disk

two

period,

Condition

of

board,

wi

Condi~ion

the

Ml

the

are

Lhe

thout

memory

cycle.

PReSET

transfers

usually

on

2

boards

the

(jenerating

3

This

Grounding

CPU

would

exec

the

Caution

typically

during

information

Other

and

the

order

does

use

DMA

has

been

board

consists

signal

PRESET

is

held

not

with

u t

ion.

READY

a

common

to

not

of

not

DMA.

must

the

eliminated

to

generate

connected

allows

in

a

occur

a

in

front

The

line

should

be

hold

programming

on

uses

prevent

a

problem

a few

occur

not

in

If

you

interrupt

necessary

a

of

an

Ul

reset

a

panel

re

is

condition

Vector

where

are

a

popular

othe

exercised

the

CPU

pulse.

handling

of

the

video

due

display

to

microseconds.

a

Vector

are

usin(j

the

refresh

by

providing

to

short

RC

to

be

reset

network

the

set

Graphic

the

r

with

in

See

this

READY

the

Graphic

CPU

signals.

pulse

C8,

front

by

the

for

computer,

READY

ways

way

in

of

PROM

a

wait

Section

problem

line

glitching.

relatively

computer

DMA

alone]

for

additional

synchronized

R12,

panel

next

more

line

wh i

suspending

are

to

longer

Rll,

reset

Ml

than

2 mS.

but

is

used

ch

th

is

programming

state

III,

with

of

"User's

PROM

synchronize

These

short

wait

since

with

the

than

circuitry

with

to

condition

5witch.

cycle

(memory

can

to

can

CPU

600

last

none

4<3K

2 ms

on

a

l~vision

1 -

1/]/78

Page 9

Vector

Graphic

48K

Dynamic

RAH

GOoLJ

5

cycles

can

generating

through

48K

Graphic

to

your

signal

the

board

computer,

Z-80

coming

described

Graphic

modifications

not

be

a

200

open

as

a

CPU

from

in

the

computers

made

interrupted

micro-second

collector

separate

you

will

board

the

48K

User's

shipped

at

the

inverters

board,

have

so

that

board

Guide

factory.

without

pulse

not

to

the

on

(Section

with

loss

to

in

as

make

Reset

pin

the

of

pull

U14.

part

certain

circuit

55.

III

of

48K

data).

unused

If

of

minor

These

this

board

Ul

triggers

bus

line

you

a

complete

purchased

modifications

responds

modifications

manual.)

will

have

U2

55

low

the

Vector

to

the

are

Vector

the

HeV1sion

1

1/3/7B

Page 10

vector

Graphic

48K

U:z,'namic

R.r~;"l

L'

;:~,J

6

3.1

'rhis

on

Modifications

section

the

existing

as

the

bo~[d,

1.

2.

to

is

concerned

48K

HZ,

no

board

systems.

MEMORITE,

changes

and

If

are

REFRESH SIGNAL

proper

coming

cycle

Without

RESET

circuit

reset

than

optional.

reset

result

refreshed

RFSII

from

is

generated

this

CIRCUITRY

of

the

pulse

the

PRESET

It

state

in

loss

while

III.

the

48K

CPU

board

your

or

Vector

required

Jumpers

signal,

your

CPU.

signal,

CPU

board

generated

signal

is

to

for

of

longer

memory

the

USER'S

Board

with

making

in

system

to

3,

is

which

either

can

making

This

during

every

operation

Modifications

so

by

the

on

pin

prevent

than

data,

CPU

is

in

GUIDE

and

Z-80

modifications

order

a

Vector

was

board.

be

use

is

to

is

that

48K

RAM

75.

the

2

milliseconds

since

a

reset

Board

to

use

Graphic

shipped

ins

taIled

of

the

ensure

instruction

not

possible.

can

be

it

responds

board

This

CPU

from

the

state.

to

the

48K

computer

with

to

signal

that

made

on

pin

modification

being

memory

the

prov

presently

a

fetch

to

to

the

which

is

jumpers

board

the

ide

refresh

cycle.

the

55

rather

held

would

not

such

48K

the

reset

short

in

being

in

is

a

'rtw

ubove

3.1.1

1 [

refer

a

no

you

Refresh

--------~~--~~--

a t-e

to

pin

connec t ion

generated

pin

type.

66

of

If

arrangement

inverting

CPU

j

pin

board.

pin

}~~~.2

The

bo~rd.

ulI!I:>cr

98

98.

purpose

be

on

___

Cut

Reset

microseconds)

unused)

two

us

the

by

the

this

the

tween

the

the

to

1tlod

if

Signal

Ing

manual

pin

28

bus

is

on

polarity

Cut

the

pad

bus

trace

Circuitry

of

this

pulse

reset

ications

tlJe

48E

for

0 f

of

using

not

the

the

trace

3

and

instead

modification

generated

the

your

the

the

4BK

of

in

a

pad

arc'a

CPU,

an:

discussed

boarrl

Z-80

~J

CPO

"RfS'H

CPU

i

board

signal

non-inverting

case,

it

board.

the"R'i?'STi

between

1.

of

t\

by

I f

pin

to

the

rather

th

chip

is

Area

signal

66,

pin

is

in

a

non-Vectol"

to

determine

are

and

buffer

necessary

C

if

pad

the

48K

a

(;6

to

2

~

pad

allow

board

than

deta

correct.

should

on

the

it

and

s

is

and

using

il

Graphic

of

to

is

pa~

ig

na

provided

install

the

on

pin

the

be

low:

if

the

Th

be

buffered

the

8097

modify

board

inverted

1

and

1

is

short

55

'R~SET

CPU

board,

polarity

is

signal

or

the

allows

on

connect

broug

Gn

the

a

jumper

(about

(previously

signal

is

onto

74367

jumper

for

the

h t

to

48K

to

200

a

Revision

1 -

1/3/78

Page 11

Vector

Graphic

48K

Dynamic

hA:'·;

L'Jol..J

7

generated

activated

there

Non-Vector

Boards

The

computer

Revision

computers

A

modifications

COMPUTER

RESET

SW

ITCH

are

modification

typical

{

on

pin

by

the

two

different

Graphic

systems,

I

Z-80

shipped

Reset

are

PIN

75

by

front

Z-80

described

including

Board

with

circuit

shown

+5V

\...---4

....

c+

I

_

-

tie

Reset

panel

~Grsions

Boards

(which

static

on

below:

-------I

~~~~~~~;~TIC

25 - 100

TYPI

CAL

switch.

Reset

of

and

below

systems

includes

RAI"!

boards.)

a

Z-80

...

T a z -

mfd

switch.

this

Vector

is

CPU

80

CH

The

modification:

Graphic

applicable

using

all

board

I P

signal

As

the

existing

JUMPER

INSTALLED

and

PIN

on

described

Revision

to

all

Vector

Vector

the

--,

--

S

pin

necessary

55

is

below,

1

Z-80

existing

Graphic

Graphic

....

I----I.~JO

*

z-

80

C~IP

ORIGINAL CIRCUIT

kemove

a

jumper

the

Vector

This

computer,

Z-80

the

2N3643

right-hand

of

the

75.

Hevision

the

from

capacitor.

Graphic

version

CPU

board.

220

ohm

transistor.

the

2-80

100

ohm

Resistor

including

3 -

pin

Z-89

and

corner

board,

resistor

2/7/78

of

Install

180

55

the

of

but

R

and

to

the

Boards

modification

Vector

ohm

This

the

are

and

Capacitor

pad

previously

Graphic

a

jumper

resistor

junction

schematic.

not

provided

the

capacitor

C

from

is

computers,

between

connected

will

Pads

on

which

MOuIFIED

the

board.

connected

relevent

using

pin

55

to

be

found

are

provided

Revision

are

to

to

a

and

the

emitter

near

1.

connected

CIRCUIT

Then

the

any

Vector

the

junction

the

on

Revision

Then,

connect

+

end

existing

Graphic

of

upper

remove

to

of

of

the

2

pin

Page 12

Vector

Grnvhic

48K

Dynamic

R~M

~01~~

8

3.2

Ie

reEr.esh

o[

line

you

If

Caution

The

the

CPU

memory

to

may

you

do,

sequence

HALT

should

typically

programming

should

is

Other

as

execute

follows:

common

transfers

are

usually

on

the

order

READY

data.

NOT

the

hold

LOOP

and

Line

is

held

program

use

system

also

the

pulse.

128

uses

to

not

a

of

a

in

will

be

Since

operation,

the

front

will

be

CPU

After

instructions

PUSH

MVI

DJNZ

POP

of

vrevent

problem

few

microseconds.

a

wait

interrupted

computers

panel

bomb.

exercised

in

a

wait

every

B

13,80H

LOOP

B

the

READY

video

due

state

to

if

your

when

with

state

byte

to

display

the

for

which

with

PROM

of

ensure

line

relatively

2

mS

or

could

a

front

computer

the

48K

Board

programming

600

micro-seconds

programmed,

refresh.

are

to

glitching.

longer,

result

panel

has

a

use

front

is

boards,

a

software

A

typical

synchronize

These

short

wait

the

in

being

normal

the

the

panel,

during

last

period,

loss

READY

used.

which

a

loop

loop

disk

two

3.3

If

i n t

you

err

Usi

up t the

Il':.:cessary

3.4

The

Address

48K

space.

you

will

specifying

3.5

Tllis

or.

4BK

The

Memory

~3ection

at

least

board.

48K

Mor.itor

;;ystem

appear

on.

on

are

refresh

RAM

No

not

board

T

the

DMA

using

CPU

of

board

provision

find

the

address

test

is

relevent

a

Vector

can

command.

TYfJe T

terminal

DMA

for

signals.

the

Board

is

has

any

Graphic

be

Install

0000

along

10

n g e r t

designed

been

reE0rences

of

the

if

you

tested

COOO.

indicating

with

han

made

board.

are

12K

using

the

After

the

to

48K

2

T,l

occupy

to

change

in

this

usin(J

PROM/RAM

the

board

a

few

that

location

S

wit

a

board

Vector

in

board,

h 0 u t

the

lOVler

this.

manual

Vector

your

seconds

the

yen

For

to

Graphic

in

addition

Graphic

system

COOO

COOO

DMA

era

48K

the

(the

t i

of

this

and

XX

first

must

fI

9

the

address

reason,

nlethod

computer

to

Extended

turn

C3

should

PROM

not

of

I

the

the

Revision

1 -

1/3/78

Page 13

Vector

Graphic

48K

Dynamic

Fc'l.r1

L~~,LJ

9

location)

repeat,

Depress

11.

,!lore

the

Vector

Manual.

could

and

the

RESET

thorough

MZ

no

addresses

test

system

not

key

be

written

on

the

can

be

diskette.

other

front

made

to.

than

panel

using

Refer

The

COOO

to

the

to

Appendix

test

should

terminate

MDIAG

will

be

program

J

of

automatically

printed

the

test.

supplied

the

MZ

User's

out.

on

1

Ii

/...,0

Page 14

Vecto~

Graphic

4SK

Dynamic

p~~

~~~r~

SPECIFICATIONS

10

Buffering:

Access

Power

Time:

Consumption:

Phantom:

DMA:

Availability:

49,152

8-bit

Buffered

Compatible

O.25A

Ouput

Must

of

buffer

not

Shipped

bytes

data

wait

+SV

Vector

and

interrup~3the

than

without

necessary

assembled,

and

input

with

Z-SO

states

and

O.20A

disable

Graphic

Go)

Board

2XIO

generating

guaranteed

and

at

compatible

seconds

refresh

tested,

output

4MHZ

of

without

+16V,

PROM/RAM

CPU

for

the

siqnals

burned

1

year;

typical

with

(Reset

longer

in,

no

kits

Revision

I -

1/3/78

Page 15

Vector

Graphic

4BK

Dynamic

RAM

Board

11

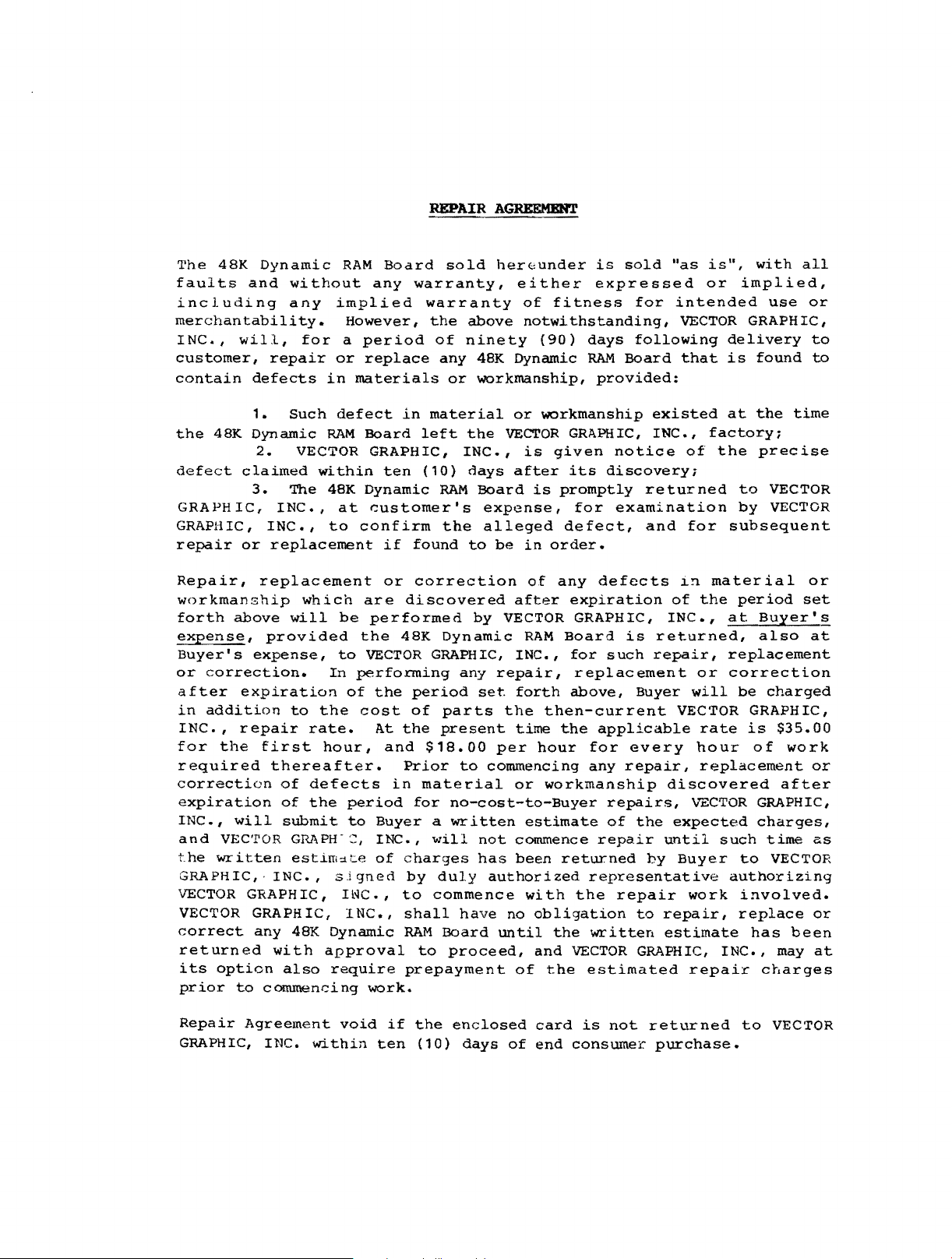

D7

U3

U15

U26

D6

48K

D5

DYNAMIC

MEMO~Y

04

D3

CHIP

02

01

LOCATIONS

00

Ul0

U22

U33

0-3FFF

4000-7FFF

8000-BFFF

Rpvision

1 -

1/3/78

Page 16

D

•

I

«RO

".

5

W

7

l

it>-------""'1-~;''-------_,

."

r4

Uz.<

V.

I

4

6

I

V

4

I

3

I

2

I

,<,

I I

-

D

-

c

B

M

WR

'T[

I!!!>

------------------

• •

-I~

--

'~j;;_;;;:

•

,

..

(

=1

~OC

..

"

:;:'f]~~)o

101

,,--

~S

SO::

--_l----~::::

•

"

~----+----+----~

-

'~---------------+-------------+---------------

::::::::

i_------~

U

"'

•

.'

101(_"

I

T4LSOO

'"

."

." C_S

,.

.,

a"

"n

'"

•

'"

'"

".

,

,

"

,

"

'"

,.

,

~

-1

~---+--~+---4----+-----+---+~

"

'"

,,

'

-

c

B

-

-

---

A

"

I

'"

,<,

7

'"

'"

."

,<,

I

6

l

----------------------

~

I

5

""1

G

131 III

at

l'O

LSn

6

'

~

..

~

.,4

AI,

132

u»

"

I

"

4

"

r4LS02

"

P"ANTOM

A"I'UCATIOH

I

"

v

-.ISS

~-

TOl

~-

-

..

NCUML

DO

3

0_

NOT

..

.. '

$CAU

0I0laf1tD

-

DRAWING

,,,

2

-,,VIII

VECTOR GRAPHIC

48 K

DYNAMIC

MEMORY

MODULE

, , ,

,~

1

-

Loading...

Loading...