Vaishali Semiconductor VT98521S1X, VT98521S1, VT98521-DW, VT98521-D Datasheet

A

dvance Information

V

p

r

T98521

3.3V Low Phase Noise Clock Multi

lie

Applications

•= Oscillator Replacement •= LCD monitor clock source

General Description

The VT98521 is a 3.3V CMOS, clock multiplier integrated circuit. The device provides an excellent quality

high frequency output clock from a lower frequency crystal or clock input. Tri-level selection inputs S0 and

S1 are used to select any one of eight multipliers, stored in the on-board ROM, and apply it to the input to

produce the desired output. The resulting output includes many commonly used frequencies up to 160

MHz. Phase Locked Loop (PLL) technology allows the device to use an input signal from an inexpensive

crystal.

When Output Enable (OE) is low, the clock output is in high impedance state.

The VT98521, when used with an inexpensive crystal, provides a cost-effective clock source for most

electronic systems.

Features

•= Low phase noise

•= Zero ppm multiplication error

•= Input clock frequency 2 - 50 MHz.

•= Input crystal frequency 5 – 27 MHz

•= Output clock frequencies up to 160 MHz.

•= 5V-tolerant inputs and output

•= Exceptionally low jitter: 25 ps one sigma

•= Fully Compatible with all popular CPUs

•= Duty Cycle of 45/55 up to 160 MHz.

•= 25mA drive capability at TTL levels

•= High-Z output for board level testing

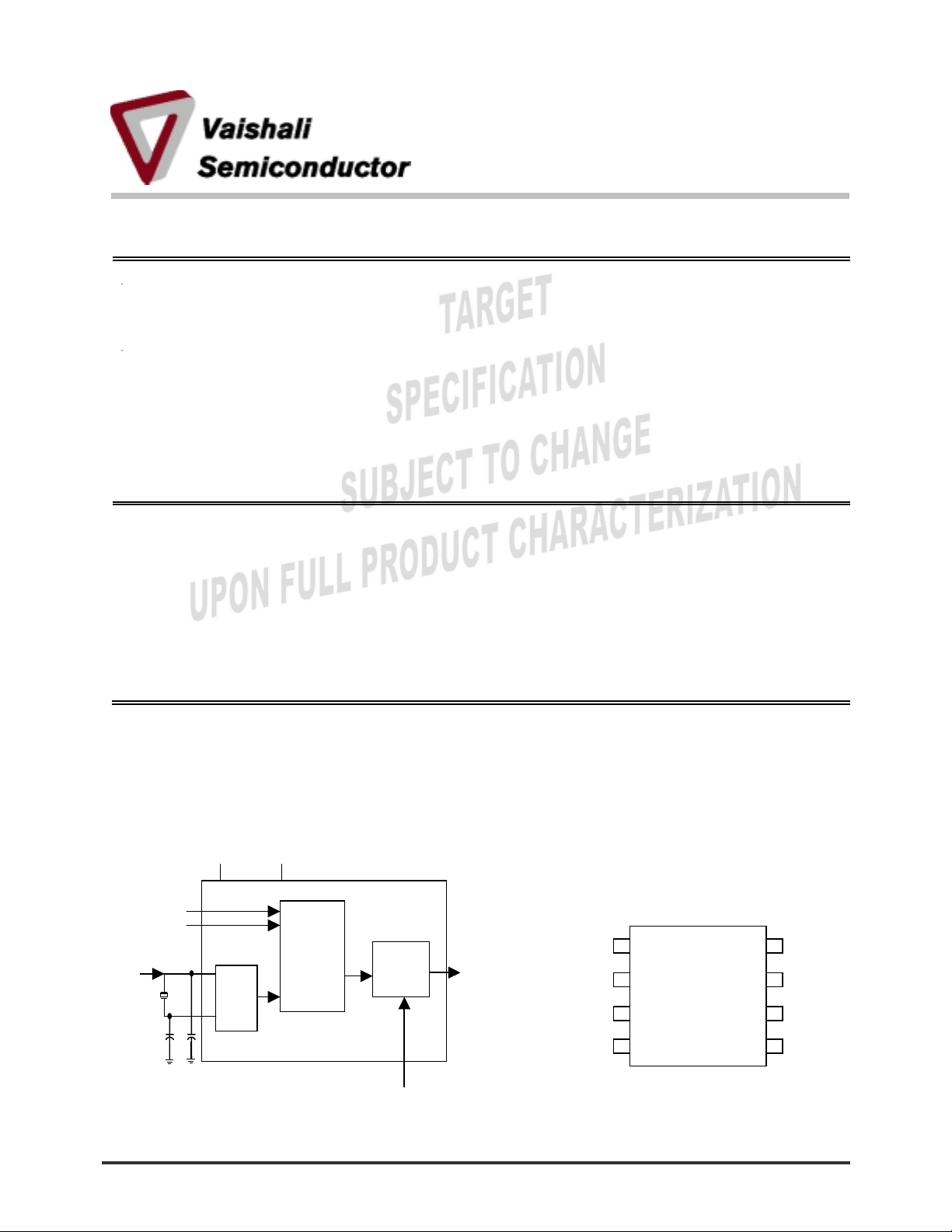

Figure 1. Functional Block Diagram

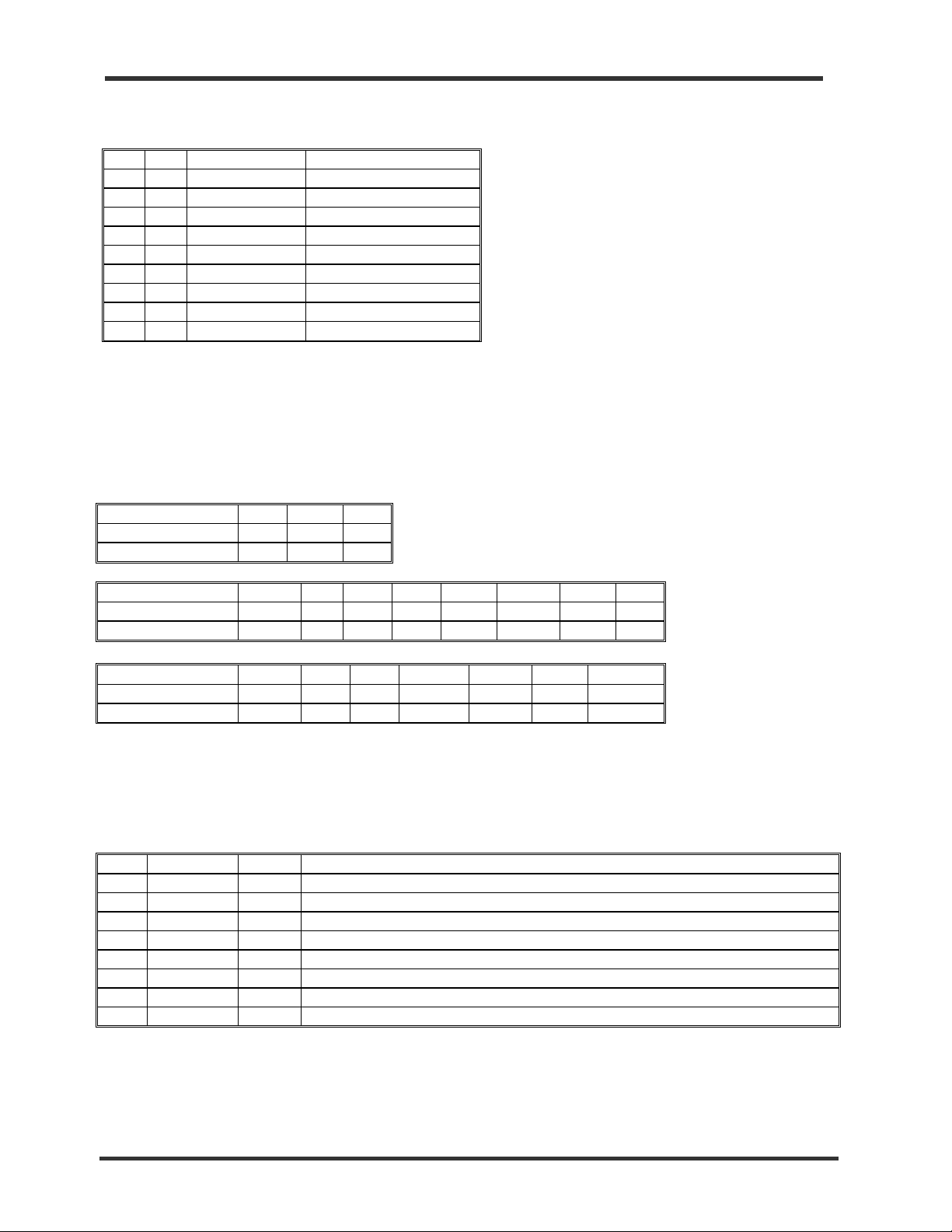

Figure 2. Pin Assignment

VDD

S0

S1

Clock or

Xtal

input

2001-08-27 Page 1 MDST-0017-00

X1/ICLK

X2

Optional

caps

Vaishali Semiconductor 1300 White Oaks Road, Ste. 200 Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063

Xtal.

Osc.

GND

PLL

Clock

Multiplier

&

ROM

Output Enable

Output

Buffer

www.vaishali.com

CLK

X1/ICLK

VDD

GND

S1

8-pin SOIC

1

2

3

4

8

7

6

5

X2

OE

S0

CLK

VT98521 Advance Information

Table 1. Clock Output Table

S1 S0 CLK Minimum Input

0 0 4 x input See table 7

0 M 5.3125 x input 20 MHz

0 1 5 x input See table 7

M 0 6.25 x input 4 MHz

M M Test*

M 1 3.125 x input 8 MHz

1 0 6 x input See table 7

1 M 3 x input See table 7

1 1 8 x input See table 7

0 = Connect to ground.

1 = Connect directly to VDD

M = Leave unconnected (floating)

* = For Vaishali internal test purposes only

Table 2. Examples of Common Output Frequencies.

Output

Input 10 12 10

Selection (S1,S0) M,M M,M 1,M

Output

Input 16.66 10 20 16 16.66 12 12 10

Selection (S1,S0) 1,M 1,0 M,1 0,0 0,0 1,0 M,0 1,1

20 24 30

50 60 62.5 64 66.66 72 75 80

Output

Input 16.66 15 20 20 15 20 19.44

Selection (S1,S0) 0,1 1,0 0,1 0,M 1,1 M,0 1,1

83.33 90 100 106.25 120 125 155.52

Table 3. Pin Description

No. Name Type Description

1 X1/ICLK I Xtal connection or clock input.

2 VDD P Connect to +3.3V

3 GND P Connect to ground.

4 S1 TI Select 1 for output clock. Connect to ground or VDD or float

5 CLK O Clock output per table 2.

6 S0 TI Select 0 for output clock. Connect to ground or VDD or float.

7 OE I Output Enable. Tri- states CLK output when low.

8 X2 O Xtal connection. Leave unconnected for clock input.

Legend:

I = Input

TI = Tri-level Input

O = Output

P = Power supply connection

2001-08-27 Page 2 MDST-0017-00

Vaishali Semiconductor 1300 White Oaks Road, Ste 200 Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063

www.vaishali.com

Loading...

Loading...