Vaishali Semiconductor VT83205S1, VT83205S1X, VT83205QX, VT83205Q, VT83205-D Datasheet

C

VT83205

3.3V Low Phase Noise VCXO

(Voltage-Controlled Crystal Oscillator)

and PLL Clock Synthesizer

Applications

•= Telecom switching

•= Set-top boxes

General Description

The Vaishali VT83205 is a single-chip, integrated VCXO and Phase Locked Loop (PLL) clock synthesizer.

The device uses the VCXO and an analog Phase-Locked Loop (PLL) to accept a 10 MHz to 14.318 MHz,

30pF (pull range of 200 ppm) crystal input, in order to produce either one or two output clocks. A 0 to 3V

control signal is used to fine tune the output clock frequency in the ±100ppm range. Select inputs SO:S2

are used for frequency and output selection.

Features

•= 3.3V supply operation

•= Packaged in 16-pin SOIC & QSOP packages.

•= Replaces separate VCXO and multiplier

•= Uses inexpensive pullable crystal

•= HDTV

•= MPEG Video clock source

•= On-chip VCXO with 200 ppm pull range (±100

ppm)

•= 5V-tolerant control inputs

•= Zero ppm synthesis error in both clocks

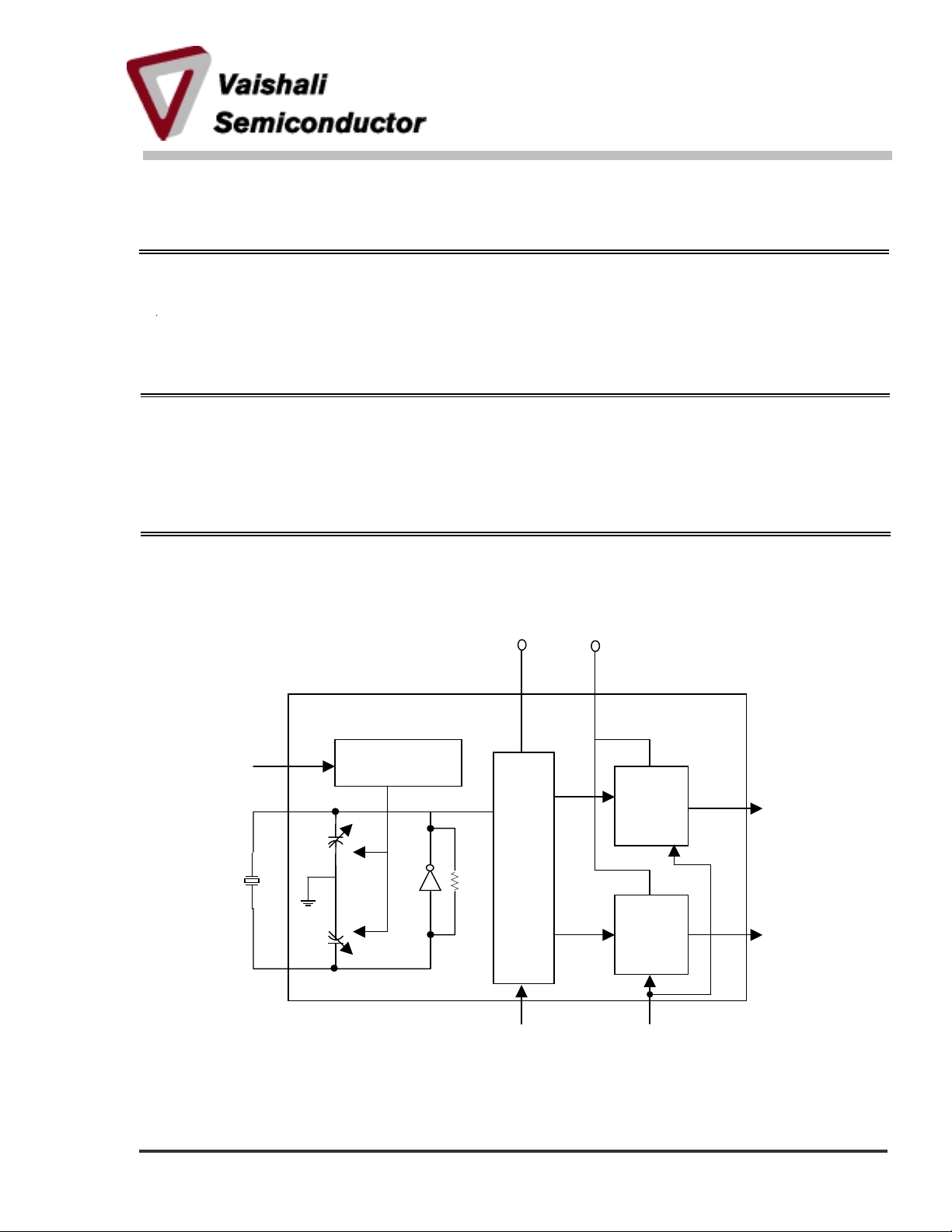

Figure 1. Functional Block Diagram

10-14 MHz

Pullable

Crystal

VIN

X2

X1

Load Cap Control

Load

Caps

VDD1 VDD2

osc

Low

Phase

Noise

PLL

Output

Buffer

Output

Buffer

LK1

CLK2

2001-03-08 Page 1 MDST-0001-01

Vaishali Semiconductor 1300 White Oaks Road, Ste. 200 Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063

S2:S0

www.vaishali.com

OE

VT83205

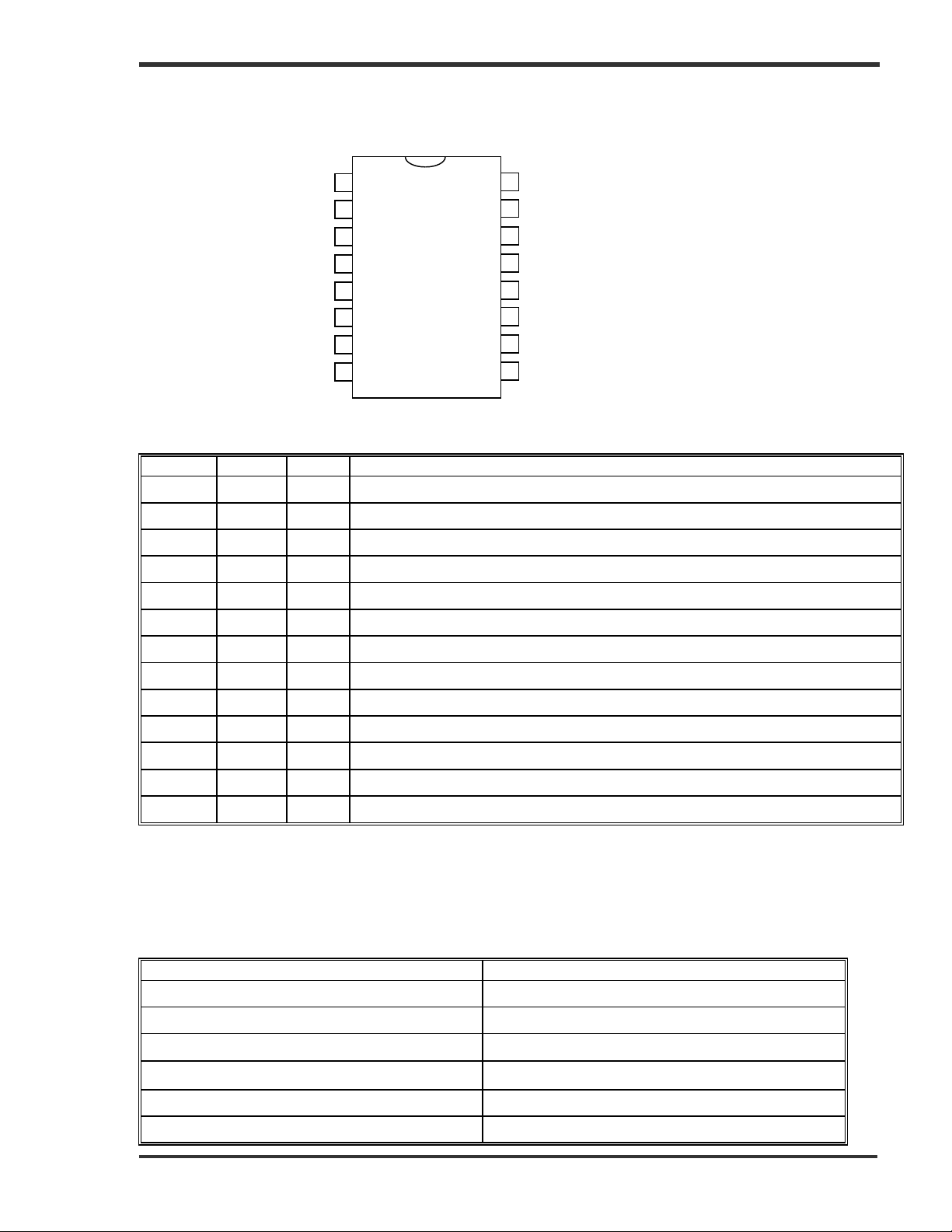

Figure 2. Pin Configuration

VT83205 Pinout

X1

V

DD

V

DD

VIN

GND

GND

OE

S2

1

2

1

3

1

4

5

6

7

8

16

15

14

13

12

11

10

X2

NC

S1

GND

CLK2

VDD2

S0

9

CLK1

Table 1. Pin Description

Name Pin # Type Description

X1 1 XI Crystal connection. Connect to a pullable crystal of 10–14.318 MHz

VDD1 2,3 P Core VDD. Connect to 3.3V

VIN 4 I Voltage input to VCXO. Zero to 3V signal controls the frequency of the VCXO.

GND 5,6,13 P Connect to ground.

S2 7 I Select input #2. Selects outputs per Table 2

OE 8 I Active HIGH Output enable . Outputs in Hi-Z state when LOW

CLK1 9 O Clock output #1 per Table 2.

SO 10 I Select input #0. Selects output per Table 2

VDD2 11 P Output VDD. Connect to 3.3V

CLK2 12 O Clock output #2 per Table 2

S1 14 I Select input #1. Selects outputs per Table 2

NC 15 - There is no internal connection to this pin.

X2 16 XO Crystal connection. Connect to a pullable crystal of 10 MHz – 14.318 MHz.

Legend: I = Input

O = Output

P = Power supply connection

XI, XO = Crystal connections.

Table 2. Pullable Crystal Specifications

Parameter Value

Correlation (load) capacitance 30 pF

C0/C1 240 max

ESR

Operating Temperature

Initial Accuracy ±20 ppm

Temperature + Aging Stability ±50 ppm

2001-03-08 Page 2 MDST-0001-01

www.vaishali.com

Vaishali Semiconductor 1300 White Oaks Road, Ste 200 Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063

35 Ω max

0°C to +70°C

Loading...

Loading...