Vaishali Semiconductor VT73227-S1X, VT73227-S1, VT73227-D Datasheet

2001-04-02 Page 1 MDST-0006-03

Vaishali Semiconductor 1300 White Oaks Road, Ste. 200 Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063

Applications

•= Set-top boxes

•= Telecom switching

•= Oscillator replacement

•= MPEG Video clock source

General Description

The Vaishali VT73227 is a single-chip, low-jitter Voltage-Controlled-Crystal-Oscillator. The device accepts

a 27 MHz, 20 pF (pull range of 200 ppm) crystal input, and produces a low jitter output at the same

frequency. A 0 to 3.0V control signal is used to fine tune the output clock frequency in the ±100ppm range.

Features

•= 3.3V operating voltage

•= Uses inexpensive pullable crystal

•= 12mA drive capability at TTL levels

•= On-chip oscillator with 200 ppm pull

range (±100 ppm)

•= 8 pin SOIC package

VT73227

VCXO

(Voltage-Controlled Crystal Oscillator)

27 MHz 3.3V

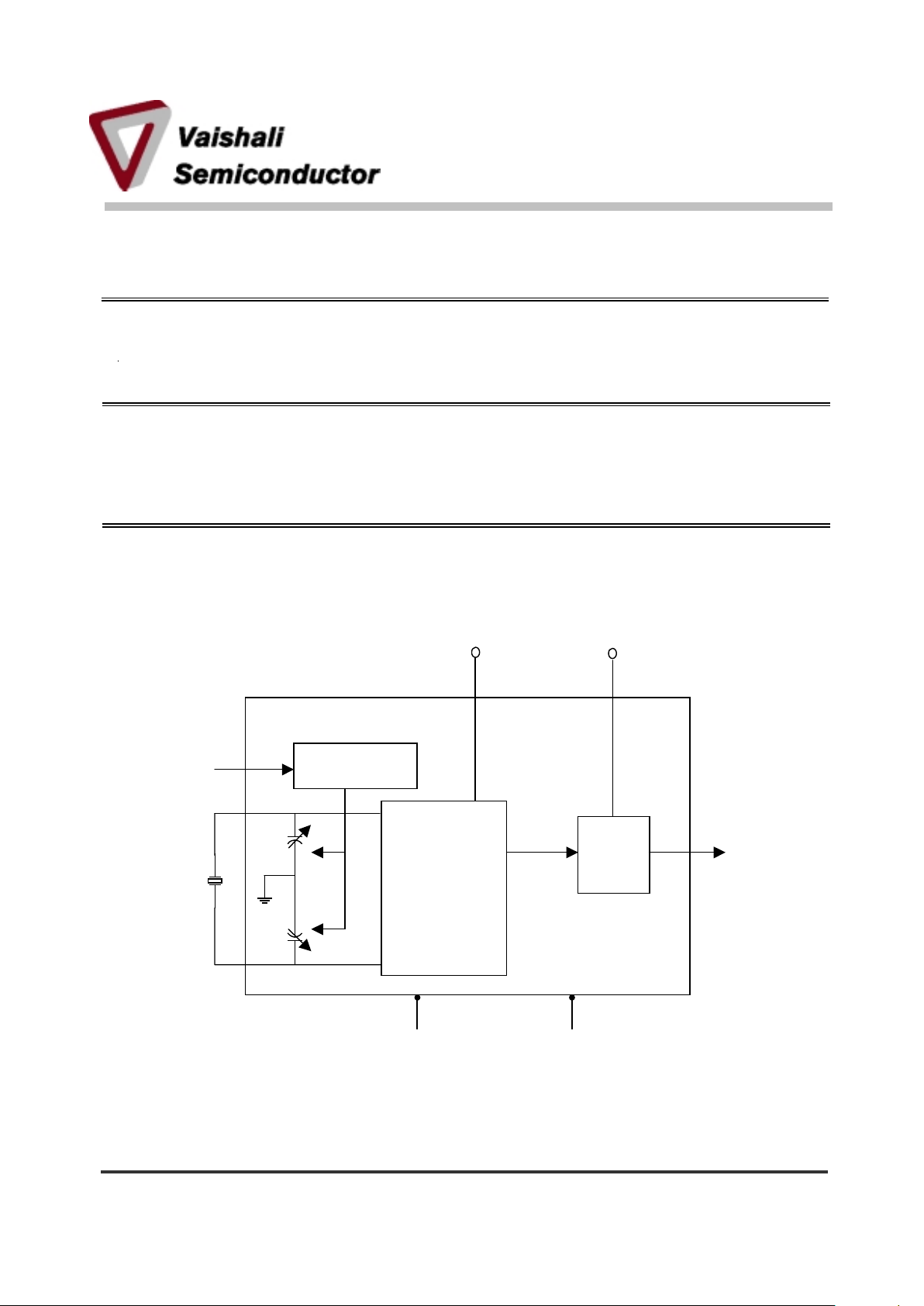

Figure 1. Functional Block Diagram

C

LK1

VDD2

X2

Load Cap Control

Output

Buffer

Load

Caps

VDD1

27 MHz

Pullable

Crystal

VIN

X1

GND1

GND2

Oscillator

VT73227

2001-04-02 Page 2 MDST-0006-03

Vaishali Semiconductor 1300 White Oaks Road, Ste. 200 Campbell CA 95008 Ph. 408.377.6060 Fax 408.377.6063

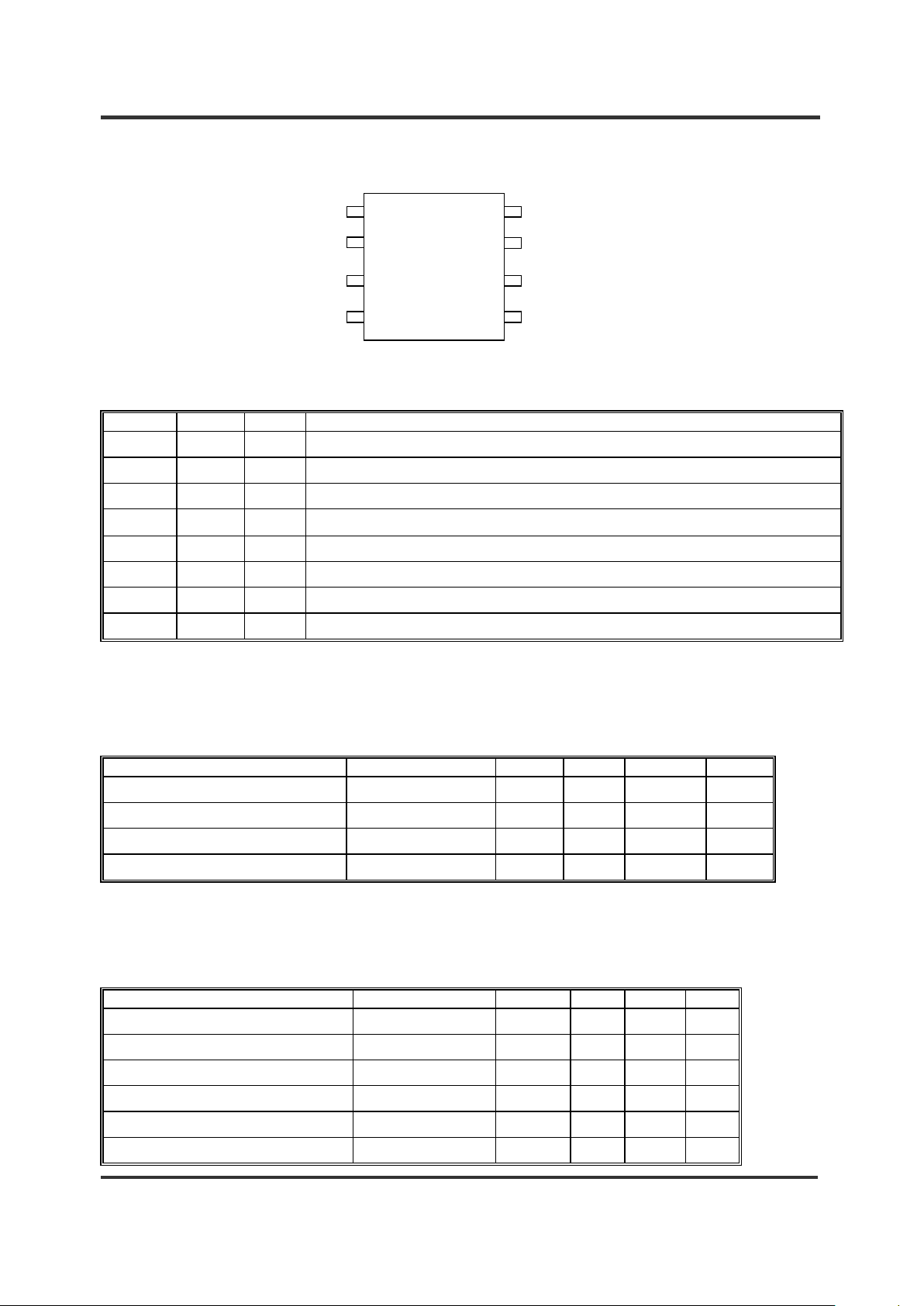

Figure 2. Pin Configuration

Table 1. Pin Description

Name Pin # Type Description

X1 1 Xi Crystal connection. Connect to a 27 MHz pullable crystal

VDD1 2 P Core VDD. Connect to 3.3V

VIN 3 I Voltage input to VCXO. Zero to 3.3V signal controls the frequency of the VCXO.

GND2 4 P Connect to ground.

CLK 5 O Clock output

VDD2 6 P Pad driver V

DD

. Connect to 3.3V

GND1 7 P Connect to ground.

X2 8 Xi Crystal connection. Connect to a 27 MHz pullable crystal.

Legend: I = Input

O = Output

P = Power supply connection

Xi = Crystal connections.

Table 2. Absolute Maximum Ratings

Parameter Conditions Min Typ Max Units

Supply voltage, VDD Referenced to GND 7 V

Inputs and Clock Outputs Referenced to GND -0.5 VDD+0.5 V

Soldering Temperature Max of 10 seconds 260 °C

Storage temperature -65 150 °C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These

ratings are stress specifications only and correct functional operation of the device at these or any other conditions

above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect product reliability.

Table 3. Operating Conditions

Parameter Conditions Min Typ Max Units

Operating Voltage, VDD 3.15 3.3 3.45 V

Input High Voltage, VIH, X1 pin only 2.5 V

Input Low Voltage, VIL, X1 pin only 0.4 V

Operating Temperature 0 70 °C

Input crystal accuracy ±30 ppm

VCXO control voltage, VIN 0 3.3 V

X1 X2

VDD1

VDD2 VIN

GND2

GND1

CLK

VT73227

8 pin (150 mil) SOIC

2

3

4

5

6

7

8

1

Loading...

Loading...