Vaishali Semiconductor VS3V125QX, VS3V125Q Datasheet

Applications

•= 3.3v to 2.5V translation

•= 2.5V to 1.8V translation

•= Hot Swapping

•= Bus switching

VS3V125

3.3V Quad Bus Switch with

Individual Active Low Enables

•= Clock gating

•= Logic replacement

General Description

The VS3V125 contains a set of four high-speed, low-resistance bus switches. Each bus switch is individually

controlled by LVTTL-compatible, ac tive-low control input (/xOE) . The low ON resistance of VS3V125 allows

inputs to be connected to outputs without adding propagation delay and without generating additional signal

noise.

The VS3V125 is designed for 3.3V to 2.5V, or 2.5V to 1.8V level translation, without any external

components. In addition, the high off -is olation between switch terminals in the ‘disable’ mode, and the nearzero propagation delay in the ‘on’ state make the VS3V125 an ideal interface element for hot-swapping

applications.

Features

•= Enhanced N-FET with no dc path to VCC or

GND in normal operating signal voltage range.

•= Low impedance bidirectional data flow

•= Pin-compatible with CBTLV3215 switch

•= Zero added ground bounce or signal noise

•= LVTTL-compatible control signals

•= Undershoot clamp diodes on all

switch and control pins

•= ESD rating >2000V (Human Body

Model) or >200V (Machine Model)

•= Latch-up current >100mA

•= Available in 150-mil wide QSOP

package

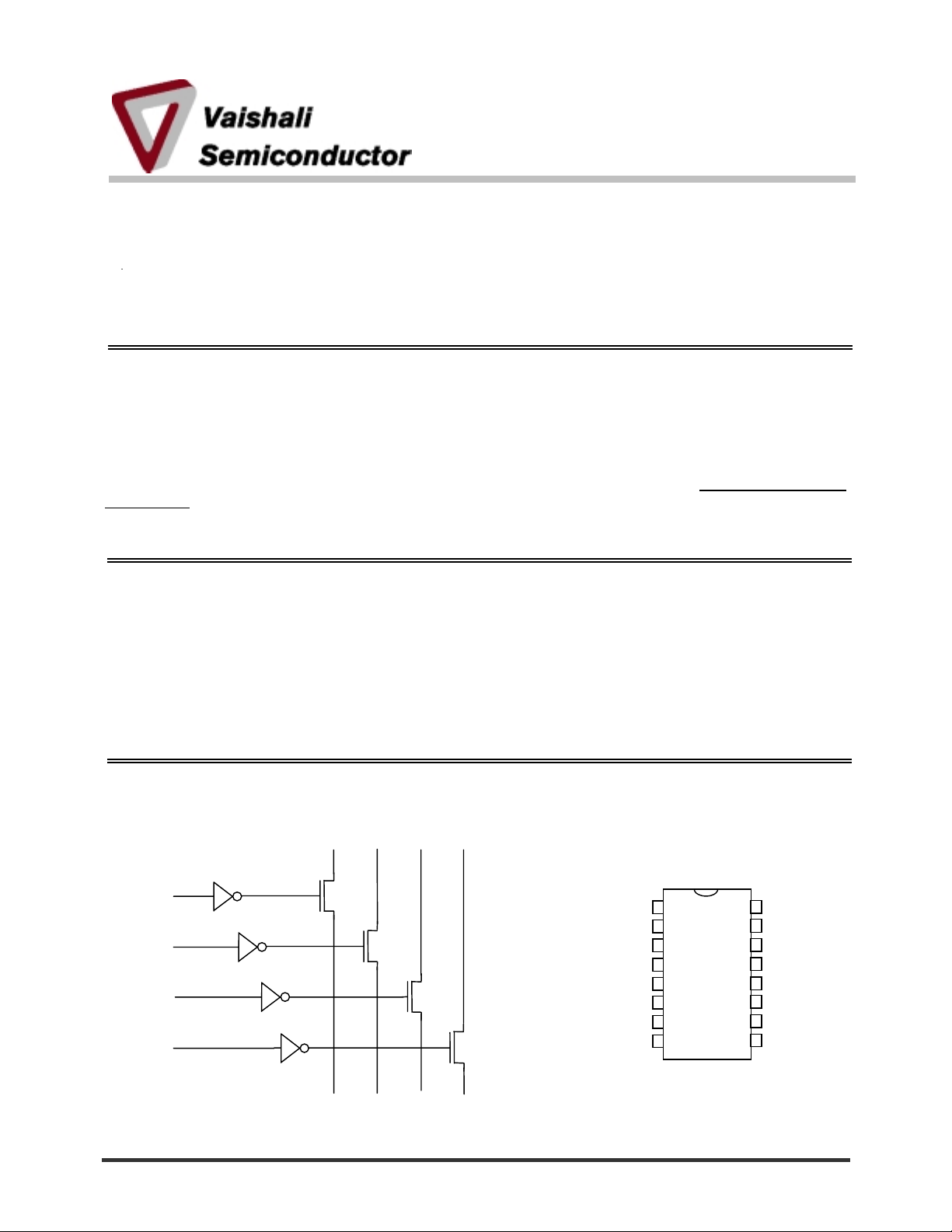

Figure 1. Functional Block Diagram Figure 2. Pin Configuration

/1OE

/2OE

/3OE

/4OE

1A 2A 3A 4A

QSOP

NC

1

/1OE

2

1A

3

1Y

4

/2OE

5

2A

6

2Y

7

GND

8

All Pins, Top View

NC= No Connect

16

15

14

13

12

11

10

V

CC

/4OE

4A

4Y

/3OE

3A

3Y

9

NC

1Y 2Y 3Y 4Y

2001-04-12 Page 1 MDSS-0002-02

www.vaishali.com

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

VS3V125

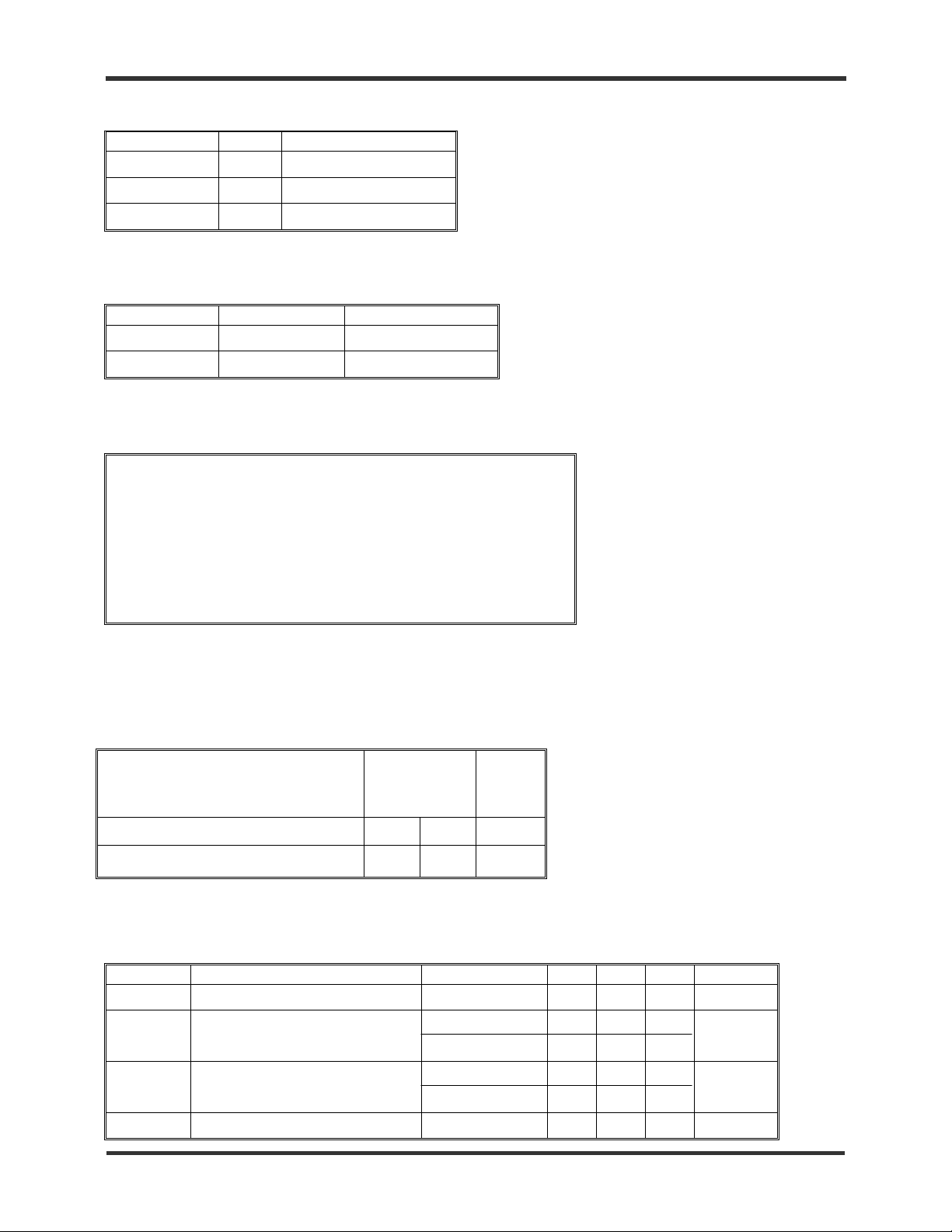

Table 1. Pin Description

Name I/O Description

1A – 4A I/O Data Input or Output

1Y – 4Y I/O Data Input or Output

/1OE - /4OE I Bus Switch Enable

Table 2. Function Table

/xOE Path Function

L xA <-> xY Enable switch

H High Impedance Disable switch

Table 3. Absolute Maximum Ratings

Supply Voltage to Ground………………………….…..-0.5V to +4.6V

DC Switch Voltage VS……………………….………….-0.5V to +4.6V

DC Input Voltage VIN…………………………………...-0.5V to +4.6V

AC Input Voltage (Pulse Width < 20ns)……………….…………-3.0V

DC Output Sink Current per Switch Pin…………………...…..120mA

Maximum Power Dissipation…………………………….…..0.5 Watts

Storage Temperature………………………………...-65oC to +150oC

Note ABSOLUTE MAXIMUM CONTINUOUS RATINGS are those values beyond which damage to the device may

occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability.

Functional operation under absolute maximum rated conditions is not implied.

Table 4. Capacitance

TA = 25oC, f = 1MHz, VIN = 0V, V

OUT

= 0V

QSOP

Pins Typ Max Unit

Control Inputs 4 5 pF

VSwitch Channels ( Switch OFF ) 5 7 pF

Note Capacitance is guaranteed, but not production tested. Total capacitance of a path, when the switch is closed, is

the sum of the switch terminal capacitances.

Table 5. Recommended Operating Conditions

Symbol Parameter Conditions Min Typ Max Units

VCC Power supply voltage 2.3 3.6 V

VIL Low level input voltage

(Control inputs)

VIH High level input voltage

(Control inputs)

TA Operating free-air temperature -40 85

Note: All unused control i nputs of the device must be held at Vcc or GND, to ensure proper device operation

2001-04-12 Page 2 MDSS-0002-002

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

Vcc = 2.3 to 2.7

Vcc =2.7 to 3.6

Vcc = 2.3 to 2.7

Vcc = 2.7 to 3.6

www.vaishali.com

0.7

0.8

1.7

2.0

V

V

o

C

Loading...

Loading...