Vaishali Semiconductor VN16218L2 Datasheet

r

Advance Information

VN16218

2.5 Gigabit SERDES Transceive

Applications

•= Fast serial backplane transceiver •= High-speed point-to-point links

General Description

The VN16218 is a low power single chip, 2.5GBd transceiver . It provides a 2.5GBd serial link interface in

the physical layer and includes a Serialize/Deserialize (SERDES) capability. Other functions inc lude clock

generation, clock data recovery, and word synchronization. In addition, an internal loopback function is

provided for system debugging.

The VN16218 is ideal for 2.5 Gigabit, serial backplane and proprietary point-to-point applications. The

device supports both fiber-optic and copper media.

The transmitter sec tion of the VN16218 ac c epts 20- bit wide TTL data and latches it on the rising edge of the

incoming Trans mit Byte Clock (TBC) and serializes the data onto the TX ± differential outputs, at a baud rate

that is twenty times the TBC frequency. The data is converted to a high-speed serial data stream . The

transmit PLL loc k s to the 125 MHz TBC. This cloc k is then multiplied by 20 to supply a 2.5 GHz serial clock

for parallel-to-ser ial conversion. T he high-speed serial outputs can interfac e directly with copper cables or

PCB traces. W here optical transm ission is requir ed, the outputs can connect to a separate optical module.

When copper lines are the medium, equalization is available for improved performance.

The receiver section of the VN16218 accepts a serial data stream of 2.5 GBd and recovers 20 bit parallel

data. The rec eiver PLL lock s on to the incoming s erial signal and recovers the high-speed inc oming clock

and data. The serial data is converted back into 20-bit parallel data format. Byte alignment is accomplished

by optional recognition of the K28.5+ comma character.

The recovered parallel data is sent to CMOS outputs , together with two 125 MHz clocks, RBC and RBCN,

that are 180 degrees out of phase from each other.

Features

•= 20-bit wide parallel Tx, Rx busses

•= 20-bit LVTTL interface for transmit and

receive data at 125 MHz

•= 125 MHz complementary receive and

byte clocks

•= Low Power Consumption

•= ESD rating >2000V (Human Body Model)

or >200V (Machine Model)

2001-11-09 Page 1 MDSN-0003-00

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 Ph. 408.377.6060 Fax 408.377.6063

www.vaishali.com

•= Parallel loopback mode

•= Available in 14 mm x 14 mm

LQFP package

•= Differential PECL serial output

•= I/O power supply 3.3V

•= Core power supply 1.8 V

COM DET

RBC

RBCN

VSST

VSSA

NC

VSST

TBC/REFNCVSS

VDD

TEST1

EQEN

EN

CD

RX-F

EWR

TEST2

VDDP77VSSP

VDDP75TX

TX

VDDT72VSSA

VDDA70VSSA

VDDA68RX

RX

VDD

A

RX064RX1063RX1

RX11

VSSA

VN16218 Advance Information

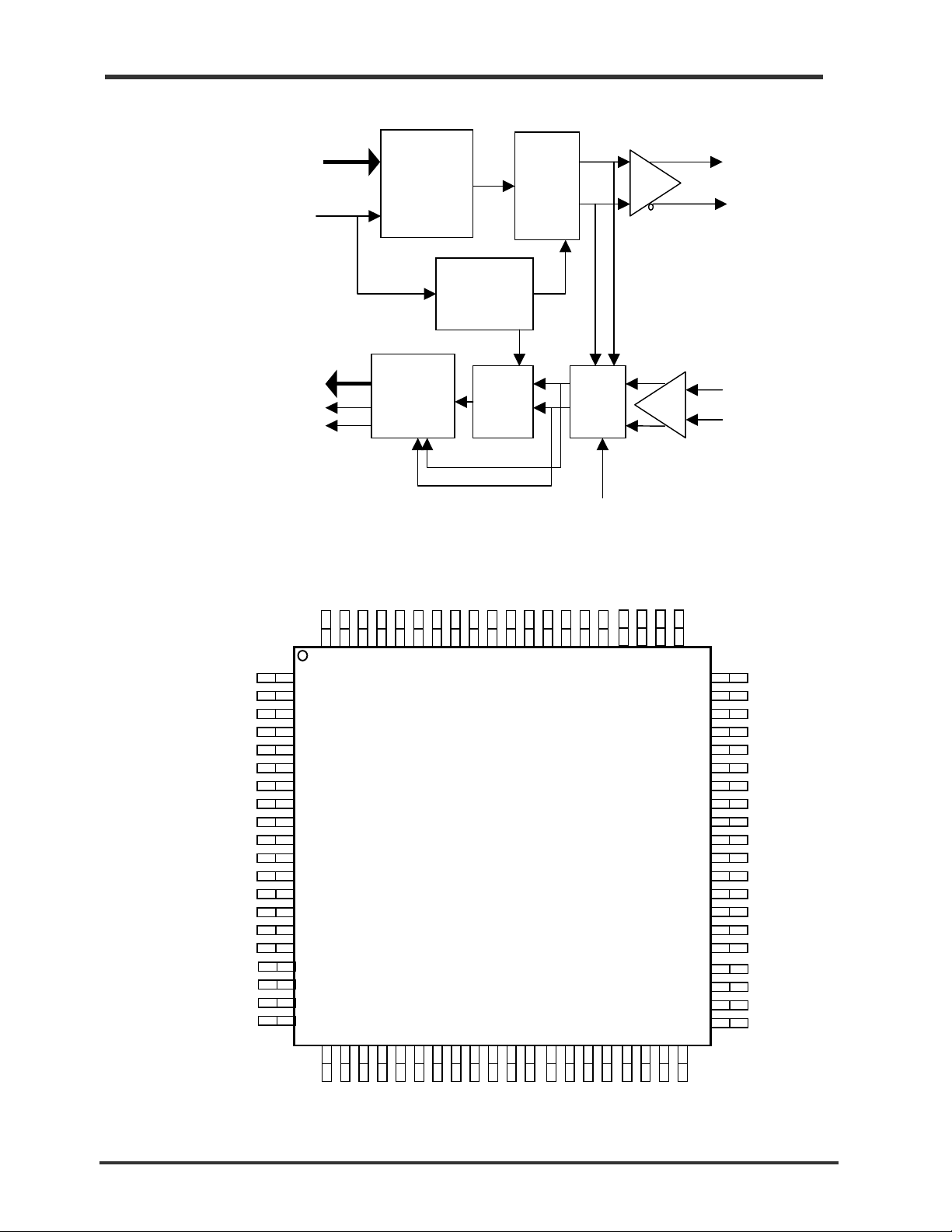

Figure 1. Functional Block Diagram

T[0:19]

TBC/REF

(125 MHz)

Input Latch

Parallel

Serial

Converter

to

D+

D-

Line

Driver

TX+

TX-

RCLK (125MHz)

R[0:19]

Comma Detect

Serial

Parallel

Converter

to

PLL Clock

Multiply X 20

Clock

Recovery

Mux 4:2

Equalizer

Loopback Enable

RX+

RX-

Figure 2. Pin Configuration

-

+

VDDT

TX0

TX10

TX1

TX11

TX2

VSS

TX12

TX3

TX13

TX4

TX14

80

79 NC78

1

2

3

4

5

6

7

8

9

10

11

12

13 VDD

14 TX5

15 TX15

16 TX6

17 TX16

18 TX7

19 TX17

20 TX8

21 22 23 24 25 26 27 28 29 30 31 32

76

74

73

71

TX9

TX19

TX18

VDDA

2001-11-09 Page 2 MDSN-0003-00

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

www.vaishali.com

+

69

33 34 35 36

67

-

62

66

-

65

37 38 39 40

61

60 VSS

59 RX2

58 RX12

57 RX3

56 RX13

55 RX4

54 RX14

53 VDD

52 RX5

51 RX15

50 RX6

49 RX16

48 RX7

47 RX17

46 VDD

45 RX8

44 RX18

43 RX9

42 RX19

41 VSS

VN16218 Advance Information

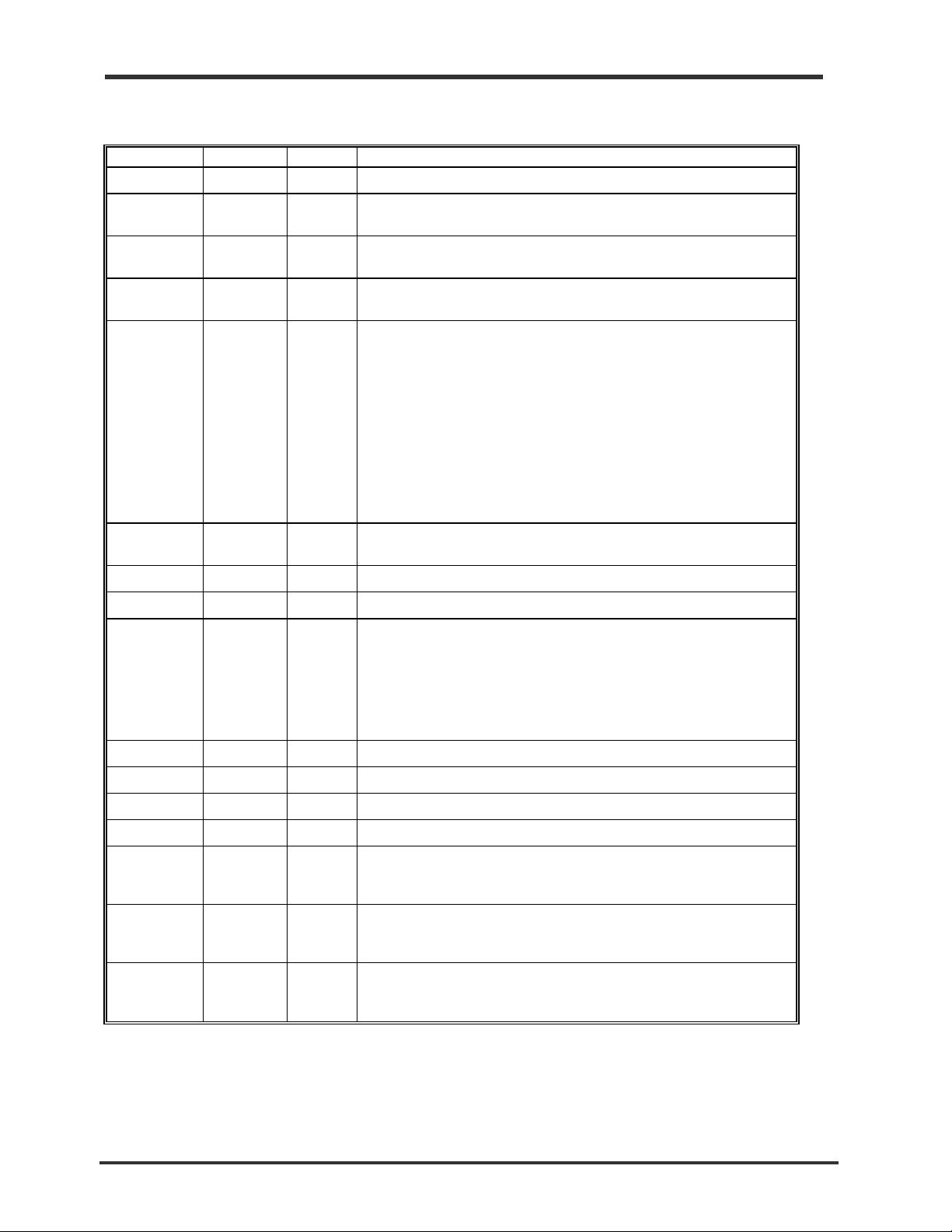

Table 1. Pin Description

Name Pin # Type Description

VDDT 1, 73 P 3.3V power supply

VSS 7, 30, 41,

60

VDD 13, 31, 46,

53

VDDA 21, 66, 69,

71

TX[0:19]

VSSA 25, 61, 70,

NC 26, 29, 79 No Connection

VSST 27, 40 P TTL ground

TBC/REF 28 I-TTL Transmit Byte Clock / Reference Clock . A 125 MHz clock supplied

2, 4, 6

9,11, 14

16, 18, 20

23, 3, 5

8,10,12

15, 17, 19

22, 24

72

P Digital Ground. 0V

P Digital Power Supply. Connect to 1.8V

P Analog Power Supply. Connect to 1.8V

I-TTL Transmit Data Bus (bits 0 through 19). 20 bit transmit character.

Parallel data on this bus is clocked in on the rising edge of TBC.

The data bit corresponding to T0 is transmitted first

P Analog Ground. 0V

by the host system. The transmitter section accepts this signal as

the frequency reference clock. It is multiplied by 20 to generate the

serial bit clock and other internal clocks. The transmit side also

uses this clock as the transmit byte clock for the incoming parallel

data TX0 …. TX19. It also serves as the reference clock for the

receive portion of the transceiver

TEST1 32 I-TTL Test pin. For Vaishali use only. User should connect to VDD

EQEN 33 I-TTL Equalizer enable

EN_CD 34 I-TTL Enables comma detect

RX-F 35 O Receiver filter pin. For Vaishali use only.

EWR 36 I-TTL Enable Internal WRAP mode. This pin is LOW in normal operation.

When enabled High, an internal loop-back path from the transmitter

to the receiver is enabled, TX+ is HIGH and TX- is LOW

COM_DET 37 O-TTL Comma Detect. This output goes HIGH to signify that R0:6 contains

a comma character (0011111). COM_DET can be sampled on the

rising edge of TBC

RBC, RBCN 38, 39 O-TTL Recovered Byte Clock. Recovered clock and its complement

derived from the RX± data rate divided by 20. The rising edge of

RBC corresponds to a new word on RX[0:19]

2001-11-09 Page 3 MDSN-0003-00

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

www.vaishali.com

VN16218 Advance Information

Name Pin # Type Description

RX[0:19]

RX+, RX- 68, 67 I-diff Receiver serial inputs. The device recognizes receiver inputs when

TX+, TX- 74, 75 O diff Transmitter serial ouputs. When EWR is LOW, the serialized

VDDP 76,78 P High-speed output driver power supply. Connect to 1.8V

VSSP 77 P High speed output driver ground. 0V

TEST2 80 I-TTL Test pin for Vaishali internal use only. User should tie this pin to

Legend: I = Input

O = Output

P = Power supply connection

65, 63, 59

57, 55, 52

50, 48, 45

43, 64 ,62

58, 56, 54

51,49,47

44, 42

O-TTL Receive Data Bus, Bits 0 through 19. 20 bit received data

character. Parallel data on this bus can be sampled on the rising

edge of RBC. R0 is the first bit received on RX+/RX-

EWR is LOW

transmit data is available on these pins. When EWR is HIGH, TX+

is HIGH and TX- is LOW

GND for normal operation

Functional Block Description

PLL Clock Multiplier

The VN16218 employs a user-supplied 125 MHz clock both as a reference clock and as a Transmit Byte

Clock (TBC). The PLL Clock Multiplier multiplies the TBC by 20 to generate a baud rate clock of 2.5 GHz.

The TBC also clocks in the incoming parallel data.

Serializer (Parallel-to-Serial Converter)

Input data arrives at the T[0:19] bus as two parallel 10 bit characters and is latched into the input latch on

the rising edge of TBC. The data is serialized and transmitted on the TX differential outputs at a baud rate

of twenty times the frequency of TBC. Bit T0 is transmitted first. Incoming data is already encoded for

transmission using either the 8B/10B block code, as specified in the Fibre Channel specification, or an

equivalent edge-rich, DC-balanced code. If EWR is HIGH, the transmitter will be disabled, with TX+ HIGH

and TX- LOW. If EWR is LOW, the transmitter outputs serialized data. According to the fibre channel

specification, a transmission character is an encoded byte of 10 bits. The 20 bit interface of the VN16218

corresponds to two transmission characters, as shown in Table 2 below.

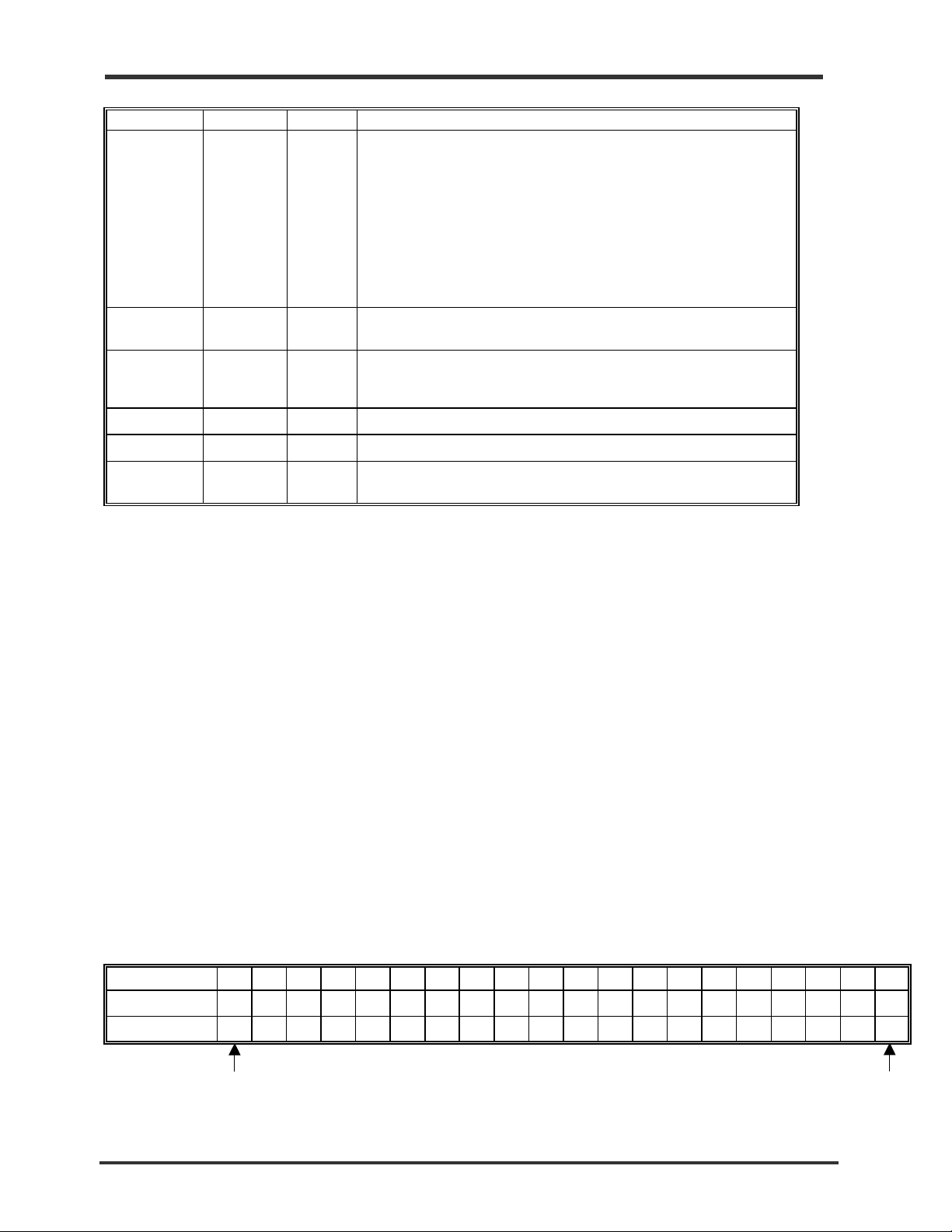

Table 2. Transmission Sequence and Mapping to Fibre Channel Characte r

Parallel Data Bits

8B/10Bit Position

Valid Comma Pos.

Last Data Bit Transm i tted

19 18 17 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

j h g f i e d c b a j h g f i e d c b a

1 1 1 1 1 0 0

First Data Bit Transmitted

2001-11-09 Page 4 MDSN-0003-00

Vaishali Semic onductor 747 Camden Avenue, Suite C Cam pbel l CA 95008 P h. 408.377.6060 Fax 408.377.6063

www.vaishali.com

Loading...

Loading...