V3 Semiconductor V380SDC-75REVA0 Datasheet

© 2000 V3 Semiconductor Corp. V380SDC_A0 Datasheet Rev 1.01 DS-SD01-0101

1

V380SDC A0 Datasheet

V380SDC High Performance SDRAM Controller

for 32-bit and 64-bit Embedded Processors

1.0 About the V380SDC

▼

Direct interface to these processors:

• AMD

®

AM29030/40™

• IBM

®

PowerPC 401™ Gx

• IDT

®

79RC32364™

• Intel

®

i960

®

Cx/Hx/Jx/Rx/Vx

• Motorola

®

M68040™ and 68K/ColdFire

®

• PowerPC™ 750/60x

▼

Up to 75 MHz local bus clock

▼

Up to 2 Kbytes of continuous burst access for

64-bit processors and 1 Kbyte for 32-bit

processors

▼

Zero-wait-state bursting

▼

Dynamic bus protocol switching

▼

User-customized processor bus interface

▼

Support for up to 2 Gbytes of (Enhanced)

SDRAM

▼

Compatible with PC66, PC100, PC133 SDRAM

▼

Supports a wide range of synchronous DRAMs,

from 16 Mbit to 256 Mbit

▼

Support for up to 4 single-bank or 2 dual-bank

industry standard 168-pin SDRAM DIMM(s) or

144-pin SO-DIMM(s)

▼

I

2

C EEPROM interface for Serial Presence

Detect (SPD) on DIMM

▼

Optional EEPROM initialization

▼

8-bit bus watch timer

▼

System heartbeat and watchdog timers

▼

Two 32-bit general purpose timers with pulsewidth modulation capability—useful for RTOS

▼

16-bytes of general purpose registers

▼

Designed to work with the EPC family of PCI

bridges from V3 Semiconductor

▼

3.3 V operation with 5 V tolerant inputs

▼

Industrial temperature range (

− 40°C to +85°C)

▼

Low-cost 100-pin PQFP package

DS-SD01-0101.fm Page 1 Monday, June 5, 2000 11:03 AM

About the V380SDC

2

V380SDC_A0 Datasheet Rev 1.01 DS-SD01-0101 © 2000 V3 Semiconductor Corp.

The V380SDC High Performance SDRAM Controller provides all aspects of SDRAM control for high performance

embedded systems. The V380SDC enables system designers to replace many lower integration support components

with a single, high-integration device. This saves design time, board space, and manufacturing cost.

The V380SDC from V3 Semiconductor provides the necessary (Enhanced) SDRAM access protocol and bus timing

resources to work with the latest (E)SDRAM devices. The processor interface on the V380SDC implements the bus

protocol of many popular RISC CPUs (AM29030/40, PowerPC 401 Gx, IDT 79RC32364, i960 Cx/Hx/Jx/Rx/Vx,

M68040, 68K/ColdFire, PowerPC 750/60x). The V380SDC is also fully compatible with the EPC family of PCI

bridges available from V3 Semiconductor.

The

V380SDC

supports a total SDRAM memory subsystem size of up to 2 Gbytes. Standard memory devices from

16 Mbit to 256 Mbit are supported; 8-, 16-, 32-bit and 64-bit accesses are allowed. Four single-bank or two dualbank industry standard 168-pin PC SDRAM DIMM(s) or 144-pin SO-DIMM(s) with Serial Presence Detect (SPD)

are also supported.

The

V380SDC

provides an 8-bit bus watch timer to detect and recover from accesses to unpopulated memory

regions. Two on-chip, general purpose, 32-bit timers can be individually configured as a pulse width modulator or

they may be used in other modes such as retriggerable or one-shot.

The

V380SDC

is packaged in a low-cost 100-pin EIJA Plastic Quad Flat Pack (PQFP), and is available in 75 MHz

speed grade.

This document contains the product codes, pinout, package mechanical information, DC characteristics, and AC

characteristics for the V380SDC. Detailed functional information is contained in the User’s Manual.

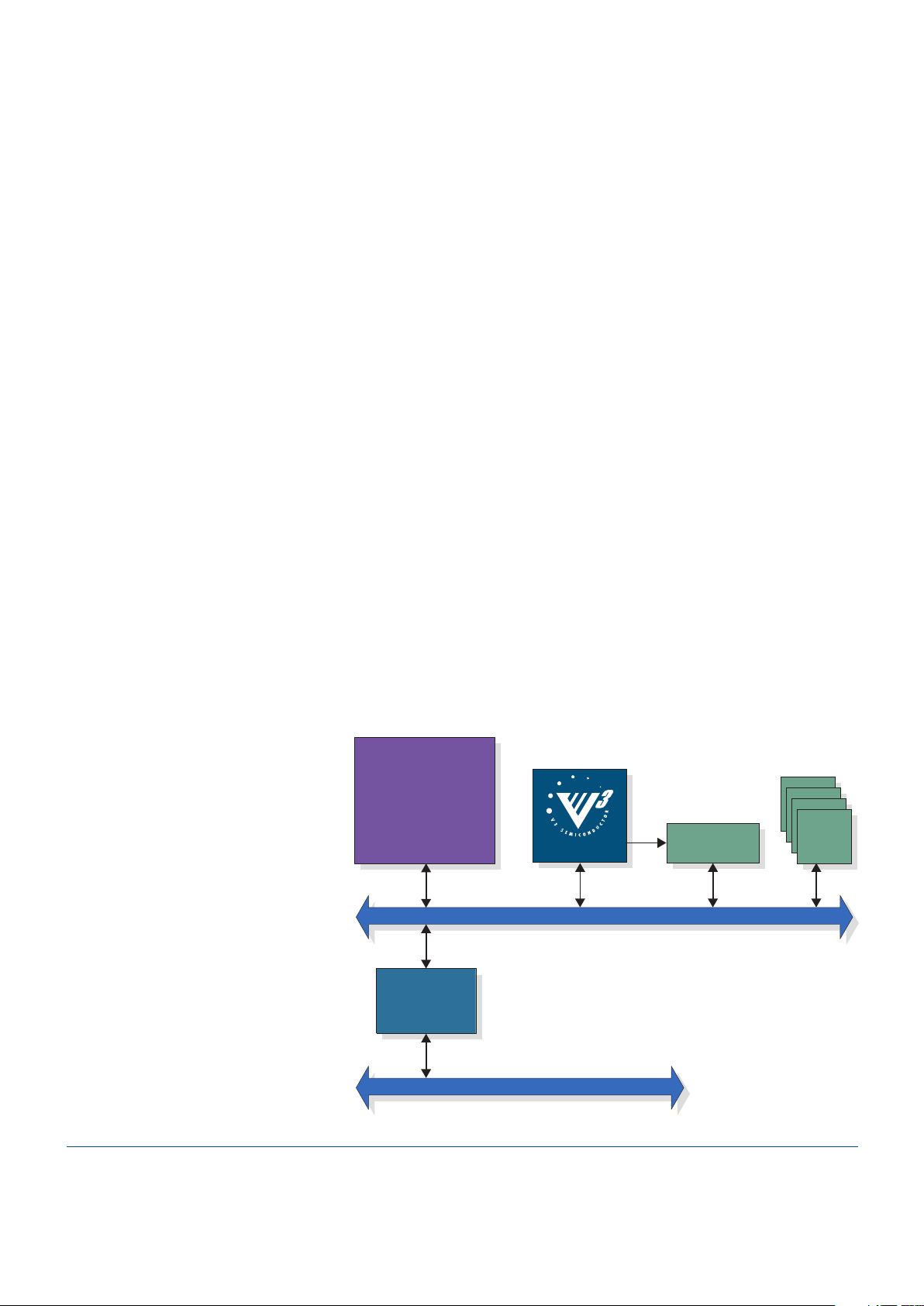

Figure 1: Example Application

Note:

V3 Semiconductor retains

the rights to change the

documentation, the

specifications, or device

functionality at any time

without notice. Contact V3

and verify that you have the

latest copy of all documents

before finalizing a design.

i960Cx/Hx/Jx/Rx/Vx,

PowerPC 401Gx,

IDT 79RC32364,

M68040/ColdFire/68K,

PowerPC 750, or

Am29030/40

Processor

V3

Local-to-PCI

Bridge

SDRAM

DIMM(s)

Flash

Local Bus

PCI Bus

V380SDC

DS-SD01-0101.fm Page 2 Monday, June 5, 2000 11:03 AM

Product Codes

© 2000 V3 Semiconductor Corp. V380SDC_A0 Datasheet Rev 1.01 DS-SD01-0101

3

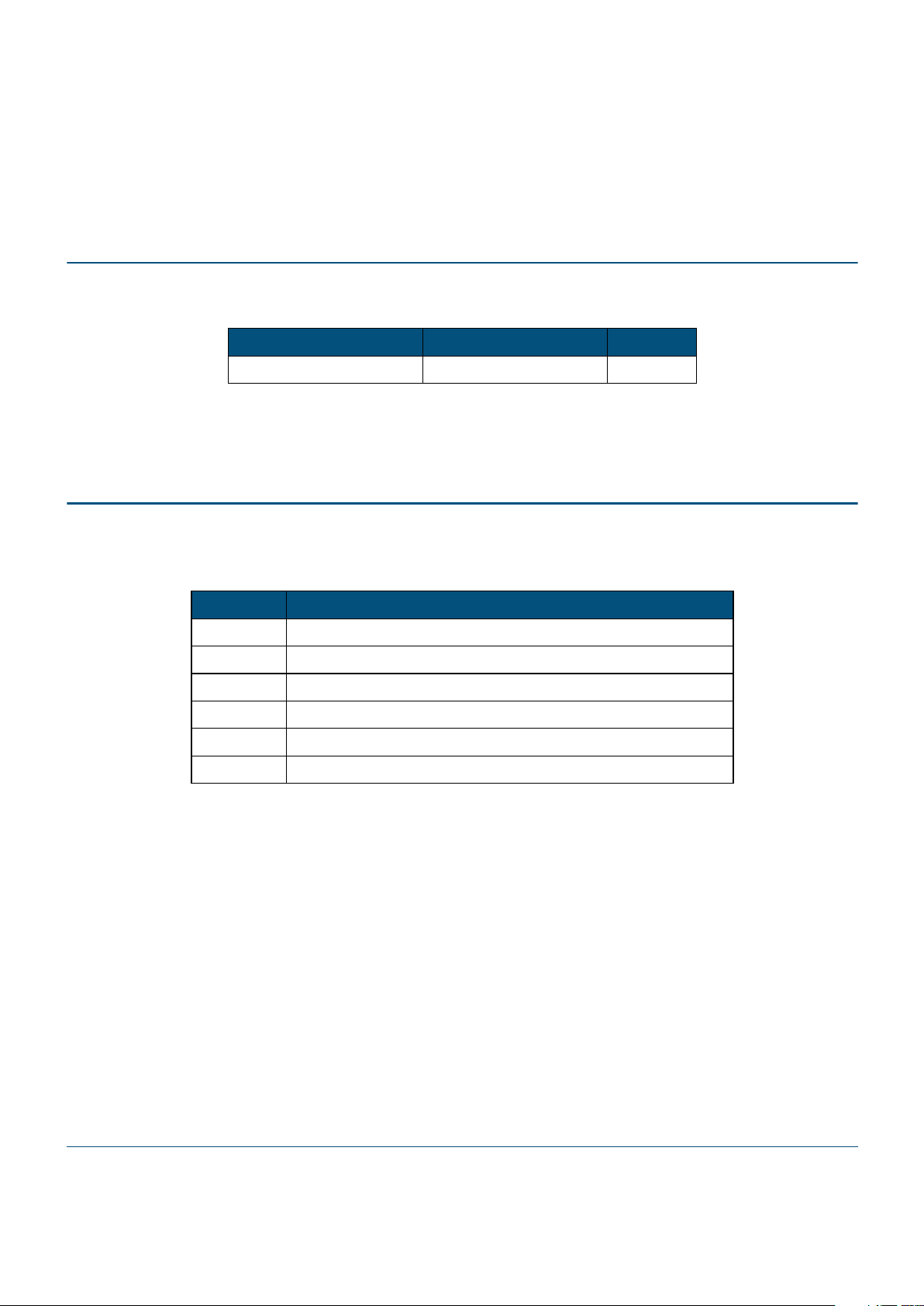

2.0 Product Codes

3.0 Pin Description

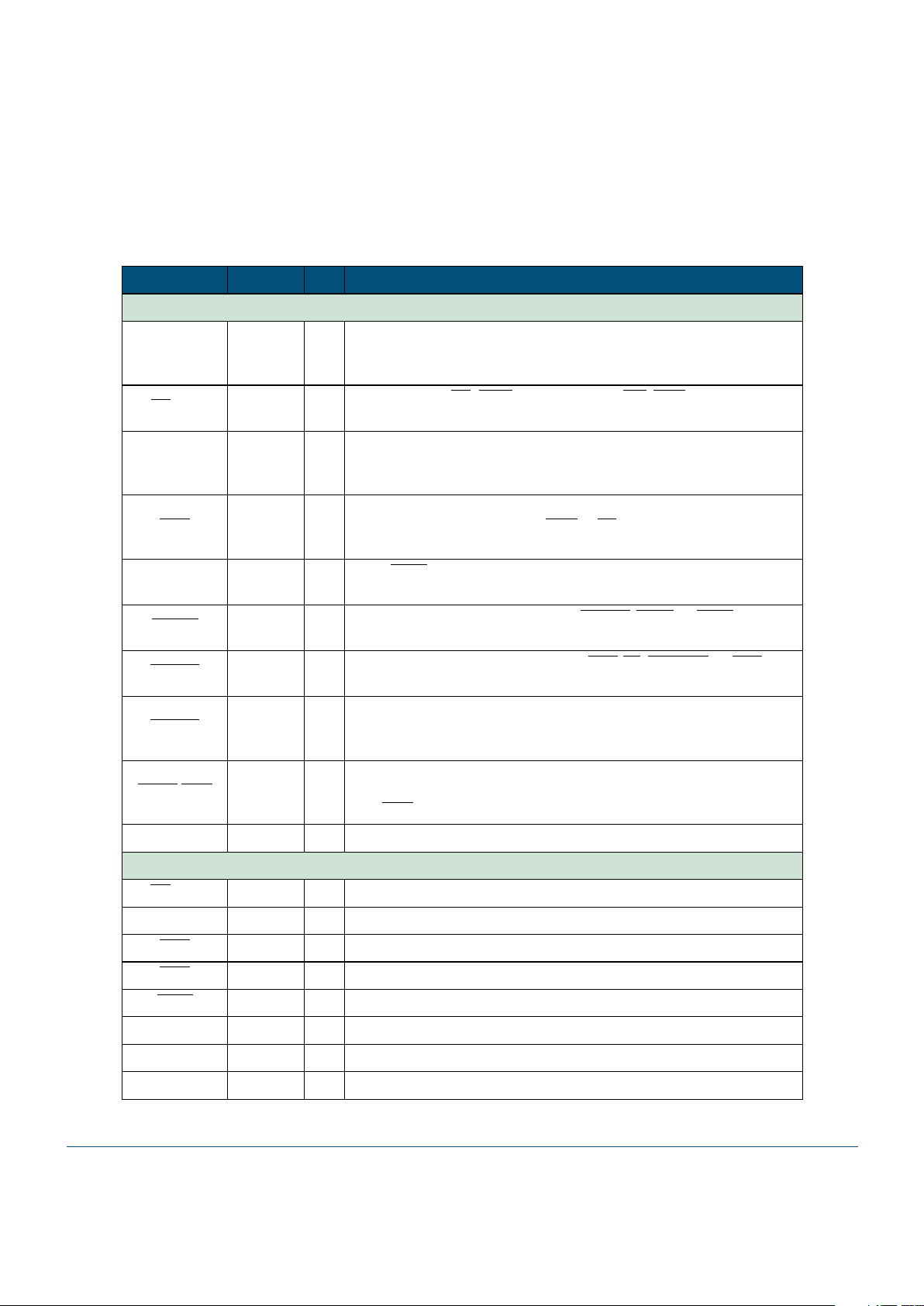

Table 2 lists the pin types found on the V380SDC; Table 3 describes the function of each pin.

Table 1: Product Code

Product Code

Package Frequency

V380SDC-75 REV A0 100-pin EIAJ PQFP 75 MHz

Table 2: Pin Types

Pin Type

Description

I/O

8

TTL I/O pin with 8 mA output drive.

I/O

D

TTL input with open drain output.

I TTL input only pin.

O

D

TTL open drain output.

O

8

TTL output pin with 8 mA output drive.

O

12

TTL output pin with 12 mA output drive.

DS-SD01-0101.fm Page 3 Monday, June 5, 2000 11:03 AM

Pin Description

4

V380SDC_A0 Datasheet Rev 1.01 DS-SD01-0101 © 2000 V3 Semiconductor Corp.

Table 3: Signal Descriptions

Signal

Type R

a

Description

Processor Bus Interface

A[31:2] I

Address Bus For demultiplexed processors, A[31:2] is used.

For multiplexed processors, only A[31:8] is used; A[2] is used as ALE

(Address Latch Enable) input.

BE[3:0] I

Byte Enables (BE

, BWE), Transfer Size (SIZ, TSIZ), or Address

(A[1:0]) are multiplexed on these pins depending on processor mode.

AD[7:0] I/O

8

Z

Address (Data) Bus For demultiplexed processors, AD[7:0] is used

as D[7:0]. For multiplexed processors, AD[7:0] is used as the

multiplexed address/data bus.

ADS

I

Address Strobe Asserted low to indicate the beginning of a bus

cycle: It can be interpreted as REQ or TS depending on processor

mode.

WNR I

Write/Read

It can be interpreted as RNW or RD depending on

processor mode.

BLAST

I

Burst Last It can be interpreted as BURST, TBST, or LAST

depending on processor mode.

READY I/O

8

Z

Data Ready It can be interpreted as RD

Y, TA, RDYRCV, or ACK

depending on processor mode.

ARTRY I

Address Retry for PPC750 processor. During reset, the state of the

pin along with the processor mode also determine the default value of

the SDC_REG_BASE register.

AACK/DEN I/O

8

Z

Address Acknowledge for PPC750 processor or Data Enable

output in other processor modes intended for buffer control.

This DEN

output is not to be connected to the processor.

TT[1:0] I

T ransfer Type

SDRAM Interface

CS[3:0] O

8

Z

SDRAM Chip Select

MA[14:0] O

12

Z

SDRAM Memory Address MA[14:13] are typically used for BA[1:0]

RAS

O

12

Z

SDRAM Row Address Strobe

CAS

O

12

Z

SDRAM Column Address Strobe

MWE

O

12

Z

SDRAM Memory Write Enable

DQM[7:0] O

8

Z

SDRAM Data Mask

IOC[3:0] I/O

8

Z

Multi-purpose I/O which can be configured for many functions

SDA I/O

D

Z

Serial EEPROM Data

DS-SD01-0101.fm Page 4 Monday, June 5, 2000 11:03 AM

Loading...

Loading...