V3 Semiconductor V350EPC-40, V350EPC-33 Datasheet

Copyright © 1998, V3 Semiconductor Corp. V350EPC DataSheet Rev 1.1 1

V350EPC Rev. A0 / A1

LOCAL BUS TO PCI BRIDGE

FOR MULTIPLEXED A/D PROCESSORS

V3 Semiconductor reserves the right to change the specifications of this product without notice.

V350EPC and V96BMC are trademarks of V3 Semiconductor. All other trademarks are the property of their respective owners.

• Glueless interface to Intel’s i960Jx and IBM’s

PowerPC

TM

401Gx processors

• Configurable for primary master, bus master or

target operation.

• Type 0 and type 1 configuration cycles.

•Upto1KbyteburstaccessonPCIorlocal.

• Large,640-byteFIFOs using V3’s unique

D

YNAMIC BANDWIDTH ALLOCATION™ architecture

• 64-byte read FIFO per aperture.

• Enhanced support for 8/16-bit local bus devices

with programmable region sizes.

• 3.3 volt support

• Dual bi-directional address space remapping

• Fully compliant with PCI 2.1 specification

• On-the-fly byte order(endian) conversion

•I

2

O ATU and messaging unit including

hardware controlled circularqueues

• 2 channel DMA controller plus multiprocessor

DMA chaining and demand mode DMA

• Hot swapping capability

• 16 8-bit bi-directionalmailboxregisters with

doorbell interrupts

• Flexible PCI and local interrupt management

• Optional power-on serial EEPROM initialization

• 33MHz and 40MHz local bus versions

• Industrials temperature grade -40 to +85’C

• Low cost 160-pin EIAJPQFP package

V350EPC is a high-performance and low-cost

generic so lution for interfa cin g b oth 32- bit and

16-bit multiplex ed local bus applic at ions to the

PCI bus. V350EPC directly connects to i960Jx or

i960Sx proces sors without a ny glue logic.

Minimal glue logic is required for highperformance interfacing to other multiplexed

processors like Motorola ColdFire™.

V350EPC is the second generation of V3’s I

2

O

ready PCI bridges - fully backw ar d com patible

with both V961PBC and V960PBC Rev B2

devices - and is supporting powerful features like

Hot Swap and DMA chaining. The PCI bus can

be run at the full 33MHz frequency, independent

of local bus clock rate. The overall throughput of

the system is dramatica lly im proved by

increasing the FIFO depths and utilizing the

unique D

YNAMIC BANDWIDTH ALLOCATION™

architecture.

Access to the PCI bus can be performed through

two programmable address apertures. Two more

aper tur es a re provided for PCI -to- loc al b us

accesses. There are 64- byte s of read FIFOs in

each direction, 32-byte dedicated for each

aperture .

Two high-performance DMA channels with

chaining and demand mode capabilities provide

a powerful data transfer engine for bulk data

transfers. Ma ilbox regis ters and flex ible PCI

interrupt controllers are also included to provide

a simple mechanism to emulate PCI device

control ports. The part is available in 160-pin low

cost PQFP packages in 33MHz and 40MHz

versions.

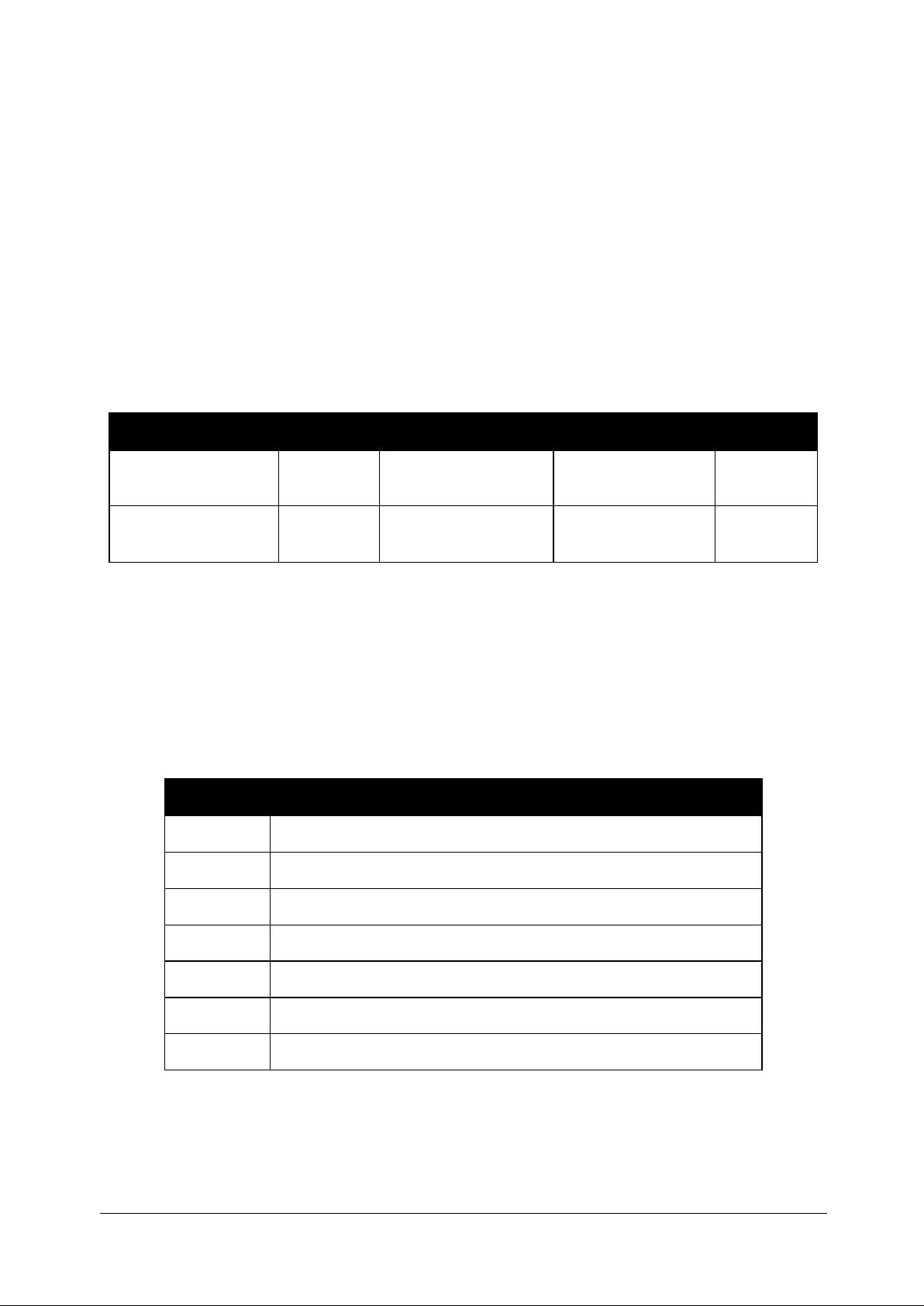

i960Jx

CPU

V96BMC

MEMORY

CONTROL

D

R

A

M

ROM

V350EPC

LOCAL TO

PCI BRIDGE

TYPICALAPPLICATION

PERIPHERAL

PCI

PCI SLOT or EDGE CONNECTOR

V350EPC

2 V350EPC Data Sheet Rev 1.1 Copyright© 1998, V3 SemiconductorInc.

This document contains the product codes, pinouts, package mechanical information, DC

characteristics, and AC characteristics for the V350EPC. Detailed functional information is contained

in the User’s Manual.

V3 Semiconductor retains the rights to change documentation, specifications, or device

functi ona li ty at any tim e wit h out no t ic e. Ple ase ve rif y tha t you ha ve th e late s t copy of all

documents before finalizing a design.

1.0 Product Codes

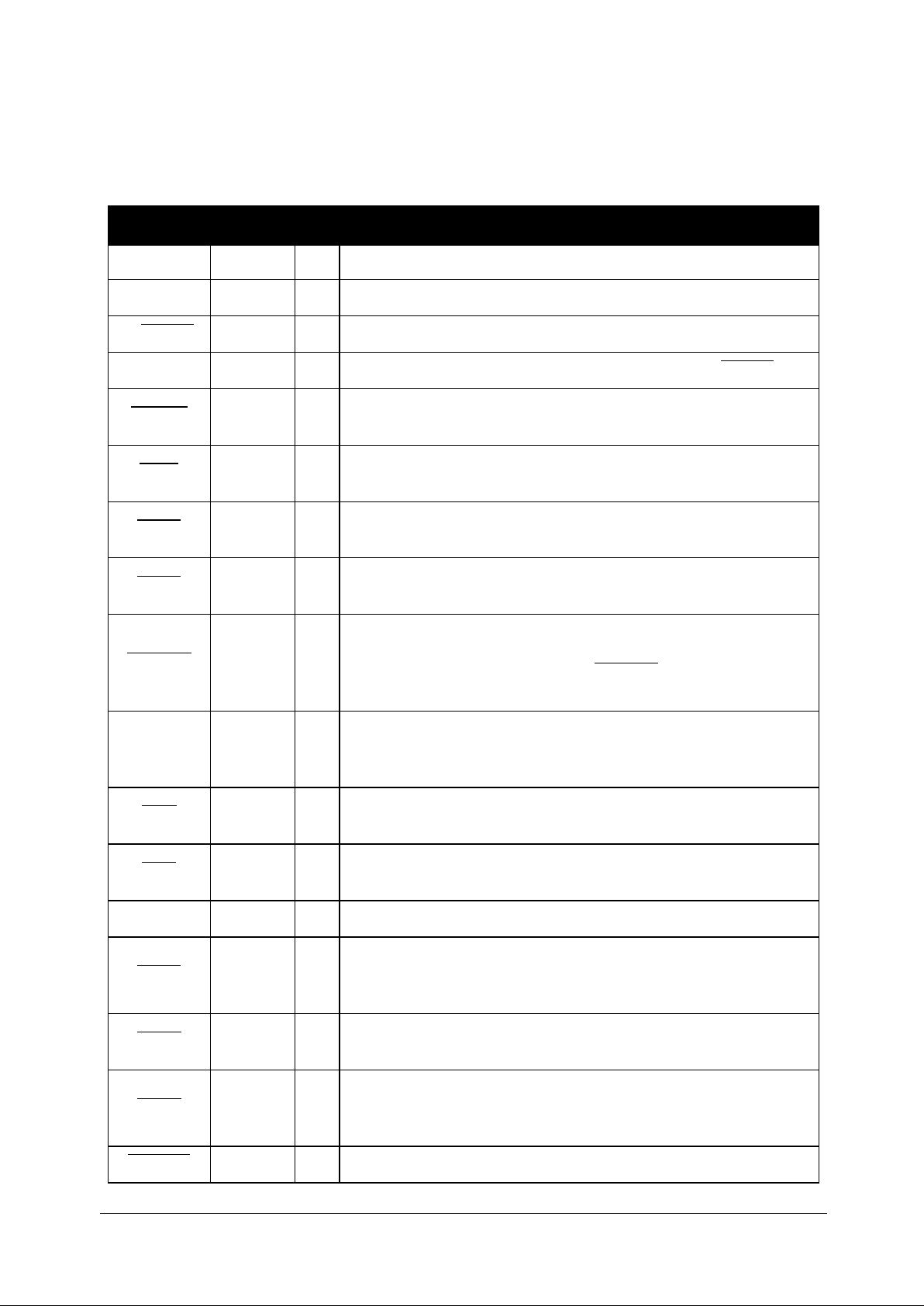

2.0 Pin Description and Pinout

Table 2 below lists the pin types found on the V350EPC. Table 3 describes the function of each pin on

the V350EPC. Table 5 lists the pins by pin number. Figure 1 shows the pinout for the 160-pin EIAJ

PQFP packageand Figure 2 shows the mechanical dimensions of thepackage.

Table 1: Product Codes

Product Code Processors Bus Type Package Frequency

V350EPC-33

REV A0 / A1

i960Jx/Sx 32/16-bit multiplexed 160-pin EIAJ P QFP 33MHz

V350EPC-40

REV A0 / A1

i960Jx/Sx 32/16-bit multiplexed 160-pin EIAJ P QFP 40MHz

Table 2: Pin Types

Pin Type Description

PCI I PCI input only pin.

PCI O PCI output only pin.

PCI I/O PCI tri-state I/O pin.

PCI I/OD PCI input with open drain output.

I/O

4

TTL I/O pin with 4mA output drive.

I TTL input only pin.

O

4

TTL output pinwith 4mA outputdrive.

V350EPC

Copyright © 1998, V3 Semiconductor Corp. V350EPC DataSheet Rev 1.1 3

Table 3: S i gnal Descriptions

PCI Bus Interface

Signal Type R

a

Description

AD[31:0] PCI I/O Z Address and data, multiplexed on the same pins.

C/BE[3:0]

PCI I/O Z Bus Command and Byte Enables, multiplexed on the same pins.

PAR PCI I/O Z Parity represents even parity across AD[31:0] and C/BE[3:0]

.

FRAME

PCI I/O Z

Cycle Frame indicatesthe beginning andburst lengthof an

access.

IRDY

PCI I/O Z

Initiator Ready indicates the initiating agent’s (bus master’s) ability

to complete the current data phase of the transaction.

TRDY

PCI I/O Z

Target Ready indicates the target agent’s (selected device’s) ability to complete the current data phase of t he transaction.

STOP

PCI I/O Z

Stop indicatesthe currenttarget is requesting the master to stop

the current transaction (retry or disconnect).

DEVSEL

PCI I/O Z

Device Select,when actively driven by a target, indicates the driving device has decoded its addressas the targetof the current

access. As an input to the initiator, DEVSEL

indicates whether

any device on the bushas been selected.

IDSEL PCI I

InitializationDevice Select is used as a chip select during configuration read andwrite transactions. It must be driven high in order

to access the chip’s internal configuration space.

REQ

PCI O Z

Request indicates to the arbiter that this agent requests use of the

bus.

GNT

PCI I

Grant indicates to the agent that access tothe bus has been

granted.

PCLK PCI I PCLK providestiming for all transactions on the PCI bus.

PRST

PCI I/O Z/L

Acts as an input when RDIR is high, an output when RDIR is low.

As an input it is assertedlow to bringall internal EPC operation to

a reset state.

PERR

PCI I/O Z

Parity Error is used to report data parity errors during all PCI

transactions except a Special Cycle.

SERR PCI I/OD Z

System Error is used to report address parity errors, data parity

errors on the Special Cycle command, orany other system error

where the result will be catastrophic.

INT[A:D]

PCI I/OD Z Level-sensitive interr upt requests maybe receivedor generated.

V350EPC

4 V350EPC Data Sheet Rev 1.1 Copyright© 1998, V3 SemiconductorInc.

Local Bus Interface

Signal Type R Description

LAD[31:0]

LAD[15:0]

b

I/O4 Z Local multiplexed addressand data bus.

LA[31:16]

b

I/O4 Z Local address bus.

LA[5:2] O4 Lower local address bus (non-multiplexed version).

ALE I/O4 Z

AddressLatch Enable : used to latch the address during the

address phase.

BE[3:0]

BE[1:0]

b

I/O4 Z Local bus byte enables.

W/R

I/O4 Z Write/Read.

ADS

AS

b

I/O4 Z Asserted low to indicate the beginning of a bus cycle.

RDYRCV

READY

b

I/O4 Z Local Bus data ready

HOLD O4 L

Localbus hold request: asserted by the chip toinitiate a localbus

mastercycle.

HOLDA I Local bus hold acknowle dge.

LPAR[3:0]

LPAR[1:0]

b

I/O4 Z Local bus parity.

BLAST

I/O4 Z Burst last.

BTERM

c

I/O4 Z Bus Time-out. Burst terminate.

LINT

O4 H Local interruptrequest.

LRST

I/O4 L/Z Local bus RESET signal.

LCLK I Local bus clock.

Serial EEPROM Interface

Signal Type R Description

SCL/LPERR

O4 X EEPROM clock. Local parity error.

SDA I/O4 X EEPROM data.

Table 3: Signal Descriptions (cont’d)

V350EPC

Copyright © 1998, V3 Semiconductor Corp. V350EPC DataSheet Rev 1.1 5

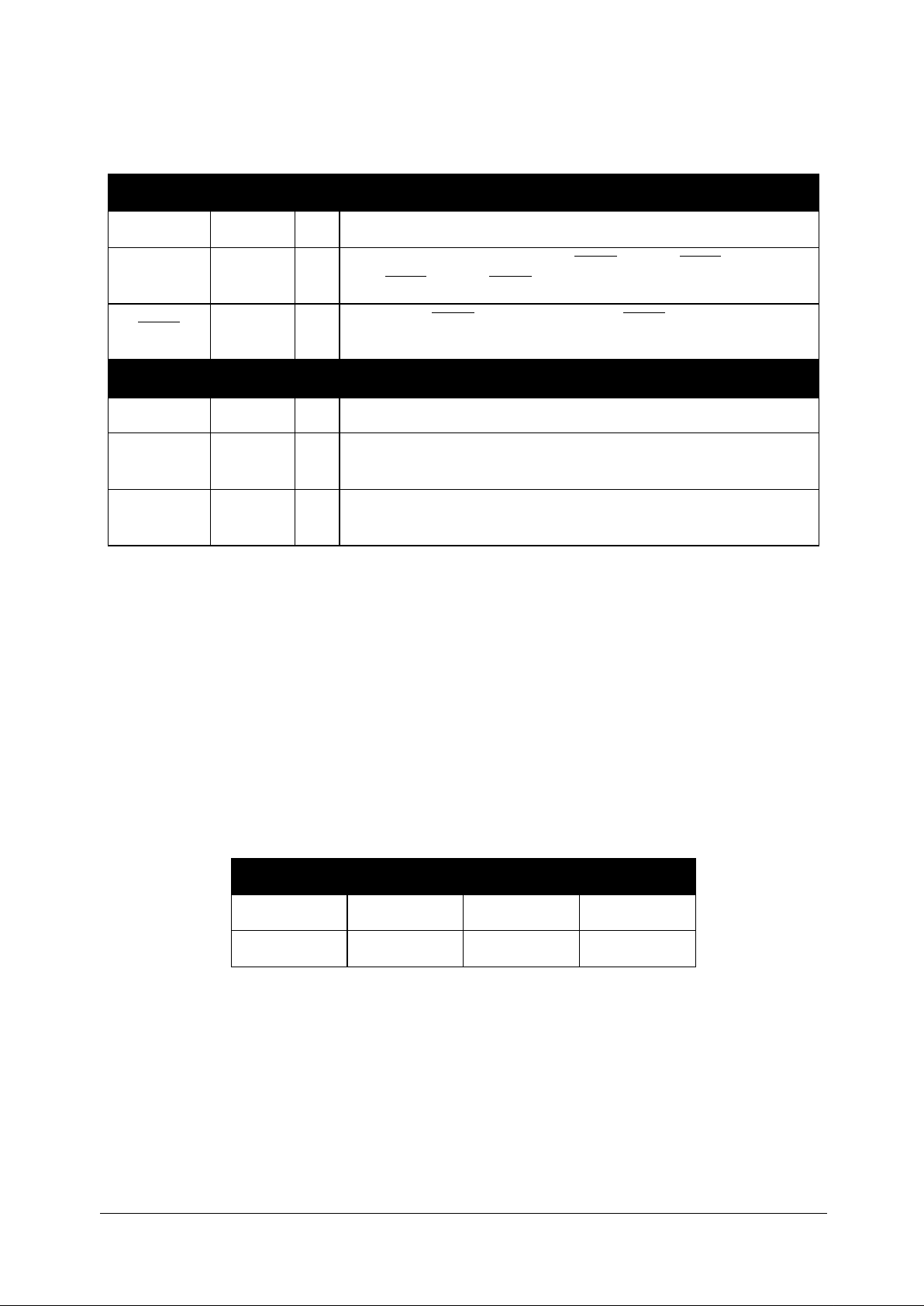

2.1 Test Mode Pins

Several device pins are used during manufacturing test to put the V350EPC device into various test

modes.These pinsmust be maintained at proper levels during reset to insure proper operation.

Thisis typically handled through pull-up or pull-down resistors (typically 1K to 10K) on the signalpins if

they are not guaranteedto be at theproper level during reset. Table4 below shows the reset statesfor

test mode pins:

Configuration

Signal Type R Description

RDIR I

Reset direction. T ie low to drive PRST

out and LRST in, high to

drive LRST

out and PRSTin.

EN5V

I

Selects 5V (EN5V

drivenlow) or 3.3V (EN5V driven high) device

operation modes.

Power and Ground Signals

Signal Type R Description

V

CC

-

POWER leads intended for external connection to a V

CC

board

plane.

GND -

GROUND leads intended for external connection to a GND board

plane.

a.R indicates state during reset.

b. Applies to i960Sx mode.

c. Applies to i960Jx mode.

Ta ble 4: RESET State for Test M ode Pins

Mode Pin 134 Pin 135 Pin 153

i960Jx Pull-Down Pull-Up Pull-Down

i960Sx Pu ll-Down Pull-Down Pull-Down

Table 3: Signal Descriptions (cont’d)

V350EPC

6 V350EPC Data Sheet Rev 1.1 Copyright© 1998, V3 SemiconductorInc.

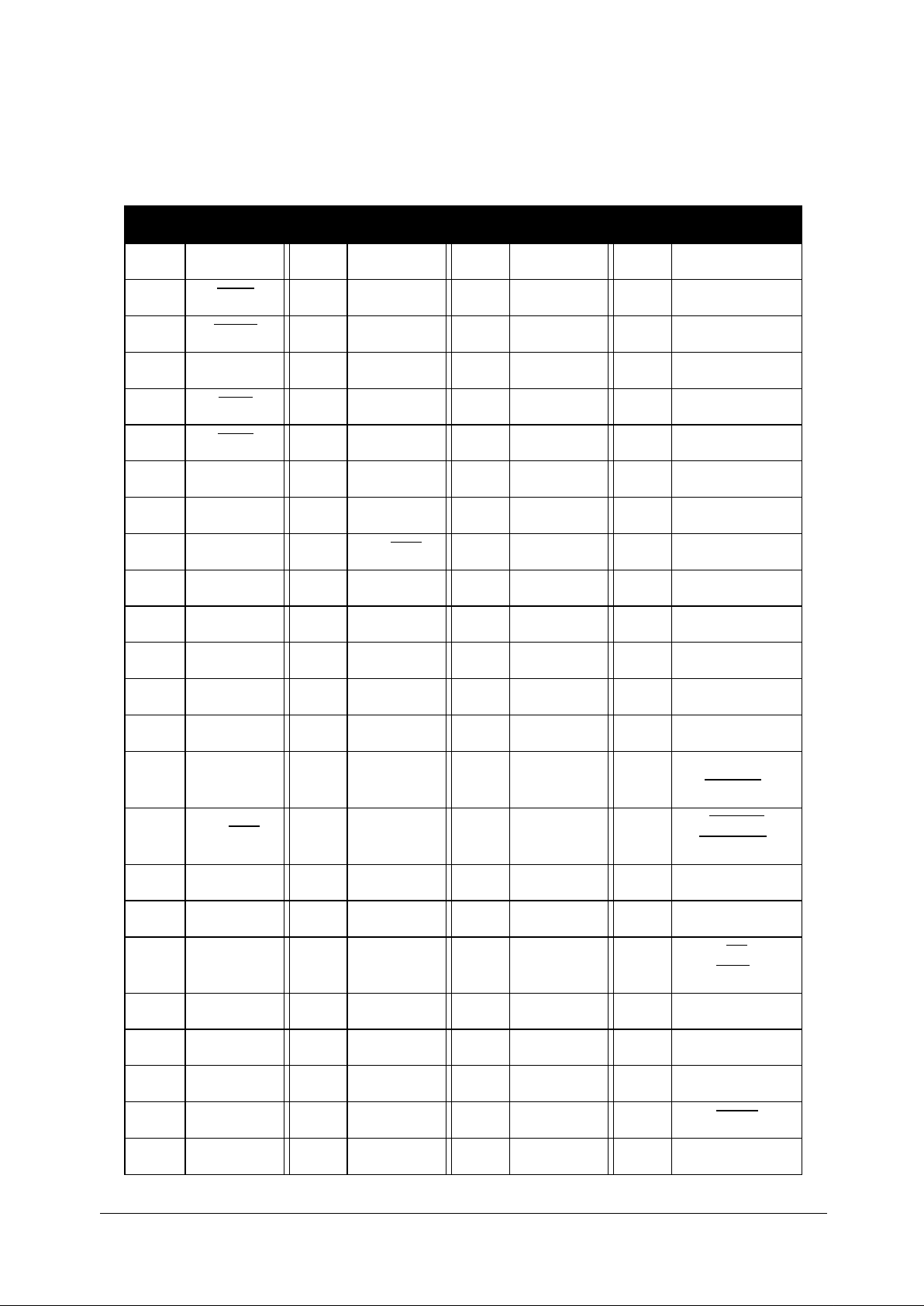

Table 5: Pin Assignments

PIN # Signal PIN # Signal PIN # Signal PIN # Signal

1V

CC

41 V

CC

81 V

CC

121 V

CC

2INTD42 AD14 82 NC 122 NC

3PRST

43 AD13 83 LAD8 123 LA(Da)25

4 PCLK 44 AD12 84 NC 124 LA5

5GNT

45 AD11 85 LAD9 125 LA(Da)26

6REQ

46 AD10 86 NC 126 LA4

7 AD31 47 AD9 87 LAD10 127 LA(D

a

)27

8 AD30 48 AD8 88 NC 128 LA3

9 AD29 49 C/BE0

89 LAD11 129 LA(Da)28

10 AD28 50 V

CC

90 NC 130 LA2

11 GND 51 GND 91 LAD12 131 LA(D

a

)29

12 AD27 52 AD7 92 NC 132 LA(D

a

)30

13 AD26 53 AD6 93 LAD13 133 LA(D

a

)31

14 AD25 54 AD5 94 NC 134 ALE

15 AD24 55 AD4 95 LAD14 135

’0’

BTERM

a

16 C/BE3 56 AD3 96 NC 136

READY

RDYRCV

a

17 IDSEL 57 AD2 97 LAD15 137 HOLD

18 AD23 58 AD1 98 NC 138 HOLDA

19 AD22 59 AD0 99 LA(D

a

)16 139

AS

ADS

a

20 V

CC

60 V

CC

100 V

CC

140 V

CC

21 GND 61 GND 101 GND 141 GND

22 AD21 62 LAD0 102 NC 142 LCLK

23 AD20 63 NC 103 LA(D

a

)17 143 EN5V

24 AD19 64 LAD1 104 NC 144 V

CC

Loading...

Loading...