Usi G43 Schematic

8

7

6

5

4

3

2

1

F F

E E

D D

C C

B B

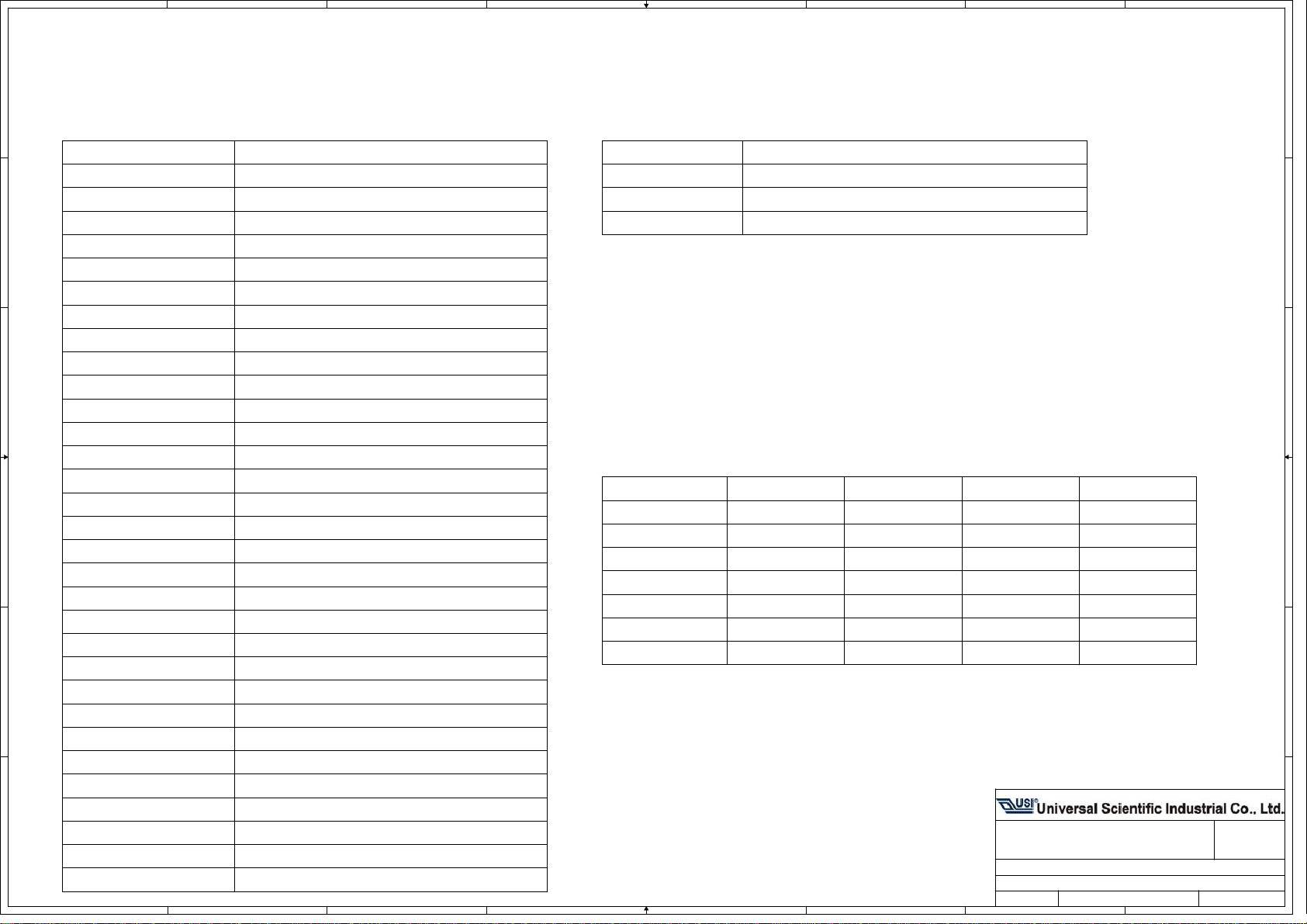

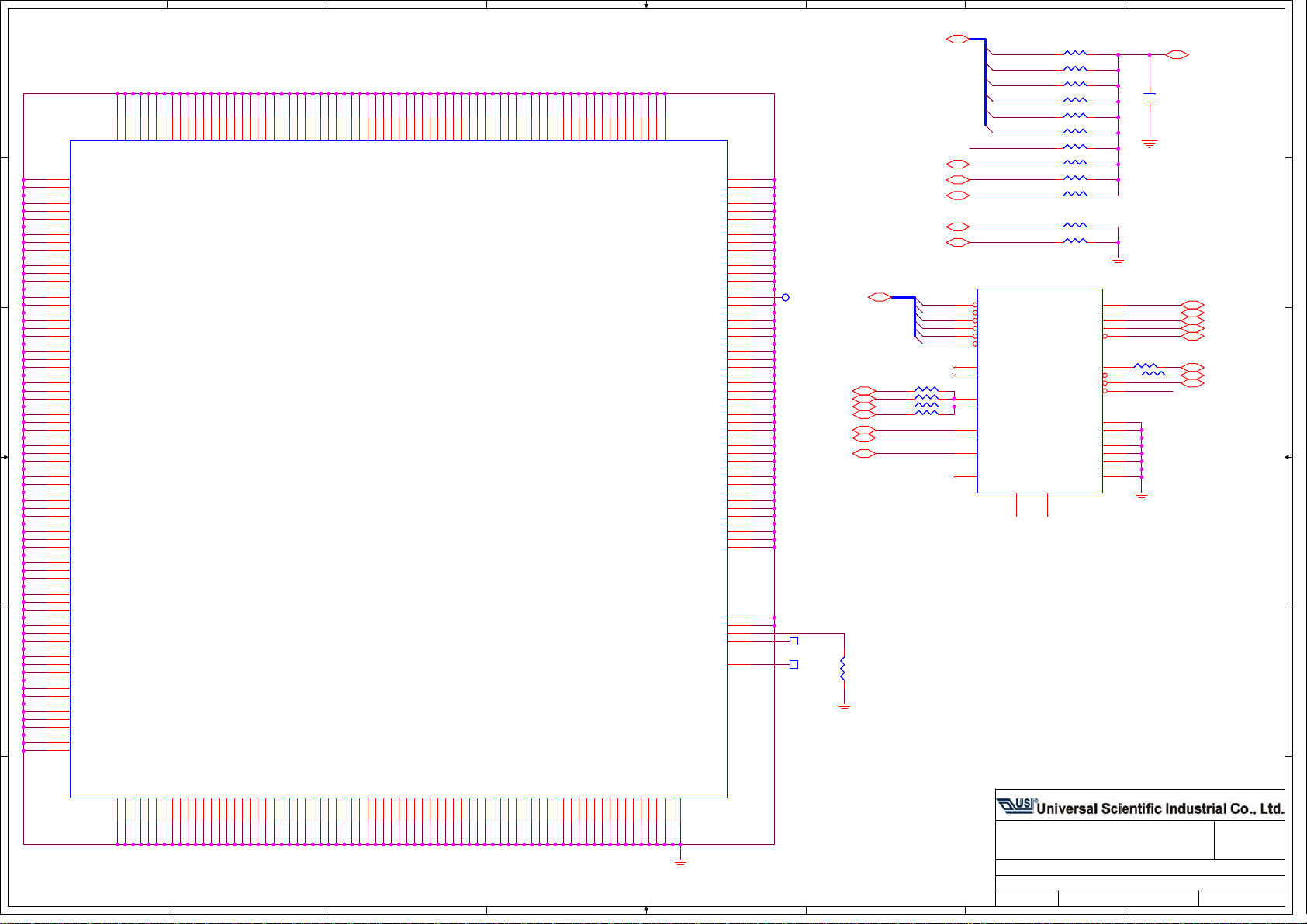

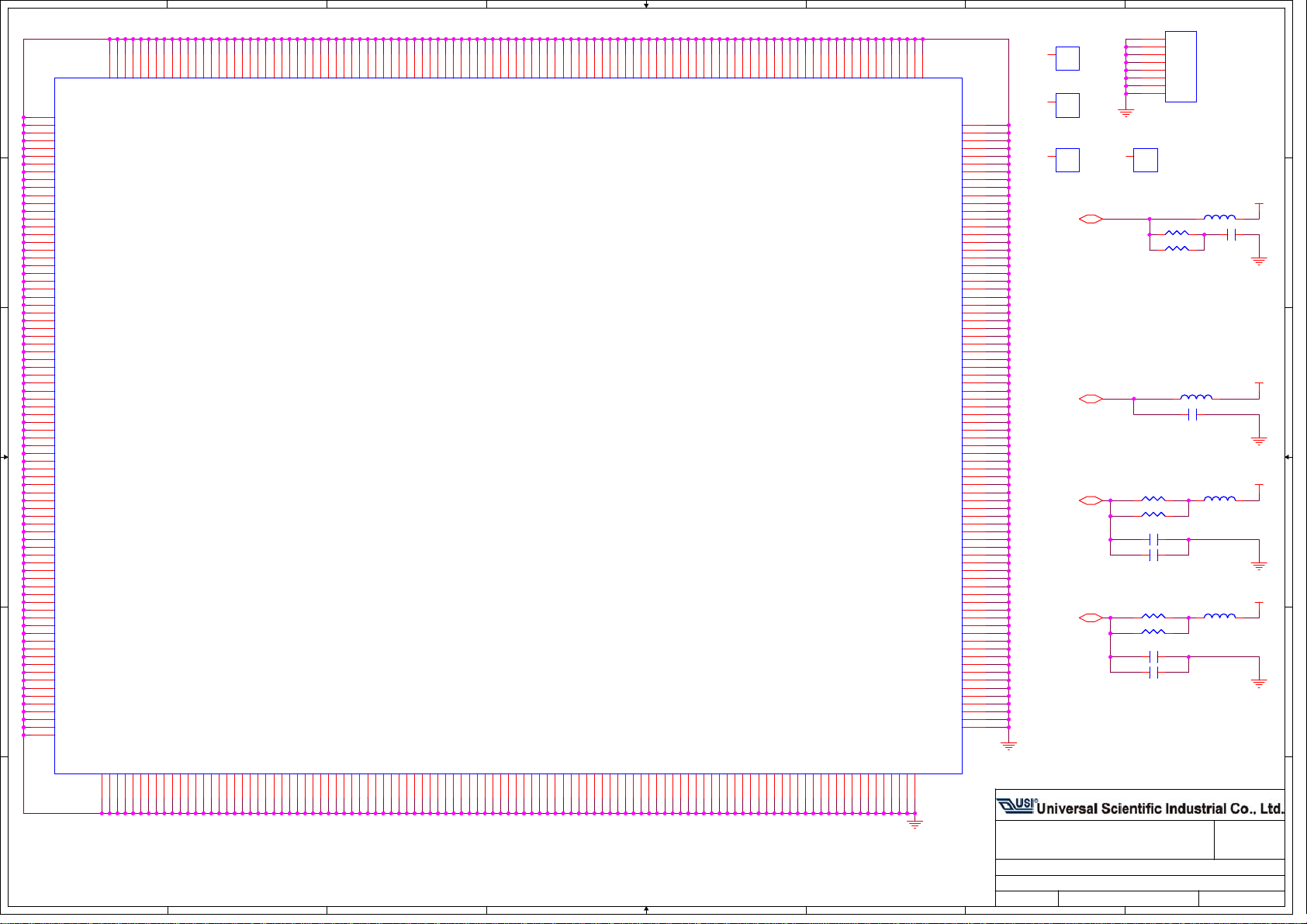

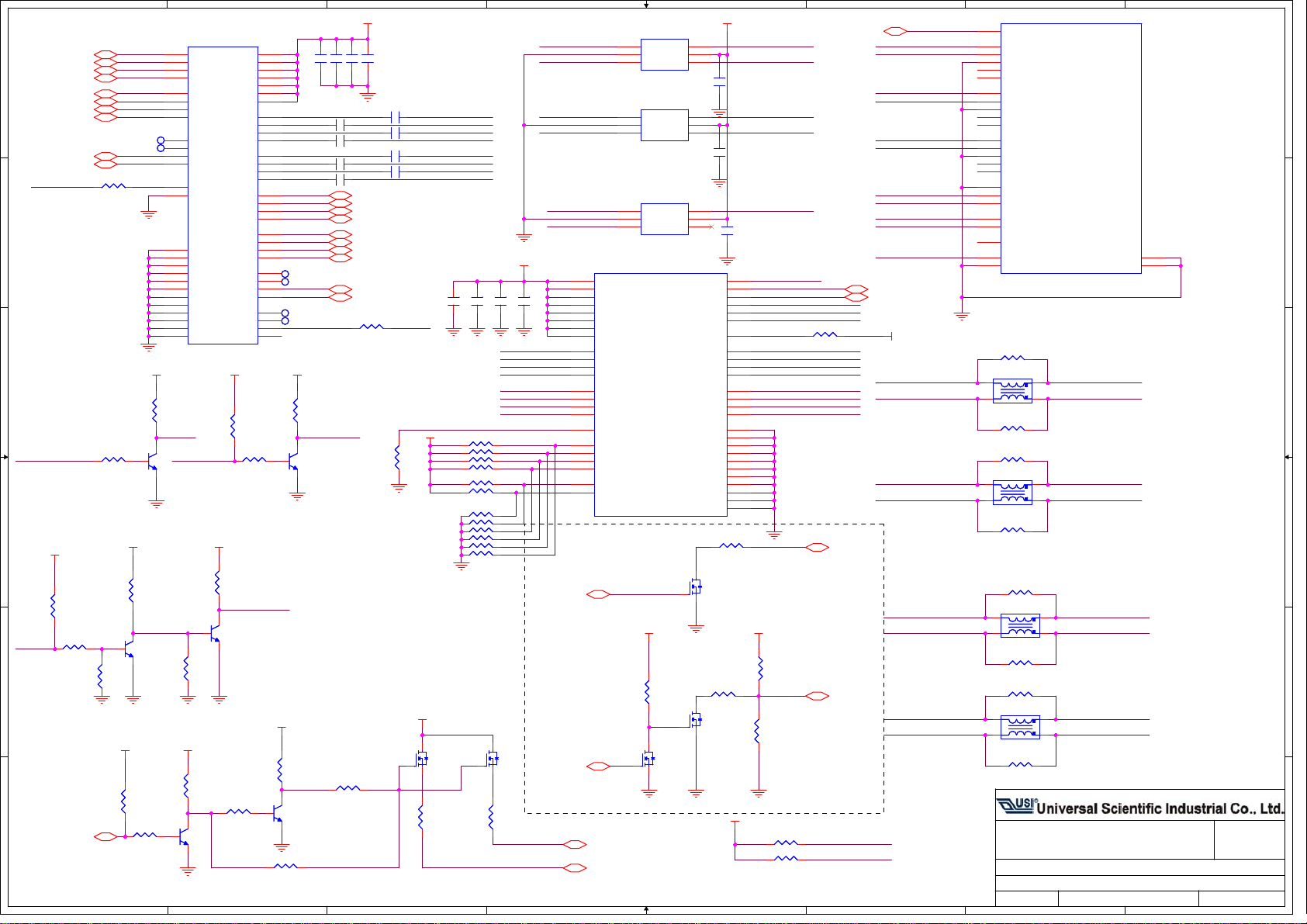

G43 Schematics

CONTENTS

Page Description

1 Title

2 System Block

3, 4, 5

6, 7, 8, 9

10,11,12

13

14

15

16, 17, 18, 19

20

21

22

23

24

25

26

27

28

29

30

31

32

33,34,35,36,37,38 POWER

CPU Socke LGA775

Intel EagleLake GMCH

DDR2 & MEM DECOUPLE

DVI PORT

HDMI PORT

VGA PORT

ICH10

CK505

SIO

IDE

COM, LPT, PS/2, FP HEADER

SATA, FRONT USB

BACK USB

FAN

AUDIO

AUDIO JACK

LAN

PCIEX16 & X1 SLOT

PCI SLOT

1394

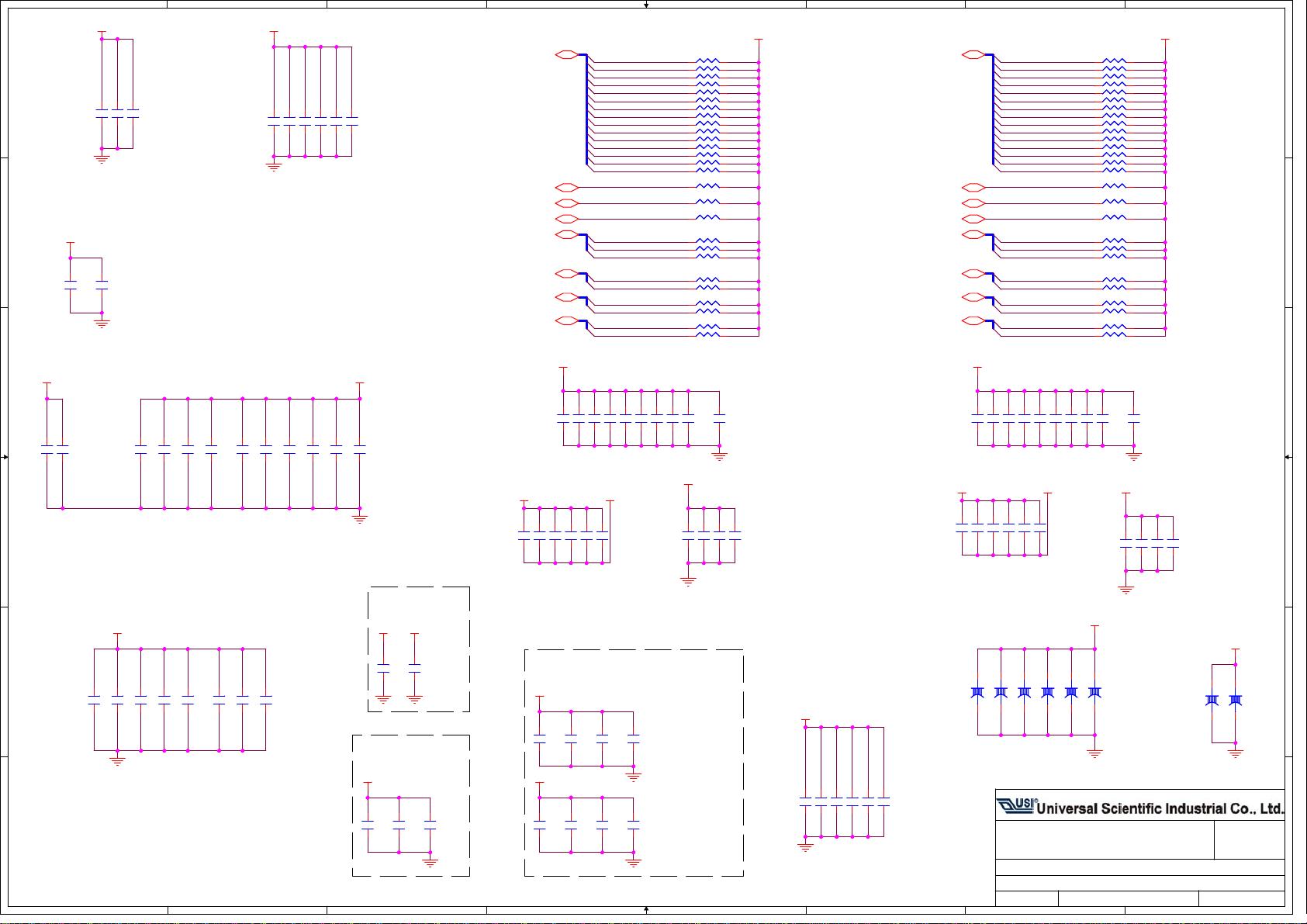

Bypass Capacitor

Reference Description

CB 0.1UF_0402

CP 0.01UF_0402

CM

1UF_0603

PCI Resource

Device

IDSEL

INT1#

INT2#

INT3#

INT4#

REQ#

GNT#

PCI Slot 1 PCI Slot 2

AD16 AD18

PCI_INTEPCI_INTFPCI_INTGPCI_INTH-

P_REQ0-

PCI_INTFPCI_INTGPCI_INTHPCI_INTEP_REQ1-

P_GNT0- P_GNT1-

PCI SLOT 3

AD20

PCI_INTGPCI_INTHPCI_INTEPCI_INTF-

P_REQ2P_GNT2-

1394

AD22

PCI_INTH-

P_REQ3P_GNT3-

39 RESET MAP

40

41

42

43

A A

44

45

46

8

CLOCK MAP

ICH GPIO MAP

SIO GPIO MAP

POWER DELIVERY

POWER SEQUENCE

HISTORY1

HISTORY2

7

TITLE:

TITLE:

TITLE:

G43NB

G43NB

G43NB

TITLE

TITLE

TITLE

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

6

5

4

3

A3

<Doc>

<Doc>

<Doc>

James Xiong

James Xiong

James Xiong

Date: PAGE:

Date: PAGE:

Date: PAGE:

Wednesday, April 02, 2008

Wednesday, April 02, 2008

Wednesday, April 02, 2008

2

REV:

REV:

REV:

146

146

146

1

0.2

0.2

0.2

of

of

of

8

7

6

5

4

3

2

1

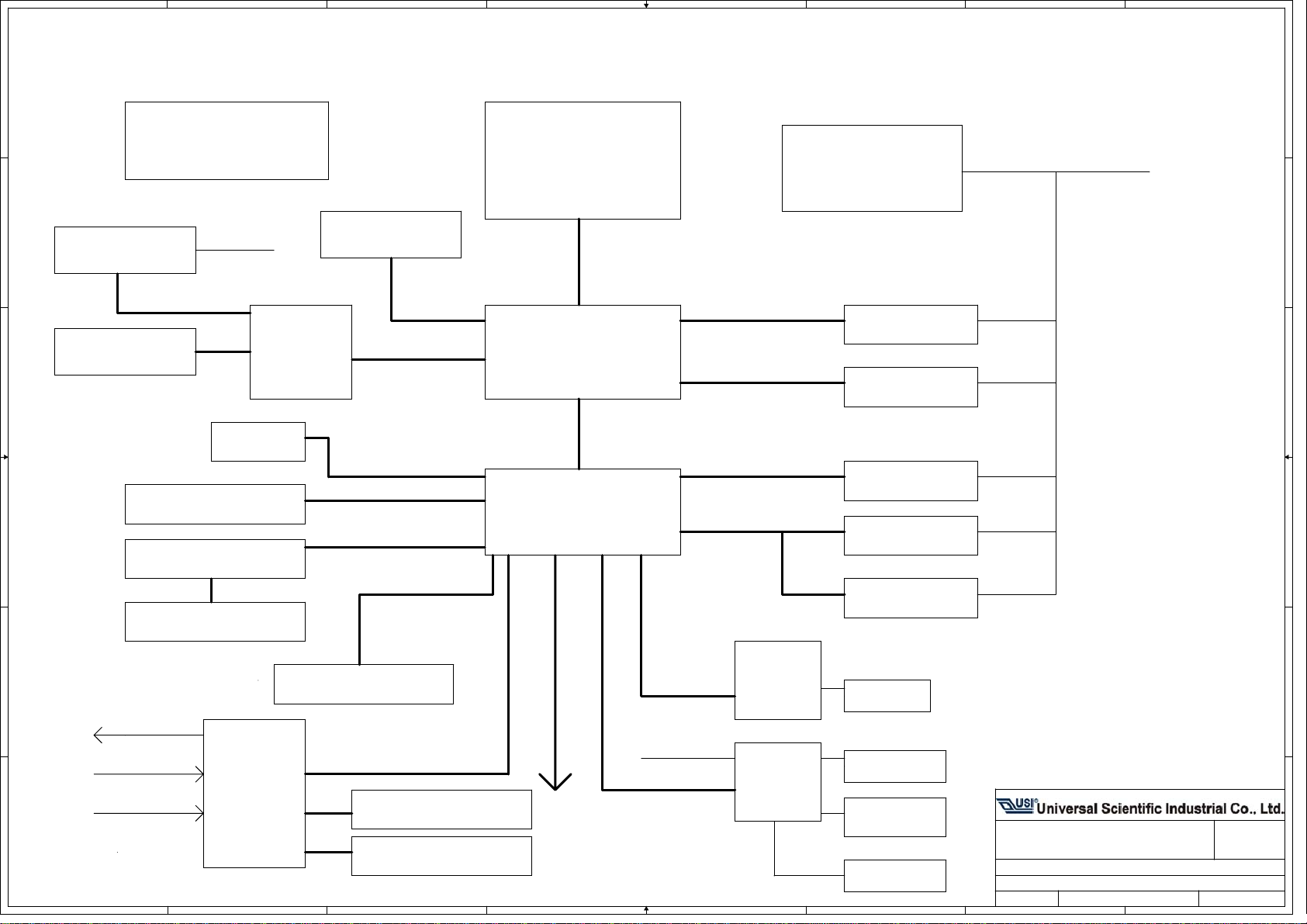

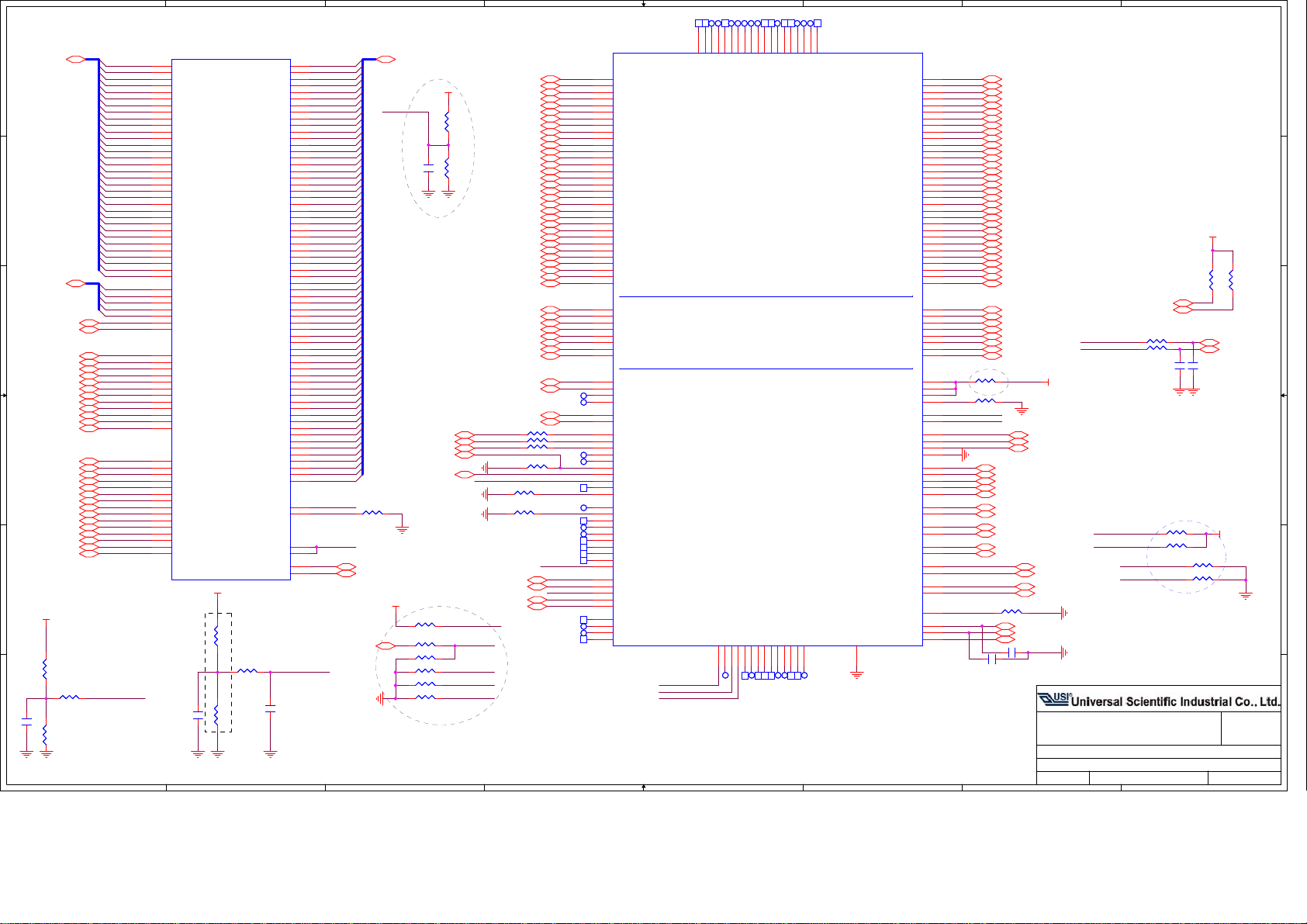

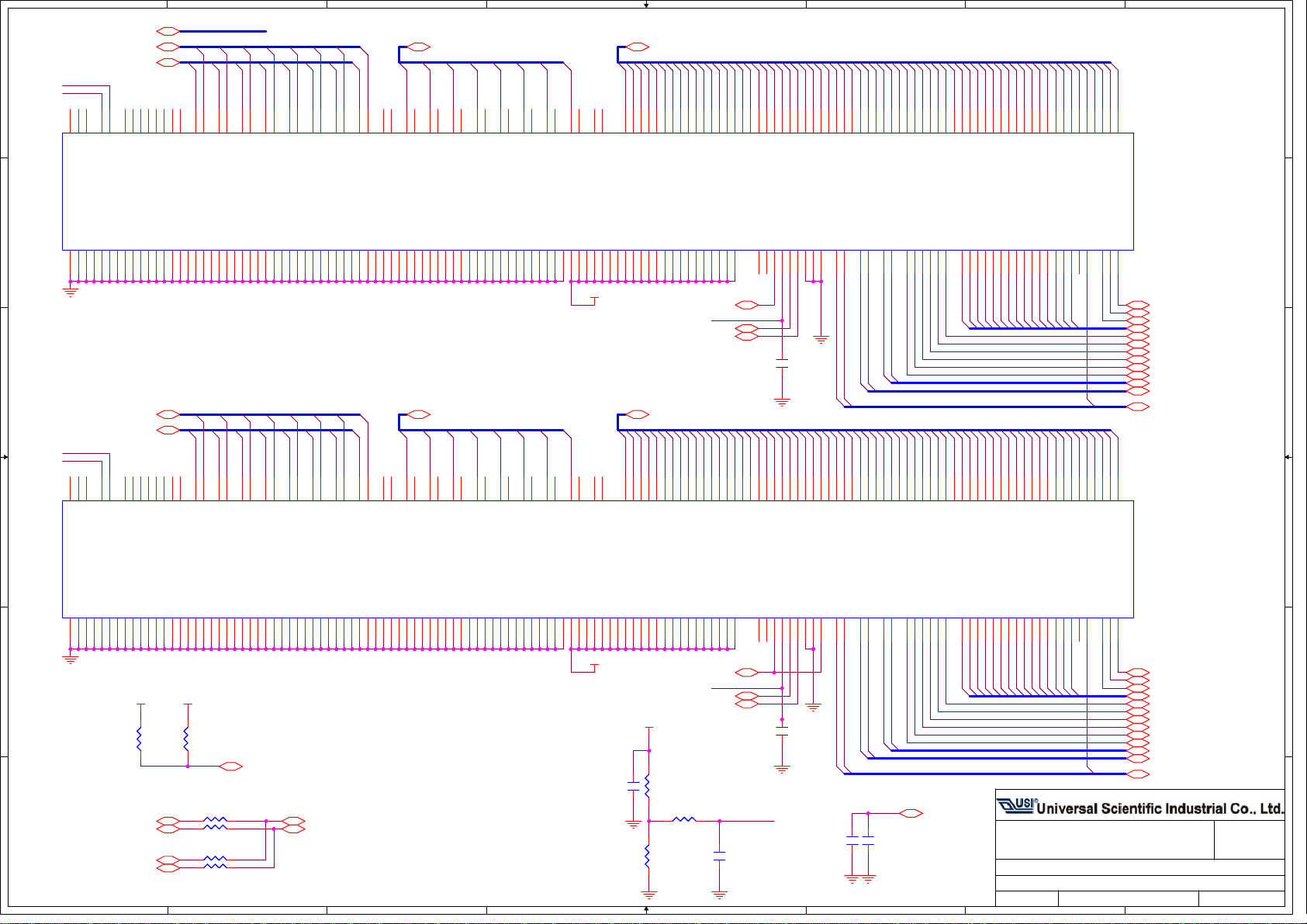

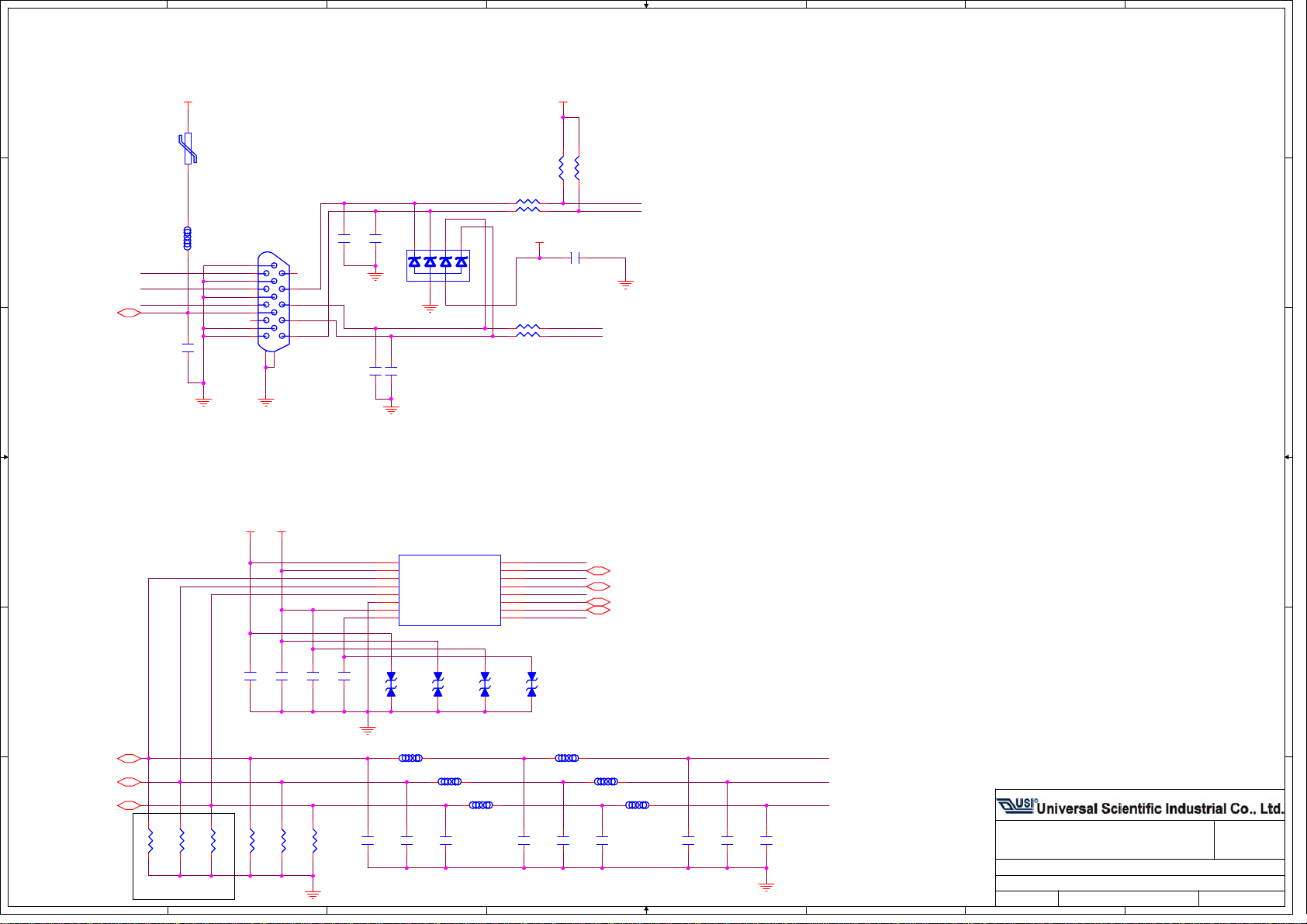

Block Diagram - G43

F F

Power

Circuit

Page 32,33,34,35,36,37,38

E E

PCIE X16

Page 29

DVI-D PORT

Page 13

D D

SMBus

Switch

Page 13

VGA PORT

Page 14

PCIE X16

LGA775

Processor

Page 3,4,5

1333/1066/800

FSB

G43

Page 6,7,8,9

DDR2

667/800

MHz

DDR2

667/800

Clock Gen.

SLG505YC264B

64PIN

Page 19

DDR2 CHA

Page 10

DDR2 CHB

Page 11

SMBus

MHz

SPI

Page 18

SATA Ports

Page 23

C C

SPI

SATA

QST

Page 15,16,17,18

FAN

Page 25

USB 2.0

DMI

ICH10

SMBus

PCIE X1

PCI

PCIE X1

Page 29

PCI Slot

Page 30

1394

HECETA

Page 25

INTEL

B B

USB 2.0

Page 23,24

Line Out

HD

Mic In

Line In

A A

8

Audio

CODE

ALC888

Page 26,27

7

HD Audio

SPDIF

Page 26

HD HEADER

Page 27

6

5

GLCI

SMBus

LPC

82567

Page 28

SIO

W83627DHG

Page 20

4

Page 31

RJ45

Serial

PS2 K/M

LPT

3

TITLE:

TITLE:

TITLE:

G43NT

G43NT

G43NT

SYSTEM BLOCK

SYSTEM BLOCK

SYSTEM BLOCK

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

2

<Doc>

<Doc>

<Doc>

James Xiong

James Xiong

James Xiong

Date: PAGE:

Date: PAGE:

Date: PAGE:

Wednesday, April 02, 2008

Wednesday, April 02, 2008

Wednesday, April 02, 2008

1

REV:

REV:

REV:

0.2

0.2

0.2

246

246

246

of

of

of

1

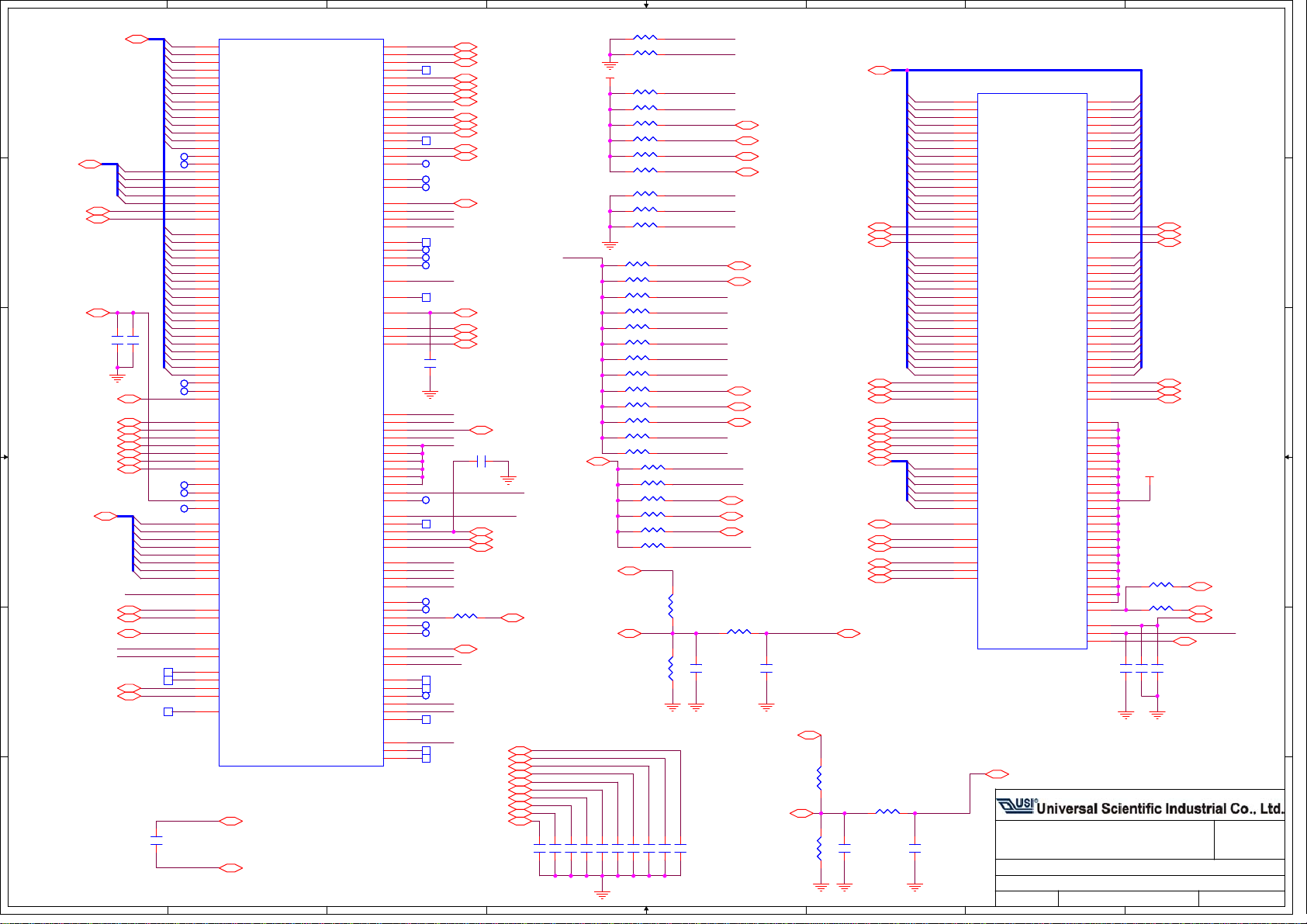

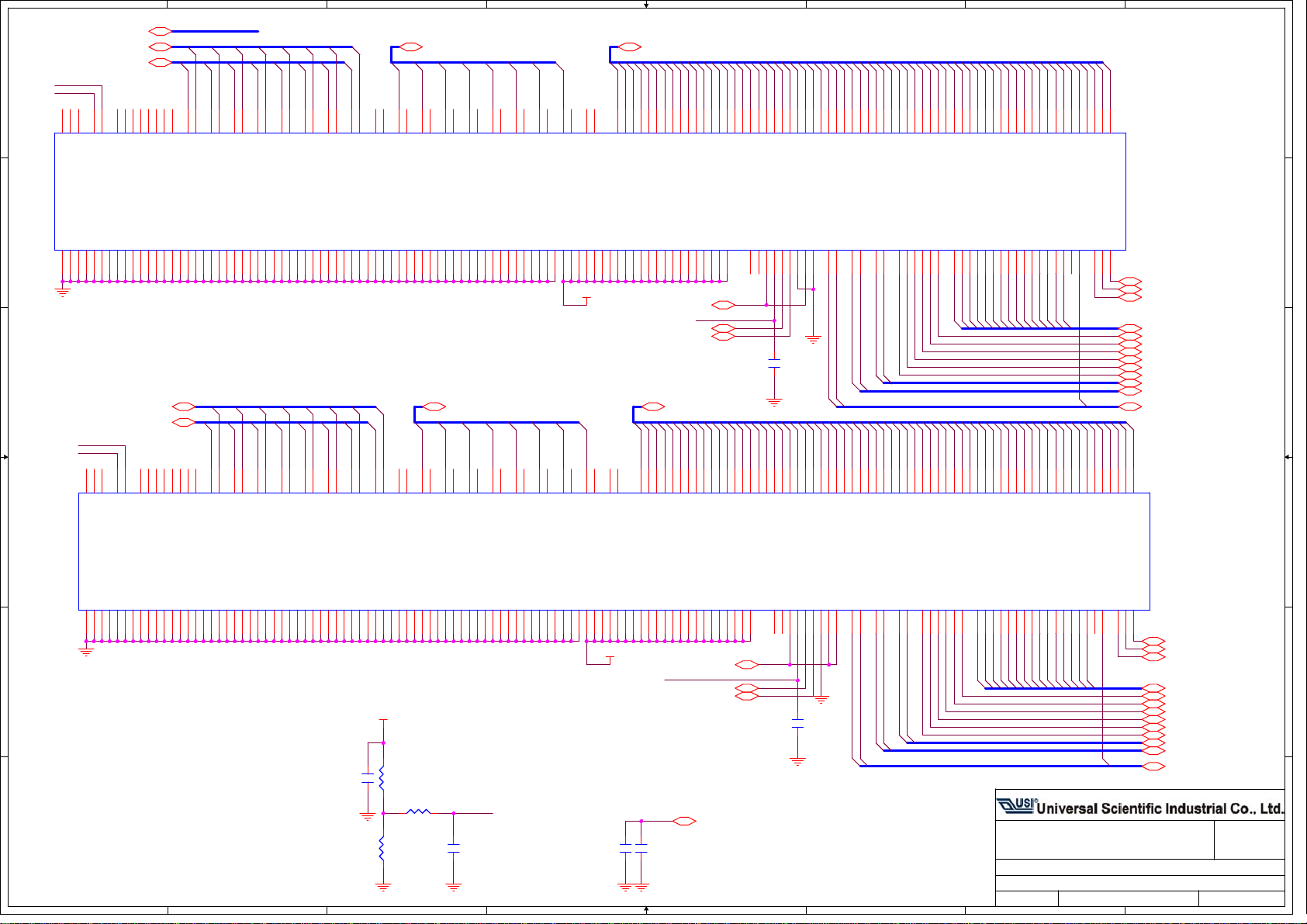

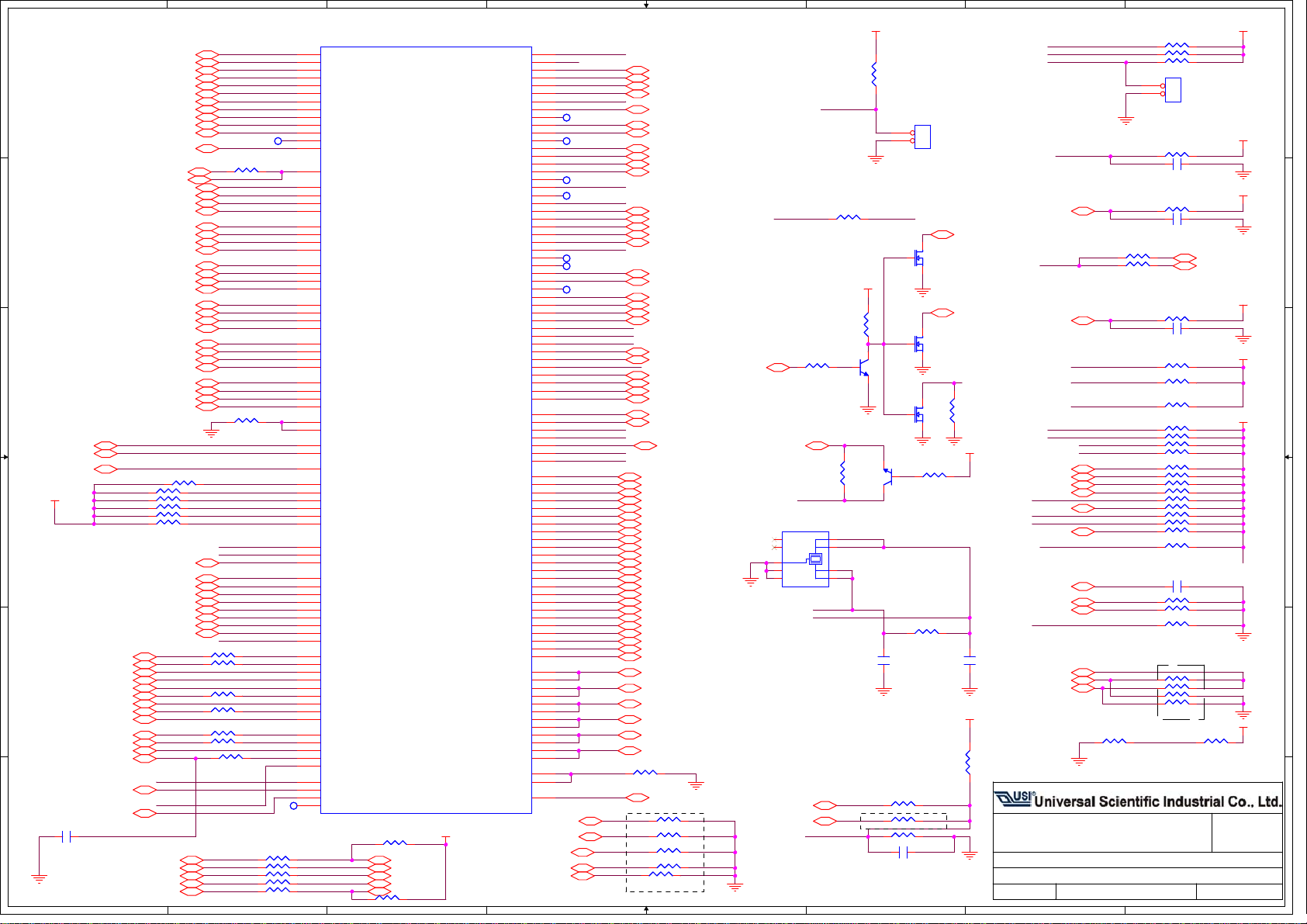

H_A-[3..35]6

A A

H_REQ-[0..4]6

H_ADSTB0-6

H_PECI15,20

B B

H_VCCPLL7

C C

D D

E E

F F

H_ADSTB1-6

H_STPCLK-15

CPUVID[0..7]36

CLK_HOST_CPU19

CLK_HOST_CPU-19

VCC_SENSE36

VSS_SENSE36

H_FERR-15

H_IGNNE-15

SKTOCC-15,20

H_SMI-15

H_A20M-15

H_INTR15

H_NMI15

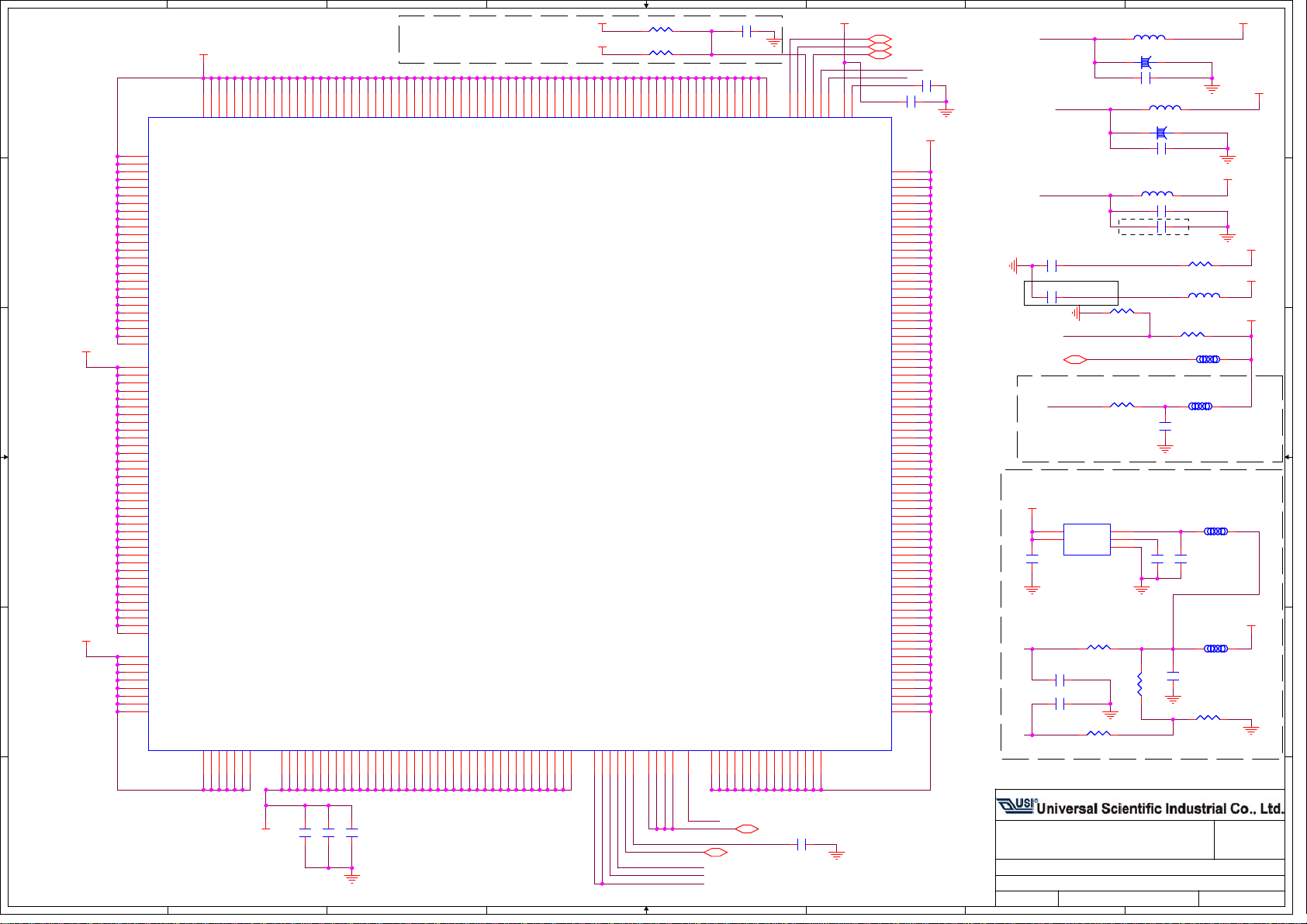

1

H_REQ-0

H_REQ-1

H_REQ-2

H_REQ-3

H_REQ-4

0805

0805

C1

C1

10UF

10UF

CPU_THERMDA

CPU_THERMDC

CP1CP1

CPUVID0

CPUVID1

CPUVID2

CPUVID3

CPUVID4

CPUVID5

CPUVID6

CPUVID7

H_VID_SEL

T24T24

T25T25

T29T29

H_A-3

H_A-4

H_A-5

H_A-6

H_A-7

H_A-8

H_A-9

H_A-10

H_A-11

H_A-12

H_A-13

H_A-14

H_A-16

T1T1

T5T5

H_A-17

H_A-18

H_A-19

H_A-20

H_A-21

H_A-22

H_A-23

H_A-24

H_A-25

H_A-26

H_A-27

H_A-28

H_A-29

H_A-30

H_A-31

H_A-32

H_A-33

H_A-34

H_A-35

T13T13

T14T14

T15T15

T16T16

T18T18

C15

C15

X_100PF

X_100PF

AB6

AA4

AD6

AA5

AB5

AC5

AB4

AF5

AF4

AG6

AG4

AG5

AH4

AH5

AC4

AE4

AD5

A23

B23

D23

C23

AM2

AL5

AM3

AL6

AK4

AL4

AM5

AM7

AN7

G28

AE8

AL1

AK1

AN3

AN4

AN5

AN6

2

J1A

J1A

L5

A3-

P6

A4-

M5

A5-

L4

A6-

M4

A7-

R4

A8-

T5

A9-

U6

A10-

T4

A11-

U5

A12-

U4

A13-

V5

A14-

V4

A15-

W5

A16-

N4

RESERVED10

P5

RESERVED11

K4

REQ0-

J5

REQ1-

M6

REQ2-

K6

REQ3-

J6

REQ4-

R6

ADSTB0-

G5

PECI

A17-

W6

A18-

Y6

A19-

Y4

A20A21A22A23A24A25A26A27A28A29A30A31A32A33-

AJ5

A34-

AJ6

A35RESERVED12

RESERVED13

ADSTB1-

P2

SMI-

K3

A20M-

R3

FERR_PBE-

K1

LINT0

L1

LINT1

N2

IGNNE-

M3

STPCLKVCCA

VSSA

VCCPLL

VCCIOPLL

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VID7

VID_SELECT

F28

BCLK0

BCLK1

SKTOCCFC25

FC24

VCC_SENSE

VSS_SENSE

VCC_MB_REGULATION

VSS_MB_REGULATION

F29

RESERVED14

LGA775_72MMX72MM_INTEL

LGA775_72MMX72MM_INTEL

CPU_THERMDC 20

CPU_THERMDA 20

2

1 of 4

1 of 4

FC0_BOOTSELECT

ADSBNR-

HIT-

FC35

BPRIDBSYDRDY-

HITM-

IERR-

INITLOCKTRDY-

FC36

DEFER-

GTLREF2

FC37

FC29

FC30

BR0BPMB3BPMB2-

TESTHI10

FC31

FC32

FC33

FC34

GTLREF0

FC15

RESET-

RS0-

RS1-

RS2-

TESTHI0

TESTHI1

DPSLP-

TDI_M

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

FC8

RESERVED15

SLP-

RESERVED16

PWRGOOD

PROCHOT-

THERMTRIP-

COMP0

COMP1

COMP2

COMP3

RESERVED17

RESERVED18

BPMB1RESERVED20

RESERVED21

GTLREF3

BPMB0-

TDO_M

RESERVED22

FC10

RESERVED23

GTLREF1

FC3

FC22

RESERVED19

FC39

D2

C2

D4

H4

G8

B2

C1

E4

AB2

P3

C3

E3

AD3

G7

F2

AB3

U2

U3

F3

G3

G4

H5

J16

H15

H16

J17

H1

H29

G23

B3

F5

A3

F26

W3

P1

W2

F25

G25

G27

G26

G24

F24

AK6

G6

L2

AH2

N1

AL2

M2

A13

T1

G2

R1

N5

AE6

C9

D16

A20

G10

G1

U1

E23

E24

F23

H2

J2

J3

Y1

V2

AA2

3

T2T2

H_IERR-

T4T4

T3T3

T6T6

T7T7

TESTHI_8

TESTHI_9

TESTHI_10

T8T8

T9T9

T10T10

T11T11

CPU_GTLREF0

T12T12

C2 XC2 X

CLOSE TO CPU

TESTHI_0

TESTHI_1

DPSLPTESTHI_12

TESTHI_2-7

T17T17

T19T19

H_COMP0

H_COMP1

H_COMP2

H_COMP3

T20T20

T21T21

R34 51R

R34 51R

T22T22

T23T23

H_BPM0_2

TESTHI_12

T26T26

T27T27

T28T28

CPU_GTLREF1

H_COMP4

T30T30

BOOTSELECT

T31T31

T32T32

CLOSE TO CPU

SST: 100PF

SCH5127: 2200PF

3

C3 XC3 X

H_FORCEPH_IO-

PM_SLP_N

H_IGNNE-15

H_STPCLK-15

THERMTRIP_ICH-15

H_ADS- 6

H_BNR- 6

H_HIT- 6

H_BPRI- 6

H_DBSY- 6

H_DRDY- 6

H_HITM- 6

H_INIT- 15

H_LOCK- 6

H_TRDY- 6

H_DEFER- 6

CPU_GTLREF2 4

H_BR0- 6

H_CPURST- 5,6,36

H_RS0- 6

H_RS1- 6

H_RS2- 6

DPSLP- 15

H_PWRGD- 15

H_PROCHOT- 15

THERMTRIP_ICH- 15

H_PECI15,20

H_SMI-15

H_INTR15

H_NMI15

H_INIT-15

VTT_OUT_R 4,5,36

0402

0402

CPU_GTLREF3 4

H_A20M-15

H_FERR-15

C5 XC5 X

VTT_OUT_R4,5,36

CPU_GTL0_DIVIDER4

C6 XC6 X

4

Place resistors outside socket cavity

R1 49R9_1%

R1 49R9_1%

0402

0402

R2 49R9_1%

R2 49R9_1%

0402

0402

FSB_VTT

R3 51R

R3 51R

0402

0402

R6 51R

R6 51R

0402

0402

R7 470R

R7 470R

0402

0402

R8 470R

R8 470R

0402

0402

R9 470R

R9 470R

0402

0402

R4 62R

R4 62R

0402

0402

CLOSE TO ICH

R5 49R9_1%

R5 49R9_1%

0402

0402

R10 49R9_1%

R10 49R9_1%

0402

0402

R11 51R

R11 51R

0402

0402

VTT_OUT_L

R12 62R

R12 62R

0402

0402

X_51R

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

R25 62R

R25 62R

R26 X

R26 X

R27 X

R27 X

R28 X

R28 X

R29 X

R29 X

R30 680R

R30 680R

R32

R32

57.6R_1%

57.6R_1%

R36

R36

100R_1%

100R_1%

C12 XC12 X

C10 XC10 X

C11 XC11 X

4

C7 XC7 X

VTT_OUT_R4,5,36

C8 XC8 X

R13 X

R13 X

R14 51R

R14 51R

R15 51R

R15 51R

R16 51R

R16 51R

R17 51R

R17 51R

R18 X

R18 X

R19 51R

R19 51R

R20 62R

R20 62R

R21 X

R21 X

R22 X

R22 X

R23 51R

R23 51R

R24 X

R24 X

C9 XC9 X

PM_SLP_N

TESTHI_1

TESTHI_8

TESTHI_9

TESTHI_10

DPSLPTESTHI_12

X_49.9R_1%

X_100R

H_BPM0_2

H_COMP4

X_49.9R_1%

0402

0402

X_130R_1%

0402

0402

0402

0402

X_49.9R_1%

0402

0402

X_49.9R_1%

0402

0402

0402

0402

C13 XC13 X

C14 XC14 X

5

H_COMP0

H_COMP1

TESTHI_0

TESTHI_2-7

H_COMP2

H_COMP3

BOOTSELECT

H_CPURST- 5,6,36

PM_SLP_N 6

H_BR0- 6

PM_DPRSTP- 4,6,15

H_PWRGD- 15

H_IERRH_FORCEPH_IO-

H_PROCHOT- 15

PSI- 4,36

H_VID_SEL

CM1CM1

H_COMP7 4

R35 10R_1%R35 10R_1%

CLOSE TO CPU_GTLREF PIN

CPU_GTL1_DIVIDER4

5

FSB_SEL0 6,19

FSB_SEL1 6,19

FSB_SEL2 6,19

H_FERR- 15

C4 XC4 X

X_220PF

VTT_OUT_R4,5,36

ITP_CLKOUT-5

R3757.6R_1% R3757.6R_1%

R39100R_1% R39100R_1%

H_D-[0..63]6

H_DBI0-6

H_DSTBN0-6

H_DSTBP0-6

H_DBI1-6

H_DSTBN1-6

H_DSTBP1-6

H_TRST-5

H_BPM-[0..5]5

DBRESET-5,15,22

ITP_CLKOUT5

FSB_SEL06,19

FSB_SEL16,19

FSB_SEL26,19

6

H_TCK5

H_TDI5

H_TDO5

H_TMS5

CPU_GTLREF0 4

R38 10R_1%R38 10R_1%

CM2CM2

6

H_D-0

H_D-1

H_D-2

H_D-3

H_D-4

H_D-5H_A-15

H_D-6

H_D-7

H_D-8

H_D-9

H_D-10

H_D-11

H_D-12

H_D-13

H_D-14

H_D-15

H_D-16

H_D-17

H_D-18

H_D-19

H_D-20

H_D-21

H_D-22

H_D-23

H_D-24

H_D-25

H_D-26

H_D-27

H_D-28

H_D-29

H_D-30

H_D-31

H_BPM-0

H_BPM-1

H_BPM-2

H_BPM-3

H_BPM-4

H_BPM-5

C16 XC16 X

X_220PF

J1B

J1B

A10

A11

B10

C11

B12

C12

D11

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

G11

G12

E12

AE1

AD1

AF1

AC1

AG1

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

G29

H30

G30

B4

C5

A4

C6

A5

B6

B7

A7

D8

A8

C8

B9

G9

F8

F9

E9

D7

2 of 4

2 of 4

D0D1D2D3D4D5D6D7D8D9D10D11D12D13D14D15DBI0DSTBN0DSTBP0-

D16D17D18D19D20D21D22D23D24D25D26D27D28D29D30D31DBI1DSTBN1DSTBP1-

TCK

TDI

TDO

TMS

TRST-

BPM0BPM1BPM2BPM3BPM4BPM5-

DBRITP_CLK0

ITP_CLK1

BSEL0

BSEL1

BSEL2

LGA775_72MMX72MM_INTEL

LGA775_72MMX72MM_INTEL

CPU_GTLREF1 4

TITLE:

TITLE:

TITLE:

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

7

H_D-32

G16

D32-

H_D-33

E15

D33-

H_D-34

E16

D34-

H_D-35

G18

D35-

H_D-36

G17

D36-

H_D-37

F17

D37-

H_D-38

F18

D38-

H_D-39

E18

D39-

H_D-40

E19

D40-

H_D-41

F20

D41-

H_D-42

E21

D42-

H_D-43

F21

D43-

H_D-44

G21

D44-

H_D-45

E22

D45-

H_D-46

D22

D46-

H_D-47

G22

D47-

D19

DBI2-

G20

DSTBN2-

G19

DSTBP2-

DBI3DSTBN3DSTBP3-

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

FC40

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

G43NT

G43NT

G43NT

LGA775 1/3

LGA775 1/3

LGA775 1/3

Date: PAGE:

Date: PAGE:

Date: PAGE:

A3

A3

A3

7

D20

D48-

D17

D49-

A14

D50-

C15

D51-

C14

D52-

B15

D53-

C18

D54-

B16

D55-

A17

D56-

B18

D57-

C21

D58-

B21

D59-

B19

D60-

A19

D61-

A22

D62-

B22

D63-

C20

A16

C17

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

AM6

AA1

J1

F27

<Doc>

<Doc>

<Doc>

James Xiong

James Xiong

James Xiong

Sunday, April 06, 2008

Sunday, April 06, 2008

Sunday, April 06, 2008

H_D-48

H_D-49

H_D-50

H_D-51

H_D-52

H_D-53

H_D-54

H_D-55

H_D-56

H_D-57

H_D-58

H_D-59

H_D-60

H_D-61

H_D-62

H_D-63

R31 0R

R31 0R

R33 X

R33 X

CB1CB1

FSB_VTT

X_0R

CB2CB2

CB3CB3

H_DBI2- 6

H_DSTBN2- 6

H_DSTBP2- 6

H_DBI3- 6

H_DSTBN3- 6

H_DSTBP3- 6

0402

0402

0402

0402

VTT_OUT_L

VTT_SEL 33

8

VTT_PWRGD 33,36

VR_READY 15,36

VTT_OUT_R 4,5,36

REV:

REV:

REV:

0.2

0.2

0.2

346

346

346

of

of

of

8

1

A A

H_COMP73

PM_DPRSTP-3,6,15

B B

C C

D D

E E

H_COMP8

MS_ID0

PSI-3,36

IMPSEL

MS_ID1

J1C

J1C

AG22

VCCP1

K29

VCCP2

AM26

T116T116

AL8

AE12

AE11

W23

W24

W25

T25

Y28

AL18

AC25

W30

Y30

AN14

AD28

Y26

AC29

M29

U24

AC27

AM18

AM19

AB8

AC26

T30

AM9

AF15

AC8

AE14

N23

W29

U29

AC24

AC23

Y23

AN26

AN25

AN11

AN18

Y27

Y25

AD24

AE23

AE22

AN19

AE21

AM30

AE19

AC30

AE15

M30

K27

M24

AN21

VCCP3

VCC

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

J23

VCCP22

VCCP23

VCCP24

VCCP25

VCCP26

VCCP27

J8

VCCP28

J28

VCCP29

VCCP30

VCCP31

VCCP32

VCCP33

VCCP34

VCCP35

VCCP36

VCCP37

VCCP38

VCCP39

VCCP40

VCCP41

VCCP42

VCCP43

VCCP44

VCCP45

VCCP46

VCCP47

VCCP48

VCCP49

VCCP50

V8

VCCP51

K8

VCCP52

VCCP53

VCCP54

VCCP55

VCCP56

VCCP57

VCCP58

VCCP59

VCCP60

VCCP61

2

X

CPU_GTL0_DIVIDER3

CPU_GTL1_DIVIDER3

CPU_GTLREF03

CPU_GTLREF13

T34T34

T33T33

B13

T2

F6

AE3

E7

V1

FC21

MSID1

VCCP62T8VCCP63

N25

AC28

D14

W1

FC17Y3FC18

MSID0

COMP8

DPRSTP-

RESERVED5

RESERVED6

RESERVED7E6RESERVED8

VCCP64

VCCP65

VCCP66

VCCP67

VCCP68M8VCCP69

VCCP70

VCCP71

N30

W26

AE18

AJ26

AD25

AD26

X

0402

0402

0R

0R

stuff 0R

0402

0402

X

X

0402

0402

X

X

0402

0402

T37T37

T36T36

T35T35

E5

D1

FC20

VCCP72

VCCP73

VCCP74

VCCP75L8VCCP76

VCCP77Y8VCCP78

VCCP79

U25

M25

M26

AM29

U23

AJ12

AD27

CPU_GTLREF_OUT

R40

R40

CPU_GTLREF_OUT

R41

R41

R43

R43

R46

R46

VCORE

AK9

M28

AF12

VCCP226

VCCP225

VCCP224

VCCP223N8VCCP222

LGA775_72MMX72MM_INTEL

LGA775_72MMX72MM_INTEL

VCCP80

VCCP81

VCCP82

VCCP83

VCCP84

VCCP85

N27

U28

M23

AG29

AM22

3

CPU_GTLREF3 3

CPU_GTLREF2 3

AF19

K26

J14

AN22

N24

VCCP221

VCCP220

VCCP219

VCCP218

3 of 4

3 of 4

VCCP86

VCCP87U8VCCP88

VCCP89

VCCP90

K28

K24

AD8

AK18

4

VCC3

1UF

1UF

CM3

CM3

1K

1K

0402

0402

CPU_GTL_CTRL115

AH8

AD29

AL29

AG8

AA8

AG18

J30

AF14

M27

AK14

Y24

AF21

AD30

AL9

AG19

J27

J12

W28

T28

VCCP217

VCCP216W8VCCP215

VCCP214

VCCP213

VCCP212

VCCP211

VCCP210

VCCP209

VCCP208

VCCP207J9VCCP206

VCCP205

VCCP204

VCCP203

VCCP202

VCCP201

VCCP200

VCCP199

VCCP198

VCCP91

VCCP92

VCCP93

VCCP94

VCCP95

VCCP96

VCCP97

VCCP98

VCCP99

VCCP100

VCCP101

VCCP102

VCCP103

VCCP104

VCCP105

VCCP106

VCCP107

VCCP108

VCCP109

VCCP110

J22

T29

Y29

AE9

AK12

AH28

AH21

AH22

AK25

AK19

AM14

AM25

J25

T24

U30

AJ18

AG15

AL21

AG21

AG25

AM21

U1

1

VDD

2

VSS

AL26

AG12

3

VCCP193

VCCP115

GTL3004U1GTL3004

AG28

AH27

VCCP192

VCCP116

J20

AJ22

GTL_REF

S0

AH29

AH19

AJ14

VCCP191

VCCP190

VCCP189

VCCP188

VCCP117

VCCP118

VCCP119

VCCP120

W27

AH18

AH26

R47

R47

J13

J24

AM12

VCCP197

VCCP196

VCCP195

VCCP194

VCCP111

VCCP112

VCCP113

VCCP114

J19

J15

AH30

5

6

VTT

CPU_GTLREF_OUT

5

4

S1

AH11

AF22

AF9

N26

VCCP187

VCCP186

VCCP185

VCCP184

VCCP183

VCCP182

VCCP181

VCCP180

VCCP179

VCCP178

VCCP177

VCCP176

VCCP175

VCCP174

VCCP173

VCCP172

VCCP171

VCCP170

VCCP169

VCCP168

VCCP167

VCCP166

VCCP165

VCCP164

VCCP163

VCCP162

VCCP161

VCCP160

VCCP159

VCCP158

VCCP157

VCCP156

VCCP155

VCCP154

VCCP153

VCCP152

VCCP151

VCCP150

VCCP149

VCCP148

VCCP147

VCCP146

VCCP145

VCCP144

VCCP143

VCCP142

VCCP141

VCCP140

VCCP139

VCCP138

VCCP137

VCCP136

VCCP135

VCCP134

VCCP133

VCCP132

VCCP131

VCCP130

VCCP129

VCCP128

VCCP127

VCCP126

VCCP125

VCCP124

VCCP123

VCCP121

VCCP122

AN8

AL25

CM4

CM4

1UF

1UF

AG9

AN12

AK8

T27

AJ19

U26

AJ8

AN15

AL22

AH12

N28

T26

AM8

AL19

K23

P8

K25

J11

J29

AH9

AJ25

AL30

N29

AG14

AK11

AJ9

AL12

AH25

AN30

AL14

K30

AJ11

AL11

AM11

AJ21

AG30

AK21

AF8

AM15

AD23

AF11

AK15

AG27

J21

J18

J26

AL15

AF18

AH15

AN9

AG26

AJ15

J10

AK26

AG11

AN29

AK22

R8

T23

U27

AH14

R44

R44

1K

1K

0402

0402

VTT_OUT_R 3,5,36

CPU_GTL_CTRL2 15

VTT_OUT_R3,5,36

MS_ID0

MS_ID1

VTT_OUT_R3,5,36

VTT_OUT_R3,5,36

6

R52 X

R52 X

R53 X

R53 X

R54

R54

57.6R_1%

57.6R_1%

R56

R56

100R_1%

100R_1%

57.6R_1%

57.6R_1%

R59

R59

100R_1%

100R_1%

R57

R57

H_COMP8

IMPSEL

MS_ID0

MS_ID1

R42

R42

R45 51R

R45 51R

R48 X

R48 X

R49 X

R49 X

0402

0402

R51

R51

X

X

X_1K

X_0R

0402

0402

X_0R

0402

0402

For Quad-core CPU support in future

R55 10R_1%R55 10R_1%

CM5CM5

CLOSE TO CPU_GTLREF PIN

R58 10R_1%R58 10R_1%

CM6CM6

CLOSE TO CPU_GTLREF PIN

Q1

Q1

B

B

1

7

24R9_1%

24R9_1%

0402

0402

0402

0402

X_51R

0402

0402

0402

0402

0402

0402

R50

R50

680R

680R

C

C

X_3904_SOT23

X_3904_SOT23

E

E

2 3

X_220PF

C17 XC17 X

X_220PF

C18 XC18 X

8

VRD_EN 36

CPU_GTLREF2 3

CPU_GTLREF3 3

TITLE:

TITLE:

TITLE:

G43NB

G43NB

F F

1

2

3

4

5

6

G43NB

LGA775 2/3

LGA775 2/3

LGA775 2/3

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

7

<Doc>

<Doc>

<Doc>

Tim Zhao

Tim Zhao

Tim Zhao

Date: PAGE:

Date: PAGE:

Date: PAGE:

Saturday, April 05, 2008

Saturday, April 05, 2008

Saturday, April 05, 2008

REV:

REV:

REV:

446

446

446

8

0.1

0.1

0.1

of

of

of

1

2

3

4

5

6

7

8

H_BPM-[0..5]3

A A

AG23

AF20

AL28

AA23

V26

AM4

AB1

AJ27

R30

E27

AE17

AE20

P24

AN24

AF17

AG24

AF23

AF24

AN27

AN28

AF25

AF26

AF27

AF28

AF29

H28

AF30

AE13

AG10

AA30

AB23

AB24

AB25

AN16

AB26

AB27

AN17

AG20

AB28

AB29

AB30

AK24

C13

AH1

AE26

J1D

J1D

VSS266

VSS265

VSS264

VSS263

VSS262

VSS261

VSS260

VSS259

VSS258

VSS257T7VSS256

VSS255

VSS254

VSS253

VSS252H3VSS251

VSS250

VSS249

VSS248

VSS247

VSS246

VSS245

VSS244

VSS243

VSS242

VSS241

VSS240

VSS239F7VSS238

VSS237

VSS236

VSS235

VSS234F4VSS233

VSS232N3VSS231

VSS230

VSS229

VSS228M7VSS227

VSS226

VSS225

VSS224

VSS223

VSS222E8VSS221

VSS220M1VSS219

C10

VSS1

D12

VSS2

C24

VSS3

K2

VSS4

C22

VSS5

AN1

VSS6

B14

VSS7

AE16

B11

AL10

AK23

H12

AF7

AK7

E14

E11

AL16

AL24

AK13

D21

AL20

D18

AN2

AK16

AK20

AM27

AM1

AL13

AL17

C19

E28

AK30

D24

AL23

A12

AE28

AE29

AE30

AN20

AF10

AE24

AM24

AN23

H13

AC6

AC7

AH6

C16

AM16

AE25

AE27

AJ28

F19

AH13

AD7

AH16

AK17

E17

AH17

AH20

AE5

AH23

AE7

AM13

K7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

H7

VSS16

VSS17

L28

VSS18

Y5

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

L25

VSS40

J7

VSS41

VSS42

VSS43

K5

VSS44

J4

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

H9

VSS52

H8

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

4 of 4

4 of 4

LGA775_72MMX72MM_INTEL

LGA775_72MMX72MM_INTEL

B B

C C

D D

E E

VSS218L7VSS217L6VSS216

AJ4

VSS215

VSS214

VSS213V7VSS212

VSS211

VSS210

VSS209B8VSS208B5VSS207B1VSS206D3VSS205A9VSS204D5VSS203D6VSS202A6VSS201C4VSS200D9VSS199E2VSS198A2VSS197

A18

H6

VSS196

VSS195

VSS194

VSS193

VSS192

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS164

VSS163

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS152

VSS151

VSS150

VSS149

VSS148

VSS267

VSS268

FC23

FC26

VRDSEL

AF13

AE10

AF16

P29

V3

P30

R23

R24

U7

R25

R26

R27

R28

R29

E25

AL7

T6

V23

V24

T3

V25

AN10

E20

R7

V27

R5

V28

V29

R2

V30

E26

P7

AA24

AA25

P4

AA26

AA27

AN13

AA28

N7

N6

AA29

L27

Y7

AL27

D15

L29

L30

AH7

AJ7

A24

E29

AL3

T115T115

H_BPM-[0..5]3

ITP_CLKOUT3

CLK_HOST_ITP19

CLK_HOST_ITP-19

ITP_CLKOUT-3

SMB_CLK10,19,23

SMB_DATA10,19,23

VTT_OUT_R3,4,36

SAM TEC BSH -03-01-H-D

T38T38

T39T39

R78 X

R78 X

0402

0402

X_1K

H_TDO3

H_TDI3

H_TMS3

H_TCK3

H_TRST-3

H_BPM-0

H_BPM-1

H_BPM-2

H_BPM-3

H_BPM-4

H_BPM-5

R75 XR75 X

R73 0RR73 0R

R72 0RR72 0R

R74 XR74 X

TESTIN-

J28J28

9

BPM0*

7

BPM1*

6

BPM2*

4

BPM3*

3

BPM4*

1

BPM5*

16

100M_CLK_DP

18

100M_CLK_DN

13

XDP_H_CLK_DP

15

XDP_H_CLK_DN

22

SCL

24

SDA

14

VTT

28

NC0

H_BPM-0

H_BPM-1

H_BPM-2

H_BPM-3

H_BPM-4

H_BPM-5

NC1H1NC2

R60 51R

R60 51R

0402

0402

R61 51R

R61 51R

0402

0402

R62 51R

R62 51R

0402

0402

R63 51R

R63 51R

0402

0402

R64 51R

R64 51R

0402

0402

R65 51R

R65 51R

0402

0402

R66 62R

R66 62R

0402

0402

R67 62R

R67 62R

0402

0402

R68 62R

R68 62R

0402

0402

R69 62R

R69 62R

0402

0402

R70 62R

R70 62R

0402

0402

R71 62R

R71 62R

0402

0402

TDO

TDI

TMS

TCK

TRST*

PWRGOOD

RESET*

DBR*

TESTIN*

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

H2

CB4CB4

23

29

31

30

25

R76 1K5_1%

R76 1K5_1%

10

19

21

12

2

5

8

11

17

20

26

27

0402

0402

TESTIN-

0402

0402

VTT_OUT_R 3,4,36

R771K

R771K

H_TDO 3

H_TDI 3

H_TMS 3

H_TCK 3

H_TRST- 3

VTT_OUT_R 3,4,36

H_CPURST- 3,6,36

DBRESET- 3,15,22

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102L3VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132V6VSS133W4VSS134

VSS135

VSS136

VSS137

VSS138

VSS139Y2VSS140C7VSS141

VSS142

VSS143

VSS144

VSS145W7VSS146

VSS147

L26

L24

F22

F16

AF3

AF6

AK5

AJ30

AJ10

AJ16

AJ17

F F

AH24

1

AK29

F13

AH3

AG7

AJ23

AK10

AM10

L23

F10

2

A15

B24

A21

B20

H11

AD4

H27

AE2

AH10

AM23

AJ29

B17

H26

H25

H24

H23

H10

H22

H21

H20

H19

AA3

AA7

AK27

AK28

AM20

3

AA6

H18

AB7

H17

P28

P26

H14

AC3

AJ24

AM17

P27

AK2

AJ13

AM28

4

P23

P25

AJ20

AG17

AG16

AG13

5

6

TITLE:

TITLE:

TITLE:

G43NT

G43NT

G43NT

LGA 775 3/3

LGA 775 3/3

LGA 775 3/3

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

7

<Doc>

<Doc>

<Doc>

James Xiong

James Xiong

James Xiong

Date: PAGE:

Date: PAGE:

Date: PAGE:

Sunday, April 06, 2008

Sunday, April 06, 2008

Sunday, April 06, 2008

8

REV:

REV:

REV:

0.2

0.2

0.2

546

546

546

of

of

of

1

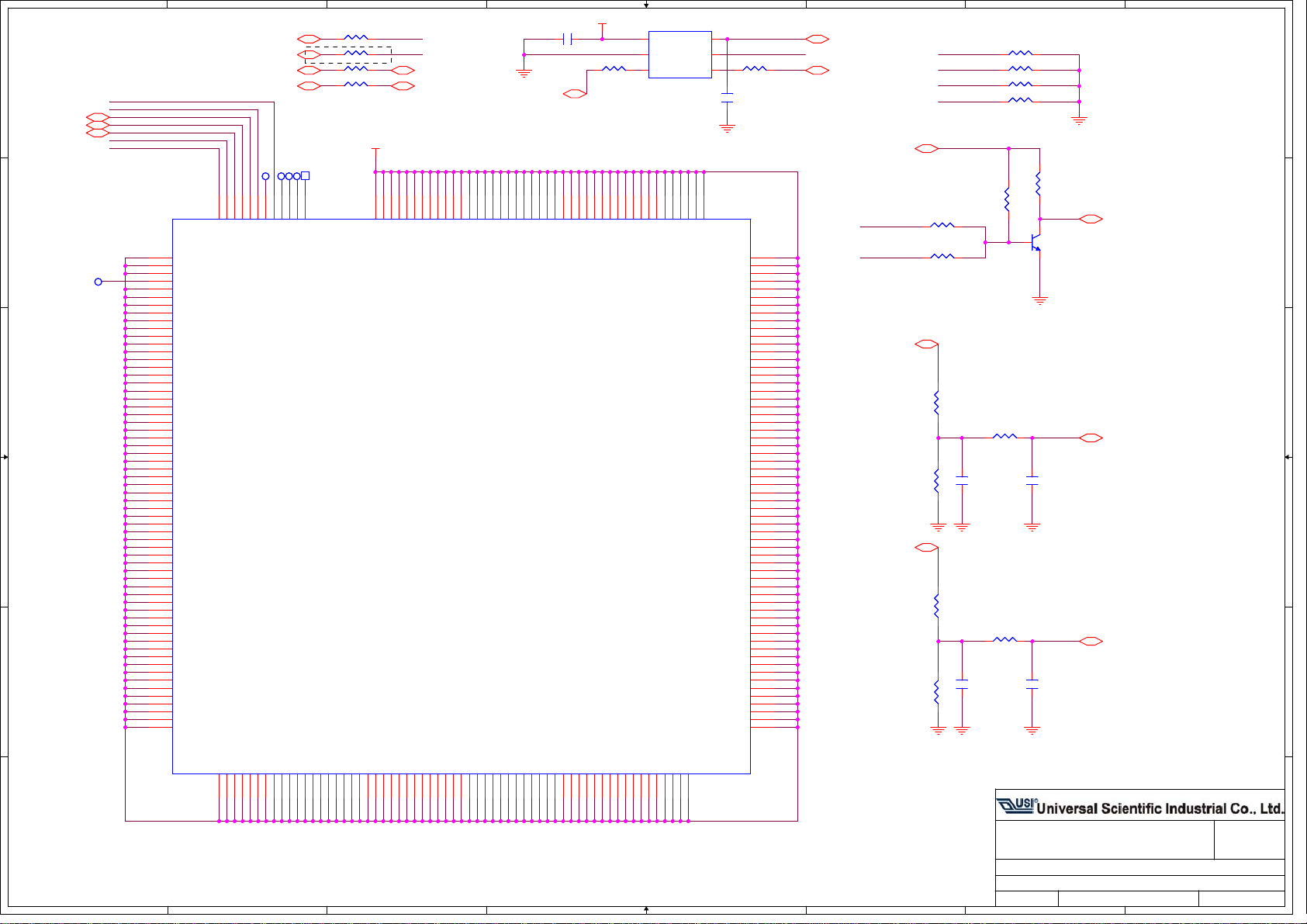

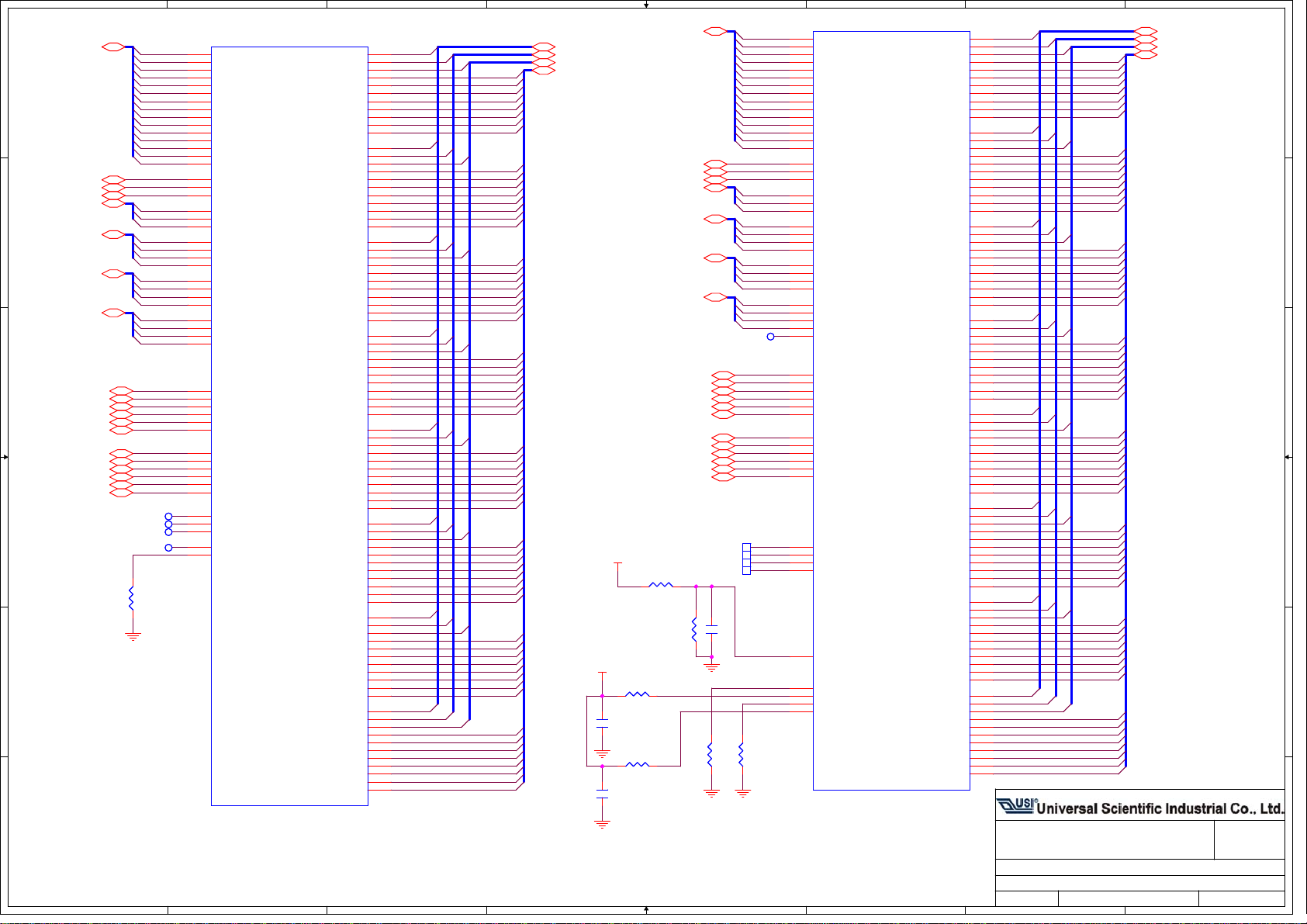

U2A

AA35

AA37

AA36

L36

L37

J38

F40

H39

L38

L43

N39

N35

N37

J41

N40

M45

R35

T36

R36

R34

R37

R39

U38

T37

U34

U40

T34

Y36

U35

U37

Y37

Y34

Y38

G38

K35

J39

C43

G39

J40

T39

C39

B39

B40

K31

J31

F33

J25

K25

F26

C32

D32

D30

J42

J44

H37

L42

D27

H42

G44

J43

H45

K44

H40

G43

L44

G42

L40

U2A

FSB_AB_3

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQB_0

FSB_REQB_1

FSB_REQB_2

FSB_REQB_3

FSB_REQB_4

FSB_ADSTBB_0

FSB_ADSTBB_1

FSB_DSTBPB_0

FSB_DSTBNB_0

FSB_DINVB_0

FSB_DSTBPB_1

FSB_DSTBNB_1

FSB_DINVB_1

FSB_DSTBPB_2

FSB_DSTBNB_2

FSB_DINVB_2

FSB_DSTBPB_3

FSB_DSTBNB_3

FSB_DINVB_3

FSB_ADSB

FSB_BNRB

FSB_BPRIB

FSB_BREQ0B

FSB_CPURSTB

FSB_DBSYB

FSB_DEFERB

FSB_DRDYB

FSB_HITB

FSB_HITMB

FSB_LOCKB

FSB_RSB_0

FSB_RSB_1

FSB_RSB_2

FSB_TRDYB

EAGLELAKE

EAGLELAKE

CM7CM7

H_A-[3..35]3

A A

B B

H_REQ-[0..4]3

H_ADSTB0-3

H_ADSTB1-3

C C

H_DSTBP0-3

H_DSTBN0-3

H_DBI0-3

H_DSTBP1-3

H_DSTBN1-3

H_DBI1-3

H_DSTBP2-3

H_DSTBN2-3

H_DBI2-3

H_DSTBP3-3

H_DSTBN3-3

H_DBI3-3

D D

E E

F F

H_ADS-3

H_BNR-3

H_BPRI-3

H_BR0-3

H_CPURST-3,5,36

H_DBSY-3

H_DEFER-3

H_DRDY-3

H_HIT-3

H_HITM-3

H_LOCK-3

H_RS0-3

H_RS1-3

H_RS2-3

H_TRDY-3

FSB_VTT

GTLREF Voltage should be 0.63xVTT = 0.8V

0402

0402

R99

R99

R95

R95

49R9_1%

49R9_1%

301R_1%

301R_1%

0402

0402

HD_SWING S/B 1/4xVTT +/-2%

CB6CB6

R106

R106

100R_1%

100R_1%

H_A-3

H_A-4

H_A-5

H_A-6

H_A-7

H_A-8

H_A-9

H_A-10

H_A-11

H_A-12

H_A-13

H_A-14

H_A-15

H_A-16

H_A-17

H_A-18

H_A-19

H_A-20

H_A-21

H_A-22

H_A-23

H_A-24

H_A-25

H_A-26

H_A-27

H_A-28

H_A-29

H_A-30

H_A-31

H_A-32

H_A-33

H_A-34 H_D-31

H_A-35 H_D-32

H_REQ-0

H_REQ-1

H_REQ-2

H_REQ-3

H_REQ-4

51R resistor to MCH GTLREF

pins is 1.5" max

HXSWING

0402

0402

10/10 mils

1

1 of 6

1 of 6

FSB

FSB

FSB_VTT

FSB_ACCVREF

R91: 57.6R

R100: 100R

R91

R91

57.6R_1%

57.6R_1%

R96

R96

49R9_1%

49R9_1%

R101

R101

100R_1%

100R_1%

2

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_DVREF

HPL_CLKINP

HPL_CLKINN

0402

0402

2

C21 XC21 X

H_D-0

F44

H_D-1

C44

H_D-2

D44

H_D-3

C41

H_D-4

E43

H_D-5

B43

H_D-6

D40

H_D-7

B42

H_D-8

B38

H_D-9

F38

H_D-10

A38

H_D-11

B37

H_D-12

D38

H_D-13

C37

H_D-14

D37

H_D-15

B36

H_D-16

E37

H_D-17

J35

H_D-18

H35

H_D-19

F37

H_D-20

G37

H_D-21

J33

H_D-22

L33

H_D-23

G33

H_D-24

L31

H_D-25

M31

H_D-26

M30

H_D-27

J30

H_D-28

G31

H_D-29

K30

H_D-30

M29

G30

J29

H_D-33

F29

H_D-34

H29

H_D-35

L25

H_D-36

K26

H_D-37

L29

H_D-38

J26

H_D-39

M26

H_D-40

H26

H_D-41

F25

H_D-42

F24

H_D-43

G25

H_D-44

H24

H_D-45

L24

H_D-46

J24

H_D-47

N24

H_D-48

C28

H_D-49

B31

H_D-50

F35

H_D-51

C35

H_D-52

B35

H_D-53

D35

H_D-54

D31

H_D-55

A34

H_D-56

B32

H_D-57

F31

H_D-58

D28

H_D-59

A29

H_D-60

C30

H_D-61

B30

H_D-62

E27

H_D-63

B28

HXSWING

B24

HRCOMP

A23

GMCH_GTLREF

C22

B23

P29

P30

GMCH_GTLREF

X_220PF

Place close to GMCH pin

CL_VREF

Follow CRB.

Design checklist shows 1K/465R

0:PCIE16 Lane number reversed

1:PCIE16 normal operation

0402

0402

R88

R88

16R5_1%

16R5_1%

CLK_HOST_GMCH 19

CLK_HOST_GMCH- 19

VCC3

PEG_PINB713,29

3

H_D-[0..63] 3

CB5CB5

FSB_SEL03,19

FSB_SEL13,19

FSB_SEL23,19

EXP_SLR13

EXP_EN13,29

0: Enable Internal TPM

Float: Disable Internal TPM

R92

R92

0402

0402

X

X

R93

R93

0402

0402

X

X

R94

R94

0402

0402

X

X

R97

R97

0402

0402

X

X

R98

R98

0402

0402

X

X

R100

R100

0402

0402

X

X

Oct 1 added

3

VCC1.125V_CL

1K_1%

1K_1%

0402

0402

R79

R79

0402

0402

464R_1%

464R_1%

R80

R80

PM_EXTTS_N

MCH_RSVD_K16

DUALX8_EN

MCH_RSVD_J15

MCH_RSVD_J20

CLK_PE_100M_GMCH19

CLK_PE_100M_GMCH-19

SDVO_CTRL_DATA13,29

SDVO_CTRL_CLK13,29

R83 10K

R83 10K

R84 10K

R84 10K

R85 10K

R85 10K

MCH_CLPWROK16,38

EXP_RXP_029

EXP_RXN_029

EXP_RXP_129

EXP_RXN_129

EXP_RXP_229

EXP_RXN_229

EXP_RXP_329

EXP_RXN_329

EXP_RXP_429

EXP_RXN_429

EXP_RXP_529

EXP_RXN_529

EXP_RXP_629

EXP_RXN_629

EXP_RXP_729

EXP_RXN_729

EXP_RXP_829

EXP_RXN_829

EXP_RXP_929

EXP_RXN_929

EXP_RXP_1029

EXP_RXN_1029

EXP_RXP_1129

EXP_RXN_1129

EXP_RXP_1213

EXP_RXN_1213

EXP_RXP_1329

EXP_RXN_1329

EXP_RXP_1429

EXP_RXN_1429

EXP_RXP_1529

EXP_RXN_1529

DMI_RXP_016

DMI_RXN_016

DMI_RXP_116

DMI_RXN_116

DMI_RXP_216

DMI_RXN_216

DMI_RXP_316

DMI_RXN_316

R86 X

R86 X

MCH_RSVD_K16

R87

R87

X

X

R89

R89

1K

1K

CL_N_DATA16

CL_N_CLK16

CL_RST16

4

U2B

U2B

2 of 6

2 of 6

F6

PEG_RXP_0

G7

PEG_RXN_0

H6

PEG_RXP_1

G4

PEG_RXN_1

J6

PEG_RXP_2

J7

PEG_RXN_2

L6

PEG_RXP_3

L7

PEG_RXN_3

N9

PEG_RXP_4

N10

PEG_RXN_4

N7

PEG_RXP_5

N6

PEG_RXN_5

R7

PEG_RXP_6

R6

PEG_RXN_6

R9

PEG_RXP_7

R10

PEG_RXN_7

U10

PEG_RXP_8

U9

PEG_RXN_8

U6

PEG_RXP_9

U7

PEG_RXN_9

AA9

PEG_RXP_10

AA10

PEG_RXN_10

R4

PEG_RXP_11

P4

PEG_RXN_11

AA7

PEG_RXP_12

AA6

PEG_RXN_12

AB10

PEG_RXP_13

AB9

PEG_RXN_13

AB3

PEG_RXP_14

AA2

PEG_RXN_14

AD10

PEG_RXP_15

AD11

PEG_RXN_15

AD7

DMI_RXP_0

AD8

DMI_RXN_0

AE9

DMI_RXP_1

AE10

DMI_RXN_1

AE6

DMI_RXP_2

AE7

DMI_RXN_2

AF9

DMI_RXP_3

AF8

DMI_RXN_3

D9

EXP_CLKP

E9

EXP_CLKN

AB13

T54T54

T55T55

0402

0402

0402

0402

0402

0402

T56T56

T57T57

0402

0402

T58T58

I_TPM_EN-

0402

0402

T59T59

TCEN

0402

0402

T60T60

T61T61

T62T62

T63T63

T64T64

T65T65

T66T66

DUALX8_EN

CL_VREF DPL_100M_REFSSCLKIN-

T67T67

T68T68

T69T69

T70T70

4

AD13

AB15

AN13

AW2

AN10

AN11

J13

G13

F17

G16

P15

M20

N17

F15

H17

K16

G15

L17

R32

J17

G20

N25

T14

T15

R14

R15

F20

AY4

AY2

AN8

AN9

AR7

RSVD15

RSVD16

SDVO_CTRLDATA

SDVO_CTRLCLK

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

EXP_SLR

EXP_SM

RSVD29

RSVD17

ITPM_ENB

RSVD18

CEN

BSCANTEST

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

DUALX8_ENABLE

CL_DATA

CL_CLK

CL_VREF

CL_RSTB

CL_PWROK

JTAG_TMS

JTAG_TDO

JTAG_TDI

JTAG_TCK

EAGLELAKE

EAGLELAKE

PM_EXTTS_N

MCH_RSVD_J20

MCH_RSVD_J15

5

T46T46

T45T45

T43T43

T44T44

T41T41

T40T40

T42T42

DP1DP1

W30

B14

AK15

AE30

AF30

AC30

AD30

A44

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

PCI Express Interface

PCI Express Interface

DMI Interface

DMI Interface

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

J20

J15

L13

L11

M16

T71T71

T72T72

5

T48T48

T47T47

BD1

NC9

RSVD6

J16

T73T73

T52T52

T51T51

T53T53

T50T50

T49T49

DP2DP2

DP3DP3

DP4DP4

DP5DP5

BD45

BE2

BE44

AN16

AW44

R42

U32

B45

AN17

AD42

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

NC19

RSVD11

RSVD10B2RSVD9

RSVD7

RSVD12

RSVD13

RSVD14

RSVD8

A45

U30

U31

R31

BE1

M17

BE45

T78T78

T77T77

T75T75

T76T76

T74T74

T79T79

DP7DP7

DP6DP6

6

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

EXP_RCOMPO

EXP_COMPI

EXP_ICOMPO

EXP_RBIAS

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

HDA_BCLK

HDA_RSTB

HDA_SDI

HDA_SDO

HDA_SYNC

DDPC_CTRLDATA

DDPC_CTRLCLK

DPRSTPB

CRT_DDC_DATA

CRT_DDC_CLK

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

DAC_IREF

ICH_SYNCB

VSS

C16

6

SLPB

RSTINB

PWROK

C11

B11

A10

B9

C9

D8

B8

C7

B7

B6

B3

B4

D2

C2

H2

G2

J2

K2

K1

L2

P2

M2

T2

R1

U2

V2

W4

V3

AA4

Y4

AC1

AB2

AC2

AD2

AD4

AE4

AE2

AF2

AF4

AG4

10mils/10mils

EXP_COMP

Y7

Y8

Y6

EXP_RBIAS

AG1

HSYNC_R

D14

VSYNC_R

C14

B18

D18

C18

F13

AU4

AV4

AU2

AV1

AU3

F11

J11

P43

P42

L15

M15

E15

D15

DPL_100M_REFSSCLKIN

G8

G9

AS SHORT AS POSSIBLE

DAC_IREF

B15

AN6

AR4

K15

EXP_TXP_0 29

EXP_TXN_0 29

EXP_TXP_1 29

EXP_TXN_1 29

EXP_TXP_2 29

EXP_TXN_2 29

EXP_TXP_3 29

EXP_TXN_3 29

EXP_TXP_4 29

EXP_TXN_4 29

EXP_TXP_5 29

EXP_TXN_5 29

EXP_TXP_6 29

EXP_TXN_6 29

EXP_TXP_7 29

EXP_TXN_7 29

EXP_TXP_8 29

EXP_TXN_8 29

EXP_TXP_9 29

EXP_TXN_9 29

EXP_TXP_10 29

EXP_TXN_10 29

EXP_TXP_11 29

EXP_TXN_11 29

EXP_TXP_12 13

EXP_TXN_12 13

EXP_TXP_13 13

EXP_TXN_13 13

EXP_TXP_14 13

EXP_TXN_14 13

EXP_TXP_15 13

EXP_TXN_15 13

DMI_TXP_0 16

DMI_TXN_0 16

DMI_TXP_1 16

DMI_TXN_1 16

DMI_TXP_2 16

DMI_TXN_2 16

DMI_TXP_3 16

DMI_TXN_3 16

Follow CRB.

Design checklist shows 24R9

0402

0402

0402

0402

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_HDA_BCLK 15

MCH_HDA_RST- 15

MCH_HDA_SDIN3 15

MCH_HDA_SDO 15

MCH_HDA_SYNC 15

DDPC_CTRLDATA 29

DDPC_CTRLCLK 29

PM_DPRSTP- 3,4,15

PM_SLP_N 3

VGA_DDC_DA_3V 14

VGA_DDC_CLK_3V 14

CLK_96M_DOT

CLK_96M_DOT-

R90

R90

1K02_1%

1K02_1%

0402

0402

PRST_GMCH- 20

PWR_GD 15,20,21,23,31,38

ICH_SYNC- 15

C19 XC19 X

C20 XC20 X

7

HSYNC_R

VSYNC_R

R8149R9_1%

R8149R9_1%

VCC1.125V_CORE

R82750R_1%

R82750R_1%

VGA_RED 14

VGA_GREEN 14

VGA_BLUE 14

CLK_96M_DOT 19

CLK_96M_DOT- 19

DPL_100M_REFSSCLKIN 19

DPL_100M_REFSSCLKIN- 19

TITLE:

TITLE:

TITLE:

G43NT

G43NT

G43NT

GMCH 1/4

GMCH 1/4

GMCH 1/4

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

7

Date: PAGE:

Date: PAGE:

Date: PAGE:

Custom

Custom

Custom

VGA_DDC_CLK_3V14

VGA_DDC_DA_3V14

R102 33R

R102 33R

R103 33R

R103 33R

CLK_96M_DOT

DPL_100M_REFSSCLKIN

R482

R482

R485

R485

CLK_96M_DOTDPL_100M_REFSSCLKIN-

Stuff for no graphic

<Doc>

<Doc>

<Doc>

James Xiong

James Xiong

James Xiong

Sunday, April 06, 2008

Sunday, April 06, 2008

Sunday, April 06, 2008

0402

0402

0402

0402

R490

R490

R494

R494

C22 XC22 X

X_10K

X_10K

0402

0402

X_10K

X_10K

0402

0402

C23 XC23 X

8

VCC3

0402

0402

2K2_1%

2K2_1%

R104

R104

VGA_HSYNC_3V 14

VGA_VSYNC_3V 14

VCC1.125V_CORE

X_10K

X_10K

0402

0402

X_10K

X_10K

0402

0402

REV:

REV:

REV:

8

0402

0402

2K2_1%

2K2_1%

R105

R105

0.2

0.2

0.2

646

646

646

of

of

of

8

VCC1.125V_CORE

F F

U2C

U2C

3 of 6

3 of 6

U21

VCC_74

U22

VCC_75

U23

VCC_76

U24

VCC_77

U25

VCC_78

U26

VCC_79

U27

VCC_80

U29

VCC_81

W19

VCC_82

W21

VCC_83

E E

FSB_VTT

D D

C C

VCC1.8V_DDR2

B B

W23

W25

W27

W29

Y20

Y22

Y24

Y26

AC4

AF3

R22

R21

R24

R23

R20

P24

P22

P21

P20

N22

N21

N20

M22

M21

K22

K21

H22

H21

G22

G21

F22

F21

E23

D24

D23

D22

C26

C24

B26

B25

A25

BE36

BE31

BE27

BE23

BD38

BD34

BD29

BD25

F9

H4

L3

P3

V4

L22

L21

J22

J21

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VTT_FSB_35

VTT_FSB_34

VTT_FSB_33

VTT_FSB_32

VTT_FSB_31

VTT_FSB_30

VTT_FSB_29

VTT_FSB_28

VTT_FSB_27

VTT_FSB_26

VTT_FSB_25

VTT_FSB_24

VTT_FSB_23

VTT_FSB_22

VTT_FSB_21

VTT_FSB_20

VTT_FSB_19

VTT_FSB_18

VTT_FSB_17

VTT_FSB_16

VTT_FSB_15

VTT_FSB_14

VTT_FSB_13

VTT_FSB_12

VTT_FSB_11

VTT_FSB_10

VTT_FSB_9

VTT_FSB_8

VTT_FSB_7

VTT_FSB_6

VTT_FSB_5

VTT_FSB_4

VTT_FSB_3

VTT_FSB_2

VTT_FSB_1

VCC_SM_15

VCC_SM_14

VCC_SM_13

VCC_SM_12

VCC_SM_11

VCC_SM_10

VCC_SM_9

VCC_SM_8

T29

VCC_73

VCC_SM_7

BD21

T27

VCC_72

VCC_SM_6

BB39

T26

VCC_71

VCC_SM_5

BA41

T25

VCC_70

VCC_SM_4

AY40

T24

VCC_69

VCC_SM_3

AV44

7

T23

VCC_68

VCC_SM_2

AT45

T22

VCC_67

VCC_SM_1

AP44

T21

VCC_66

R29

VCC_65

R27

VCC_64

R26

VCC_63

VCC_EXP_38

AK4

R25

AJ25

VCC_62

VCC_EXP_37

AK3

AK2

AJ23

VCC_61

VCC_60

VCC_EXP_36

VCC_EXP_35

AJ2

AJ21

VCC_59

VCC_EXP_34

AJ1

AJ19

VCC_58

VCC_EXP_33

Y15

AJ17

AJ16

VCC_57

VCC_EXP_32

Y14

W15

AG29

VCC_56

VCC_55

VCC_EXP_31

VCC_EXP_30

U15

AG26

VCC_54

VCC_EXP_29

U14

AG24

VCC_53

VCC_EXP_28

AK9

6

INT VRM Disable : Stuff R1078, Empty R1077

INT VRM Enable : Stuff R1077, Empty R1078

AG22

AG20

AG17

AG16

AF29

AF27

AF26

AF25

AF24

AF23

AF22

AF21

AF20

AF19

AF17

AF16

VCC_52

VCC_51

VCC_50

VCC_49

VCC_48

VCC_47

VCC_46

VCC_45

VCC_44

VCC_43

VCC_42

VCC_41

VCC_40

VCC_39

VCC_38

VCC_37

EAGLELAKE

EAGLELAKE

VCC_EXP_27

VCC_EXP_26

VCC_EXP_25

VCC_EXP_24

VCC_EXP_23

VCC_EXP_22

VCC_EXP_21

VCC_EXP_20

VCC_EXP_19

VCC_EXP_18

VCC_EXP_17

VCC_EXP_16

VCC_EXP_15

VCC_EXP_14

VCC_EXP_13

VCC_EXP_12

AJ9

AJ8

AJ7

AK8

AK7

AK6

AK13

AK12

AJ6

AJ14

AJ13

AJ12

AJ11

AK11

AK10

AJ10

AE29

VCC_36

VCC_EXP_11

AG15

AE27

VCC_35

VCC_EXP_10

AF15

AE25

VCC_34

VCC_EXP_9

AF14

AE23

VCC_33

VCC_EXP_8

AE15

AE21

VCC_32

VCC_EXP_7

AE14

AE19

VCC_31

VCC_EXP_6

AD15

AE17

VCC_30

VCC_EXP_5

AD14

AE16

VCC_29

VCC_EXP_4

AC15

AD29

VCC_28

VCC_EXP_3

AB14

AD26

AA15

5

AD24

VCC_27

VCC_26

VCC_EXP_2

VCC_EXP_1

AA14

VCC1.5V

AD22

AD20

VCC_25

VCC1.125V_CORE

R107 0R

R107 0R

R108 X

R108 X

AD17

AD16

AC29

AC27

AC25

AC23

VCC_24

VCC_23

VCC_22

VCC_21

VCC_20

VCC_19

VCCA_DAC1

VCCA_DAC2

VCCA_EXP

VCCDQ_CRT

VCCDPLL_EXP

B19

A17

B20

B12

D19

U33

AC21

VCC_18

VCC_17

VCCD_HPLL

AC19

VCC_16

VCC_SMCLK1

AK32

AC17

VCC_15

VCC_SMCLK2

AL31

AC16

VCC_14

VCC_SMCLK3

AL32

0402

0402

0402

0402

AB30

VCC_13

VCC_SMCLK4

AM31

AB29

VCC_12

AB26

VCC_11

VCCCML_DDR

AM30

AB24

VCC_10

AB22

VCC_9

4

AB20

AA30

VCC_8

VCC_7

VCC_CL84

VCC_CL85

Y29

W31

C24 X

C24 X

0805

0805

X_4.7UF

AA29

AA27

AA25

AA23

VCC_6

VCC_5

VCC_4

VCC_CL83

VCC_CL81

VCC_CL82

Y30

Y33

AJ15

AK14

AA21

AA19

VCC_3

VCC_2

VCC_1

VCC_CL78

VCC_CL79

VCC_CL80

Y32

AM29

B16

VCC_CL76

VCC_CL77

AM24

AM25

AM26

AG2

B22

VCCA_HPLL

VCCAPLL_EXP

VCCAVRM_EXP

VCC_CL73

VCC_CL74

VCC_CL75

AM21

AM22

A21

D20

C20

VCCA_MPLL

VCCA_DPLLA

VCC_CL71

VCC_CL72

AM17

AM20

VCC3

VCCA_DPLLB

AR2

E19

VCC3_3

VCC_HDA

VCC_CL1

VCC_CL2

VCC_CL3

VCC_CL4

VCC_CL5

VCC_CL6

VCC_CL7

VCC_CL8

VCC_CL9

VCC_CL10

VCC_CL11

VCC_CL12

VCC_CL13

VCC_CL14

VCC_CL15

VCC_CL16

VCC_CL17

VCC_CL18

VCC_CL19

VCC_CL20

VCC_CL21

VCC_CL22

VCC_CL23

VCC_CL24

VCC_CL25

VCC_CL26

VCC_CL27

VCC_CL28

VCC_CL29

VCC_CL30

VCC_CL31

VCC_CL32

VCC_CL33

VCC_CL34

VCC_CL35

VCC_CL36

VCC_CL37

VCC_CL38

VCC_CL39

VCC_CL40

VCC_CL41

VCC_CL42

VCC_CL43

VCC_CL44

VCC_CL45

VCC_CL46

VCC_CL47

VCC_CL48

VCC_CL49

VCC_CL50

VCC_CL51

VCC_CL52

VCC_CL53

VCC_CL54

VCC_CL55

VCC_CL56

VCC_CL57

VCC_CL58

VCC_CL59

VCC_CL60

VCC_CL61

VCC_CL62

VCC_CL63

VCC_CL64

VCC_CL65

VCC_CL66

VCC_CL67

VCC_CL68

VCC_CL69

VCC_CL70

3

VCCA_GPLLD 9

VCCA_HPLL 9

VCCA_MPLL 9

VCCA_DPLLA

VCCA_DPLLB

VCC_AZA

C270 X

C270 X

0603

VCC1.125V_CL

AA31

AB31

AC31

AD31

AE31

AF31

AG30

AG31

AJ30

AJ31

AK16

AK17

AK19

AK20

AK21

AK22

AK23

AK24

AK25

AK26

AK27

AK29

AK30

AL1

AL10

AL11

AL12

AL14

AL15

AL16

AL17

AL19

AL2

AL20

AL21

AL22

AL23

AL24

AL25

AL26

AL27

AL29

AL4

AL5

AL6

AL7

AL8

AL9

AM2

AM3

AM4

AP1

AP2

Y31

AJ27

AJ29

AA32

AA33

AB32

AB33

AD32

AD33

AE32

AE33

AF32

AJ32

AK31

AL30

AM15

AM16

0603

C208 0.1UF_X7RC208 0.1UF_X7R

2

10UH_100MA

VCCA_DPLLA

VCCA_DPLLB

VCC_SMCLK

VCCD_HPL

C269 X

C269 X

0603

0603

VCCCML_DDR

C271 X

C271 X

0603

0603

stuff 1000PF

VCC_AZA

H_VCCPLL3

VCC_CRT

DAC FILTER

PLACE THE CAPS AT ENDS OF POWER CORRIDOR

VCC5

U3

U3

1

VIN

VOUT

3

EN

X_FAN2502S33X

X_FAN2502S33X

CM9 XCM9 X

VCCA_DAC

R113 1R

R113 1R

C272 XC272 X

C273 XC273 X

VCC_EXP

R116 1R

R116 1R

10UH_100MA

L1

L1

CE1 220UF_6.3V

CE1 220UF_6.3V

+ D5P2.5

+ D5P2.5

C25 0.1UF_X7RC25 0.1UF_X7R

L2

L2

CE2 220UF_6.3V

CE2 220UF_6.3V

C26 0.1UF_X7RC26 0.1UF_X7R

0.16UH_500MA

0.16UH_500MA

L3

L3

C27 22UF

C27 22UF

C268 XC268 X

stuff 1000PF

R110 X

R110 X

0402

0402

R112 1R

R112 1R

0402

0402

5

4

BYP

2

GND

0402

0402

R11440.2R_1%

R11440.2R_1%

0402

0402

10UH_100MA

10UH_100MA

+ D5P2.5

+ D5P2.5

R111 0R

R111 0R

FB_600R_100MHZ_200MA

FB_600R_100MHZ_200MA

L5

L5

FB_600R_100MHZ_200MA

FB_600R_100MHZ_200MA

CM8CM8

C28XC28

X

0402

0402

CM10CM10

1

L_0805

L_0805

L_0805

L_0805

VCC1.8V_DDR2

L_0805

L_0805

0805

0805

R109 0RR109 0R

0.1UH_100MA

0.1UH_100MA

L4

L4

L6

L6

L_0805

L_0805

0402

0402

FB_0603

FB_0603

FB_0603

FB_0603

L7 X

L7 X

C29 X

C29 X

0805

0805

L8

L8

FB_600R_100MHZ_200MA

FB_600R_100MHZ_200MA

R115 39.2_1%

R115 39.2_1%

0402

0402

VCC1.125V_CORE

VCC1.125V_CORE

VCC1.125V_CL

VCC1.125V_CL

VCC1.5V

FB_0603

FB_0603

VCC3

FB_0603

FB_0603

C302.2UF

C302.2UF

C312.2UF

C312.2UF

C322.2UF

C322.2UF

0603

0603

0603

0603

0603

A A

8

VCC1.125V_CORE

7

0603

6

5

VCCCML_DDR

VCC_SMCLK

VCCD_HPL

VCC_CRT

VCC_EXP

VCCA_DAC

VCC_SMCLK

VCCA_GPLL 9

4

C95 X

C95 X

0603

0603

TITLE:

TITLE:

TITLE:

G43NT

G43NT

G43NT

GCMH 2/4

GCMH 2/4

GCMH 2/4

Document Number :

Document Number :

Document Number :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

3

A3

<Doc>

<Doc>

<Doc>

James Xiong

James Xiong

James Xiong

Date: PAGE:

Date: PAGE:

Date: PAGE:

Saturday, April 05, 2008

Saturday, April 05, 2008

Saturday, April 05, 2008

2

REV:

REV:

REV:

746

746

746

1

0.2

0.2

0.2

of

of

of

1

M_MAA_A[0..14]10,12

A A

M_WE_A-10,12

M_CAS_A-10,12

M_RAS_A-10,12

M_SBS_A[0..2]10,12

M_SCS_A-[0..3]10,12

B B

M_SCKE_A[0..3]10,12

M_ODT_A[0..3]10,12

C C

D D

E E

F F

DDR_CLK_P0_A10

DDR_CLK_N0_A10

DDR_CLK_P1_A10

DDR_CLK_N1_A10

DDR_CLK_P2_A10

DDR_CLK_N2_A10

DDR_CLK_P3_A10

DDR_CLK_N3_A10

DDR_CLK_P4_A10

DDR_CLK_N4_A10

DDR_CLK_P5_A10

DDR_CLK_N5_A10

1

M_MAA_A0

M_MAA_A1

M_MAA_A2

M_MAA_A3

M_MAA_A4

M_MAA_A5

M_MAA_A6

M_MAA_A7

M_MAA_A8

M_MAA_A9

M_MAA_A10

M_MAA_A11

M_MAA_A12

M_MAA_A13

M_MAA_A14

M_SBS_A0

M_SBS_A1

M_SBS_A2

M_SCS_A-0

M_SCS_A-1

M_SCS_A-2

M_SCS_A-3

M_SCKE_A0

M_SCKE_A1

M_SCKE_A2

M_SCKE_A3

M_ODT_A0

M_ODT_A1

M_ODT_A2

M_ODT_A3

T95T95

T96T96

T97T97

T112T112

0402

0402

R118

R118

0R

0R

BC41

BC35

BB32

BC32

BD32

BB31

AY31

BA31

BD31

BD30

AW43

BC30

BB30

AM42

BD28

AW42

AU42

AV42

AV45

AY44

BC28

AU43

AR40

AU44

AM43

BB27

BD27

BA27

AY26

AR42

AM44

AR44

AL40

AY37

BA37

AW29

AY29

AU37

AV37

AU33

AT33

AT30

AR30

AW38

AY38

AR43

BB40

AT44

BC24

AR6

2

U2D

U2D

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_WEB

DDR_A_CASB

DDR_A_RASB

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CSB_0

DDR_A_CSB_1

DDR_A_CSB_2

DDR_A_CSB_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CKB_0

DDR_A_CK_1

DDR_A_CKB_1

DDR_A_CK_2

DDR_A_CKB_2

DDR_A_CK_3

DDR_A_CKB_3

DDR_A_CK_4

DDR_A_CKB_4

DDR_A_CK_5

DDR_A_CKB_5

DDR3_A_CSB1

DDR3_A_MA0

DDR3_A_WEB

DDR3_DRAMRSTB

DDR3_DRAM_PWROK

EAGLELAKE

EAGLELAKE

2

4 of 6

4 of 6

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DM_0

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQS_1

DDR_A_DQSB_1

DDR_A_DM_1

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_DM_2

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A

DDR_A

DDR_A_DQ_31

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_DM_4

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQS_5

DDR_A_DQSB_5

DDR_A_DM_5

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQS_6

DDR_A_DQSB_6

DDR_A_DM_6

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQS_7

DDR_A_DQSB_7

DDR_A_DM_7

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

BC5

BD4

BC3

BC2

BD3

BD7

BB7

BB2

BA3

BE6

BD6

BB9

BC9

BD9

BB8

AY8

BD11

BB11

BC7

BE8

BD10

AY11

BD15

BB15

BD14

BB14

BC14

BC16

BB16

BC11

BE12

BA15

BD16

AR22

AT22

AV22

AW21

AY22

AV24

AY24

AU21

AT21

AR24

AU24

AH43

AH42

AK42

AL41

AK43

AG42

AG44

AL42

AK44

AH44

AG41

AD43

AE42

AE45

AF43

AF42

AC44

AC42

AF40

AF44

AD44

AC41

Y43

Y42

AA45

AB43

AA42

W42

W41

AB42

AB44

Y44

Y40

T44

T43

T42

V42

U45

R40

P44

V44

V43

R41

R44

3

M_DQS_A0

M_DQS_A-0

M_DQM_A0

M_DQS_A1

M_DQS_A-1

M_DQM_A1

M_DQS_A2

M_DQS_A-2

M_DQM_A2

M_DQS_A3

M_DQS_A-3

M_DQM_A3

M_DQS_A4

M_DQS_A-4

M_DQM_A4

M_DQS_A5

M_DQS_A-5

M_DQM_A5

M_DQS_A6

M_DQS_A-6

M_DQM_A6

M_DQS_A7

M_DQS_A-7

M_DQM_A7

3

M_D_A0

M_D_A1

M_D_A2

M_D_A3

M_D_A4

M_D_A5

M_D_A6

M_D_A7

M_D_A8

M_D_A9

M_D_A10

M_D_A11

M_D_A12

M_D_A13

M_D_A14

M_D_A15

M_D_A16

M_D_A17

M_D_A18

M_D_A19

M_D_A20

M_D_A21

M_D_A22

M_D_A23

M_D_A24

M_D_A25

M_D_A26

M_D_A27

M_D_A28

M_D_A29

M_D_A30

M_D_A31

M_D_A32

M_D_A33

M_D_A34

M_D_A35

M_D_A36

M_D_A37

M_D_A38

M_D_A39

M_D_A40

M_D_A41

M_D_A42

M_D_A43

M_D_A44

M_D_A45

M_D_A46

M_D_A47

M_D_A48

M_D_A49

M_D_A50

M_D_A51

M_D_A52

M_D_A53

M_D_A54

M_D_A55

M_D_A56

M_D_A57

M_D_A58

M_D_A59

M_D_A60

M_D_A61

M_D_A62

M_D_A63

4

M_DQS_A[0..7] 10

M_DQS_A-[0..7] 10

M_DQM_A[0..7] 10

M_D_A[0..63] 10

VCC1.8V_DDR2

VCC1.8V_DDR2

R120 80R6_1%

R120 80R6_1%

R123 80R6_1%

R123 80R6_1%

4

M_MAA_B[0..14]11,12

M_SBS_B[0..2]11,12

M_SCS_B-[0..3]11,12

M_SCKE_B[0..3]11,12

M_ODT_B[0..3]11,12

DDR_CLK_P0_B11

DDR_CLK_N0_B11

DDR_CLK_P1_B11

DDR_CLK_N1_B11

DDR_CLK_P2_B11

DDR_CLK_N2_B11

DDR_CLK_P3_B11

DDR_CLK_N3_B11

DDR_CLK_P4_B11

DDR_CLK_N4_B11

DDR_CLK_P5_B11

DDR_CLK_N5_B11

Place close to MCH

R117 1K_1%R117 1K_1%

0402

0402

CB8CB8

0402

0402

CB9CB9

M_CAS_B-11,12

M_RAS_B-11,12

R119

R119

1K_1%

1K_1%

5

U2E

BD24

BB23

BB24

BD23

BB22

BD22

BC22

BC20

BB20

BD20

BC26

BD19

BB19

BE38

BA19

BD36

BC37

BD35

BD26

BB26

BD18

BB35

BD39

BB37

BD40

BC18

AY20

BE17

BB18

BD37

BC39

BB38

BD42

AV40

AY33

AW33

AV31

AW31

AW35

AY35

AT31

AU31

AP31

AP30

AW37

AV35

AK33

AJ33

AN30

AN29

BB44

AY42

BA43

BC43

BC44

U2E

DDR_B_MA_0

DDR_B_MA_1

DDR_B_MA_2

DDR_B_MA_3

DDR_B_MA_4

DDR_B_MA_5

DDR_B_MA_6

DDR_B_MA_7

DDR_B_MA_8

DDR_B_MA_9

DDR_B_MA_10

DDR_B_MA_11

DDR_B_MA_12

DDR_B_MA_13

DDR_B_MA_14

DDR_B_WEB

DDR_B_CASB

DDR_B_RASB

DDR_B_BS_0

DDR_B_BS_1

DDR_B_BS_2

DDR_B_CSB_0

DDR_B_CSB_1

DDR_B_CSB_2

DDR_B_CSB_3

DDR_B_CKE_0

DDR_B_CKE_1

DDR_B_CKE_2

DDR_B_CKE_3

DDR_B_ODT_0

DDR_B_ODT_1

DDR_B_ODT_2

DDR_B_ODT_3

DDR3_B_ODT3

DDR_B_CK_0

DDR_B_CKB_0

DDR_B_CK_1

DDR_B_CKB_1

DDR_B_CK_2

DDR_B_CKB_2

DDR_B_CK_3

DDR_B_CKB_3

DDR_B_CK_4

DDR_B_CKB_4

DDR_B_CK_5

DDR_B_CKB_5

RSVD25

RSVD26

RSVD27

RSVD28

DDR_VREF

DDR_RPD

DDR_RPU

DDR_SPD

DDR_SPU

EAGLELAKE

EAGLELAKE

M_MAA_B0

M_MAA_B1

M_MAA_B2

M_MAA_B3

M_MAA_B4

M_MAA_B5

M_MAA_B6

M_MAA_B7

M_MAA_B8

M_MAA_B9

M_MAA_B10

M_MAA_B11

M_MAA_B12

M_MAA_B13

M_MAA_B14

M_WE_B-11,12

M_SBS_B0

M_SBS_B1

M_SBS_B2

M_SCS_B-0

M_SCS_B-1

M_SCS_B-2

M_SCS_B-3

M_SCKE_B0

M_SCKE_B1

M_SCKE_B2

M_SCKE_B3

M_ODT_B0

M_ODT_B1

M_ODT_B2

M_ODT_B3

T80T80

T81T81

T82T82

T84T84

T83T83

CB7CB7

DDR_VREF

DDR_RPD

DDR_RPU

DDR_SPD

DDR_SPU

0402

0402

0402

0402

80R6_1%

80R6_1%

249R_1%

249R_1%

R121

R121

R122

R122

5

6

5 of 6

5 of 6

6

DDR_B_DQS_0

DDR_B_DQSB_0

DDR_B_DM_0

DDR_B_DQ_0

DDR_B_DQ_1

DDR_B_DQ_2

DDR_B_DQ_3

DDR_B_DQ_4

DDR_B_DQ_5

DDR_B_DQ_6

DDR_B_DQ_7

DDR_B_DQS_1

DDR_B_DQSB_1

DDR_B_DM_1

DDR_B_DQ_8

DDR_B_DQ_9

DDR_B_DQ_10

DDR_B_DQ_11

DDR_B_DQ_12

DDR_B_DQ_13

DDR_B_DQ_14

DDR_B_DQ_15

DDR_B_DQS_2

DDR_B_DQSB_2

DDR_B_DM_2

DDR_B_DQ_16

DDR_B_DQ_17

DDR_B_DQ_18

DDR_B_DQ_19

DDR_B_DQ_20

DDR_B_DQ_21

DDR_B_DQ_22

DDR_B_DQ_23

DDR_B_DQS_3

DDR_B_DQSB_3

DDR_B_DM_3

DDR_B_DQ_24

DDR_B_DQ_25

DDR_B_DQ_26

DDR_B_DQ_27

DDR_B_DQ_28

DDR_B_DQ_29

DDR_B_DQ_30

DDR_B

DDR_B

DDR_B_DQ_31

DDR_B_DQS_4

DDR_B_DQSB_4

DDR_B_DM_4

DDR_B_DQ_32

DDR_B_DQ_33

DDR_B_DQ_34

DDR_B_DQ_35

DDR_B_DQ_36

DDR_B_DQ_37

DDR_B_DQ_38

DDR_B_DQ_39

DDR_B_DQS_5

DDR_B_DQSB_5

DDR_B_DM_5

DDR_B_DQ_40

DDR_B_DQ_41

DDR_B_DQ_42

DDR_B_DQ_43

DDR_B_DQ_44

DDR_B_DQ_45

DDR_B_DQ_46

DDR_B_DQ_47

DDR_B_DQS_6

DDR_B_DQSB_6

DDR_B_DM_6

DDR_B_DQ_48

DDR_B_DQ_49

DDR_B_DQ_50

DDR_B_DQ_51

DDR_B_DQ_52

DDR_B_DQ_53

DDR_B_DQ_54

DDR_B_DQ_55

DDR_B_DQS_7

DDR_B_DQSB_7

DDR_B_DM_7

DDR_B_DQ_56

DDR_B_DQ_57

DDR_B_DQ_58

DDR_B_DQ_59

DDR_B_DQ_60

DDR_B_DQ_61

DDR_B_DQ_62

DDR_B_DQ_63

M_DQS_B0

AW8

M_DQS_B-0

AW9

M_DQM_B0

AY6

AV7