USDIGITAL LS7084, LS7083 Datasheet

LS7083 & LS7084

1

2

3

45

6

7

8

+5V

Gnd

A in B in

X4/X1 input

DnClk out

UpClk out

LS7083

1

2

3

45

6

7

8

+5V

Gnd

A in B in

Up/Dn out

Clock out

LS7084

Rbias

4 +5V

5 ChannelB3 ChannelA1 Ground

4 +5V

5 ChannelB3 ChannelA1 Ground

74193

type

Cascadable

Up/Dn

Counter

5

4

4516

type

Up/Dn

Counter

15

10

Top View

Rbias

+5V

X4/X1 input

+5V

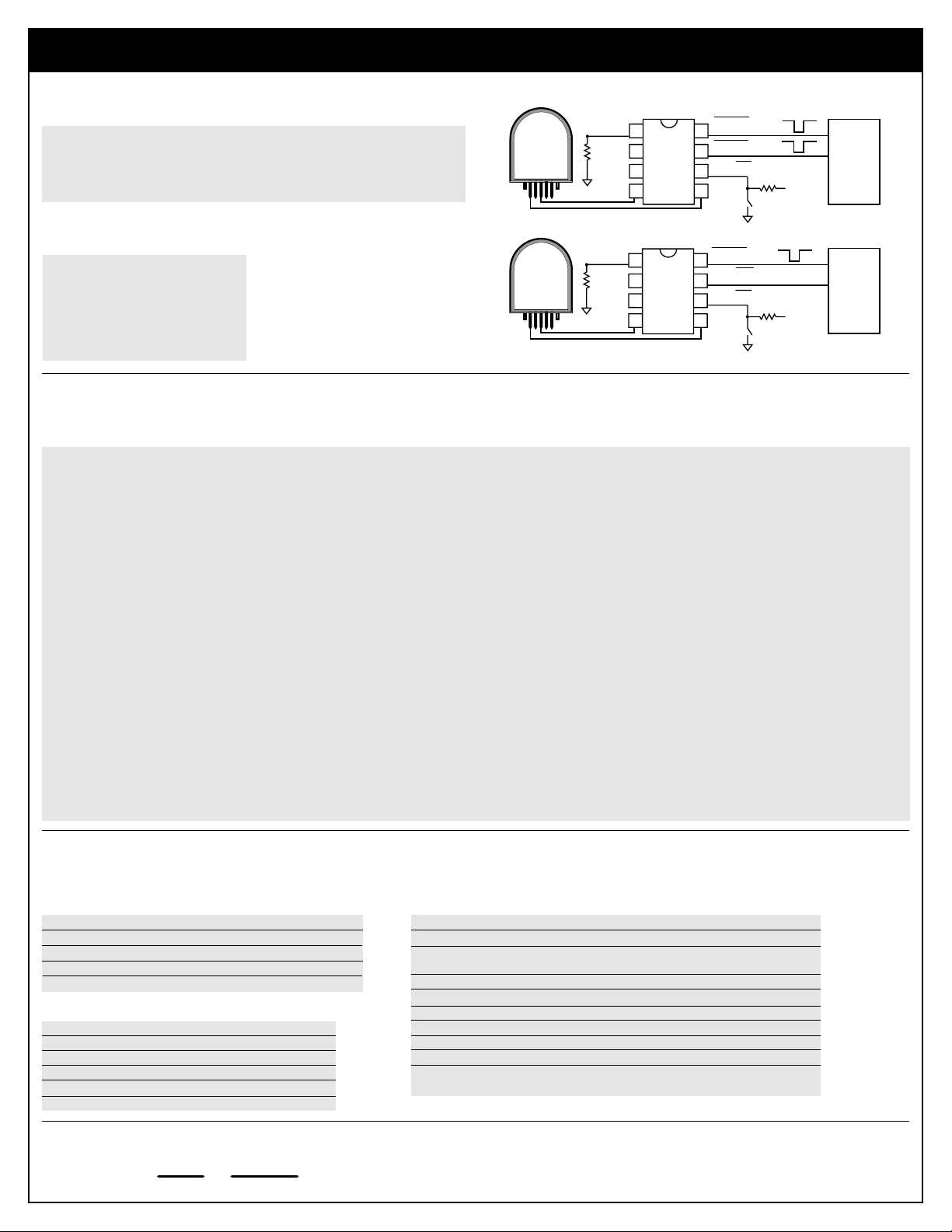

Example Circuit

5 Ch. B

4 +5v

3 Ch. A21 Gnd

Optical Encoder

5 Ch. B

4 +5v

3 Ch. A21 Gnd

Optical Encoder

Cascadable

Encoder to Counter Interface Chips

Description:

These devices allow incremental shaft encoders to drive standard up/down

counters. Connect the encoder quadrature outputs to the A and B inputs. The

LS7083 outputs can connect directly to the up and down clock inputs of

counters such as 74193 or 40193. The LS7084 outputs can connect directly

to the Clock and Up/Dn inputs of counters such as 4516 or 74169.

Features:

Ø X4 or X1 resolution multiplication.

Ø TTL and CMOS compatible.

Ø Low power (micro-amps).

Ø 8-pin DIP or SOIC package.

Ø No external clocks required.

Ø Drive standard Up/Dn counters.

Ø Monolithic CMOS.

Pin Descriptions:

Pin 1 (Rbias input):

Connect a resistor to ground for the internal current mirror which feeds the two internal 2-axis one-shots. The resistor value sets the width of the low-true

clock outputs. A typical value is 300kOhm which sets the output pulse width to 1µs and max A,B frequency to 250kHz. Minimum resistor value is 50kOhm.

See the Rbias table (next page) for other values. The chip's current consumption is inversely proportional to this resistance. Typical current is 40µA @ 100KOhm

and 6µA @ 2MegOhm.

Pins 4 & 5 (A & B inputs):

Connect to the A and B quadrature outputs of the encoder. Both inputs have debounce filters. Minimum pulse width is set at 160ns. There is no maximum limit.

Input current is less than 1 µA. The A and B inputs can be swapped to reverse the direction of the external counters.

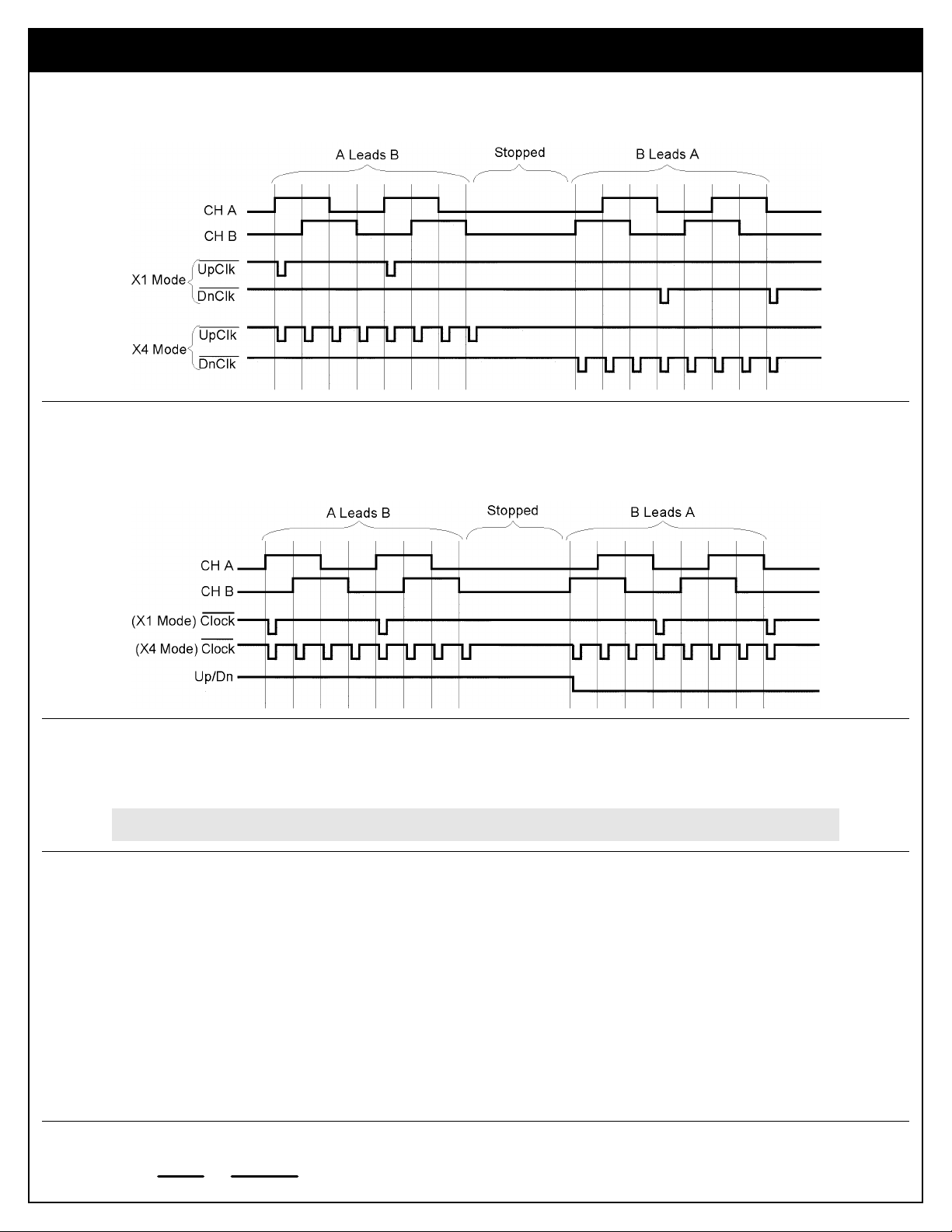

Pin 6 (X4/X1 input):

A high level applied to this input selects X4 mode, a low level selects the X1 mode. Input current is less than 1µA. Do not let this input float. In X4 mode, a clock

pulse is generated for every transition of the A or B input. Note that there are 4 transitions per cycle of quadrature code. Thus, a 500 cycle/rev encoder will

produce 2000 counts/rev in X4 mode. In X1 mode, only one clock is generated per quadrature cycle.

LS7083 pin 7 (Down Clock output):

Normally high, low-true. The low level pulse width is set by pin 1. Down counts are enabled only when B leads A (clockwise rotation). In X4 mode, one pulse

is generated for each A/B state change. In X1 mode, one pulse is generated per quadrature cycle.

LS7084 pin 7 (Up/Down Clock output):

This output steers the external counter up or down. High = Up (A leads B), Low = Down (B leads A).

LS7083 pin 8 (Up Clock output):

Normally high, low-true. The low level pulse width is set by pin 1. Up counts are enabled only when A leads B (counter-clockwise rotation). In X4 mode, one

pulse is generated for each A/B state change. In X1 mode, one pulse is generated per quadrature cycle.

LS7084 pin 8 (Clock output):

Normally high, low-true. The low level pulse width is set by pin 1. In X4 mode, one pulse is generated for each A/B state change regardless of count direction.

In X1 mode, one pulse is generated per quadrature cycle. The external counter should count on the rising (high-going) edge of this output.

Surface Mount Package:

The 8-pin SOIC package has the same pin-out as the DIP version shown above.

Absolute Maximum Ratings: DC Electrical Characteristics for 5V Operation:

Parameter Min. Max. Units

Operating temperature 0 70 °C

Storage temperature -65 150 °C

Voltage at any input -.5 VCC+.5 Volts

Supply voltage (Vcc) 10.5 Volts

RBias Resistor Value vs. Timing:

Resistor Pulse Width Max A,B Freq

100kOhm 400ns 625kHz

300kOhm 1µs 250kHz

500kOhm 1.4µs 180kHz

2MegOhm 5µs 50kHz

10MegOhm 25µs 10kHz

US

Digital

Corporation

TM

phone: 360.260.2468 l sales: 800.736.0194 l fax: 360.260.2469

email: sales@usdigital.com l website: www.usdigital.com

11100 ne 34th circle l vancouver, washington 98682 USA

Parameter Min. Max. Units Notes

Supply voltage 4.75 10.5 Volts

Supply current - 8.0 µ A A,B = 0Hz

Rbias=300k

X4/X1 logic low 1.4 Volts

X4/X1 logic high 3.7 Volts

A,B logic low 0.6 Volts

A,B logic high 3.3 Volts

Low output current 1.75 mA Vout = 0.4V

High output current 1.0 mA Vout = 4.75V

Ø Use standard CMOS levels when operating with higher supply

voltages up to 10.5 Volts.

page

1

LS7083 & LS7084

LS7083 Timing Diagram:

LS7084 Timing Diagram:

Encoder to Counter Interface Chips

Timing Diagram Notes:

The maximum time delay from the A or B input to the leading edge of any output is 235ns. The pulse width of all clock outputs is set

by the value of the Rbias resistor as shown in the table above. Typical rise or fall time of each logic output 10 to 20ns.

Ordering Information:

US

Digital

Corporation

DIP Package (300mil):

LS7083-DIP o r

LS7084-DIP

SOIC Package:

LS7083-SOIC o r

LS7084-SOIC

TM

phone: 360.260.2468 l sales: 800.736.0194 l fax: 360.260.2469

email: sales@usdigital.com l website: www.usdigital.com

11100 ne 34th circle l vancouver, washington 98682 USA

Price:

$3.05 / 1

$2.45 / 25

$1.95 / 100

$1.65 / 500

$1.40 / 1K

Technical Data, Rev. 07.24.01, July 2001

All information subject to change without notice.

page

2

Loading...

Loading...