uPI uP6306NSM8, uP6306USM8 Schematic [ru]

uP6306

A

300KHz, 5A/3A, 26V High-Efficiency

Synchronous-Rectified Buck Converter

General Description

The uP6306 is a high efficiency synchronous-rectified buck

converter with internal power switches. Fixed 300kHz PWM

operation allows possible smallest output ripple and

external component size. With high conversion efficiency

and small package, the uP6306 is ideally suitable for

applications where PCB area is especially concerned.

Designed with slope-compensated current mode control,

the uP6306 features fast transient response to step load

change. The converter supports PSM mode operation at

light load condition, thus yields very high efficiency over a

wide range of load current.

With integrated high voltage MOSFET, the uP6306 is

capable of delivering 5A/3A output current over a wide input

range from 5V to 26V. The output voltage is adjustable

from 0.8V to 80% of VIN by a voltage divider.

Other features include internal soft-start, chip enable, undervoltage, over-temperature and over-current protections. The

uP6306 is available in a thermally enhanced PSOP-8

package.

pplications

Distributed Power Systems

Networking Systems

FPGA/DSP/ASIC Power Supplies

Green Electronics/ Appliances

Notebook Computers

Features

5V to 26V Input Voltage Range

Integrated Power MOSFET

60m

ΩΩ

Ω(5A)/120m

ΩΩ

ΩΩ

Ω(3A) PMOSFET for High Side

ΩΩ

Switch

30m

ΩΩ

Ω(5A)/60m

ΩΩ

ΩΩ

Ω(3A) NMOSFET for Low Side

ΩΩ

Switch

Automatic PWM/PSM Operation for High

Efficiency

Up to 96% Conversion Efficiency

Accurate Reference: 0.8V (

Current Mode PWM Operation

Fixed Frequency: 300kHz

Internal Soft-Start

Under-Voltage Protection

Over-Temperature and Over-Current Protection

PSOP-8 Package

RoHS Compliant and Halogen Free

+/- +/-

+/- 1.5%)

+/- +/-

Ordering Information

rebmuNredrOepyTegakcaPkrameR

XX-8MSN6036PuL8-POSPSTEFSOMOKIN

XX-8MSU6036PuL8-POSPSTEFSOMQIBU

tnerruCnoitarepO:XXedoC

A5=50;A3=30:.g.e

Note: uPI products are compatible with the current IPC/

JEDEC J-STD-020 requirement. They are halogen-free,

RoHS compliant and 100% matte tin (Sn) plating that are

suitable for use in SnPb or Pb-free soldering processes.

1

VDD5

AGND

FB

Rev. F01, File Name: uP6306-DS-F0100

2

3

AGND

45

PSOP-8

8

LX

7

6

PGNDVIN

LX

VCC5

COMP/EN

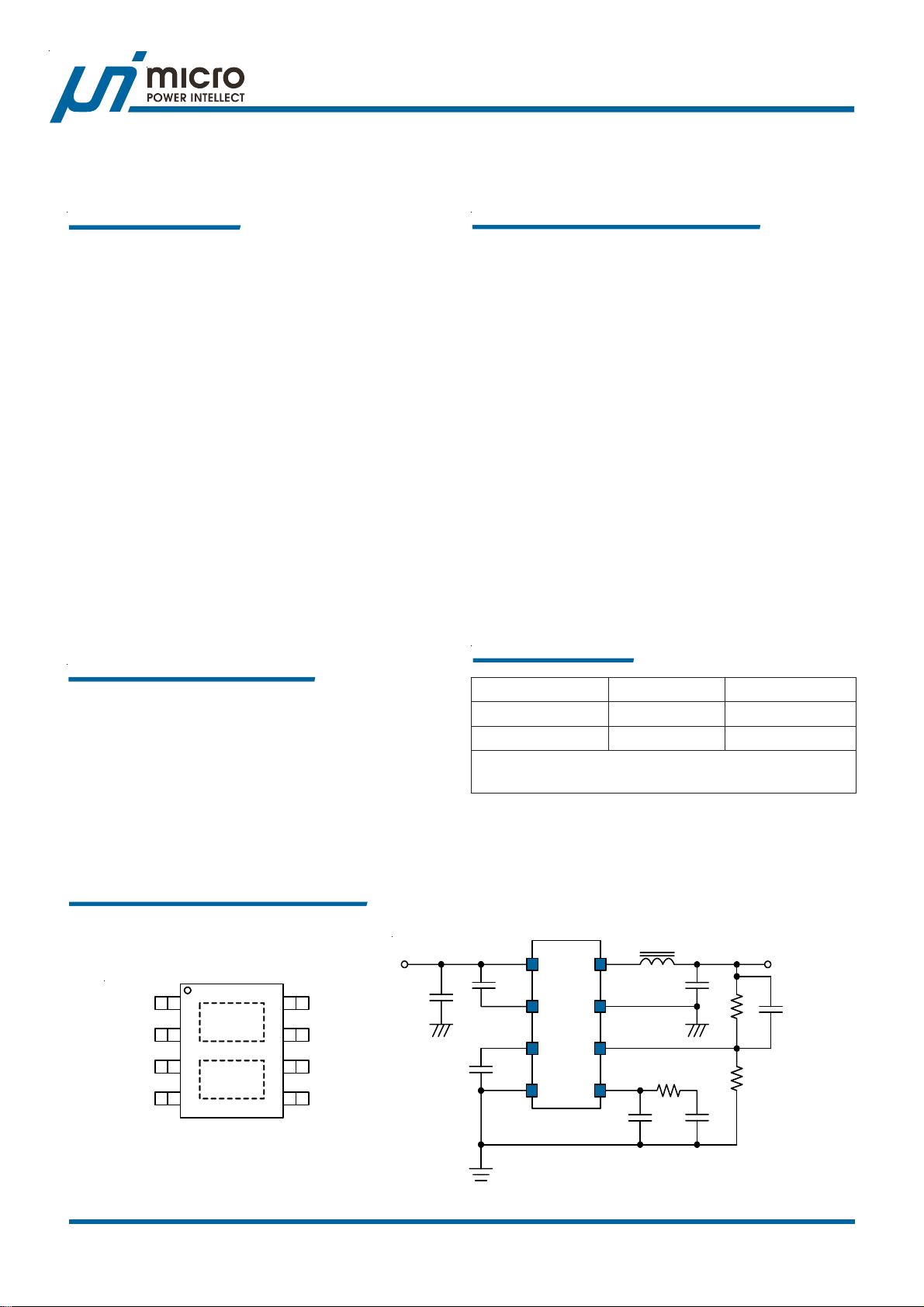

Pin Configuration & Typical Application Circuit

R2

R1

V

OUT

Optional

V

IN

VIN

VDD5

VCC5

AGND

uP6306

LX

PGND

FB

COMP/EN

1uPI Semiconductor Corp., http://www.upi-semi.com

.oNniPemaNniPnoitcnuFniP

n

uP6306

Functional Pin Descriptio

1NIV

25DDV

3DNGA

4BF

5NE/PMOC

65CCV

7XL

8DNGP

.tupnIylppuSrewoP ehtsrewopdnaegatlovtuptuoehtottnerrucseilppustahtegatlovtupnI

.srotalugerraenilV5lanretni

.revirDTEFSOMreppUrofylppuSsaiB morfroticapaccimarecFu7.4muminimatcennoC

.egatlovsaibehtssapybotnipNIVotnipsiht

.dnuorGlangiS .nipsihtotstnenopmoclangisllamsllafonruterehttcennoC

.egatloVkcabdeeF morfredividrotsiserA.reifilpmarorreehtottupnignitrevniehtsinipsihT

.egatlovnoitalugerehttesotdesusiDNGAottuptuoeht

.tuptuOreifilpmArorrE tupnignitrevni-nonehtdna)AE(reifilpmarorreehtfotuptuoehtsisihT

-egatlovehtetasnepmocotnipBFehthtiwnoitanibmocninipsihtesU.srotarapmocMWPehtfo

.retrevnocehtfopoolkcabdeeflortnoc

.ylppuSsaiB rewolehtroftnerrucgniylppus,rotalugerraenilV5lanretnifotuptuoehtsinipsihT

nipsihtmrofroticapaccimarecFu7.4muminimatcennoC.yrtiucriclanretnidnarevirdTEFSOM

.egatlovsaibehtssapybotnipDNGAot

.tuptuOsehctiwSlanretnI .rotcudnituptuoehtotnipsihttcennoC

.nruteRdnuorGrewoPniaM .nruterroticapactupnidnatuptuoehtottcennoC

.tuptuOsehctiwSlanretnI elpitlumhtiwBCPotderedlosllewebdluohsdapdesopxeehT

IdaPdesopxE

yllacirtceleebdluohsnipsihT.ecnamrofreplamrehtlamitporofenalpdnuorgotsaiv

.BCPnonipXLotdetcennoc

IIdaPdesopxE

.dnuorGlangiS .nipsihtotstnenopmoclangisllamsllafonruterehttcennoC

FB

AGND

COMP/EN

V

REF

(0.8V)

SS

Soft

Start

Error

Amplifier

0.8V

0.5V

VCC5

POR

Enable

Internal

Regulator

OCP

Comparator

PWM

Comparator

Oscillator

PWM

VDD5

300mV

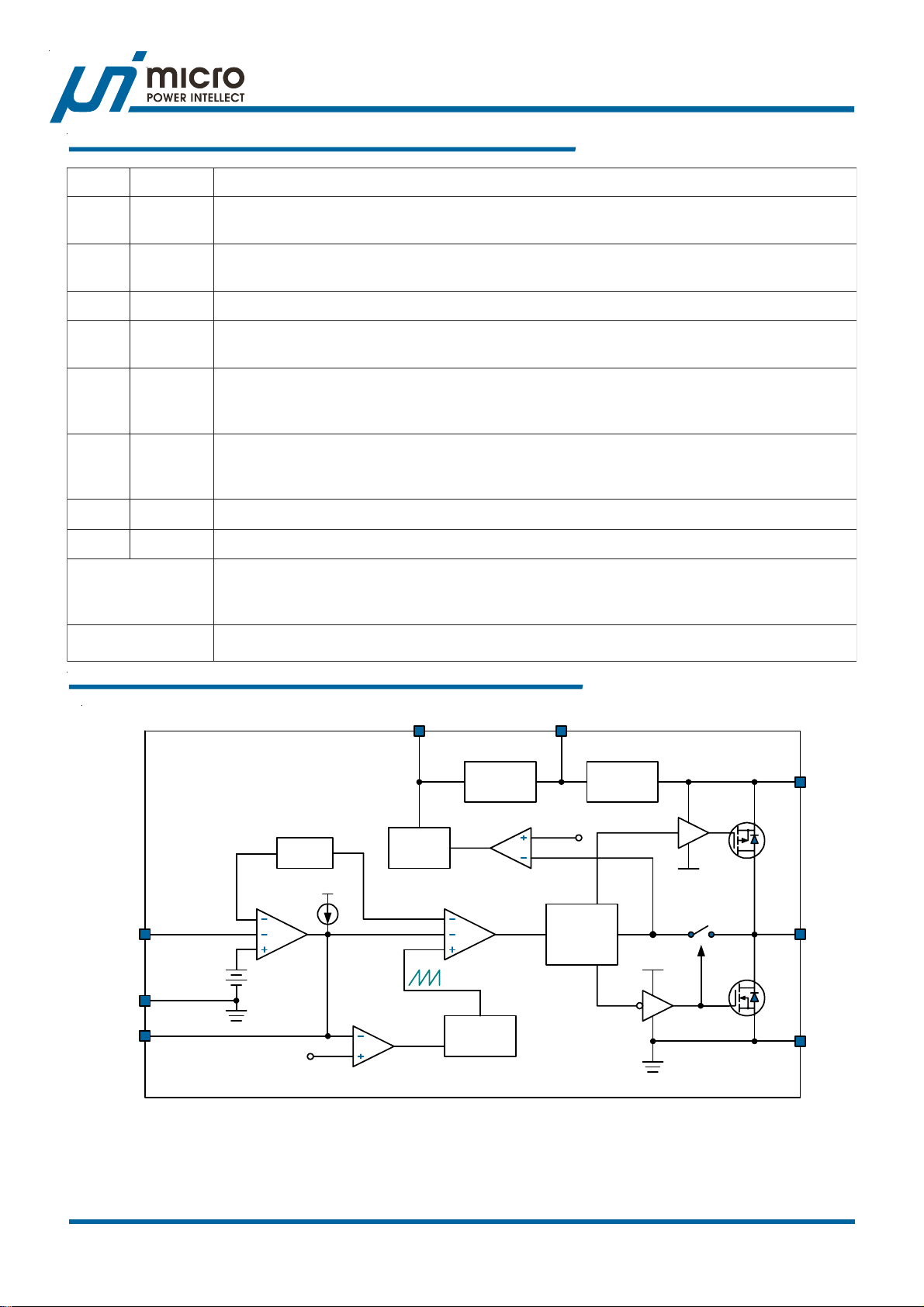

Functional Block Diagram

Internal

Regulator

VDD5

Gate

Control

Logic

VCC5

VIN

LX

PGND

Rev. F01, File Name: uP6306-DS-F0100

2uPI Semiconductor Corp., http://www.upi-semi.com

uP6306

Functional Description

The uP6306 is a high efficiency synchronous-rectified buck

converter with internal power switches. Fixed 300kHz PWM

operation allows possible smallest output ripple and

external component size. With high conversion efficiency

and small package, the uP6306 is ideally suitable for

applications where PCB area is especially concerned.

Designed with current mode control, the uP6306 features

fast transient response to step load change. The converter

supports PSM mode operation at light load condition, thus

yields very high efficiency over a wide range of load current.

With integrated high voltage MOSFET, the uP6306 is

capable of delivering 5A/3A output current over a wide input

range from 5V to 26V. The output voltage is adjustable

from 0.8V to 80% of VIN by a voltage divider. Other features

include internal soft-start, chip enable, under-voltage, overtemperature and over-current protections. The uP6306 is

available in a thermally enhanced PSOP-8 package.

Input Supply Voltage, V

IN

The uP6306 operates with single supply input at VIN pin.

The VIN pin supplies current for output voltages and provides

current for internal control circuit and gate drivers. The

supply voltage range is from 5V to 26V. The uP6306 draws

pulsed current from VIN pin with sharp edges each time

the upper switch turns on, resulting in voltage ripples and

spikes at supply input. A minimum 22uF ceramic capacitor

with shortest PCB trace is highly recommended for

bypassing the supply input.

The uP6306 integrates two 5V linear regulators. A linear

regulator regulates (VIN - VDD5) voltage at 5V for upper

gate driver. The other linear regulator regulates (VCC5 GND) voltage at 5V for internal control circuit and lower

gate driver. Both VDD5 and VCC5 need a minimum 4.7uF

capacitor for locally bypassing the output voltage of linear

regulators.

The VCC5 voltage is continuously monitored for power on

reset (POR) to insure its voltage is high enough for normal

operation. The POR threshold level is typically 4.2V at

VCC5 rising. For fixed VIN = 5V operation, connect VCC5

pin to VIN pin directly. Otherwise the dropout voltage of the

linear regulator will make VCC5 < 4.2V and below its POR

threshold voltage.

connected together to LX pin.

Bias Voltage

Internal linear regulators generate voltages for driving the

power MOSFET and biasing the internal control circuits.

The VDD5 voltage is regulated to -5V with respect to VIN

fro driving the PMOSFET. The gate of PMOSFET is driven

to VDD5 when turned on. A minimum 4.7uF ceramic

capacitor is required from VDD5 to VIN pin for locally

bypassing the VDD5 voltage.

The VCC5 is regulated to +5V with respective to AGND pin

for driving the NMOSFET and biasing the internal control

circuits. The gate of NMOSFET is driven to VCC5 when

turned on. A minimum 4.7uF ceramic capacitor is required

from VCC5 to AGND pin for locally bypassing the VCC5

voltage.

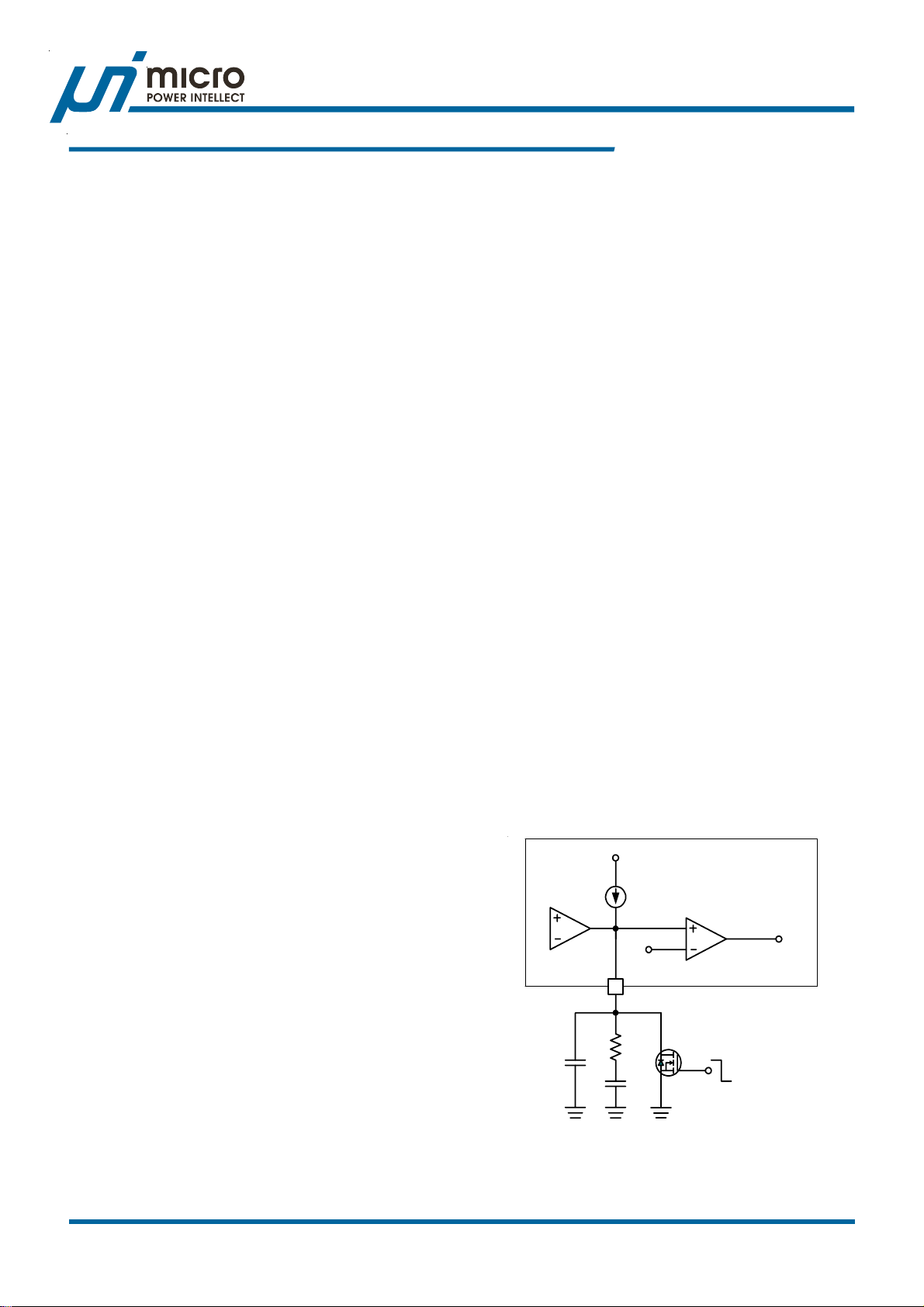

Chip Enable

The COMP/EN is a multifunctional pin: control loop

compensation and chip enable as shown in Figure 1. An

Enable Comparator monitors the COMP/EN pin for chip

enable. A signal level transistor is adequate to pull this pin

down to ground and shut down the uP6306. An 80uA current

source charges the external compensation network with

0.8V ceiling when this pin is released. If the voltage at

COMP/EN pin exceeds 0.5V, the uP6306 initiates its

softstart cycle.

The 80uA current source keeps charging the COMP/EN

pin to its ceiling until the feedback loop boosts the COMP/

EN pin higher than 0.8V according to the feedback signal.

The current source is cut off when V

is higher than

COMP

0.8V during normal operation.

Error

Amp.

0.8V

80uA

5

COMP/EN

0.5V

uP6306

Enable

Enable

Comp.

Power Switches

The uP6306 integrates internal power switches to form a

synchronous buck converter: 60mΩ(5A)/120mΩ(3A)

PMOSFET for upper switches 30mΩ(5A)/60mΩ(3A)

NMOSFET for lower switch. The source of PMOSFET is

connected to VIN pin, the source of NMOSFET is

connected to PGND pin. The drains of both MOSFETs are

Rev. F01, File Name: uP6306-DS-F0100

Disable

Enable

Figure 1. Chip Enable Function

3uPI Semiconductor Corp., http://www.upi-semi.com

uP6306

Functional Description

SoftStart

A built-in Soft Start is used to prevent surge current from

power supply input during turn on (referring to the Functional

Block Diagram). The error amplifier is a three-input device.

Reference voltage V

or the internal soft start voltage SS

REF

whichever is smaller dominates the behavior of the noninverting inputs of the error amplifier. SS internally ramps

up to 0.8V in 2ms after the softstart cycle is initiated. The

ramp is created digitally, so there will be 100 small discrete

steps. Accordingly, the output voltage will follow the SS

signal and ramp up smoothly to its target level.

The SS signal keeps ramping up after it exceeds the internal

0.8V reference voltage. However, the internal 0.8V reference

voltage takes over the behavior of error amplifier after SS >

V

. When the SS signal climb to its ceiling voltage (4V),

REF

the uP6306 claims the end of softstart cycle and enable

the under voltage protection of the output voltage.

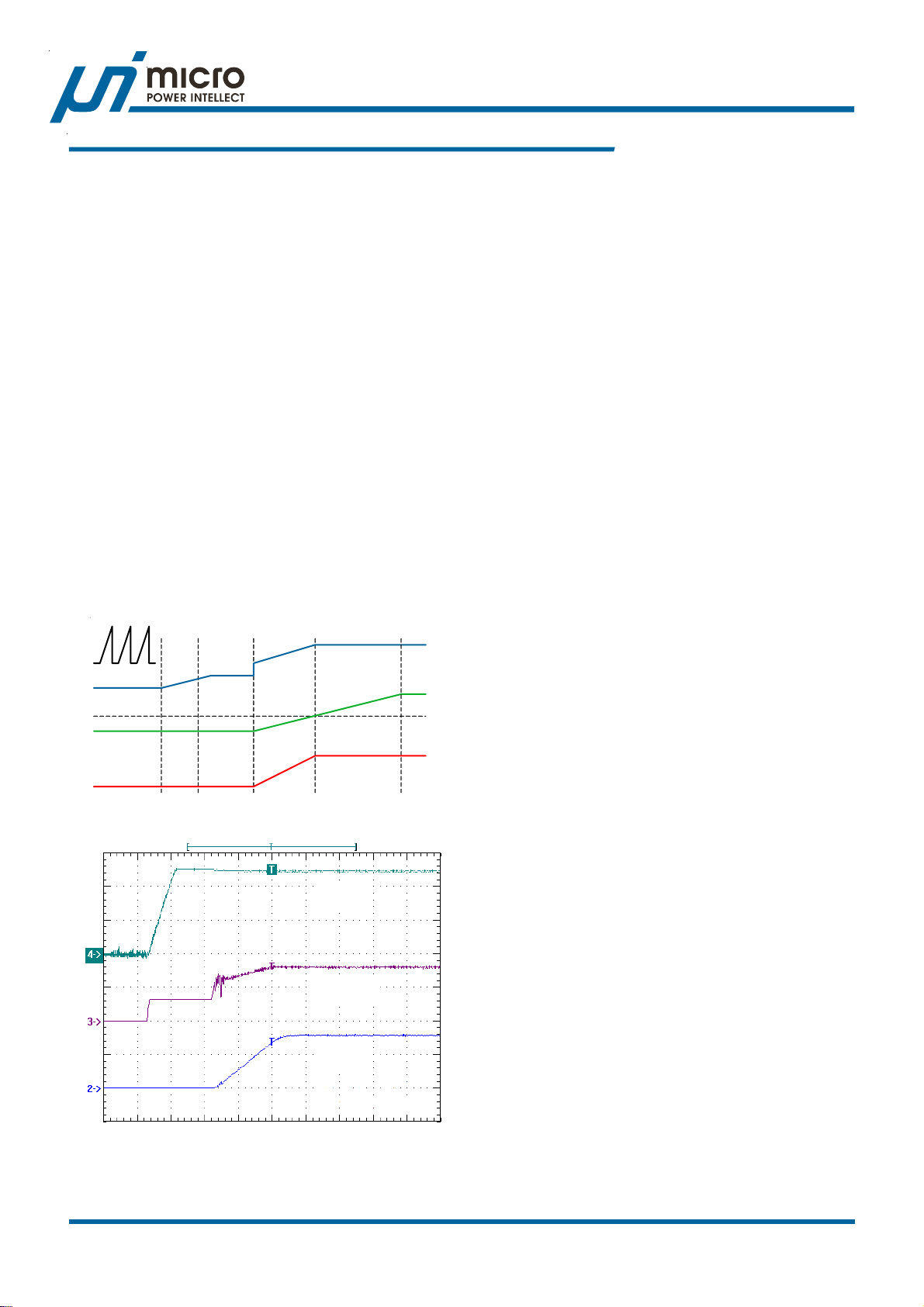

Figure 2 shows a typical start up interval for uP6306 where

the COMP/EN pin has been released from a grounded

(system shutdown) state.

Ramp

COMP/EN

V

REF

T1 T2 T3 T4 T5

SS

V

OUT

The internal 80uA current source starts to charge the

compensation network after the COMP/EN pin is released

from grounded at T1. The COMP/EN exceeds 0.5V and

enables the uP6306 at T2. The COMP/EN continues

ramping up and stays at 0.8V before the SS starts ramping

up at T3. The uP6306 initializes itself such as current limit

level setting (see the relative section) during the time interval

between T2 and T3. The output voltage follows the internal

SS and ramps up to its final level during T3 and T4. At T4,

the reference voltage V

error amplifier as the internal SS crosses V

takes over the behavior of the

REF

. The internal

REF

SS keeps ramping up and stay at 4V at T5, where the

uP6306 asserts the end of softstart cycle.

PWM Operation

The uP6306 adopts slope-compensated, current mode

PWM control capable of achieving 80% duty cycle. During

normal operation, the uP6306 operates at PWM mode to

regulate output voltage by transferring the power to the

output voltage cycle by cycle at a constant 300kHz

frequency. The uP6306 turns on the upper switch at each

rising edge of the internal oscillator allowing the inductor

current to ramp up linearly. The switch remains on until

either the current-limit is tripped or the PWM comparator

turns off the switch for regulating output voltage. The upper

switch current is sensed, slope compensated and

compared with the error amplifier output COMP/EN to

determine the adequate duty cycle. The FB pin senses

output feedback voltage from an external resistive divider.

When the load current increases, it causes a slight

decrease in the feedback voltage relative to the 0.8V

reference, which in turn, causes the error amplifier output

voltage to increase until the average inductor current

matches the new load current.

Time 1ms/Div

Figure 2. Softstart Behavior.

Rev. F01, File Name: uP6306-DS-F0100

5VCC

(2V/Div)

COMP/EN

(1V/Div)

V

OUT

(2V/Div)

A Pseudo Diode Emulator monitors inductor current by

sensing voltage drop across the lower switch when it turns

on. The lower switch turns off to emulate the free wheel

diode used in traditional asynchronous buck converter and

allows the converter entering discontinuous conduction

mode when inductor current crosses zero. This reduces

conduction loss and increase power conversion efficiency

at light condition.

PSM Operation

A finite minimum on-time for both upper and lower switches

is implemented for normal operation. Consequently, the

converter will enter pulse-skipping mode (PSM) during

extreme light load condition or when modulation index (V

OUT

VIN) is extreme low. The equivalent switching frequency is

reduced. This could reduce switching loss and further

/

4uPI Semiconductor Corp., http://www.upi-semi.com

Loading...

Loading...