UNISEM US1060CT, US1060CP, US1060CM Datasheet

US1260

3-1

Rev. 1.9

3/22/99

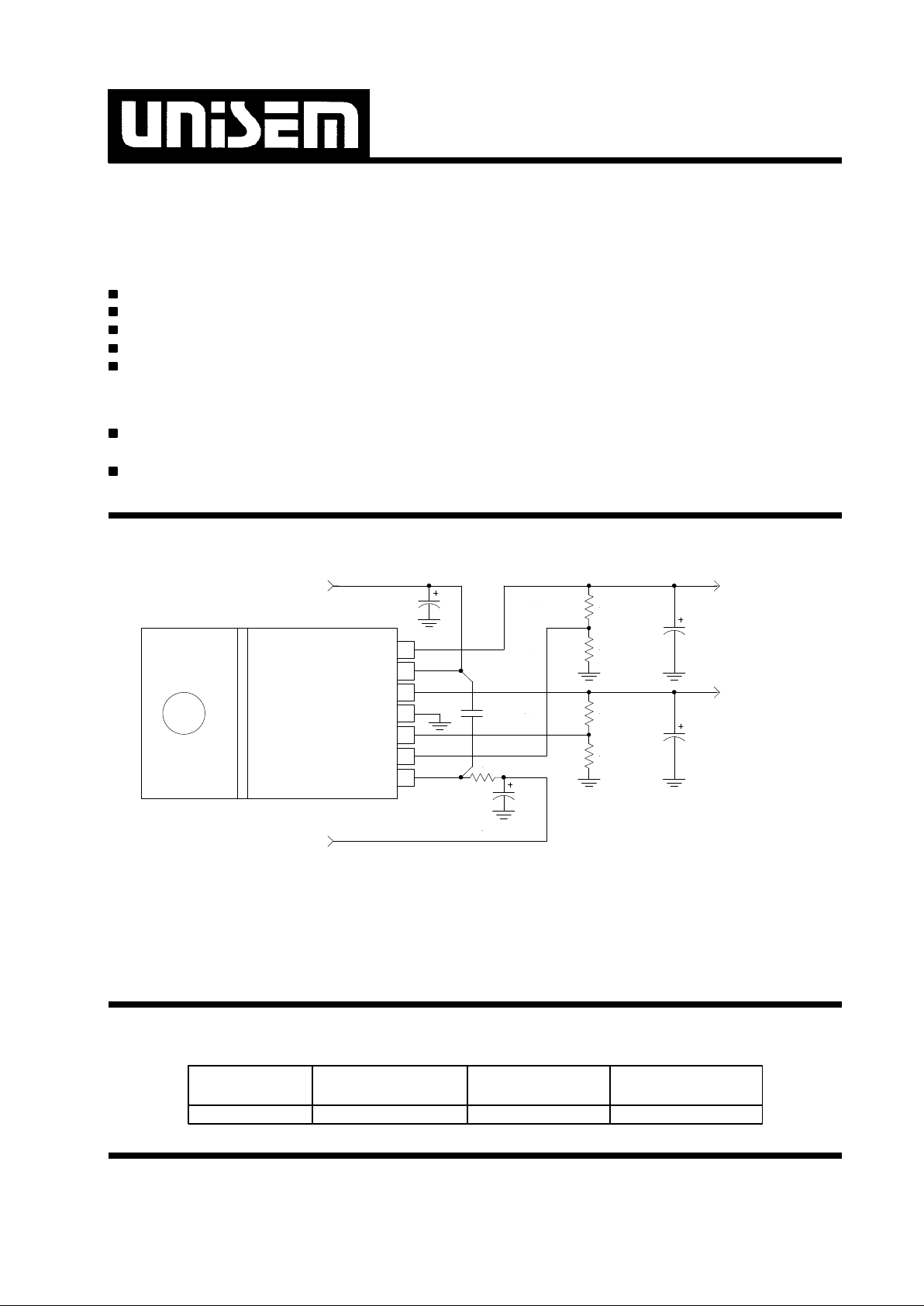

TYPICAL APPLICATIONTYPICAL APPLICATION

FEATURESFEATURES

Guaranteed <1.3V Dropout at 6A (output #2)

Guaranteed <0.6V Dropout at 1A (output #1)

Fast Transient Response

1% Voltage Reference Initial Accuracy

Built in Thermal Shutdown

APPLICATIONSAPPLICATIONS

Providing a single package solution for GTL+

and High Speed Bus Termination

Dual supply P55C applications

DESCRIPTIONDESCRIPTION

The US1260 product using a proprietary process combines a dual low drop out adjustable output regulators in

a single package with one output having a minimum of

6A and the other one having a 1A output current capability. This product is specifically designed to provide well

regulated supplies for low voltage ICs such as 3.3V to

1.5V and 2.5V supplies for the GTL+ termination

and the new clock for Pentium II applications.Other

applications include low cost dual supply for proces-

sors such as Intel P55C where 2.8V and 3.3 V are

needed for the Core and the I/O supplies from the

5V input.

DUAL 6A AND 1A LOW DROPOUT

POSITIVE ADJUSTABLE REGULATOR

Notes: P55C is trade mark of Intel Corp.

Typical application of US1260 in the Pentium ΙΙ design with the 1.5V output providing for GTL+ termination

while 2.5V supplies the clock chip.

Notes: Pentium ΙΙ is trade mark of Intel Corp.

3.3V

2.5V / 1A

1.5V / 6A

C1 R1

R2

R3

R4

C2

C3

US1260

1260app7-1.0

Vctrl

Vfb1

Vfb2

Gnd

Vout2

Vin

Vout1

1

2

3

4

5

6

7

5V

C5

U1

C4

R5

PACKAGE ORDER INFORMATIONPACKAGE ORDER INFORMATION

Tj (°C) 7 PIN PLASTIC 7 PIN PLASTIC 7 PIN PLASTIC

TO220(T) TO263(M) POWER FLEX(P)

0 TO 150 US1260CT US1260CM US1260CP

US1260

3-2

Rev. 1.9

3/22/99

Unless otherwise specified ,these specifications apply over ,Cin=1 uF,Cout=10uF,and Tj=0 to 150°C.Typical

values refer to Tj=25°C. Ifl=6A for output #1,and Ifl=1A for output #2. Vfb=Vo for both outputs.Vctrl=Vin=3.3V.

PARAMETER SYM TEST CONDITION MIN TYP MAX UNITS

Vctrl Input Voltage 3.0 V

Reference Voltage Vref Io=10mA,Tj=25°C 1.188 1.200 1.212 V

Io=10mA 1.176 1.200 1.224

Line Regulation Io=10mA,Vout+1.3V<Vin=Vctrl<7V 0.2 %

Load Regulation (note 1) 10mA<Io<Ifl 0.4 %

Dropout Voltage (output #2) Io=4A, Vctrl=4.75V , Vin=3.3V 1.0 V

Io=3A, Vctrl=4.75V , Vin=3.3V 0.7 V

(Note 2) Io=2A, Vctrl=4.75V , Vin=3.3V 0.35 0.5

Dropout Voltage (output #1) Io=1A, Vctrl=4.75V , Vin=3.3V 0.4 0.6 V

(Note 2) Io=1A, Vctrl=Vin=4.75V 1.3

Current Limit (output #2) ICL2 dVo=100mV 6.1 A

Current Limit (output #1) ICL1 dVo=100mV 1.1 A

Thermal Regulation 30 mS pulse,Io=Ifl 0.01 0.02 %/W

Ripple Rejection f=120HZ ,Co=25uF Tantalum

Io=0.5*Ifl 70 dB

Feedback Pin Input Current Ifb Io=10mA 0.02 uA

Temperature Stability Io=10mA 0.5 %

Long Term Stability Ta=125°C,1000 Hrs 0.3 1 %

RMS Output Noise Ta=25°C 10hz<f<10khz 0.003 %Vo

Minimum Load Current(Note 3) 5 mA

Note 3 : Minimum load current is defined as the minimum current required at the output in order for the output voltage to maintain regulation. Typically the resistor

dividers are selected such that it automatically maintains this current.

Note 1 : Low duty cycle pulse testing with Kelvin connections are required in order to maintain accurate data.

Note 2 : Drop-out voltage is defined as the minimum

differential voltage between Vin and Vout required to maintain regulation at Vout. It is measured when the output

voltage drops 1% below its nominal value.

ABSOLUTE MAXIMUM RATINGSABSOLUTE MAXIMUM RATINGS

Input Voltage (Vin) ............................................................. 7V

Power Dissipation ............................................ Internally Limited

Storage Temperature Range ................................ -65°C TO 150°C

Operating Junction Temperature Range ...................... 0°C TO 150°C

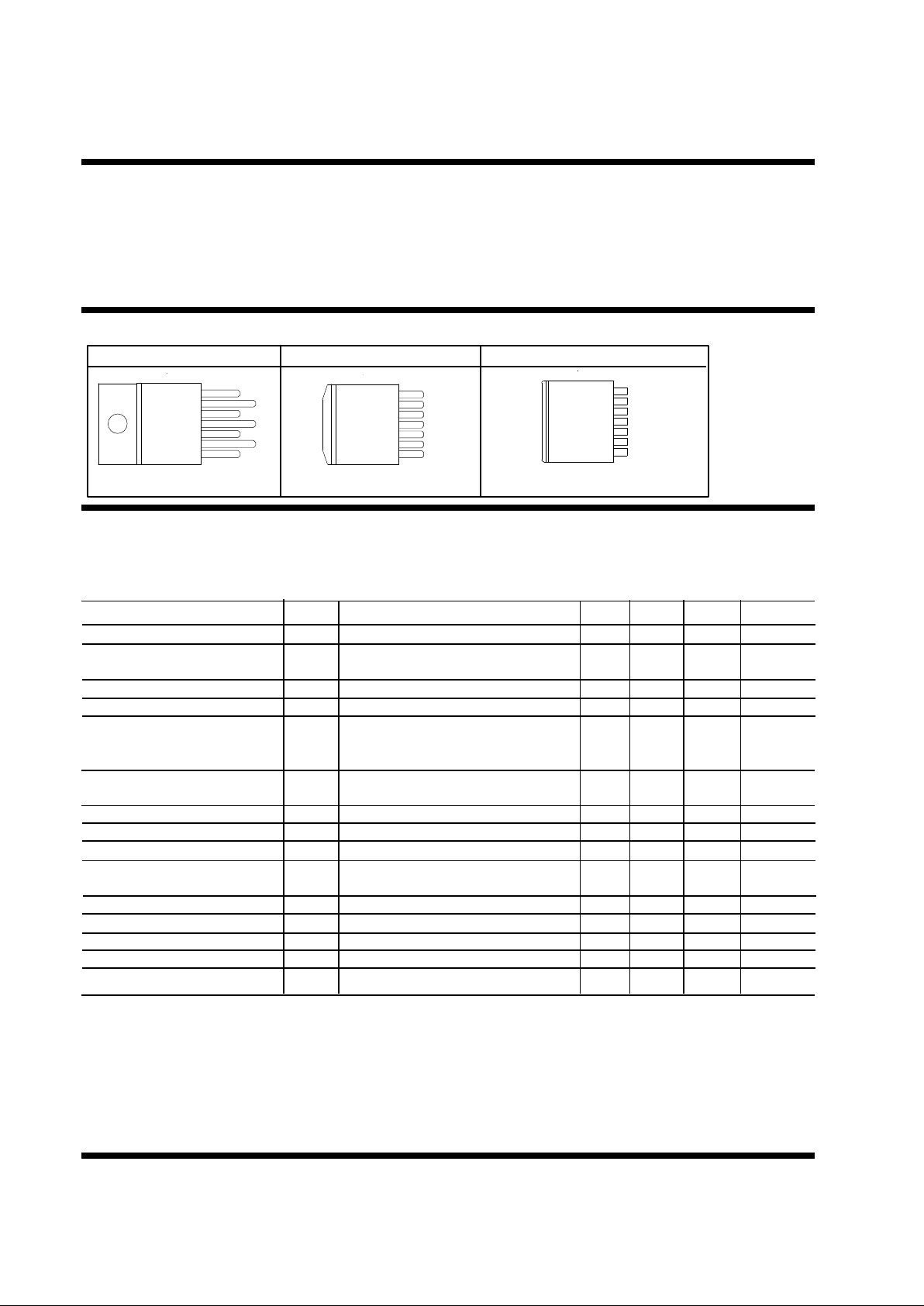

PACKAGE INFORMATIONPACKAGE INFORMATION

7 PIN PLASTIC TO220 7 PIN PLASTIC TO263 7 PIN POWER FLEX (P)

θJT =2.7°C/W θJA =60°C/W θJA =30°C/W for 1"sq pad θJA =30°C/W for 1"sq pad

ELECTRICAL SPECIFICATIONSELECTRICAL SPECIFICATIONS

FRONT VIEW

1

2

3

4

5

6

7

Vctrl

Vfb1

Vfb2

Gnd

Vout2

Vin

Vout1

FRONT VIEW

1

2

3

4

5

6

7

Vctrl

Vfb1

Vfb2

Gnd

Vout2

Vin

Vout1

M7

FRONT VIEW

1

2

3

4

5

6

7

Vctrl

Vfb1

Vfb2

Gnd

Vout2

Vin

Vout1

US1260

3-3

Rev. 1.9

3/22/99

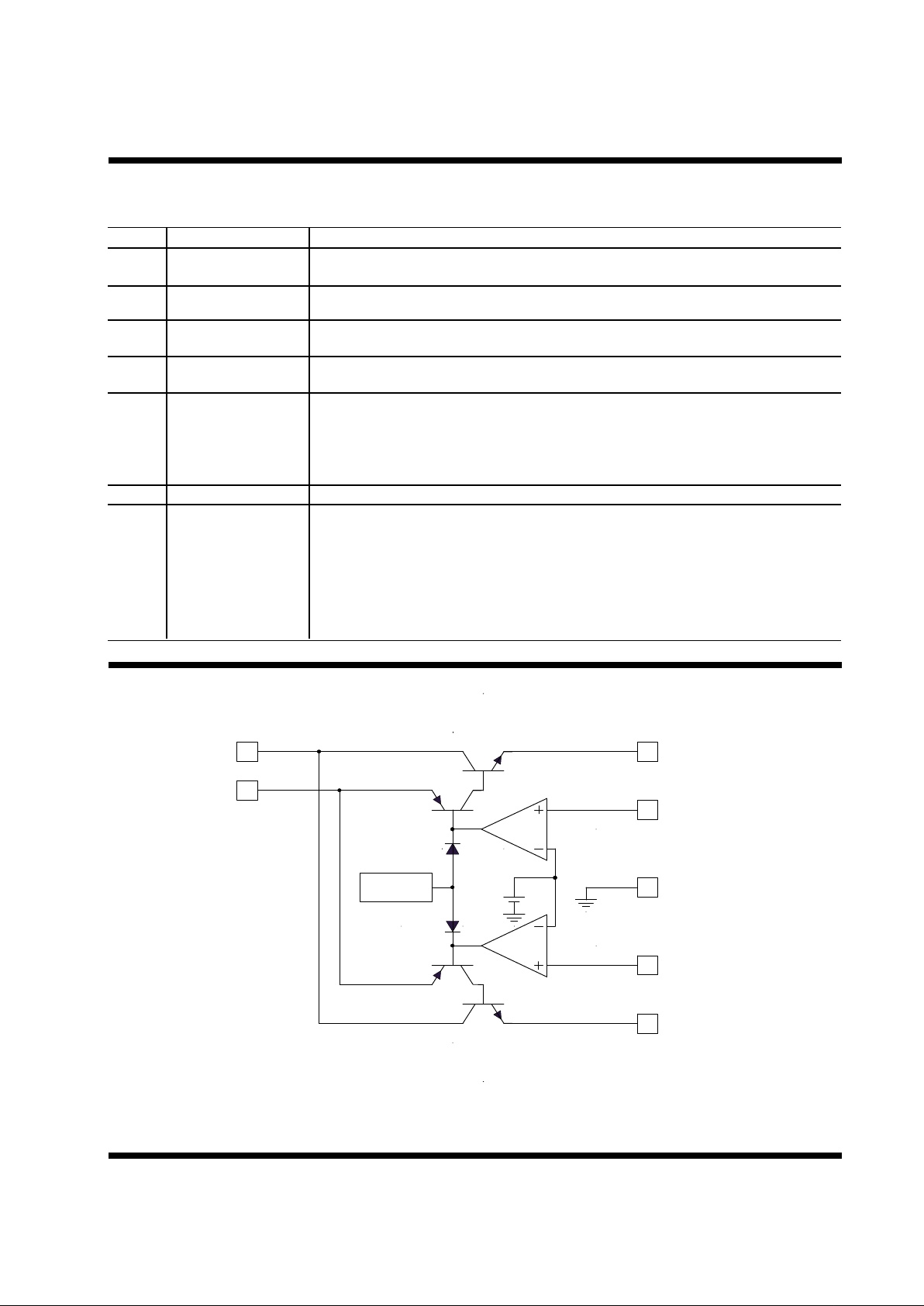

BLOCK DIAGRAMBLOCK DIAGRAM

Figure 1 - Simplified block diagram of the US1260

PIN DESCRIPTIONSPIN DESCRIPTIONS

PIN # PIN SYMBOL PIN DESCRIPTION

3 Vfb2 A resistor divider from this pin to the Vout #2 pin and ground sets the output

voltage. See application ckt for the divider setting for 1.5V output.

2 Vfb1 A resistor divider from this pin to Vout #1 pin and ground sets the output

voltage.See application ckt for the divider setting for 2.5V output.

5 Vout2 The output #2 (high current) of the regulator. A minimum of 100uF capacitor

must be connected from this pin to ground to insure stability.

7 Vout1 The output #1 (low current) of the regulator. A minimum of 100uF capacitor

must be connected from this pin to ground to insure stability.

6 Vin The power input pin of the regulator. Typically a large storage capacitor is

connected from this pin to ground to insure that the input voltage does not sag

below the minimum drop out voltage during the load transient response. This

pin must always be higher than both Vout pins by the amount of the dropout

voltage(see datasheet) in order for the device to regulate properly.

4 Gnd This pin is connected to GND. It is also the TAB of the package.

1 Vctrl The control input pin of the regulator. This pin via a 10Ω resistor is connected

to the 5V supply to provide the base current for the pass transistor of both

regulators. This allows the regulator to have very low dropout voltage

which allows one to generate a well regulated 2.5V supply from the 3.3V input.

A high frequency, 1 uF capacitor is connected between this pin and Vin pin to

insure stability.

Vctrl

Vin

Gnd

6

1

4

1260blk1-1.1

5 Vout2

7 Vout1

THERMAL

SHUTDOWN

1.20V

2 Vfb1

3 Vfb2

+

Loading...

Loading...