UMC UM3750M, UM3750 Datasheet

UN13750

Programmable

Encoder/Decoder

Single chip contains both Encoder and Decoder.

3V to 11 V operation.

On chip oscillator uses non-critical RC components.

Cross interference of

recetver

is virtually eliminated

by circuitry which requires 4 valid words to be received,

each within 64ms of the other.

General Description

The UM3750 Encoder/Decoder is a CMOS/LSI digital

code Transmitter-Receiver system. Working in the transmit (encoder) mode, the

UM3750 will sequentially encode

and transmit 12 bits of input. Each of the 12 bits may

be 1 or 0 to allow 4096 different codes.

In the receive (decoder) mode, the incoming signal is

compared to the local code

an error IS detected the system

In

a sequential manner

will

reset and beain its

Once

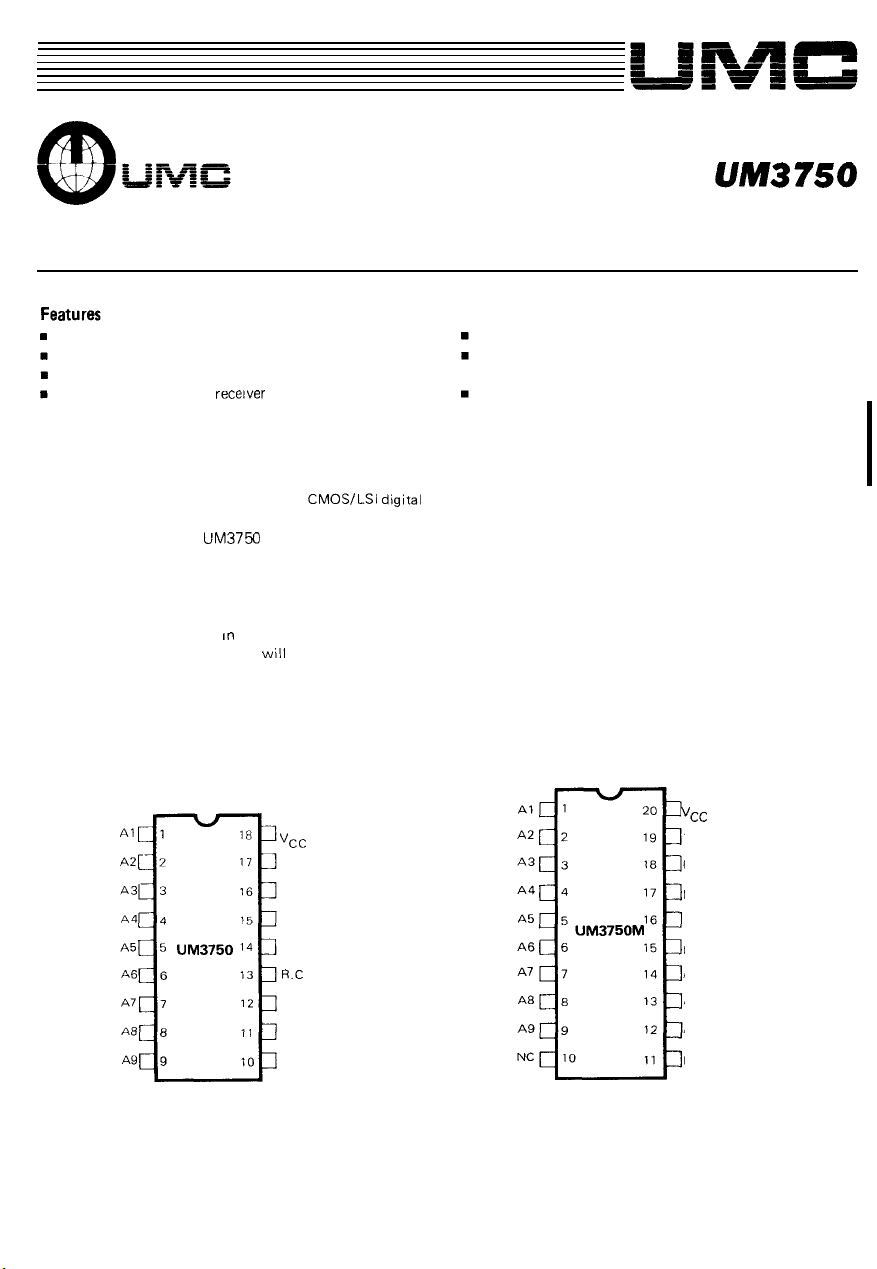

Pin Configurations

“cc

TX/RX OUTPUT

RECEIVER INPUT

MODE SELECT

“ss

R.C INPUT

A12

All

A10

Schmitt Trigger input provides excellent noise immunity.

Applications. alarm control system, security system

cordless telephone, remote control.

Interfaces with RF, ultrasonic, or infrared modulators

and demodulators

comparison on the next word.

correctly, a “valid” signal is generated. This signal

64ms counter and triggers a

If all 12 bits are

3-stage

counter. The

received

clears a

3-stage

counter counts the “valid” pluses and when 4 pulses have

been detected, the TX/RX output pin goes low. After the

TX/RX output pin goes low, the next “valid” must be

received within

128ms,

giving a one valid in 6 requirement

to keep the TX/RX output pin.

“cc

TX/RX OUTPUT

RECEIVER INPUT

MODE SELECT

“SS

R.C.

INPUT

A12

All

A10

NC

I

2-3

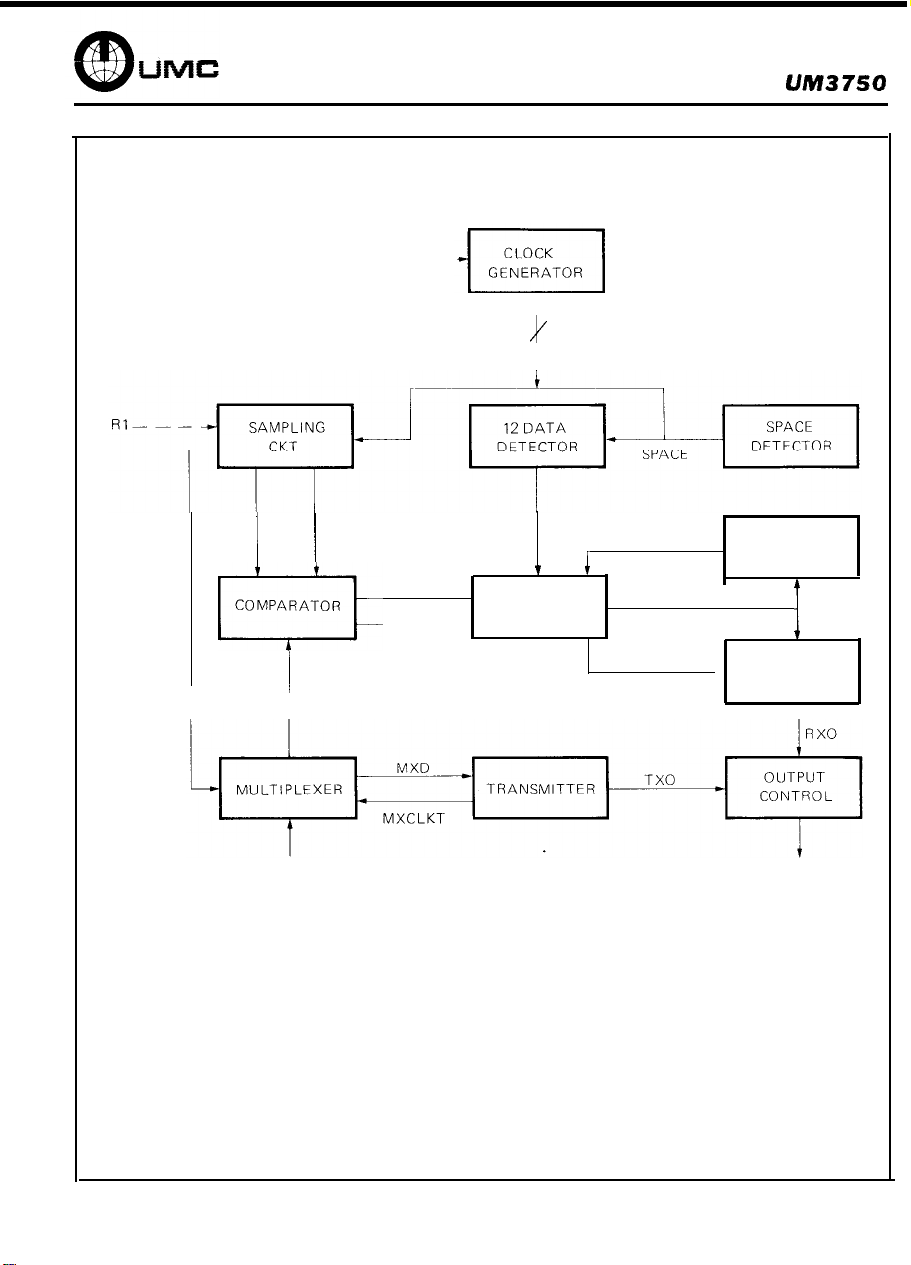

Block

urn3750

Diagram

R.C.INPUT - - - - - -

CPCLK

COMPARATOR

I

RID

I

L

MXCLKR

MXD

-

ERROR

CLR

WD

7

STATE

CONTROLLER

TIM0

i

VLD

INIT

64ms/128ms

TIMER

I

VALID 4

COUNTER

Al-Al2

Block

Diagram Description

CPCLK

WXCLKR: CLK of Multiplexer when in Receiver mode

WXCLKT

MXD:

RID

VLD.

CLK of Comparator

CLK of Multiplexer when in Transmitter mode

Output data of Multiplexer (one of Al, A2

A12)

Sampled data by Sampling CKT

“Valid” signal. It is used to trigger Valid 4

Counter and

reset 64ms/128ms

Timer

....

2-4

CLR:

ERROR:

TIMO :

T/R OUT:

INIT:

WD:

TXO:

PXO:

Clear signal of Comparator

Error signal from Comparator

TIMER time-out signal

Transmit/Receiver output pin

Reset signal of Valid 4 Counter

Word detected signal

Transmitter output

Receiver output

T/R

OUT

(64ms or 128ms)

Loading...

Loading...