u-blox EVK-NINA-W132, EVK-NINA-W1,EVK-NINA-B2, EVK-NINA-W102, EVK-NINA-W101, EVK-NINA-W131 User Manual

...Page 1

EVK-NINA-W1/EVK-NINA-B2

Evaluation Kit for NINA-W1 and NINA-B2 modules

User Guide

Abstract

This document describes how to set up the EVK-NINA-W1/EVK-NINA-B2 evaluation kits to evaluate

NINA-W1 series and NINA-B2 series stand-alone modules. It also describes the different options for

debugging and the development capabilities included in the evaluation board.

www.u-blox.com

UBX-17011007 - R05

Page 2

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Page 2 of 21

Document Information

Title EVK-NINA-W1/EVK-NINA-B2

Subtitle Evaluation Kit for NINA-W1 and NINA-B2 modules

Document type User Guide

Document number UBX-17011007

Revision and date R05 29-Nov-2018

Disclosure Restriction

This document applies to the following products:

Product name Software version PCN reference

EVK-NINA-W101 N/A EVK-NINA-W102 N/A EVK-NINA-W131 N/A -

EVK-NINA-W132 N/A EVK-NINA-W151 N/A EVK-NINA-W152 N/A EVK-NINA-B221 N/A -

EVK-NINA-B222 N/A -

u-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this

document. Copying, reproduction, modification or disclosure to third parties of this document or any part thereof is only

permitted with the express written permission of u

-blox.

The information contained herein is provided “as is” and u

-blox assumes no liability for its use. No warranty, either express or

implied, is given, including but not limited

to, with respect to the accuracy, correctness, reliability and fitness for a particular

purpose of the information. This document may be revised by u

-blox at any time without notice. For the most recent

documents, visit www.u

-blox.com.

Copyright © u

-blox AG.

Page 3

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Page 3 of 21

Contents

Document Information ................................................................................................................................ 2

Contents .......................................................................................................................................................... 3

1 Product description .............................................................................................................................. 4

1.1 Overview ........................................................................................................................................................ 4

1.2 Kit includes ................................................................................................................................................... 6

1.2.1 EVK-NINA-B221 and EVK-NINA-W1x1 .......................................................................................... 6

1.2.2 EVK-NINA-B222 and EVK-NINA-W1x2 .......................................................................................... 6

1.3 I/O allocation................................................................................................................................................. 6

1.4 Jumper description .................................................................................................................................... 7

1.4.1 Default jumper configuration ........................................................................................................... 9

1.4.2 RMII to PHY jumper configuration................................................................................................... 9

1.5 LEDs .............................................................................................................................................................10

1.5.1 RGB-LED Jumper configuration ....................................................................................................10

1.6 Connectors .................................................................................................................................................11

1.7 Buttons ........................................................................................................................................................11

1.8 Configuration options ..............................................................................................................................12

1.8.1 Power supply ......................................................................................................................................12

2 Setting up the evaluation board ..................................................................................................... 13

2.1 EVK without software (open CPU) .........................................................................................................13

2.2 EVK with u-blox connectivity software .................................................................................................14

2.2.1 Starting up .........................................................................................................................................14

2.2.2 Getting the latest software ............................................................................................................14

Appendix ........................................................................................................................................................ 15

A Layouts.................................................................................................................................................... 15

B Schematic drawings ........................................................................................................................... 16

C Glossary .................................................................................................................................................. 19

Related documents ................................................................................................................................... 20

Revision history .......................................................................................................................................... 20

Contact ........................................................................................................................................................... 21

Page 4

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 4 of 21

1 Product description

1.1 Overview

The EVK-NINA-W1/EVK-NINA-B2 evaluation kit includes an evaluation board, which can be used as a

reference design for the NINA-W1 or NINA-B2 series modules, a quick start guide, and a USB cable.

For the NINA-B221 and the NINA-W1x1 module, the evaluation board is prepared with a U.FL coaxial

connector for connecting the external antenna. The NINA-B222 and the NINA-W1x2 module has an

onboard antenna; thus the EVK-NINA-B222 and the EVK-NINA-W1x2 evaluation board does not have

a U.FL connector.

The main features of the EVK-NINA-W1/EVK-NINA-B2 are:

• Available in several variants:

o NINA-B221 and NINA-B222

o NINA-W101 and NINA-W102

o NINA-W131 and NINA-W132

o NINA-W151 and NINA-W152

• All of the module pins are available at connectors or jumpers

• Can be powered through USB (J8) or external power supply (J23)

• Equipped with a Quad High Speed USB to Multipurpose UART/MPSSE IC (FT4232) that allows

serial communication and flashing over USB.

The EVK-NINA-W1/EVK-NINA-B2 evaluation kits are available in the following variants, depending on

the NINA module that is mounted on the EVK:

• EVK-NINA-B221 – Evaluation kit for NINA-B221 module, RF port available on U.FL connector (J21)

• EVK-NINA-B222 – Evaluation kit for NINA-B222 module with onboard antenna

• EVK-NINA-W101 – Evaluation kit for NINA-W101 module, RF port available on U.FL connector

(J21)

• EVK-NINA-W102 – Evaluation kit for NINA-W102 module with onboard antenna

• EVK-NINA-W131 – Evaluation kit for NINA-W131 module, RF port available on U.FL connector

(J21)

• EVK-NINA-W132 – Evaluation kit for NINA-W132 module with onboard antenna

• EVK-NINA-W151 – Evaluation kit for NINA-W151 module, RF port available on U.FL connector

(J21)

• EVK-NINA-W152 – Evaluation kit for NINA-W152 module with onboard antenna

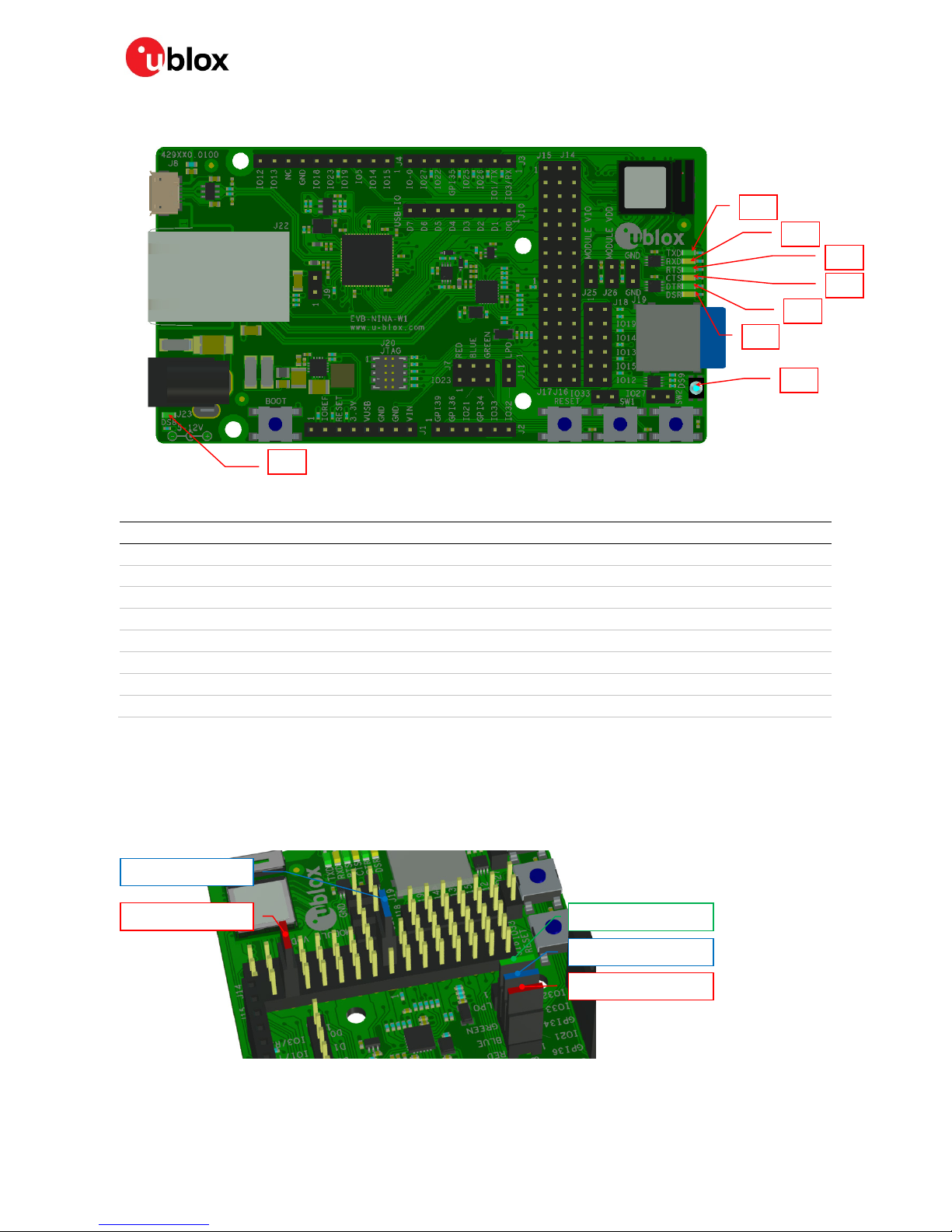

This section describes the main connectors and settings that are required to get started. Figure 1

and Figure 2 show the two different antenna variants of the EVK-NINA-W1/EVK-NINA-B2 evaluation

board.

Page 5

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 5 of 21

Figure 1: EVK-NINA-W1/EVK-NINA-B2 evaluation board with U.FL connector for external antenna

Figure 2: EVK-NINA-W1/EVK-NINA-B2 evaluation board with internal antenna

⚠ Take care while handling the EVK-NINA-B222 and EVK-NINA-W1x2. Applying force to the NINA

module might damage the internal antenna.

Page 6

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 6 of 21

1.2 Kit includes

1.2.1 EVK-NINA-B221 and EVK-NINA-W1x1

The EVK-NINA-B221 and EVK-NINA-W1x1 evaluation kits include the following:

• EVK-NINA-B221 or EVK-NINA-W1x1 evaluation board

• 2.4 GHz foldable antenna (Ex-It 2400) with reverse polarity SMA connector

• RP-SMA - U.FL cable assembly, 100 mm length

• USB cable

• Quick Start guide

1.2.2 EVK-NINA-B222 and EVK-NINA-W1x2

The EVK-NINA-B222 and EVK-NINA-W1x2 evaluation kits include the following:

• EVK-NINA-B222 and EVK-NINA-W1x2

• USB cable

• Quick Start guide

1.3 I/O allocation

The block diagram in Figure 3 provides a better understanding of how I/O signals from the module are

made available at connectors and/or interfaces of the EVK.

Sixteen (16) I/O signals are available at the middle row of the I/O allocator. These signals can be

distributed to connectors and/or interfaces on the EVK by use of jumpers to connect the associated

middle and outer row pin(s).

The signals IO-12, IO-13, IO-14 and IO-15 can be disconnected from the J4 connector by not

populating the corresponding jumpers at J18. This can be useful if the SDIO signals D2, D3, CLK, and

CMD are directed to the SD card reader (J19).

Eight signals are connected directly between the module and the J2 or J3 connector.

Figure 3: Block diagram of EVK-NINA-W10

Page 7

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 7 of 21

☞ When reset-n is released, the module pin 27 is read as boot-n. When IO-0 is connected to the

module, it must be held high during start up.

1.4 Jumper description

Parameter Description Name Default

Enable SW1 Jumper at J5-1_J5-2 connects switch 1 to module pin-7 J5

Enable SW2

Jumper at J6-1_J6-2 connects switch 2 to IO-27

(Jumper at J14-15_J14-16 must be populated to connect IO27 to module

pin-18)

J6

Enable RGB-LED Jumper at J7-1_J7-2 connects RED LED to IO-23

(Jumper at J15-3_J14-5 must be populated to connect IO23 to module

pin-1)

J7-RED

Jumper at J7-3_J7-4 connects BLUE LED to IO-21

(Jumper at J16-1_J16-2 must be populated to connect IO21to module

pin-8)

J7-BLUE

Jumper at J7-5_J7-6 connects GREEN LED to IO-33 J7-GREEN

IO/Interface

select

Module pin to IO/Interface distribution J14 See Table 3

IO/Interface

select

Module pin to IO/Interface distribution J15 See Table 3

IO/Interface

select

Module pin to IO/Interface distribution J16 See Table 3

IO/Interface

select

Module pin to IO/Interface distribution J17 See Table 3

IO/Interface

select

Module pin to IO/Interface distribution J18 See Table 3

Enable VCC_IO Connects EVK internal 3.3 V to module pin-9 to supply module VCC_IO J25

Enable VCC Connects EVK internal 3.3 V to modle pin-10 to supply module VCC J26

Table 1: EVK-NINA-W1/EVK-NINA-B2 jumper descriptions

Figure 4: Jumper positions on the EVK

Middle row jumper pin Connected to

J14-1 Module pin-28

J14-3 Module pin-29

J14-5 Module pin-1

J14-7 Module pin-21

J14-9 Module pin-20

J14-11 Module pin-16

J15 (pin-1)

J16 (pin-1)

J17 (pin-1)

J14 (pin-1)

J7 (pin-1)

J26 (pin-1)

J25 (pin-1)

J18 (pin-1)

J6 (pin-1) J5 (pin-1)

Page 8

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 8 of 21

Middle row jumper pin Connected to

J14-13 Module pin-17

J14-15 Module pin-18

J16-1 Module pin-8

J16-3 Module pin-27

J16-5 Module pin-25

J16-7 Module pin-24

J16-9 Module pin-31

J16-11 Module pin-35

J16-13 Module pin-32

J16-15 Module pin-36

Table 2: Available module pins at the middle row of jumpers J14 and J16

Connected to

Left row

jumper pin

Middle row

jumper pin

Right row

jumper pin

Connected to Default

IO-5, J4 pin-3 J15-1 J14-1 J14-2 SPI_CS, U5-PB-3 [ J15-1_J14-1 ]

IO-18, J4 pin-6 J15-2 J14-3 J14-4 SPI_CLK, U5-PB-0 [ J15-2_J14-3 ]

IO-23, J4 pin-5 J15-3 J14-5 J14-6 SPI_MOSI, U5-PB-1 [ J15-3_J14-5 ]

reserved J15-4 J14-7 J14-8 J18 pin-1_3 [ J14-7_J14-8 ]

reserved J15-5 J14-9 J14-10 IO-22, J3 pin-6 (RTS) [ J14-9_J14-10 ]

reserved J15-6 J14-11 J14-12 IO-25, J3 pin-4 (DTR) [ J14-11_J14-12 ]

reserved J15-7 J14-13 J14-14 IO-26, J3 pin-3 (DSR) [ J14-13_J14-14 ]

reserved J15-8 J14-15 J14-16 IO-27, J3 pin-7 [ J14-15_J14-16 ]

reserved J17-1 J16-1 J16-2 IO-21, J2 pin-3 [ J16-1_J16-2 ]

reserved J17-2 J16-3 J16-4 IO-0, J3 pin-8 [ J16-3_J16-4 ]

reserved J17-3 J16-5 J16-6 reserved

reserved J17-4 J16-7 J16-8 reserved

Reserved J17-5 J16-9 J16-10 J18 pin-5 [ J16-9_J16-10 ]

Reserved J17-6 J16-11 J16-12 J18 pin-7 [ J16-11_J16-12 ]

Reserved J17-7 J16-13 J16-14 J18 pin-9 [ J16-13_J16-14 ]

Reserved J17-8 J16-15 J16-16 J18 pin-11 [ J16-15_J16-16 ]

Table 3: IO-allocation via jumpers J14, J15, J16, and J17

Connected to

Left row

jumper pin

Right row jumper pin Connected to Default

J14-8 J18-1 J18-2 SPI_MISO, U5-PB-2

J14-8 J18-3 J18-4 IO-19, J4 pin-4 (CTS) [ J18-3_J18-4 ]

J16-10 J18-5 J18-6 IO-14, J4 pin-2 [ J18-5_J18-6 ]

J16-12 J18-7 J18-8 IO-13, J4 pin-9 [ J18-7_J18-8 ]

J16-14 J18-9 J18-10 IO-15, J4 pin-1 [ J18-9_J18-10 ]

J16-16 J18-11 J18-12 IO-12, J4 pin-10 [ J18-11_J18-12 ]

Table 4: IO-allocation via jumper J18

Page 9

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 9 of 21

1.4.1 Default jumper configuration

Figure 5: Jumper configuration to enable UART, IOs, and switches 1 and 2

1.4.2 RMII to PHY jumper configuration

The jumpers shown in Figure 6 must be inserted to connect the 10Base-T/100Base-TX PHY with the

associated module RMII interface pins.

When the RMII PHY is connected to the module, the “BLUE-LED” is not available at IO-21.

Figure 6: RMII to PHY jumper configuration

J18

-10 to IO15

Mod pin

-21 to J18-3

SW2 to IO27

Mod pin

-20 to IO22 (RTS)

Mod pin

-16 to IO25 (DTR)

Mod pin

-17 to IO26 (DSR)

3.3V to Mod pin

-10

3.3V to Mod pin

-9

J18

-6 to IO14

J18

-8 to IO13

SW1 to IO33

J18

-12 to IO12

Mod pin

-31 to J18-5

Mod pin

-35 to J18-7

Mod pin

-32 to J18-9

Mod pin

-36 to J18-11

J18

-4 to IO19 (CTS)

Mod pin

-18 to IO27

Mod pin

-27 to IO0

Mod pin

-29 to IO18

Mod pin

-28 to IO5

Optional: Jumpers to connect

J20

Jumpers to connect Ethernet

PHY

Page 10

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 10 of 21

1.5 LEDs

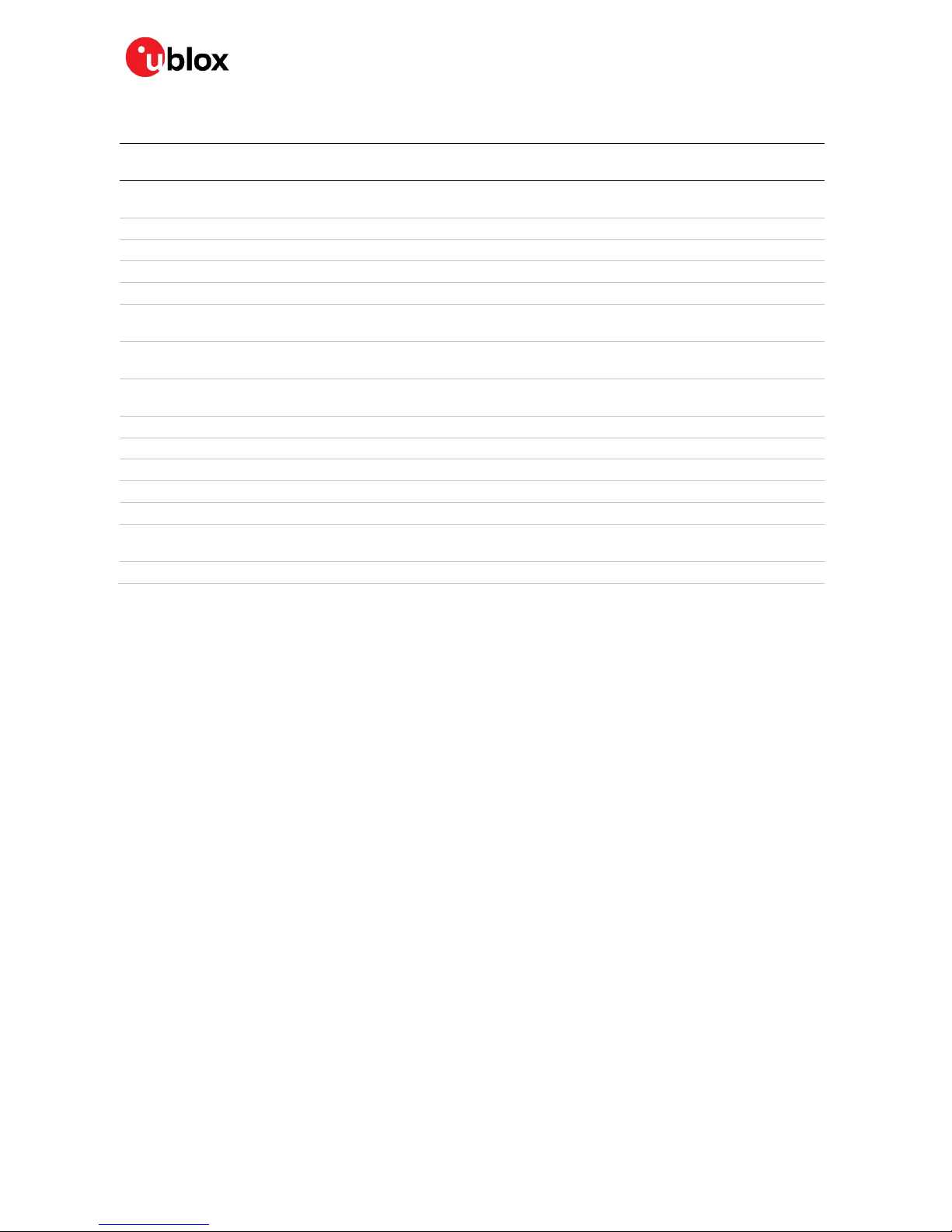

Figure 7: Position of LEDs on EVK-NINA-W1/EVK-NINA-B2

Function Description Name Color

Power LED Supplied from the EVK 3.3 V DC/DC converter DS8 Green

UART TxD Flashing LED indicates UART Tx activity (output from the module) DS2 Green

UART RxD Flashing LED indicates UART Rx acitivty (input to the module) DS3 Amber

UART RTS LED indicates UART RTS status (output from the module) DS4

[ 1 ]

Green

UART CTS LED indicates UART CTS status (input to the module) DS5

[ 1 ]

Amber

UART DTR LED indicates UART DTR status (output from the module) DS6

[ 1 ]

Green

UART DSR LED indicates UART DSR status (input to the module) DS7

[ 1 ]

Amber

status RGB LED to present module satus DS9

[ 1 ]

RGB

Table 5: EVK-NINA-W1/EVK-NINA-B2 LEDs description

☞ [1] To control the LEDs, the corresponding signal jumper(s) must be populated.

1.5.1 RGB-LED Jumper configuration

The jumpers shown in Figure 7 must be inserted to connect the RGB-LED driver with the associated

module pins.

Figure 8: RGB-LED to IO signals jumpers

DS2

DS4

DS8

DS5

DS6

DS9

DS7

DS3

IO-33 to GREEN LED

IO-21 to BLUE LED

IO-23 to RED LED

Mod pin-1 to IO-23

Mod pin-8 to IO-21

Page 11

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 11 of 21

1.6 Connectors

The available connectors on the EVK-NINA-W1/EVK-NINA-B2 board are shown in Figure 9.

Figure 9: EVK-NINA-W1/EVK-NINA-B2 connectors

Connector Description

J1, J2, J3, J4 Connectors for accessing the NINA-W1 IO signals (GPIO)

J8 USB connector; type Micro-B

J10 Reserved

J21 RF-port at U.FL coaxial connector for external antenna (not used on EVK-NINA-B221 or EVK-NINA-W1x2)

J22 RJ45 connector, RMII to PHY

J23 2.1 mm Power jack, positive center pin, 5 – 12 V

Table 6: EVK-NINA-W1/EVK-NINA-B2 connector descriptions

1.7 Buttons

The EVK-NINA-W1/EVK-NINA-B2 evaluation board has four buttons as explained in Table 7. Two of

them can be connected to NINA pins via jumper configuration.

Button Description

RESET Reset button, triggers the reset logic that pulls module pin-19 low

BOOT If reset is asserted pressing BOOT-switch will pull module pin-27 low

SW1 General function button connected to jumper J5 pin-2

SW2 General function button connected to jumper J6 pin-2

Table 7: EVK-NINA-W1/EVK-NINA-B2 buttons descriptions

Page 12

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Product description Page 12 of 21

1.8 Configuration options

Module pin

number

IO- signal

Primary

function

Accessible at

Jumper/Connector

Module pin

number

IO-

signal

Primary

function

Accessible at

Jumper/Connector

1 GPIO-23

J14-5, [J4-5, J7-1]

( 1

)

20 GPIO-22 UART_RTS J14-9, [J3-7]

( 1 )

2 GPI-34 J2-3 21 GPIO-19 UART_CTS J14-7, [J4-4]

( 1 ) ( 2 )

3 GPI-39 J2-1 22 GPIO-1 UART_TXD J3-2

4 GPI-36 J2-2 23 GPIO-3 UART_RXD J3-1

5 GPIO-32 J2-6, J11-2 24 GPIO-4 J16-7

6,12, 14 GND

J1-6,-7, J4-7, J121,-2

25 GPIO-2 J16-5

7 GPIO-33 J2-5, J5-1, J7-5 26, 30 GND

J1-6,-7, J4-7, J121,-2

8 GPIO-21

J16-1, [J2-4, J7-3]

( 1

)

27 GPIO-0 J16-3, [J3-8]

( 1 )

9 VCC_IO J25-2 28 GPIO-5 J14-1, [J4-3]

( 1 )

10 VCC J26-2 29 GPIO-18 J14-3, [J4-6]

( 1 )

13 RF-port Antenna J21 31 GPIO-14 J16-9, [J4-2]

( 1 ) ( 2 )

16 GPIO-25 UART_DTR J14-11, [J3-4]

( 1 )

32 GPIO-15 J16-13, [J4-1]

( 1 ) ( 2 )

17 GPIO-26 UART_DSR J14-13, [J3-3]

( 1 )

34 GPI-35 J3-5

18 GPIO-27

J14-15, [J3-6, J6-1]

(

1 )

35 GPIO-13 J16-11, [J4-9]

( 1 ) ( 2 )

19 RESET-N RESET (J1-3 via logic) 36 GPIO-12 J16-15, [J4-10]

( 1 ) ( 2 )

Table 8: Module pin to IO signal conversion

☞ (1) Connector/jumper placed inside the brackets indicates that a jumper must be positioned at the

corresponding position of the IO distribution jumpers J14 – J17 if the IO-signal is to be presented

at the designated connector/jumper as mentioned in Table 3.

☞ (2) These IO signals require a second jumper to be positioned at the IO distribution jumper J18 as

mentioned in Table 4.

1.8.1 Power supply

The supply voltage to the EVK-NINA-W1/EVK-NINA-B2 evaluation board can be sourced from the

following connectors:

• USB (J8)

☞ Depending on your USB source, the USB supply current may be insufficient.

• External power supply (J23): The external supply voltage must be in the range 5 – 12 V

Page 13

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Setting up the evaluation board Page 13 of 21

2 Setting up the evaluation board

The EVK-NINA-W10 is delivered without any software (open CPU) and the software must be

developed by the user.

The EVK-NINA-B2, EVK-NINA-W13 and the EVK-NINA-W15 is delivered with the ublox connectivity

software pre-flashed on the module.

⚠ The module is designed to be used only with the applicable software and only compatible software

can be flashed on the module.

Before connecting the module, download and install the latest u-blox s-center evaluation software

from the u-blox website.

Plug in external supply power at connector J23 or connect J8 (USB type Micro B) to a USB host using

the USB cable. The status light (DS8) will turn green, indicating that the internal EVK 3.3 V is on.

⚠ When using the evaluation board with external antenna, before powering up the EVK, ensure that

you have connected the 2.4 GHz antenna with the U.FL antenna connector (J21). Failing to do so

may cause undesired operation.

⚠ Be careful to check polarity before connecting external power supply to the evaluation board.

Center conductor is positive (+) and the ring is negative (-).

⚠ The current consumption during startup of the evaluation board can be high.

The operating system will install the correct COM port drivers automatically. The drivers will need to

be installed only when you connect the unit to a new computer for the first time. For more information

about the COM ports and their configuration, see the FTDI FT4232H Datasheet [6].

One COM port will automatically be assigned to the unit by the Windows OS. To view the assigned

COM ports on Windows 7, follow the steps mentioned below:

• Open the Control Panel and click Hardware and Sound.

• Click Device Manager in Devices and Printers. This will open the Device Manager window where

you can view the assigned COM ports.

2.1 EVK without software (open CPU)

The chapter is applicable to the following EVKs.

• EVK-NINA-W101

• EVK-NINA-W102

When using the NINA-W10 open CPU variant, it is not possible to download the u-blox connectivity

software. Use the software developed and compiled using the Espressif SDK on this variant.

Information on how to build and FLASH the module when using Espressif SDK is available at the

following URL - http://esp-idf.readthedocs.io/en/latest/get-started/index.html.

This URL webpage provides information on how to set up the software environment using the

hardware based on the Espressif ESP32 such as NINA-W10 and also how to use the ESP-IDF

(Espressif IoT Development Framework).

The following steps must be performed to compile, flash, and execute a program on NINA-W10:

• Set up the Toolchain

o Windows, Mac, and Linux is supported

• Get the ESP-IDF

Page 14

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Setting up the evaluation board Page 14 of 21

o Download the GIT repository provided by Espressif

• Setup Path to ESP-IDF

o The tool chain program can access the ESP-IDF using the IDF_PATH environment variable

• Build and Flash

o Start a Project, Connect, Configure, Build and Flash a program

More information about this is available at http://esp-idf.readthedocs.io/en/latest/index.html

More information on this topic can be found in the NINA-W1 System Integration Manual [7].

2.2 EVK with u-blox connectivity software

This section is applicable for the following EVKs:

• EVK-NINA-B221

• EVK-NINA-B222

• EVK-NINA-W131

• EVK-NINA-W132

• EVK-NINA-W151

• EVK-NINA-W152

2.2.1 Starting up

Perform the following steps to enable communication with the module:

1. Start the u-blox s-center evaluation software.

2. Use the default baud rate 115200, 8N1 with flow control. Now, it is possible to communicate with

the module through AT commands.

For a list of available AT commands, see the u-blox Short Range AT Commands Manual [5].

2.2.2 Getting the latest software

Go to the u-blox support web page to obtain the latest available software. Instructions on reflashing

the evaluation board can be found in the Software section of the NINA-B2 System Integration Manual

[8] or the NINA-W1 System Integration Manual [7].

Page 15

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Appendix Page 15 of 21

Appendix

A Layouts

Figure 10: Primary and secondary side layouts of EVK-NINA-W1/EVK-NINA-B2

R1

0

D

S

8

D5

J8

J23

R20

C8

F1

R19

D1

C9

J22

C34

C14

R18

R17

D4

C40

D3

S4

C42

L1

C44

C

41

C43

C46

C45

R72

R69

R71

C

26

R30

R21

R1

C47

U7

J24

C15

FB1

FB2

Y1

R13

J4

R2

R74

R75

C21

R2

9

C16

C12

C13

R23

U6

R37

R3

L2

C17

C23

C25

R25

R

22

C10

J1

C20

U5

J20

C18

C11

C22

C19

C24

R33

R51

R34

R31

R41

R16

R38

R1

1

U4

C3

R32

D6

R68

C4

FB3

R52

D2

J10

R40

J3

J2

J7

C38

Y3

C33

C

32

R53

R39

R67

U

8

C35

C36

C49

C48

R43

R

36

U9

C39

J11

R55

Y2

C

31

R57

C3

0

R64

R65

R59

R58

R60

R35

C27

R47

R48

R5

6

R62

R61

R63

R54

C37

R42

R28

J17

J15

S3

R27

J16

J14

R

26

C7

J18

J25

J5

C

28

S1

R

70

R45

C29

J2

6

R46

R78

R81

R73

R66

R79

R80 R77

R44

R76

C5

J6

U1

U3

C1

U2

C2

S2

DS7

DS6

DS5

DS4

DS3

DS2

C

6

R8

R9

R7

R6

R5

R4

97

5

3

1

10

8

6

42

R24

R

50

R49

J12

M1

R12

R14

R15

J21

DS1

J19

1

TP4

TP3

TP2

TP1

TP6

TP5

TP7

R1

50

R149

Page 16

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Appendix Page 16 of 21

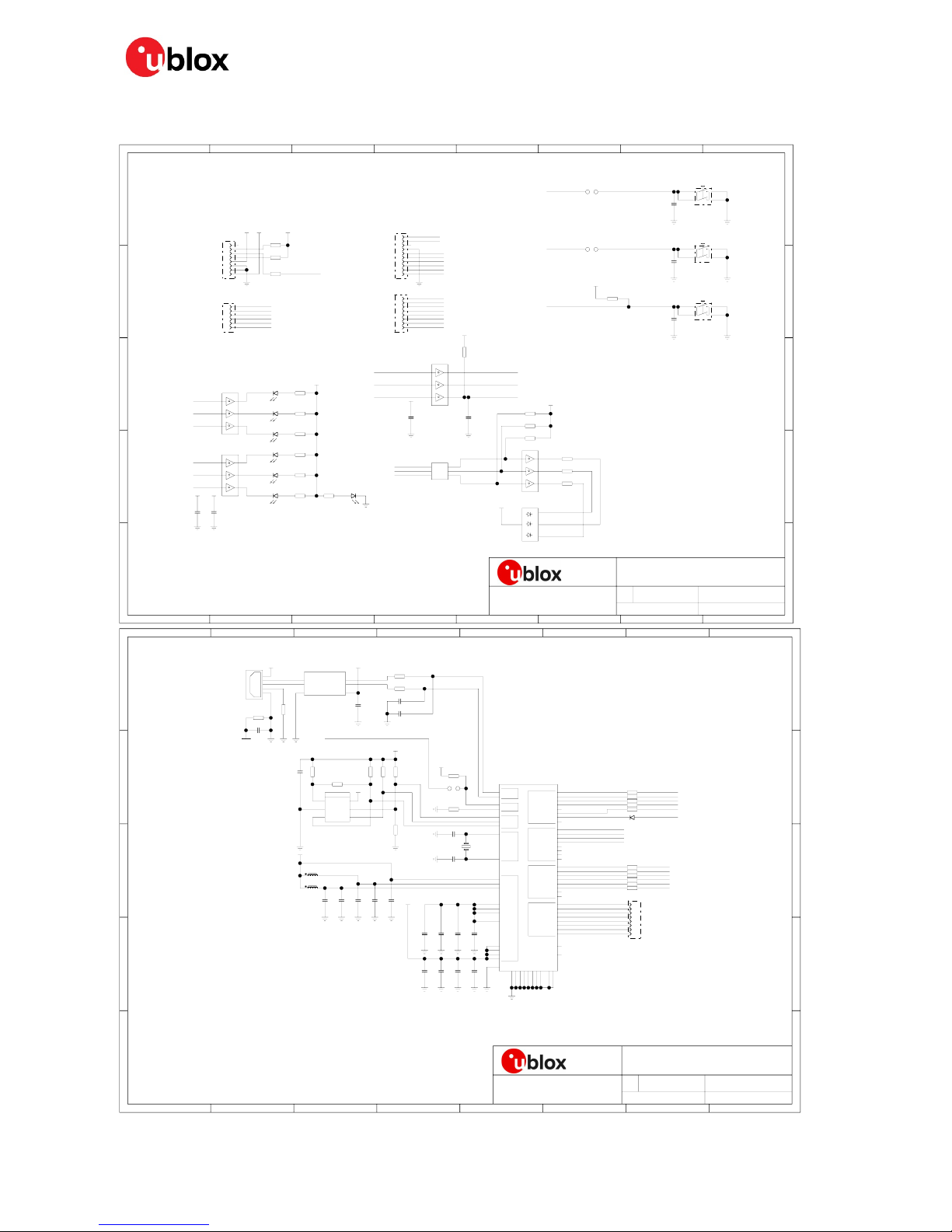

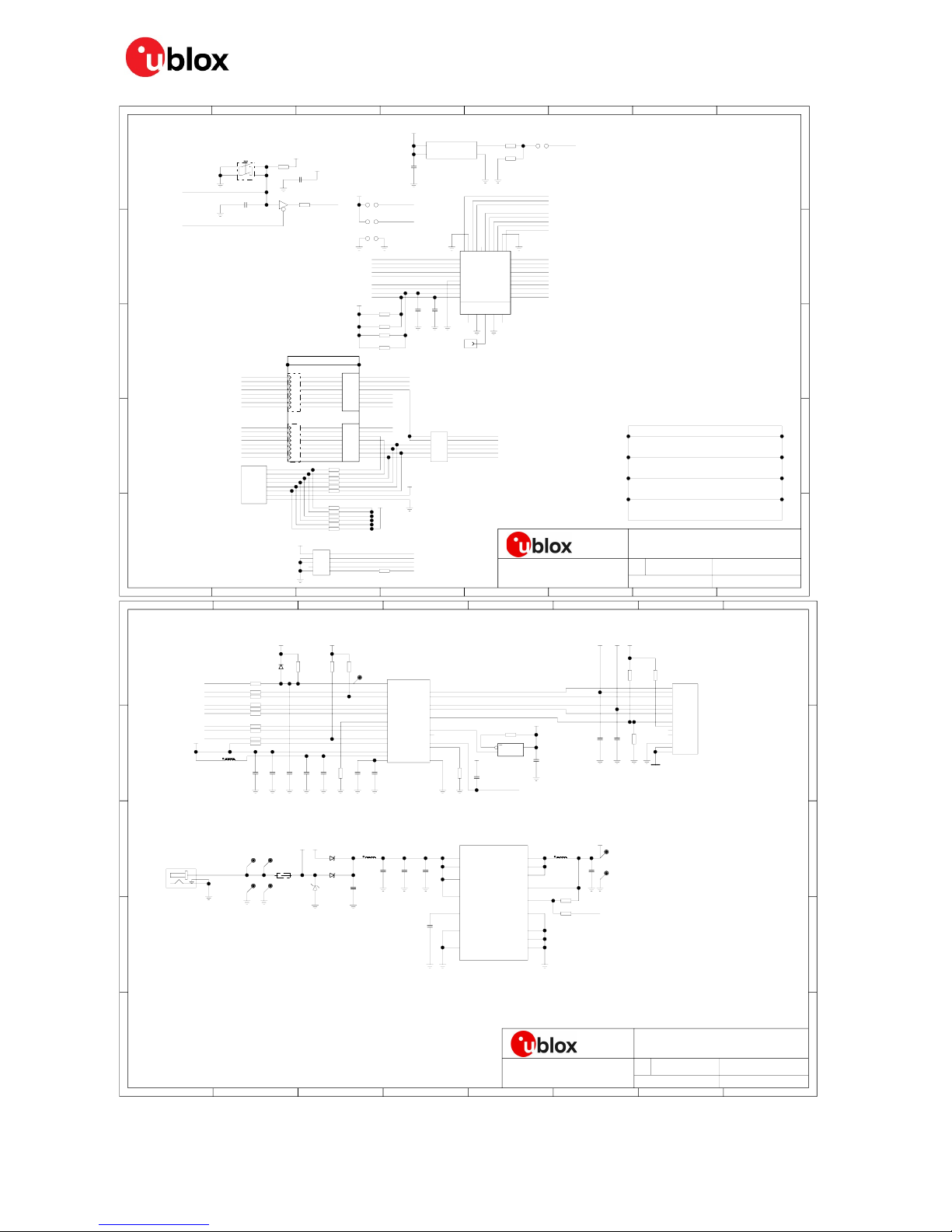

B Schematic drawings

T

XD

RXD

DSR

CTS

RTS

DTR

5V0

5%

100N

2U2

We d M ar 15 1 6 :0 5: 4 0 20 17

PA GE 1 OF 5

EV B- NI NA -W 1

Ovik

<U BX_ CO MP AN Y> $C ha n ge : 58 3 81 7

B

04

I-39

I-36

I-34

IO- 21/ SPI _HD /BL UE_ LED /RM II_ TXE N

IO- 33/ SW- 1/G REE N_L ED

IO-3 2/L PO

ORA NG E

10%

VCC =3V 3;G ND= GND

ET H_ RES ET -D LY

IO- 0/S YS_ BOO T/R MII _CL K

RES ET -N

MOP- 23

MOP- 22

MOP- 34

IO-1 2/S DIO_ D2/T DI

IO- 13/ SDI O_D 3/T CK

I-35

IO- 22/ RTS /SP I_W P/R MII _TX D1

IO- 27/ SW- 2/R MII _CR SDV

IO- 25/ DTR /RM II_ RXD 0

IO- 26/ DSR /RM II_ RXD 1

IO-1 /TX D

IO-3 /RX D

AR

DUI NO_ 1C

IO-0

IO-22

IO-25

IO-26

IO-27

IO- 15/ SDI O_C MD/ TDO

EVB _RE SET -N

MOP- 3

MOP- 4

IO-21

ARD UIN O_1 B

MOP- 7

MOP- 2

5%

NC

VCC =3V 3;G ND= GND

VCC =3V 3;G ND= GND

IO-22

220R

220R

100N

3V

3

220R

10%

10%

3V3

IO-26

IO-19

IO-25

5%

5%

5%

220R

GRE EN

220R 5%

100N

10%10%

100N

10K

ORA NG E

IOREF

33R

3V3

GRE EN

220R

MOP-2 2

MOP-2 3

GND

IO-13

IO- 18/ SPI _CL K

0

5%

0

R

0

VIN

10%

IO-12

100N

SW2

VIN

10K

ORA NG E

5%

IO-27

SW-1

3V3

IO-2 1

MOP -7

5%1K0

1K0

5%2K7

3V3

10K

10K 5%

5%10K

VCC =3V 3;G ND= GND

RGB

LED _RE D

LED _G RE EN

LED _BL UE

5%

100N

IO-18

3V3

RESE T

IO-23

IO-19

IO-5

EVB _R ES ET- N

3V3

ETH _R ES ET- N

3V3

H E A D E R S / L E D / S W

IO-2 3

5%

3V3USB_5 V

RES ET -N

20%

ET H_ RES ET -D LY

EVB _R ES ET- N

GRE EN

220R

GRE EN

MOP -7

5%

NC

5%

0R

ARD UIN O_1 A

GND

GND

3V3

MOP- 5

IO- 23/ SPI _DI /RE D/L ED

IO- 19/ SPI _DO /CT S/R MII _TX D0

IO-5 /SP I_CS

IO- 14/ SDI O_C LK/ TMS

IO-14

ARD UIN O_1 D

IO-15

1

1

1

1

1

1

1

1

1

1

1

1

R

G

B

A

65

43

21

U2

U3

U4

J7

U1

DS1

R8

R9 R10

R6

R7

R5

R16

R1

R4

R14

R12

R15

R28

R27

R26

R3

R2

74LVC3G07

wurth_150141m173100

74LVC3G07

74LVC3G07

74LVC3G07

DRAWING TITLE :

6

5

4

3

2

1

1

2

5

4

3

8

7

6

1

2

5

4

3

6

7

8

9

10

1

2

5

4

3

8

7

6

R11

4

5

6

3

1 7

2

AC

AC

AC

AC

5

6

3

1 7

2

5

6

3

1 7

2

1

2

3

8

4

5

6

7

3

1

6

3

8

C

2

4

4

2

AC

1 2

1

3

3

A C

3

1

4

2

2

7

10

5

4

3

1

6

2

1

3

5 6

4

2

5

7

6 2

3

1

1 3

2

4

6

4

A

1

5

1

2

5

1

2

7

8

9

C1

C2

C6 C5C7

C3

C4

DS8

DS3

DS7

DS5

DS6

DS2

DS4

J1

J3

S3

S2

S1

J5

J6

J2

J4

E

D

C

B

A A

E

D

C

B

12345678

345678 2

U-BLOX AG

DATE :

SWITZERLAND

1

THALWIL

GROUP :

D

ESIGN BY :

ICM:

PCB_VER.:

VERSION :PROJECT :

A3

W

ed Ma r 1 5

07 :4 4 :1 2 20 1 7

EV B- NI NA -W 1

PA GE 2 O F 5

B

Ovik

<U BX_ CO MP AN Y>

04

$C ha n ge : 58 3 81 7

10%

100N

1

2MHZ

EVB _R ESE T- N

3P9

+/-0 .5P

30R @1 00 MHZ

10%

100N

100N

100N

5%10K

5%10K

5%

18P

5%

FTDI_ SPI_ CLK

FTDI_ BOOT -N

5%

D

NI

10%

20%

0

USB_5 V

2K2

100N

10%

10%

100N

10%

100N

100N

10%

10%

10%

100N

10%

100N

10%

100N

30R @1 00 MHZ

20%

4U7

10%

10%

FTDI_ IO-D 1

4U7

FTDI_ TDI

FTDI_ IO-D 2

0R

0

0R

0

0R

0R

U S B - F T D I I N T E R F A C E

4U7

20%

3V3

3V3

FTDI_ IO-D 3

FTDI_ IO-D 4

FTDI_ IO-D 5

5%

0

IO-22

12K

10K

3V3

40PPM

3P9

0

0R

0R

USB_

DM_D

FTD I_U SB_ DP

5%

18P

5%

1%

FTDI_ SPI_ CS

0

FTDI_ RESE T-N

FTDI_ TDO

FTDI_ SPI_ MISO

5

%

0

0R

IO-25

IO-26

0

0

0R

IO-19

FTDI_ DSR

FTDI_ IO-D 0

0R

0R

0R

0

MOP-2 2FTDI_ RXD

0R

0

MOP-2 3FTDI_ TXD

FTDI_ DTR

FTDI_ CTS

FTDI_ RTS

FTDI_ SPI_ MOSI

FTDI_ IO-D 7

FTDI_ IO-D 6

0

0

USB_ DP_ D

FTDI_ TMS

0R

FTDI_ TCK

+/-0 .5P

5%

3V3

JTAG_ BOOT -N

RESET -N

JTAG_ TMS

JTAG_ TDO

JTAG_ TDI

JTAG_ TCK

FTD I_U SB_ DM

100N

10K

10K

3V3

10M

100N

SGND =GN DA

USB_ DP

USB_ DM

USB_5 V

DNI

10K

100K

5%

U

SB MICRO B

GND

AGND

GND

GND

GND

GND

GND

GND

GND

GND

DM

VUSB

GND

DP

N.C.

TXD/TCK/SCL

DTR#/GPIO0

CTS#/TMS/CS

DSR#/GPIO1

DCD#/GPIO2

RI#/TXDEN#/GPIO3

RTS#/TDO/DI

RTS#/TDO/DI

CTS#

RI#/TXDEN#

EECLK

EECS

DP

DM

RESET#

EEDATA

CTS#/TMS/CS

DTR#/GPIO0

RXD/TDI/DO

TXD/TCK/SCL

OSCI

TXD

DCD#

RXD

VCORE

DSR#/GPIO1

DCD#/GPIO2

TXD

CTS#

RI#/TXDEN#/GPIO3

RXD

RTS#

SUSPEND#

PWREN#

TEST

RI#/TXDEN#

RXD/TDI/DO

VCCIO

VCCIO

VCCIO

VCCIO

VCORE

DCD#

DSR#

RTS#

DSR#

DTR#

DTR#

VCORE

VREGOUT

OSCO

VPHY

VPLL

VREGIN

REF

93XX56X

GNDA

U6

J8

VCCGND

I/O1 I/O1

I/O2 I/O2

GND

DI

VCC

CS

CLK

DO

CAT AN

R19

R13

R40

R18

R17

R32

R39

R38

R37

R36

R35

R30

R33

R31

R41

R34

R29

R20

FT4232H

D6

C25

C34

C26

J10

C14

C8

DRAWING TITLE :

1

2

3

4

5

8

7

6

P

OWER

PORT APORT BPORT CPORT D

R23

R21

R25

R22

R24

2

1

5

3

4

16

21

19

22

23

24

28

18

54

46

62

63

8

7

14

61

29

30

27

26

2

48

45

52

64

32

33

38

41

34

39

40

36

60

13

59

17

56

42

31

20

37

58

57

53

44

43

55

12

49

3

4

9

50

62

3

6

5

4

1

4

6

7

8

2

1

5

6

3

5

1

2

4

3

USBLC6 2SC6

C13

C19

C18

C17

C23

C22

C21

C16

C15

C24

C12

C11

C20

C

9

C10

FB2

FB1

J24

E

D

C

B

A A

E

D

C

B

12345678

345678 2

U-BLOX AG

DATE :

SWITZERLAND

1

THALWIL

GROUP :

DESIGN BY :

ICM:

PCB_VER.:

VERSION :PROJECT :

1

105147525

351115

65

D1

Y1

U5

A3

Page 17

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Appendix Page 17 of 21

M

OP- 9 -> VCC _I O

PO P UL A TE P O S IT I ON M 1 W IT H N I NA - W1 3 2

EV B -N I NA -W 1 02 W I TH I N T ER N AL A NT E NN A

PR OD U CT V AR I AN TS

PO PU L AT E PO S M1 W I TH NI N A- W1 0 1

EV B -N I NA -W 1 01 W I TH U . F L C O NN E C T OR

MOP -1 0 -> VC C

MOP -6 - > GND

MO P- 7 -> SW-1 / L E D_ GR EE N/ GP IO -3 3

MO P- 8 -> RMII _ T X EN /L ED _B LU E/ GP IO -2 1

MO P- 5 -> LPO_ C L K /G PI O_ 32

MOP -4 - > GPI- 36

MOP -3 - > GPI- 39

MOP -2 - > GPI- 34

MO P- 1 -> SPI_ D I / LE D_ RE D/ GP IO -2 3

MO P- 35 -> JT AG _T CK /S DI O_ D3 /G PI O- 13

3 X 1 6 PIN HEA DE R

PO P UL A TE P O S IT I ON M 1 W IT H N I NA - W1 0 2

EV B -

NI N A- W 13 1 WI T H U . FL CO N NE C TO R

PO PU L AT E PO S M1 W I TH NI N A- W1 3 1

EV B -N I NA -W 1 32 W I TH I N T ER N AL A NT E NN A

MOP -3 0 -> GN D

MO P- 32 -> JT AG _T DO /S DI O_ CM D/ GP IO -1 5/ BS P- 1( 10 K P UL L- DO WN )

MOP -3 3 -> RE SER VE D

MOP -3 4 -> GP I35

AN TE N NA U .F L CO NN E C T OR

MO P- 36 -> JT AG _T DI /S DI O_ D2 /G PI O- 12 /B SP -2 (1 0K PULL -U P)

MO P- 27 -> RM II _C LK /G PI O- 0/ BO OT -N (1 0K P UL L- UP )

MO P- 28 -> SP I_ CS /I 2C _S DA /G PI O- 5/ BS P- 0

MO P- 29 -> SP I_ CL K/ I2 C_ SC L/ GP IO -1 8

MO P- 31 -> JT AG _T MS /S DI O_ CL K/ GP IO -1 4

MOP -1 4 -> GN D

M

OP -1 8 -> RMI I_ CR SD V/ SW -2 /G PI O- 27

MO P- 23 -> UA RT _R XD /G PI O- 3

MO P- 25 -> RM II _M DC LK /S DI O_ D0 /G PI O- 2/ BS P- 3

MO P- 24 -> RM II _M DI O/ SD IO _D 1/ GP IO -4

MOP -2 2 -> UA RT_ TX D/ GP IO- 1

MO P- 21 -> RM II _T XD 0/ SP I_ DO /U AR T_ CT S/ GP IO -1 9

MO P- 20 -> RM II _T XD 1/ UA RT _R TS /G PI O- 22

MO P- 19 -> RE SE T- N( 15 0K P UL L- UP 10 NF TO GN D)

MO P- 17 -> RM II _R XD 1/ UA RT _D SR /G PI O- 26

MO P- 16 -> RM II _R XD 0/ UA RT _D TR /G PI O- 25

MOP -1 5 -> RE SER VE D

MOP -1 1 -> RE SER VE D

MOP -1 2 -> GN D

MOP -1 3 -> RF _PO RT

MOP -2 6 -> GN D

Th u M

ar 16 16 :1 7 :4 5 20 1 7

PA GE 3 O F 5

EV B- NI NA -W 1

Ovik

<U BX_ CO MP AN Y> $C ha n ge : 58 3 81 7

B

04

10K 5%

BO M_ EV K_ NI NA _W 13 2= UB XH 14 -0 00 03 48

BO M_ EV K_ NI NA _W 13 1= UB XH 14 -0 00 03 49

1K0

RESE T-N

BOM _E VK _N INA _W 13 2= DNI

FTDI_ SPI_ CLK

MOP -28

JTAG_ TDO

0

FTDI_ SPI_ CS

3V3

10%

MOP- 18

RESE T-N

MOP- 17

MOP- 16

ETH_T XD1

MOP- 20

MOP-2 1

MOP- 36

MOP- 29

MOP- 32

MOP-3 1

MOP- 28

MOP -34

MOP- 27

MOP- 35

3V3

5%

ETH _R ES ET- N

VC C= 3V 3; GN D= GN D

3V3

MOP- 9

2K7

10K

DNI

DNI

0R

MOP- 10

IO-0

5%

10R

10R

10R

10R

3V3

SDIO_ D2

SDIO_ D1

10R

5%

5%

SDIO_ D3

GND =GND

JTAG_ TDI

JTAG_ RESE T-N

10K

10K 5%

5%

10K

JTAG_ TMS

MOP- 25

SDIO_ D0

SDIO_ CLK

SDIO_ CMD

3V3

3V3

5%

10K

5%5%10K

5%10K

ETH_M DC

ETH_R EFCL K

10R

5%

5%

5%

MOP- 36

JTAG_ TMS

JTAG_ TCK

0R

IO-12

IO-15

IO-13

IO-14

MOP -5

5%

5%

20P PM

MOP- 3

MOP- 2

MOP-1

1

00N

MOP- 10

3V3

MOP- 8

JTAG_ TDO

IO-26

MOP- 5

DNI

MOP- 27

MOP -16

MOP -20

MOP -17

MOP -18

MOP -24

ETH_T XEN

JTAG_ TCK

JTAG_ TDI

IO-18

ETH_T XD0

IO-23

IO-27

MOP- 23

MOP- 24

MOP- 25

10N

10%

J

TAG _B OO T-N

10%

100N

I

O

-19

MOP-3 1

ETH_M DIO

IO-5

NINA-W1

FTDI_ SPI_ MISO

100N

10%

ETH_C RSDV

ETH_R XD1

ETH_R XD0

MOP -29

MOP- 1

MOP- 21

IO-21

MOP- 32

MOP- 35

MOP- 27

10

0N

MOP- 22

MOP- 9

MOP- 8

0R

0R

DNI

IO-22

0R

10

%

IO-25

32 .7 68 KH Z

SPI_M ISO/ IO-1 9

FTDI_ SPI_ MOSI

MOP- 7

MOP- 4

3V3

9

7

5

1

3

12

10

8

6

11

2

4

6

12

1615

1413

11

1

109

87

5

43

2

6

12

1615

1413

11

1

109

87

5

43

2

109

1

7

3

5

8

2

6

4

29

33

28

34

35

36

26

31

27

15

14

13

12

11

32

30

J

20

J14

J16

J18

DAT1

DAT2

CD/DAT3

CLK

CMD

VDD

VSS

DAT0

7

42

1

4

1

10

6

4

3

5

2

8

7

5

8

9

2

6

3

22

23

25

17

24

3

2

16

4

1

21

20

19

18

6

7

8

10

9

5

MICROSD CARD

R80

R79

R78

R77

R76

R73

R70

R66

R46

R45

R44

R43

R48

R47

R50

R49

R150

R149

R51

R42

R81

J17

C39

J15

C48

DRAWING TITLE :

1

1

2

3

4

5

8

7

6

1

2

3

4

5

8

7

6

J19

VDD

GND

CLKOUT

CLKOE

1

22

23

25

17

24

3

2

16

4

1

21

20

19

18

6

7

8

10

9

5

6

12

1615

1413

11

1

109

87

5

43

2

2

1

5

4

3

6

7

8

6

12

1615

1413

11

1

109

87

5

43

2

2

1

5

4

3

6

7

8

2

4

1

5

1

10

1211

6

8

3

7

9

4

3 2

3

4

21

21

ANTENNA

C28

C27

C29

U

9

NC7SZ125

OE_N

J11

J26

J12

S4

J21

J25

E

D

C

B

A A

E

D

C

B

12345678

345678 2

U-BLOX AG

DATE :

SWITZERLAND

1

THALWIL

GROUP :

DESIGN BY :

ICM:

PCB_VER.:

VERSION :PROJECT :

29

33

28

34

35

36

26

31

27

15

14

13

12

11

32

30

Y2 OV_7604_C7

M1

A3

2. 1M M PO W ER J AC K

4. 75 V < VI N < 12 V

Fr i M a r 1 7 1 1: 30 : 21 2 0 17

Ovik

04

$C ha n ge : 5 83 81 7

EV B- NI NA - W1

PA GE 4 O F 5<U BX _CO MP AN Y>

B

ETH_ MDC

ETH_ MDI O

ETH_ TXE N

10R

4K7

3V3

10R

VIN

1K0

22U 20%

0

5%

20%

DNI

0R

PHY_ XO_ IN

PHY_ LED 0

5%

22P

10%

22U

100N

10%

DNI

1K0

5%

3V3

3N3

10N

22U

100N

4U7

5%

10R

5%

10%

GN D= GN D

P O W E R & E T H E R N E T

1K0

100K

1%

0

1%

5%

5%

20%

5%1K0

1K0

PHY_ RXP

PHY_ TXP

120R

3V3

5%

5%

2U2

3V3

3V3

2U2

6K49

3V3

20%

3V3

10%

5%

EVB_ RESET -N

0R

10%

100N

10%

PHY_ RXN

PHY_ TXN

2U2

5%

5%

5%

5%

5%

5%

ETH_ RXD 1

ETH_ RXD

0

ETH_ TXD 1

ETH_ TXD 0

10R

10R

10R

10R

10%

ETH_ CRS DV

3V3

20%

100N

100N

10%

10%

ETH _RE FCL K

+/- 20 PP M

25. 0MH Z

GND =GN D

10R

100N

5%

PWR _JA CK_ IN

10U

30%

3V3

10%

1N5

10K

ETH _RE SET -N

4K7

10%

10%

4U7

USB_ 5V

30R @1 00 MHZ

CAT

AN

GNDA

CHS_GND

CHS_GND

YELLOW_LED_A

YELLOW_LED_C

GREEN_LED_A

GREEN_LED_C

CHS_GND

CT

RD-

RD+

CT

TD-

TD+

ST

OUT

VCC

LED0/ANEN_SPEED

REF_CLK

RXD1

RXD0

INTRP

CRSDV/PHYAD[1:0]

RST_N

MDC

GND

MDIO

TXEN

RXER

TXD0

TXD1

VDDIO

VDD_1_2

VDDA_3_3

TX-

TX+

RX+

RX-

XI

XO

REXT

J22

U8

Y3

CAT

AN

R65

C35

C33

C49

C30

C31

C36

C32

R56

R52

R57

R69

R74

L1

FB3

R68

R72R71

R75

R60

R61

R62

R58

R59

R63

R64

KSZ8081

L2

C44 C45C43

D2

DRAWING TITLE :

D5

R54

R55

R67

R53

15

17

10

11

A

9

212

14

13

5

11

9

6

3

2

6

3

3

10

9

14

13

16

15

5

4

7

8

24

1

2

1

21

2

1

6

1

3

18

14

19

20

12

8

4

10

13

3

16

12

41

C

21

11

8

23

4

5

7

CA

C47

C41

C38

C46

C40

J23

D3

D4

CON_PWR_03_SWITCH

TP7

TP2TP1

TP6

TP5

C37

TP4TP3

C42

E

D

C

B

A A

E

D

C

B

12345678

345678 2

U-BLOX AG

DATE :

SWITZERLAND

1

THALWIL

GROUP :

DESIGN BY :

ICM:

PCB_VER.:

VERSION :PROJECT :

PGND_2

PGND_1

PG

VOS

SW_3

SW_2

SW_1

PVIN_2

PVIN_1

F1

AGND

FB

FSW

DEF

SS/TR

EN

AVIN

FUSE

U7TPS6213X

A3

Page 18

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Appendix Page 18 of 21

ALL04

02

01

REV

03

ALL OVI K

DE SC R IP TI O N

RE VI S IO N H IS T OR Y

ALL

SH EET

OVI K

ALL

20 16 -1 0- 21

DA TE / DE SI G NE R

OVI K

OVI K20 16 - 11 -0 2

20 17 - 03 -1 5

SH EE T -4 , A DD E D T P 1- TP 7

FI RS T VE R SI O N OF EV K -N IN A -W 1

SH E ET - 1, P IN S WO P O N U 1 A ND U 4

RE V IS E D A F TE R RE V IS I ON M E ET I NG 2 01 6 -1 0 -1 8 O F E VB - NI N A- W 1

SH E ET - 2, P IN S WO P O F SI G NA L S " F TD I _B O OT - N" A N D " F TD I _R E SE T -N " ,R E MO V E D J 9 R 3 3 R 34 R 41

SH E ET - 3, R EP L AC E D J1 2 W I TH 3 X2 - PI N JU M PE R S, R E DU C ED N UM B ER O F P IN S ON J2 8 , R E MO V ED T P7 - TP 1 9

SH E ET - 1, P IN S WO P O N

J2 PI N 3 AN D 4, J3 PI N 2 A ND 3, AD D ED 3 X PU - RE S IS T O R O N U1

SH E ET - 2, C HA N GE D J 8 T O M OL E X 1 0 50 1 7- 0 00 1 M IC R O U S B B SU R FA C E M O UN T WI T H T H S O LD E R T A BS

SH E ET - 3, A DD E D 6 X P U- R ES I ST O RS ON J1 9 , R E MO V ED R 46 AN D CH A NG E D V A LU E ON R4 8

SH E ET - 4, R EM O VE D " DN I " O N C 4 2 A ND C 43 (N E ED E D T O RE D UC E CO N DU C TE D EM I S SI O NS )

Th u M a r 1 6 1 6: 1 9: 1 3 20 1 7

PA GE 5 O F 5

EV B- NI NA - W1

Ovik

<U BX _C OM PA NY> $C ha n ge : 5 83 8 17

B

04

R E V I S I O N H I S T O R Y

DRAWING TITLE :

E

D

C

B

A A

E

D

C

B

12345678

345678 2

U-BLOX AG

DATE :

SWITZERLAND

1

THALWIL

GROUP :

DESIGN BY :

ICM:

PCB_VER.:

VERSION :PROJECT :

A3

Page 19

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Appendix Page 19 of 21

C Glossary

Name Definition

COM Communication

CTS Clear To Send

DSR Data Set Ready

DTR Data Terminal Ready

EVK Evaluation Kit

GND Ground

GPI General Purpose Input

GPIO General Purpose Input/Output

IO Input-Output

LED Light-Emitting Diode

PHY Physical layer

U.FL Miniature coaxial RF connector

USB Universal Serial Bus

RF Radio frequency

RMII Reduced Media-Independent Interface

RTS Request To Send

UART Universal Asynchronous Receiver/Transmitter

USB Universal Serial Bus

VCC IC power-supply pin

Table 9: Explanation of abbreviations used

Page 20

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Related documents Page 20 of 21

Related documents

[1] NINA-W10 Data Sheet, document number UBX-17065507

[2] NINA-W13 Data Sheet, document number UBX-17006694

[3] NINA-W15 Data Sheet, document number UBX-18006647

[4] NINA-B2 Data Sheet, document number UBX-18006649

[5] u-blox Short Range AT Commands Manual, document number UBX-14044127

[6] FTDI FT4232H QUAD HIGH SPEED USB TO MULTIPURPOSE UART/MPSSE IC Datasheet -

http://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS_FT4232H.pdf

[7] NINA-W1 System Integration Manual, document number UBX-17005730

[8] NINA-B2 System Integration Manual, document number UBX-18011096

☞ For regular updates to u-blox documentation and to receive product change notifications, register

on our homepage (www.u-blox.com).

Revision history

Revision Date Name Comments

R01 22-May-2017 ovik, kgom Initial release.

R02 04-Jul-2017 ovik, mwej

Updated Figure 9 and Table 8

due to pin swap on connectors J2 and J3.

Updated Figure 10 and schematic drawing (Appendix B). Updated assigned COM

ports in section 2.1.

R03 09-Nov-2017 kgom

Renamed this document as EVK-NINA-W13 User Guide and updated the content

due to the availability of a separate user guide for the

EVK-NINA-W10x evaluation kits (UBX-17057549).

R04 12-Mar-2018 cmag

Updated the software version to 1.0.0 in the last table on page 2 and the “Related

documents and links” section.

R05 29-Nov-2018 fbro, kgom

Renamed this document. Restructured the information to include

support for

EVK-NINA-W1 and EVK-NINA-B2.

Page 21

EVK-NINA-W1/EVK-NINA-B2 - User Guide

UBX-17011007 - R05 Contact Page 21 of 21

Contact

For complete contact information, visit us at www.u-blox.com.

u-blox Offices

North, Central and South America

u-blox America, Inc.

Phone: +1 703 483 3180

E-mail: info_us@u-blox.com

Regional Office West Coast:

Phone: +1 408 573 3640

E-mail: info_us@u-blox.com

Technical Support:

Phone: +1 703 483 3185

E-mail: support@u-blox.com

Headquarters

Europe, Middle East, Africa

u-blox AG

Phone: +41 44 722 74 44

E-mail: info@u-blox.com

Support: support@u-blox.com

Asia, Australia, Pacific

u-blox Singapore Pte. Ltd.

Phone: +65 6734 3811

E-mail: info_ap@u-blox.com

Support: support_ap@u-blox.com

Regional Office Australia:

Phone: +61 2 8448 2016

E-mail: info_anz@u-blox.com

Support: support_ap@u-blox.com

Regional Office China (Beijing):

Phone: +86 10 68 133 545

E-mail: info_cn@u-blox.com

Support: support_cn@u-blox.com

Regional Office China (Chongqing):

Phone: +86 23 6815 1588

E-mail: info_cn@u-blox.com

Support: support_cn@u-blox.com

Regional Office China (Shanghai):

Phone: +86 21 6090 4832

E-mail: info_cn@u-blox.com

Support: support_cn@u-blox.com

Regional Office China (Shenzhen):

Phone: +86 755 8627 1083

E-mail: info_cn@u-blox.com

Support: support_cn@u-blox.com

Regional Office India:

Phone: +91 80 405 092 00

E-mail: info_in@u-blox.com

Support: support_in@u-blox.com

Regional Office Japan (Osaka):

Phone: +81 6 6941 3660

E-mail: info_jp@u-blox.com

Support: support_jp@u-blox.com

Regional Office Japan (Tokyo):

Phone: +81 3 5775 3850

E-mail: info_jp@u-blox.com

Support: support_jp@u-blox.com

Regional Office Korea:

Phone: +82 2 542 0861

E-mail: info_kr@u-blox.com

Support: support_kr@u-blox.com

Regional Office Taiwan:

Phone: +886 2 2657 1090

E-mail: info_tw@u-blox.com

Support: support_tw@u-blox.com

Loading...

Loading...