Page 1

UHC124 USB Host Controller

Data Sheet

TransDimension Inc.

2 Venture

Irvine, CA 92618

www.transdimension.com

Phone: (949) 727-2020

Fax: (949) 727-3232

sales@transdimension.com

techsupport@transdimension.com

TransDimension Document Number: MU1002

Rev. 1.05, February, 2002

Page 2

TransDimension Inc. UHC124 Data Sheet

Revision History

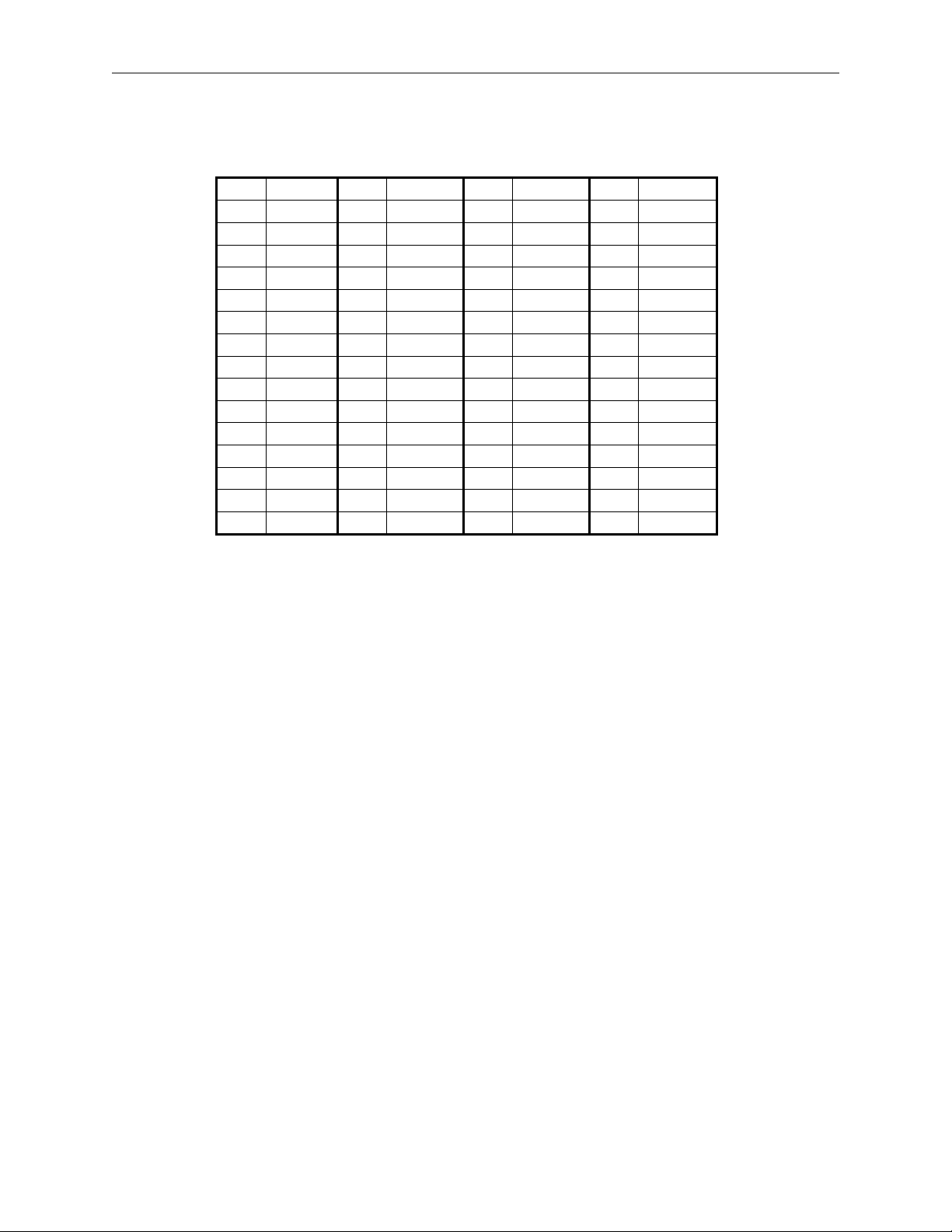

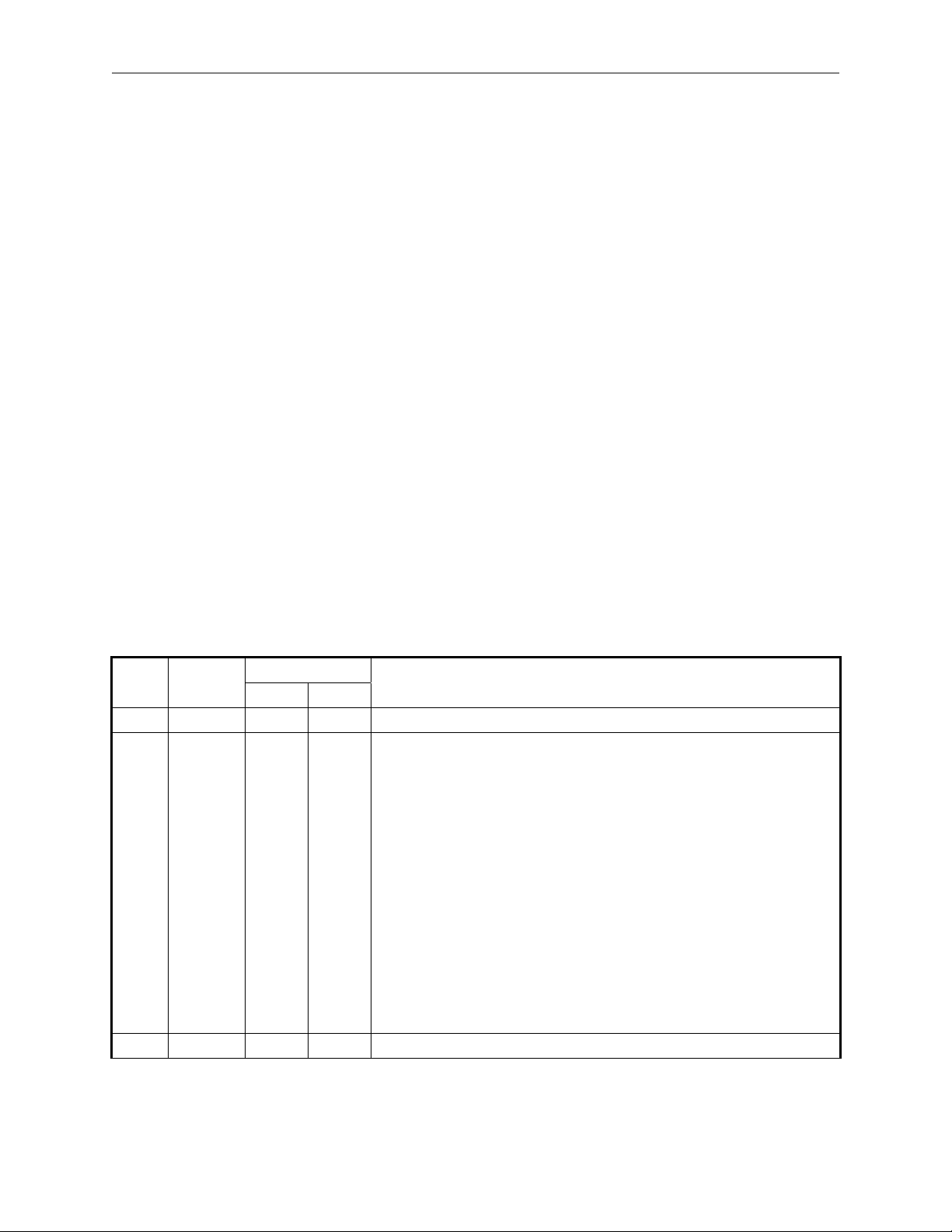

Version Number Release Date Notes

0.5 Aug., 1999 First release

0.75

Nov., 1999

• Changed UhcControl register

• Re-organized Interrupt Modes

• Moved batch interrupt control/status to

UhcInterruptEnable/UhcInterruptStatus

• Removed XDInterruptEnable field

• Pinout provided

• Added section on oscillator and PLL

• Added section on the root hub

• Added USB host state transition section

0.80 Dec., 1999

0.90 Jun., 2000

0.92 Jul., 2000

0.93

Aug., 2000

• Revised XDControl and XDStatus

• Revised all sections

• Added sections on interface and software

• Added chip pin assignment table and diagram

• Modified Sections 9 & 10 examples

• Modified electrical specifications for logic signals

0.95

Sept., 2000

• Changed pin assignments for DPn, DMn (n = 1, 2, 3,

and 4)

• Swapped Bits 7 & 5 of XDControl

0.97 Feb., 2001

0.98

Apr., 2001

• Made modifications for typos, etc.

• Modified legal statements

• Removed “Advanced Information”

• Removed “Confidential”

• Modified chip marking to match product

• Added a section on double buffering

• Corrected V

and VOL specifications

OH

• Corrected bus cycle specifications

• Added recommended landing pattern

• Added soldering profile

• Added storage conditions

1.00

May, 2001

• Corrected several typos

• Modified text on integrating the UHC124 to generic

USB host software

• Added/corrected electronic and timing specifications

• Corrected Maximum Absolute Ratings

• Added procedures of entering power save state

1.01 May, 2001

• Change “TDI Part Number:” on the cover page to

“TDI Document Number:”

1.02 August, 2001

1.03 Sept. 2001

1.04 October 2001

• Format change, added Sales Offices.

• Format change.

• Colorized the block diagram and updated feature list

TransDimension Inc. - Proprietary

Page 3

TransDimension Inc. UHC124 Data Sheet

1.04A December

• Updated sales contact list on last page.

2001

1.05 February

2002

• Refered readers to our website for all sales rep.

offices

Note: This data sheet is subject to change without notice.

TransDimension Inc. - Proprietary

Page 4

TransDimension Inc. UHC124 Data Sheet

THE DEVICE AND ITS DOCUMENTATION ARE PROVIDED “AS IS”.

TRANSDIMENSION HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS,

STATUTORY AND IMPLIED, APPLICABLE TO THE SOFTWARE AND ITS

DOCUMENTATION AND ANY RELATED PRODUCTS, INCLUDING, BUT NOT

LIMITED TO, ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT OR

FITNESS FOR A PARTICULAR PURPOSE. TRANSDIMENSION ASSUMES NO

LIABILITY FOR ANY ACT OR OMISSION OF LICENSEE. IN NO EVENT SHALL

TRANSDIMENSION BE LIABLE FOR DIRECT, SPECIAL, INDIRECT, INCIDENTAL,

PUNITIVE, EXEMPLARY OR CONSEQUENTIAL DAMAGES, INCLUDING, WITHOUT

LIMITATION, LOSS OF PROFITS OR REVENUE, LOSS OF PRODUCTS, DATA OR ANY

ASSOCIATED EQUIPMENT, COST OF CAPITAL, COST OF SUBSTITUTED EQUIPMENT

OR PARTS, FACILITIES OR SERVICES, DOWN-TIME OR LABOR COSTS, EVEN IF

TRANSDIMENSION HAS BEEN ADVISED OF THE POSSIBILITY THEREOF. The device

and any related products are not designed, authorized, or warranted to be suitable for use in lifesupport devices or systems or other critical applications. Any such use and subsequent liabilities

that may arise from such use are totally the responsibilities of the Licensee.

© 2002, TransDimension Inc., All rights reserved.

All product names are trademarks or registered trademarks of their respective owners.

TransDimension Inc. - Proprietary

Page 5

TransDimension Inc. UHC124 Data Sheet

Contents

1. Features and Block Diagram .................................................................................................. 1

1.1 Features of UHC124 ................................................................................................... 1

1.2 Block Diagram............................................................................................................ 2

1.3 Pin Assignments.......................................................................................................... 3

1.4 Abbreviations.............................................................................................................. 5

2. System Overview.................................................................................................................... 6

2.1 Interface with MCUs................................................................................................... 6

2.2 Control Memory and Transaction Descriptors ........................................................... 6

2.3 Batch Processing......................................................................................................... 7

2.4 Data Memory .............................................................................................................. 9

2.5 Double Buffering ........................................................................................................ 9

2.6 Interrupt to MCU ...................................................................................................... 10

2.7 Root Hub................................................................................................................... 10

2.8 External Crystal/Oscillator........................................................................................ 10

2.9 About UHCI and OHCI ............................................................................................ 10

2.10 USB Host API........................................................................................................... 11

2.11 RTOS Support........................................................................................................... 12

2.12 System Suspend and Resume.................................................................................... 12

2.13 Power Saving State ................................................................................................... 12

3. Signal Definitions................................................................................................................. 13

3.1 Oscillator and PLL.................................................................................................... 13

3.2 MCU Interface .......................................................................................................... 13

3.3 USB Root Hub Ports................................................................................................. 14

3.4 Test Modes................................................................................................................ 14

3.5 Power and Ground .................................................................................................... 14

4. Memory Map........................................................................................................................ 15

5. Control Registers.................................................................................................................. 16

5.1 Overview................................................................................................................... 16

5.2 UhcControl Register.................................................................................................. 16

5.3 UhcTransSelect Register........................................................................................... 20

5.4 UhcTransDone Register............................................................................................ 21

5.5 UhcIntpStatus Register ............................................................................................. 21

5.6 UhcIntpEnable Register............................................................................................ 23

5.7 UhcFmInterval Register............................................................................................ 24

5.8 UhcFmRemaining Register....................................................................................... 25

5.9 UhcFmNumber Register ........................................................................................... 25

5.10 UhcMaxOverhead Register....................................................................................... 26

5.11 UhcMagicNumber Register ...................................................................................... 26

6. Transaction Descriptor ......................................................................................................... 28

TransDimension Inc. - Proprietary i

Page 6

TransDimension Inc. UHC124 Data Sheet

6.1 Overview................................................................................................................... 28

6.2 XDControl................................................................................................................. 29

6.3 XDStatus................................................................................................................... 30

6.4 XDDevAddress ......................................................................................................... 31

6.5 XDEndpoint .............................................................................................................. 31

6.6 XDBufAddress.......................................................................................................... 32

6.7 XDBufLength ........................................................................................................... 32

6.8 XDXferCount............................................................................................................ 33

7. Root Hub .............................................................................................................................. 34

7.1 Down Stream Ports ................................................................................................... 34

7.2 Port Power Management........................................................................................... 34

7.3 Root Hub as a USB Device....................................................................................... 35

7.4 Hub Characteristics................................................................................................... 37

7.5 Port Manipulation ..................................................................................................... 38

7.6 Port Status Change Endpoint (EP1).......................................................................... 38

8. Host Controller Functional States ........................................................................................ 40

8.1 UHC124 States and State Transitions....................................................................... 40

8.2 UsbOperational ......................................................................................................... 41

8.3 UsbReset ................................................................................................................... 41

8.4 UsbSuspend............................................................................................................... 41

8.5 UsbResume ............................................................................................................... 42

8.6 PowerSave................................................................................................................. 42

9. Hardware Setup and Interface to MCU ................................................................................ 43

9.1 Power Supply............................................................................................................ 43

9.2 PowerOnReset and MasterReset............................................................................... 43

9.3 Crystal Oscillator ...................................................................................................... 43

9.4 Root Hub Ports.......................................................................................................... 44

9.5 Memory Access ........................................................................................................ 44

9.6 Test Modes................................................................................................................ 50

10. Software Issues..................................................................................................................... 51

10.1 Resets ........................................................................................................................ 51

10.2 Transaction Specification.......................................................................................... 52

10.3 Batch Dispatching..................................................................................................... 54

10.4 Transaction/Batch Scheduling .................................................................................. 54

10.5 Transaction Status Interpretation and Handling ....................................................... 55

10.6 USB Requests (Control Transfers) ........................................................................... 59

10.7 UHC124 Operation ................................................................................................... 60

10.8 Software Support ...................................................................................................... 63

11. Bus Cycle Timing................................................................................................................. 64

11.1 Memory Write Cycle ................................................................................................ 64

11.2 Memory Read Cycle ................................................................................................. 64

12. Electrical Ratings.................................................................................................................. 65

TransDimension Inc. - Proprietary ii

Page 7

TransDimension Inc. UHC124 Data Sheet

12.1 Absolute Maximum Ratings ..................................................................................... 65

12.2 Recommended/Normal Operating Conditions.......................................................... 65

12.3 D.C. Characteristics .................................................................................................. 65

12.4 A.C. Characteristics .................................................................................................. 66

13. Packaging, Soldering and Storage........................................................................................ 67

13.1 Package Diagram ...................................................................................................... 67

13.2 Packaging Dimensions.............................................................................................. 68

13.3 Landing Pattern......................................................................................................... 69

13.4 Soldering Profile ....................................................................................................... 70

13.5 Storage Conditions.................................................................................................... 70

14. Sales Offices:........................................................................................................................ 71

TransDimension Inc. - Proprietary iii

Page 8

TransDimension Inc. UHC124 Data Sheet

1. Features and Block Diagram

1.1 Features of UHC124

• USB host controller for embedded applications (set-top box, PDA, cell phone, digital camera,

Bluetooth USB HCI physical bus, etc.)

• USB Specification 2.0 (low and full speed) fully compliant

• Patent pending design

• Standard 8-bit microprocessor bus interface

• Supports batch processing of up to 16 USB transactions without interrupting the MCU

• Supports both full speed (12 Mbps) and low speed (1.5 Mbps) USB transfers

• Supports all four types of USB transfers (control, bulk, interrupt, and isochronous with

maximum packet size of 1023 bytes)

• Supports double and circular buffering for all four types of Host controller transactions

• Direct device-to-device data transfer in one Frame

• Separate transaction descriptor and data memory space

• Hardware generated Start of Frame (SOF)

• 2 KB data memory

• Support in-place processing in the data memory – used for applications requiring peer-to-

peer data transfer between USB devices

• Supports transaction spill over

• Power management with host suspend, remote wakeup, and power saving modes

• Fully qualified, market proven root hub with four downstream ports and integrated analog

transceivers

• Supports OHCI/UHCI compliant USB host stack

• USB device driver software available including printer, speaker, mass storage device, hub,

modem, ethernet, mouse, keyboard, digital camera, video camera, cell phone, STB, PDA, etc.

• Embedded RTOS software available for popular microprocessors, RISCs, CISCs, and DSPs

using WinCE, Linux, VxWorks, Nucleus, Lynx, QNX, pSOS, PowerTV, SMX, ThreadX,

VRTX, ITRON, MS-DOS operating systems

• 6 MHz crystal/oscillator to reduce cost and EMI

• Single 3.3V power supply

• Shipping industrial grade operating temperature range devices

• Military and Automotive grade available upon request

• 64 pin LQFP package

TransDimension Inc. - Proprietary

1

Page 9

TransDimension Inc. UHC124 Data Sheet

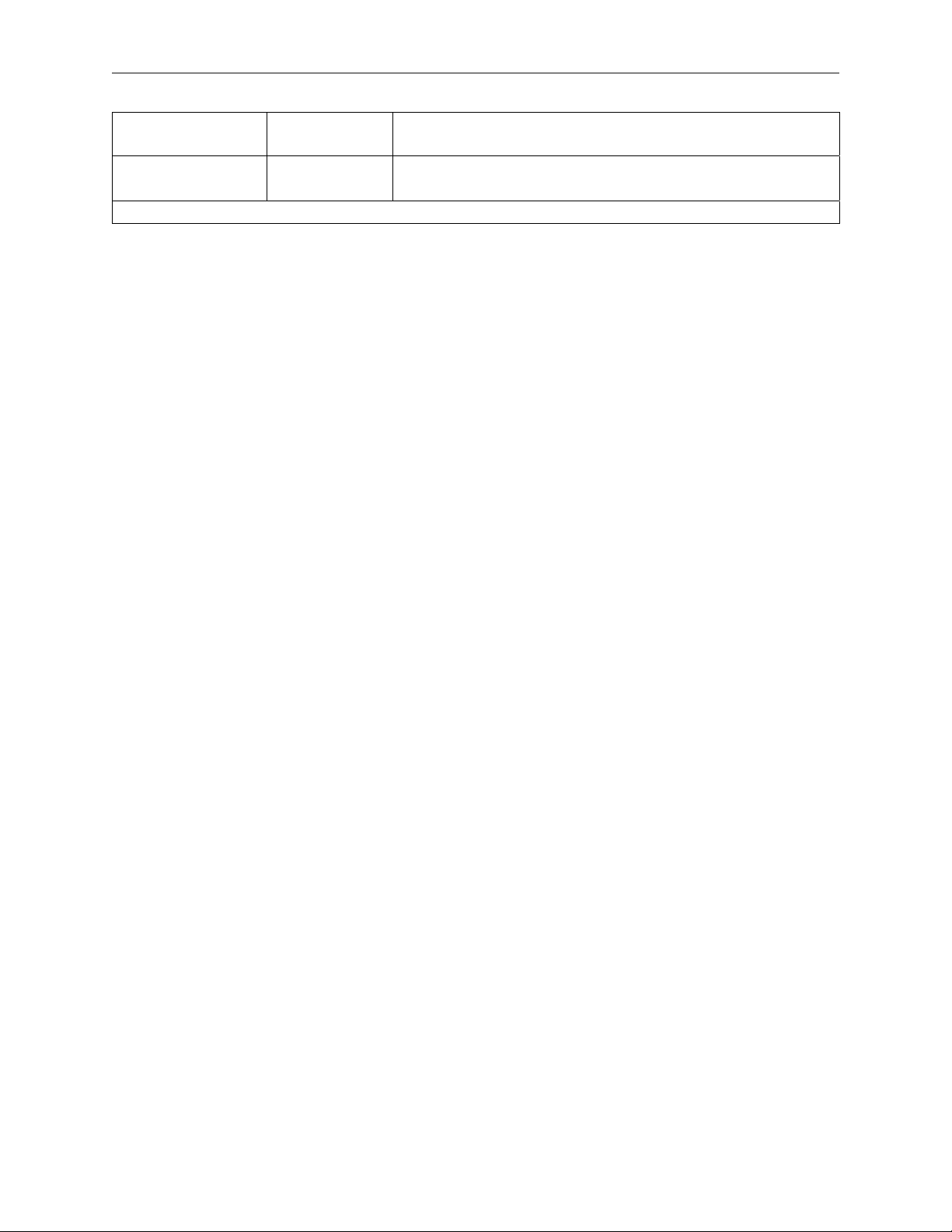

1.2 Block Diagram

OSC1

OSC

2

LPF

/RESET

A11..A0

..D0

D

7

/CS

/WR

/RD

ADS

MODE

12

8

PLL

PwrSav

Memory/

Register

Access

&

MCU

Interface

48MHz

12MHz

6MHz

USB Host

Control Logic

Registers

(16 Bytes)

Control

Memory

(256 Bytes)

Data

Memory

(2K Bytes)

5

Fig. 1 UHC124 block diagram

Host

SIE

PortChange[0:4]

Root Hub

With

Four

Downstream

Ports

DP1, DM1

/PO

, /OC

1

DP2, DM2

/PO

, /OC

2

DP3, DM3

/PO

, /OC

3

DP4, DM4

/PO

, /OC

4

1

2

3

4

TransDimension Inc. - Proprietary

2

Page 10

TransDimension Inc. UHC124 Data Sheet

1.3 Pin Assignments

1 V

17 OSC1 33 VDD 49 VSS

DD

2 A0 18 OSC2 34 DP1 50 D4

3 A1 19 LPF 35 DM1 51 D5

4 A2 20 VDD 36 VSS 52 D6

5 A3 21 TEST0 37 DP2 53 D7

6 A4 22 TEST1 38 DM2 54 /RESET

7 A5 23 TEST2 39 DP3 55 /WR

8 A6 24 TEST3 40 DM3 56 /RD

9 A7 25 /OC1 41 DP4 57 TMS0

10 A8 26 /OC2 42 DM4 58 TMS1

11 A9 27 /OC3 43 TEST4 59 TMS2

12 A10 28 /OC4 44 D0 60 TMS3

13 A11 29 /PO1 45 D1 61 /INT

14 MODE 30 /PO2 46 D2 62 ADS

15 /CS 31 /PO3 47 D3 63 GNDP

16 VSS 32 /PO4 48 VDD 64 VSS

TransDimension Inc. - Proprietary

3

Page 11

TransDimension Inc. UHC124 Data Sheet

DD

V

4

TEST

4

DM

3

2

D

D

1

0

D

D

4

DP

3

DM

3

DP

2

DM

2

DP

1

DM

DP

SS

V

1

DD

V

VSS

/RESET

/WR

/RD

TMS0

TMS1

TMS2

TMS3

/INT

ADS

GNDP

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

49 32

50 31

D4

51 30

D5

52 29

D6

53 28

D7

54 27

55 26

56 25

57 24

58 23

59 22

60 21

61 20

62 19

63 18

/PO4

/PO3

/PO2

/PO1

/OC4

/OC3

/OC2

/OC1

TEST3

TEST2

TEST1

TEST0

VDD

LPF

OSC2

VSS

64 17

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

■

0

1

2

3

4

5

6

7

8

DD

A

A

A

A

A

A

A

V

A

9

A

A

10

11

A

A

/CS

SS

V

MODE

Fig. 2 UHC124 LQFP 64-pin package (top view)

OSC1

TransDimension Inc. - Proprietary

4

Page 12

TransDimension Inc. UHC124 Data Sheet

1.4 Abbreviations

The following are some abbreviations used in this document.

API Application Programming Interface

CM Control Memory

DM Data Memory

FSBT Full Speed Bit Time

HC Host Controller

HCD Host Controller Driver

HCFS Host Controller Functional State

ISR Interrupt Service Routine

OHCI Open Host Controller Interface

PLL Phase Locked Loop

RTOS Real Time Operating System

SOF Start of Frame

UHCI Universal Host Controller Interface

XD Transaction Descriptor

TransDimension Inc. - Proprietary

5

Page 13

TransDimension Inc. UHC124 Data Sheet

2. System Overview

The UHC124 is a low-cost, high-performance, non-PCI USB host controller with unique, patentpending features that are indispensable for achieving high data throughput and low interrupt

rates. It is the only one on the market that is designed from the ground up for embedded

applications with full USB specification compliance. It is optimized for cost, performance and

ease of development. The software/hardware co-designed architecture enables high performance

while maintaining simplicity and flexibility that are critical for embedded applications. It can be

interfaced to CISC or RISC microprocessors, microcontrollers, or digital signal processors

(DSPs) and is ideal for providing USB host functions to a wide range of applications including

mobile devices, cell phones, PDAs, point-of-sale systems, test equipment, set-top boxes, Internet

appliances, as well as serving as an interface for USB to Bluetooth controllers.

TransDimension offers complete solutions using the UHC124 including development kits,

embedded USB host software and UHCI software interfaces to various real time operating

systems optimized for the UHC124. The complete solutions offer the advantages of shortened

time-to-market, simplified procurement and technical support from one source.

In the following, it is assumed that the reader has basic knowledge of microprocessor based

systems, as well as USB Specification 1.1. References to specific chapters and sections of USB

Specification 1.1 are cited in a pair of brackets. For instance, [9.3:183, 11.16:266] refers to “9.3

USB Device Request” on page 183, and “11.16 Requests” on page 266 of USB 1.1 Specification.

2.1 Interface with MCUs

UHC124 may be interfaced with a microprocessor-based system using either one of the two

following methods:

• For MCUs with standard external data buses, UHC124 can be interfaced directly via 8 bits of

its data bus and 12 bits of its address bus. When UHC124 operates under this mode, its

internal memory blocks, as well as its control/status registers, are mapped into the

processor’s address space.

• For MCUs without an external data bus, UHC124 may be interfaced using an 8-bit output

port and an 8-bit bi-directional port. Under this mode, a built-in, auto incrementing address

register allows accessing to a large block of UHC124 memory with a single (address) write

cycle, followed by as many read/write cycles as the number of data bytes to be transferred

from/to the UHC124.

Careful design of both hardware and software interfaces may allow a MCU with external data

buses to take advantage of UHC124’s auto-incremented addressing. See Section 9 for details.

2.2 Control Memory and Transaction Descriptors

The 256 bytes of Control Memory (CM) are evenly divided into 16 sections, each of which (16

bytes) specifies a Transaction Descriptor (XD) holding the following control information for a

USB transaction:

TransDimension Inc. - Proprietary

6

Page 14

TransDimension Inc. UHC124 Data Sheet

• Targeted USB device address (0-127) and endpoint number (0-15)

• Transaction type (SETUP, IN, or OUT)

• Starting address of the data block in UHC124 data memory

• Number of bytes to be transferred

• Whether the transaction is targeted to an isochronous endpoint

• Speed (data rate) of the targeted USB device

• Data sequence DATA0/1 (for an OUT transaction)

Upon completion of a transaction, the XD contains information about:

• Transaction status (Ack, Nak, Stall, Timeout, Error, or Overflow)

• Data sequence (for an IN transaction)

• Number of bytes actually transferred (for an IN transaction)

The sixteen XDs are hereafter referred to as XD0, XD1, …, XD9, XDA, XDB, …, XDE, and XDF.

2.3 Batch Processing

The Host Controller Driver (HCD) may organize up to 16 USB transactions into a transaction

batch, or simply a batch. A batch may contain transactions for full-speed (FS: 12 Mbit/sec) and

low-speed (LS: 1.5 Mbit/sec) USB devices, of four types of endpoints (control, bulk, interrupt

and isochronous) and all transaction types (SETUP, IN and OUT).

a USB transaction

Token Packet Data Packet Handshake Packet

t

XD2

ISO:IN:1023

XD3

BULK:OUT:64

XD8

SETUP

XDC

INT:IN:2

XDD

INT:IN:1

t

Fig. 3 USB transaction and UHC124 transaction batch

For instance, five transactions are grouped together to form a transaction batch (Fig. 3) with

• an isochronous, IN transaction of 1,023 bytes for real time imaging via XD

• a full speed, bulk OUT transaction of 64 bytes for a printer via XD

• a SETUP transaction sent to a low speed device via XD

• a low speed, IN interrupt transaction for a keyboard via XD

• a full speed, IN interrupt transaction for a hub via XD

;

8

; and

C

.

D

;

3

;

2

TransDimension Inc. - Proprietary

7

Page 15

TransDimension Inc. UHC124 Data Sheet

(XD)

(XD)

(XD)

(XD)

Compared with other USB host controller designs, batch processing is a very important and

unique feature of UHC124. Our software/hardware co-design solves the serious shortcomings of

other embedded USB host controller designs that generate an interrupt upon completion of every

USB transaction. These naïve designs:

• result in significant loss of USB bus bandwidth since the invocation (interrupt latency time)

and execution of the interrupt service routine (ISR), (or of certain portion of the ISR at the

minimum,) cannot overlap with USB bus activity. This problem is more obvious and

damaging when data packet sizes are small, which is typical for many USB applications,

making double buffering impractical.

• waste MCU’s time due to processor/RTOS overhead for ISR invocation and execution.

With its batch processing capability, a single register write to the UHC124 can dispatch

altogether up to 16 transactions, and a single interrupt is generated only after the completion of

all of them. The system throughput is therefore significantly improved maximizing the

bandwidth on the USB. At the same time, the number of interrupts to the MCU is greatly

reduced, saving processor resources for non-USB activities.

Before a batch is dispatched, a set of XDs must be allocated. Such a XD, designated for a

transaction, must then be specified (See Section 10). The batch is dispatched under the control

of user software (see Section 5 for details). XDs in a batch are processed by the UHC124 in

sequence - the one with the lowest index is processed first.

Multiple batches may be dispatched and processed by the UHC124 within a single USB frame (1

ms ± 0.5 µS). For easy programming, UHC124 allows transactions to spill over the USB frame

boundaries - if transactions scheduled for a batch cannot be completed in the current frame, they

will be transparently attempted following a hardware-generated Start of Frame (SOF).

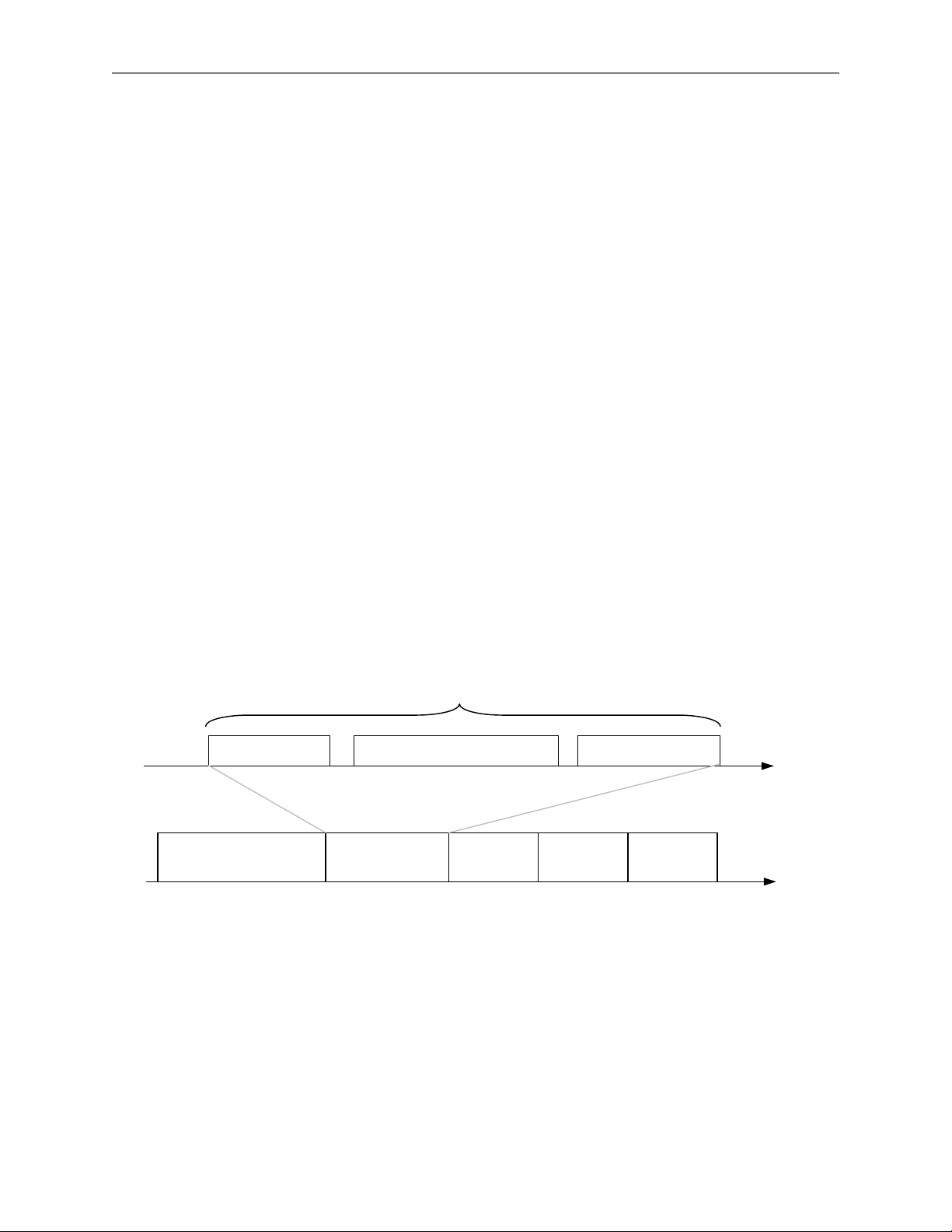

A transaction batch involving XD0, XD1, XD4, and XDC

XACT

XACT

SOF

XACT

XACT

t

Fig. 4 Transactions in a batch “spill over” the boundary of a USB frame

The Host Controller Driver (HCD) may use the UhcMaxOverhead Register (see Section 5) to

limit the number of transactions in a frame to any number, giving user the flexibility of spreading

multiple transactions over several frames using a single batch.

The HCD, however, should take careful consideration of the total time required for a scheduled,

yet to be dispatched transaction batch, as well as on the real time remaining in the current frame,

if frame sensitive isochronous and interrupt transactions are present in the embedded application.

TransDimension Inc. - Proprietary

8

Page 16

TransDimension Inc. UHC124 Data Sheet

Instructions will be given in Section 10 on how to calculate time required for a single

transaction, and that for a batch of multiple transactions.

2.4 Data Memory

The 2,048 bytes of data memory (DM) built into the UHC124 serve as data buffers shared

between the MCU and USB system. Unless the data packet is known to be of zero length, a

block of DM of proper size must be allocated for the transaction. The starting address and the

length of this memory block (in bytes) must be specified in the XD.

For a SETUP or OUT transaction, data must be written into this allocated buffer area before the

transaction can be dispatched along with a batch. For an IN transaction, on the other hand, data

will become available after the transaction is completed, provided that no exceptions occurred

during transaction processing, where an exception is a device Stall, device Nak, Timeout, or data

transfer Error as defined in USB Specification [8.5:162].

2.5 Double Buffering

Double buffering, and its more general form circular buffering, are effective ways to maximize

the USB system throughput. Note that UHC124 supports dual port memory access to its entire

addressing space (control registers, CM and DM). Together with its batch processing capability,

double buffering becomes attractive even for transactions with small data packets.

XD0

XD

4

XD

XD

1

Cluster

5

Cluster

XD

XD

1

C

XD7

Fig. 5 Double buffering of two XD clusters

Depending on the application, user software may organize XDs into two or more XD clusters.

USB transactions associated with a cluster are dispatched as a batch. In Fig. 5 two XD clusters

are employed for double buffering. Note that a XD (XD1) is included in more than one cluster.

While one batch for Cluster A is being processed by the UHC124, another batch for Cluster B is

dealt by user software by which completed transactions are processed, and new ones prepared.

Once the batch for Cluster A is completed, the user software enables the batch for Cluster B.

In the presence of isochronous transfers, XD clusters must be scheduled in such a way that each

USB frame contains exactly one transaction for each active isochronous endpoint. Under the

circumstance, a XD cluster must not take longer than approximately 950 µS on the USB bus.

TransDimension Inc. - Proprietary

9

Page 17

TransDimension Inc. UHC124 Data Sheet

For UHC124, the software overhead involved to swap two operating XD clusters is minimum –

only one 16-bit register (UhcTransSelect) and an 8-bit register (UhcControl) need to be updated.

See Section 5 for descriptions on these registers.

2.6 Interrupt to MCU

Under user software control, the UHC124 may generate an interrupt (active low) to the MCU

upon any one of the following conditions and/or events:

• Root hub port status change

• Batch completion (i.e., all transactions in the batch have been processed)

• Batch stop. Software may elect to stop a batch after a transaction if:

- any one of the transactions in the batch is successfully completed;

- any one of the transactions in the batch fails (device Stall, Timeout or data/packet Error);

or

- the targeted USB device has returned a Nak for any one of the transactions in the batch

• Host controller error

• Start of frame

The first three conditions provide flexibility to balance required high data throughput and the

demand on MCU resources. All five interrupt sources can be masked.

2.7 Root Hub

The UHC124 employs a fully qualified, market proven 4-port USB hub, AT43312A by Atmel

Corp., (San Jose, CA) as its root hub. USB transceivers are built-in for all four downstream

ports. Technical details for the root hub are given in Section 7.

2.8 External Crystal/Oscillator

A PLL (Phase Locked Loop) is integrated on-chip to generate, from a single 6 MHz crystal or

crystal oscillator, the 48 MHz, 12 MHz and 6 MHz clock signals required by UHC124 internal

circuitry minimizing EMI. Section 9 gives instructions to construct a working oscillator circuit

as well as an external compensating RC network for the internal PLL.

2.9 About UHCI and OHCI

UHC124 is fully compliant with USB Specification 2.0 (for full speed and low speed operation).

However, it is not UHCI/OHCI because it is not intended for the PCI bus. OEMs may develop

or license, a HCD providing a software interface that appear to the rest of the USB host stack as

if there were a UHCI or an OHCI compliant host controller.

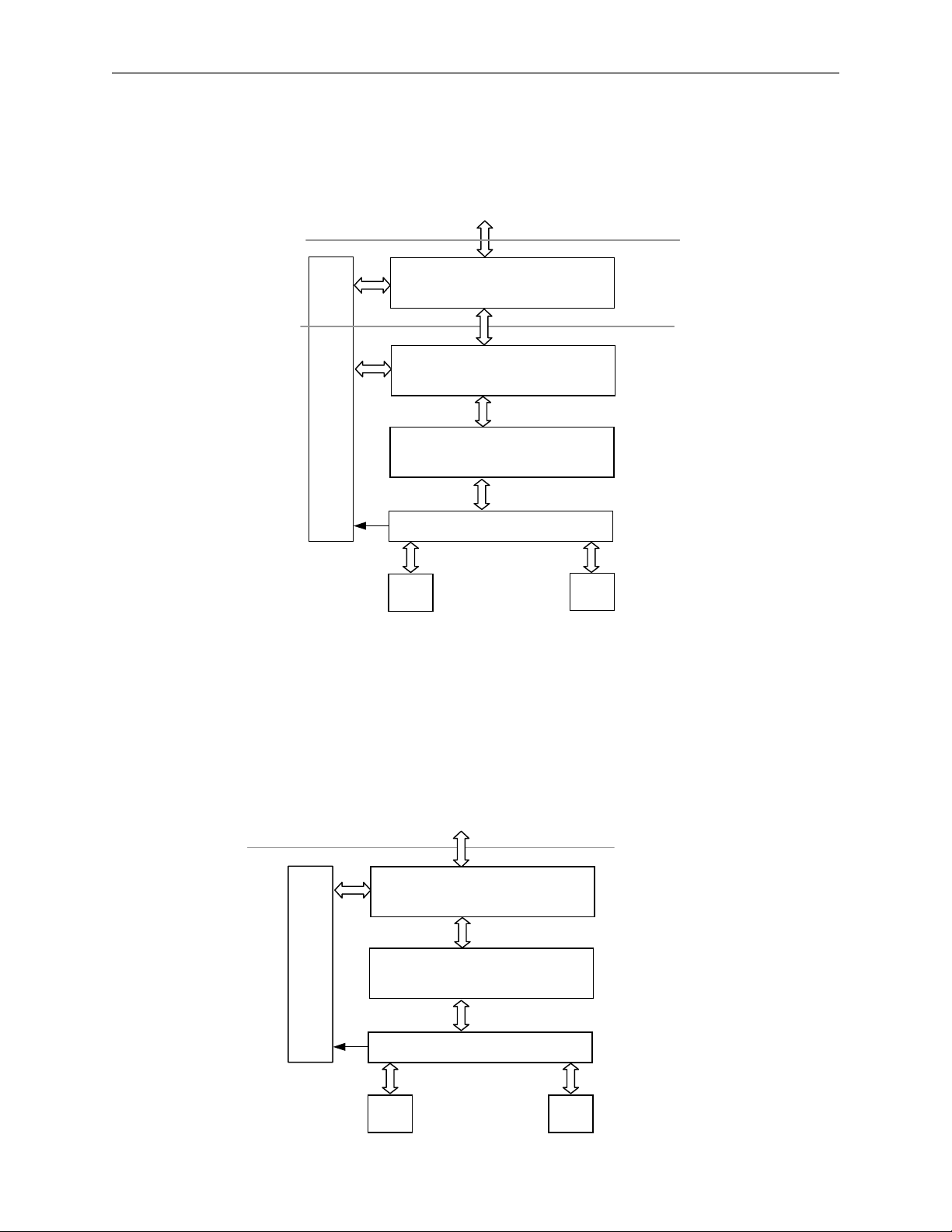

In Fig. 6, a carefully crafted USB host engine “steals” a small fraction of the MCU’s time, to

support UHCI/OHCI operation. The UHCI support for the UHC124 is readily available from

TransDimension. Please contact sales@transdimension.com for OCHI support.

TransDimension Inc. - Proprietary

10

Page 18

TransDimension Inc. UHC124 Data Sheet

USB host software (USBD, etc)

Higher Level

HCDI

HCD for OHCI/UHCI

(UHC124 independent)

UHCI/OHCI

Simulated OHCI/UHCI

(UHC124 dependent)

USB Host Engine

UHC124 Interface

(MCU specific)

/INT

UHC124

USB Devices

…

Fig. 6 Software interface compatible to UHCI/OHCI

2.10 USB Host API

OEMs may license from TransDimension an OS-independent UHC124 Programming Interface

Library, supporting direct UHC124 operation and efficient USB host control independent of any

RTOS. This solution is attractive for embedded systems with dedicated USB devices. Note that

OEMs may have to write device drivers using functions in this library.

USB device driver(s)

(MCU independent)

USBD and HCD

USBDI:

API (specified by

TransDimension)

(MCU specific)

UHC124

USB Host Engine

UHC124 Interface

/INT

USB Devices

…

TransDimension Inc. - Proprietary

11

Page 19

TransDimension Inc. UHC124 Data Sheet

Fig. 7 Embedded USB host application written with UHC124 Programming Interface Library

2.11 RTOS Support

Many modern RTOS’ (real time operating system) are now supporting USB host operation with

their own USB host stacks. TransDimension has made the UHC124 working under several

widely used RTOS’, WinCE, VxWorks, Linux, etc., and on various hardware platforms

(X86/ISA, Arm, StrongArm, MIPs, etc.) Developers should be aware that under the situation, it

is in principle the responsibility of the chosen RTOS to provide various USB device drivers

(such as the one for HID devices).

2.12 System Suspend and Resume

Under the control of user software, the UHC124 may bring the USB system into suspend state,

as dictated by USB 1.1 specification [7.1.7.4:122]. While the oscillator for UHC124 is still

running, all USB bus activities, including SOF generation, are stopped. The system may be

brought out of the suspend state by HCD software, or by a remote wakeup [9.2.5.2: 181]

originated from a downstream USB device.

2.13 Power Saving State

Under the control of user software, the UHC124 may enter the power saving state, in which all

internal clocks are stopped, and the PLL is disabled. A small quiescent current (about 200 µA) is

consumed by the UHC124. Reactivating the system requires a master reset or a power on reset.

See Section 8.6 for details.

TransDimension Inc. - Proprietary

12

Page 20

TransDimension Inc. UHC124 Data Sheet

3. Signal Definitions

Abbreviations of signal types:

I = Input

O = Output

B = Bi-directional

V = Power supply, ground

3.1 Oscillator and PLL

Name Type Pin No. Description

OSC1 I 17 Oscillator Input: input to the inverting oscillator amplifier.

OSC2 O 18

LPF I 19

3.2 MCU Interface

Name Type Pin No. Description

A11:A0 I 13:2 Address Bus: A11(pin 13) selects CM or DM.

D7:D4

D3:D0

B

53:50

47:44

/CS I 15 Chip Select: active low.

/WR I 55 Memory Write Strobe: active low.

/RD I 56 Memory Read Strobe: active low.

MODE

I

14

Oscillator Output: output of the inverting oscillator

amplifier.

PLL Filter: connecting to a passive RC network; see Section

9 on proper usage of this pin.

Data Bus: D7 is the most significant bit.

Memory Access Mode.

MODE = 1: Non-multiplexed memory access. D

7:D0

are

connected to the MCU’s data bus, A11:A0 to its address bus;

MODE = 0: Multiplexed memory access with autoincremented address. When accessing a block of UHC124

memory, the 12-bit starting address is first latched into the

chip by writing the least significant 8-bits of the address into

D7:D0 while holding ADS high, and placing the most

significant 4-bits of the address on A

. Data is then

11:A8

retrieved out of, or stored into UHC124 memory with

successive read or write operations through D7:D0, while pin

ADS is pulled low. The memory address is automatically

incremented internally for each subsequent memory access.

A7:A0 are not used under this mode.

TransDimension Inc. - Proprietary

13

Page 21

TransDimension Inc. UHC124 Data Sheet

ADS

I

62

Address/Data Select: see discussion on signal MODE; When

MODE = 1, this pin has no effect, and it should be tied to

VSS for noise immunity.

/INT O 61 Interrupt: generated for microprocessor; active low.

/RESET I 54 Master Reset: resets entire USB system; active low.

GNDP I 63

Voltage Reference: for built-in power on reset (POR),

connect to V

(ground) for normal operation.

SS

3.3 USB Root Hub Ports

Name Type Pin No. Description

DP1

DP

2

DP3

DP4

DM1

DM2

DM3

DM4

/OC1

/OC2

/OC3

/OC4

/PO1

/PO2

/PO3

/PO4

B

B

I

O

34

37

39

41

35

Port Data for USB I/O:

DP1:DP4 and DM1:DM4 are the differential signal pairs to

connect downstream USB devices [7.1:107].

38

40

42

25

26

27

28

29

30

31

32

Over Current Indicator: input signal to indicate to the root

hub that over current is detected at the port; active low. If

/OCn is asserted, the root hub will de-assert /POn, and report

the status in the root hub’s port status register.

Power On Switch: output signal to turn on the external

voltage supplying power to a port; active low. /POn is deasserted when a power supply problem is detected at /OCn,

where n is 1, 2, 3, or 4.

3.4 Test Modes

Name Type Pin No. Description

TMS3:

TMS0

TEST4:

TEST

0

I 60:57

B

43,

24:21

Test Mode Select: used only for factory testing; connect to

VSS for normal operation.

Test Signal I/O: used only for factory testing; working in

output mode during normal operation, they must be left

floating.

3.5 Power and Ground

Name Type Pin No. Description

VDD V

VSS V

1,20

33,48

16,36

49, 64

3.3V Power Supply. All four pins must be connected.

Ground. All four pins must be connected.

TransDimension Inc. - Proprietary

14

Page 22

TransDimension Inc. UHC124 Data Sheet

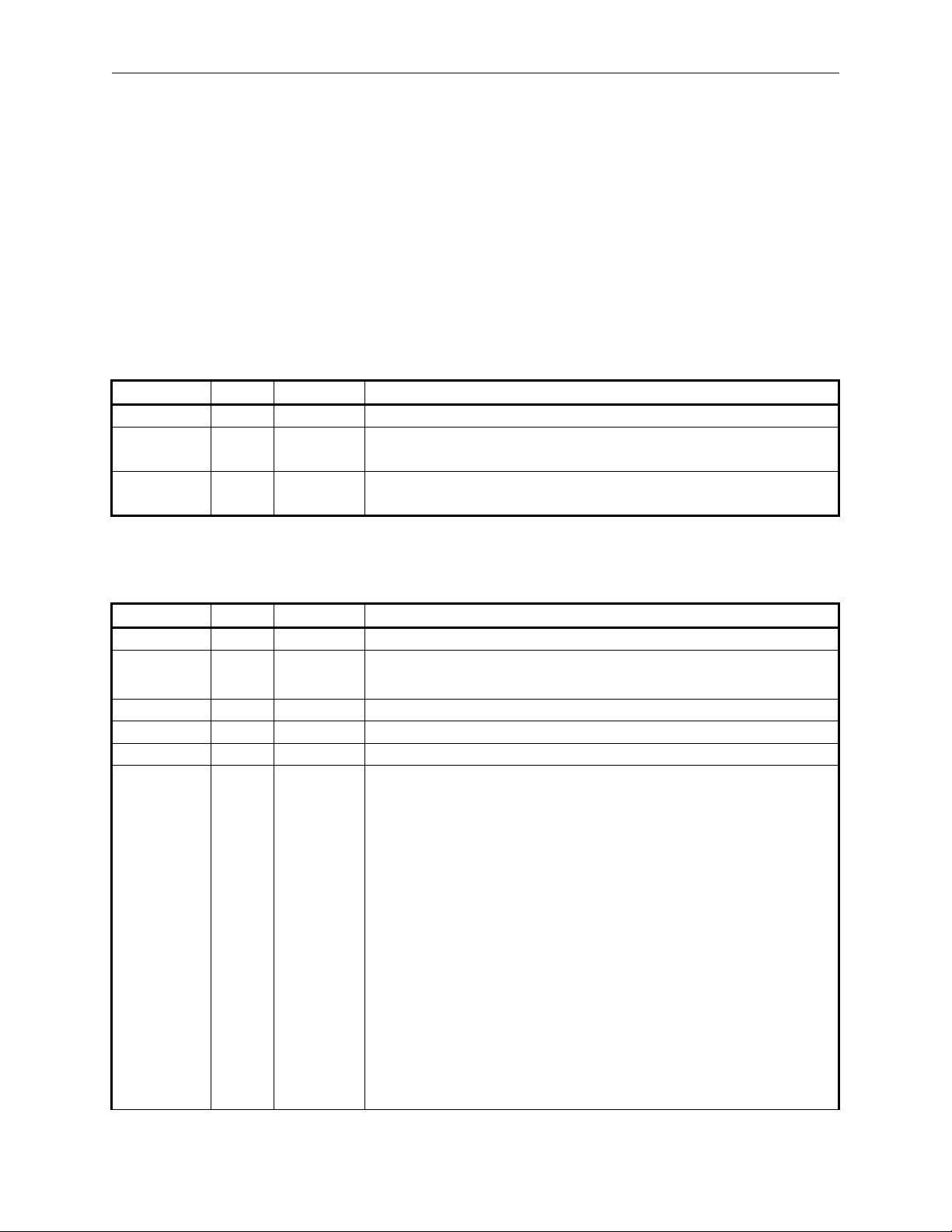

4. Memory Map

The UHC124’s control memory (CM), data memory (DM), and its registers are organized into a

4 kB block, which, at the developer’s discretion, may be mapped into a MCU’s memory space.

000H

00FH

010H

3FFH

400H

4FFH

500H

6FFH

700H

7FFH

800H

FFFH

Fig. 8 UHC124 memory map (memory block sizes not to scale)

Reading from a location in a reserved segment of UHC124 addressing space returns 00H, while

writing to such a location has no effect.

Note that the MCU and UHC124’s control circuitry share the entire addressing space of the

UHC124. An arbitration mechanism inside the chip allows dual port access.

The lowest 16 bytes of this addressing space are system control/status registers described in

detail in the next section.

Control Registers (16 bytes)

Reserved

Control Memory (CM, 256 bytes) for

16 Transaction Descriptors (XDs),

each of which is 16 bytes.

Reserved

Magic Reset (used only for factory

test).

Data Memory (DM, 2048 bytes)

TransDimension Inc. - Proprietary

15

Page 23

TransDimension Inc. UHC124 Data Sheet

5. Control Registers

5.1 Overview

This section discusses UHC124 control registers:

• UhcControl 000-001H system level control

• UhcTransSelect 002-003H batch transaction select

• UhcTransDone 004-005H transaction status check

• UhcIntpStatus 006H interrupt status report

• UhcIntpEnable 007H interrupt enable/disable

• UhcFmInterval 008-009H frame interval

• UhcFmRemaining 00A-00BH frame remaining

• UhcFmNumber 00C-00DH frame number

• UhcMaxOverhead 00EH maximum frame overhead

• UhcMagicNumber 00FH chip/version id, port status change

5.2 UhcControl Register

This register defines the operating states of the UHC124, and is used by the HCD to issue

commands such as to initiate a soft reset, to dispatch a transaction batch, and to bring the

UHC124 from one host controller functional state (HCFS) to another.

Setting (writing a ‘1’ to) a specific bit of the UhcControl register is a command to the UHC124,

whereas writing a 0 to that bit has no effect. A total of seven commands can be applied to the

UHC124 through this register:

• PowerSave write ‘1’ to Bit 7 enter power save state

• SoftReset write ‘1’ to Bit 5 soft reset

• USBReset write ‘1’ to Bit 4 USB system reset

• USBSuspend write ‘1’ to Bit 3 enter suspend state

• USBResume write ‘1’ to Bit 2 resume from suspend state

• USBOperational write ‘1’ to Bit 1 enter operational state

• BatchOn write ‘1’ to Bit 0 dispatch a transaction batch

Writing to register UhcControl (000H) with multiple bits set to ‘1’, (such as 06H whose bit

pattern contains two 1’s,) introduces ambiguity and/or inconsistency into the system, and is

therefore ignored by the UHC124.

Moreover, only a valid command under the current HCFS is accepted by the UHC124. For

instance, command USBResume does not make sense unless the USB system is currently

suspended. See Section 8 on HCFS definitions and valid state transitions.

TransDimension Inc. - Proprietary

16

Page 24

TransDimension Inc. UHC124 Data Sheet

Developers should be aware that since the clocks for the MCU are in general not synchronized

with that of UHC124’s, a command takes up to 167 ns to become effective.

Reading the register retrieves the UHC124’s current HCFS:

OWERSAVE Bit 7 Power saving state (always read 0)

• P

• U

SBRESET Bit 4 USB system reset in progress

• USBSUSPEND Bit 3 system in suspend state

• USBRESUME Bit 2 system is resuming from suspend state

• USBOPERATIONAL Bit 1 system in normal operation state

• BATCHON Bit 0 a batch is being processed by UHC124

In the following, a word containing letters of mixed upper and lower cases, such as

USBSuspend, is a command issued to UHC124 (by writing a ‘1’ to some bit of UhcControl).

The very same word in upper case (small caps), such as USBSUSPEND, is the corresponding

HCFS that the system currently assumes, which is obtained by reading the UhcControl register.

In addition, HC denotes the Host Controller (UHC124), and HCD stands for Host Control

Driver, which is used interchangeably with phase “user software”.

Register Address: 000H (low byte)

001H (high byte)

Reset: Signals vary (see bit descriptions below)

Read/Write

Bit Default

HCD HC

Description

15:8 00H Reserved

7

0

R/W

R/W

PowerSave/ POWERSAVE:

When a ‘1’ is written into this bit, the UHC124 enters

OWERSAVE state immediately if the current state is

P

USBSUSPEND (see section 8.6 for more detailed steps).

The UHC124’s internal clocks are all stopped in

POWERSAVE state.

To exit the POWERSAVE state (i.e., to have the bit cleared),

MasterReset (/RESET) must be applied which restarts

clocks, and places the UHC124 in U

SBRESET state.

Since it is impossible to access memory or registers in the

POWERSAVE state, this bit is always 0 when read.

6 0 Reserved.

TransDimension Inc. - Proprietary

17

Page 25

TransDimension Inc. UHC124 Data Sheet

5

0

W

SoftReset:

This bit is set by the HCD to initiate a software reset, which

brings the UHC124 into U

initializes all UHC124 registers and state machines - except

UhcFmInterval, UhcFmNumber, UhcFmRemaining and

UhcMaxOverhead. A batch in progress will be aborted.

R

SBSUSPEND state. SoftReset

Unlike USBReset (Bit 4), SoftReset takes less than 200 ns

to accomplish, and it does not reset the root hub and all

downstream ports.

This bit is always 0 when read.

4

1

R/W

R/W

USBReset/USBRESET:

Setting this bit to 1 initializes all UHC124 registers, state

machines, the root hub and all downstream ports, regardless

of the UHC124’s current HCFS. The HCD must ensure that

the UHC124 remains in USBRESET state for a minimum of

50 ms per USB Specification 1.1 [10.2.8.1:214].

PowerOnReset (generated internally by the UHC124 when

power is applied to it the first time) and MasterReset

(/RESET pin) have almost the same effect as that of

USBReset, except that for PowerOnReset and MasterReset,

memory access is disabled during the first 12 ms.

This bit is cleared upon user issuing a SoftReset command,

or a USBOperational command.

TransDimension Inc. - Proprietary

18

Page 26

TransDimension Inc. UHC124 Data Sheet

3

0

R/W

R/W

USBSuspend/USBSUSPEND:

Setting this bit to ‘1’ while the UHC124 is in

SBOPERATIONAL state brings it to USBSUSPEND state,

U

which disables batch dispatching and SOF generation. This

in turn, in less than 5 ms, makes the root hub and connected

devices to enter their respective suspend state [7.1.7.4:122].

If there is a batch in progress, U

SBSUSPEND will be entered

after its completion.

Another way to bring UHC124 into USBSUSPEND state is

through SoftReset.

The UH124C is brought out of USBSUSPEND (to enter

USBRESUME) upon a RemoteWakeup originated by a

downstream USB device, or by the HCD issuing a

USBResume command.

It is also possible to exit from USBSUSPEND, and enter

USBOPERATIONAL directly by writing a ‘1’ into Bit 1 of the

UhcControl register. This method is effective when The

UHC124 remains in USBSUSPEND state for less than 3 ms,

and none of the devices, including the root hub, have yet

actually been suspended. A typical use of this feature is to

resume normal USB operation immediately following a

SoftReset.

This bit is cleared upon PowerOnReset, MasterReset, and

USBReset. It is set after SoftReset.

2

0

R/W

R/W

USBResume/USBRESUME:

When set to ‘1’ while the system is in USBSUSPEND, the

UHC124 enters U

SBRESUME state, in which batch

dispatching and SOF generation are still being disabled.

A RemoteWakeup from a downstream device while the

system is in USBSUSPEND will also cause the UHC124 to

enter USBRESUME automatically.

The system remains in U

SBRESUME state for about 20 ms

before it automatically falls into USBOPERATIONAL.

This bit is cleared upon PowerOnReset, MasterReset,

USBReset, and SoftReset.

TransDimension Inc. - Proprietary

19

Page 27

TransDimension Inc. UHC124 Data Sheet

1

0

R/W

R/W

USBOperational/USBOPERATIONAL:

Setting this bit to ‘1’ while the UHC124 is in USBRESET or

SBSUSPEND enters state USBOPERATIONAL, which enables

U

SOF generation and batch dispatching.

The user software may notice that the first batch dispatched

after entering U

SBOPERATIONAL may take longer time to

complete. This is because transactions in a batch cannot be

processed by the UHC124 until the first SOF is generated,

which may take up to 1 ms to occur.

Caution must be taken when USBOPERATIONAL is entered

directly from USBSUSPEND – it is possible that the system

has been in that state for longer than 3 ms, and some or all

of its connected devices have already entered their

respective suspend state. A transaction aimed to such a

(suspended) device will inevitably result in a transaction

TimeOut. This problem can be resolved automatically with

USB’s error recovery protocol [8.7:172].

This bit is cleared upon PowerOnReset, MasterReset,

USBReset, and SoftReset.

0

0

R/W

R/W

BatchOn/BATCHON:

Setting this bit to ‘1’ while the system is in

USBOPERATIONAL dispatches a transaction batch. It is reset

to 0 if any one of the following condition occurs:

1. All selected transactions have been processed;

2. A stop condition for a transaction, as specified in its XD,

is satisfied (see Bits StopOnSucc, StopOnNak, and

StopOnFail of XDControl in the next section).

3. Batch is aborted due to MasterReset, USBReset or

SoftReset.

This bit is cleared upon PowerOnReset, MasterReset,

USBReset, and SoftReset.

5.3 UhcTransSelect Register

Register Address: 002H (low byte)

003H (high byte)

Reset: PowerOnReset, MasterReset, USBReset and SoftReset.

TransDimension Inc. - Proprietary

20

Page 28

TransDimension Inc. UHC124 Data Sheet

This register is used to select a subset of transactions, out of 16 XDs in CM, to form a transaction

batch. XDn, located at 4n0H – 4nFH of the UHC124’s addressing space, is included in the batch

if Bit n of UhcTransSelect is set to ‘1’, where n = 0, 1, …, 9, A, …, E, F, in hex.

Note that once dispatched, transactions selected in a batch are processed by the UHC124, one at

a time, starting from the XD with the lowest index.

5.4 UhcTransDone Register

Register Address: 004H (low byte)

005H (high byte)

Reset: PowerOnReset, MasterReset, USBReset and SoftReset.

This register is used to monitor the progress of a transaction batch. If Bit n of UhcTransDone is

set by the UHC124, it indicates that the transaction associated with XDn has been processed.

UhcTransDone is cleared by the UHC124 as soon as a BatchOn command is issued to the

UhcControl register.

Upon completion or termination of a batch, Bit 0 of UhcControl is set back to ‘0’, the status of a

transaction involved in this batch, as far as its progressing status is concerned, can be derived

from information provided in UhcTransSelect and UhcTransDone:

Bit n of

UhcTransSelect

0 0

1

Bit n of

UhcTransDone

1

Transaction Status

Transaction associated with XDn was not

selected for the batch.

Transaction associated with XDn was selected

for the batch, and has been processed by the

UHC124. Status of the transaction is in

XDStatus of XDn. (See next section for

detailed discussion of XDs).

1

0

Two possibilities: (i) transaction associated

with XDn was selected for the batch, but has

not been processed; (ii) The batch stopped in

response to an anticipated outcome of an

earlier transaction. See description on XD

(next section) for details on batch stop

conditions.

0 1 System error (not suppose to happen).

5.5 UhcIntpStatus Register

Register Address: 006H

Reset: PowerOnReset, MasterReset, USBReset, and SoftReset.

TransDimension Inc. - Proprietary

21

Page 29

TransDimension Inc. UHC124 Data Sheet

This register reports the following system events and conditions that may cause an interrupt on

the /INT pin:

• BatchStopped Bit 7 batch stopped before all transactions are processed

• BatchCompleted Bit 6 all transactions in a batch have been processed

• HostError Bit 3 a host error occurred

• ResumeDetected Bit 2 entering U

SBRESUME state

• PortChange Bit 1 status change occurred on one of the root hub ports

• StartOf Frame Bit 0 start of a USB frame

A bit is asserted (set to ‘1’) as soon as the designated event occurs, or condition holds. User

software may acknowledge the event by writing a ‘1’ to the bit, which will have the bit cleared.

All bits will remain ‘1’ after asserted, and be cleared explicitly by user software (writing ‘1’ to

them). In addition, Bit 7 (BatchStopped) and Bit 6 (BatchCompleted) will also be automatically

cleared by UHC124 upon a BatchOn command applied to the UhcControl register.

Read/Write

Bit Default

7

0

HCD HC

R/W

W

BatchStopped:

This bit is set when a batch is stopped due to a software

anticipated stop condition that occurred as the result of a

transaction (Success, Nak, or Failure). See description on

Description

XDControl in the next section for details.

The UHC124 clears this bit automatically upon dispatching

of a new transaction batch.

6

0

R/W

W

BatchCompleted:

This bit is set when all selected XDs in a batch have been

processed.

The UHC124 clears this bit automatically upon dispatch of a

new transaction batch.

5:4 00 Reserved.

3

0

R/W

W

HostError:

This bit is set when the UHC124 detects a host controller

error – often caused by a transaction with an illegal data

packet that would take more than 1 ms to complete.

TransDimension Inc. - Proprietary

22

Page 30

TransDimension Inc. UHC124 Data Sheet

2

0

R/W

W

ResumeDetected:

This bit is set when the UHC124 enters USBRESUME state

(from U

SBSUSPEND) in response to a USBResume

command, or to a RemoteWakeup originated from a

downstream USB device.

1

0

R/W

W

PortChange:

This bit is set whenever there is a status change in the root

hub, or in any of its four downstream ports.

It is the responsibility of user software to identify the port

(or root hub itself) that has had the change (see description

on MagicNumber register), and to find out what happened.

The latter requires issuing of a hub class request to retrieve

the status of that port (or of the root hub).

0

0

R/W

W

StartOfFrame:

This bit is set by the UHC124 at the beginning of each USB

frame. The actual SOF packet is generated approximately

12 FSBT (approximately 1 µs) after the bit is asserted.

5.6 UhcIntpEnable Register

Register Address: 007H

Reset: PowerOnReset, MasterReset, USBReset, and SoftReset.

Bits in UhcIntpEnable have a one-to-one correspondence with those in UhcIntpStatus. A level

triggered interrupt is generated (pin /INT is pulled low) when any one of designated

events/conditions is reported by UIntpStatus, and the corresponding interrupt source is enabled

in UhcIntpEnable.

Setting ‘1’ to a bit of this register enables the corresponding interrupt source.

TransDimension Inc. - Proprietary

23

Page 31

TransDimension Inc. UHC124 Data Sheet

Read/Write

Bit Default

HCD HC

Description

7 0 R/W R BatchStopped Interrupt Enable.

6 0 R/W R BatchCompleted Interrupt Enable.

5:4 00 Reserved.

3 0 R/W R HostError Interrupt Enable.

2 0 R/W R ResumeDetect Interrupt Enable.

1 0 R/W R PortChange Interrupt Enable.

0 0 R/W R StartOfFrame Interrupt Enable.

5.7 UhcFmInterval Register

Register Address: Low byte: 008H

High byte: 009H

Reset: PowerOnReset, MasterReset, and USBReset.

The least significant 14 bits of the UhcFmInterval register determine the duration of a USB

frame in terms of its full speed (12 Mbit per second) bit times (FSBTs). This register can be used

to fine-tune the frame duration for certain applications.

Note that USB specification requires that the frame to be 1 ms ± 0.5 µs [7.1.12:126], which

translates to 12,000 ± 6 counts for the 12 MHz clock. Setting this register to a value out of this

range may cause compatibility problems for most USB devices, especially hubs. Moreover, user

software may not change the frame internal more than 1 FSBT during less than 6 frames. To

read/write from/to this register, user software must first read/write its LSB (008H), followed by

another read/write of its MSB (009H).

Read/Write

Bit Default

HCD HC

Description

15:14 Reserved

13:0

2EDFH

R/W

FrameInterval:

The register should be set to a value that is 1 less than the

number of FSBTs constituting the desired USB frame.

After a PowerOnReset, a MasterReset (/RESET pin) or a

R

USBReset, the register is default to 2EDFH (11,999 in

decimal), corresponding to a USB frame of 12,000

FSBTs, or exactly 1 ms.

If the register is updated by user software, the new value

will not take effect until the start of the next frame.

TransDimension Inc. - Proprietary

24

Page 32

TransDimension Inc. UHC124 Data Sheet

5.8 UhcFmRemaining Register

Register Address: 00AH (low byte)

00BH (high byte)

Reset: PowerOnReset, MasterReset, and USBReset.

This register is a 14-bit down counter, whose value can be read “on the fly” by user software to

determine the instantaneous time relative to the beginning of the current USB frame.

To read from this register, user software must first issue a read to its LSB (00AH), followed by

another one for the MSB (00BH).

Read/Write

Bit Default

HCD HC

Description

15:14 00 Reserved

13:0

000H

R

R/W

FrameRemaining:

The value of this register decrements once per full speed

bit time. It is reloaded with the value of UhcFmInterval

once it reaches 0. The frame boundary is the bit boundary

on which the value of this register changes from ‘0’ to that

of UhcFmInterval.

5.9 UhcFmNumber Register

Register Address: 00CH (low byte)

00DH (high byte)

Reset: PowerOnReset, MasterReset, and USBReset.

This register is an 11-bit counter, whose value is broadcast over the USB system riding SOF

packets.

While reading this register, the HCD must read the low byte (00CH) first.

Read/Write

Bit Default

HCD HC

Description

15:11 00000 Reserved.

10: 0

000H

R

R/W

FrameNumber:

The register is incremented by 1 at each frame boundary,

following which a SOF packet carrying the current frame

number is generated.

TransDimension Inc. - Proprietary

25

Page 33

TransDimension Inc. UHC124 Data Sheet

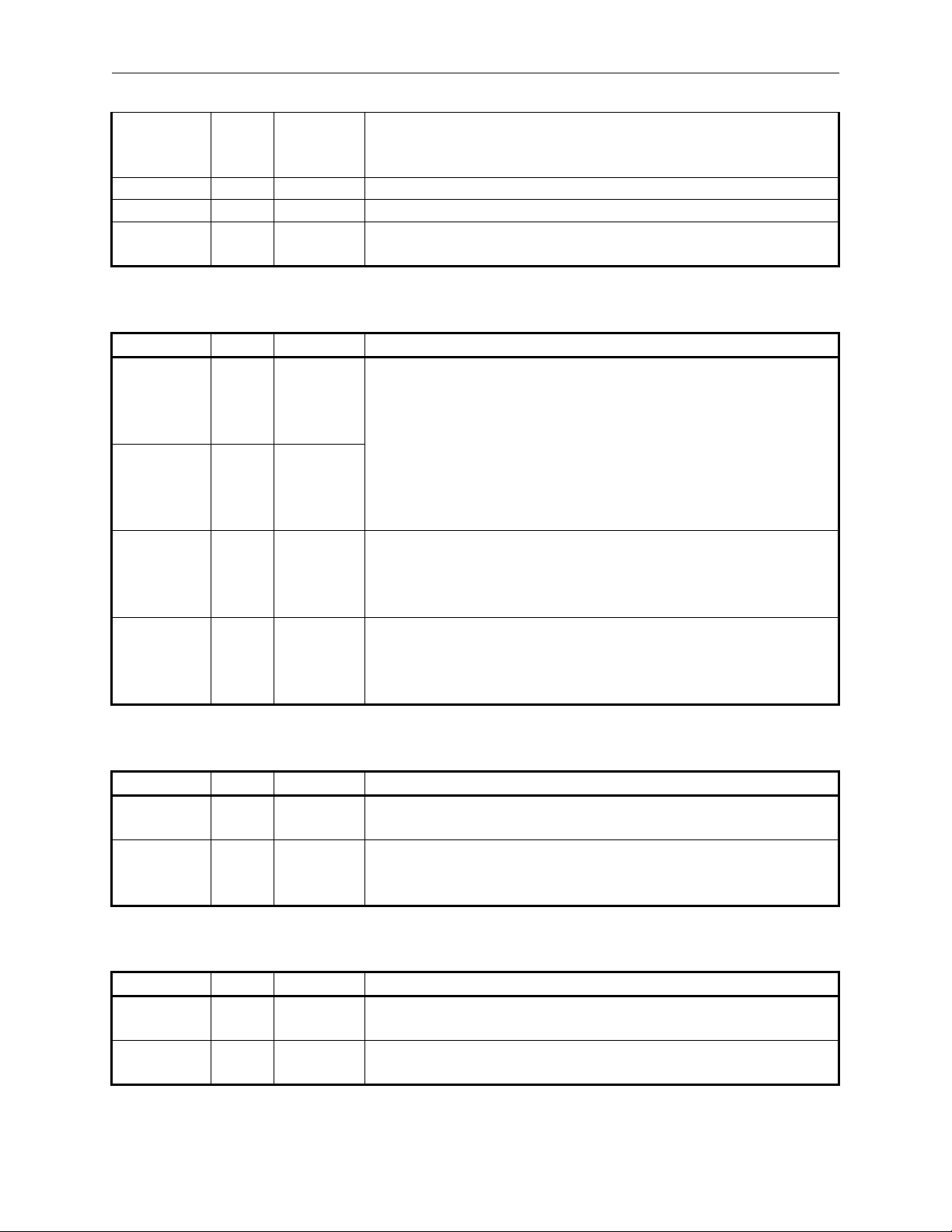

5.10 UhcMaxOverhead Register

Register Address: 00EH

Reset: PowerOnReset, MasterReset, and USBReset.

This register is used to fine-tune the time usable for USB transactions in a frame. As illustrated

in Fig. 9, USB transactions can only be carried out in a frame after the SOF packet, and before

EOF

. The value of UhcMaxOverhead ranges from 10 to 255. Setting the register to a value less

M

than 10 is not recommended.

Before a transaction is processed by the UHC124, user software may wish to estimate the time

required for the transactions to be successfully carried out, or timeout, before EOF

in the

M

current frame. If there is not enough time, some transactions will “spill over” to the next frame.

In other words, it will not be processed until after the next SOF packet.

12

SOF

~ 35

usable for

transactions

EOF

Max

Overhead

USB Frame (12,000 bit time: 1 ms)

EOF

35

t

in full speed

bit time (FSBT)

1 FSBT = 83.3 ns

Fig. 9 USB frame under UHC124 (time not to scale)

Read/Write

Bit Default

HCD HC

MaxOverhead:

Description

7: 0

C0H R/W

R

Number of USB Full Speed Bit Times (FSBTs) between

EOFM and EOF1 (10-255 decimal). See Fig. 9.

5.11 UhcMagicNumber Register

Register Address: 00FH

Reset: PowerOnReset, MasterReset, USBReset, and SoftReset.

This register is used to read the UHC124’s chip identification (DBH), as well as to retrieve

PortChange, i.e., which down stream port, or the root hub itself, has a status change. Operation

of UhcMagicNumber register is illustrated with the following state diagram:

TransDimension Inc. - Proprietary

26

Page 34

TransDimension Inc. UHC124 Data Sheet

)

)

RD (chip id) or

WR (not 55H)

RD [chip id] or

WR (not AAH)

WR (55H

WR (AAH

RD [port/hub status change] or

WR (anything)

Fig. 10 Operation of UhcMagicNumber register (00FH)

The following steps must be followed to read PortChange:

1. Read the register;

2. Write 55H to the register;

3. Write AAH to the register; and finally

4. Read the register - retrieving a byte containing PortStatusChange and HubStatusChange:

Read/Write

Bit Default

HCD HC

Description

7:5 000 Reserved.

PortStatusChange:

4:1

0000

R

W

Bit n is asserted if there has been a status change on Port n

of the root hub.

0

0

R

W

HubStatusChange:

Asserted if there has been a status change on the root hub.

Note that this byte reflecting port/hub status change is identical to that obtained through an IN

transaction via EP1, an IN interrupt endpoint, of the root hub [11.13.1:257]. An asserted status

change bit can be cleared only through a ClearPortFeature request as described in the USB

specification [11.13.2:257].

TransDimension Inc. - Proprietary

27

Page 35

TransDimension Inc. UHC124 Data Sheet

6. Transaction Descriptor

6.1 Overview

The 256 bytes of UHC124’s addressing space starting from 400H are reserved as Control

Memory (CM), which holds 16 transaction descriptors (XD) denoted as XD

XD

, …, XDF.

A

XD Location

XD0 400H - 40FH

XD1 410H - 41FH

XD2 420H - 42FH

XD3 430H - 43FH

XD4 440H - 44FH

XD5 450H - 45FH

XD6 460H - 46FH

XD7 470H - 47FH

XD8 480H - 48FH

XD9 490H - 49FH

XDA 4A0H - 4AFH

XDB 4B0H - 4BFH

XDC 4C0H - 4CFH

XDD 4D0H - 4DFH

XDE 4E0H - 4EFH

XDF 4F0H - 4FFH

Each XD consists of the following fields:

XDControl 1 byte @ offset 0 transaction control

XDStatus 1 byte @ offset 1 transaction status

XDDevAddress 1 byte @ offset 2 device address (0-127)

XDEndpoint 1 byte @ offset 3 endpoint number (0-15)

XDBufAddress 2 bytes @ offset 4 address of data area (800-FFFH)

XDBufLength 2 bytes @ offset 6 data length (0-1,023)

XDXferCount 2 bytes @ offset 8 number of bytes not transferred

Upon a BatchOn command, the XDs selected for the batch are loaded, one at a time, into the

chip’s USB Host Control Logic (Fig. 1), and processed. As long as the BATCHON bit of

UhcControl is set, the user software should not attempt to modify any selected, yet to be

processed XDs. See discussion on registers UhcTransSelect and UhcTransDone in the previous

section for details.

, XD1, XD2, …XD9,

0

TransDimension Inc. - Proprietary

28

Page 36

TransDimension Inc. UHC124 Data Sheet

6.2 XDControl

XD Offset: 0

XDControl contains information needed to process the transaction. It must be specified before

the transaction is dispatched along with a batch.

Bit Description

7

StopOnSucc:

When this bit is set, the current batch stops after the transaction of this

XD if the transaction has been successful.

For IN, this means that the device returns a data packet to the host with

no error. For SETUP and non-isochronous OUT, this means that the host

received an ACK from the device. For isochronous OUT, the transaction

is always considered successful after it is dispatched.

If the batch must be continued after this transaction, regardless of its

outcome, set Bits 7:5 to 000.

6

StopOnNak:

When this bit is set, the current batch stops after the transaction of this

XD if device has responded with a Nak.

5

StopOnFail:

When this bit is set, the current batch stops after the transaction

associated with this XD when one of following occurs:

• device has returned Stall;

• device has failed to respond within 18 bit times (Timeout); or

• there has been an Error in the packet returned by the device.

4

DevSpeed:

Data rate for the targeted device – 0: full speed (12 Mbits/sec); 1: low

speed (1.5 Mbits/sec).

3

Isochronous:

This bit is set to ‘1’ if the transaction is isochronous.

2

OutDataSeq:

Data sequence toggle for a non-isochronous, OUT transaction - 0:

DATA0; 1: DATA1 [8.6:168].

This bit is irrelevant for IN transactions. For SETUP or isochronous

OUT transactions, this bit should be set to ‘0’.

TransDimension Inc. - Proprietary

29

Page 37

TransDimension Inc. UHC124 Data Sheet

1:0

TransType:

Type of the transaction – 00: SETUP (host to device); 01: OUT (host to

device); 10: IN (device to host); and 11: reserved.

6.3 XDStatus

XD Offset: 1

The UHC124 returns the status of the transaction in this location of the XD after the transaction

is completed. User software may read this byte upon completion of the batch when B

ATCHON of

UhcControl is no longer asserted, or at the minimum, after this transaction is processed (To

determine whether a transaction in a batch has been processed, registers UhcTransSelect and

UhcTransDone must be consulted, see previous section for details.)

Bit Description

7 Reserved.

6

Stall:

This bit is asserted by the UHC124 as the result of a Stall packet received

from the endpoint of the USB device.

5

Error:

The bit is asserted by the UHC124 if during the transaction

• a CRC error occurred for the data packet of an IN transaction;

• a PID error occurred; or

• a corrupted packet (such as missed bit stuffing bits) is encountered.

4

Overflow:

This bit is set when the UHC124 receives more data from the device than

that specified in XDBufLength. Note that excessive data is truncated.

This bit is irrelevant for SETUP and OUT transactions.

3

Timeout:

This bit is set by the UHC124 as it fails to receive any response from the

device 18 bit times after the token packet in an IN transaction, or after

the device bounded data packet in a SETUP or OUT transaction.

2

Nak:

The bit is set if the UHC124 has received a Nak packet from the device

for this transaction.

TransDimension Inc. - Proprietary

30

Page 38

TransDimension Inc. UHC124 Data Sheet

1

InDataSeq:

This bit is set by the UHC124 for an IN transaction - 0: a DATA0 data

packet has been received; 1: a DATA1 data packet has been received.

It is irrelevant for OUT transactions.

0

Ack:

This bit is asserted if the UHC124 has received an Ack packet from the

device for a SETUP transaction, or a non-isochronous OUT transaction.

It is irrelevant for IN transactions and isochronous OUT transactions.

6.4 XDDevAddress

XD Offset: 2

Bit Description

7 Reserved.

6:0

DevAddress:

This is the 7-bit address of the USB device targeted by the transaction.

6.5 XDEndpoint

XD Offset: 3

Bit Description

7:4 Reserved.

3:0

Endpoint:

This is the 4-bit endpoint number of the USB device targeted by the

transaction.

TransDimension Inc. - Proprietary

31

Page 39

TransDimension Inc. UHC124 Data Sheet

6.6 XDBufAddress

XD Offset: 4 (low byte)

5 (high byte)

Bit Description

15:12 Reserved.

11:0

BufAddress:

This is the starting address of the data area allocated for the transaction.

The 12-bit address specified here is relative to 000H. (Thus a valid value

for the field must fall between 800H and FFFH.)

6.7 XDBufLength

XD Offset: 6 (low byte)

7 (high byte)

Bit Description

15:10 Reserved.

9:0

BufLength:

This is the length of the data (in bytes) for the transaction.

Note that for an IN transaction, the data packet may contain more data

than anticipated. In this case, the Overflow bit of XDStatus is asserted,

and the excessive data bytes are truncated. It is therefore recommended

to always employ here the size of the endpoint buffer for IN transactions,

even if it may not be completely filled.

For EP0, the size of the endpoint buffer is given in field

bMaxPacketSize0 of the device descriptor [9.6.1:196]; and for other

endpoints, it is presented to the host in field wMaxPacketSize of the

corresponding endpoint descriptor [9.6.4:203].

TransDimension Inc. - Proprietary

32

Page 40

TransDimension Inc. UHC124 Data Sheet

6.8 XDXferCount

XD Offset: 8 (low byte)

9 (high byte)

Bit Description

15:10 Reserved

9:0

XferCount:

This contains the result of a down counter in the USB Host Controller

Logic (Fig. 1). At the beginning of the transaction, the counter was

loaded with the value of XDBufLength. The counter is then decremented

by one for every byte transferred. If more bytes than that indicated by

BufLength are actually transferred, XferCount is set to zero, and the

Overflow bit in XDStatus is asserted.

The content of this down counter is copied to XferCount only after the

transaction is completed. Thus it may not be read “on the fly” while the

transaction is in progress. Moreover, XferCount is meaningful only for

IN transactions – it is always zero for SETUP and OUT transactions.

TransDimension Inc. - Proprietary

33

Page 41

TransDimension Inc. UHC124 Data Sheet

7. Root Hub

The UHC124 employs the AT43312A (by Atmel) as its root hub. It supports the following

standard descriptors: Device Descriptor, Configuration Descriptor, Interface Descriptor,

Endpoint Descriptor, and Hub Descriptor. Other supported standard requests and hub class

requests include ClearHubFeature, ClearPortFeature, GetBusState, GetHubDescriptor,

GetHubStatus, GetPortStatus, SetHubDescriptor, SetHubFeature, SetPortFeature. See USB

Specification 1.1 [11.16:266] for details.

7.1 Down Stream Ports

Each of the four downstream ports of the root hub can be connected to a full speed or a low

speed device. 15 kΩ pull-down resistors are required at DPn and DMn data lines (n = 1, 2, 3, or

4). To satisfy the impedance matching requirement, a 22 Ω resistor must be inserted between a

USB data line (DPn or DMn) and its corresponding pin at the Type A connector. See Fig. 13 in

Section 9 for a schematic description.

Per USB specification, the speed of the USB device attached to a downstream port is determined

at the time of enumeration, depending on which data line (DPn or DMn) is pulled high

[7.1.5:113].

If a port is connected to a low speed device, the root hub will not propagate any traffic to that

port unless it is prefixed with a preamble PID. However, low speed packets (following the

preamble PID) are propagated down stream to both low and full speed devices. A packet targeted

to a low speed device is placed on the bus four FSBT after the preamble PID [11.8.4:252].

7.2 Port Power Management

Over-current conditions can be detected on a per port basis, and be furnished to the UHC124’s

root hub through its /OCn pins (active low, n = 1, 2, 3 or 4). As soon as /OCn is asserted, the root

hub sets the PORT_OVER_CURRENT bit of the port’s status word and the

C_PORT_OVER_CURRENT bit of the port’s status change word [11.16.2.6:273], and at the

same time, the power to the offending port is turned off.

An external switching device is needed to perform the actual “turn-on” and “turn-off” (of the

power) for each port. Any type of switching device is acceptable as long as it has a sufficiently

low voltage drop even when the device connecting to the port absorbs full power. In its simplest

form, this switch can be a P-channel MOSFET, though power-switching ICs specially designed

for USB, such as TPS2044/2054 by TI and MIC2524/2527 by Micrel are recommended.

The USB specification requires that the voltage drop at the power switch and board traces be no

more than 100 mV. A good conservative maximum drop at the power switch itself should be no

more than 75mV. Careful design and selection of the power switch and PCB layout is required to

meet the specifications.

TransDimension Inc. - Proprietary

34

Page 42

TransDimension Inc. UHC124 Data Sheet

Each port has its own power control pin /POn (active low, n = 1, 2, 3 or 4), which is asserted only

when a SetPortFeature request with feature PORT_POWER is issued to the specific port. /POn is

de-asserted upon anyone of the following conditions:

1. PowerOnReset, MasterReset or USBReset;

2. Over current condition; or

3. Request of ClearPortFeature with feature PORT_POWER.

7.3 Root Hub as a USB Device

As a special case of a USB device, the UHC124 root hub has two endpoints: Endpoint 0 (EP0),

and Endpoint 1 (EP1). EP0 is used for root hub enumeration, for port manipulation, and for

retrieving information about its configuration and hub/port status. By definition, all transfers

to/from EP0 are control transfers, more specifically, standard USB requests and hub class