Page 1

T

1

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

Description

Dedicated to fulfilling the demanding requirements of

performance-conscious photographers, Transcend

proudly releases its Extreme Plus 600X CompactFlash

cards with Turbo MLC technology. With its amazing

performance, the Transcend 600x CompactFlash

memory card allows the professional photographers

and enthusiasts to get the most from your digital single

lens reflex (DSLR) camera. Users are guaranteed to

makes consecutive shooting and non-stop video

recording and share their digital artwork with the world!

G

C

F

F

6

6

0

0

0

0

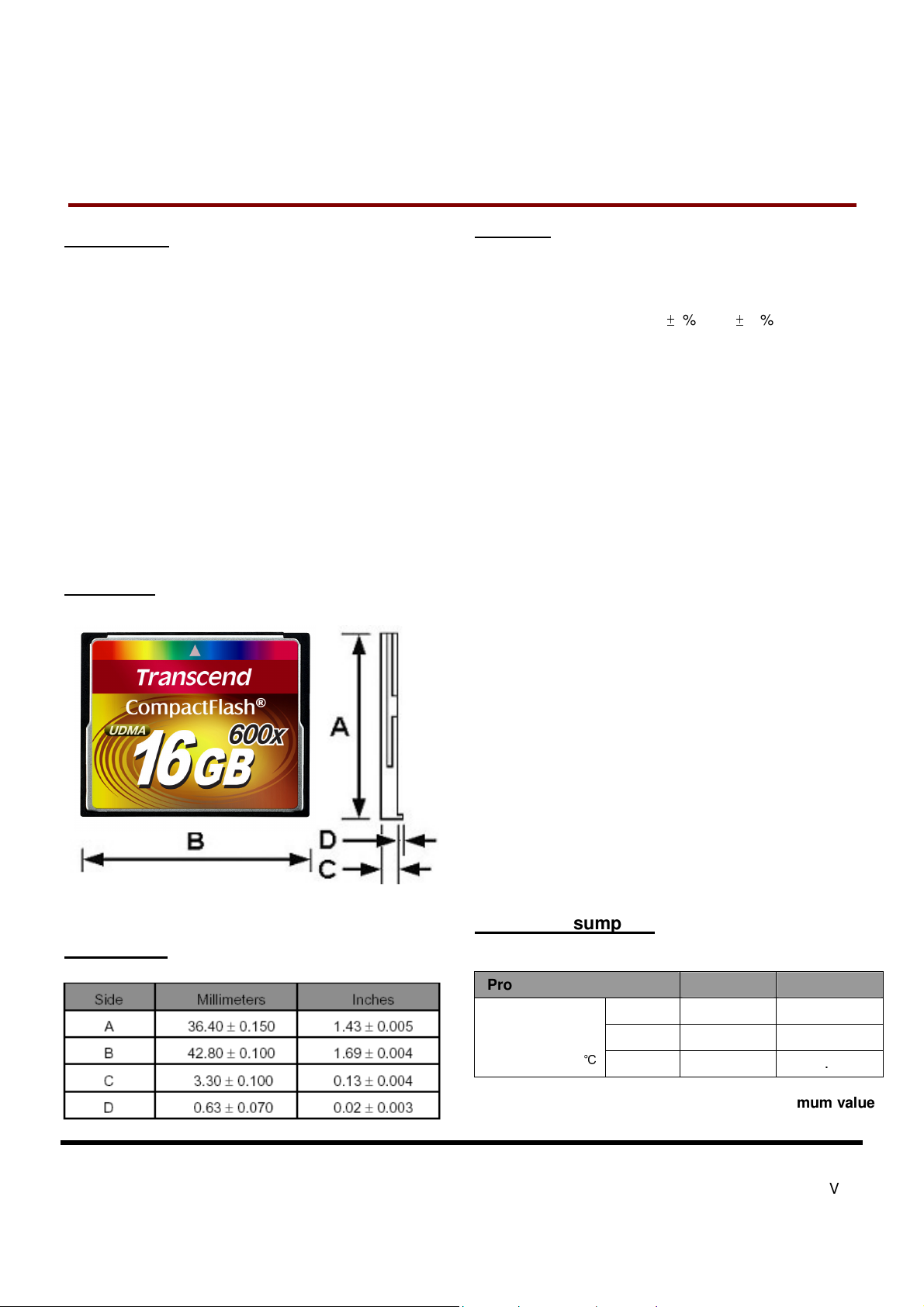

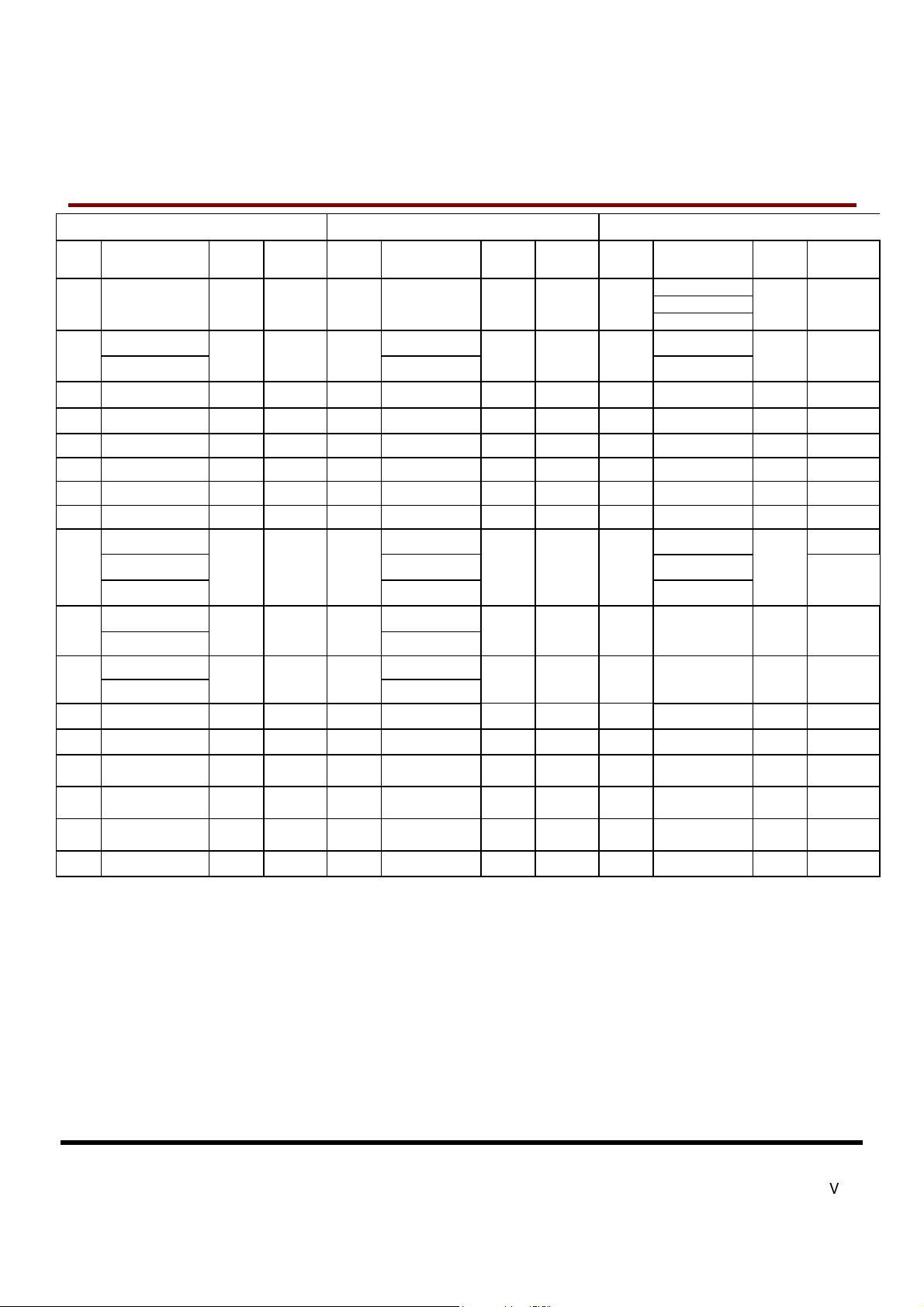

Placement

600X CompactFlash Card

Features

•

CompactFlash Specification Version 4.1 Complaint

•

RoHS compliant products

• Single Power Supply: 3.3V±5% or 5V±10%

•

Operating Temperature: -25oC to 85oC

•

Storage Temperature: -40oC to 85oC

•

Operating/ Storage Humidity: 5% to 95%

•

Operation Modes:

•

True IDE Mode supports:

•

PC Card Mode supports up to Ultra DMA Mode 6

PC Card Memory Mode

PC Card IO Mode

True IDE Mode

Ultra DMA Mode 0 to Ultra DMA Mode 6 (Ultra DMA

mode 5/6 must use Power supply: 3.3V)

MultiWord DMA Mode 0 to MultiWord DMA Mode 4

PIO Mode 0 to PIO Mode 6

Dimensions

Transcend Information Inc.

•

True IDE mode: Fixed Disk (Standard)

•

PC Card Mode: Removable Disk (Standard)

• Durability of Connector: 10,000 times

• Built-in 15 bit ECC (Error Correction Code) functionality

• Support Global Wear-Leveling to extend product life

• Compliant to CompactFlash, PC Card Mode, and ATA

standards

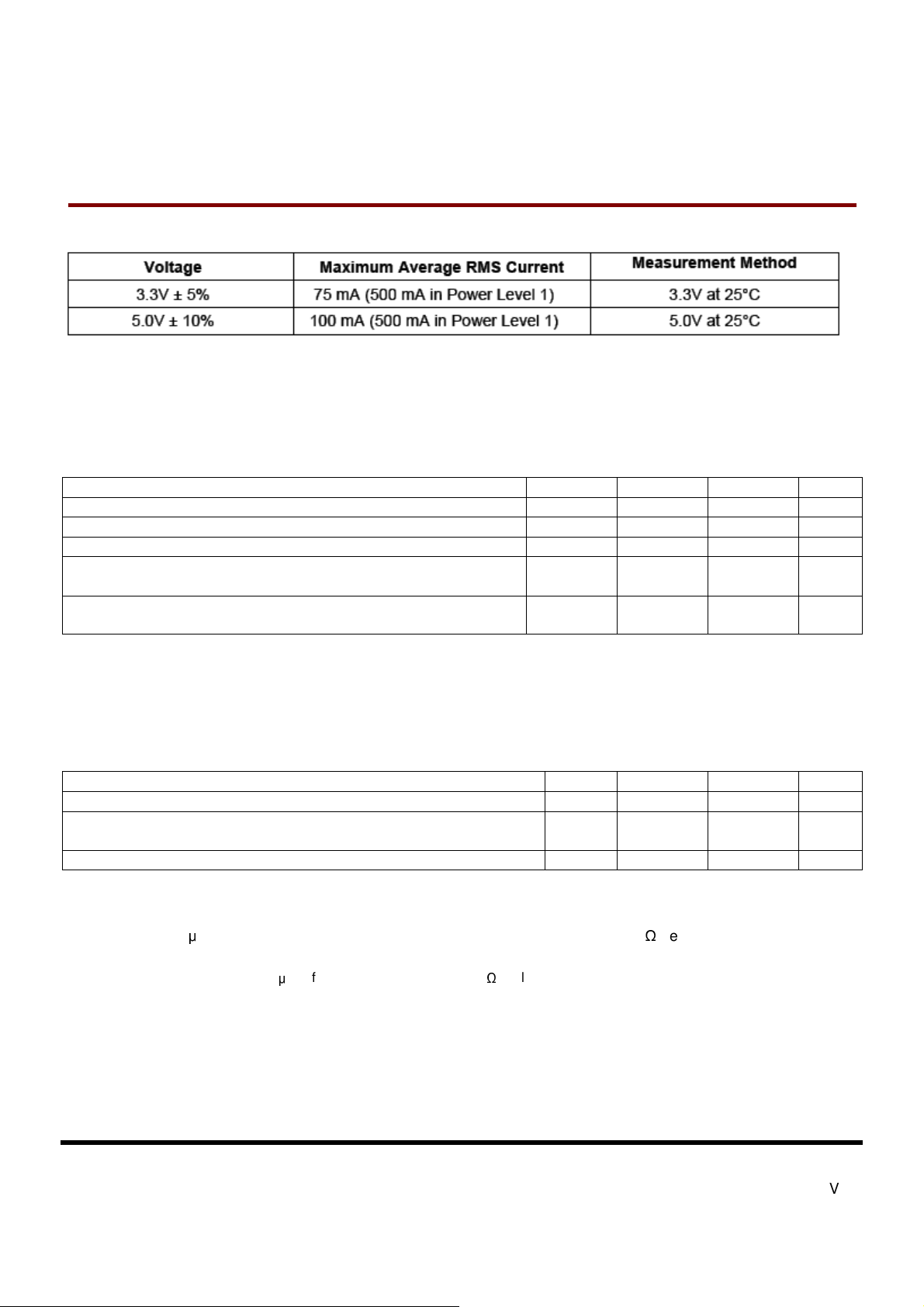

Power

Consumption

Product TS8GCF600 TS16GCF600

Power

Consumption

(DC 3.3V @25℃)

Standby

Read

Write

2.4mA 2.5mA

222.8mA 232.8mA

218.1mA 211.5mA

* Maximum value

V1.0

Page 2

T

2

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

G

C

F

F

6

6

0

0

0

0

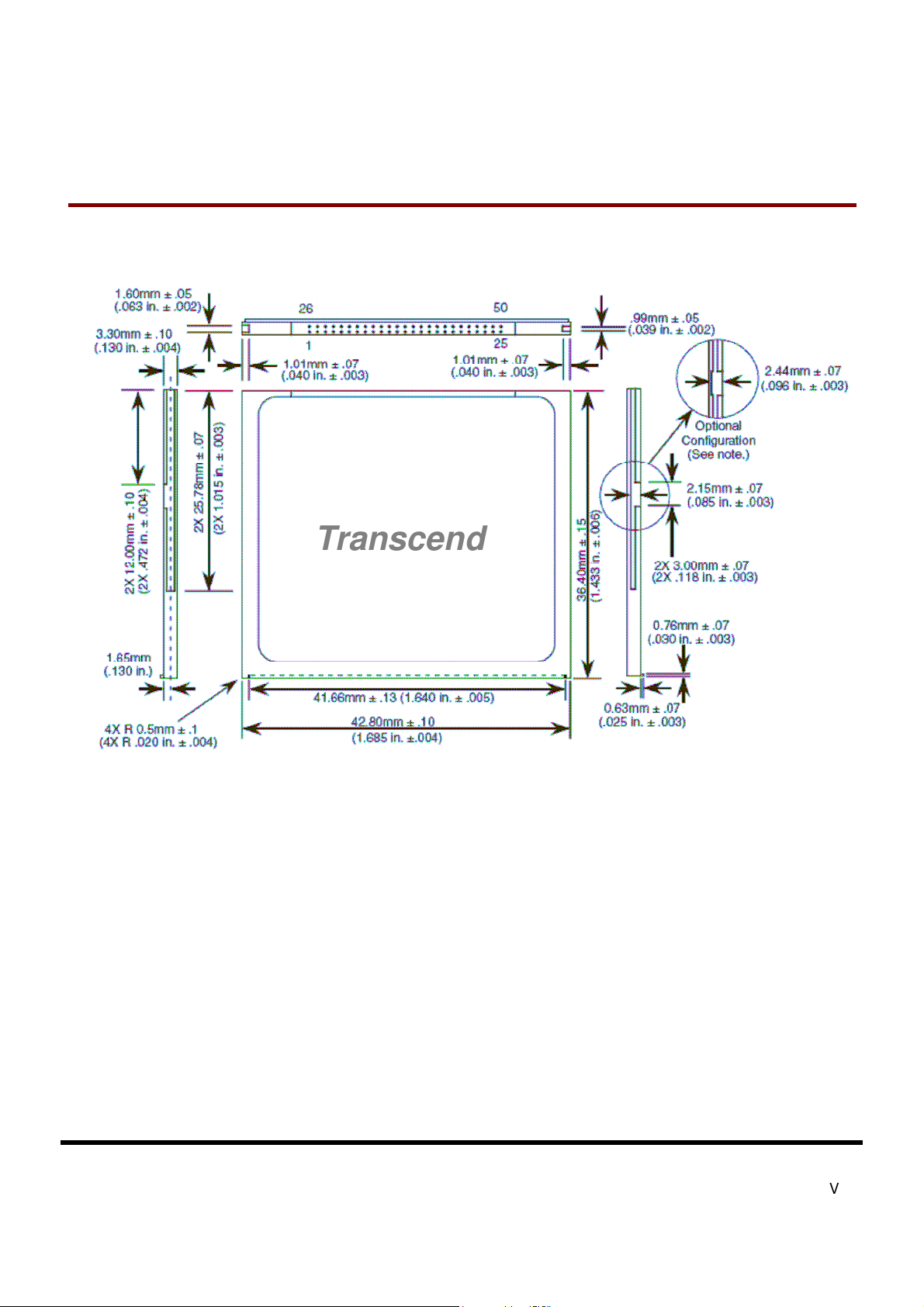

600X CompactFlash Card

Transcend

Transcend Information Inc.

V1.0

Page 3

T

3

S

8

G

~

1

6

G

T

S

8

G

8

G

~

~

T

S

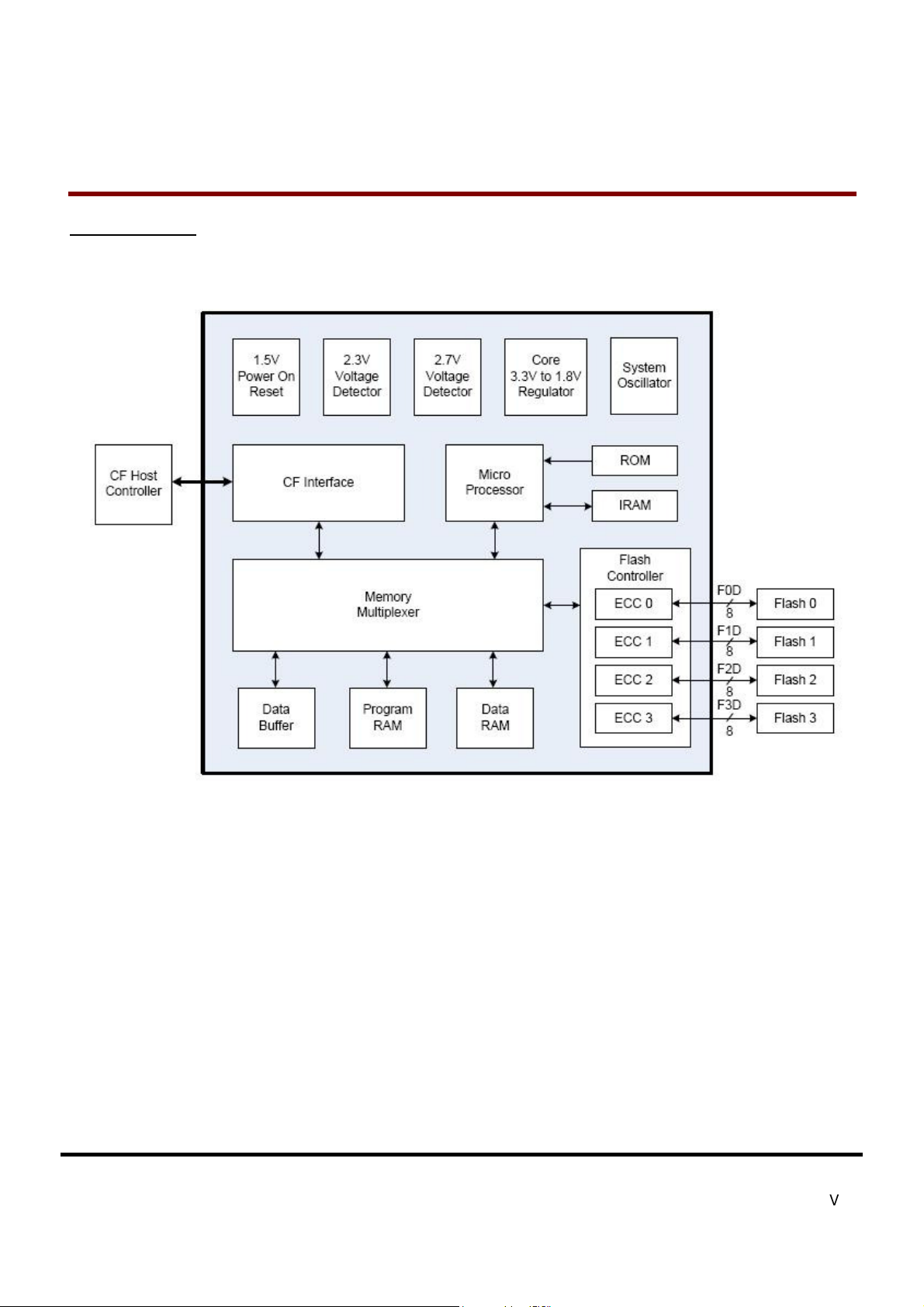

Block Diagram

1

1

6

6

G

G

C

C

C

F

F

F

6

6

6

0

0

0

0

0

0

600X CompactFlash Card

Transcend Information Inc.

V1.0

Page 4

T

4

T

T

S

S

S

8

8

8

G

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

C

C

F

F

F

6

6

6

0

0

0

0

0

0

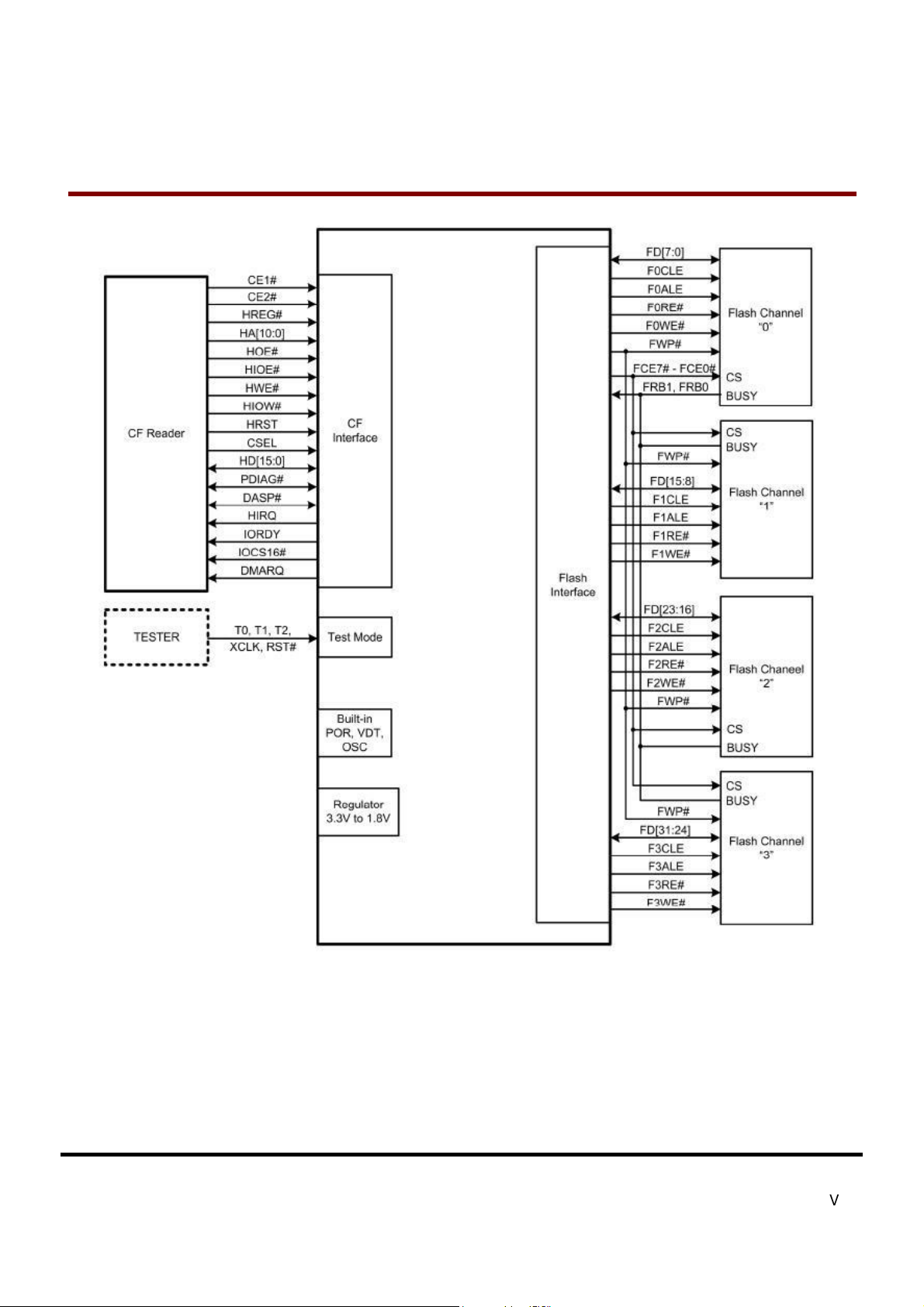

600X CompactFlash Card

Transcend Information Inc.

V1.0

Page 5

T

5

S

8

G

~

1

6

G

C

F

6

0

0

6

6

0

0

0

0

T

T

S

S

8

8

G

G

~

~

1

1

6

6

G

G

C

C

F

F

Pin Assignments and Pin Type

600X CompactFlash Card

PC Card Memory Mode

Pin

Num

1 GND

2 D03 I/O I1Z, OZ3 2 D03 I/O I1Z, OZ3

3 D04 I/O I1Z, OZ3 3 D04 I/O I1Z, OZ3

4 D05 I/O I1Z, OZ3 4 D05 I/O I1Z, OZ3

5 D06 I/O I1Z, OZ3 5 D06 I/O I1Z, OZ3

6 D07 I/O I1Z, OZ3 6 D07 I/O I1Z, OZ3

7 -CE1 I I3U 7 -CE1 I I3U 7 -CS0 I I3Z

8 A10 I I1Z 8 A10 I I1Z 8 A102 I I1Z

9 -OE I I3U 9 -OE I I3U 9 -ATA SEL

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

Signal

Name

Pin

Type

A09 I I1Z 10 A09 I I1Z 10 A092 I I1Z

A08 I I1Z 11 A08 I I1Z 11 A082 I I1Z

A07 I I1Z 12 A07 I I1Z 12 A072 I I1Z

VCC

A06 I I1Z 14 A06 I I1Z 14 A062 I I1Z

A05 I I1Z 15 A05 I I1Z 15 A052 I I1Z

A04 I I1Z 16 A04 I I1Z 16 A042 I I1Z

A03 I I1Z 17 A03 I I1Z 17 A032 I I1Z

A02 I I1Z 18 A02 I I1Z 18 A02 I I1Z

A01 I I1Z 19 A01 I I1Z 19 A01 I I1Z

A00 I I1Z 20 A00 I I1Z 20 A00 I I1Z

D00 I/O I1Z, OZ3 21 D00 I/O I1Z, OZ3 21 D00 I/O I1Z, OZ3

D01 I/O I1Z, OZ3 22 D01 I/O I1Z, OZ3 22 D01 I/O I1Z, OZ3

D02 I/O I1Z, OZ3 23 D02 I/O I1Z, OZ3 23 D02 I/O I1Z, OZ3

WP O OT3 24 -IOIS16 O OT3 24 -IOCS16

-CD2 O Ground 25 -CD2 O Ground

-CD1 O Ground 26 -CD1 O Ground

D111 I/O I1Z, OZ3 27 D111 I/O I1Z, OZ3 27 D111 I/O I1Z, OZ3

D121 I/O I1Z, OZ3 28 D121 I/O I1Z, OZ3 28 D121 I/O I1Z, OZ3

D131 I/O I1Z, OZ3 29 D131 I/O I1Z, OZ3 29 D131 I/O I1Z, OZ3

D141 I/O I1Z, OZ3 30 D141 I/O I1Z, OZ3 30 D141 I/O I1Z, OZ3

D151 I/O I1Z, OZ3 31 D151 I/O I1Z, OZ3 31 D151 I/O I1Z, OZ3

-CE21 I I3U 32 -CE21 I I3U 32 -CS11 I I3Z

-VS1 O Ground 33 -VS1 O Ground

In, Out Type Pin Num

Ground 1 GND

Power 13 VCC

PC Card I/O Mode

Signal

Name

Pin

Type

In, Out

Ground

Power

Type

True IDE Mode

Pin

Num

1 GND

2 D03 I/O I1Z, OZ3

3 D04 I/O I1Z, OZ3

4 D05 I/O I1Z, OZ3

5 D06 I/O I1Z, OZ3

6 D07 I/O I1Z, OZ3

13 VCC

25 -CD2 O Ground

26 -CD1 O Ground

33 -VS1 O Ground

Signal

Name

4

Pin

Type

O ON3

In, Out

Type

Ground

I I3U

Power

Transcend Information Inc.

V1.0

Page 6

T

6

S

T

S

T

S

Pin

Num

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

8

G

~

1

6

G

C

F

6

0

0

8

G

~

1

6

G

C

8

G

~

1

6

PC Card Memory Mode

Signal Name

-HIOE

HSTROBE

HDMARDY

-IOWR -IOWR -IOWR7

STOP

-WE I I3U 36 -WE I I3U 36 -WE3 I I3U

READY O OT1 37 -IREQ O OT1 37 INTRQ O OZ1

VCC Power 38 VCC Power 38 VCC Power

-CSEL5 I I2Z 39 -CSEL5 I I2Z 39 -CSEL I I2U

-VS2 O OPEN 40 -VS2 O OPEN 40 -VS2 O OPEN

RESET I I2Z 41 RESET I I2Z 41 -RESET I I2Z

-WAIT -WAIT IORDY7 ON1

-DDMARDY

DSTROBE11

-INPACK -INPACK

-DMARQ12

-REG I I3U 44 -REG

-DMACK

BVD2 O OT1 45 -SPKR O OT1 45 -DASP I/O I1U, ON1

BVD1 O OT1 46 -STSCHG O OT1 46 -PDIAG I/O I1U, ON1

D081 I/O

D091 I/O

D101 I/O

GND Ground 50 GND Ground 50 GND Ground

F

G

C

F

10

11

10,11

10

12

DMACK

6

0

0

6

0

0

Pin

Type

In, Out

Type

I I3U 34

I I3U 35

O OT1 42

O OT1 43

I1Z,

OZ3

I1Z,

OZ3

I1Z,

OZ3

PC Card I/O Mode

Pin

Num

Signal Name

-HIOE

HSTROBE10

-HDMARDY11

10,11

STOP

-DDMARDY10

DSTROBE

-DMARQ12

47 D081 I/O

48 D091 I/O

49 D101 I/O

12

Type

11

600X CompactFlash Card

Pin

In, Out

Type

I I3U 34

I I3U 35

O OT1 42

O OT1 43 DMARQ O OZ1

I I3U 44 -DMACK 6 I I3U

I1Z,

OZ3

I1Z,

OZ3

I1Z,

OZ3

Pin

Num

47 D081 I/O I1Z, OZ3

48 D091 I/O I1Z, OZ3

49 D101 I/O I1Z, OZ3

True IDE Mode

Signal Name

-HIOE7

HSTROBE8

-HDMARDY

8,9

STOP

-DDMARDY8

DSTROBE9

9

Pin

Type

I I3Z

I I3Z

O

4

In, Out

Type

OT113

Note: 1) These signals are required only for 16 bit accesses and not required when installed in 8 bit systems. Devices should allow for 3-state

signals not to consume current.

2) The signal should be grounded by the host.

3) The signal should be tied to VCC by the host.

4) The mode is required for CompactFlash Storage Cards.

5) The -CSEL signal is ignored by the card in PC Card modes. However, because it is not pulled upon the card in these modes,

it should not be left floating by the host in PC Card modes. In these modes, the pin should be connected by the host to PC

Card A25 or grounded by the host.

6) If DMA operations are not used, the signal should be held high or tied to VCC by the host. For proper operation in older hosts: while DMA

operations are not active, the card shall ignore this signal,including a floating condition

7) Signal usage in True IDE Mode except when Ultra DMA mode protocol is active.

8) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Write is active.

9) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Read is active.

10) Signal usage in PC Card I/O and Memory Mode when Ultra DMA mode protocol DMA Write is active.

11) Signal usage in PC Card I/O and Memory Mode when Ultra DMA mode protocol DMA Read is active.

12) Signal usage in PC Card I/O and Memory Mode when Ultra DMA protocol is active.

Transcend Information Inc.

V1.0

Page 7

T

7

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

Input Leakage Current

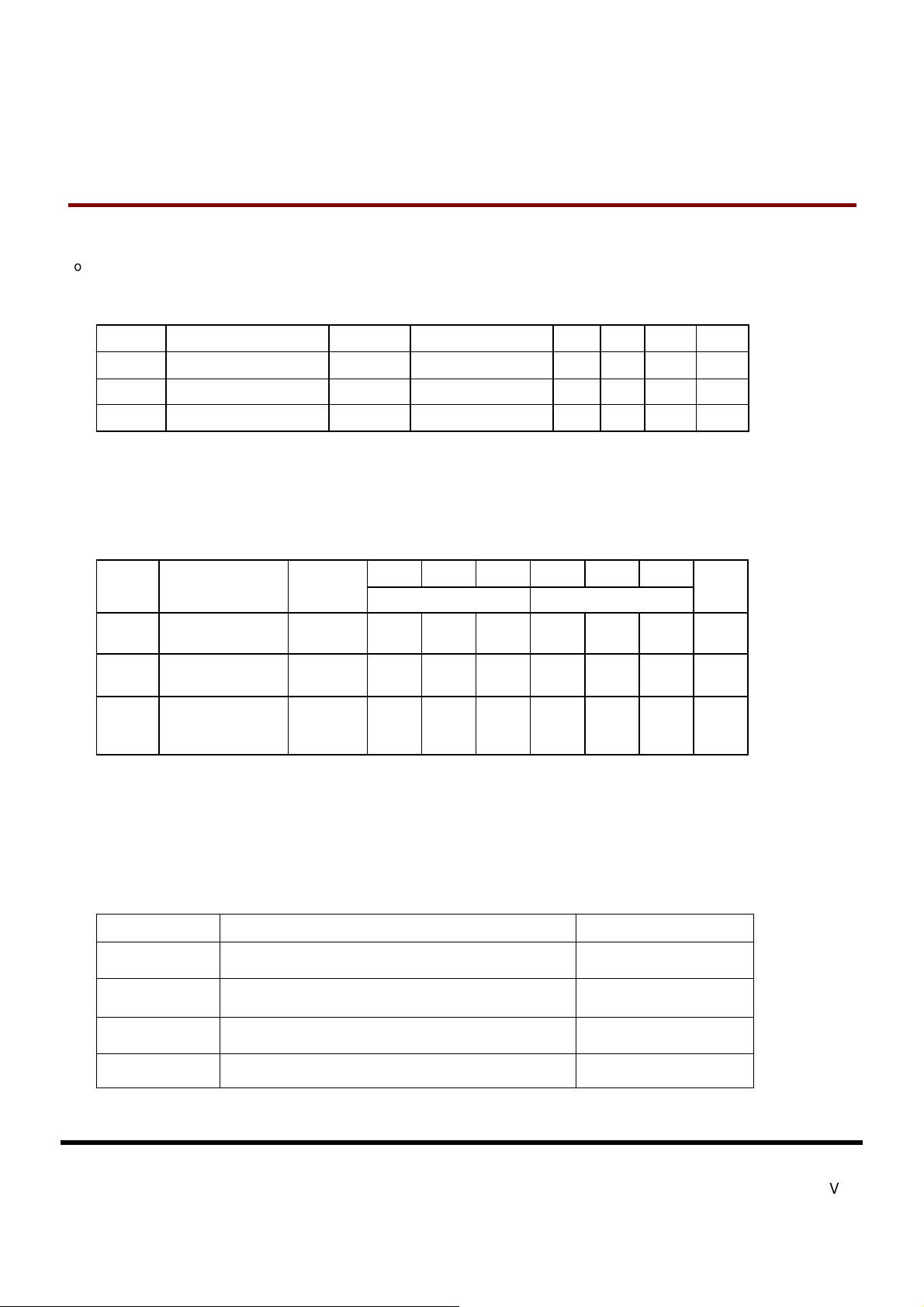

Note: In Table 1 below, x refers to the characteristics described in table 2. For example, I1U indicates a pull-up resistor with a type 1

input characteristic.

Type Parameter Symbol

IxZ Input Leakage Current

IxU Pull-Up Resistor RPU1 Vcc = 5.0V 50k

IxD Pull-Down Resistor RPD1 Vcc = 5.0V 50k

Note: The minimum pull-up resistor resistance meets the PCMCIA PC Card specification of 10k ohms but is intentionally higher in the

CompactFlash Specification to reduce power use.

Input Characteristics

Type Parameter

1

2

3

Notes: 1) The host provides a logic output high voltage for a CMOS load of .9 x VCC. For a 5 volt product, this translates to .9 x

4.5 = 4.05 volts minimum Voh.

F

G

C

F

Input Voltage

CMOS

Input Voltage

CMOS

Input Voltage

CMOS Schmitt

Trigger

6

6

0

0

0

0

600X CompactFlash Card

Table 1: Input Leakage Current

Conditions MIN TYP MAX Units

IL Vih = Vcc / Vil = Gnd -1

500k Ohm

500k Ohm

1 µA

Table 2: Input Characteristics

Symbol

Vih

Vil

Vih

Vil

Vth

Vtl

MIN TYP MAX MIN TYP MAX

VCC = 3.3 V VCC = 5.0 V

2.4

1.5

1.8

1.0

0.6 4.0

0.6 2.0

1

2.8

2.0

0.8

0.8

Units

Volts

Volts

Volts

Output Drive Type

Note: In Table 3 below, x refers to the characteristics described in Table 4. For example, OT3 refers to Totem pole output with a type

3 output drive characteristic.

Type

OTx Totempole Ioh & Iol

OZx Tri-State N-P Channel Ioh & Iol

OPx P-Channel Only Ioh Only

ONx N-Channel Only Iol Only

Transcend Information Inc.

Table 3: Output Drive Type

Output Type

Valid Conditions

V1.0

Page 8

T

8

S

8

G

~

1

6

G

C

F

6

0

T

S

8

G

~

1

6

G

T

S

8

G

~

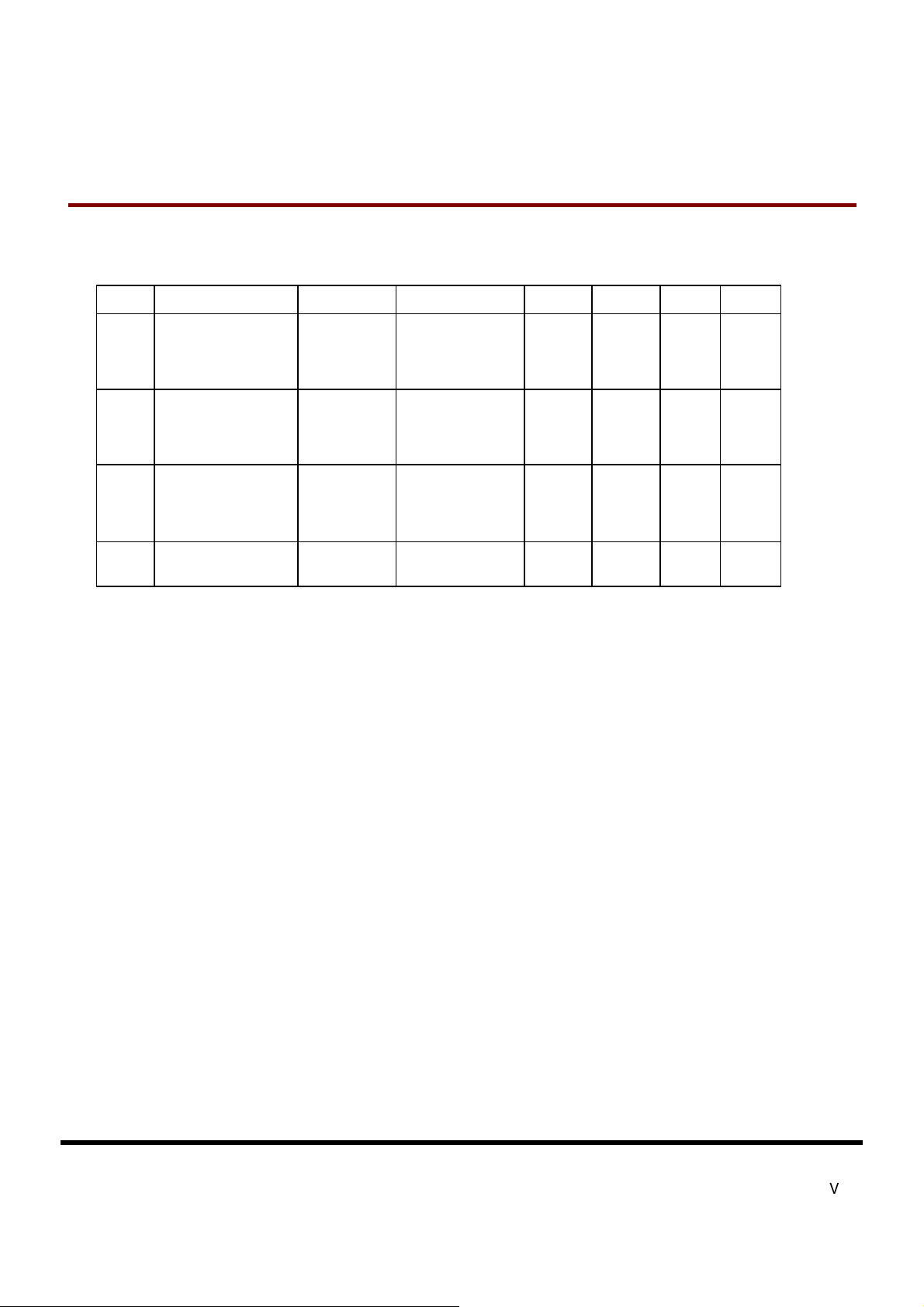

Output Drive Characteristics

Type

1 Output Voltage

2 Output Voltage

3 Output Voltage

X

C

1

6

G

C

Parameter

Tri-State Leakage

F

6

0

F

6

0

Current

0

0

0

600X CompactFlash Card

Table 4: Output Drive Characteristics

Symbol

Voh

Vol

Voh

Vol

Voh

Vol

Ioz

Conditions

Ioh = -4 mA

Iol = 4 mA

Ioh = -4 mA

Iol = 4 mA

Ioh = -4 mA

Iol = 4 mA

Vol = Gnd

Voh = Vcc

MIN

Vcc

-0.8V

Vcc

-0.8V

Vcc

-0.8V

-10

TYP MAX

Units

Gnd

+0.4V

Volts

Gnd

+0.4V

Volts

Gnd

+0.4V

10 µA

Volts

Transcend Information Inc.

V1.0

Page 9

T

9

select the following:

configuration control and status

READY and Write

Present signal in

CompactFlash Storage

S

8

G

~

1

6

G

C

6

G

G

C

C

F

F

F

T

T

S

S

8

8

G

G

~

~

1

1

6

Signal Description

6

6

6

0

0

0

0

0

0

600X CompactFlash Card

Signal Name

A10 – A00

(PC Card Memory Mode)

A10 – A00

(PC Card I/O Mode)

A02 - A00

(True IDE Mode)

BVD1

(PC Card Memory Mode)

-STSCHG

(PC Card I/O Mode)

Status Changed

-PDIAG

(True IDE Mode)

BVD2

(PC Card Memory Mode)

-SPKR

(PC Card I/O Mode)

-DASP

(True IDE Mode)

Dir.

I

I

I/O

I/O

Pin

8,10,11,12,

14,15,16,17,

18,19,20

18,19,20

46

45

Description

These address lines along with the -REG signal are used to

The I/O port address registers within the CompactFlash Storage Card , the

memory mapped port address registers within the CompactFlash Storage Card,

a byte in the card's information structure and its

registers.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode, only A[02:00] are used to select the one of eight registers

in the Task File, the remaining address lines should be grounded by the

host.

This signal is asserted high, as BVD1 is not supported.

This signal is asserted low to alert the host to changes in the

Protect states, while the I/O interface is configured. Its use is controlled by the

Card Config and Status Register.

In the True IDE Mode, this input / output is the Pass Diagnostic signal in the

Master / Slave handshake protocol.

This signal is asserted high, as BVD2 is not supported.

This line is the Binary Audio output from the card. If the Card does not support

the Binary Audio function, this line should be held negated.

In the True IDE Mode, this input/output is the Disk Active/Slave

the Master/Slave handshake protocol.

-CD1, -CD2

(PC Card Memory Mode)

-CD1, -CD2

(PC Card I/O Mode)

-CD1, -CD2

(True IDE Mode)

Transcend Information Inc.

O

26,25

These Card Detect pins are connected to ground on the

Card. They are used by the host to determine that the CompactFlash Storage

Card is fully inserted into its socket.

This signal is the same for all modes.

This signal is the same for all modes.

V1.0

Page 10

T

10

cate to the card

the host to PC

the host to PC

a Master or a

between the host

Byte of the Word. D08 is the LSB

on the low order

T

T

S

S

S

8

8

8

G

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

C

C

F

F

F

6

6

6

0

0

0

0

0

0

600X CompactFlash Card

Signal Name

-CE1, -CE2

(PC Card Memory Mode)

Card Enable

-CE1, -CE2

(PC Card I/O Mode)

Card Enable

-CS0, -CS1

(True IDE Mode)

-CSEL

(PC Card Memory Mode)

-CSEL

(PC Card I/O Mode)

-CSEL

(True IDE Mode)

Dir.

I

I

Pin

7,32

39

These input signals are used both to select the card and to indi

whether a byte or a word operation is being performed. -CE2 always accesses

the odd byte of the word.-CE1 accesses the even byte or the Odd byte of the

word depending on A0 and -CE2. A multiplexing scheme based on A0,-CE1,

-CE2 allows 8 bit hosts to access all data on D0-D7. See Table 27, Table 29,

Table 31, Table 35, Table 36 and Table 37.

This signal is the same as the PC Card Memory Mode signal.

In the True IDE Mode, -CS0 is the address range select for the task file

registers while -CS1 is used to select the Alternate Status Register and the

Device Control Register.

While –DMACK is asserted, -CS0 and –CS1 shall be held negated and the

width of the transfers shall be 16 bits.

This signal is not used for this mode, but should be connected by

Card A25 or grounded by the host.

This signal is not used for this mode, but should be connected by

Card A25 or grounded by the host.

This internally pulled up signal is used to configure this device as

Slave when configured in the True IDE Mode.

Description

D15 - D00

(PC Card Memory Mode)

D15 - D00

(PC Card I/O Mode)

D15 - D00

(True IDE Mode)

GND

(PC Card Memory Mode)

GND

(PC Card I/O Mode)

GND

(True IDE Mode)

I/O

--

Transcend Information Inc.

31,30,29,28,

27,49,48,47,

6,5,4,3,2,

23, 22, 21

1,50

When this pin is grounded, this device is configured as a Master.

When the pin is open, this device is configured as a Slave.

These lines carry the Data, Commands and Status information

and the controller. D00 is the LSB of the Even

of the Odd Byte of the Word.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode, all Task File operations occur in byte mode

bus D[7:0] while all data transfers are 16 bit using D[15:0].

Ground.

This signal is the same for all modes.

This signal is the same for all modes.

V1.0

Page 11

T

11

of

transfers between host

device when it is ready to transfer data to

handshake manner with

while the host is

is not selected in

PC Card and True

gates I/O data onto

Card when the card is configured to use

signal has the same

signal is asserted

in bursts.

rising and falling edge of HSTROBE

T

T

S

S

S

8

G

~

1

G

G

~

~

1

1

6

8

8

Signal Name

6

6

G

G

G

C

C

C

F

F

F

6

6

6

0

0

0

0

0

0

Dir.

Pin

600X CompactFlash Card

Description

-INPACK

(PC Card Memory Mode except

Ultra DMA Protocol Active)

-INPACK

(PC Card I/O Mode except Ultra

DMA Protocol Active)

Input Acknowledge

-DMARQ

(PC Card Memory Mode -Ultra

DMA Protocol Active)

-DMARQ

(PC Card I/O Mode -Ultra DMA

Protocol Active)

DMARQ

(True IDE Mode)

-HIOE

(PC Card Memory Mode except

Ultra DMA Protocol Active)

-HIOE

(PC Card I/O Mode except Ultra

DMA Protocol Active)

-HIOE

(True IDE Mode – Except Ultra

DMA Protocol Active)

-HDMARDY

(All Modes - Ultra DMA Protocol

DMA Read)

HSTROBE

(All Modes - Ultra DMA Protocol

DMA Write)

O

I

43 This signal is not used in this mode.

The Input Acknowledge signal is asserted by the CompactFlash Storage Card

when the card is selected and responding to an I/O read cycle at the address

that is on the address bus. This signal is used by the host to control the enable

any input data buffers between the CompactFlash Storage Card and the CPU.

Hosts that support a single socket per interface logic, such as for Advanced

Timing Modes and Ultra DMA operation may ignore the –INPACK signal from

the device and manage their input buffers based solely on Card Enable signals.

This signal is a DMA Request that is used for DMA data

and device. It shall be asserted by the

or from the host. For Multiword DMA transfers, the direction of data transfer is

controlled by -HIOE and -IOWR. This signal is used in a

(-)DMACK, i.e., the device shall wait until the host asserts (-)DMACK before

negating (-)DMARQ, and re-asserting (-)DMARQ if there is more data to

transfer.

In PCMCIA I/O Mode, the -DMARQ shall be ignored by the host

performing an I/O Read cycle to the device. The host shall not initiate an I/O

Read cycle while -DMARQ is asserted by the device.

In True IDE Mode, DMARQ shall not be driven when the device

the Drive-Head register.

While a DMA operation is in progress, -CS0 (-CE1)and -CS1 (-CE2) shall be

held negated and the width of the transfers shall be 16 bits.

If there is no hardware support for True IDE DMA mode in the host, this output

signal is not used and should not be connected at the host. In this case, the

BIOS must report that DMA mode is not supported by the host so that device

drivers will not attempt DMA mode operation.

A host that does not support DMA mode and implements both

IDE modes of operation need not alter the PC Card mode connections while in

True IDE mode as long as this does not prevent proper operation in any mode.

34 This signal is not used in this mode.

This is an I/O Read strobe generated by the host. This signal

the bus from the CompactFlash Storage

the I/O interface.

In True IDE Mode, while Ultra DMA mode is not active, this

function as in PC Card I/O Mode.

In all modes when Ultra DMA mode DMA Read is active, this

by the host to indicate that the host is ready to receive Ultra DMA dataThe host may negate – HDMARDY to pause an Ultra DMA transfer.

In all modes when Ultra DMA mode DMA Write is active, this signal is the data

out strobe generated by the host. Both the

cause data to be latched by the device. The host may stop generating

HSTROBE edges to pause an Ultra DMA data-out burst.

Transcend Information Inc.

V1.0

Page 12

T

12

Except

Except Ultra

operation and is held low when the card is

shall not cause the READY signal to remain continuously in

Interrupt Request. This line is

S

8

G

~

1

6

G

C

F

T

S

8

G

~

1

6

T

S

8

G

Signal Name

-IOWR

(PC Card Memory Mode–

Ultra DMA Protocol Active)

-IOWR

(PC Card I/O Mode –

DMA Protocol Active)

-IOWR

(True IDE Mode – Except Ultra

DMA Protocol Active)

STOP

(All Modes – Ultra DMA Protocol

Active)

-OE

(PC Card Memory Mode)

-OE

(PC Card I/O Mode)

-ATA SEL

(True IDE Mode)

READY

(PC Card Memory Mode)

-IREQ

(PC Card I/O Mode)

INTRQ

(True IDE Mode)

~

1

6

G

G

6

C

F

6

C

F

6

0

0

0

0

0

0

Dir.

I

I

O

Pin

35

9

37

600X CompactFlash Card

This signal is not used in this mode.

The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into

the CompactFlash Storage Card controller registers when the CompactFlash

Storage Card is configured to use the I/O interface.

The clocking shall occur on the negative to positive edge of the signal (trailing

edge).

In True IDE Mode, while Ultra DMA mode protocol is not active, this signal has

the same function as in PC Card I/O Mode. When Ultra DMA mode protocol is

supported, this signal must be negated before entering Ultra DMA mode

protocol.

In All Modes, while Ultra DMA mode protocol is active, the assertion of this

signal causes the termination of the Ultra DMA data burst.

This is an Output Enable strobe generated by the host interface. It is used to

read data from the CompactFlash Storage Card in Memory Mode and to read

the CIS and configuration registers.

In PC Card I/O Mode, this signal is used to read the CIS and configuration

registers.

To enable True IDE Mode this input should be grounded by the host.

In Memory Mode, this signal is set high when the CompactFlash Storage Card

is ready to accept a new data transfer

busy.

At power up and at Reset, the READY signal is held low (busy) until the

CompactFlash Storage Card has completed its power up or reset function. No

access of any type should be made to the CompactFlash Storage Card during

this time.

Note, however, that when a card is powered up and used with RESET

continuously disconnected or asserted, the Reset function of the RESET pin is

disabled. Consequently, the continuous assertion of RESET from the

application of power

the busy state.

I/O Operation – After the CompactFlash Storage Card Card has been

configured for I/O operation, this signal is used as strobed low to generate a pulse mode interrupt or held low for a level mode

interrupt.

In True IDE Mode signal is the active high Interrupt Request to the host.

Description

Transcend Information Inc.

V1.0

Page 13

T

13

Except

Except Ultra

High for Common Memory,

shall keep the

the

REG

shall ignore the

RESET pin is high with the

S

8

G

~

1

6

G

C

F

T

S

8

G

~

1

6

T

S

8

G

Signal Name

-REG

(PC Card Memory Mode–

Ultra DMA Protocol Active)

Attribute Memory Select

-REG

(PC Card I/O Mode –

DMA Protocol Active)

-DMACK

(PC Card Memory Mode when

Ultra DMA Protocol Active)

DMACK

(PC Card I/O Mode when Ultra

DMA Protocol Active)

-DMACK

(True IDE Mode)

~

1

6

G

G

6

C

F

C

F

6

6

0

0

0

0

0

0

Dir.

I

Pin

44

600X CompactFlash Card

This signal is used during Memory Cycles to distinguish between Common

Memory and Register (Attribute) Memory accesses.

Low for Attribute Memory.

In PC Card Memory Mode, when Ultra DMA Protocol is supported by the host

and the host has enabled Ultra DMA protocol on the card the, host

-REG signal negated during the execution of any DMA Command by the device.

The signal shall also be active (low) during I/O Cycles when the I/O address is

on the Bus.

In PC Card I/O Mode, when Ultra DMA Protocol is supported by the host and

host has enabled Ultra DMA protocol on the card the, host shall keep the signal asserted during the execution of any DMA Command by the device.

This is a DMA Acknowledge signal that is asserted by the host in response to

(-)DMARQ to initiate DMA transfers.

In True IDE Mode, while DMA operations are not active, the card

(-)DMACK signal, including a floating condition.

If DMA operation is not supported by a True IDE Mode only host, this signal

should be driven high or connected to VCC by the host.

A host that does not support DMA mode and implements both PC Card and

True-IDE modes of operation need not alter the PC Card mode connections

while in True-IDE mode as long as this does not prevent proper operation all

modes.

Description

RESET

(PC Card Memory Mode)

RESET

(PC Card I/O Mode)

-RESET

(True IDE Mode)

VCC

(PC Card Memory Mode)

VCC

(PC Card I/O Mode)

VCC

(True IDE Mode)

--

I

41 The CompactFlash Storage Card is Reset when the

following important exception:

The host may leave the RESET pin open or keep it continually high from the

application of power without causing a continuous Reset of the card. Under

either of these conditions, the card shall emerge from power-up having

completed an initial Reset.

The CompactFlash Storage Card is also Reset when the Soft Reset bit in the

Card Configuration Option Register is set.

This signal is the same as the PC Card Memory Mode signal.

In the True IDE Mode, this input pin is the active low hardware reset from the

host.

13,38 +5 V, +3.3 V power.

This signal is the same for all modes.

This signal is the same for all modes.

Transcend Information Inc.

V1.0

Page 14

T

14

VS2 is

Except

Except Ultra

Card to signal the

signal is asserted

signal is the data

rising and falling edge of DSTROBE

write data to the

igured in the

C

does not have a write protect

IOIS16) function. A

ormed at

device is expecting

S

8

G

~

1

6

G

C

F

T

S

8

G

~

1

6

T

S

8

G

Signal Name

-VS1

-VS2

(PC Card Memory Mode)

-VS1

-VS2

(PC Card I/O Mode)

-VS1

-VS2

(True IDE Mode)

-WAIT

(PC Card Memory Mode –

Ultra DMA Protocol Active)

-WAIT

(PC Card I/O Mode –

DMA Protocol Active)

IORDY

(True IDE Mode – Except Ultra

DMA Protocol Active)

-DDMARDY

(All Modes – Ultra DMA Write

Protocol Active)

DSTROBE

(All Modes – Ultra DMA Read

Protocol Active)

~

1

6

G

G

6

C

F

6

C

F

6

0

0

0

0

0

0

Dir.

O

O

Pin

33

40

42

600X CompactFlash Card

Voltage Sense Signals. -VS1 is grounded on the Card and sensed by the Host

so that the CompactFlash Storage Card CIS can be read at 3.3 volts and reserved by PCMCIA for a secondary voltage and is not connected on the Card.

This signal is the same for all modes.

This signal is the same for all modes.

The -WAIT signal is driven low by the CompactFlash Storage

host to delay completion of a memory or I/O cycle that is in progress.

This signal is the same as the PC Card Memory Mode signal.

In True IDE Mode, except in Ultra DMA modes, this output signal may be used

as IORDY.

In all modes, when Ultra DMA mode DMA Write is active, this

by the device during a data burst to indicate that the device is ready to receive

Ultra DMA data out bursts. The device may negate -DDMARDY to pause an

Ultra DMA transfer.

In all modes, when Ultra DMA mode DMA Read is active, this

in strobe generated by the device. Both the

cause data to be latched by the host. The device may stop generating

DSTROBE edges to pause an Ultra DMA data in burst.

Description

-WE

(PC Card Memory Mode)

-WE

(PC Card I/O Mode)

-WE

(True IDE Mode)

WP

(PC Card Memory Mode)

Write Protect

-IOIS16

(PC Card I/O Mode)

-IOCS16

(True IDE Mode)

I

O

Transcend Information Inc.

36 This is a signal driven by the host and used for strobing memory

registers of the CompactFlash Storage Card when the card is conf

memory interface mode. It is also used for writing the configuration registers.

In PC Card I/O Mode, this signal is used for writing the configuration registers.

In True IDE Mode, this input signal is not used and should be connected to VC

by the host.

24

Memory Mode – The CompactFlash Storage Card

switch. This signal is held low after the completion of the reset initialization

sequence.

I/O Operation – When the CompactFlash Storage Card is configured for I/O

Operation Pin 24 is used for the -I/O Selected is 16 Bit Port (Low signal indicates that a 16 bit or odd byte only operation can be perf

the addressed port.

In True IDE Mode this output signal is asserted low when this

a word data transfer cycle.

V1.0

Page 15

T

15

S

8

G

~

1

6

G

C

F

6

0

0

6

6

0

0

0

0

600X CompactFlash Card

T

T

S

S

8

8

G

G

~

~

1

1

6

6

G

G

C

C

F

F

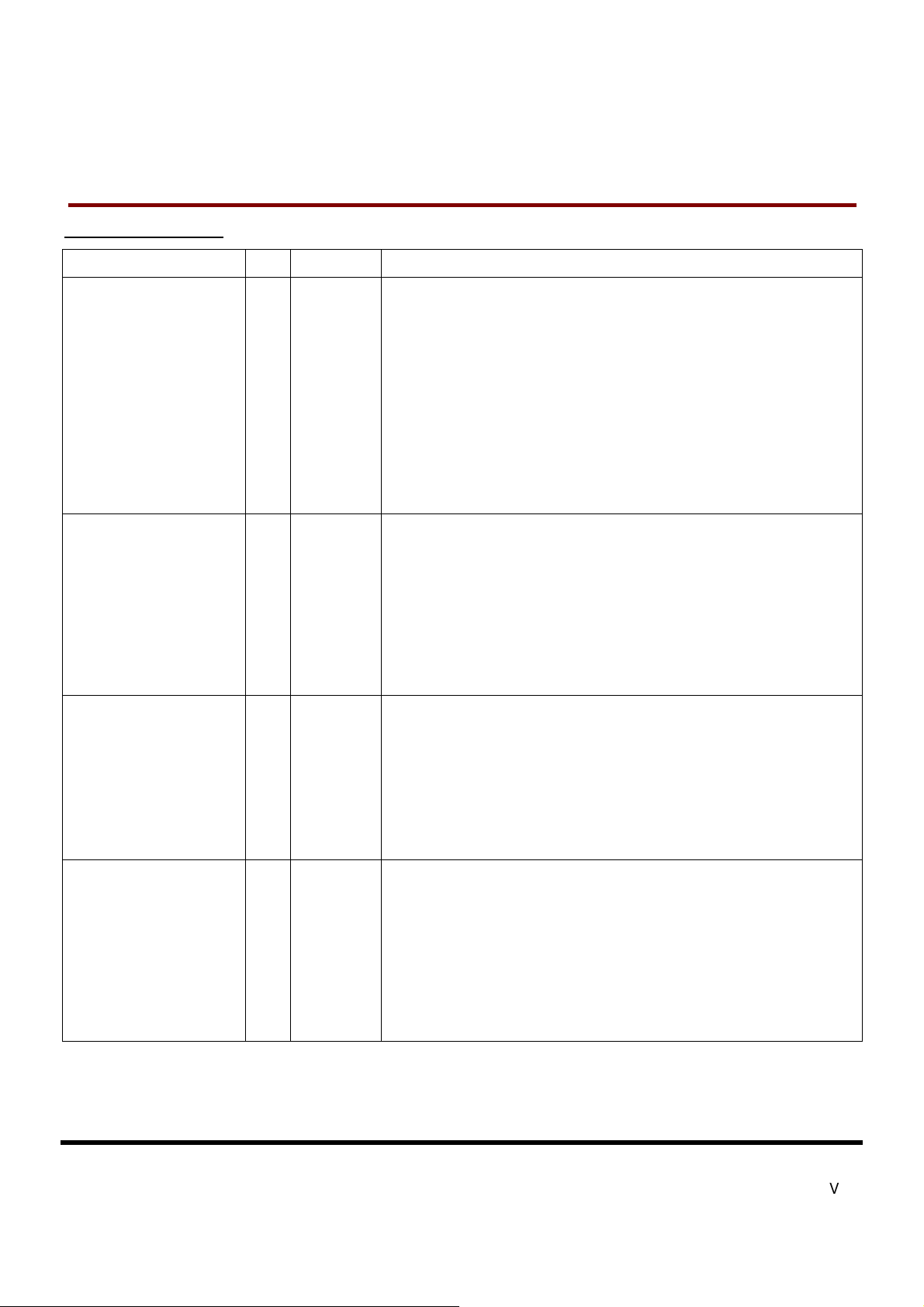

Electrical Specification

The following tables indicate all D.C. Characteristics for the CompactFlash Storage Card. Unless

otherwise stated, conditions are:

Vcc = 5V ±10%

Vcc = 3.3V ± 5%

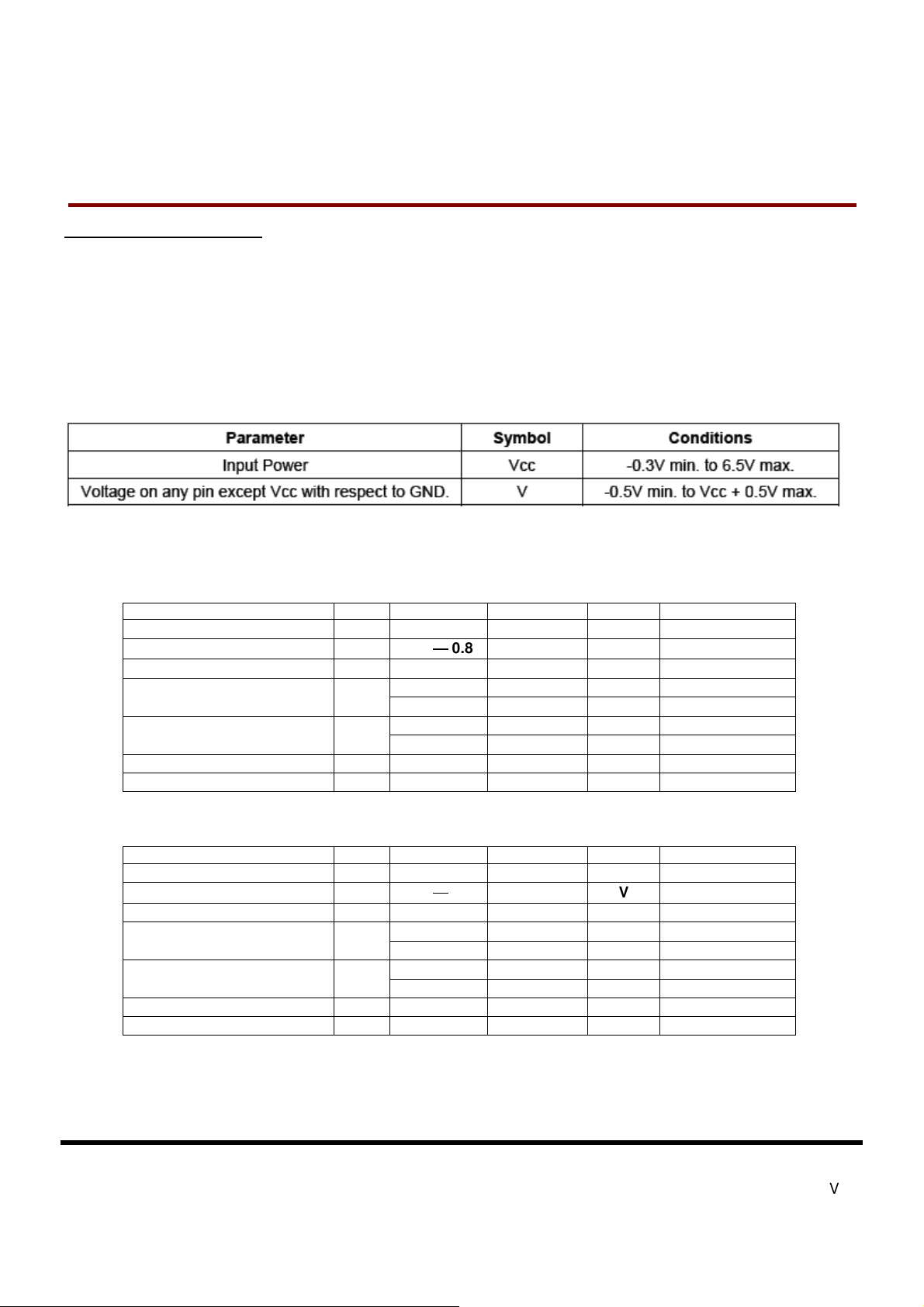

Absolute Maximum Conditions

DC Characteristics

CompactFlash Interface I/O at 5.0V

Parameter

Supply Voltage

High level output voltage VOH

Low level output voltage VOL 0.8

High level input voltage VIH

Low level input voltage VIL

Pull up resistance2 RPU 50 73 KOhm

Pull down resistance RPD 50 97 KOhm

CompactFlash Interface I/O at 3.3V

Parameter

Supply Voltage

High level output voltage VOH

Low level output voltage VOL 0.8

High level input voltage VIH

Low level input voltage VIL

Pull up resistance2 RPU 52.7 141 KOhm

Pull down resistance RPD 47.5 172 KOhm

1. Include CE1, CE2, HREG, HOE, HIOE, HWE, HIOW pins

2. Include CE1, CE2, HREG, HOE, HIOE, HWE, HIOW, CSEL (P35), PDIAG, DASP pins

Symbol

V

CC

Symbol

V

CC

Min.

4.5 5.5

VCC

─

0.8

─

──

4.0

2.92

0.8

1.70

Min.

3.135 3.465

VCC

────

0.8

2.4

2.05

0.6

1.25

Max.

Max.

Unit

V

V

V

V

V

V

V

Unit

V

V

V

V

V

V

V

Remark

Non-schmitt trigger

Schmitt trigger

Non-schmitt trigger

Schmitt trigger

Remark

Non-schmitt trigger

Schmitt trigger

Non-schmitt trigger

Schmitt trigger

1

1

1

1

Transcend Information Inc.

V1.0

Page 16

T

16

output shall

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

T

S

8

G

Input Power

~

~

1

1

6

6

G

G

C

C

F

F

6

6

0

0

0

0

600X CompactFlash Card

Input Characteristics for UDMA mode >4

In UDMA modes greater than 4, the following characteristics apply. Voltage output high and low values shall be met

at the source connector to include the effect of series termination.

Table: Input Characteristics (UDMA Mode > 4)

Parameter Symbol MIN MAX Units

DC supply voltage to drivers V

Low to high input threshold V+ 1.5 2.0 Volts

High to low input threshold V- 1.0 1.5 Volts

Difference between input thresholds:

((V+

current value

Average of thresholds:

((V+

current value

) - (V-

) + (V-

current value

current value

))

))/2

V

V

THRAVG

DD3

HYS

3.3 –8% 3.3% + 8% Volts

320 Volts

1.3 1.7 Volts

Output Drive Characteristics for UDMA mode > 4

In UDMA modes greater than 4, the characteristics specified in the following table apply. Voltage output high and low

values shall be met at the source connector to include the effect of series termination.

Table: Output Drive Characteristics (UDMA Mode > 4)

Parameter

DC supply voltage to drivers V

Voltage output high at -6 mA to +3 mA (at VoH2 the

be able to supply and sink current toVDD3)

Voltage output low at 6 mA V

Notes:

oLDASP

1) I

2) I

3) Voltage output high and low values shall be met at the source connector to include the effect of series termination.

4) A device shall have less than 64 μA of leakage current into a 6.2 KΩ pull-down resistor while the INTRQ signal is in the released

state.

shall be 12 mA minimum to meet legacy timing and signal integrity.

oH

value at 400 μA is insufficient in the case of DMARQ that is pulled low by a 5.6 kΩ resistor.

Symbol

3.3 –8% 3.3% + 8% Volts

DD3

V

V

oH2

0.51 Volts

oL2

MIN

–0.51 V

DD3

MAX

+0.3 Volts

DD3

Units

Transcend Information Inc.

V1.0

Page 17

T

17

Gnd R

up

S

8

G

~

1

6

G

C

F

6

0

0

6

6

0

0

0

0

600X CompactFlash Card

T

T

S

S

8

8

G

G

~

~

1

1

6

6

G

G

C

C

F

F

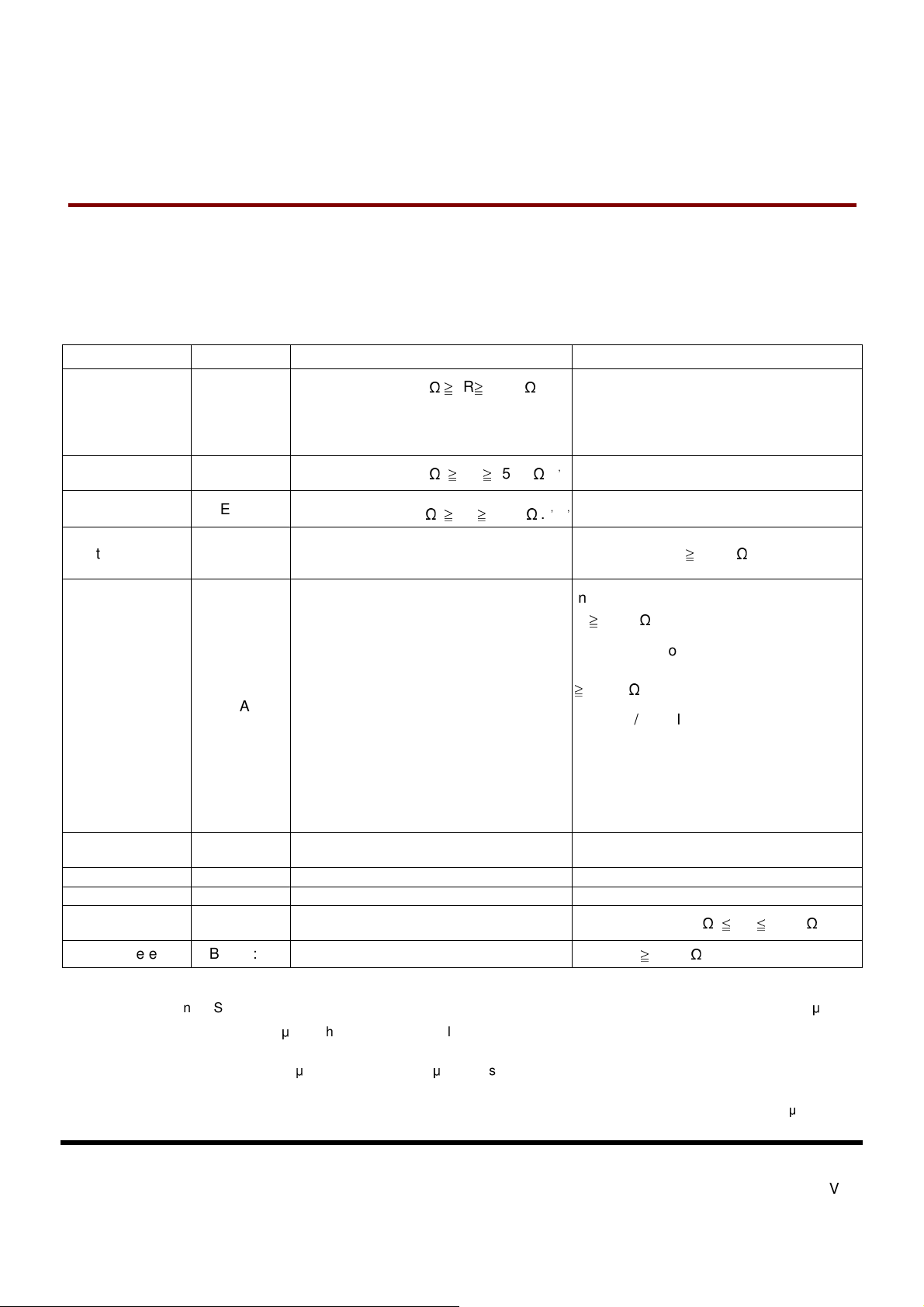

Signal Interface

Electrical specifications shall be maintained to ensure data reliability. Additional requirements are necessary for

Advanced Timing Modes and Ultra DMA modes operations. See next sections for additional information.

Item Signal Card10 Host

Control Signal

Status Signal

-CE1

-CE2

-REG

-HIOE

-IOWR

-OE

-WE

RESET

READY

-WAIT

WP

-INPACK

Pull-up to VCC 500 K

shall be sufficient to keep inputs inactive

when the pins are not connected at the

1

host.

Pull-up to VCC 500 KΩ ≧ R ≧ 50 KΩ.

Pull-up to VCC 500 KΩ ≧ R ≧ 50 KΩ.

Ω ≧ R≧

50 KΩ and

1,2

1,2,9,

Pull-up to VCC R ≧ 10 KΩ.

In PCMCIA PC Card modes Pull-up to V

R ≧ 10 KΩ.4

In True IDE mode, if DMA operation is

supported by the host, Pull-down to

≧

5.6 KΩ.5

PC Card / True IDE hosts switch the pullto pull down in True IDE mode if DMA

operation is supported.

The PC Card mode Pull-up may be left

active during True IDE mode if True IDE

DMA operation is not supported.

10

3

CC

Address

Data Bus D[15:00]

Card Detect

Voltage Sense

Battery/Detect BVD[2:1]

A[10:00]

-CSEL

-CD[2:1] Connected to GND in the card

-VS1

-VS2

Notes: 1) Control Signals: each card shall present a load to the socket no larger than 50 pF

low state and 150 μA high state, including pull-resistor. The socket shall be able to drive at least the following

10

load

while meeting all AC timing requirements: (the number of sockets wired in parallel) multiplied by (50 pF

with DC current 700 μA low state and 150 μA high state per socket).

2) Resistor is optional.

3) Status Signals: the socket shall present a load to the card no larger than 50 pF

Transcend Information Inc.

1.

Pull-up to Vcc 10 KΩ ≦ R ≦100KΩ.

Pull-up R ≧ 50 KΩ.

10

10

at a DC current of 400 μA low

3.6

at a DC current of 700 μA

V1.0

Page 18

T

18

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

4) Status Signals: the socket shall present a load to the card no larger than 50 pF

5) Status Signals: the socket shall present a load to the card no larger than 50 pF

6) BVD2 was not defined in the JEIDA 3.0 release. Systems fully supporting JEIDA release 3 SRAM cards shall

7) Address Signals: each card shall present a load of no more than 100pF

8) Data Signals: the host and each card shall present a load no larger than 50pF

9) Reset Signal: This signal is pulled up to prevent the input from floating when a CFA to PCMCIA adapter is used

10) Host and card restrictions for CF Advanced Timing Modes and Ultra DMA modes: Additional Requirements for

Additional Requirements for CF Advanced Timing Modes

The CF Advanced Timing modes include PC Card I/O and Memory modes that are 100ns or faster, PC Card Ultra

DMA modes 3 or above and True IDE PIO Modes 5,6, Multiword DMA Modes 3,4 and True IDE Ultra DMA modes

3 or above.

When operating in CF Advanced timing modes, the host shall conform to the following requirements:

1) Only one CF device shall be attached to the CF Bus.

2) The host shall not present a load of more than 40pF to the device for all signals, including any cabling.

3) The maximum cable length is 0.15 m (6 in). The cable length is measured from the card connector to the host

controller. 0.46 m (18 in) cables are

4) The -WAIT and IORDY signals shall be ignored by the host.

Devices supporting CF Advanced timing modes shall also support slower timing modes, to ensure operability with

systems that do not support CF Advanced timing modes

F

G

C

F

state and 100 μA high state, including pull-up resistor. The card shall be able to drive at least the following load

10

while meeting all AC timing requirements: 50 pF at a DC current of 400 μA low state and 100 μA high state.

state and 100 μA high state, including pull-up resistor. The card shall be able to drive at least the following load

10

while meeting all AC timing requirements: 50 pF at a DC current of 400 μA low state and 100 μA high state.

state and 100 μA high state, including pull-up resistor. The card shall be able to drive at least the following load

10

while meeting all AC timing requirements: 50 pF at a DC current of 400 μA low state and 1100 μA high state.

pull-up pin 45 (BVD2) to avoid sensing their batteries as “Low.”

150μA high state. The host shall be able to drive at least the following load

requirements: (the number of sockets wired in parallel) multiplied by (100pF with DC current 450μA low state

and 150μA high state per socket).

150μA high state. The host and each card shall be able to drive at least the following load

AC timing requirements: 100pF with DC current 1.6mA low state and 300μA high state. This permits the host to

wire two sockets in parallel without derating the card access speeds.

in a PCMCIA revision 1 host. However, to minimize DC current drain through the pull-up resistor in normal

operation the pull-up should be turned off once the Reset signal has been actively driven low by the host.

Consequently, the input is specified as an I2Z because the resistor is not necessarily detectable in the input

current leakage test.

CF Advanced Timing Modes and Ultra DMA Electrical Requirements for additional required limitations on the

implementation of CF Advanced Timing modes and Ultra DMA modes respectively.

6

6

0

0

0

0

10

not

supported.

600X CompactFlash Card

10

at a DC current of 400 μA low

10

at a DC current of 400 μA low

at a DC current of 450μA low state and

10

while meeting all AC timing

10

at a DC current of 450μA and

10

while meeting all

Transcend Information Inc.

V1.0

Page 19

T

19

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

Ultra DMA Electrical Requirements

Host and Card signal capacitance limits for Ultra DMA operation

The host interface signal capacitance at the host connector shall be a maximum of 25 pF for each signal as measured at

1 MHz.

The card interface signal capacitance at the card connector shall be a maximum of 20 pF for each signal as measured at

1 MHz.

Series termination required for Ultra DMA operation

Series termination resistors are required at both the host and the card for operation in any of the Ultra DMA modes. Table

describes typical values for series termination at the host and the device.

F

G

C

F

6

6

0

0

0

0

600X CompactFlash Card

Table: Typical Series Termination for Ultra DMA

Signal Host Termination Device Termination

-HIOE (-HDMARDY,HSTROBE) 22 ohm 82 ohm

-IOWR (STOP) 22 ohm 82 ohm

-CS0, -CS1 33 ohm 82 ohm

A00, A01, A02 33 ohm 82 ohm

-DMACK 22 ohm 82 ohm

D15 through D00 33 ohm 33 ohm

DMARQ 82 ohm 22 ohm

INTRQ 82 ohm 22 ohm

IORDY (-DDMARDY, DSTROBE) 82 ohm 22 ohm

-RESET 33 ohm 82 ohm

−

NOTE

termination is not required for operation in an Ultra DMA mode. Shows signals also requiring a pull-up or

pull-down resistor at the host. The actual termination values should be selected to compensate for transceiver

and trace impedance to match the characteristic cable impedance.

Only those signals requiring termination are listed in this table. If a signal is not listed, series

Transcend Information Inc.

V1.0

Page 20

T

20

T

T

S

S

S

8

8

8

G

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

C

C

F

F

F

6

6

6

0

0

0

0

0

0

600X CompactFlash Card

Table: Ultra DMA Termination with Pull-up or Pull down Example

Printed Circuit Board (PCB) Trace Requirements for Ultra DMA

On any PCB for a host or device supporting Ultra DMA:

The longest D[15:00] trace shall be no more than 0.5" longer than either STROBE trace as measured from the

IC pin to the connector.

The shortest D[15:00] trace shall be no more than 0.5" shorter than either STROBE trace as measured from

the IC pin to the connector.

Ultra DMA Mode Cabling Requirement

Operation in Ultra DMA mode requires a crosstalk suppressing cable. The cable shall have a grounded line

between each signal line.

For True IDE mode operation using a cable with IDE (ATA) type 40 pin connectors it is recommended that the

host sense the cable type using the method described in the ANSI INCITS 361-2002 AT Attachment - 6

standard, to prevent use of Ultra DMA with a 40 conductor cable.

Transcend Information Inc.

V1.0

Page 21

T

21

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

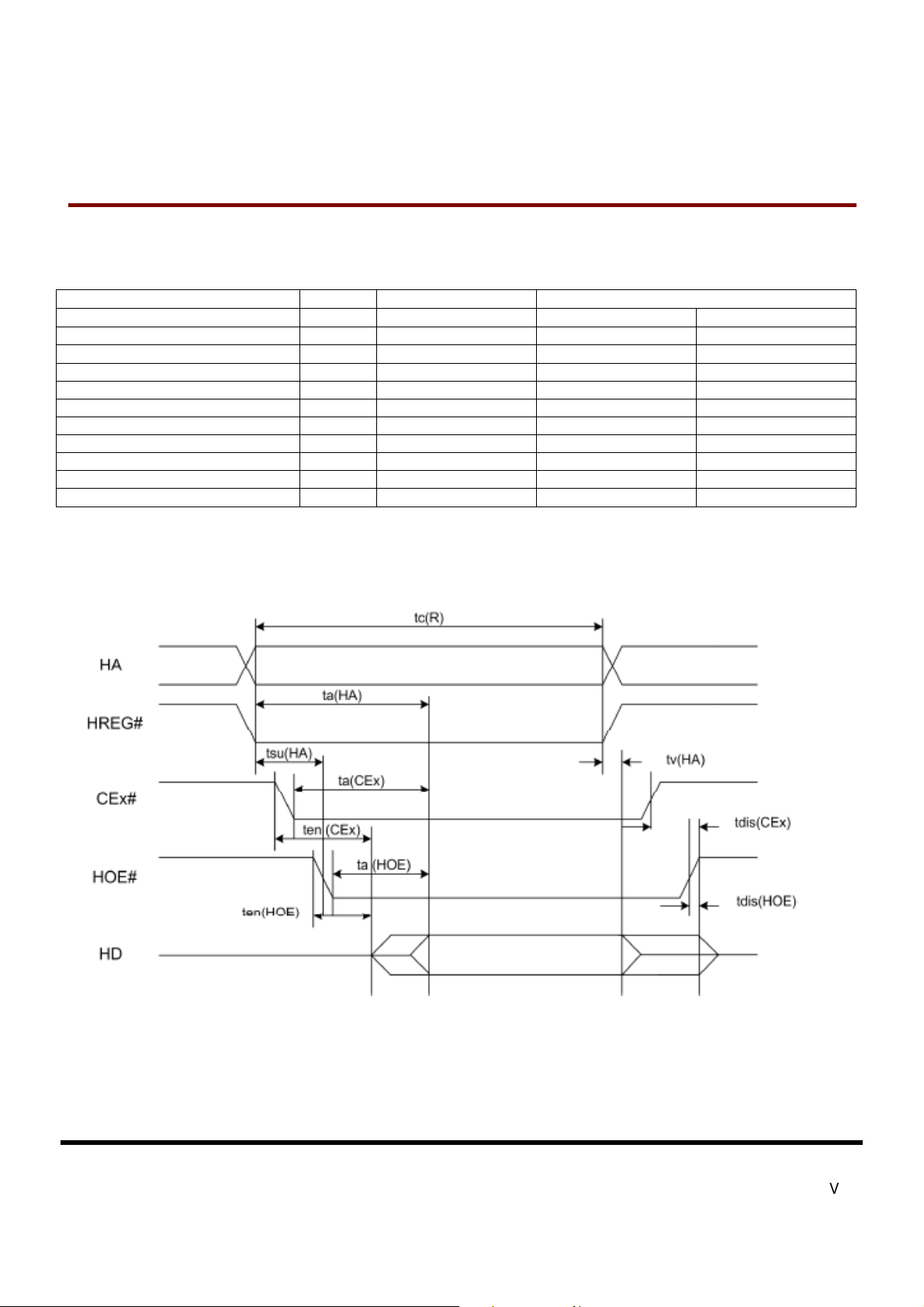

Attribute Memory Read Timing Specification

Attribute Memory access time is defined as 300 ns. Detailed timing specs are shown in Table below

Speed Version 300 ns

Read Cycle Time tc(R) tAVAV 300

Address Access Time ta(A) tAVQV 300

Card Enable Access Time ta(CE)

Output Enable Access Time ta(OE)

Output Disable Time from CE tdis(CE)

Output Disable Time from OE tdis(OE)

Address Setup Time tsu (A)

Output Enable Time from CE ten(CE)

Output Enable Time from OE ten(OE)

Data Valid from Address Change

Note: All times are in nanoseconds. Dout signifies data provided by the CompactFlash Storage Card to the system. The -CE signal or

both the -OE signal and the -WE signal shall be de-asserted between consecutive cycle operations.

G

Item

C

F

F

6

6

0

0

0

0

Symbol

tv(A) tAXQX 0

IEEE Symbol

tELQV 300

tGLQV 150

tEHQZ 100

tGHQZ 100

tAVGL 30

tELQNZ 5

tGLQNZ 5

600X CompactFlash Card

Min ns.

Max ns.

Transcend Information Inc.

V1.0

Page 22

T

22

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

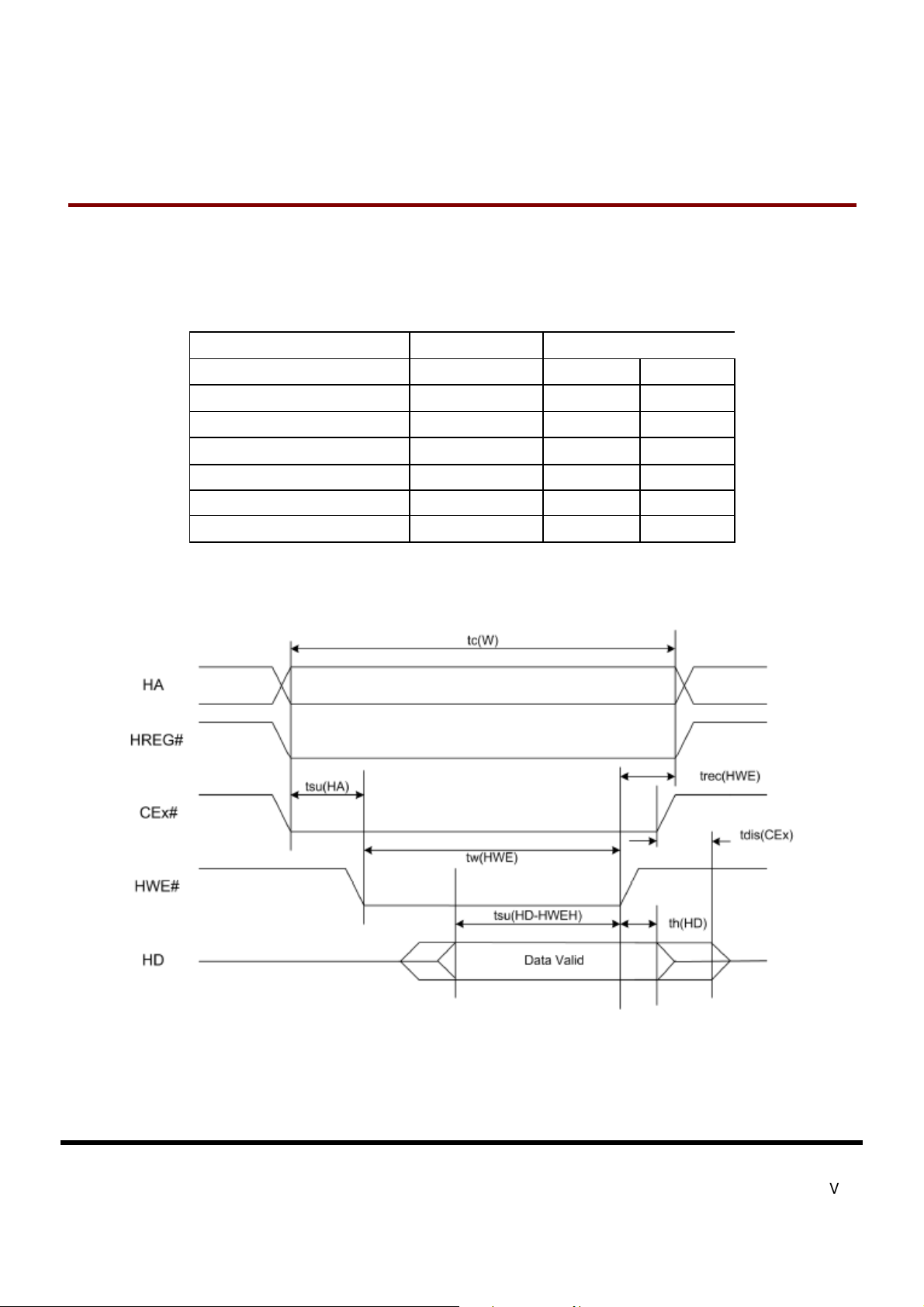

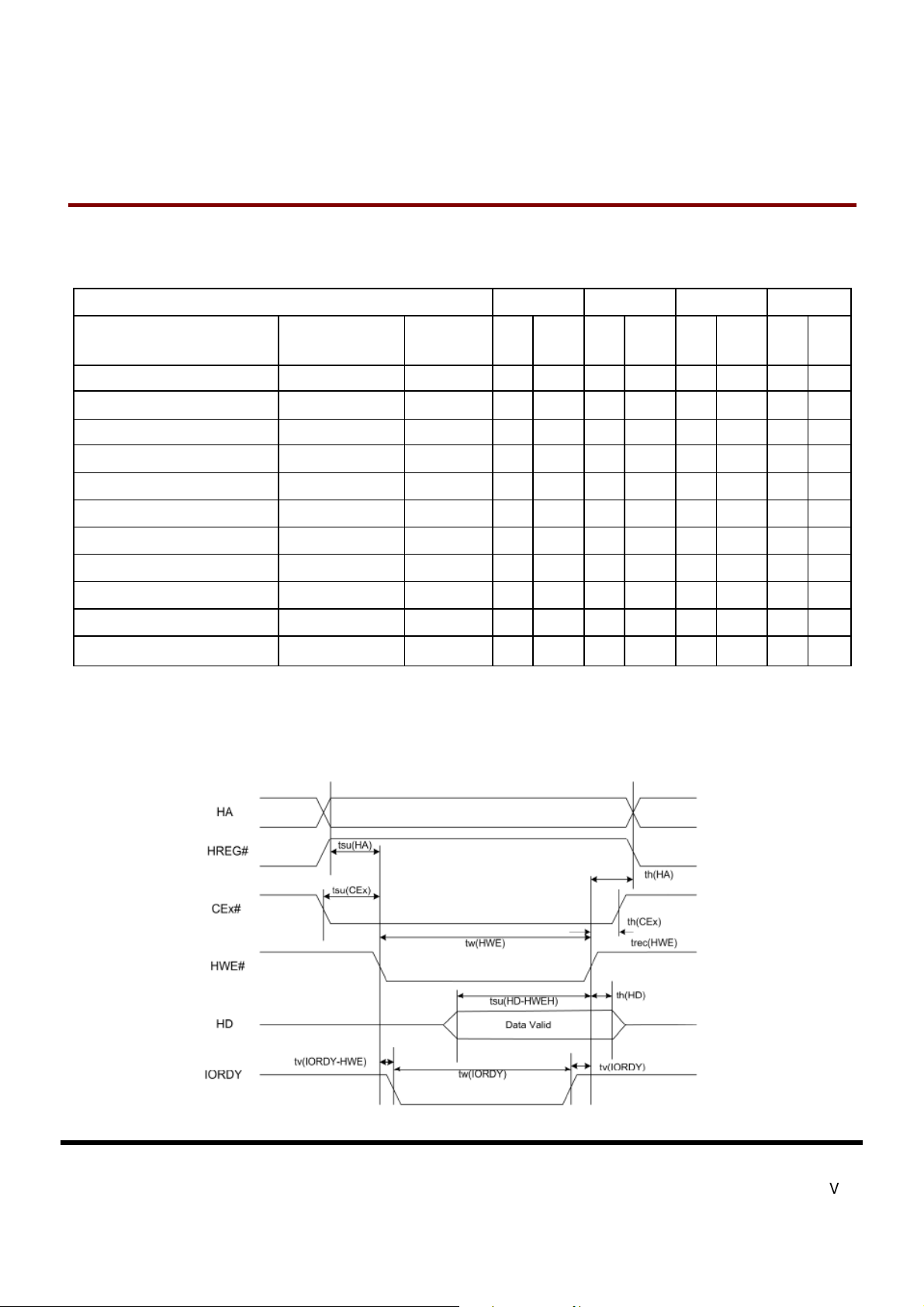

Configuration Register (Attribute Memory) Write Timing Specification

The Card Configuration write access time is defined as 250 ns. Detailed timing specifications are shown in Table

below.

G

C

F

F

6

0

0

6

0

0

Table: Configuration Register (Attribute Memory) Write Timing

600X CompactFlash Card

Speed Version

Item

Write Cycle Time tc(W) 250

Write Pulse Width tw(HWE) 150

Address Setup Time tsu(HA) 30

Write Recovery Time trec(HWE) 30

Data Setup Time for WE tsu(HD-HWEH) 80

Data Hold Time th(HD) 30

Note: All times are in nanoseconds. Din signifies data provided by the system to the CompactFlash Storage Card .

Symbol

250 ns

Min ns

Max ns

Transcend Information Inc.

V1.0

Page 23

T

23

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

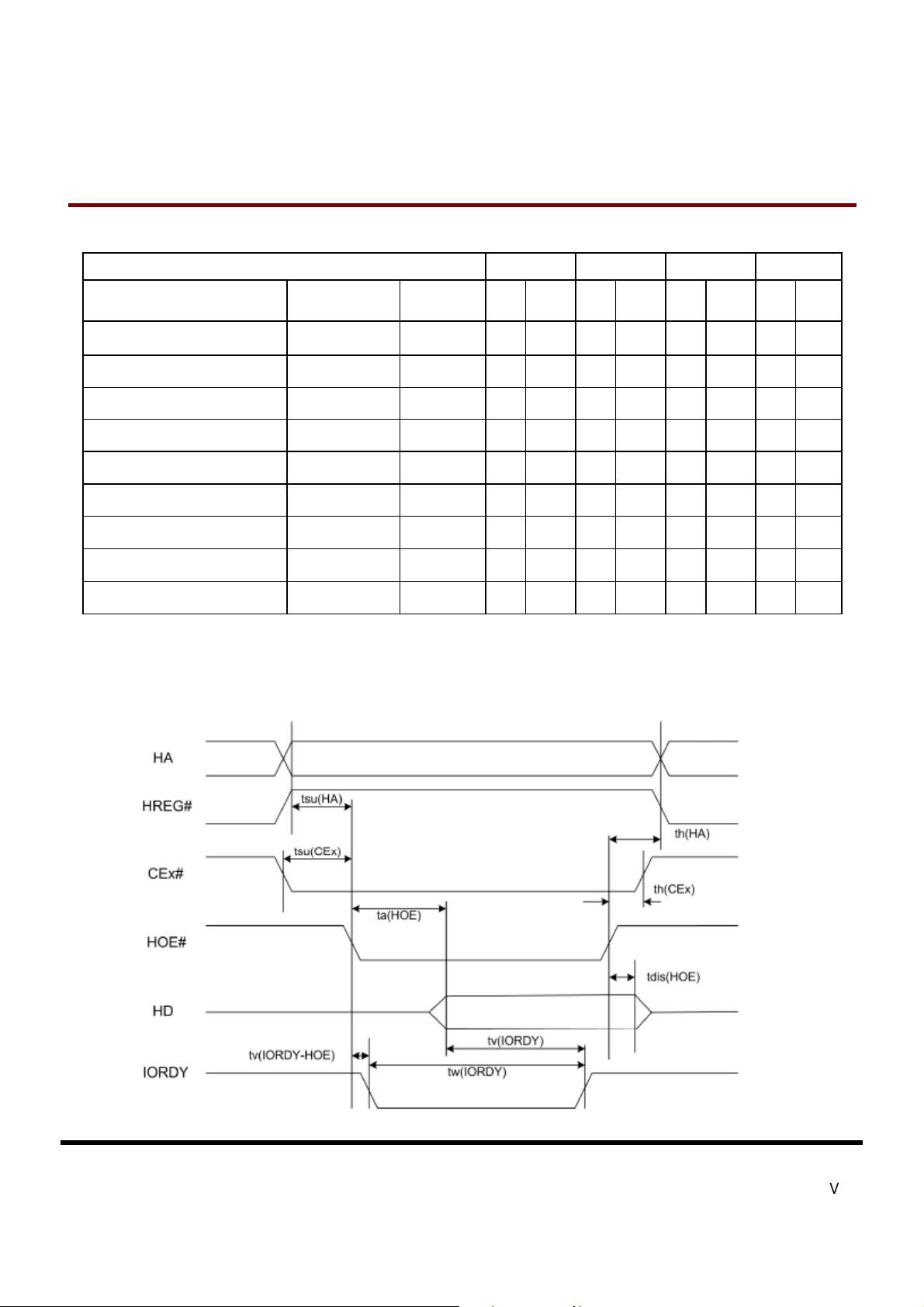

Common Memory Read Timing Specification

G

Item

C

F

F

6

6

0

0

0

0

Symbol

Cycle Time Mode:

IEEE

Symbol

600X CompactFlash Card

250 ns

Min

Max

ns.

ns.

Min

ns.

120 ns

Max

ns.

100 ns

Min

ns.

Max

ns.

Min

ns.

80 ns

Max

ns.

Output Enable Access Time ta(HOE) tGLQV

Output Disable Time from HOE tdis(HOE) tGHQZ

Address Setup Time tsu(HA) tAVGL 30

Address Hold Time th(HA) tGHAX 20

CEx Setup before HOE tsu(CEx) tELGL 5

CEx Hold following HOE th(CEx) tGHEH 20

Wait Delay Falling from HOE tv(IORDY-HOE) tGLWTV

Data Setup for Wait Release tv(IORDY) tQVWTH

Wait W idth Time

Notes:1) –WAIT is not supported in this mode.

2) The maximum load on -WAIT is 1 LSTTL with 50 pF (40pF below 120nsec Cycle Time) total load. All times are in

nanoseconds. Dout signifies data provided by the CompactFlash Storage Card to the system. The -W AIT signal may be

ignored if the -OE cycle to cycle time is greater than the Wait Width time. The Max Wait Width time can be determined from the

Card Information Structure. The Wait W idth time meets the PCMCIA PC Card specification of 12µs but is intentionally less in

this specification.

2

tw(IORDY) tWTLWTH

125

100

35

0

350

15

15

5

15

60

60

35

0

350

10

15

5

15

50

50

10

10

10

35

0

350

45

45

5

1

na

1

na

na

1

Transcend Information Inc.

V1.0

Page 24

T

24

S

8

G

~

1

6

G

C

F

6

0

0

6

6

0

0

0

0

T

T

S

S

8

8

G

G

~

~

1

1

6

6

G

G

C

C

F

F

Common Memory Write Timing Specification

Cycle Time Mode: 250 ns

Item

Data Setup before HWE tsu (HD-HWEH) tDVWH 80

Data Hold following HWE th(HD) tWMDX 30

HWE Pulse Width tw(HWE) tWLWH 150

Address Setup Time tsu(HA) tAVWL 30

Symbol

IEEE

Symbol

Min

ns.

Max

ns.

600X CompactFlash Card

120 ns

Min

ns.

50

15

70

15

Max

ns.

100 ns

Min

ns.

40

10

60

10

Max

ns.

Min

ns.

30

10

55

10

80 ns

Ma

x

ns.

CEx Setup before HWE tsu(CEx) tELWL 5

Write Recovery Time trec(HWE) tWMAX 30

Address Hold Time th(HA) tGHAX 20

CEx Hold following HWE th(CEx) tGHEH 20

Wait Delay Falling from HWE tv (IORDY-HWE) tWLW TV

WE High from Wait Release tv(IORDY) tWTHWH 0

Wait W idth Time

Notes: 1) –WAIT is not supported in this mode.

2) The maximum load on -WAIT is 1 LSTTL with 50 pF (40pF below 120nsec Cycle Time) total load. All times are in

nanoseconds. Din signifies data provided by the system to the CompactFlash Storage Card. The -WAIT signal may be

ignored if the -HWE cycle to cycle time is greater than the Wait Width time. The Max Wait Width time can be determined

from the Card Information Structure. The Wait Width time meets the PCMCIA PC Card specification of 12µs but is

intentionally less in this specification.

2

tw (IORDY) tWTLWTH

5

15

15

15

35

350

35

0

350

5

15

15

15

35

0

350

5

15

15

10

na

1

na

1

1

na

Transcend Information Inc.

V1.0

Page 25

T

25

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

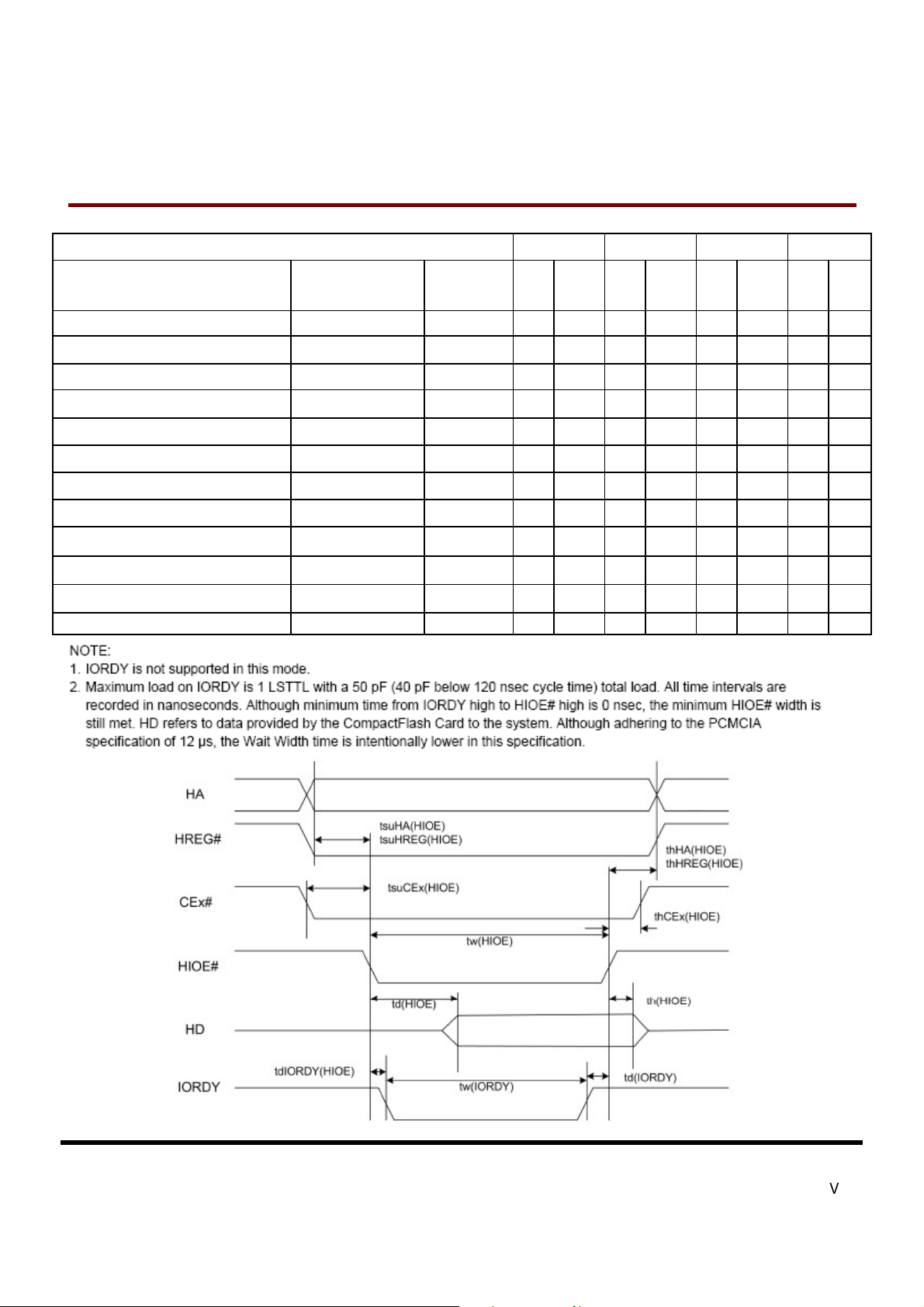

I/O Input (Read) Timing Specification

Item

Data Delay after HIOE td(HIOE) tlGLQV

Data Hold following HIOE th(HIOE) tlGHQX 0

HIOE Width Time tw(HIOE) tlGLIGH 165

Address Setup before HIOE tsuA(HIOE) tAVIGL 70

G

C

F

F

6

6

0

0

0

0

Cycle Time Mode: 250 ns

Symbol

IEEE

Symbol

Min

ns.

Max

ns.

100

600X CompactFlash Card

120 ns

Min

Max

ns.

5

70

25

ns.

50

100 ns

Min

Max

ns.

50

5

65

25

ns.

80 ns

Min

ns.

5

55

15

Ma

x

ns.

45

Address Hold following HIOE thA(HIOE) tlGHAX 20

CEx Setup before HIOE tsuCE(HIOE) tELIGL 5

CEx Hold following HIOE thCE(HIOE) tlGHEH 20

HREG Setup before HIOE tsuREG (HIOE) tRGLIGL 5

HREG Hold following HIOE thREG (HIOE) tlGHRGH 0

Wait Delay Falling from HIOE2 tdWT(HIOE) tlGLWTL

Data Delay from Wait Rising2 td(IORDY) tWTHQV

Wait W idth Time2 tw(IORDY) tWTLWTH

10

35

0

350

5

10

5

0

350

10

5

10

5

0

35 35 Na

0 0 Na

350

10

5

10

5

0

Na

1

1

1

Transcend Information Inc.

V1.0

Page 26

T

26

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

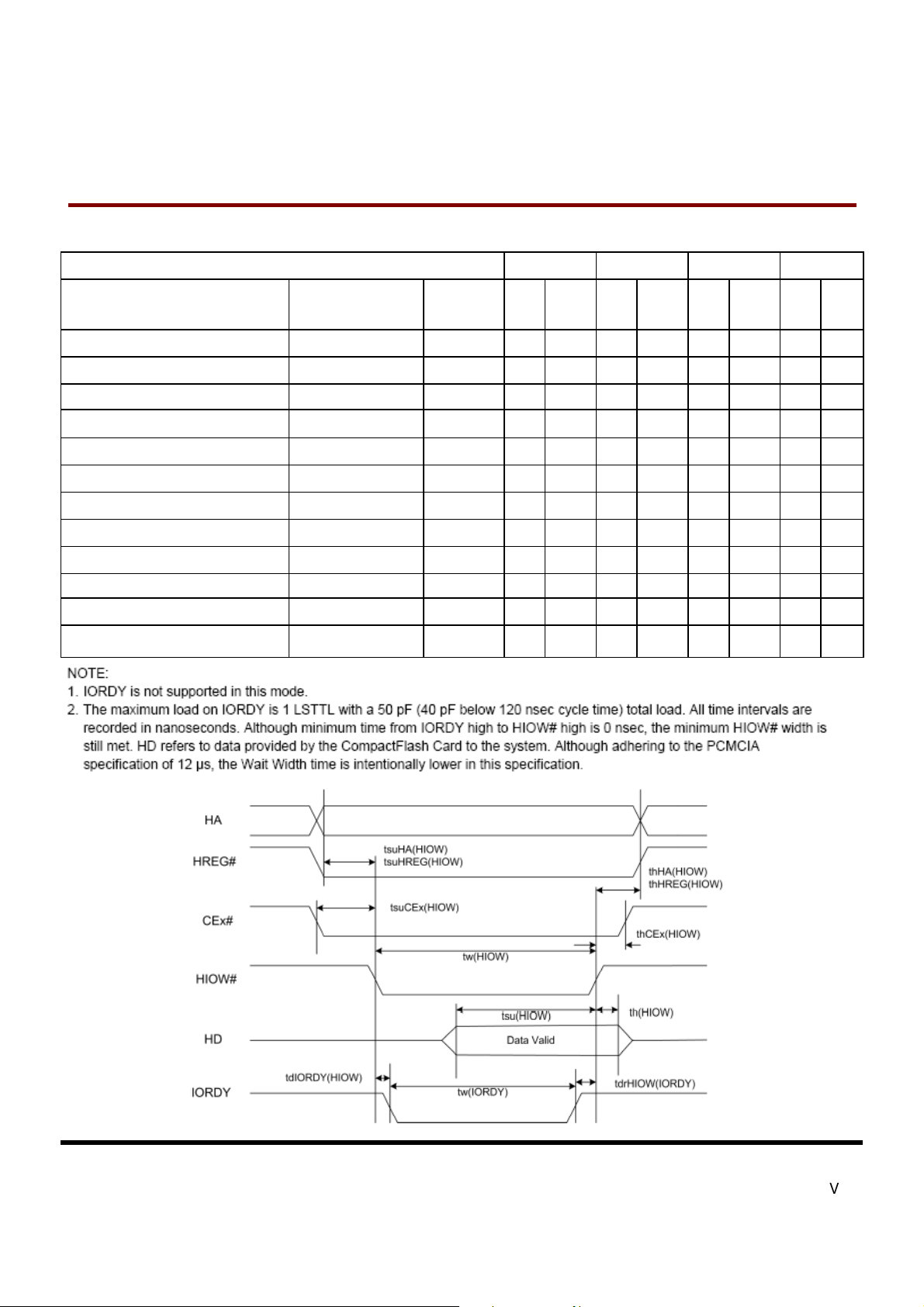

I/O Output (Write) Timing Specification

Data Setup before HIOW tsu(HIOW) tDVIWH 60

F

G

C

F

Item Symbol

6

6

0

0

0

0

Cycle Time Mode: 255 ns

IEEE

Symbol

Min

ns.

600X CompactFlash Card

Min

ns.

120 ns

Max

ns.

Max

ns.

20 20 15

100 ns

Min

Max

ns.

ns.

Min

ns.

80 ns

Ma

x

ns.

Data Hold following HIOW th(HIOW) tlW HDX 30

HIOW Width Time tw(HIOW) tlWLIWH 165 70 65 55

Address Setup before HIOW tsuA(HIOW) tAVIWL 70

Address Hold following HIOW thA(HIOW) tlWHAX 20

CEx Setup before HIOW tsuCE (HIOW ) tELIWL 5

CEx Hold following HIOW thCE (HIOW) tlWHEH 20

HREG Setup before HIOW tsuREG (HIOW) tRGLIWL 5

HREG Hold following HIOW thREG (HIOW) tlWHRGH 0

Wait Delay Falling from HIOW2 tdWT(HIOW) tlWLWTL

HIOW high from Wait high2 tdrHIOW (IORDY) tWTJIWH 0

Wait W idth Time2 tw(IORDY)

tWTLWT

H

10 5 5

25 25 15

20 10 10

5 5 5

20 10 10

5 5 5

0 0 0

35

350 350

35 35 Na1

0 0 Na1

350

Na1

Transcend Information Inc.

V1.0

Page 27

T

27

6

5

5

0

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

True IDE PIO Mode Read/Write Timing Specification

t0 Cycle time (min) 600 383 240 180 120 100 80 1

t1

t2 HIOE/HIOW (min) 165 125 100 80 70 65 55 1

t2 HIOE/HIOW (min) Register (8 bit) 290 290 290 80 70 65 55 1

t2i HIOE/HIOW recovery time (min) - - - 70 25 25 20 1

F

G

C

F

Address Valid to HIOE/HIOW

setup (min)

6

6

0

0

0

0

Item

0 1

70 50 30 30 25 15 10

600X CompactFlash Card

Mode

2

3

4

5

Note

t3 HIOW data setup (min) 60 45 30 30 20 20 15

t4 HIOW data hold (min) 30 20 15 10 10 5

t5 HIOE data setup (min) 50 35 20 20 20 15 10

t6 HIOE data hold (min) 5 5 5 5 5 5

T6Z HIOE data tristate (max) 30 30 30 30 30 20 20 2

Address valid to -IOCS16

t7

assertion (max)

Address valid to -IOCS16 released

t8

(max)

t9 HIOE/HIOW to address valid hold 20 15 10 10 10 10 10

Read Data Valid to IORDY active

tRD

(min), if IORDY initially low after tA

tA IORDY Setup time 35 35 35 35 35 na

tB IORDY Pulse Width (max) 1250 1250 1250 1250 1250 na

tC IORDY assertion to release (max) 5 5 5 5 5 na

Notes: All timings are in nanoseconds. The maximum load on -IOCS16 is 1 LSTTL with a 50 pF (40pF below 120nsec Cycle Time)

total load. All times are in nanoseconds. Minimum time from -IORDY high to -HIOE high is 0 nsec, but minimum -HIOE width

shall still be met.

1) t0 is the minimum total cycle time, t2 is the minimum command active time, and t2i is the minimum command recovery time

or command inactive time. The actual cycle time equals the sum of the actual command active time and the actual command

inactive time. The three timing requirements of t0, t2, and t2i shall be met. The minimum total cycle time requirement is

greater than the sum of t2 and t2i. This means a host implementation can lengthen either or both t2 or t2i to ensure that t0 is

equal to or greater than the value reported in the device’s identify device data. A CompactFlash Storage Card

implementation shall support any legal host implementation.

2) This parameter specifies the time from the negation edge of -HIOE to the time that the data bus is no longer driven by the

CompactFlash Storage Card (tri-state).

3) The delay from the activation of -HIOE or -HIOW until the state of IORDY is first sampled. If IORDY is inactive then the host

shall wait until IORDY is active before the PIO cycle can be completed. If the CompactFlash Storage Card is not driving

IORDY negated at tA after the activation of -HIOE or -HIOW, then t5 shall be met and tRD is not applicable. If the

CompactFlash Storage Card is driving IORDY negated at the time tA after the activation of -HIOE or -HIOW, then tRD shall

be met and t5 is not applicable.

4) t7 and t8 apply only to modes 0, 1 and 2. For other modes, this signal is not valid.

5) IORDY is not supported in this mode.

90 50 40 n/a n/a n/a n/a 4

60 45 30 n/a n/a n/a n/a 4

0 0 0 0 0 0

5

na5 3

5

na5

5

na

5

Transcend Information Inc.

V1.0

Page 28

T

28

T

T

S

S

S

8

8

8

G

G

G

~

~

~

1

1

1

6

6

6

G

G

G

C

C

C

F

F

F

6

6

6

0

0

0

0

0

0

600X CompactFlash Card

Transcend Information Inc.

V1.0

Page 29

T

29

S

8

G

~

1

6

G

C

F

6

0

0

6

6

0

0

0

0

T

T

S

S

8

8

G

G

~

~

1

1

6

6

G

G

C

C

F

F

True IDE Multiword DMA Mode Read/Write Timing Specification

Item

t

O

Cycle time (min) 480 150 120 100 80 1

t

D

-HIOE / -HIOW asserted width (min) 215 80 70 65 55 1

t

E

-HIOE data access (max) 150 60 50 50 45

t

F

-HIOE data hold (min) 5 5 5 5 5

G

t

-HIOE/-HIOW data setup (min) 100 30 20 15 10

H

t

-HIOW data hold (min) 20 15 10 5 5

I

t

-HREG to –HIOE/-HIOW setup (min) 0 0 0 0 0

t

J

-HIOE / -HIOW to -HREG hold (min) 20 5 5 5 5

t

KR

-HIOE negated width (min) 50 50 25 25 20 1

KW

t

-HIOW negated width (min) 215 50 25 25 20 1

LR

t

-HIOE to DMARQ delay (max) 120 40 35 35 35

LW

t

-HIOW to DMARQ delay (max) 40 40 35 35 35

M

t

CEx valid to –HIOE / -HIOW 50 30 25 10 5

N

t

CEx hold 15 10 10 10 10

Mode 0

(ns)

Mode 1

(ns)

Mode 2

(ns)

600X CompactFlash Card

Mode 3

(ns)

Mode 4

(ns)

Note

Transcend Information Inc.

V1.0

Page 30

T

30

T

T

S

S

S

8

8

8

G

G

G

~

1

6

G

C

F

6

0

0

~

1

6

G

C

G

C

F

F

~

1

6

6

6

0

0

0

0

600X CompactFlash Card

Transcend Information Inc.

V1.0

Page 31

T

31

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

True IDE Ultra DMA Mode Read/Write Timing Specification

Ultra DMA operations can take place in any of the three basic interface modes: PC Card Memory mode, PC Card I/O

mode, and True IDE (the original mode to support UDMA). The usage of signals in each of the modes is shown in Table

24:Ultra DMA Signal Usage In Each Interface Mode

UDMA Signal Type

DMARQ Output 43 (-INPACK) -DMARQ -DMARQ DMARQ

HREG Input

G

C

F

F

6

6

0

0

0

0

600X CompactFlash Card

Pin # (Non

UDMA MEM

MODE)

44 (-REG) -DMACK DMACK -DMACK

PC CARD MEM

MODE UDMA

PC CARD IO MODE

UDMA

TRUE IDE MODE

UDMA

HIOW Input

HIOE Input

IORDY Output

HD [15:0] Bidir

HA [10:0] Input

CSEL Input

HIRQ Output 37 (READY) READY -INTRQ INTRQ

CE1

CE2

Notes:1) The UDMA interpretation of this signal is valid only during an Ultra DMA data burst.

2) The UDMA interpretation of this signal is valid only during and Ultra DMA data burst during a DMA Read command.

3) The UDMA interpretation of this signal is valid only during an Ultra DMA data burst during a DMA Write command.

4) The HSTROBE and DSTROBE signals are active on both the rising and the falling edge.

5) Address lines 03 through 10 are not used in True IDE mode.

Several signal lines are redefined to provide different functions during an Ultra DMA data burst. These lines assume their

UDMA definitions when:

1 an Ultra DMA mode is selected, and

2 a host issues a READ DMA, or a WRITE DMA command requiring data transfer, and

3 the device asserts (-)DMARQ, and

4 the host asserts (-)DMACK.

These signal lines revert back to the definitions used for non-Ultra DMA transfers upon the negation of -DMACK by the

host at the termination of an Ultra DMA data burst.

Input

35 (-HIOW) STOP 1 STOP 1 STOP 1

34 (-HIOE)

42 (-WAIT)

… (D[15:00]) D[15:00] D[15:00] D[15:00]

… (A[10:00]) A[10:00] A[10:00] A[02:00] 5

39 (-CSEL) -CSEL -CSEL -CSEL

7 (-CE1)

31 (-CE2)

-HDMARDY(R) 1,

2HSTROBE(W)

-DDMARDY(W)

DSTROBE(R)

-CE1

-CE2

1, 3, 4

1. 2. 4

1, 3

-HDMARDY(R)

HSTROBE(W)

-DDMARDY(W)

DSTROBE(R)

-CE1

-CE2

1, 2

1, 3, 4

1, 3

1. 2. 4

-HDMARDY(R)

HSTROBE(W)

-DDMARDY(W)

DSTROBE(R)

-CS0

-CS1

1, 2

1, 3, 4

1, 3

1. 2. 4

With the Ultra DMA protocol, the STROBE signal that latches data from D[15:00] is generated by the same agent (either

host or device) that drives the data onto the bus. Ownership of D[15:00] and this data strobe signal are given either to the

device during an Ultra DMA data-in burst or to the host for an Ultra DMA data-out burst.

During an Ultra DMA data burst a sender shall always drive data onto the bus, and, after a sufficient time to allow for

propagation delay, cable settling, and setup time, the sender shall generate a STROBE edge to latch the data. Both

edges of STROBE are used for data transfers so that the frequency of STROBE is limited to the same frequency as the

data.

Words in the IDENTIFY DEVICE data indicate support of the Ultra DMA feature and the Ultra DMA modes the device is

capable of supporting. The Set transfer mode subcommand in the SET FEATURES command shall be used by a host to

select the Ultra DMA mode at which the system operates. The Ultra DMA mode selected by a host shall be less than or

Transcend Information Inc.

V1.0

Page 32

T

32

S

8

G

~

1

6

G

C

F

6

0

0

T

S

8

G

~

1

6

G

C

T

S

8

G

~

1

6

equal to the fastest mode of which the device is capable. Only one Ultra DMA mode shall be selected at any given time.

All timing requirements for a selected Ultra DMA mode shall be satisfied. Devices supporting any Ultra DMA mode shall

also support all slower Ultra DMA modes.

An Ultra DMA capable device shall retain the previously selected Ultra DMA mode after executing a software reset

sequence or the sequence caused by receipt of a DEVICE RESET command if a SET FEATURES disable reverting to

defaults command has been issued. The device may revert to a Multiword DMA mode if a SET FEATURES enable

reverting to default has been issued. An Ultra DMA capable device shall clear any previously selected Ultra DMA mode

and revert to the default non-Ultra DMA modes after executing a power-on or hardware reset.

Both the host and device perform a CRC function during an Ultra DMA data burst. At the end of an Ultra DMA data burst

the host sends its CRC data to the device. The device compares its CRC data to the data sent from the host. If the two

values do not match, the device reports an error in the error register. If an error occurs during one or more Ultra DMA data

bursts for any one command, the device shall report the first error that occurred. If the device detects that a CRC error

has occurred before data transfer for the command is complete, the device may complete the transfer and report the error

or abort the command and report the error.

NOTE -If a data transfer is terminated before completion, the assertion of INTRQ should be passed through to the host

software driver regardless of whether all data requested by the command has been transferred.

G

C

F

F

6

6

0

0

0

0

600X CompactFlash Card

Transcend Information Inc.

V1.0

Page 33

T

33

T

T

S

S

S

8

G

8

G

8

G

Name

2CYCTYP

t

t

CYC

t

2CYC

t

DS

t

DH

DVS

t

DVH

t

CS

t

CH

t

t

CVS

t

CVH

t

ZFS

t

DZFS

FS

t

LI

t

~

1

6

G

C

F

6

0

0

~

1

6

G

C

~

1

6

F

G

C

F

UDMA Mode

0

Min Max Min Max Min Max Min Max Min Max Min Max Min Max

240

112

230

15.0

5.0

70.0

6.2

15.0

5.0

70.0

6.2

0

70.0

0 150 0 150 0 150 0 100 0 100 0 75 0 60 Note 4

6

6

230

0

0

0

0

10.0

48.0

10.0

48.0

48.0

160

73

153

5.0

6.2

5.0

6.2

UDMA

Mode 1

0

200

UDMA

Mode 2

120

54

115

7.0

5.0

31.0

6.2

7.0

5.0

31.0

6.2

0

31.0

170

UDMA

Mode 3

90

39

86

7.0

5.0

20.0

6.2

7.0

5.0

20.0

6.2

0

20.0

130

UDMA

Mode 4

60

25

57

5.0

5.0

6.7

6.2

5.0

5.0

6.7

6.2

0

6.7

120

UDMA

Mode 5

40

16.8

38

4.0

4.6

4.8

4.8

5.0

5.0

10.0

10.0

35

25

90

600X CompactFlash Card

UDMA

Mode 6

30 Sender

13.0 Note 3

29 Sender

2.6

3.5

4.0

4.0

5.0

5.0

10.0 Host

10.0 Host

25 Device

17.5 Sender

Recipient

Recipient

Sender

Sender

Device

Device

80 Device

Measure

location (see

Note 2)

t

t

t

t

t

t

t

t

t

t

t

t

Notes:

MLI

UI

AZ

ZAH

ZAD

ENV

RFS

RP

IORDYZ

ZIORDY

ACK

SS

20

0

20

0

20 70 20 70 20 70 20 55 20 55 20 50 20 50 Host

160

0

20

50

1) All timing measurement switching points (low to high and high to low) shall be taken at 1.5 V.

2) All signal transitions for a timing parameter shall be measured at the connector specified in the measurement

location column. For example, in the case of tRFS, both STROBE and –DMARDY transitions are measured at

the sender connector.

3) The parameter tCYC shall be measured at the recipient’s connector farthest from the sender.

10

75

20

20

0

20

0

125

0

20

50

20

0

10

70

20

20

0

100

0

20

50

10

60

20

20

0

20

0

100

0

20

50

10

60

20

20

0

20

0

100

0

20

50

10

60

20

20

0

20

0

85

0

20

50

20 Host

0 Host

10

50

20

10 Note 5

20 Host

0 Device

50 Sender

85 Recipient

20 Device

0 Device

20 Host

50 Sender

Transcend Information Inc.

V1.0

Page 34

T

34

T

T

S

S

S

8

G

~

1

6

8

8

G

G

G

~

1

6

G

~

1

6

G

4) The parameter tLI shall be measured at the connector of the sender or recipient that is responding to an

incoming transition from the recipient or sender respectively. Both the incoming signal and the outgoing

response shall be measured at the same connector.

5) The parameter tAZ shall be measured at the connector of the sender or recipient that is driving the bus but must

release the bus the allow for a bus turnaround.

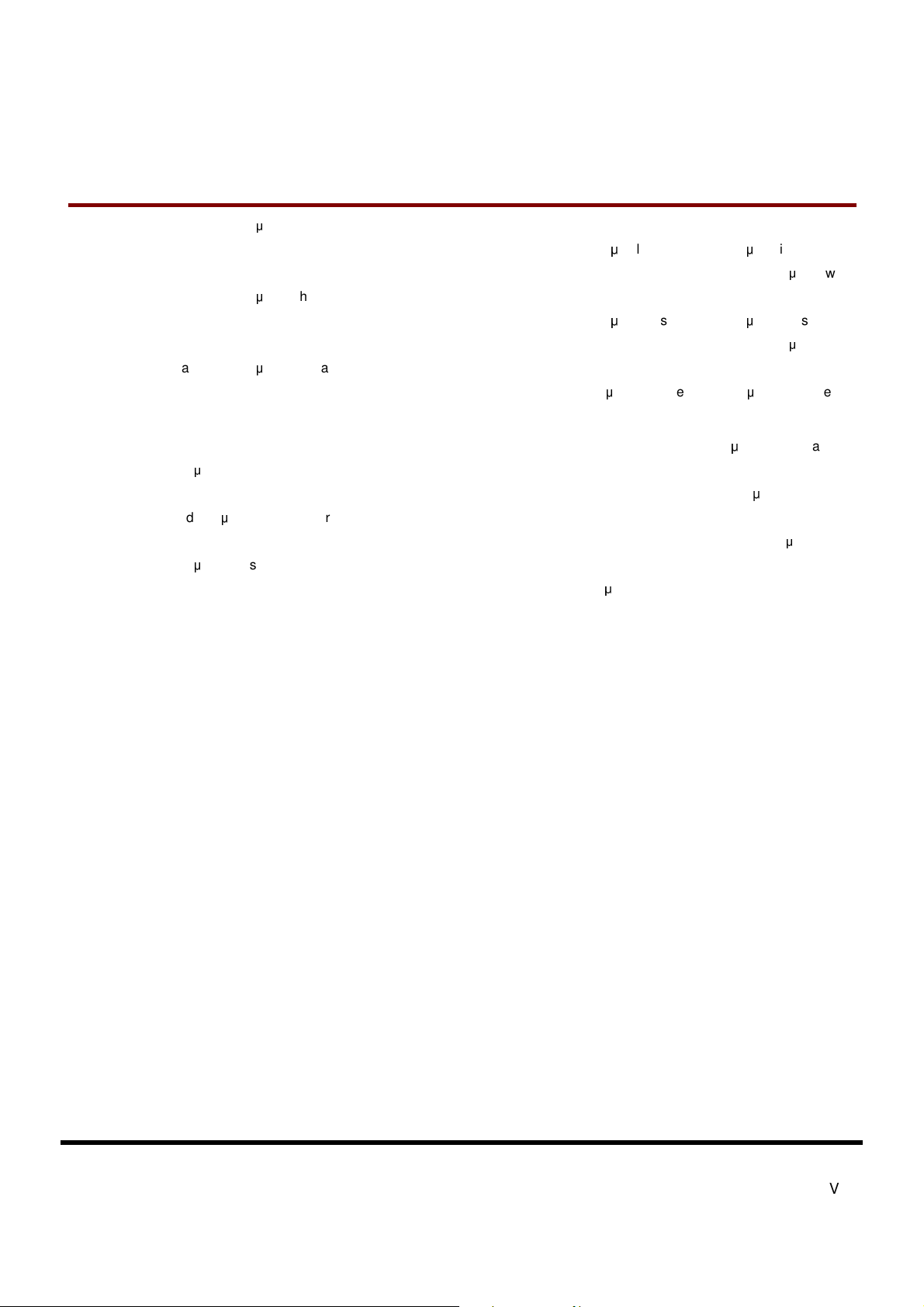

Name Comment

2CYCTYP

t

CYC

t

2CYC

t

t

DS

t

DH

t

DVS

t

DVH

CS

t

CH

t

CVS

t

CVH

t

ZFS

t

t

DZFS

t

FS

t

LI

MLI

t

UI

t

AZ

t

ZAH

t

ZAD

t

t

ENV

t

RFS

RP

t

IORDYZ

t

ZIORDY

t

ACK

t

t

SS

C

F

6

0

0

6

6

0

0

0

0

600X CompactFlash Card

C

C

F

F

Typical sustained average two cycle time

Cycle time allowing for asymmetry and clock variations (from STROBE edge to STROBE edge)

Two cycle time allowing for clock variations (from rising edge to next rising edge or from falling edge to

next falling edge of STROBE)

Data setup time at recipient (from data valid until STROBE edge) 2, 5

Data hold time at recipient (from STROBE edge until data may become invalid) 2, 5

Data valid setup time at sender (from data valid until STROBE edge) 3

Data valid hold time at sender (from STROBE edge until data may become invalid) 3

CRC word setup time at device 2

CRC word hold time device 2

CRC word valid setup time at host (from CRC valid until -DMACK negation) 3

CRC word valid hold time at sender (from -DMACK negation until CRC may become invalid) 3

Time from STROBE output released-to-driving until the first transition of critical timing.

Time from data output released-to-driving until the first transition of critical timing.

First STROBE time (for device to first negate DSTROBE from STOP during a data in burst)

Limited interlock time 1

Interlock time with minimum 1

Unlimited interlock time 1

Maximum time allowed for output drivers to release (from asserted or negated)

Minimum delay time required for output

drivers to assert or negate (from released)

Envelope time (from -DMACK to STOP and -HDMARDY during data in burst initiation and from

DMACK to STOP during data out burst initiation)

Ready-to-final-STROBE time (no STROBE edges shall be sent this long after negation of -DMARDY)