Transcend TX2400KLU-4GK Description

240PIN DDR3 2400Mhz UDIMM

T

X

2

4

0

0

K

L

U

-

4

G

K

T

X

2

4

0

0

K

L

U

-

4

T

X

2

4

0

0

K

L

U

G

-

4

G

K

K

aXeRAM 4GB Kit With 256Mx8 CL10 at 1.65V

Description

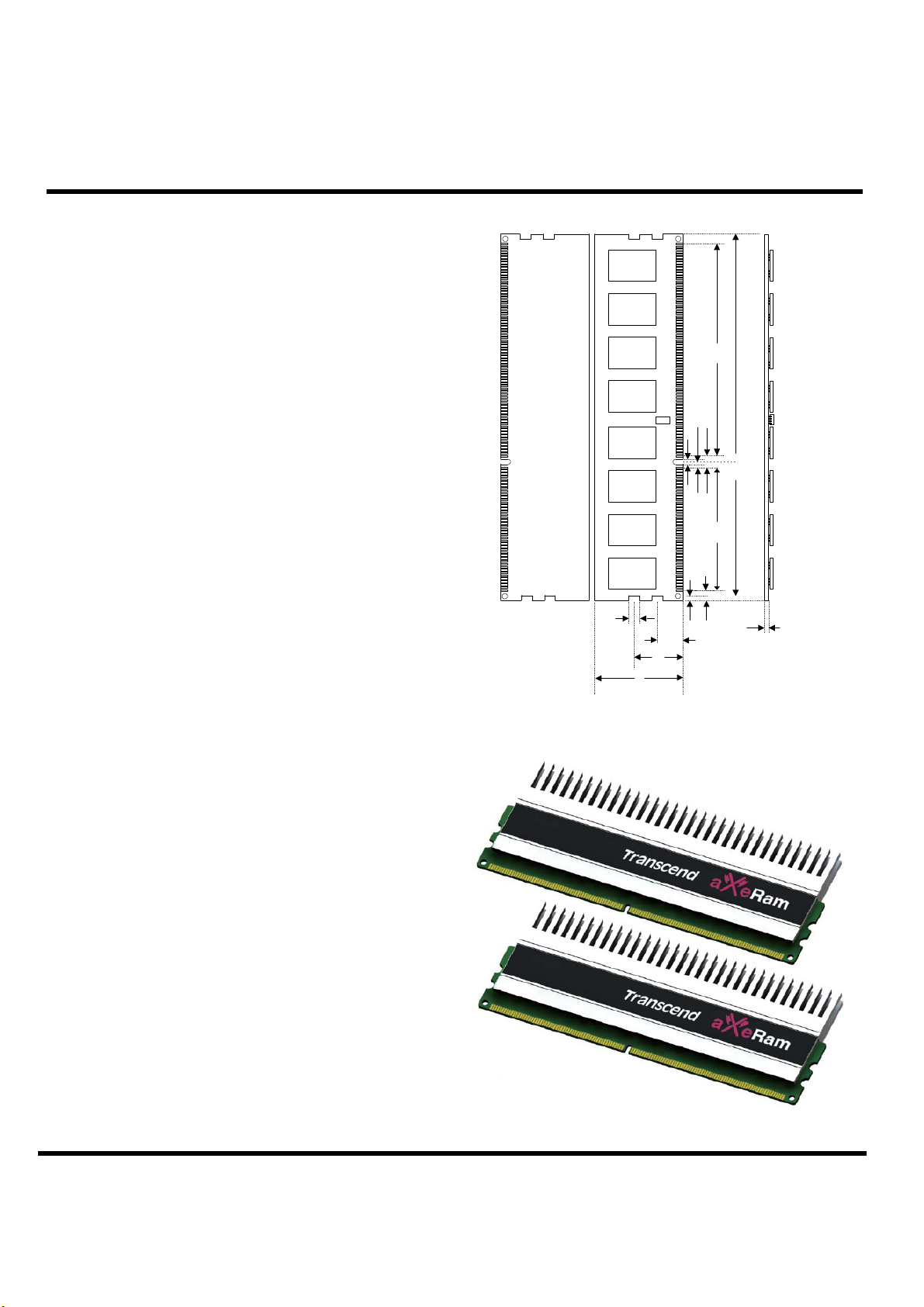

The TX2400KLU-4GK consists of 2pcs 2GB DDR3

SDRAM modules. The 2GB module is a 256M x 64bits

DDR3-2400 Unbuffered DIMM. The 2GB module

consists of 8pcs 256Mx8bits DDR3 SDRAMs in FBGA

packages and a 2048 bits serial EEPROM on a 240-pin

printed circuit board. The TX2400KLU-4GK is a Dual

In-Line Memory Module and is intended for mounting into

240-pin edge connector sockets.

Synchronous design allows precise cycle control with the

use of system clock. Data I/O transactions are possible

on both edges of DQS. Range of operation frequencies,

programmable latencies allow the same device to be

useful for a variety of high bandwidth, high performance

memory system applications.

Features

• RoHS compliant products.

Placement

B

D

E

F

A

C

G

H

I

K

L

M

J

• Tested at SPD settings:

2400MHz 10-12-11-28 at 1.65V

• SPD programmed at:

JEDEC standard 1333MHz 9-9-9-24 at 1.5V

XMP support 2400MHz 10-12-11-28 at 1.65V

• Max clock Freq: 1200MHZ; 2400Mb/S/Pin.

• Programmable CAS Latency: 10

• 8 bit pre-fetch

• Burst Length: 4, 8

• Bi-directional Differential Data-Strobe

• Internal calibration through ZQ pin

• On Die Termination with ODT pin

• Serial presence detect with EEPROM

• Asynchronous reset

Product With Heatsink

Transcend Information Inc.

1

240PIN DDR3 2400Mhz UDIMM

T

X

2

4

0

0

K

L

U

-

4

G

K

T

X

2

4

0

0

K

L

U

-

4

T

X

2

4

0

0

K

L

U

G

-

4

G

K

K

aXeRAM 4GB Kit With 256Mx8 CL10 at 1.65V

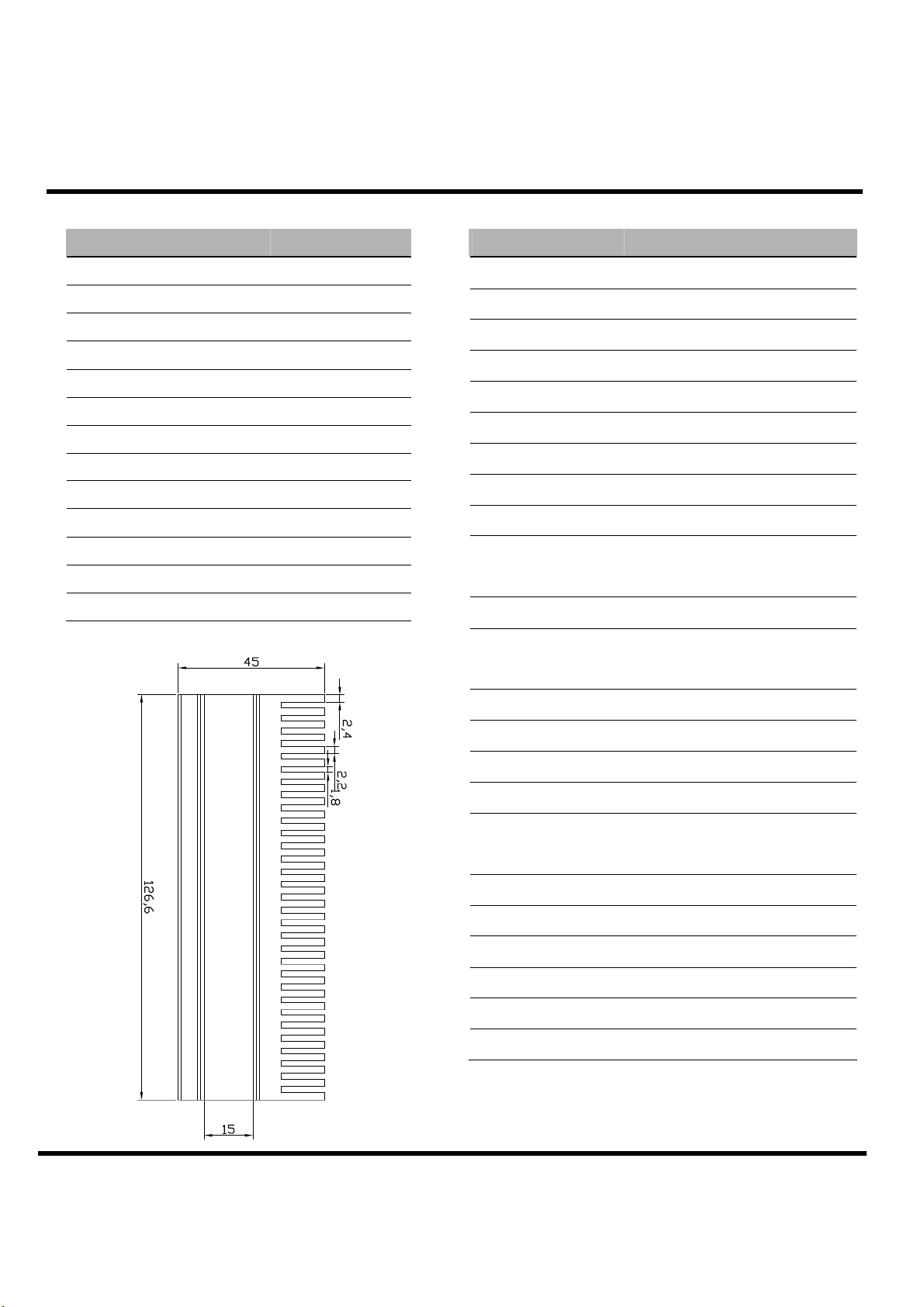

Module Dimensions

Side Millimeters Inches

A 133.35±0.15 5.250±0.006

B 71 2.795

C 47 1.850

D 5 0.197

E 2.5 0.0980

F 1.5±0.10 0.059±0.039

G 5.175 0.204

H 2.311 0.091

I 3±0.1 0.118±0.00394

J 9.5 0.374

K 17.3 0.681

L 30±0.15 1.181±0.006

M 1.27±0.10 0.050±0.004

Heatsink Dimensions

Pin Identification

Symbol Function

A0~A15, BA0~BA2 Address Inputs

/RAS Row Address Strobe

/CAS Column Address Strobe

/WE Write Enable

/S0, /S1 Chip Selects

CKE0, CKE1 Clock Enables

ODT0, ODT1 On-die termination control

DQ0~DQ63 Data Input/Output

CB0~CB7 ECC Check bits

DQS0~DQS8

Data Strobe

/DQS0~/DQS8

DM0~DM8 Data Masks

CK0, /CK0

Clocks Input

CK1, /CK1

/RESET Reset Pin

/EVENT Temperature Event Pin

VDD Core and I/O Power

VSS Ground

VREFDQ

VREFCA

VTT Termination Voltage

VDDSPD SPD Power

SCL SPD Clock Input

SDA SPD Data

SA0~SA2 SPD Address

NC No Connection

Input/Output Reference

Transcend Information Inc.

2

Loading...

Loading...