Page 1

Programmable Controller

PROGRAMMING MANUAL

Compatible modules

PC2/L2 series

PC2J series

PC3J series

SUB-CPU

Page 2

PROGRAMMING MANUAL

1. MAKING SEQUENCE CIRCUITS

2. EXECUTION OF PROGRAM

3. PARAMETER

4. USER MEMORY STRUCTURE

5. INSTRUCTION WORDS

1

2

3

4

5

Page 3

FOREWORD

Thank you very much for purchasing our Programmable Controller.

This operation manual is the programming manual for TOYOPUC-PC2/3 series.

For safety use of this product, read carefully this manual and other related individual operation

manuals altogether. Further, keep these manuals in file at an easily accessible place so that

persons concerned can read them anytime as necessary.

The distributor or dealer of this product is requested to hand over the said manuals to the end

user without fail.

The specification and other relevant information included in this Manual are subject to change

due to better improvement without prior notice.

Any product applicable to the strategic goods (or services) stipulated in the Foreign Exchange

and Foreign Trade Control Act is subject to export license of the Japanese Government, where

exported to overseas.

Should this product result in trouble during the guarantee period due to somewhat cause

attributed to our responsibility, necessary device(s) or parts(s) shall be repaired or replaced at

our discretion. For any other trouble or accident out of our responsibility , our company shall be

released from the responsibility for injury which may arise from such a trouble or accident.

i

Page 4

FOR SAFETY OPERATION

Before installing, operating, maintaining and checking, read carefully this Manual without fail for

proper and safety operation and work. Any operator and any maintenance man who relate to

this product (Programmable Controller) are requested to acquire the knowledge on devices,

safety information and cautions before being engaged in the operation and maintenance. This

Manual classifies the safety caution level into "WARNING" and "CAUTION" using alert symbols

as follows.

Failure to observe the instructions given in this Manual could result

in death or bodily injury of the operator.

Failure to observe the instructions given in this Manual could result in

risk of bodily injury or physical damage to equipment, etc.

Don't overhaul the module and don't touch the module internals,

with the power switch kept ON.

Failure to observe this instruction could result in electric shock.

Don't touch the terminals with the power switch kept ON.

Failure to observe this instruction could result in electric shock.

Execute write during PC run (write during run) only when cyclic

operation of main equipment/machine is in shutdown.

Failure to observe this instruction could result in breakdown of its

device(s) and bodily injury from mis-operation, if any.

In handling the lithium battery, read and observe " Lithium Battery

Handling Cautions " given in this Manual. Improper handling

would cause liquid leak, overheat, sparking, and fracture, which

could then result in breakdown of units and devices and bodily

injury.

Regarding safe-related signals and emergency stop circuit, etc.,

handle those signals in external units without through this system.

ii

Page 5

Use this product under an environment which meets the

environmental general specification specified in this Manual.

Don't attach/detach each module to/from its base, with the power

switch kept ON.

Don't touch directly the electronic circuits inside the module.

Failure to observe this instruction could result in breakdown of the

module by static electricity.

iii

Page 6

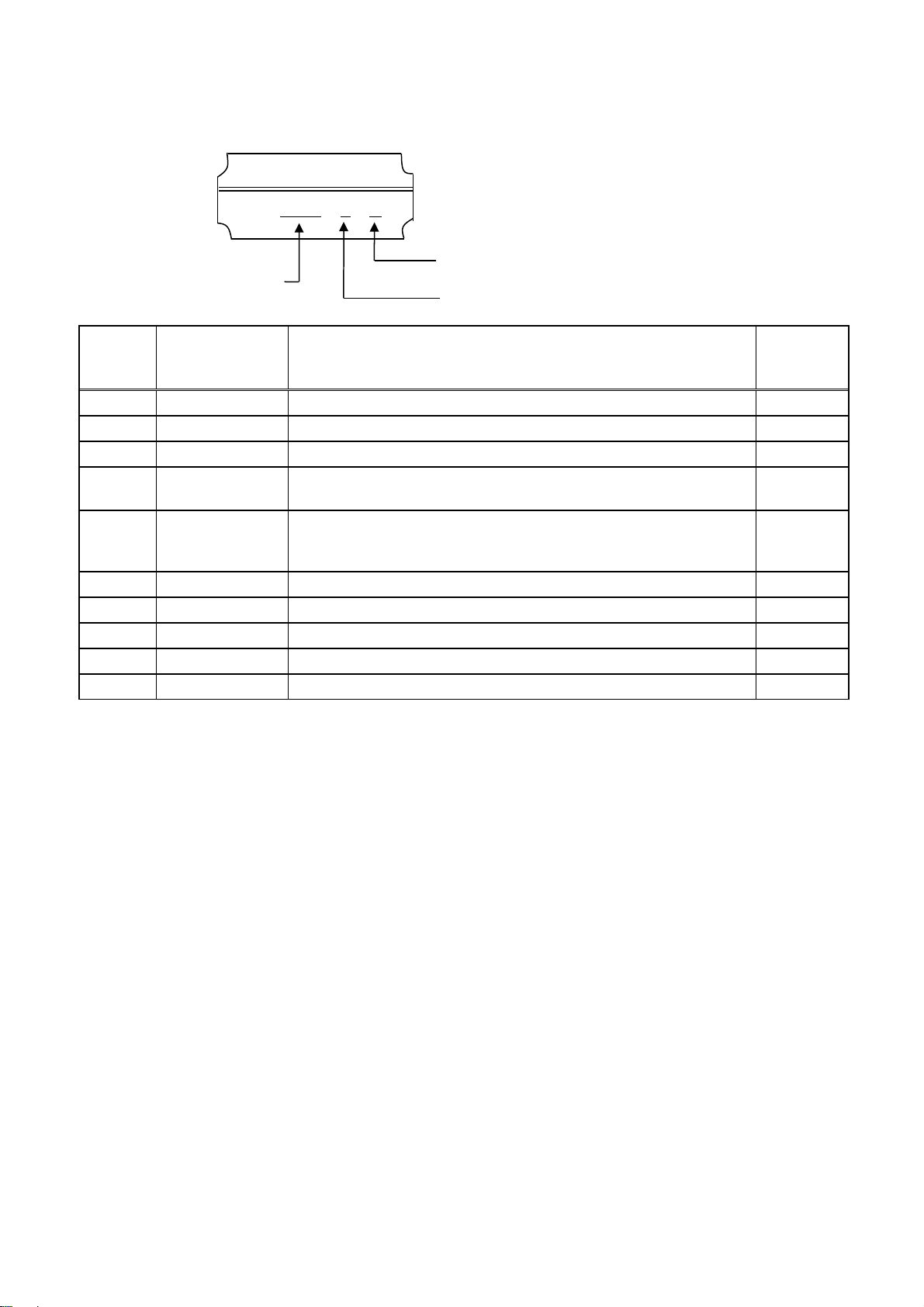

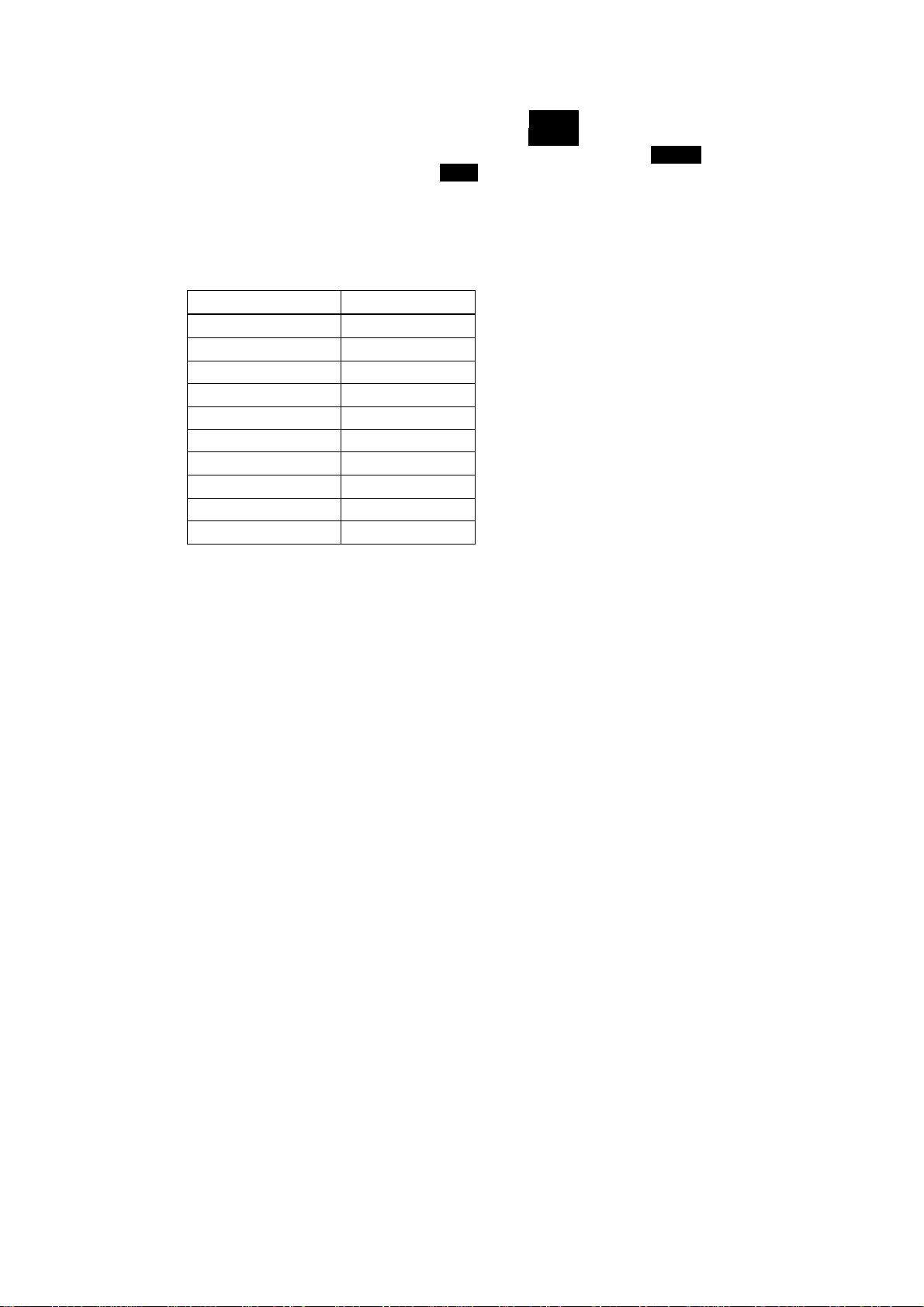

REVISION HISTORY OF OPERATION MANUAL

g

j

T

Operation manual revision No. is added as a part of Manual No. described on the cover sheet of

the manual.

Operation Manual No.

T - 3 0 7 # E

N: Japanese E: English

Series No.

Revision symbol

Revision

No.

1 2003.06.30 1st revision

2 2004.09.02 Correction of MSET/CSET command

3 2005.01.10 Correction of CSET command

4 2006.01.01

5 2006.03.20

6 2006.11.10 Correct missing description.

7 2007.03.30 Correction of I/O address allocation

8 2012.05 TOYODA brand logo added on the front cover

9 2013.04 Correction of errors

10 2022.03 TOYODA brand logo removed

Date of Revision Revision Details

The company name “TOYODA MACHINE WORKS,LTD”

is chan

ed to “JTEKT CORPORATION”

Special register was corrected.

The device that was able to use the PC3 series was corrected.

Clock ad

ustment instruction is added

Equivalent

Japanese

manual

version

-3079N

iv

Page 7

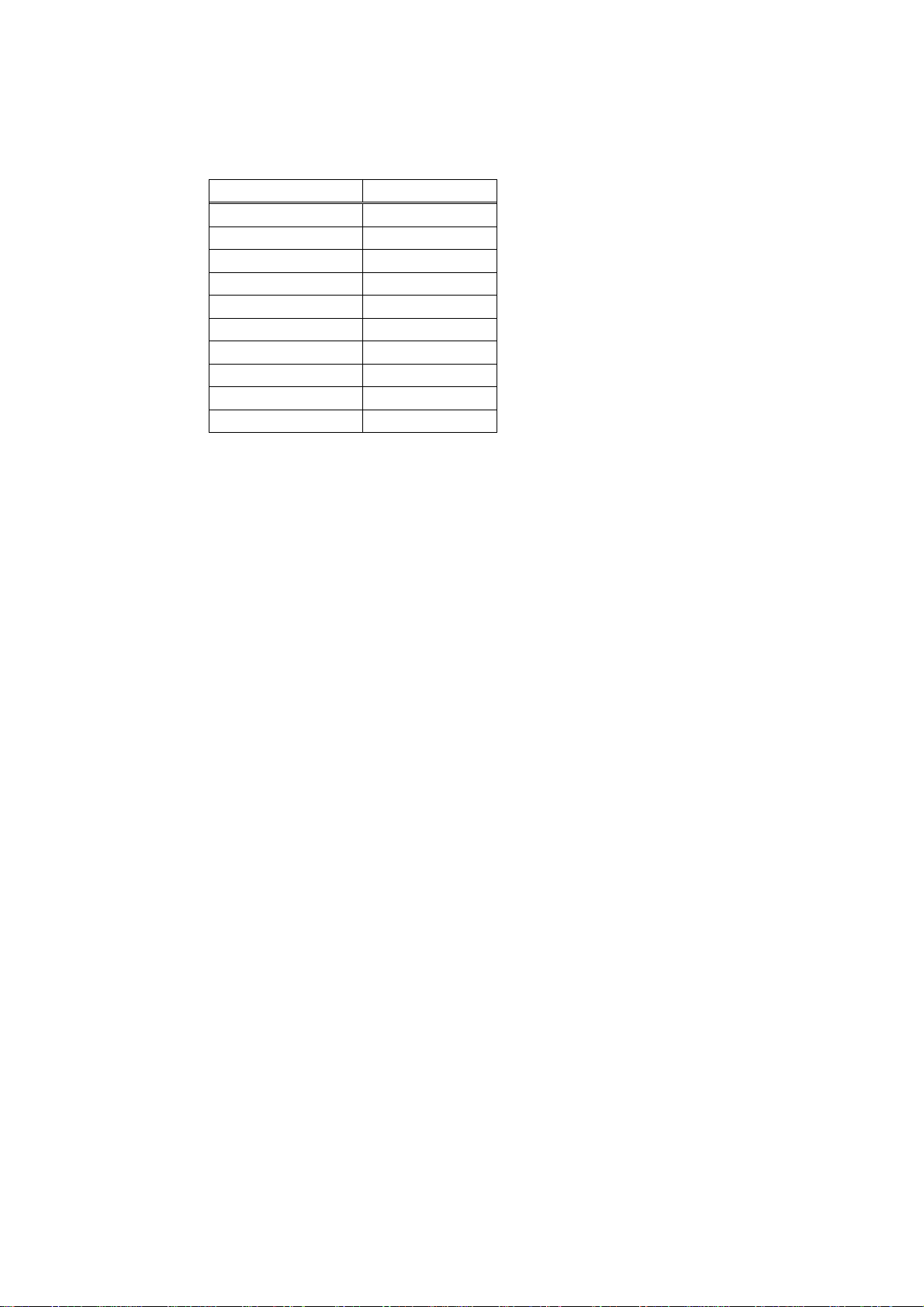

Composition of Related Operation Manuals

Operation

manual No.

T-822#E PC2 series

T-833#E PC2J series

T-845#E PC2J SUB-CPU

T-862#E PC2JN

T-873#E

T-880#E PC2S1 series

T-300#E PC3J series

T-303#E PC3JNF/PC3JNM

T-304#E PC3JM

T-310#E PC3JD

T-320#E PC3JB series

T-311#E PC3JG

PC2JNM

PC2JNF

Title Outline

This manual describes the basic

operating procedure, functions, and

specifications of PC2 series.

This manual describes the basic

operating procedure, functions, and

specifications of PC2J series.

This manual describes the basic operating

procedure, functions, and specifications of

SUB-CPU.

This manual describes the basic operating

procedure, functions, and specifications of

PC2JN.

This manual describes the basic operating

procedure, functions, and specifications of

PC2JNM/PC2JNF.

This manual describes the basic operating

procedure, functions, and specifications of

PC2S1 series.

This manual describes the basic operating

procedure, functions, and specifications of

PC3J series.

This manual describes the basic operating

procedure, functions, and specifications of

PC3JNF/PC3JNM.

This manual describes the basic operating

procedure, functions, and specifications of

PC3JM.

This manual describes the basic operating

procedure, functions, and specifications of

PC3JD.

This manual describes the basic operating

procedure, functions, and specifications of

PC3JB series.

This manual describes the basic operating

procedure, functions, and specifications of

PC3JG.

v

Page 8

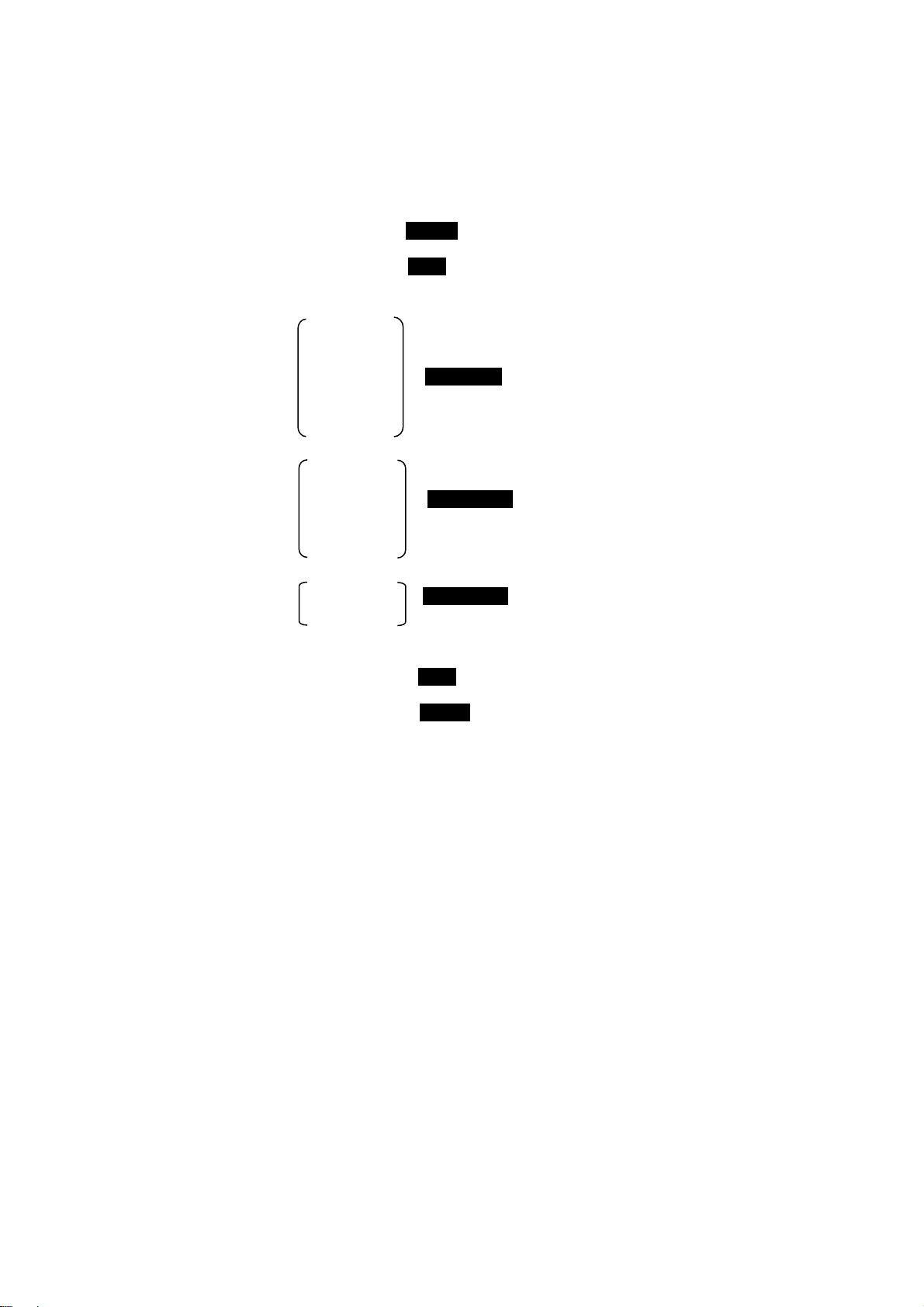

This manual describes programming with the TOYOPUC-PC2/3 series.

Although the basic programming method is common to all the PC2/3 series, there are differences

in the application instructions and the external I/O devices which can be used and in the program

capacities, etc. Model-specific functions are marked as shown below. Common functions are not

marked.

Along with this manual, it is recommended that you read the operation manuals for TOUOPUC.

PC/L2-specific functions------------------PC2/L2

PC2J series-specific function------------PC2J

The PC2J series controllers are classified into two types according to the program capacity.

8KW

PC2J

PC2JS

PC2JR

PC2JF

PC2F

PC2FS

PC2J-8KW

16KW

PC2JC

PC2J16

SUB-CPU

PC2JN

PC2J-16KW

32KW

PC2JNM

PC2JNF

PC2J-32KW

PC3J-specific functions---------------PC3J

PC3JG-specific functions-------------PC3JG

Ver.---------This is usable for the specific version or later.

PC2/L2, PC2J : Ver 3.50 or later

PC2JS/JR : Ver2.30 or later

PC2JC : Ver 3.20 or later

PC2J16 : Ver2.10 or later

SUB-CPU : Ver2.50 or later

PC2JNM/PC2JNF : Ver2.00 or later

This is not usable for PC2JN.

vi

Page 9

Contents

FOREWORD

FOR SAFETY OPERATION

REVISION HISTORY OF OPERATION MANUAL

Composition of Related Operation Manuals

Contents 1

1. MAKINK SEQUENCE CIRCUITS.........................................................................................................................1-1

1.1. Usage of TOYOPUC...................................................................................................................................... 1-1

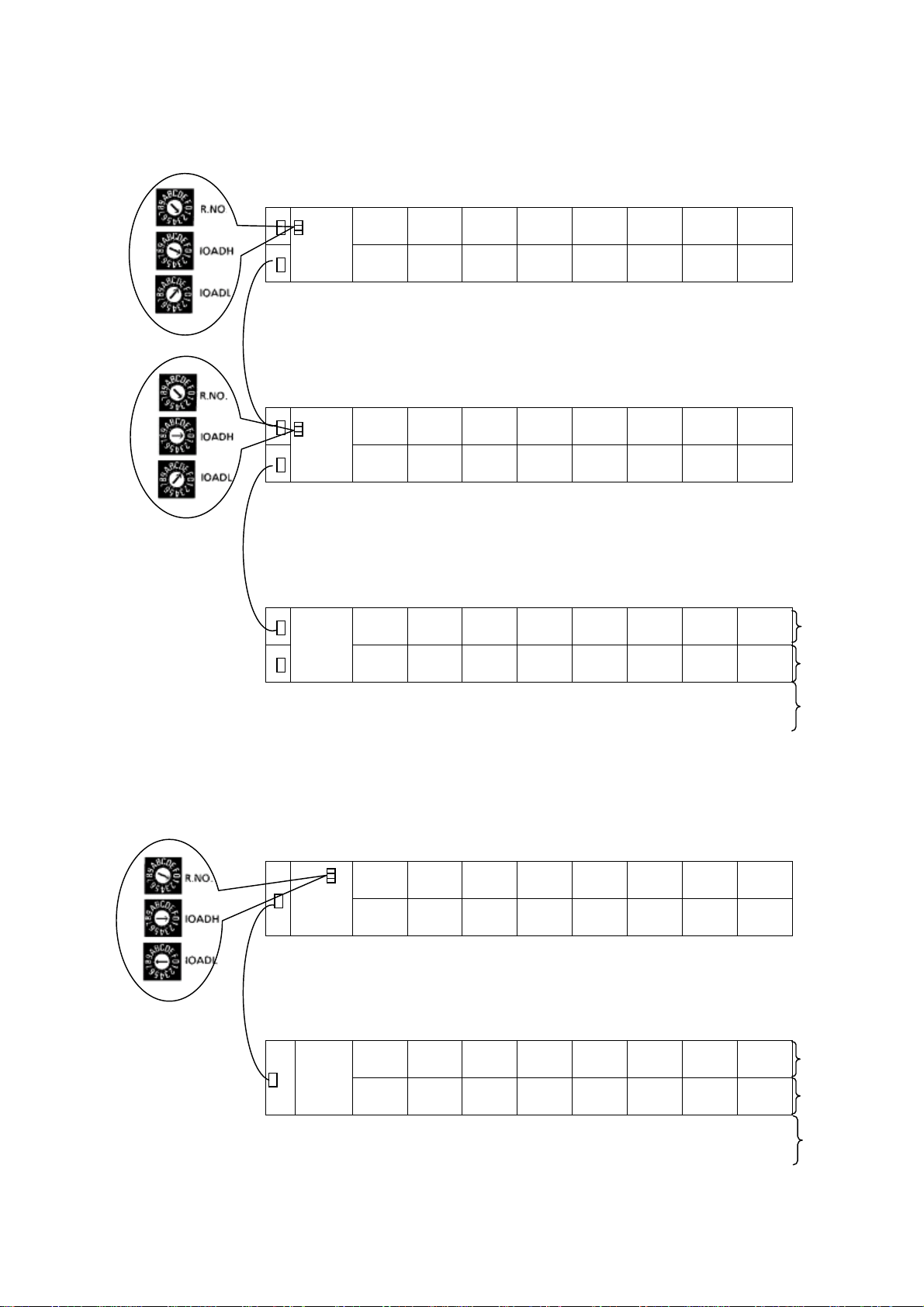

1.1.1. Connection between I/O devices and TOYOPUC...................................................................................1-1

1.1.2. I/O address.............................................................................................................................................. 1-1

1.2. Circuit diagram configuration ......................................................................................................................... 1-4

1.3. I/O circuit ........................................................................................................................................................ 1-5

1.3.1. Input section ............................................................................................................................................1-5

1.3.2. Output section..........................................................................................................................................1-6

1.4. Logic section ..................................................................................................................................................1-7

1.4.1. Internal relay (dummy output).................................................................................................................. 1-7

1.4.2. Timer........................................................................................................................................................ 1-8

1.4.3. Counter....................................................................................................................................................1-9

1.4.4. Keep relay..............................................................................................................................................1-10

1.4.5. Edge detection....................................................................................................................................... 1-11

1.4.6. Special relay..........................................................................................................................................1-12

1.4.7 Link relay ................................................................................................................................................1-37

1.4.8. Designation of Register Bit PC3J........................................................................................................ 1-38

1.5. Application instruction...................................................................................................................................1-39

1.5.1. Application instruction............................................................................................................................ 1-39

1.5.2. Data register.......................................................................................................................................... 1-39

1.5.3. File register............................................................................................................................................ 1-40

1.5.4. Link register........................................................................................................................................... 1-40

1.5.5. Current value register............................................................................................................................1-40

1.5.6. Buffer register PC3JG............................................................................................................................1-40

1.5.7. Special register...................................................................................................................................... 1-41

2. EXECUTION OF PROGRAM............................................................................................................................... 2-1

2.1. Processing operation......................................................................................................................................2-1

2.2. Subroutine......................................................................................................................................................2-4

2.3. Interrupt program PC2/L2............................................................................................................................ 2-5

2.3.1. Periodic interrupt......................................................................................................................................2-5

2.3.2. External interrupt .....................................................................................................................................2-6

2.3.3. Interrupt program considerations.............................................................................................................2-7

2.4. Scan time ....................................................................................................................................................... 2-8

3. PARAMETER........................................................................................................................................................ 3-1

3.1. Contents of parameters.................................................................................................................................. 3-1

3.2. Setting the parameters................................................................................................................................... 3-4

3.2.1. Auto setting by CPU module....................................................................................................................3-4

3.2.1.1. In case of PC2/L2, PC2J.............................................................................................................. 3-4

3.2.1.2. In case of PC3J series.................................................................................................................3-8

3.2.2. Setting with a peripheral device...............................................................................................................3-9

4. USER MEMORY STRUCTURE............................................................................................................................4-1

4.1. Program memory structure ............................................................................................................................ 4-1

4.1.1. In case of PC2/L, PC2J ........................................................................................................................... 4-1

4.1.2. In case of PC3J series............................................................................................................................. 4-2

4.2. Data memory structure................................................................................................................................. 4-11

4.2.1. In case of PC2/L, PC2J ......................................................................................................................... 4-1 1

4.2.1.1. Data memory map........................................................................................................................... 4-11

4.2.1.2. Data memory address..................................................................................................................... 4-12

4.2.2. In case of PC3J series........................................................................................................................... 4-15

4.2.2.1. Data memory map...........................................................................................................................4-15

4.2.2.2. I/O address table ........................................................................................................................4-18

5. INSTRUCTION WORDS.......................................................................................................................................5-1

5.1. Basic instructions ...........................................................................................................................................5-1

Page 10

5.1.1. Extension on the PC3J series .................................................................................................................5-2

1.STR, STR NOT............................................................................................................................................5-6

2.AND, AND NOT...........................................................................................................................................5-7

3.OR, OR NOT ...............................................................................................................................................5-8

4.AND STR.....................................................................................................................................................5-9

5.OR STR..................................................................................................................................................... 5-10

6.

...

OUT....................................................................................................................................................... 5-11

7.

....

SET.......................................................................................................................................................5-12

8.

...

RST.......................................................................................................................................................5-13

9.PTS, NTS...................................................................................................................................................5-14

10.FPS, FRD, FPP .......................................................................................................................................5-16

11.

...

FST.......................................................................................................................................................5-17

12..NOT.......................................................................................................................................................5-18

13..NOP.......................................................................................................................................................5-19

5.2. Timer and counter instructions..................................................................................................................... 5-20

1.TMRH (Direct mode 10ms timer) .......................................................................................................... 5-25

2.TMRH (Indirect mode 10ms timer)........................................................................................................5-26

3.TMR (Direct mode 100ms timer)...........................................................................................................5-27

4.TMR (Indirect mode 100ms timer) ........................................................................................................5-28

5.TMRSH (Direct mode 10ms integrating timer)...................................................................................... 5-29

6.TMRSH (Indirect mode 10ms integrating timer) ................................................................................... 5-30

7.TMRS (Direct mode 100 ms integrating timer) .....................................................................................5-31

8.TMRS (Indirect mode 100 ms integrating timer)...................................................................................5-32

9.CNT (Direct mode up counter)..............................................................................................................5-33

10.CNT (Indirect mode up counter).......................................................................................................... 5-34

11.CNTD (Direct mode down counter).....................................................................................................5-35

12.CNTD (Indirect mode down counter) ..................................................................................................5-36

13.CNTH (Direct mode up/down counter)................................................................................................5-37

14.CNTH (Indirect up/down counter) .......................................................................................................5-39

15.ETMRH Extended 10ms Timer...........................................................................................................5-41

16.ETMR Extended 100ms Timer............................................................................................................ 5-42

17.ETMRSH Extended 10ms Integrating Timer....................................................................................... 5-43

18.ETMRS Extended 100ms Integrating Timer .......................................................................................5-44

19.ECNT Extended Counter (UP)............................................................................................................ 5-45

20.ECNTD Extended Counter (Down).....................................................................................................5-46

21.ECNTH Extended Counter (Up-Down) ............................................................................................... 5-47

5.3. Contact type application instructions............................................................................................................5-48

1.=H 2-digit hexadecimal constant comparison (=)..................................................................................5-50

2.=D 3-digit decimal constant comparison (=)..........................................................................................5-51

3.=N Byte data comparison (=) ................................................................................................................5-52

4.W=H 4-digit hexadecimal constant comparison (=).............................................................................. 5-53

5.W=D 5-digit decimal constant comparison (=)......................................................................................5-54

6.W=N Word data comparison (=)............................................................................................................5-55

7.D=H 8-digit hexadecimal constant comparison (=) *.............................................................................5-56

8.D=D 10-digit decimal constant comparison (=) * ..................................................................................5-57

9.D=N 32-bit data comparison (=) * ......................................................................................................... 5-58

10.<>H 2-digit hexadecimal constant comparison (<>)...........................................................................5-59

11.<>D 3-digit decimal constant comparison (<>)....................................................................................5-60

12.<>N Byte data comparison (<>)..........................................................................................................5-61

13.W<>H 4-digit hexadecimal constant comparison (<>)........................................................................ 5-62

14.W<>D 5-digit decimal constant comparison (<>)................................................................................5-63

15.W<>N Word data comparison (<>)..................................................................................................... 5-64

16.D<>H 8-digit hexadecimal constant comparison (<>) * ...................................................................... 5-65

17.D<>D 10-digit decimal constant comparison (<>) *............................................................................5-66

18.D<>N 32-bit data comparison (<>) * ...................................................................................................5-67

19.>H 2-digithexadecimal constant comparison (>)................................................................................. 5-68

20.>D 3-digit decimal constant comparison (>)........................................................................................5-69

21.>N Byte data comparison (>) .............................................................................................................. 5-70

22.W>H 4-digit hexadecimal constant comparison (>)............................................................................5-71

23.W>D 5-digit decimal constant comparison (>).................................................................................... 5-72

Page 11

24.W>N Word data comparison (>)..........................................................................................................5-73

25.D>H 8-digit hexadecimal constant comparison (>) *........................................................................... 5-74

26.D>D 10-digit decimal constant comparison (>) * ................................................................................5-75

27.D>N 32-bit data comparison (>) * ....................................................................................................... 5-76

28.>=H 2-digit hexadecimal constant comparison (>=)...........................................................................5-77

29.>=D 3-digit decimal constant comparison (>=)................................................................................... 5-78

30.>=N Byte data comparison (>=)..........................................................................................................5-79

31.W>=H 4-digit hexadecimal constant comparison (>=)........................................................................ 5-80

32.W>=D 5-digit decimal constant comparison (>=)................................................................................5-81

33.W>=N Word data comparison (>=)..................................................................................................... 5-82

34.D>=H 8-digit hexadecimal constant comparison (>=) * ...................................................................... 5-83

35.D>=D 10-digit decimal constant comparison (>=) *............................................................................5-84

36.D>=N 32-bit data comparison (>=) * ...................................................................................................5-85

37.<H 2-digit hexadecimal constant comparison (<)................................................................................5-86

38.<D 3-digit decimal constant comparison (<)........................................................................................5-87

39.<N Byte data comparison (<) *............................................................................................................ 5-88

40.W<H 4-digit hexadecimal constant comparison (<)............................................................................5-89

41.W<D 5-digit decimal constant comparison (<).................................................................................... 5-90

42.W<N Word data comparison (<) *.......................................................................................................5-91

43.D<H 8-digit hexadecimal constant comparison (<) *........................................................................... 5-92

44.D<D 10-digit decimal constant comparison (<) * ................................................................................5-93

45.D<N 32-bit data comparison (<) * ....................................................................................................... 5-94

46.<=H 2-digit hexadecimal constant comparison (<=)...........................................................................5-95

47.<=D 3-digit decimal constant comparison (<=)................................................................................... 5-96

48.<=N Byte data comparison (<=) *........................................................................................................5-97

49.W<=H 4-digit hexadecimal constant comparison (<=)........................................................................ 5-98

50.W<=D 5-digit decimal constant comparison (<=)................................................................................5-99

51.W<=N Word data comparison (<=) *................................................................................................. 5-100

52.D<=H 8-digit hexadecimal constant comparison (<=) * .................................................................... 5-101

53.D<=D 10-digit decimal constant comparison (<=) *..........................................................................5-102

54.D<=N 32-bit data comparison (<=) * .................................................................................................5-103

5.4. Output type application instructions Note)............................................................................................... 5-104

5.4.1. Transfer instructions ............................................................................................................................ 5-122

1.MOV 2-digit Hex constant transfer (FUN100).....................................................................................5-123

2.WMOV 4-digit Hex constant transfer (FUN101).................................................................................. 5-124

3.DMOV 8-digit Hex constant transfer (FUN102) ..................................................................................5-125

4.MOVP 2-digit BCD constant transfer (FUN103)..................................................................................5-126

5.WMOVP 4-digit BCD constant transfer (FUN1)..................................................................................5-127

6.DMOVP 8-digit BCD constant transfer (FUN104)...............................................................................5-128

7.MOVR 3-digit decimal constant transfer (FUN105) ............................................................................ 5-129

8.WMOVR 5-digit decimal constant transfer (FUN7)............................................................................. 5-130

9.DMOVR 10-digit decimal constant transfer (FUN106)........................................................................ 5-131

10.MOVQ 3-digit octal transfer (FUN107)..............................................................................................5-132

11.WMOVQ 6-digit octal transfer (FUN8)...............................................................................................5-133

12.DMOVQ 11-digit octal transfer (FUN108) .........................................................................................5-134

13.MOVT 2-digit Hex constant transfer to two places (FUN62).............................................................5-135

14.WMOVT 4-digit Hex constant transfer to two places (FUN 110).......................................................5-136

15.MOVE 1-byte data direct transfer (FUN90).......................................................................................5-137

16.WMOVE 2-byte data direct transfer (FUN0) .....................................................................................5-138

17.DMOVE 4-byte data direct transfer (FUN111)...................................................................................5-139

18.MOVF 1-byte data indirect transfer 1 (FUN74).................................................................................5-140

19.WMOVF 2-byte data indirect transfer 1 (FUN112)............................................................................5-141

20.DMOVF 4-byte data indirect transfer 1 (FUN113) *..........................................................................5-142

21.MOVG 1-byte data indirect transfer 2 (FUN75) ................................................................................5-143

22.WMOVG 2-byte data indirect transfer 2 (FUN114)........................................................................... 5-144

23.DMOVG 4-byte data indirect transfer 2 (FUN115) *..........................................................................5-145

24.MOVH 1-byte data indirect transfer 3 (FUN76).................................................................................5-146

25.WMOVH 2-byte data indirect transfer 3 (FUN116) ...........................................................................5-147

26.DMOVH 4-byte data indirect transfer 3 (FUN117) *.......................................................................... 5-148

27.BMOV1 Byte data block transfer 1 (FUN70).....................................................................................5-149

Page 12

28.BMOV2 Byte data block transfer 2 (FUN118) *.................................................................................5-150

29.WBMOV Word data block transfer (FUN119) *.................................................................................5-151

30.BMVI Byte data indirect block transfer (FUN71)...............................................................................5-152

31.WBMVI Word data indirect block transfer (FUN120) *......................................................................5-153

32.DIV Byte data delivery (FUN5)..........................................................................................................5-154

33.WDIV Word data delivery (FUN122).................................................................................................5-155

34.DDIV 32-bit data delivery (FUN123) *...............................................................................................5-156

35.BDIV Byte data block delivery(FUN72).............................................................................................5-157

36.WBDIV Word data block delivery(FUN126) ......................................................................................5-158

37.PUP Byte data extraction (FUN6) .....................................................................................................5-159

38.WPUP Word data extraction (FUN124) ............................................................................................5-160

39.DPUP 32-bit data extraction (FUN125) * ..........................................................................................5-161

40.BPUP Byte data block extraction(FUN73) ........................................................................................ 5-162

41.WBPUP Word data block extraction(FUN127).................................................................................. 5-163

42.SXCH 4-bit data exchange(FUN53)..................................................................................................5-164

43.XCH 8-bit data exchange(FUNl32) ................................................................................................... 5-165

44.WXCH 16-bit data exchange(FUN2)................................................................................................. 5-166

45.DXCH 32-bit data exchange(FUN133) *...........................................................................................5-167

46.BXCH Byte data block exchange(FUN134)......................................................................................5-168

47.WBXCH Word data block exchange (FUN 135) ...............................................................................5-169

48.JIS Storage in JIS code (FUN 109)...................................................................................................5-170

49.FIL1 Byte data fill 1 (FUN 77)............................................................................................................5-171

50.FIL2 Byte data fill 2 (FUN 128) * .......................................................................................................5-172

51.WFIL Word data fill (FUN 129) *........................................................................................................5-173

52.FILI1 Byte data indirect fill 1 (FUN 78)..............................................................................................5-174

53.FILI2 Byte data indirect fill 2 (FUN 130) * .........................................................................................5-175

54.WFILI Word data indirect fill (FUN 131) *..........................................................................................5-176

55.CMOV Byte data transfer on clearance confirmation (FUN 20)........................................................5-177

56.WCMOV Word data transfer on clearance confirmation (FUN 166)................................................. 5-178

57.CLR Matching data clearance (byte) (FUN 21).................................................................................5-179

58.WCLR Matching data clearance (Word) (FUN 167) ......................................................................... 5-180

59.REF External input transfer (FUN 283) !#..........................................................................................5-181

60.REFO External output transfer (FUN 284) !#.....................................................................................5-182

61.MOVJ 1-byte transfer from register to file register (FUN 144) %&.....................................................5-183

62.WMOVJ 2-byte transfer from register to file register (FUN 145) %&..................................................5-184

63.DMOVJ 4-byte transfer from register to file register (FUN 146) %&...................................................5-185

64.MOVK 1-byte transfer from file register to register (FUN 147) %&.....................................................5-186

65.WMOVK 2-byte transfer from file register to register (FUN 148) %&.................................................5-187

66.DMOVK 4-byte transfer from file register to register (FUN 149) %&..................................................5-188

5.4.2. Arithmetic operations...........................................................................................................................5-189

67.+ Byte data binary addition (FUN 168).............................................................................................. 5-190

68.W+ Word data binary addition (FUN 92)........................................................................................... 5-191

69.D+ 32-bit data binary addition (FUN 169) .........................................................................................5-192

70.+P 2-digit BCD addition (FUN 177)................................................................................................... 5-193

71.W+P 4-digit BCD addition (FUN 10) ................................................................................................. 5-194

72.D+P 8-digit BCD addition (FUN 178) ................................................................................................5-195

73.- Byte data binary subtraction (FUN 170) .........................................................................................5-196

74.W- Word data binary subtraction (FUN 93).......................................................................................5-197

75.D- 32-bit data binary subtraction (FUN 171).....................................................................................5-198

76.-P 2-digit BCD subtraction (FUN 179)...............................................................................................5-199

77.W-P 4-digit BCD subtraction (FUN 11)..............................................................................................5-200

78.D-P 8-digit BCD subtraction (FUN 180)............................................................................................ 5-201

79.* Byte data binary multiplication (FUN 172)...................................................................................... 5-202

80.W* Word data binary multiplication (FUN 94) ................................................................................... 5-203

81.D* 32-bit data binary multiplication (FUN 173)..................................................................................5-204

82.*P 2-digit BCD multiplication (FUN 181) ...........................................................................................5-205

83.W*P 4-digit BCD multiplication (FUN 182)........................................................................................5-206

84.D*P 8-digit BCD multiplication (FUN 183).........................................................................................5-207

85.W/B Word data binary division 1 (FUN 95) ....................................................................................... 5-208

86./ Byte data binary division (FUN 174) #.............................................................................................5-209

Page 13

87.W/ Word data binary division 2 (FUN 175) #.....................................................................................5-210

88.D/ 32-bit data binary division (FUN 176) #......................................................................................... 5-211

89./P 2-digit BCD division (FUN 184).....................................................................................................5-212

90.W/P 4-digit BCD division (FUN 185) ................................................................................................. 5-213

91.D/P 8-digit BCD division (FUN 186)..................................................................................................5-214

5.4.3 Logical operation instructions...............................................................................................................5-215

92.AND Byte data logical product(AND) (FUN 13)................................................................................5-216

93.WAND Word data logical product(AND) (FUN 187).......................................................................... 5-217

94.DAND 32-bit data logical product(AND) (FUN 188).......................................................................... 5-218

95.OR Byte data logical sum(OR) (FUN 14)..........................................................................................5-219

96.WOR Word data logical sum(OR) (FUN 189)................................................................................... 5-220

97.DOR 32-bit data logical sum(OR) (FUN 190) ...................................................................................5-221

98.NOT Byte data inversion (FUN 9) .....................................................................................................5-222

99.WNOT Word data inversion (FUN 191) ............................................................................................5-223

100.DNOT 32-bit data inversion (FUN 192)...........................................................................................5-224

101.XOR Byte data exclusive logical sum(XOR) (FUN 18) ................................................................... 5-225

102.WXOR Word data exclusive logical sum(XOR) (FUN 193) ............................................................ 5-226

103.DXOR 32-bit data exclusive logical sum(XOR) (FUN 194).............................................................5-227

5.4.4 Increment and decrement....................................................................................................................5-228

104.INC Byte data binary increment (FUN 195) ....................................................................................5-229

105.WINC Word data binary increment (FUN 63)..................................................................................5-230

106.DINC 32-bit data binary increment (FUN 196)................................................................................ 5-231

107.INCP 2-digit BCD increment (FUN 199)..........................................................................................5-232

108.WINCP 4-digit BCD increment (FUN 200)......................................................................................5-233

109.DINCP 8-digit BCD increment (FUN 201).......................................................................................5-234

110.DEC Byte data binary decrement (FUN 197)..................................................................................5-235

111.WDEC Word data binary decrement (FUN 64) ............................................................................... 5-236

112.DDEC 32-bit data binary decrement (FUN 198) .............................................................................5-237

113.DECP 2-digit BCD decrement (FUN 202).......................................................................................5-238

114.WDECP 4-digit BCD decrement (FUN 203)....................................................................................5-239

115.DDECP 8-digit BCD decrement (FUN 204).....................................................................................5-240

5.4.5. Search .................................................................................................................................................5-241

116.SRH1 Byte data search 1 (FUN 88)................................................................................................5-242

117.WSRH1 Word data search 1 (FUN 89)........................................................................................... 5-244

118.SRH2 Byte data search 2 (FUN 212)..............................................................................................5-246

119.WSRH2 Word data search 2 (FUN 213).........................................................................................5-248

120.DSRH 32-bit data Search (FUN 214)..............................................................................................5-250

5.4.6 Parity....................................................................................................................................................5-252

121.MKP1 Odd parity composition (FUN 83).........................................................................................5-253

122.MKP2 Even parity composition (FUN 81) .......................................................................................5-254

123.PCH1 Odd parity check (FUN 84)...................................................................................................5-255

124.PCH2 Even Parity check (FUN 82)................................................................................................. 5-256

5.4.7. Data conversion...................................................................................................................................5-257

125.BIN 2-digit BCD to 8-bit binary (FUN 152)...................................................................................... 5-258

126.WBIN 4-digit BCD to 16-bit binary (FUN 3).....................................................................................5-259

127.DBIN 8-bit BCD to 32-bit binary (FUN 153)....................................................................................5-260

128.BCD 8-bit binary to 2-digit BCD (FUN 154) .................................................................................... 5-261

129.WBCD 16-bit binary to 4-bit BCD (FUN 4)......................................................................................5-262

130.DBCD 32-bit binary to 8-digit BCD (FUN 155)................................................................................ 5-263

131.JBIN JIS code to binary (FUN 156).................................................................................................5-264

132.BJIS Binary to JIS code (FUN 157) ................................................................................................5-266

133.DECO 4 to 16 decoder (FUN 50)....................................................................................................5-268

134.ENCO 16 to 4 encoder (FUN 51)....................................................................................................5-270

135.SEG 7-segment decode (FUN 52).................................................................................................. 5-272

136.WTIM1 Hours, minutes, and seconds to seconds (FUN 158) ........................................................5-274

137.WTIM2 Seconds to hours, minutes and seconds (FUN 159) ......................................................... 5-276

138.CDSET Code conversion set (FUN 85).......................................................................................... 5-278

139.CDO1 Code conversion output 1 (FUN 86) ....................................................................................5-279

140.CDO2 Code conversion output 2 (FUN 87) ....................................................................................5-280

Page 14

5.4.8 Comparison..........................................................................................................................................5-281

141.CP Byte data comparison (FUN 17)................................................................................................5-282

142.WCP Word data comparison (FUN 12)...........................................................................................5-283

143.DCP 32-bit data comparison (FUN 211) .........................................................................................5-284

5.4.9. Bit operation.........................................................................................................................................5-285

144.BSET Byte data bit set (FUN 136) *................................................................................................ 5-286

145.WBSET Word data set (FUN 137).................................................................................................. 5-287

146.DBSET 32-bit data bit set (FUN 138) * ...........................................................................................5-288

147.BRST Byte data bit reset (FUN 139) * ............................................................................................ 5-289

148.WBRST Word data bit reset (FUN 140)..........................................................................................5-290

149.DBRST 32-bit data bit reset (FUN 141) *........................................................................................ 5-291

150.BPU Bit extraction (FUN 54) *.........................................................................................................5-292

151.WBPU Word data bit extraction (FUN 142).....................................................................................5-293

152.DBPU 32-bit data extraction (FUN 143) * .......................................................................................5-294

153.SUM Byte data ON-bit count (FUN 208).........................................................................................5-295

154.WSUM Word data ON-bit count (FUN 209).................................................................................... 5-296

155.DSUM 32-bit data ON-bit count (FUN 210) .................................................................................... 5-297

5.4.10 Shift....................................................................................................................................................5-298

156.SFR Byte data 1 bit right shift (FUN 217) *.....................................................................................5-299

157.WSFR Word data 1 bit right shift (FUN 36) *..................................................................................5-300

158.DSFR 32-bit data 1 bit right shift (FUN 218) *.................................................................................5-301

159.BSFR Byte data n bits right shift (FUN 224) *.................................................................................5-302

160.WBSFR Word data n bits right shift (FUN 225) *............................................................................5-303

161.DBSFR 32-bit data n bits right shift (FUN 226) *.............................................................................5-304

162.SFL Byte data 1 bit left shift (FUN 219) *........................................................................................5-305

163.WSFL Word data 1 bit left shift (FUN 37) * .....................................................................................5-306

164.DSFL 32-bit data 1 bit left shift (FUN 220) *....................................................................................5-307

165.BSFL Byte data n bits left shift (FUN 227) *....................................................................................5-308

166.WBSFL Word data n bits left shift (FUN 228) *...............................................................................5-309

167.DBSFL 32-bit data n bits left shift (FUN 229) *................................................................................5-310

168.SRL Byte data 1 bit right-left shift (FUN 221) * ............................................................................... 5-311

169.WSRL Word data 1 bit right-left shift (FUN 222) *...........................................................................5-312

170.DSRL 32-bit data 1 bit right-left shift (FUN 223) *...........................................................................5-313

171.BSRL Byte data n bits right-left shift (FUN 230)..............................................................................5-314

172.WBSRL Word data n bits right-left shift (FUN 231).........................................................................5-315

173.DBSRL 32-bit data n bits right-left shift (FUN 232) ......................................................................... 5-316

174.SUP 4 bit data upper-digit direction shift (FUN 251)....................................................................... 5-317

175.UP1 Byte data upper-digit direction shift 1 (FUN 91)......................................................................5-318

176.UP2 Byte data upper-digit direction shift 2 (FUN 252).................................................................... 5-319

177.WUP Word data upper-digit direction shift (FUN 253).................................................................... 5-320

178.DUP 32-bit data upper-digit direction shift (FUN 254) ....................................................................5-321

179.SDOWN 4 bit data lower-digit direction shift (FUN 255)................................................................. 5-323

180.DOWN Byte data lower-digit direction shift (FUN 256)...................................................................5-324

181.WDOWN Word data lower-digit direction shift (FUN 257) .............................................................. 5-325

182.DDOWN 32-bit data lower-digit direction shift (FUN 258)...............................................................5-326

183.FIFW Byte data FIFO write (FUN 160)............................................................................................ 5-328

184.WFIFW Word data FIFO write (FUN 161).......................................................................................5-329

185.DFIFW 32-bit data FIFO write (FUN 162).......................................................................................5-330

186.FIFR Byte data FIFO read (FUN 163).............................................................................................5-332

187.WFIFR Word data FIFO read (FUN 164)........................................................................................ 5-334

188.DFIFR 32-bit data FIFO read (FUN 165) ........................................................................................5-336

189.SFIN Accumulation shift input (FUN 68).........................................................................................5-338

190.SFOUT Accumulation shift output (FUN 69)...................................................................................5-340

5.4.11. Rotate.................................................................................................................................................5-342

191.RRC Byte data right rotate with carry (FUN 233) * .........................................................................5-343

192.WRRC Word data right rotate with carry (FUN 234) * ....................................................................5-344

193.DRRC 32-bit data right rotate with carry (FUN 235) *..................................................................... 5-345

194.RR Byte data right rotate without carry (FUN 242) *.......................................................................5-346

195.WRR Word data right rotate without carry (FUN 243) *.................................................................. 5-347

196.DRR 32-bit data right rotate without carry (FUN 244) *.................................................................. 5-348

Page 15

197.RLC Byte data left rotate with carry (FUN 236) *............................................................................ 5-349

198.WRLC Word data left rotate with carry (FUN 237) * .......................................................................5-350

199.DRLC 32-bit data left rotate with carry (FUN 238) *........................................................................5-351

200.RL Byte data left rotate without carry (FUN 245) *.......................................................................... 5-352

201.WRL Word data left rotate without carry (FUN 246) *.....................................................................5-353

202.DRL 32-bit data left rotate without carry (FUN 247) * .....................................................................5-354

203.RLRC Byte data right-left rotate with carry (FUN 239).................................................................... 5-355

204.WRLRC Word data right-left rotate with carry (FUN 240)............................................................... 5-356

205.DRLRC 32-bit data right-left rotate with carry (FUN 241)............................................................... 5-357

206.RLR Byte data right-left rotate without carry (FUN 248) .................................................................5-358

207.WRLR Word data right-left rotate without carry (FUN 249) ............................................................ 5-359

208.DRLR 32-bit data right-left rotate without carry (FUN 250)............................................................. 5-360

5.4.12. Programmed branch.......................................................................................................................... 5-361

209.JMP JUMP (FUN 272).....................................................................................................................5-362

210.CALL Subroutine call (FUN 273).....................................................................................................5-363

211.RET Return from subroutine (FUN 464)..........................................................................................5-364

212.FOR Start repetition (FUN 472) #....................................................................................................5-365

213.FORN Start repetition (indirect) (FUN 476) #...................................................................................5-366

214.NEXT End of repetition (FUN 480) #...............................................................................................5-367

5.4.13 Master control ....................................................................................................................................5-368

215.MC Master control set (FUN 440)...................................................................................................5-369

216.MCR Master control reset (FUN 444) .............................................................................................5-370

5.4.14. Input/output control............................................................................................................................5-371

217.RIO Input/output refresh (FUN 280) !..............................................................................................5-372

218.RI Input refresh (FUN 281)..............................................................................................................5-373

219.RO Output refresh (FUN 282)......................................................................................................... 5-374

5.4.15. Sequential interrupt ........................................................................................................................... 5-375

220.DI Interrupt inhibit (FUN 276) %.......................................................................................................5-376

221.PDI Partial interrupt inhibit (FUN 278) %.........................................................................................5-377

222.EI Interrupt enable (FUN 277) %......................................................................................................5-378

223.PEI Partial interrupt enable (FUN 279) %........................................................................................5-379

224.RETI Return from interrupt routine (FUN 468) %.............................................................................5-380

5.4.16. Label.................................................................................................................................................. 5-381

225.START Main program start (FUN 448)............................................................................................5-382

226.END Main program end (FUN 452).................................................................................................5-383

227.PEND End of program (FUN 456)................................................................................................... 5-384

228.LABEL Label (FUN 460)..................................................................................................................5-385

5.4.17 Special module data transfer .............................................................................................................5-386

229.SPR Special module byte-data readout (for readout of file for the SIO module) (FUN 304)........5-387

230.SPW Special module byte-data write (for writing of file for the SIO module) (FUN 306)............. 5-389

231.HCR High-speed counter data readout (FUN 316) !.......................................................................5-391

232.HCW High-speed counter data write (FUN 317) !...........................................................................5-392

233.IOR Shared I/O unit data readout (for A/D module) (FUN 318) !....................................................5-393

234.IOW Shared I/O unit data write (for A/D module) (FUN 319) !........................................................5-394

5.4.18. Sequential debug............................................................................................................................... 5-395

235.ENB Trace enable (FUN 274).........................................................................................................5-396

236.TRG Trace trigger (FUN 275)..........................................................................................................5-397

5.4.19. I/O monitor control.............................................................................................................................5-398

237.KEY I/O monitor key input (FUN 294) %#.........................................................................................5-401

238.LEDD I/O monitor display (FUN 289) %#.........................................................................................5-402

239.LEDC I/O monitor display clear (FUN 290) %#................................................................................5-404

5.4.20. Application instruction for memory card PC2/L2 ............................................................................... 5-405

240.CDR Memory card data read (FUN 296) $......................................................................................5-406

241.CDW Memory card data write (FUN 297) $.....................................................................................5-407

242.CDIR Indirect memory card data read (FUN 298) $........................................................................5-408

243.CDIW Indirect memory card write (FUN 299) $...............................................................................5-409

5.4.21. Other application instruction.............................................................................................................. 5-410

244.SYS Setting/resetting of I/O monitor error automatic indication ..................................................... 5-411

245.ANN Annunciator (FUN 291)...........................................................................................................5-412

246.USC User defined clock (FUN 293)................................................................................................5-413

Page 16

247.ADJ Built-in clock 30-second adjustment (FUN 292) !....................................................................5-414

248.BAUD Peripheral device communication speed setting (FUN 288) #.............................................5-415

249.STOP Program stop (FUN 287)......................................................................................................5-416

250.WDR Scan timer reset (FUN 46).....................................................................................................5-417

5.4.22. Extension of applied instruction for PC3J series PC3J.....................................................................5-418

251.BBMOV Bit Block Transfer (move) (FUN 121) PC3J......................................................................5-422

252.STURN 4bits inversion (FUN 259) PC3J........................................................................................ 5-423

253.TURN 8bits inversion (FUN 260) PC3J...........................................................................................5-423

254.WTURN 16bits inversion (FUN 261) PC3J..................................................................................... 5-423

255.MOVAD Address Constant Transfer (Move) (FUN 320) PC3J.......................................................5-425

256.+H Addition of hexadecimal 2-digit constant (FUN 323) PC3J....................................................... 5-426

257.W+H Addition of hexadecimal 4-digit constant (FUN 324) PC3J....................................................5-427

258.D+H Addition of hexadecimal 8-digit constant (FUN 325) PC3J ....................................................5-428

259.+HP Addition of BCD 2-digit constant (FUN 326) PC3J................................................................. 5-429

260.W+HP Addition of BCD 4-digit constant (FUN 327) PC3J.............................................................. 5-430

261.D+HP Addition of BCD 8-digit constant (FUN 328) PC3J............................................................... 5-431

262.

-H

Deduction of hexadecimal 2-digit constant (FUN 329) PC3J.................................................... 5-432

263.W-H Deduction of hexadecimal 4-digit constant (FUN 330) PC3J................................................. 5-433

264.D-H Deduction of hexadecimal 8-digit constant (FUN 331) PC3J.................................................. 5-434

265.-HP Addition of BCD 2-digit constant (FUN 332) PC3J.................................................................. 5-435

266.W-HP Addition of BCD 4-digit constant (FUN 333) PC3J............................................................... 5-436

267.D-HP Addition of BCD 8-digit constant (FUN 334) PC3J................................................................5-437

268.*H Multiplication of hexadecimal 2-digit constant (FUN 335) PC3J................................................5-438

269.W*H Multiplication of hexadecimal 4-digit constant (FUN 336) PC3J ............................................5-439

270.D*H Multiplication of hexadecimal 8-digit constant (FUN 337) PC3J.............................................5-440

271.*HP Multiplication of BCD 2-digit constant (FUN 338) PC3J .......................................................... 5-441

272.W*HP Multiplication of BCD 4-digit constant (FUN 339) PC3J....................................................... 5-442

273.D*HP Multiplication of BCD 8-digit constant (FUN 340) PC3J........................................................5-443

274./H Divide of hexadecimal 2-digit constant (FUN 341) PC3J........................................................... 5-444

275.W/H Divide of hexadecimal 4-digit constant (FUN 342) PC3J........................................................ 5-445

276.D/H Divide of hexadecimal 8-digit constant (FUN 343) PC3J ........................................................ 5-446

277./HP Divide of BCD 2-digit constant (FUN 344) PC3J .....................................................................5-447

278.W/HP Divide of BCD 4-digit constant (FUN 345) PC3J.................................................................. 5-448

279.D/HP Divide of BCD 8-digit constant (FUN 346) PC3J...................................................................5-449

280.ANDH Logical product (AND) of hexadecimal 2-digit constant (FUN 347) PC3J...........................5-450

281.WANDH Logical product (AND) of hexadecimal 4-digit constant (FUN 348) PC3J........................5-451

282.DANDH Logical product (AND) of hexadecimal 8-digit constant (FUN 349) PC3J ........................5-452

283.ORH Logical sum (OR) of hexadecimal 2-digit constant (FUN 350) PC3J.....................................5-453

284.WORH Logical sum (OR) of hexadecimal 4-digit constant (FUN 351) PC3J.................................5-454

285.DORH Logical sum (OR) of hexadecimal 8-digit constant (FUN 352) PC3J.................................. 5-455

286.XORH Exclusive logical sum (XOR) of hexadecimal 2-digit constant (FUN 353 ) PC3J.................5-456

287.WXORH Exclusive logical sum (XOR) of hexadecimal 4-digit constant (FUN 354) PC3J.............5-457

288.DXORH Exclusive logical sum (XOR) of hexadecimal 8-digit constant (FUN 355) PC3J.............. 5-458

289.STI1 Byte data sum (FUN 362) PC3J............................................................................................. 5-459

290.WSTI1 Word data sum (FUN 363) PC3J........................................................................................5-459

291.DSTI1 32-bit data sum (FUN 364) PC3J.........................................................................................5-459

292.MAX Byte data maximum value retrieve (FUN 374) PC3J.............................................................5-461

293.WMAX Word data maximum value retrieve (FUN 375) PC3J ........................................................ 5-461

294.DMAX 32-bit data maximum value retrieve (FUN 376) PC3J......................................................... 5-461

295.MIN Byte data minimum value retrieve (FUN 377) PC3J ...............................................................5-462

296.WMIN Word data minimum value retrieve (FUN 378) PC3J...........................................................5-462

297.DMIN 32-bit data minimum value retrieve (FUN 379) PC3J........................................................... 5-462

298.AVE Byte data average (FUN 380) PC3J .......................................................................................5-463

299.WAVE Word data average (FUN 381) PC3J...................................................................................5-463

300.DAVE 32-bit data average (FUN 382) PC3J................................................................................... 5-463

301.CRET Return from subroutine (FUN 285) PC3J.............................................................................5-463

302.ARIO Area-designated I/O refresh (FUN 295) PC3J......................................................................5-464

303.SYS Applied command flag clear mode setting (FUN 300) PC3J..................................................5-465

304.BRSET Buffer register(EB) address set (FUN 371) PC3JG.........................................................5-466

305.WBR Data loading from the buffer register(EB) (FUN 372) PC3JG.............................................5-467

Page 17

306.WBW Data saving to the buffer register(EB) (FUN 373) PC3JG .................................................5-468

307.MSET Output of the message for DLNK-M2 (FUN 302) PC3JG .................................................5-469

308.CSET I/O Register read-out instruction issue to TOYOPUC-PCS (FUN 370) PC3JG..................... 5-470

309.SYS Clock adjustment instruction (FUN 300) PC3J.........................................................................5-479

Note) The instructions marked with # can be used by the L2 but not by the PC2 of the version before

SCPU-3.01.

The instructions marked with * can not be use by the PC2 of the some versions.

The available versions are the following as.

CPU Version

PC2J Ver3.50 or later

PC2JS/JR Ver2.30 or later

PC2JF Ver3.50 or later

PC2F Ver4.30 or later

PC2FS Ver2.10 or later

PC2JC Ver3.20 or later

PC2J16 Ver2.10 or later

SUB-CPU Ver2.50 or later

PC2JNM/PC2JNF Ver2.00 or later

PC2JN Ver2.10 or later

The instructions marked with ! can not be used by the SUB-CPU.

The instructions marked with % can be used by the PC2/L2.

The instructions marked with $ can be used by the PC2/L2 of the Ver SCPU-4.10 or later.

The instructions marked with & can be used by the PC3J series.

Page 18

Index of instruction words

- Byte data binary subtraction (FUN 170) 5-196

* Byte data binary multiplication (FUN 172) 5-202

*H Multiplication of hexadecimal 2-digit constant (FUN 335) PC3J 5-438

*HP Multiplication of BCD 2-digit constant (FUN 338) PC3J 5-441

*P 2-digit BCD multiplication (FUN 181) 5-205

/ Byte data binary division (FUN 174) # 5-209

/H Divide of hexadecimal 2-digit constant (FUN 341) PC3J 5-444

/HP Divide of BCD 2-digit constant (FUN 344) PC3J 5-447

/P 2-digit BCD division (FUN 184) 5-212

+ Byte data binary addition (FUN 168) 5-190

+H Addition of hexadecimal 2-digit constant (FUN 323) PC3J 5-426

+HP Addition of BCD 2-digit constant (FUN 326) PC3J 5-429

+P 2-digit BCD addition (FUN 177) 5-193

<=D 3-digit decimal constant comparison (<=) 5-96

<=H 2-digit hexadecimal constant comparison (<=) 5-95

<=N Byte data comparison (<=) * 5-97

<>D 3-digit decimal constant comparison (<>) 5-60

<>H 2-digit hexadecimal constant comparison (<>) 5-59

<>N Byte data comparison (<>) 5-61

<D 3-digit decimal constant comparison (<) 5-87

<H 2-digit hexadecimal constant comparison (<) 5-86

<N Byte data comparison (<) * 5-88

=D 3-digit decimal constant comparison (=) 5-51

=H 2-digit hexadecimal constant comparison (=) 5-50

=N Byte data comparison (=) 5-52

>=D 3-digit decimal constant comparison (>=) 5-78

>=H 2-digit hexadecimal constant comparison (>=) 5-77

>=N Byte data comparison (>=) 5-79

>D 3-digit decimal constant comparison (>) 5-69

>H 2-digithexadecimal constant comparison (>) 5-68

>N Byte data comparison (>) 5-70

ADJ Built-in clock 30-second adjustment (FUN 292) ! 5-414