PRODUCT GUIDE

Microcomputer

2006-10

http://www.semicon.toshiba.co.jp/eng

02 03

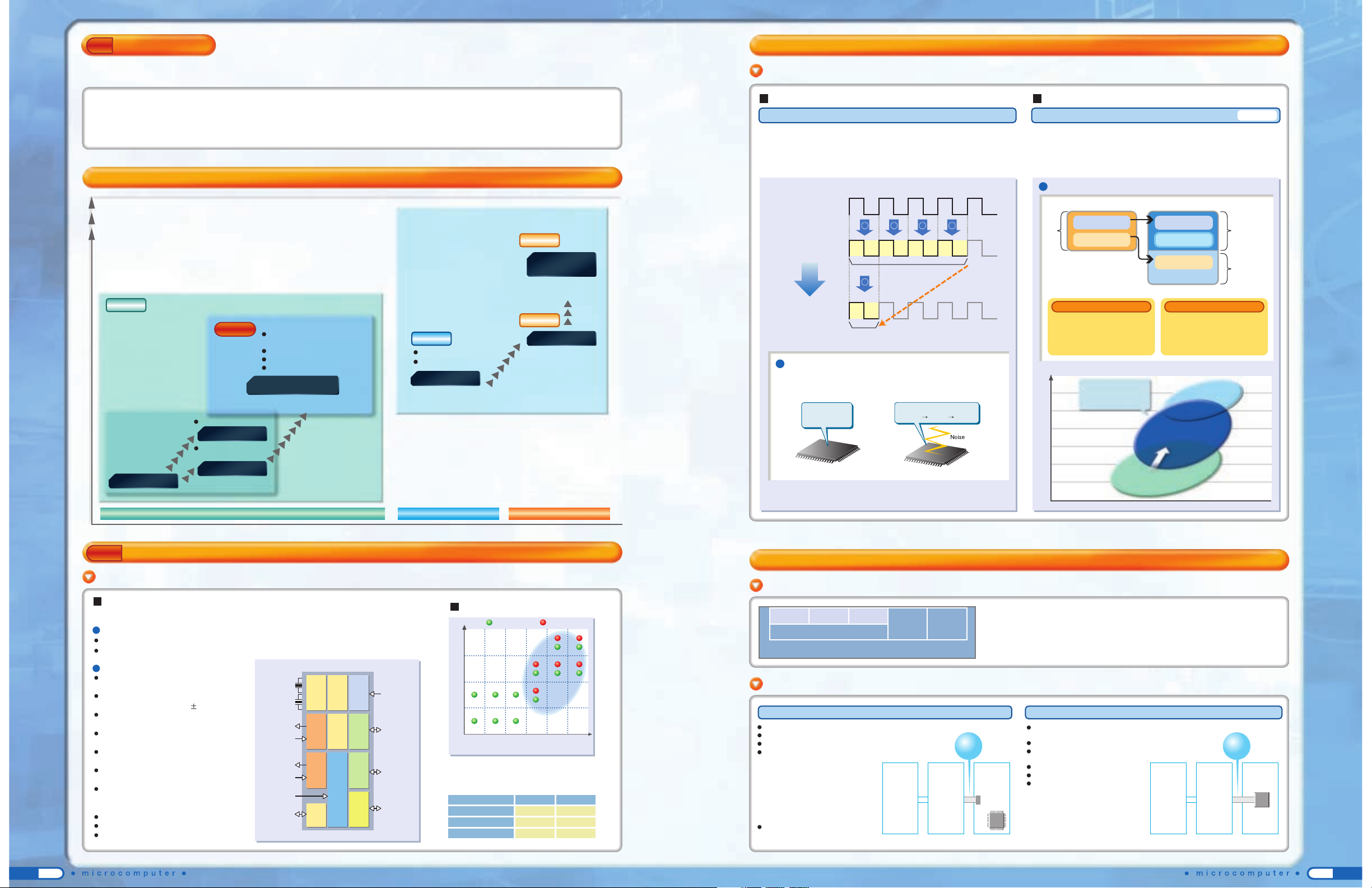

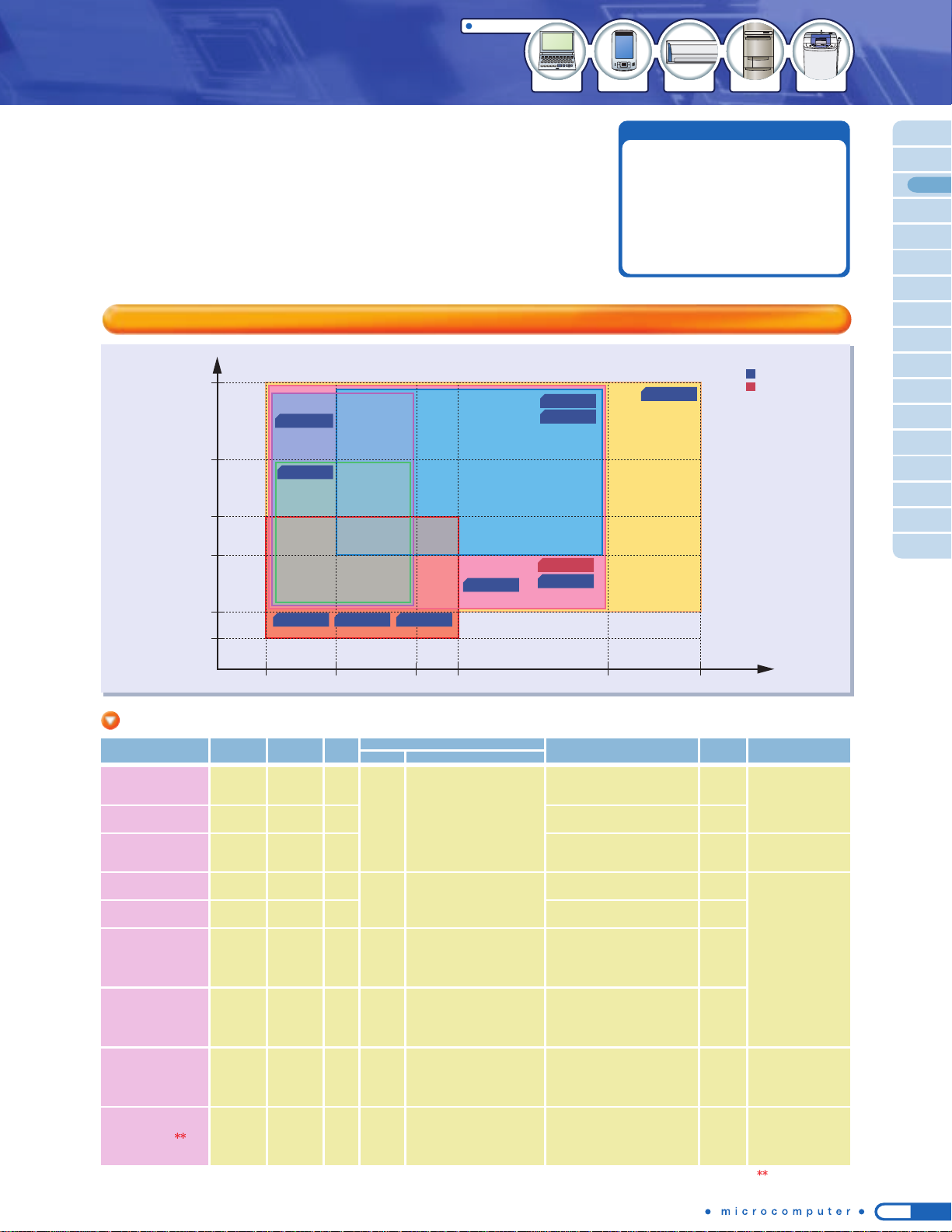

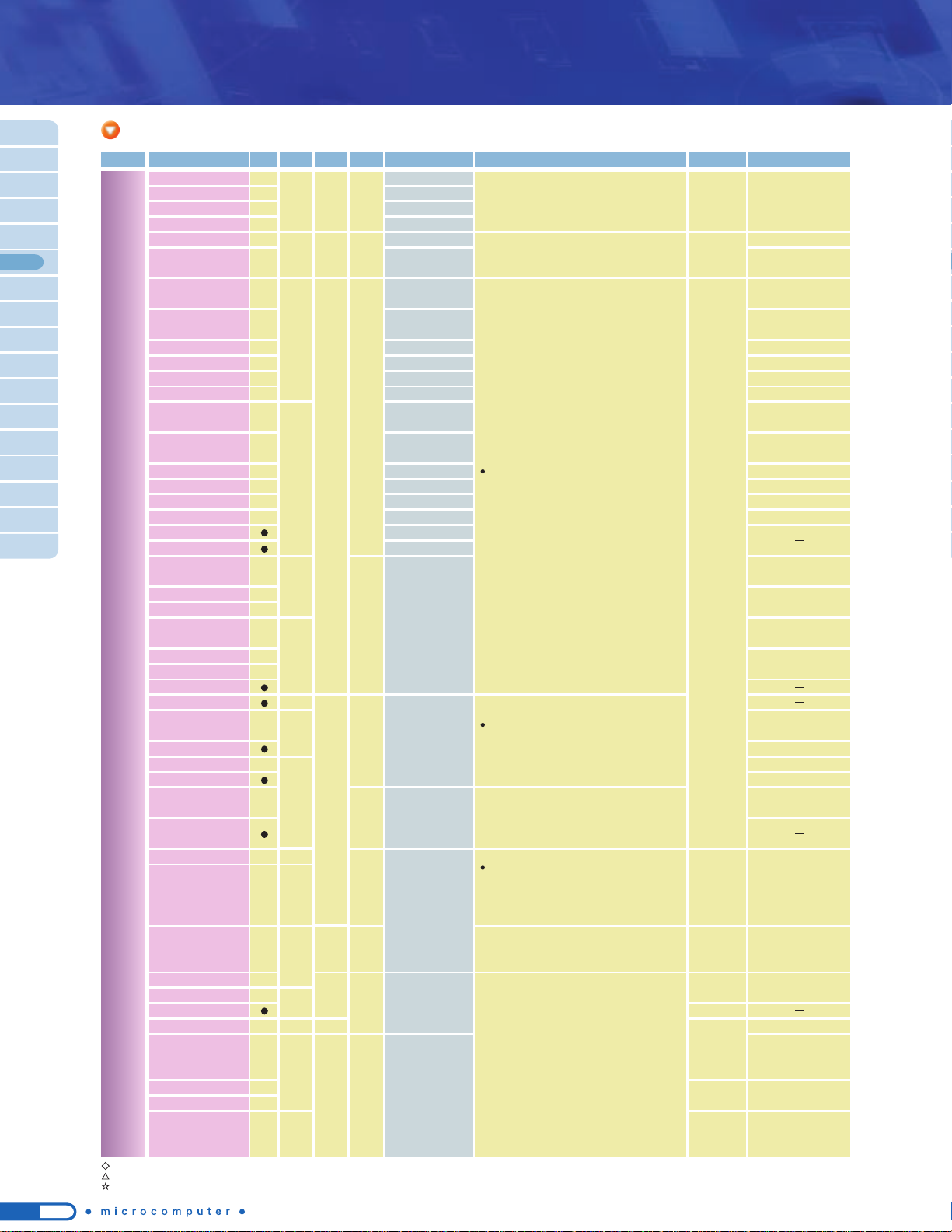

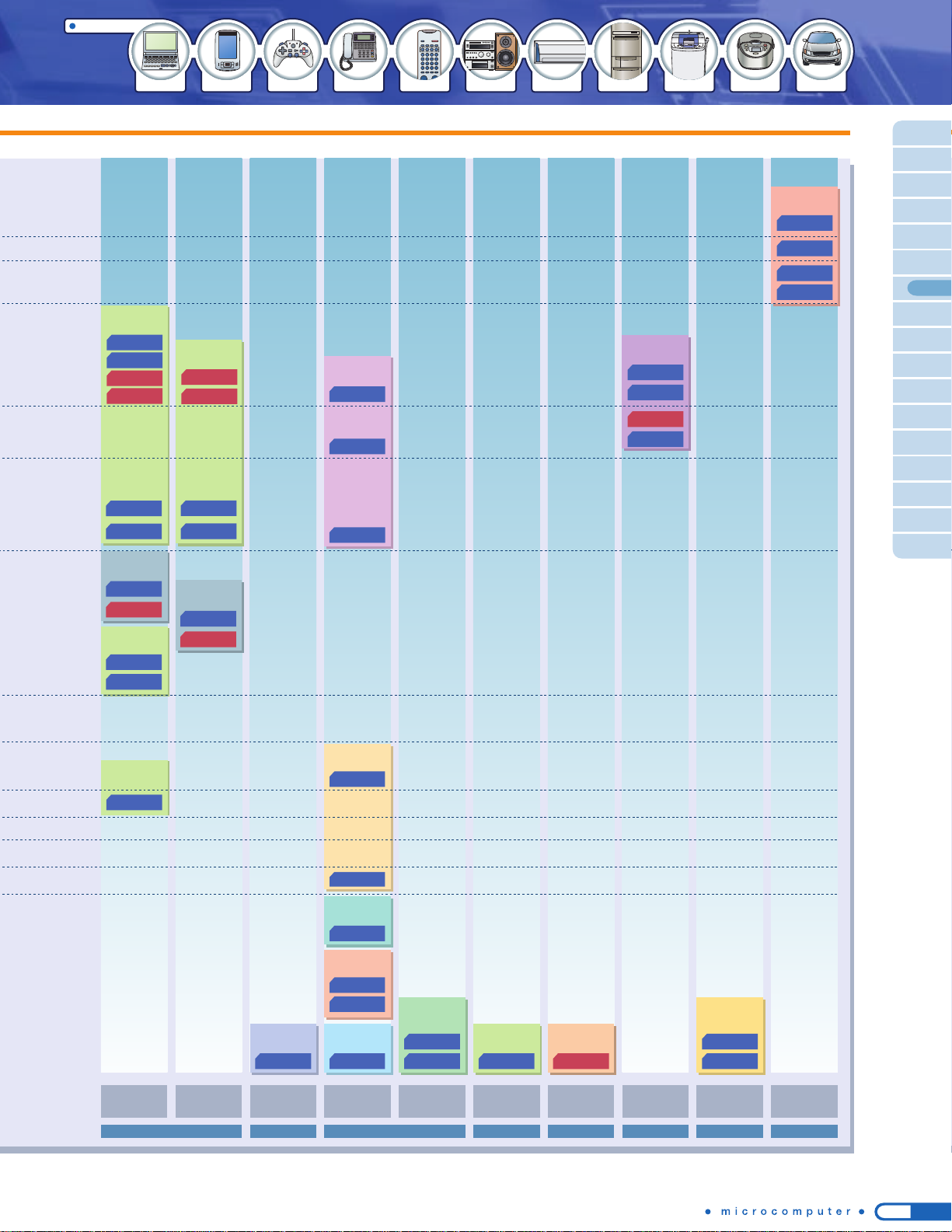

Toshiba microcomputer line-up

Toshiba softwear IP line-up

TX49 Family

FamilyTLCS-900

Toshiba microcomputer development system product line-up

Toshiba offers total solutions to meet your microcomputer needs with an extensive

product line-up supported by our software and development system experts.

64-pin QFP

14mm

14mm / 0.8mm pitch

64-pin LQFP

10mm

10mm / 0.5mm pitch

TLCS-900/H Series

TLCS-900/L

Series

TLCS-900

Series

TLCS-900/L1 Series

TX49/H2 Series

TX49/L4 Series

TX49/L3 Series

TX49/H3 Series

TX49/H4 Series

TX49/W4 Series

TX99 Family

TX99/H4 Series

TLCS-900/H1 Series

High-Speed

TLCS-900/H1 Series

16-bit 32-bit

32-bit

32-bit

64-bit

64-bit

8-bit

Portable devices

Digital information appliances (broadband/OA equipment)

Digital consumer (DSC/DVC/DVD/DTV/STB)

Automotive equipment

Automotive equipment

Audio

TV/communications (cordless phones)/electric appliances/inverter appliances

TX19A Series

TX19 Series

TX19 Family

TX39 Series

MeP

TX39 Family

Performance

TLCS-47 Family

TLCS-870/C Series

Toshiba Integrated

Development Environment

(TIDE)

TLCS-870 Series

RTE47 model 10 system

RTE47 system

RTE870 model 10 system

TLCS-870/X Series

TLCS-870/C1 Series

TLCS-900 Family

TX19 Series

TX19A Series

RTE870/X model 25 system

RTE870/X model 15 system

RTE870/C model 15 system

RTE870/C Light system

RTE900 model 25 system

RTE900 model 15 system

DSU PROBE for N-WIRE

DSU PROBE model 120

DSU PROBE model 110

In-circuit emulator

On-chip debug emulator

NEW

Real-Time OS

Real-Time OS

Real-Time OS

8

-bit

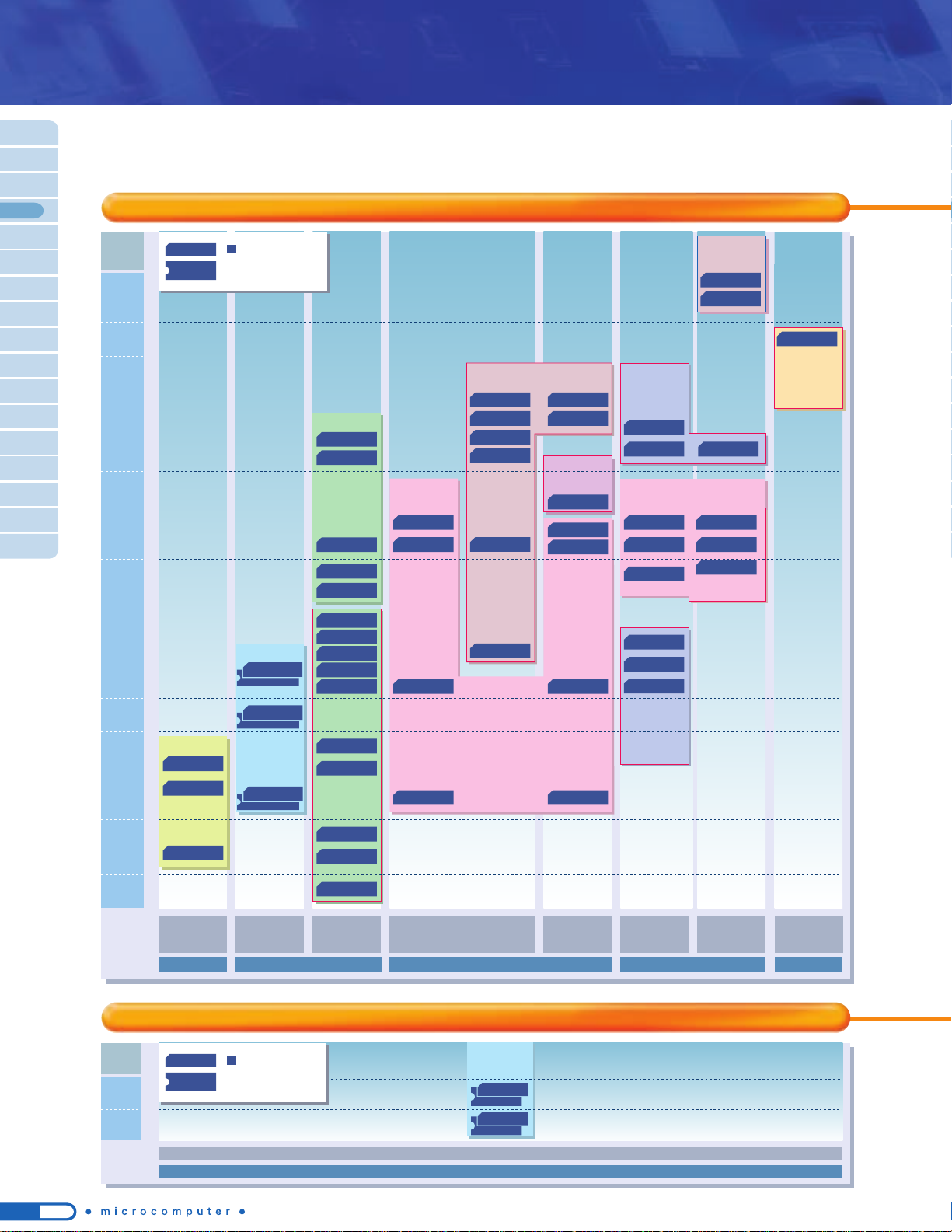

TLCS-870 Family

TLCS-870/X

TLCS-870/C

TLCS-870

TLCS-870/C1

NEW

Core architecture optimized

for C compiler

Minimum instruction execution time: 250 ns

Minimum instruction execution time: 125 ns

Address space extended to 1 Mbyte

■

High-speed processing capability equivalent

to 16-bit microcontrollers

■

Address space extended to 128 Kbytes

■

5-V operation

■

On-chip debug function

[New Core] TLCS-870/C1 Series

The new 8-bit CPU core delivering high-speed processing capability

and memory address space extension, while offering instruction code

compatibility with TLCS-870/C

Under development

TMP89FS60UG/FG

NEW

General-purpose 64-pin product providing various interfaces for serial

communications and a timer system

TCP/IP protocol stack

HTTP server

JPEG

IrDA protocol stack

USB1.1 (device)

Embedded file system

Authentication Library

CompactFlash Driver

SD Memory Card Driver

Library

Handwritten Recognition

Interface

Graphics

Graphical

Speech Codec

Text to Speech (TTS)

TLCS-870 FamilyLL Microcontroller

TLCS-47E Series

T4X Series

T6H Series

TLCS-870/X Series

TLCS-870/C Series

TLCS-870 Series

TLCS-870/C1

Series

TLCS-47 Family

LL Microcontroller

4-bit

Remote controls/calcurators/digital clocks/portable game machines

NEW

04 05

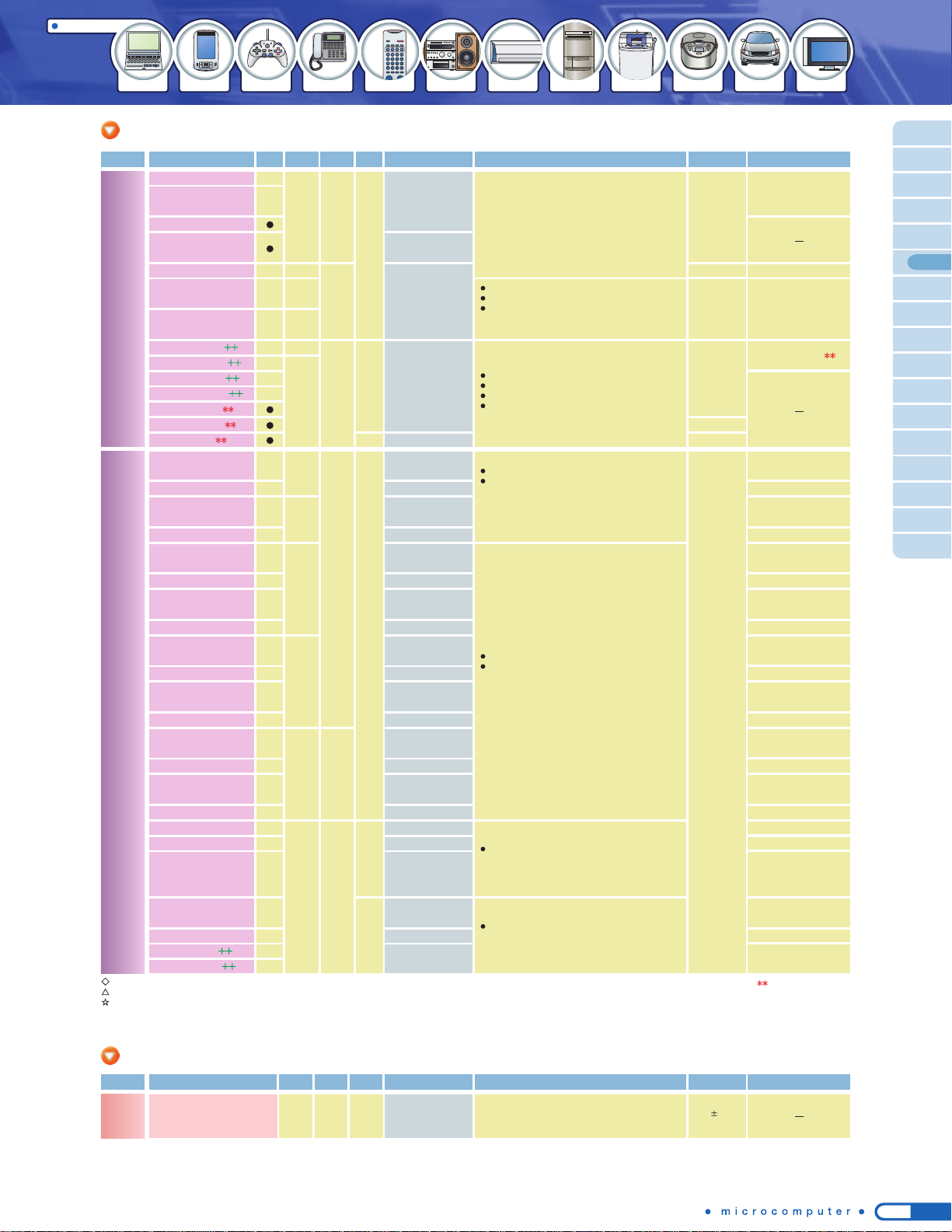

Product line-up

Toshiba has newly developed TLCS-870/C1 Series of 8-bit microcontrollers that deliver high-speed processing capability equivalent to 16-bit

microcontrollers. The TLCS-870/C1 Series achieves high-speed processing capability at low internal clock frequencies by operating one instruction

cycle in a single clock cycle. Toshiba's proprietary memory segment method allows addressing up to 128 Kbytes of memory address space.

16-bit

8-bit

32-bit

32-bit

8-bit Flash microcontrollers based on TLCS-870/C1 core

The new 8-bit CPU core delivering high-speed processing capability and memory address space extension, while offering instruction code compatibility with TLCS-870/C

NEW

NEW

8-Bit Microcontrollers

TLCS-870/X

TLCS-870/C

TLCS-870

TLCS-870/C1

TLCS-900/L1

TLCS-900/H1

High-Speed

TLCS-900/H1

NEW

Performance

Low power consumption

Low noise

Core architecture optimized

for C compiler

Minimum instruction execution

time: 250 ns

Minimum instruction execution time: 125 ns

Minimum instruction execution time: 111 ns

Minimum instruction execution

time: 125 ns

Minimum instruction execution

time: 50 ns

Address space extended to 1 Mbyte

8-bit microcontrollers

16-bit 32-bit8-bit

TMP89FS60UG/FG

✽✽

General-purpose 64-pin product providing various interfaces for serial communications and a timer system

Flash version or mask version can be selected.

16KB

42-pin 44-pin 48-pin 64-pin 80-pin 100-pin

32KB

60KB

96KB

ROM

L

LCD driver built-inStandard product

LLL

LL

L

870/C1 Series road map

(planned)

✽✽

: Under development

++

: Under planning

Part Number

TMP89CM60UG/FG

++

TMP89CS60UG/FG

++

TMP89FS60UG/FG

✽✽

ROM

32 KB

60 KB

60 KB

RAM

3.0 KB

3.0 KB

3.0 KB

8KB

16KB

32KB

64KB

96KB

128KB

Program size (data + code)

1

1

2 3 4

Accessible to the address

space (128 Kbytes)

doubled over 870/C by

the segment method

TLCS-870/C1 Series: Minimum instruction execution time of 125 ns

TLCS-870/C Series: Minimum instruction execution time of 250 ns

*The minimum instruction execution time is reduced by half compared to TLCS-870/C.

Advantages of low-frequency operation

TLCS-870/C Series

64 Kbytes (data + code)

TLCS-900/L1 Series

TLCS-870/C1 Series

128 Kbytes (Max)

Code: 64 Kbytes

Data: 64 Kbytes

Segment method

New

High-speed processing at a low clock frequency

Toshiba's proprietary memory management method (segment method)

Address space extendable to 128 Kbytes

One instruction cycle operated in a single clock cycle

Toshiba's proprietary memory segment method manages

instruction codes and data independently in separate memory

address spaces. This new method enables memory address space

extension without affecting processing speed or code efficiency for

small- to large-sized programs exceeding 64 Kbytes.

The core architecture is configured to reduce the number of clock

cycles required to complete one machine cycle to a single clock

cycle. This achieves processing performance four times that of

TLCS-870/C Series at the same internal clock frequency.

Features of TLCS-870/C1 Series

Toshiba Integrated Development Environment (TIDE)

Emulators

Development System

Toshiba microcontroller core line-up

C Compiler

Assembler

Build Manager

Debugger

Linker

Framework

Editor

*Under development. Specifications are subject to change without notice.

On-chip debug emulator In-circuit emulator

Toshiba Microcontrollers TLCS-870/C1 Series

Realizing processing capability equivalent to 16-bit microcontrollers and

memory address space extendable up to 128 Kbytes

Suitable for high-performance

and multifunctional home

appliances, audio equipment

and portable devices

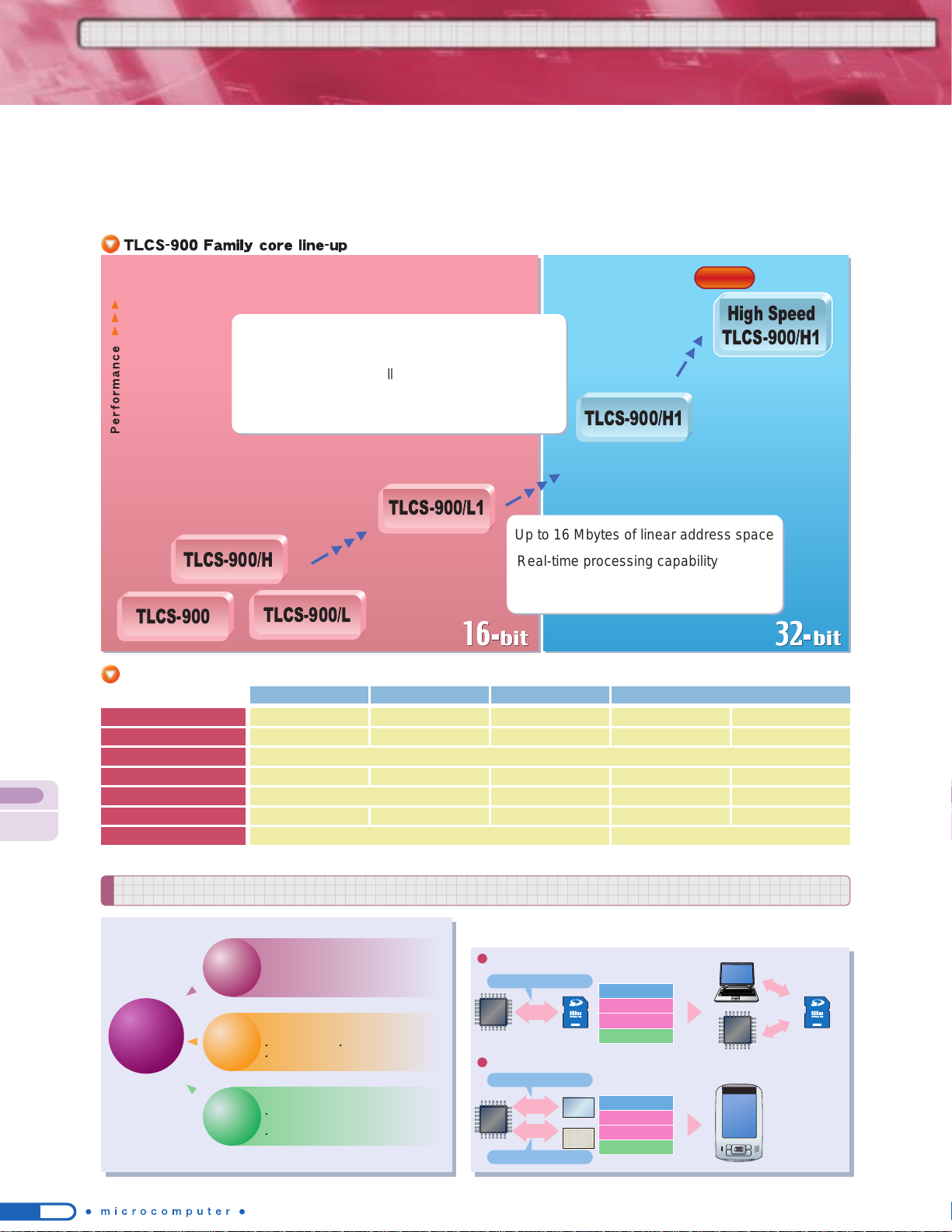

TLCS-900 Family

8-bit microcontrollers

High-speed processing capability

equivalent to 16-bit microcontrollers

Address space extended to 128 Kbytes

5-V operation

On-chip debug function

TLCS-870 Family

Suitable for home appliances

TLCS-870/C1 Core

Operating voltage: 4.5 to 5.5 V at 8 MHz, 2.7 to 5.5 V at 4.2 MHz

Clock gear:

1/4, 1/2, 1/1

Built-In Functions

Voltage detecting circuit

(Two voltage levels detectable, reset or interrupt selectable)

Power-on reset circuit

(Threshold voltage: 2.4 V

0.2 V)

8-bit timer/counter: 4 channels

(Resolution: 125 ns at 8 MHz)

16-bit timer/counter: 2 channels

(Resolution: 250 ns at 8 MHz)

UART/SIO*: 2 channels

(UART: 128 Kbps, SIO: 4 Mbps at 8 MHz)

UART: 1 channel

(UART: 128 Kbps at 8 MHz)

I

2

C/SIO*: 1 channel

(I

2

C: 400 Kbps, SIO: 4 Mbps at 8 MHz)

*

Two SIO channels can be used simultaneously.

10-bit AD converter: 16 channels

Built-in pull-up resistors

On-chip debug function (Flash version only)

8 MHz

Analog

input

TXD/RXD

SCLK/SI/

SO

SDA/SCL/

SCLK/SI/

SO

TXD/RXD

32 kHz

Pulse output

Timer/counter

input

Pulse output

Timer/counter

input

Interrupt

I/O port

POR/

VLTD

ROM

10-bit

AD

(16ch)

UART/

SIO

(2ch)

I

2

C/

SIO

(1ch)

UART

(1ch)

RAM

870/C1

Core

8-bit

timer

(4ch)

16-bit

timer

(2ch)

I/O

56

Packages:

UG: 64-pin LQFP (10 mm x 10 mm/0.50-mm pitch)

FG: 64-pin QFP (14 mm x 14 mm/0.80-mm pitch)

Internal clock

TLCS-870/C

Series

TLCS-870/C1

Series

One machine cycle

One machine cycle

◆

Compared to the TLCS-870/C, power consumption can be reduced at the

same performance level.

◆

Noise generation can be reduced.

At higher frequencies...

Low-frequency

operation

(8 MHz)

(16 MHz 24 MHz 32 MHz)

Code and data in the same area

64-Kbyte code

segment

64-Kbyte data

segment

Code

Data

Code

Additional code

Data

Code: Instruction op-codes and operands

Data: Sources and destinations of load and arithmetic instructions, etc.

Conventional 8-bit product

Segment method

Software design facilitated

Compact core and object sizes

Compared to the address bus

extension method, core and code

sizes are reduced. The instruction

set is compatible with TLCS870/C.

Unlike the bank switching method, small- to

large-sized programs need not be modified.

Processing speed and code efficiency are

unaffected even if the code size exceeds 64

Kbytes.

Using the Integrated Development Environment (IDE) together with C

Compiler enables seamless operations of coding, building and debugging

tasks which must be performed repeatedly in the software development

process. Toshiba development tools offer a variety of latest functions to

realize a user-friendly and highly efficient debug environment.

*The target system requires a separate power supply.

*The target system requires a separate power supply.

Target

system

Host

system

USB

Control

interface

cable

RTE870/C1

on-chip

debug

emulator

Target

system

Host

system

USB

MCU

probe

RTE870/C1

emulator

Business-card-sized compact emulator

No need for power supply (using USB bus power)

Target connection via a narrow-pitched cable

Extensive on-chip debug functions

Break/event : 8 breakpoints/1 event

Trace :

The last two branches

can be stored in real time.

Memory access: Display/Rewrite during

program execution in 1-byte units

(with a wait of 1 clock cycle)

Debug pin : Two I/O pins

Flash programming function

IDE included

(downloadable from website)

Compact, low-cost, yet highly functional in-circuit emulator

(compared to RTE870/C model 15)

Various 870/C1 Series devices supported by replacing the probe

Common probe with RTE870/C Light*

(*) Compact emulator for 870/C Series

Connected with the host system via USB

IDE included (downloadable from website)

Supports on-chip debug emulation.

06 07

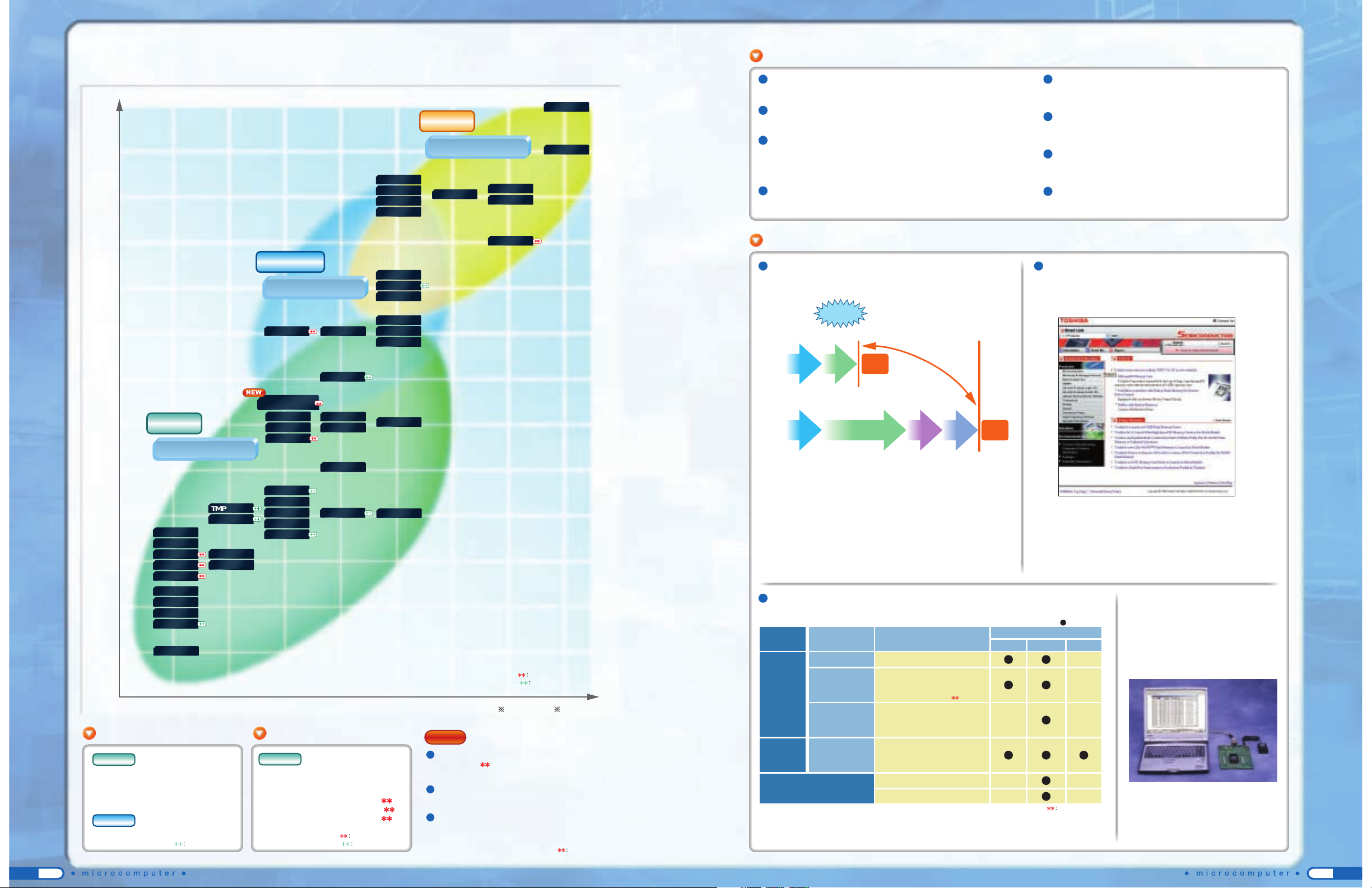

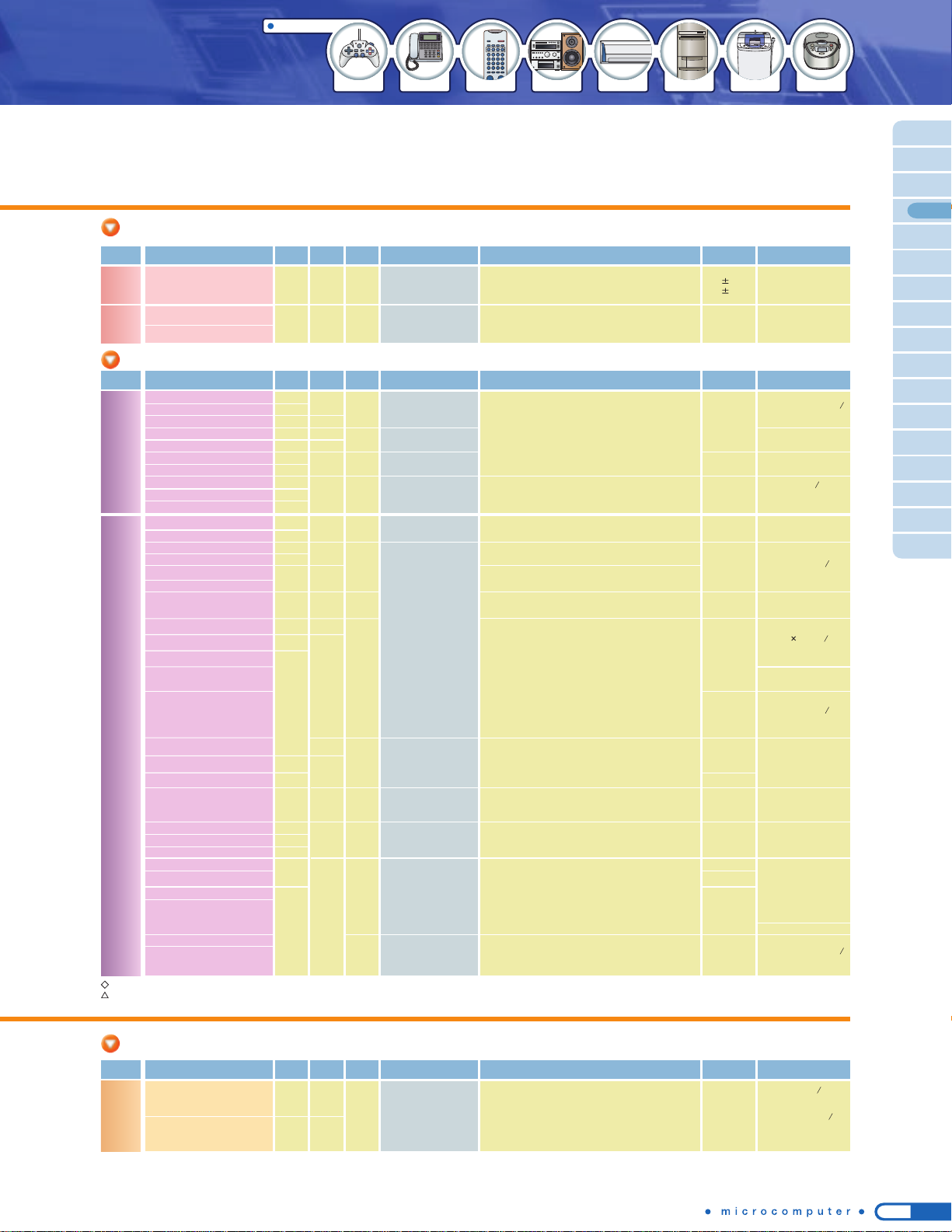

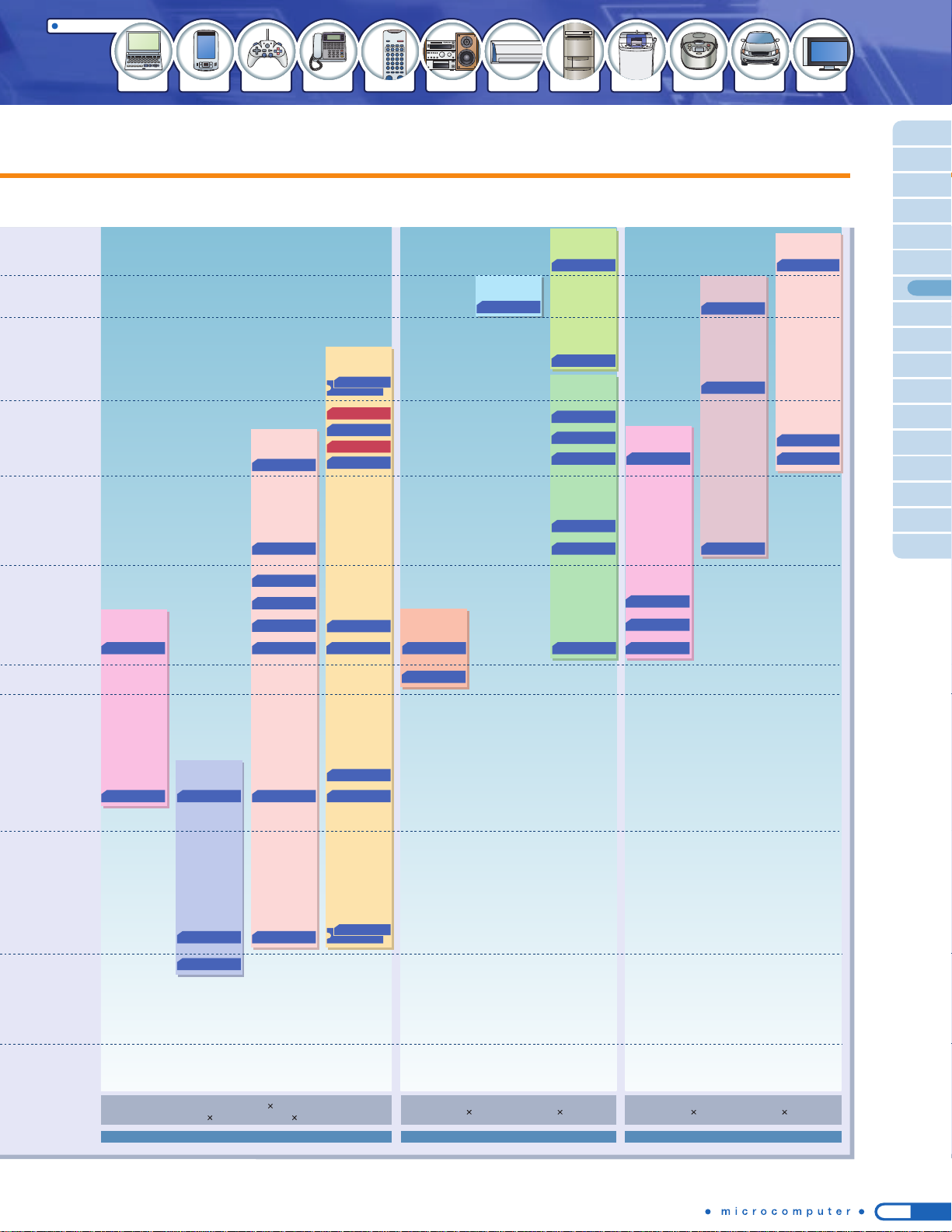

Toshiba’s Flash Microcontrollers

16-bit

4 KB

28/30/32 42/44/48 64 80 100 144 177/193

FBGA

281

FBGA

8 KB

16 KB

32 KB

48 KB

64/60

KB

96 KB

128/120

KB

256 KB

384 KB

512 KB

1 MB

2 MB

Capacity

Under development

Under development

Pin count

Under planning

Under planning

Under development

Under planning

Products with built-in LCD driver

Features of Toshiba’s Flash microcontrollers

Full support system for Toshiba’s Flash microcontrollers

Products in low-pin-count packages

8-bit

TMP86FM23++

TMP86FP24

TMP86FM25

TMP86FM26

TMP86FS27

TMP86FM28++

TMP86FM29

TMP91FW40

TLCS-870 Family

8-bit

TMP86F409

TMP86F807

TMP86F808

TMP86F809

TMP86F892++

TMP86FH09

TMP86FH12

TMP86FH46A

TMP86FM46++

TMP86FH47A

TMP86FM47++

TMP86FH92

TMP86FH92I

TMP86FH93

TLCS-870 Family

TLCS-900 Family

High-speed programming

NANO FLASHTM allows 0.5 Mbytes of data to be programmed in 2 seconds.

Flash programming service

Various programming tools

Toshiba offers a wide variety of programming tools to meet various needs of customers from

development to mass production. Programming services are also available.

Toshiba Semiconductor website

8-bit microcontroller

TMP89FS60

General-purpose 64-pin product providing various interfaces for

serial communications and a timer system

16-bit microcontroller

TMP91FY42

100-pin product featuring large-capacity Flash memory (256 Kbytes)

32-bit microcontroller

TMP92FD28

100-pin product incorporating a USB host controller

Enhanced security function

Up to 255 bytes of password protection can be implemented to

prevent illegal read accesses.

A wide range of operating voltages

Operating voltages ranging from 2.7 V to 5 V are supported.

Various Flash programming methods

In addition to serial mode and parallel mode, ISP (In System

Programming) is supported.

Low power consumption

NANO FLASHTM realizes the same level of low power

consumption compared with mask ROM products.

Quick programming service

Flash programming service is available to enable QTAT

(quick turnaround time).

On-chip debug function incorporated

The on-chip debug function improves development efficiency by

allowing debugging on mass-production boards.

Toshiba’s Flash programming tool

Flash adapter

Connection example

The Flash adapter is a programming adapter

supporting Toshiba’s microcontrollers with onchip Flash memory. Connecting the Flash

adapter with your PC allows you to program,

erase and verify on-chip Flash memory. The

Flash adapter is provided for each package type.

Category

Off-board

programming

(Note 1)

On-board

programming

(Note 2)

Programming services

(Note 4)

Tool type

Programming adapter

Note 1: Off-board programming is a method to program a Flash device before it is mounted on the system board.

Note 2: On-board programming is a method to program a Flash device after it has been mounted on the system board.

Note 3: The in-circuit programmer from Flash Support Group allows off-board single-device programming by connecting an optional adapter.

Note 4:

Programming services are also available from some of the other programming tool vendors in this table apart from Toshiba and MICROTEK.

Note 5:

Some limitations apply when the programming adapter is used for mass production. For details, contact your local Toshiba sales representative.

: Supported

Toshiba Corporation

Toshiba Corporation

MICROTEK Inc.

Flash Support Group, Inc.

HI-LO System Research Co., Ltd.

MINATO ELECTRONICS INC.

Shanghai Gengyan Electric Technology Co., Ltd

T.S ELECTRONICS CO., LTD

Flash Support Group, Inc.

HI-LO System Research Co., Ltd.

MINATO ELECTRONICS INC.

Shanghai Gengyan Electric Technology Co., Ltd

Sophia Systems Co., Ltd.

Flash Support Group, Inc.

(Note 3)

Yokogawa Digital Computer Corporation

Single-device

programmer

Gang programmer

In-circuit programmer

Tool vendor

Development

Mass production

Maintenance

Phase

(Note 5)

Toshiba offers an extensive line-up of microcontrollers with on-chip Flash memory ranging from small-capacity

to 2 Mbytes. You can find a wide variety of products from low-pin-count devices to high-functionality devices.

NEW

* The user is required to connect write signals

and mount oscillators as appropriate to each

device.

A wide variety of peripheral functions

The line-up includes products with various application-specific functions,

such as an LCD driver, an inverter motor control function (PMD), or an

IGBT control timer, as well as general-purpose products.

QTAT

Manufacturing

process

Masked

ROM

product

Flash

product

Programming

order

QTAT is achieved by programming

the Flash microcontroller at Toshiba.

(Note)

Delivery

Delivery

Mask/ES creation process

ES

evaluation

Development

Development

Flash

programing

Customer

Mask/ES

order

Customer

Customer

Mass

production

order

●QTAT

........................

Quick Flash programming service is available.

(Note)

●Quality assurance..The same level of quality as that of

mask ROM products is assured.

●Marking

...................

Custom marking is possible.

●Support

...................

In addition to programming at Toshiba,

customers can use our partner programming

houses.

Note:

Delivery time varies with various conditions such as quantity, order acceptance time,

factory operation schedule, and product type. For details, please contact your local

Toshiba sales representative.

Flash programming service enables QTAT (quick turnaround time),

allowing customers to achieve shorter time-to-market.

TMP86F409

TMP86F807

TMP86F808

TMP86F809

TMP86F892

TMP89FS60

16-bit

TX19 Family

NEW

TMP86FM46

TMP86FM47

TMP91FW40

TMP91FW60

TMP86FS64

TMP88FW44

TMP92FD23A

TMP1940

TMP1942

TMP1942

TMP19A43

TMP19A43

TMP1962

TMP19A64

TMP92FD28

TMP92FD54AI

TMP91FY42

TMP92FY60

TMP19A71

TMP86FH09

TMP86FH12

TMP86FH46A

TMP86FH47A

TMP86FH92

TMP86FH92I

TMP86FM23

TMP86FM25

TMP86FM26

TMP86FM29

TMP86FM48

TMP86FM49

TMP86FH93

TMP86FS23

TMP86FS49A

TMP86FS49AI

TMP86FM28

TMP86FP24

TMP86FS27

TMP86FS28

TMP91FU62

TMP88FW45TMP91FW27

8-bit

32-bit

TLCS-900 Family

TLCS-870 Family

TX19 Family

TLCS-900 Family

TLCS-870 Family

http://www.semicon.toshiba.co.jp/eng/index.html

Information on the entire spectrum of Toshiba

semiconductor products is avaiable here.

●Solution

You can access latest information

for each of system applications.

●Product information

You can access a wide range of new-product information,

presentation data material and other data.

Under development

08 09

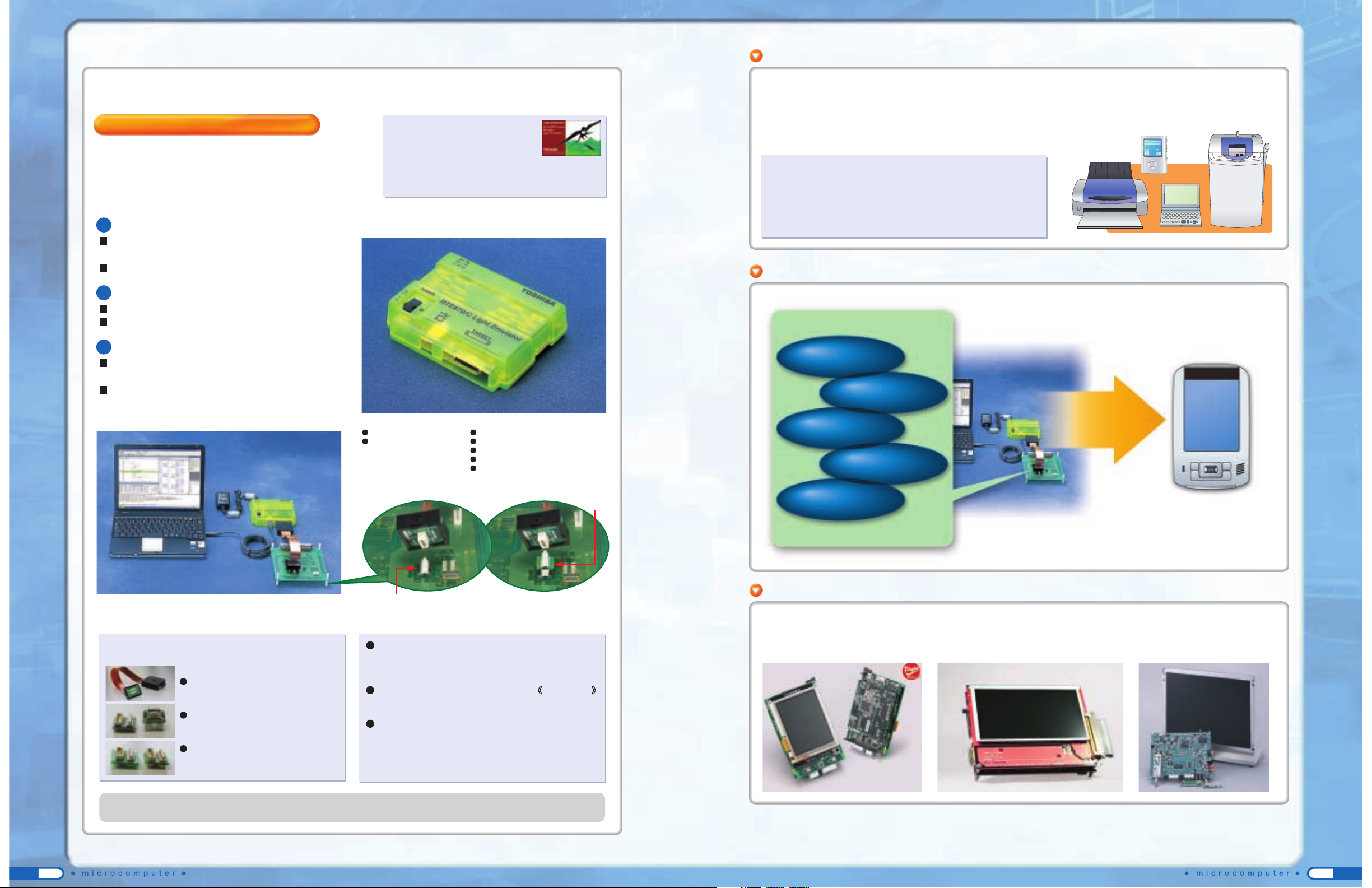

Toshiba offers a complete lineup of reliable, user-friendly development tools to support customers in each phase of

program development from design to evaluation.

Reliable, User-Friendly Development Systems for Toshiba Microcomputers

Toshiba Software IP

System Support

* The outlines of microcomputer development systems can be found on page 53 onward.

Compact ICE for TLCS-870/C Series

* For details of software IPs, see the page 61 of this product guide.

RTE870/C Light emulator

The RTE870/C Light emulator is comprised of the minimum

functions required for debugging, and comes in three types to

support all MCUs in the TLCS-870/C Series (excluding the

TMP86xx24FG).

The price is "Light".

Integration of the RTE controller and pod system makes

the emulator more affordable.

Comes with a free debugger download.

The connection is "Light".

The host interface is through USB.

Can be easily connected to a notebook PC.

The size is "Light".

A new system configuration succeeded in integrating

the system on a single board.

A smaller probe tip takes less space on the target

board.

Product components:

RTE870/C Light emulator

AC power adapter

Other required items:

Probe set

Emulation chip

Language tool

Host system (PC)

USB cable (USB standard A to B)

Target system

Host system

The probe set and options are manufactured by ADLINKS Co., Ltd. These products are distributed by Daimaru Kogyo K.K.

http://www.adlinks.co.jp/

[Usage example]

Exchange connector

Target connector

*The target system requires a separate power supply.

As product development becomes sophisticated and increasingly offers technical advantages, high-performance and

large-scale development becomes required in software development, and the development cycle has turned longer.

To address this situation, Toshiba aims to faster time to market, realize functions with software, and improve quality

by producing software components.

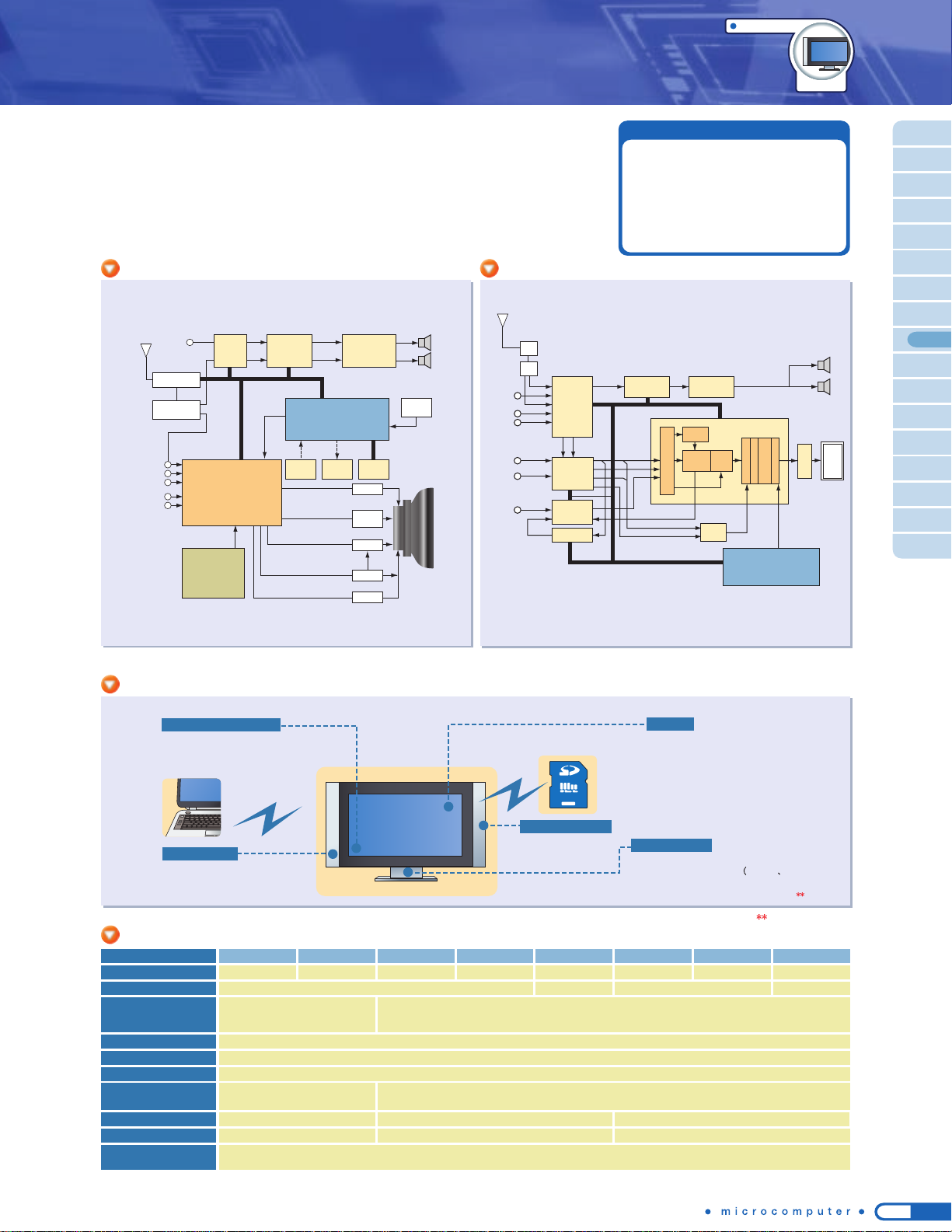

Toshiba’s MCU Plus Software IP Platform

Features of the Software IP

1. Full supports for microcomputers from 8 to 32 bits.

2. Optimized design concept for Toshiba microcomputers.

3. Pursuit of flexible designs and interfaces not limiting

application types.

4. Flexible response to any development environments

and platforms.

Option

Evaluation board for software IP (SWIP)

Reference model for LCD TV

Evaluation board for portable devices

TOP

Bottom

●

Software IPs ● Reference application software ● Reference models

We offer a v ariety of software and solution to speed up your development time.

Stacking connector

The stacking connector is used between the probe and the target

connector to raise height so that the target system can be connected

easily when there is not enough space around the target connector.

MCU mounting adapter for RTE870/C Light Bump socket

The bump socket is used together with the target connector to mount

an MCU on the target system.

M15-Light connection exchange cable

The M15-Light connection exchange cable allows you to connect the

RTE870/C Light system to a target system that has been debugged

with the RTE870/C model 15 system. (The target connecting board

used with the RTE870/C model 15 system is required.)

Probe set

The probe set is available f or each package pin count

or package type of supported MCUs.

Set components:

RTE870/C Light probe

Used to connect the emulator and target

system.

Target connector

Used to connect the probe to the target

system.

Exchange connector

Required with some MCUs.

* For the detailed specifications of the RTE870/C Light emulator, see

“Outline of TLCS-870 Family Development System on page 58.

Operation check and evaluation with a demonstration

board and application.

Software IP group

Network

File system

Speech recording

and playback,

TTS

Graphics

Security

(Authentication)

Customer’s

product

Operation check and evaluation

You can select,

evaluate and use

necessary element

technologies.

Toshiba value your support and aim to propose the best

possible platforms for various application fields.

RTE870/C Light debugger

● Exclusively for RTE870/C Light system

●

The same GUI as RTE87/C model15 debugger

Downloadable from our development system website

(User registration is required.)

AC power

adapter

RTE870/C Light

emulator

RTE870/C

Light probe

USB

10 11

CONTENTS

Microcontrollers Listed by Function/Application

Microcontrollers with motor control circuit (PMD)

12

Microcontrollers with LCD controller

13

Microcontrollers with LCD driver

14

Microcontrollers with fluorescent display tube driver

16

General-purpose microcontrollers in compact packages

17

Microcontrollers with AD converters

20

Microcontrollers for personal equipment

24

Microcontrollers for televisions

25

Microprocessors for digital equipment

26

Microcomputers for automotive applications

27

Microcontrollers for automotive motor control

29

Microcontrollers for inverter electric appliances

30

Microcontrollers for digital single-lens reflex cameras (DSLRs)

31

Microcontrollers for digital video cameras (DVCs)

31

Microcontrollers for audio (CD-MP3 control MCUs)

32

Microcontrollers for audio (Main control MCUs)

32

61

62

64

34

TX99 Family

64-Bit Superscalar TX System RISC

35

TX49 Family

64-Bit TX System RISC

39

Companion Chip

39

TX39 Family

32-Bit TX System RISC

TX19 Family

MeP

(Media embedded Processor)

32-bit TX System RISC

44

TLCS-900 Family

16/32-bit Microcontrollers

47

TLCS-870 Family

8-bit Microcontrollers

Software Development Support

Package List

63

Guide to Websites

Introducing the Latest Software IP

41

40

51

T4X Series / T6H Series

4-Bit / 8 -Bit LL Microcontroller

53

Development System

54

Outline of TX19 Family Development System

56

Outline of TLCS-900 Family Development System

58

Outline of TLCS-870 Family Development System

60

Programming tools / Accessories

System support

On-site support

Web support

Toshiba utilizes global networking to provide powerful support for system development by our customers around the world.

We provide support for microcomputer development including development systems, middleware, application software

and all types of software IP for software development. We also have an organization for providing needed information to

our customers in a timely fashion, through channels such as Web services.

Development support

Toshiba provides extensive local support to satisfy customer needs varying from region to region.

Toshiba Semiconductor Website

Toshiba is committed to supporting our customers in system development.

Software IPs

Reference application software

Reference models

We provide a wide range of software development support for

customers so that they can reduce the time required for

development.

Evaluation board for software IP (SWIP)

Evaluation board for portable devices

Evaluation board for PMD microcontrollers

Evaluation board for inverter lighting equipment

TOP

Bottom

Toshiba provides technical information through our website, with the aim of supplying information to

customers as early as possible to improve their satisfaction.

http://www.semicon.toshiba.co.jp/eng/

Fluorescent lamp lighting by

high-frequency half-bridge

inverter control

using IGBT control timer.

Dimmer function by

frequency and duty

adjustment.

Allows direct

connection to

Toshiba's

emulation pod.

Supports on-

board Flash

programming.

Supports both

sensorless and

sensored

brushless DC

motors.

Equipped with

software for

square wave and

sine wave drive.

Toshiba Electronics (Shanghai) Co.,Ltd.

TOLS Software System Engineering (Shanghai) Co.,Ltd.

Toshiba Electronics Asia, Ltd.

Hong Kong Head Office

Toshiba Electronics Trading (Malaysia) Sdn. Bhd.

Kuala Lumpur Head Office

Toshiba Electronics Service (Thailand) Co., Ltd.

Toshiba Electronics Korea Corporation

Seoul Head Office

Toshiba America Electronic Components, Inc.

Headquarters-Irvine, CA

Toshiba LSI System Support Co.,Ltd.

Toshiba Corporation Semiconductor Company

Toshiba Electronics Taiwan Corporation

Taipei Head Office

12

Applications

Air conditioners Refrigerators

Washing machines

Automotive

● Sine wave drive

● Rotor position detection function

●

Motor control timer and timer capture

●

PWM waveform generation function

● Overload protection function

● Abnormality protection function

●

Automatic commutation start and

automatic position detection start

● AD converter trigger generation

function

Series

Name

Part Number

Flash

ROM

(bytes)

RAM

(bytes)

Supply

Voltage (V)

PMD

(channel)

I/O Additional Functions Version with OTP/Flash Package

TMP88CH40NG/MG

TMP88CH40IMG

TMP88CH41NG/UG

TMP88CH41IUG

/SUG

T5BE2 T5BE1

TMP88PS42NG/FG

TMP88PS43FG

TMP88CS42NG/FG

TMP88CS43FG

16 K

64 K

870/X

DSP

TX19A

512

2K

19

33

221K32K

1

1

2

4.5 to 5.5

4.5 to 5.5

3.0 to 3.6

55

71

●

10-bit AD converter

●

UART

●

SIO

●

10-bit AD converter

●

UART/SIO

●

PWM

●

Encoder input

●

10-bit AD converter

●

UART

●

SIO

●

PWM

SDIP64/QFP64

(14

20mm)

LQFP44(10

10mm)

TMP88PH41NG/UG

SDIP42/LQFP44(10 10mm)

TMP88PH40NG/MG

SDIP28/SOP28

SOP28

QFP80(14

20mm)

TMP19A71CYUG/FG

-TMP88FW44FG

256 K

120K

10K4K75 2

2

3.0 to 3.6

4.5 to 5.5

91

●

10-bit AD converter

●

UART/SIO

●

PWM

●

Encoder input

●

10-bit AD converter

●

UART

●

SIO

●

PWM

LQFP100(14 14mm)/

QFP100(14

20mm)

TMP19A71FYUG/FG

QFP100(14 20mm)

-TMP88FW45FG

120K 4K 2

4.5 to 5.5

71

●

10-bit AD converter

●

UART

●

SIO

●

PWM

QFP80(14 20mm)

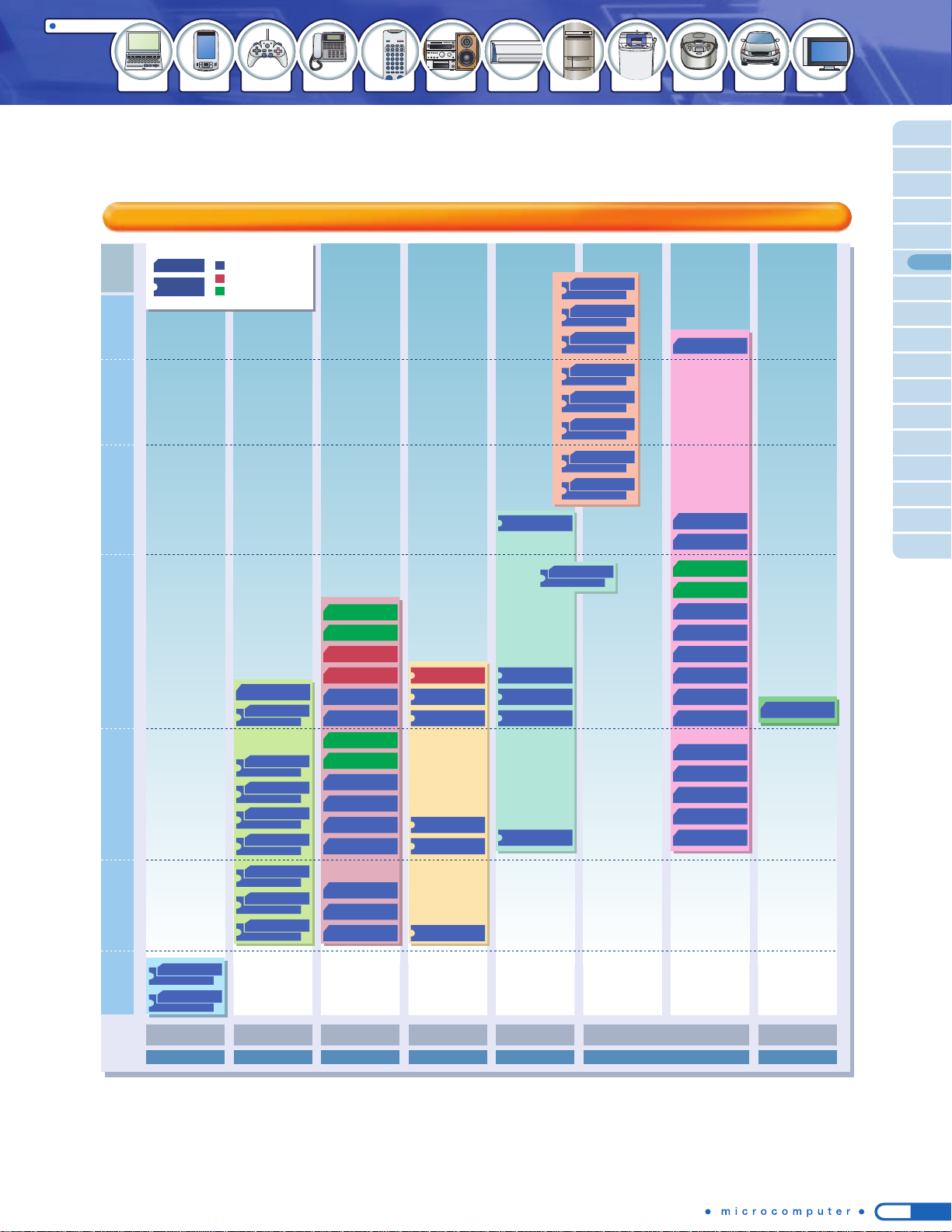

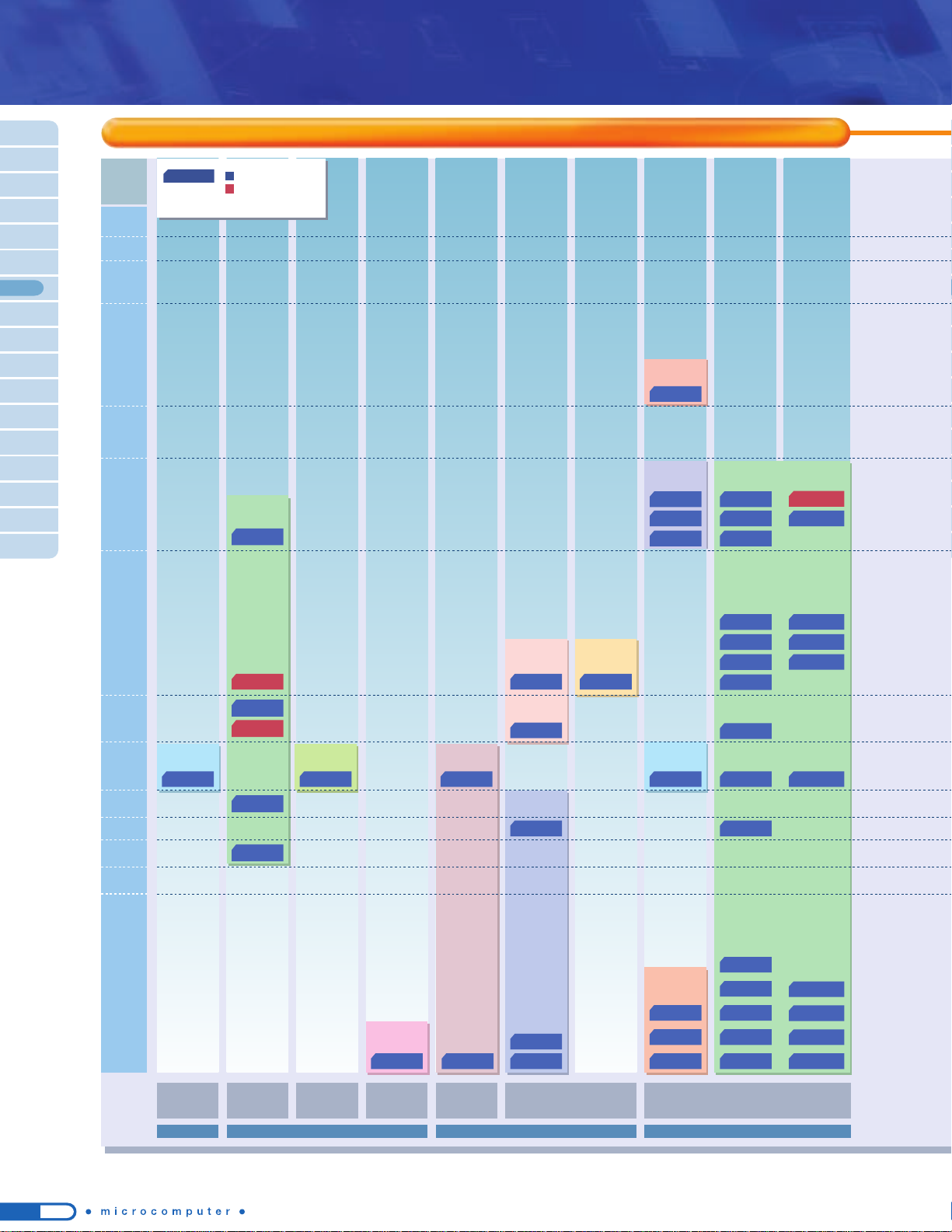

PMD 1ch

Second-generation PMD

4-channel 10-bit ADC

Second-generation PMD

8-channel 10-bit ADC

Third-generation PMD

8-channel 10-bit

high-speed

ADC

PMD 2ch

ROM

size

120/

256 K

64 K

32 K

16 K

*

For details of the products listed above, see the "Part Number List".

++: Under planning

TMP88CH41TMP88CH40

T5BE2

Second-generation PMD

16-channel 10-bit ADC

TMP88CS42

TMP88CH40I

TMP88CH41I/S

Second-generation PMD

16-channel 10-bit ADC

Second-generation PMD

Flash ROM

TMP88CS43

Second-generation PMD

Flash ROM

TMP88FW45

Third-generation

PMD

8- and 11-channel

10-bit high-speed ADCs

TMP19A71

TMP88FW44

*

PMD : Programmable Motor Driver

These microcontrollers with a motor control circuit incorporate an

inverter control function for 3-phase DC and AC motors. The motor

control circuit supports hardware configuration where motor drive

signals are linked with feedback signals from the motor, thus

controlling the motor with less load imposed on the

CPU. The line-up

includes a variety of microcontrollers supporting

120-degree

commutation and vector control.

■ Microcontrollers with motor control circuit (PMD)

28-pin 42-/44-pin 64-pin 80-pin 100-pin

8-bit microcontrollers with motor control circuit (PMD)

Microcontrollers Listed by Function / Application

Main functions

Product line-up

*

Some of the flash memories use the SuperFlash® technology under the license of Silicon Storage Technology, Inc. SuperFlash® is a registered trademark of Silicon Storage Technology, Inc.

TMP88PH40MG

TMP88PH41UG LQFP44(10x10mm)

: In mass production

: Under planning

SOP/QFP

DIP

13

Applications

Electronic dictionaries

PDAs Air conditioners Refrigerators

Washing machines

● Monochrome/Gray/Color LCD

controller

● Memory interface:

SDRAM, NAND Flash, SD card

● Large-capacity memory access

MMU

● Touch Screen interface

Part Number

ROM

(bytes)

RAM

(bytes)

Supply

Voltage (V)

I/O Additional Functions

LCD-CTRL

Display SizeColor

Package

TMP91C016FG

31

W/B

W/B

16

Gray

Gray/

Color

64seg. x 32com.

to

360seg. x 240com.

128seg. x 128com.

to

640seg. x 480com.

64seg. x 64com.

to

Color: 320seg. x 320com.

Gray: 960seg. x 480com.

-- 1.8 to 3.6

●

MMU (105MB)

●

DRAM controller

●

Display data X/Y axis conversion circuit (8 x 8)

TMP91C025FG

38-- 2.4 to 3.6

●

MMU (72MB)

●

Touch Screen interface

TMP91C820AFG

778K8K 2.7 to 3.6

●

MMU (136MB)

●

SDRAM controller

TMP92CH21FG

8216K

8K

(Boot)

2.7 to 3.6

●

MMU (512MB)

●

SDRAM controller

●

NAND Flash interface

●

Touch Screen interface

●

USB1.1 interface

64seg. x 64com.

to

640seg. x 480com.

TMP92CA25FG

9210K 2.7 to 3.6

●

MMU (512MB)

●

SDRAM controller

●

NAND Flash interface

●

Touch Screen interface

●

SPI interface

TMP92C820FG

838K-

-

Gray/

Color

136

TMP92CZ26AXBG

288K

1.4 to 1.6

3.0 to 3.6

(Two power

supplies)

●

MMU (3.1GB)

●

SDRAM controller

●

MLC NAND Flash interface

●

USB1.1 interface

●

SPI interface

8K

(Boot)

3.0 to 3.6

●

MMU (136MB)

●

SDRAM controller

TMP91C815FG

618K- 1.8 to 3.6

●

MMU (136MB)

LQFP100

(14 x 14mm)

LQFP128

(14 x 14mm)

FBGA228

(15 x 15mm,

0.8-mm pitch)

LQFP144

(16 x 16mm)

480

Common

Segment

The following microcontrollers contain LCD controller circuitry that

supports monochrome and color STN/TFT. The line-up thus supports

a wide range of LCDs with different sizes.

■ Microcontrollers with LCD controller

320

240

128

64

64

128 320 360 640 960

32

Monochrome

Monochrome /

Gray

Monochrome /

Gray

Monochrome

Color

TMP92CA25

Monochrome /

Gray / Color

TMP92CZ26A

TMP92CF29

64K / 256K /

16M Colors

TMP92CZ26A

TMP91C820A

TMP92C820

TMP92CH21

TMP92CH21

TMP91C016 TMP91C025 TMP91C815

*

For details of the products listed above, see the "Part Number List".

16-/32-bit microcontrollers with LCD controller

64seg.

x

64com.

to

64K

or more colors

:320seg.

x

480com.

4K

or fewer colors

:

640seg.

x

480com.

Gray

Gray/

Color

92

TMP92CF29FG

144K

1.4 to 1.6

3.0 to 3.6

(Two power

supplies)

●

MMU (2.1GB)

●

SDRAM controller

●

MLC NAND Flash interface

●

USB1.1 interface

●

SPI interface

8K

(Boot)

LQFP176

(20 x 20mm)

64seg.

x

64com.

to

64K

or more colors

:320seg.

x

480com.

4K

or fewer colors

:640seg.

x

480com.

Gray

Main functions

Product line-up

: In mass production

: Under development

: Under development

14

23 seg. x 4 com.

TMP86PH22

TMP86CH22

TMP86C822

64-pin44-pin 80-pin 100-pin 144-pin

LQFP

(

10 x 10mm

)

/

QFP

(

14 x 14mm

)

SDIP64/LQFP

(

10 x 10mm

)

QFP

(

14 x 20mm

)

LQFP

(

12 x 12mm

)

QFP

(

14 x 20mm

)

LQFP

(

14 x 14mm

)

LQFP

(

16 x 16mm

)

32seg. x 4 com.

8-bit AD converter:

8 channels

40seg. x 4 com.

On-chip voltage booster

40 seg .x 4 com.

8-bit AD converter:

8 channels

On-chip voltage

booster

ROM

size

4 K

8 K

16 K

24 K

32 K

48 K

60 K

64 K

128 K

42- / 44-pin

SDIP / QFP

ROM

size

2 K

4 K

24seg. x 4 com.

On-chip voltage

booster

60seg. x 16com.

On-chip voltage

booster

8-bit

AD converter:

8 channels

40 seg. x 4 com.

On-chip voltage

booster

10-bit

AD converter:

8 channels

24 seg. x 4 com.

TMP87CM29

TMP87CK29

TMP87CH29

LQFP44

(

10 x 10mm

)

32 seg. x 4 com.

On-chip voltage

booster

TMP86PM29B

TMP86FM29

TMP86CM29L

TMP86FM26

TMP86CM29B

TMP86CH21A

TMP86CH29B

TMP86C829B

TMP86C820

TMP86C420

32 seg. x 4 com.

TMP86PS23

TMP86FS23

TMP86CP23A

TMP86CM23A

TMP86PM23

TMP87PP21

TMP87CP21C

TMP87CM21C

TMP87CM21C

TMP87PP21

TMP86PS27

TMP86CP27A

TMP86CM27

TMP86FS28 TMP86FS28

TMP86CS28 TMP86CS28

TMP87CP21C

TMP87CH21C

TMP87CH21C

TMP86FP24

TMP86FS27

TMP87PP23

TMP87CP23

TMP86FM25

TMP86CM25A

TMP87CM23A

TMP87PP24A

TMP87CP24A

TMP87CM24A

TMP86CM25

TMP93CS20

20 seg x 4 com.

8-bit

AD converter:

4 channels

TMP47C222

TMP47C422

40 seg. x 4 com.

Not voltage

booster type

TMP91FW40

TMP91CW40

60seg. x 16com.

On-chip voltage

booster

8-bit

AD converter:

8 channels

TMP86CS25A

TMP86CS25AD

TMP86PS25

The following microcontrollers contain LCD driver circuitry. Some products also incorporate a voltage booster,

enabling stable LCD display even at low operating voltages and realizing low power consumption.

■ Microcontrollers with LCD driver

Microcontrollers Listed by Function / Application

: In mass production

QFP

DIP

4-bit microcontrollers with LCD driver

8-/16-bit microcontrollers with LCD driver

: In mass production

QFP

DIP

15

Applications

Game machines Telephones Remote controls Audio systems Air conditioners Refrigerators

Washing machines

Rice cookers

Series

Name

Part Number

ROM

(bytes)

RAM

(bytes)

I/O LCD Driver Additional Functions

Power

Voltage (V)

Package

Series

Name

Part Number

ROM

(bytes)

RAM

(bytes)

I/O LCD Driver Additional Functions

Power

Voltage (V)

Package

Series

Name

Part Number

ROM

(bytes)

RAM

(bytes)

I/O LCD Driver Additional Functions

Power

Voltage (V)

Package

16 K

32 K

60 K

32 K

: Guaranteed over the ambient temperature (Topr) range of -20oC to 85oC at 1.8 V to 2.0 V.

: Guaranteed over the ambient temperature (Topr) range of -20oC to 85oC at 2.7 V to 3.0 V.

*

For details of the products listed above, see the "Part Number List".

TMP87CH21CFG/CDFG

TMP87CM21CFG/CDFG

TMP87CP21CFG/CDFG

TMP87CM23AFG

TMP87CP23FG

TMP87CM24AFG

TMP87CP24AFG

TMP87CH29NG/UG

TMP87CK29NG/UG

TMP87CM29NG/UG

870

1 K

2 K

1 K

2 K

2K

1 K

40 seg. X 4 com.

40 seg. X 4 com.

(On-chip voltage booster)

32 seg. X 4 com.

24 seg. X 4 com.

23 seg. X 4 com.

●

8-bit AD converter: 8 channels

●

8-bit SIO: 2 channels

●

16-bit timer/counter: 2 channels,

8-bit timer/counter: 2 channels

●

8-bit AD converter: 5 channels

●

8-bit

UART

: 1 channel

●

18-bit timer/counter: 1 channel,

8-bit timer/counter: 4 channels

2.7 to 5.5

2.7 to 5.5

2.2 to 5.5

QFP100

(

14 X 20mm

)

LQFP100

(

14 X 14mm

)

QFP80 (14 X 20mm

)

LQFP80 (12 X 12mm

)

QFP80 (14 X 20mm

)

LQFP80 (12 X 12mm

)

SDIP64

LQFP64

(

10 X 10mm

)

870/C

256

512

1K

512

1.5K

39

39

41

48

54

42

24 seg. X 4 com.

(On-chip voltage booster)

60 seg. X 16 com.

(On-chip voltage booster)

32 seg. X 4 com.

(On-chip voltage booster)

●

8-bit AD converter: 8 channels

●

8-bit SIO: 1 channel

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

●

8-bit AD converter: 4 channels

●

8-bit SIO: 1 channel,

UART

: 1 channel

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

●

8-bit AD converter: 8 channels

●

8-bit SIO: 1 channel

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 4 channels

●

10-bit AD converter: 8 channels

●

8-bit SIO/

UART

: 1 channel

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 4 channels

●

8-bit SIO/UART: 1 channel, 8-bit UART: 1 channel

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 4 channels

●

Real-time clock with calendar

●

10-bit AD converter: 8 channels

●

8-bit SIO: 1 channel,

8-bit

UART

: 1 channel

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 4 channels

●

Multiply-accumulate calculator (MAC)

●

10-bit AD converter: 8 channels

●

8-bit SIO: 1 channel, 8-bit SIO/UART: 1 channel

●

16-bit timer/counter: 2 channels, 8-bit timer/counter: 2 channels

●

Program patch logic

●

8-bit AD converter: 8 channels

●

8-bit SIO/

UART

: 1 channel,

8-bit SIO

: 1 channel

●

18-bit timer/counter: 1 channel,

8-bit timer/counter: 4 channels

1.8 to 5.5

1.8 to 5.5

1.8 to 5.5

1.8 to 3.6

1.8 to 3.6

1.8 to 3.6

1.8 to 5.5

1.8 to 5.5

1.8 to 5.5

1.8 to 3.6

LQFP64

(

10 X 10mm

)

QFP64

(

14 X 14mm

)

LQFP64

(

10

10mm

)

QFP64

(

14 X 14mm

)

LQFP64

(

10 X 10mm

)

LQFP80

(

12 X 12mm

)

TMP93CS20FG

TMP91CW40FG

TMP91FW40FG

64 K 2 K 88

40 seg. x 4 com.

(On-chip voltage booster)

● Serial interface: 3 channels

● 10-bit AD converter: 8 channels

● 16-bit timer/counter: 4 channels,

8-bit timer/counter: 4 channels

5V

10%

3V

10%

LQFP144

(

16 x 16 mm

)

900/L

2 K

2 K

QFP100

(

14 X 20mm

)

LQFP100 (14 X 14mm

)

55

40 seg. X 4 com.

(On-chip voltage booster)

●

10-bit AD converter: 8 channels

●

8-bit

UART

: 1 channel,

8-bit SIO

: 1 channel

●

10-bit timer/counter: 1 channel,

8-bit timer/counter: 2 channels

2.7 to 5.5

1 K

QFP80

(

14 X 20mm

)

52

70

69

43

LQFP64

(

10 X 10mm

)

LQFP64

(

10 X 10mm

)

QFP64

(

14 X 14mm

)

LQFP64

(

10 X 10mm

)

LQFP44

(

10 X 10mm

)

32 seg. X 4 com.

16 K

32 K

48 K

32 K

48 K

32 K

48 K

16K

24K

32K

4 K

8 K

32K

8 K

TMP47C222N/F/U

TMP47C422N/F/U

2 K

4 K

192

256

22

20 seg. x 4 com.

47E

● 8-bit AD converter: 4 channels

● 8-bit SIO: 1 channel

●

Pulse output: remote control transmission carrier

2.5 to 5.5

SDIP42

QFP44

(

14 x 14 mm

)

QFP44

(

10 x 10 mm

)

2.7 to 5.5

2 K

62

40 seg. X 4 com.

(On-chip voltage booster)

●

10-bit AD converter: 8 channels

●

8-bit SIO/

UART

: 1 channel,

8-bit

UART

: 1 channel

●

16-bit timer/counter: 2 channel,

8-bit timer/counter: 4 channels

2.7 to 5.5

128 K 4 K 61

40 seg. x 4 com.

(Not voltage booster type)

● Serial interface: 4 channels

● 10-bit AD converter: 12 channels

● 16-bit timer/counter: 3 channels,

8-bit timer/couter: 4 channels

2.7 to 3.6

LQFP100

(

14 x 14 mm

)

900/L1

16 K

8 K

512 32

48K

60K

48K

48K

60K

16-bit microcontrollers with LCD driver

8-bit microcontrollers with LCD driver

4-bit microcontrollers with LCD driver

TMP86FM26UG

TMP86C829BUG/BFG

TMP86CH29BUG/BFG

TMP86CM29BUG/BFG

TMP86CM29LUG

TMP86FM29UG/FG

TMP86CM23AUG

♦

TMP86CP23AUG

♦

TMP86FS23UG ▲

TMP86FP24FG

TMP86CM27FG

TMP86CP27AFG

TMP86FS27FG

TMP86CM25FG

TMP86CM25AFG

TMP86FS28FG/DFG ▲

TMP86CH22UG ♦

TMP86C822UG ♦

TMP86CS25AFG

♦

TMP86CS25ADFG

♦

TMP86CS28FG/DFG ▲

TMP86C420UG/FG

TMP86C820UG/FG

TMP86CH21FG

TMP86CH21AUG ♦

*

Some of the flash memories use the SuperFlash® technology under the license of Silicon Storage Technology, Inc. SuperFlash® is a registered trademark of Silicon Storage Technology, Inc.

1.5K

32K

16 K

16

Applications

ROM

size

32 K

24 K

16 K

8 K

40 K

48 K

60 K

64 K

72 K

96 K

128 K

870/C Series

870/X

Series

64-pin 80-pin 100-pin

QFP/SDIP QFP

QFP

Audio systems Air conditioners Refrigerators

Washing machines

DVDs

The following microcontrollers incorporate high breakdown voltage output for directly driving a fluorescent display tube and a display circuit for automatically transferring display data to a port. In addition to existing products, such as a VFT driver circuit which can display digits on a segmented display, Toshiba offers a line-up of

products which support automatic display on universal-grid display tubes.

■ Microcontrollers with fluorescent display tube driver

Microcontrollers Listed by

Function

/

Application

8-/16-bit microcontrollers with fluorescent display tube driver

: In mass production

: Under development

QFP

DIP

TMP87C814

TMP87CH14

TMP87CK14

TMP87CM14

TMP87PM14

870

Series

TMP87PS71A

TMP87CS71B

TMP88PU74

TMP88CU74

TMP88CP77

TMP88CS77

TMP88PU77

TMP88CU77

TMP87PM74

TMP87CM74A

TMP87CH74A

TMP87PM75

TMP87CM75

TMP87CH75

TMP86PM74A

TMP86CM74A

TMP86CK74A

TMP86PM72

TMP86CM72

TMP86CH72

8-bit microcontrollers with fluorescent display tube driver

ROM

(bytes)

RAM

(bytes)

Series

Name

Part Number I

/ OVFT Driver(Fluorescent Tube Driver)

Additional Functions Package

TMP87C814NG/FG

TMP87CH14NG/FG

TMP87CK14NG/FG

TMP87CM14NG/FG

TMP87CS71BFG

TMP87CH74AFG

TMP87CM74AFG

TMP87CH75FG

TMP87CM75FG

TMP86CK74AFG

TMP86CM74AFG

TMP86CH72FG

TMP86CM72FG

TMP88CU74F

G

TMP88CP77FG

TMP88CS77FG

TMP88CU77FG

8 K

16 K

24 K

32 K

60 K

16 K

32 K

16 K

32 K

24 K

32 K

16 K

32 K

96 K

48 K

64 K

96 K

512

1 K

2 K

512

1K

512

1K

1K

2K

1K

2K

1K

2K

3K

870

870/C

55

73

71

70

89

54

●

8-bit SIO: 1 channel

●

16-bit timer/counter: 2 channels,

8-bit timer/counter: 2 channels

●

8-bit AD converter: 12 channels ●

8-bit SIO: 2 channels

●

16-bit timer/counter: 3 channels,

8-bit timer/counter: 1 channel

●

8-bit AD converter: 8 channels

●

8-bit SIO: 1 channel

●

16-bit timer/counter: 2 channels,

8-bit timer/counter: 2 channels

●

8-bit AD converter: 12 channels

●

8-bit SIO: 2 channels

●

16-bit timer/counter: 2 channels,

8-bit timer/counter: 2 channels

●

AD converter input: 6 channels

●

8-bit SIO: 1 channel

●

High-speed serial output

QFP80

(

14 x 20mm

)

QFP80

(

14 x 20mm

)

QFP100

(

14 x 20mm

)

QFP80

(

14 x 20mm

)

16 seg. x 16 dig.

88

SDIP64/

QFP64

(

14 x 20mm

)

Maximum breakdown

voltage:

40 V on each of 24 pins

Maximum breakdown voltage:

40 V on each of 37 pins

Programmable grid scan output

Maximum breakdown voltage:

40 V on each of 51 pins

Programmable grid scan output

●

8-bit AD converter: 8 channels ● 8-bit SIO: 1 channel

●

16-bit timer/counter: 2 channels,

8-bit timer/counter: 2 channels

QFP100

(

14 x 20mm

)

Maximum breakdown voltage:

41 V on each of 37 pins

Programmable grid scan output

●

8-bit AD converter: 6 channels ●

8-bit SIO: 1 channel

●

16-bit timer/counter: 1 channel,

8-bit timer/counter: 2 channels ●

I2C bus: 1 channel

QFP64

(

14 x 14mm

)

Maximum breakdown voltage:

41 V on each of 32 pins

Programmable grid scan output

Maximum breakdown voltage:

40 V on each of 37 pins

Programmable grid scan output

Maximum breakdown voltage:

40 V on each of 53 pins

Programmable grid scan output

870/X

71

*

For details of the products listed above, see the "Part Number List".

17

■ General-purpose microcontrollers in compact packages

This comprehensive product line comes in compact packages, including SOPs, SSOPs and 7 mm x 7 mm

48-pin flat packages.

20-pin 28-pin 30-pin 32-pin 42-pin 48-pin44-pin

SOP/DIP SOP/SDIP SDIP

LQFP

SSOP

ROM

size

4 K

2 K

64 K

8 K

16 K

48 K

32 K

SDIP LQFP/QFP

Applications

Electronic dictionaries

PDAs Game machines Telephones Remote controls Audio systems Air conditioners Refrigerators

Washing machines

Rice cookers TVsAutomotive

General-purpose microcontrollers in compact packages

TMP86P202MG/NG

TMP86P203MG/NG

TMP86C407MG/NG

TMP86C407IMG/NG

TMP86C407SMG/NG

TMP86C807MG/NG

TMP86C807IMG/NG

TMP86C807SMG/NG

TMP86F807MG/NG

TMP88CH40MG/NG

TMP88CS34NG/FG

TMP88CS38ANG/F

TMP88CS38BNG/NG

TMP88CP34NG/FG

TMP88CP38ANG/F

TMP88CM38ANG/F

TMP88CH41NG/UG

TMP88CM38BNG/F

TMP88CP38BNG/FG

TMP86C408DMG

TMP86C408IDMG

TMP86C408SDMG

TMP86C808DMG

TMP86C808IDMG

TMP86C808SDMG

TMP86F808DMG

TMP86C892IDMG

TMP86C892SDMG

TMP86CH12MG

TMP88CH40IMG

TMP86FH12MG

TMP86FH92DMG

TMP86FH92IDMG

TMP86CH92IDMG

TMP86CH92SDMG

TMP86F409NG

TMP86C809NG

TMP86F809NG

TMP86CH09NG

TMP86FH09NG

TMP86FH93NG

TMP86C846NG

TMP86CH06NG

TMP86CH46ANG

TMP86FH46ANG

TMP86CM46ANG

TMP86C845UG

TMP86C822UG

TMP86C847UG

TMP86C847IUG

TMP86C847SUG

TMP86CH47SUG

TMP86FH47AUG

TMP86CH87RUG

TMP88CH41IUG

TMP88CH41SUG

TMP86CM47AUG

TMP86CM87RUG

TMP86CH06AUG

TMP86CH47AUG

TMP86CH47IUG

TMP93CS36UG

TMP86FH47ADUG

: In mass production

: Under development

: Under planning

SOP/QFP

DIP

18

Microcontrollers Listed by Function / Application

870/C

TMP86P202MG

SOP20

●

8-bit AD converter: 4 channels

●

8-bit timer/counter: 2 channels

TMP86P202PG

DIP20

TMP86P203MG

2 K 128 14

SOP20

3.3 to 5.5

TMP86P203PG

TMP86CH06NG

DIP20

TMP86CH06AUG

♦

SDIP42

●

8-bit SIO/UART (switchable): 1 channel

●

UART: 1 channel

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

SEI

●

UART: 1 channel

●

8-bit AD converter: 6 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

SEI

●

UART: 1 channel

●

10-bit AD converter: 6 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

●

8-bit SIO: 1 channel

●

UART: 1 channel

●

10-bit AD converter: 8 channels

●

16-bit timer/counter: 1 channel, 10-bit timer/counter: 1 channel,

8-bit timer/counter: 2 channels

●

8-bit SIO: 1 channel

●

10-bit AD converter: 8 channels

●

8-bit timer/counter: 2 channels

●

8-bit SIO: 1 channel

●

UART: 1 channel

●

10-bit AD converter: 8 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

LCD

●

8-bit SIO: 1 channel

●

UART: 1 channel

●

8-bit AD converter: 4 channels

●

18-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

TMP86PH06NG

16 K 512 35

1.8 to 5.5

TMP86PH06UG

TMP86C407MG

256

22

SOP28

2.7 to 5.5

TMP86P807MG

TMP86F807MG

TMP86C407NG

SDIP28

TMP86P807NG

TMP86F807NG

TMP86C407IMG

4 K

SOP28

TMP86P807MG

TMP86C407ING

SDIP28

TMP86P807NG

TMP86C407SMG

★

SOP28

TMP86P807MG

TMP86C407SNG

★

SDIP28

TMP86P807NG

TMP86C807MG

8 K

SOP28

TMP86P807MG

TMP86F807MG

TMP86C807NG

SDIP28

TMP86P807NG

TMP86F807NG

TMP86C807IMG

SOP28

TMP86P807MG

TMP86C807ING

SDIP28

TMP86P807NG

TMP86C807SMG

★

SOP28

TMP86P807MG

TMP86C807SNG

★

SDIP28

TMP86P807NG

TMP86F807MG

SOP28

TMP86F807NG

SDIP28

TMP86C408DMG

SSOP30

TMP86P808DMG

TMP86F808DMG

TMP86P808DMG

TMP86F808DMG

4 K

24

TMP86C408IDMG

TMP86P808DMG

TMP86P808DMG

TMP86C408SDMG

★

TMP86C808DMG

8 K

TMP86C808IDMG

TMP86C808SDMG ★

TMP86F808DMG

TMP86F409NG ▲

TMP86C809NG

8 K

4 K

512

26 SDIP32

TMP86FH09NG ▲

TMP86F809NG ▲

TMP86FH09NG ▲

TMP86F809NG ▲

TMP86CH09NG

TMP86FH09NG ▲

16 K

TMP86CH12MG

24 SSOP30

TMP86FH12MG ▲

TMP86FH12MG ▲

TMP86C822UG

♦

8 K

33

LQFP44

(10 x 10mm)

1.8 to 5.5

TMP86PH22UG

♦

TMP86CH22UG

♦

16 K

TMP86C845UG

8 K

256 35

SDIP42

2.7 to 5.5

TMP86PM47AUG

TMP86PH47UG

TMP86FH47AUG

▲

TMP86C846NG

512

33

1.8 to 5.5

TMP86PH46NG

♦

TMP86PM46NG

TMP86FH46ANG

▲

TMP86CH46ANG

♦

16 K

TMP86FH46ANG ▲

TMP86CM46ANG

8 K

1 K

2.7 to 5.5

TMP86PM46NG

512

35

LQFP44

(10 x 10mm)

1.8 to 5.5

TMP86PM47AUG

TMP86PH47UG

♦

TMP86FH47AUG ▲

TMP86C847UG

TMP86C847IUG

2.7 to 5.5

TMP86PM47AUG

TMP86PH47UG

TMP86FH47AUG

TMP86C847SUG

★

16 K

32 K

1.8 to 5.5

TMP86PM47AUG

TMP86PH47UG

♦

TMP86FH47AUG ▲

TMP86FH47ADUG ▲

TMP86CH47AUG

♦

8-bit microcontrollers (TLCS-870/C Series)

Part Number Flash

ROM

(bytes)

RAM

(bytes)

Series

Name

I/O Additional FunctionsCompact Package Supply Voltage (V) Version with OTP/Flash

LQFP44

(10 x 10mm)

: Guaranteed over the ambient temperature (Topr) range of -40oC to 125oC.

: Guaranteed over the ambient temperature (Topr) range of -20oC to 85oC at 1.8 V to 2.0 V.

: Guaranteed over the ambient temperature (Topr) range of -20oC to 85oC at 2.7 V to 3.0 V.

19

Applications

Electronic dictionaries

PDAs Game machines Telephones Remote controls Audio systems Air conditioners Refrigerators

Washing machines

Rice cookers TVsAutomotive

TMP86CH47IUG

TMP86CH47SUG

★

TMP86FH47AUG ▲

TMP86FH47ADUG ▲

TMP86CM47AUG

TMP86C892IDMG

TMP86C892SDMG ★

TMP86CH92IDMG

TMP86CH92SDMG ★

TMP86FH92DMG

TMP86FH92IDMG

TMP86FH93NG

TMP86CH87RUG

TMP86CM87RUG

SDIP32

SDIP42

SSOP30

16 K

32 K

8 K

16 K

48 K

64 K

32 K

48 K

64 K

16 K

16 K

32 K

512

1 K

512

2 K

512

1.5 K

33

35

24

19

33

26

2.7 to 5.5

1.8 to 5.5

3.0 to 5.5

2.7 to 5.5

4.5 to 5.5

4.5 to 5.5

2.7 to 5.5

870/C

870/X

16-bit microcontrollers (TLCS-900/L Series)

8-bit microcontrollers (TLCS-870/C Series,TLCS-870/X Series)

Part Number Flash

ROM

(bytes)

RAM

(bytes)

Series

Name

I/O Additional FunctionsCompact Package Supply Voltage (V) Version with OTP/Flash

Part Number

ROM

(bytes)

RAM

(bytes)

Series

Name

I/O Additional FunctionsCompact Package Supply Voltage (V) Version with OTP/Flash

: Guaranteed over the ambient temperature (Topr) range of -40oC to 125oC.

CAN

SEI

UART: 1 channel

●

10-bit AD converter: 14 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

SEI

UART: 1 channel

I2C/UART

(switchable)

10-bit AD converter: 6 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

I2C

: 1 channel

PWM: 4 channels

●

8-bit AD converter: 6 channels

●

16-bit timer/counter: 2 channels, 8-bit timer/counter: 2 channels

●

Remote control detection

●

Program patch logic

I2C

: 1 channels

PWM: 10 channels

●

8-bit AD converter: 6 channels

●

16-bit timer/counter: 2 channels, 8-bit timer/counter: 2 channels

●

Remote control detection

●

Program patch logic

●

8-bit SIO: 1 channel

UART: 1 channel

●

10-bit AD converter: 4 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

●

Motor control

●

8-bit SIO: 1 channel

UART: 1 channel

●

10-bit AD converter: 8 channels

●

16-bit timer/counter: 2 channels, 8-bit timer/counter: 2 channels

●

Motor control

LQFP44

(10 x 10mm)

LQFP44

(10

x

10mm)

QFP44

(14

x

14mm)

SDIP42

QFP44

(14

x

14mm)

SDIP42

QFP44

(14

x

14mm)

SDIP42

QFP44

(14

x

14mm)

SDIP42

QFP44

(14

x

14mm)

SDIP42

QFP44

(14

x

14mm)

SDIP42

QFP44

(14

x

14mm)

SDIP42

SOP28

SOP28

SDIP28

SDIP42

QFP44

(14

x

14mm)

LQFP44

(10 x 10mm)

LQFP44

(10 x 10mm)

LQFP48

(7

x

7mm)

●

8-bit SIO: 1 channel

●

UART: 1 channel

●

10-bit AD converter: 8 channels

●

16-bit timer/counter: 1 channel, 8-bit timer/counter: 2 channels

TMP86PM47AUG

TMP86PM87RUG

TMP86FH92IDMG

TMP88PS38BNG

TMP88PS34NG

TMP88PS34FG

TMP88PS34NG

TMP88PS34FG

TMP88PS38NG

TMP88PS38FG

TMP88PS38BNG

TMP88PS38BFG

TMP88PS38NG

TMP88PS38FG

TMP88PS38BNG

TMP88PS38BFG

TMP88PS38NG

TMP88PS38FG

TMP88PS38BFG

TMP88PH40MG

TMP88PH40NG

TMP88PH40MG

TMP88PH41UG

TMP88PH41UG

TMP88PH41NG

TMP86PM47AUG

TMP86PH47UG

TMP86FH47AUG

TMP93CS36UG

64 K 2 K

33

5V 10%

900/L

LQFP44

(10 x 10mm)

●

SIO/UART: 2 channels

●

10-bit AD converter: 4 channels

●

16-bit timer/counter: 2 channels, 8-bit timer/counter: 4 channels

●

Clock gear

TMP88CP34FG

TMP88CP34NG

TMP88CS34FG

TMP88CS34NG

TMP88CM38AF

TMP88CM38ANG

TMP88CM38BFG

TMP88CM38BNG

TMP88CP38AF

TMP88CP38ANG

TMP88CP38BFG

TMP88CP38BNG

TMP88CS38FG

TMP88CS38NG

TMP88CS38BFG

TMP88CS38BNG

TMP88CH40MG

TMP88CH40NG

TMP88CH41NG

TMP88CH41IUG

TMP88CH41SUG

TMP88CH40IMG

TMP88CH41UG

: Under development

++: Under planning

: Guaranteed over the ambient temperature (Topr) range of -20oC to 85oC at 1.8 V to 2.0 V.

: Guaranteed over the ambient temperature (Topr) range of -20oC to 85oC at 2.7 V to 3.0 V.

*

Some of the flash memories use the SuperFlash® technology under the license of Silicon Storage Technology, Inc. SuperFlash® is a registered trademark of Silicon Storage Technology, Inc.

20

28-pin

SOP/SDIP

QFP/LQFP

(

10

10mm

)

SDIP/QFP

(

14

14mm

)

30-pin 42- / 44-pin 44-pin

SSOP/SDIP

20-pin

SOP/DIP

ROM

size

2 K

4 K

16 K

24 K

32 K

48 K

60 K

64 K

96 K

8-bit

AD converter:

6 channels

86C407

86C407I/S

86C807I/S

86C807

86F807

10-bit

AD converter:

4 channels

88CH40

88CH40I

120 K

10-bit

AD converter:

8 channels

86C846

86CH46A

86FH46A

88CH41

86CM46A

10-bit

AD converter:

14 channels

86CM87

86CH87

10-bit

AD converter:

8 channels

86C847

86C847I/S

86C845

86CH47A

86CH47I/S

86FH47A

88CH41

88CH41I/S

86CM47A

86CS44

*

For details of the products listed above, see the "Part Number List".

8 K

32-pin

SDIP

48-pin

LQFP

(

7

7mm

)

10-bit

AD converter:

6 channels

86FH09

86FH93

86CH09

86F409

86C809

86F809

10-bit

AD converter:

8 channels

86FH47A

8-bit

AD converter:

4 channels

86CH22

86C822

8-bit

AD converter:

6 channels

86C808I/S

86C408I/S

86FH12

86CH12

10-bit

AD converter:

6 channels

86FH92I

86FH92

86CH92I/S

86C892I/S

88CM38B

88CM38A

88CP38B

88CP38A

88CP34

8-bit

AD converter:

4 channels

86P202

86P203

10-bit

AD converter:

8 channels

88CS38B

88CS38

88CS34

8-bit

AD converter:

6 channels

86C408

86C808

86F808

Microcontrollers Listed by Function / Application

■ Microcontrollers with AD converters

8-bit microcontrollers with AD converters

: In mass production

: Under development

: Under planning

SOP/QFP

DIP

21

SDIP / QFP

(

14

20mm

)

QFP

(

14

14mm

)

/LQFP

(

10

10mm

)

64-pin

QFP

(

14

20mm

)

/ LQFP

(

12

12mm

)

80-pin 100-pin

QFP

(

14

20mm

)

/ LQFP

(

14

14mm

)

8-bit

AD converter:

8 channels

86CK74A

86CM74A

8-bit

AD converter:

8 channels

86CS25A

86CM25

86CM25A

86FM25

10-bit

AD converter:

16 channels

88FW45

88CS43

8-bit

AD converter:

6 channels

86CH72

86CM72

86CH29B

86CM29L

86CM29B

86FM29

86CM23A

86CP23A

10-bit

AD converter:

8 channels

86FS23

86C829B

8-bit

AD converter:

8 channels

86CH21A

86C820

86C420

10-bit

AD converter:

16 channels

87C841

88CS42

86CH49

86CH48I/S

86FM48

86CM49

86FS49AI

86FS49A

89FS60

86CS49

88CU74

88CP77

88CS77

88CU77

86CP27A

86FP24

86FS27

86FS28

86CS28

86CM27

10-bit

AD converter:

16 channels

86FS64

88FW44

86CS64A

8-bit

AD converter:

12 channels

8-bit

AD converter:

12 channels

10-bit

AD converter:

8 channels

Applications

Electronic dictionaries

PDAs Game machines Telephones Remote controls Audio systems Air conditioners Refrigerators

Washing machines

Rice cookers TVsAutomotive

*

Some of the flash memories use the SuperFlash® technology under the license of Silicon Storage Technology, Inc. SuperFlash® is a registered trademark of Silicon Storage Technology, Inc.

22

44-pin

64-pin

80-pin

100-pin

ROM

size

N/A

8 K

10-bit

AD converter:

8 channels

10-bit

AD converter:

4 channels

10-bit

AD converter:

4 channels

10-bit

AD converter:

4 channels

10-bit

AD converter:

4 channels

91CP27

91CK27

91CU27R

91CU27

10-bit

AD converter:

5 channels

10-bit

AD converter:

6 channels

10-bit

AD converter:

12 channels

10-bit

AD converter:

8 channels

6-bit

AD converter:

4 channels

91FY27

32 K

48 K

64 K

96 K

93CS36 93CS44

93CS45

93CS32

96C031Z

96CM40

96C141B

96C041B

93CU44

93CW4491FW27 91CW18A

93CS42A

95C061B

91C025

91C219

92CM22

91C630

91C829

91C824

1941A

93CM40

91CY22

91CY22I

91FY42

91CW28

91CW12A

91CW11

91CU10

95CW65

95C265

93CW41

93CS41

91CY28

91FY28

95CW64

93CW40D

95CS64

93CS40

10-bit

AD converter:

8 channels

10-bit

AD converter:

19 channels

512 K

1 M

2 M

1.5 M

256 K

384 K

128 K

24 K

*

For details of the products listed above, see the "Part Number List".

LQFP

(

12 x 12mm

)

QFP

(

14 x 20mm

)

QFP

(

14 x 14mm

)

LQFP

(

10 x 10mm

)

LQFP

(

10 x 10mm

)

QFP

(

14 x 20mm

)

LQFP

(

14 x 14mm

)

19A71CY

1940CYA

19A71FY

10-bit

AD converter:

8 channels

1940FDB

93CW46A

91CW12

: In mass production

: Under development

QFP

Microcontrollers Listed by Function / Application

16- / 32-bit microcontrollers with AD converters

23

LQFP

(

14 x 14mm

)

QFP

(

14 x 20mm

)

TQFP

(

14 x 14mm

)

LQFP

(

16 x 16mm

)

LQFP

(

20 x 20mm

)

QFP

(

28 x 28mm

)

LQFP

(

20 x 20mm

)

FBGA

(

12 x 12mm

)

100-pin

128-pin 144-pin 160-pin

10-bit

AD converter:

8 channels

10-bit

AD converter:

5 channels

10-bit

AD converter:

8 channels

10-bit

AD converter:

8 channels

10-bit

AD converter:

8 channels

91C815 92C820

10-bit

AD converter:

12 channels

92CM27

10-bit

AD converter:

4 channels

92CA25

93CS20

91C820A

94C251A

95C063 94C241C

10-bit

AD converter:

6 channels

92CF29

193-pin176-pin

10-bit

AD converter:

12 channels

10-bit

AD converter:

12 channels

92FD23A

92FD54AI

92CD54I

92FD23A

92CD23A

10-bit

AD converter:

16 channels

19A43FD

19A43CD

19A43FZ

19A43CZ

92CD23A

92FY23

92CY23

10-bit

AD converter:

16 channels

1942FD

1942CZ

1942CY

92FY23

92CY23

10-bit

AD converter:

4 channels

91FW40

91CW40

10-bit

AD converter:

16 channels

91FW60

91CW60

10-bit

AD converter:

16 channels

91FW60

91CW60

92CH21

10-bit

AD converter:

12 channels

91CP82T

FBGA

(

15 x 15mm

)

228-pin

10-bit

AD converter:

6 channels

92CF26A

92CZ26A

FBGA

(

13 x 13mm

)

281-pin

Applications

10-bit

AD converter:

24 channels

19A64F20B

19A64C1D

1962F10A

1962C10B

Electronic dictionaries

PDAs Game machines Telephones Remote controls Audio systems Air conditioners Refrigerators

Washing machines

Rice cookers Automotive

*

Some of the flash memories use the SuperFlash® technology under the license of Silicon Storage Technology, Inc. SuperFlash® is a registered trademark of Silicon Storage Technology, Inc.

24

Microcontrollers Listed by Function / Application

PM12:00

● SDRAM controller

TMP92CZ26

A

TMP92

CF29

TMP92CA25

TMP92CH21

TMP92C820

TMP91C820A

Applications

Electronic dictionaries

PDAs

NAND

FLASH

data

program

NOR

FLASH

Less

SDRAM

program

data

stack

VRAM

MASK

ROM

Dictionary

data

NOR

FLASH

program

DSP

MP3/JPEG

codec

keyboard

SD

CARD

Power

Device

LCDD

Column

Monochrome

LCD panel

Color

LCD panel

PC

Sound LSI

DAC

PW

amp

BLD

LCDD

ROW

USB

CPU

MCU

SDRAM I/F

NANDF I/F

SPI I/F

LCDC

SRAM

data

stack

work

VRAM

*

For details of the products listed above, see the "Part Number List".

LCD display

●

TFT (16M colors)/STN color (262K colors)

TMP92CZ26A

TMP92CF29

● TFT/STN color (4096 colors)

TMP92CH21

● Monochrome

16 gray levels

TMP92C820

TMP91C820A, etc.

● Monochrome

TMP92CA25

TMP91C815

TMP91C016

TMP91C025, etc.

PC interface

● USB circuit

TMP92CZ26A

TMP92CF29

TMP92CH21

● UART

TMP91C815, etc.

All products

Clock with calendar

● RTC circuit

TMP91C815, etc.

All products

Touch panel

interface

● AD circuit

TMP92CZ26A

TMP92CF29

TMP92CA25

TMP92CH21

TMP91C025

Memory access with

low bit unit cost

● SPI interface

TMP92CZ26

A

TMP92

CF29

TMP92CA25

● NANDF interface

TMP92CZ26

A

TMP92CA25

TMP92CH21

Large capacity memory access

● MMU circuit

TMP91C815, etc.

All products

Keyboard matrix &

Key-on wake-up

TMP91C815, etc. All products

TMP91C824FG TMP91C016FG TMP91C025FG TMP91C815FG TMP91C820AFG TMP92C820FG TMP92CH21FG

- W/B

8ch -

--

8K -

- EDO

1ch 1ch

1ch 1ch

1ch -

--

106MBmax 105MBmax

121ns

16.5MHz/2.7V

148ns

13.5MHz/2.7V

112ns

18MHz/3.0V

148ns

13.5MHz/2.7V

112ns

18MHz/3.0V

50ns

20MHz/3.0V

50ns

20MHz/3.0V

50ns

20MHz/3.0V

4ch 4ch

--

--

--

W/B

4ch

-

-

-

1ch

1ch

-

-

72MBmax

4ch

-

-

-

W/B

8ch

-

8K

-

1ch

1ch

1ch

-

136MBmax

4ch

-

-

-

16Gray

8ch

8K

8K

SDRAM

2ch

1ch

1ch

-

136MBmax

4ch

1ch

-

-

16Gray

5ch

-

8K

SDRAM

3ch

1ch

1ch

-

136MBmax

4ch

1ch

-

-

Gray/Color

4ch

8K(Boot)

16K

SDRAM

Program execute

2ch

1ch

-

-

512MBmax

4ch

1ch

USB Device

-

W/B

4ch

-

10K

SDRAM

Program execute

1ch

1ch

1ch

1ch

512MBmax

4ch

1ch

-

-

TMP92CA25FG

12.5ns

80MHz/3.0V,1.4V