Toshiba TX39 User Manual

32-Bit RISC MICROPROCESSOR

TX39 FAMILY CORE ARCHITECTURE

USER'S MANUAL

Jul. 27, 1995

R3000A is a Trademark of MIPS Technologies, Inc.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may

result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA

or others.

The products described in this document contain components made in the United States and subject to export control

of the U.S.authorities. Diversion contrary to the U.S. law is prohibited.

These TOSHIBA products are intended for usage in general electronic equipments (office equipment, communication

equipment, measuring equipment, domestic electrification, etc.).Please make sure that you consult with us before you

use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which

could have major impact to the welfare of human life (atomic energy control, airplane, spaceship, traffic signal,

combustion control, all type of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may

occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with

TOSHIBA,

1995 TOSHIBA CORPORATION

All Rights Reserved.

CONTENTS

CONTENTS

Architecture

Chapter 1 Introduction--------------------------------------------------------------------------- 3

1.1 Features ------------------------------------------------------------------------------ 3

1.1.1 High-performance RISC techniques ---------------------------------------------------- 3

1.1.2 Functions for embedded applications--------------------------------------------------- 3

1.1.3 Low power consumption ------------------------------------------------------------------- 4

1.1.4 Development environment for embedded arrays and cell-based ICs ---------- 4

1.2 Notation Used in This Manual--------------------------------------------------- 5

Chapter 2 Architecture ------------------------------------------------------------------------- 7

2.1 Overview------------------------------------------------------------------------------ 7

2.2 Registers------------------------------------------------------------------------------ 8

2.2.1 CPU registers--------------------------------------------------------------------------------- 8

2.2.2 System control coprocessor (CP0) registers ----------------------------------------- 9

2.3 Instruction Set Overview------------------------------------------------------------10

2.4 Data Formats and Addressing ----------------------------------------------------15

2.5 Pipeline Processing Overview-----------------------------------------------------18

2.6 Memory Management Unit (MMU)-----------------------------------------------19

2.6.1 R3900 Processor Core operating modes----------------------------------------------- 19

2.6.2 Direct segment mapping-------------------------------------------------------------------- 20

Chapter 3 Instruction Set Overview------------------------------------------------------------23

3.1 Instruction Formats ------------------------------------------------------------------23

3.2 Instruction Notation ------------------------------------------------------------------23

3.3 Load and Store Instructions -------------------------------------------------------24

3.4 Computational Instructions ---------------------------------------------------------27

3.5 Jump/Branch Instructions ----------------------------------------------------------32

3.6 Special Instructions ------------------------------------------------------------------35

3.7 Coprocessor Instructions-----------------------------------------------------------36

3.8 System Control Coprocessor (CP0) Instructions-----------------------------38

i

CONTENTS

Chapter 4 Pipeline Architecture-----------------------------------------------------------------39

4.1 Overview--------------------------------------------------------------------------------39

4.2 Delay Slot-------------------------------------------------------------------------------40

4.2.1 Delayed load----------------------------------------------------------------------------------- 40

4.2.2 Delayed branching---------------------------------------------------------------------------- 40

4.3 Nonblocking Load Function--------------------------------------------------------41

4.4 Multiply and Mupliply/Add Instructions (MULT, MULTU, MADD, MADDU) --41

4.5 Divide Instruction (DIV, DIVU) ----------------------------------------------------42

4.6 Streaming-------------------------------------------------------------------------------42

Chapter 5 Memory Management Unit (MMU)-----------------------------------------------43

5.1 R3900 Processor Core Operating Modes--------------------------------------43

5.2 Direct Segment Mapping -----------------------------------------------------------44

Chapter 6 Exception Processing ---------------------------------------------------------------47

6.1 Overview--------------------------------------------------------------------------------47

6.2 Exception Processing Registers--------------------------------------------------50

6.2.1 Cause register--------------------------------------------------------------------------------- 51

6.2.2 EPC (Exception Program Counter) register--------------------------------------------52

6.2.3 Status register --------------------------------------------------------------------------------- 53

6.2.4 Cache register--------------------------------------------------------------------------------- 56

6.2.5 Status register and Cache register mode bit and exception processing-------- 58

6.2.6 BadVAddr (Bad Virtual Address) register----------------------------------------------- 60

6.2.7 PRId (Processor Revision Identifier) register------------------------------------------ 60

6.2.8 Config (Configuration) register ------------------------------------------------------------ 61

6.3 Exception Details---------------------------------------------------------------------63

6.3.1 Memory location of exception vectors--------------------------------------------------- 63

6.3.2 Address Error exception -------------------------------------------------------------------- 64

6.3.3 Breakpoint exception------------------------------------------------------------------------- 65

6.3.4 Bus Error exception -------------------------------------------------------------------------- 66

ii

CONTENTS

6.3.5 Coprocessor Unusable exception -------------------------------------------------------- 68

6.3.6 Interrupts---------------------------------------------------------------------------------------- 69

6.3.7 Overflow exception--------------------------------------------------------------------------- 70

6.3.8 Reserved Instruction exception------------------------------------------------------------70

6.3.9 Reset exception------------------------------------------------------------------------------- 71

6.3.10 System Call exception----------------------------------------------------------------------- 72

6.3.11 Non-maskable interrupt --------------------------------------------------------------------- 72

6.4 Priority of Exceptions----------------------------------------------------------------73

6.5 Return from Exception Handler---------------------------------------------------73

Chapter 7 Caches ----------------------------------------------------------------------------------75

7.1 Instruction Cache---------------------------------------------------------------------75

7.2 Data Cache ----------------------------------------------------------------------------76

7.2.1 Lock function----------------------------------------------------------------------------------- 77

7.3 Cache Test Function-----------------------------------------------------------------79

7.4 Cache Refill----------------------------------------------------------------------------80

7.5 Cache Snoop--------------------------------------------------------------------------81

Chapter 8 Debugging Functions----------------------------------------------------------------83

8.1 System Control Processor (CP0) Registers-----------------------------------83

8.2 Debug Exceptions--------------------------------------------------------------------87

8.3 Details of Debug Exceptions-------------------------------------------------------90

Appendix A Instruction Set Details -------------------------------------------------------93

iii

CONTENTS

TMPR3901F

Chapter 1 Introduction---------------------------------------------------------------------------201

1.1 Features ------------------------------------------------------------------------------201

1.2 Internal Blocks-----------------------------------------------------------------------203

Chapter 2 Configuration ------------------------------------------------------------------------ 205

2.1 R3900 Processor Core------------------------------------------------------------ 205

2.1.1 Instruction limitations -----------------------------------------------------------------------206

2.1.2 Address mapping ----------------------------------------------------------------------------206

2.2 Clock Generator --------------------------------------------------------------------206

2.3 Bus Interface Unit (Bus Controller / Write Buffer)--------------------------207

2.4 Memory Protection Unit-----------------------------------------------------------208

2.4.1 Registers---------------------------------------------------------------------------------------208

2.4.2 Memory protection exception-------------------------------------------------------------210

2.4.3 Register address map----------------------------------------------------------------------211

2.5 Debug Support Unit----------------------------------------------------------------211

2.6 Synchronizer------------------------------------------------------------------------- 211

Chapter 3 Pins ------------------------------------------------------------------------------------215

Chapter 4 Operations----------------------------------------------------------------------------217

4.1 Clock-----------------------------------------------------------------------------------217

4.2 Read Operation---------------------------------------------------------------------219

4.2.1 Single read ------------------------------------------------------------------------------------219

4.2.2 Burst read--------------------------------------------------------------------------------------221

4.3 Write Operation---------------------------------------------------------------------224

4.4 Interrupts------------------------------------------------------------------------------225

4.4.1 NMI*---------------------------------------------------------------------------------------------225

4.4.2 INT[5:0]*----------------------------------------------------------------------------------------226

iv

CONTENTS

4.5 Bus Arbitration-----------------------------------------------------------------------227

4.5.1 Bus request and bus grant-----------------------------------------------------------------227

4.5.2 Cache snoop----------------------------------------------------------------------------------228

4.6 Reset ----------------------------------------------------------------------------------229

4.7 Half-Speed Bus Mode------------------------------------------------------------- 230

Chapter 5 Power-Down Mode----------------------------------------------------------------- 231

5.1 Halt mode----------------------------------------------------------------------------- 231

5.2 Standby Mode-----------------------------------------------------------------------233

5.3 Doze Mode---------------------------------------------------------------------------234

5.4 Reduced Frequency Mode-------------------------------------------------------235

v

Architecture

Architecture

1

Architecture

2

Chapter 1 Introduction

1.1 Features

The R3900 Processor Core is a high-performance 32-bit microprocessor core developed by Toshiba based on

the R3000A RISC (Reduced Instruction Set Computer) microprocessor. The R3000A was developed by

MIPS Technologies, Inc.

Toshiba develops ASSPs (Application Specific Standard Products) using the R3900 Processor Core and

provides the R3900 as a processor core in Embedded Array or Cell-based ICs. The low power consumption

and high cost-performance ratio of this processor make it especially well-suited to embedded control

applications in products such as PDAs (Personal Digital Assistants) and game equipment.

Architecture

1.1.1 High-performance RISC techniques

• R3000A architecture

− R3000A upward compatible instruction set (excluding TLB (translation lookaside buffer)

instructions and some coprocessor instructions)

− Five-stage pipeline

• Built-in cache memory

− Separate instruction and data caches

− Data cache snoop function: Invalidatation of data in the data cache to maintain cache memory

and main memory consistency on DMA transfer cycles

• Nonblocking load

− Execute the following instruction regardless of a cache miss caused by a preceding load

instruction

• DSP function

− Multiply/Add (32-bit x 32-bit + 64-bit) in one clock cycle.

1.1.2 Functions for embedded applications

• Small code size

− Branch Likely instruction:The branch delay slot accepts an instruction to be executed at the

branch target

− Hardware Interlock: Stall the pipeline at the load delay slot when the instruction in the slot

depends on the data to be loaded

3

• Real-time performance

− Cache Lock Function: Lock one set of the two-way set associative cache memory to keep data in

cache memory

• Debug support

− Breakpoint

− Single step execution

• Real-time debug system interface

1.1.3 Low power consumption

• Power Down mode

Architecture

− Prepare for Reduced Frequency mode: Control the clock frequency of the R3900 Processor Core

with a clock generator

− Halt and Doze mode: Stop R3900 Processor Core operations

• Clock can be stopped

− Clock signal can be stopped at high state

1.1.4 Development environment for embedded arrays and cell-based ICs

• Compact core

• Easy-to-design peripheral circuits

− Single direction separate bus: Bus configuration suitable for core

− Built-in cache memory: No need to consider cache operation timing

• ASIC Process

• Sufficient Development Environment

4

1.2 Notation Used in This Manual

Mathematical notation

• Hexadecimal numbers are expressed as follows (example shown for decimal number 42)

0x2A

• A K(kilo)byte is 210 = 1,024 bytes, a M(mega)byte is 220 = 1,024 x 1,024 = 1,048,576 bytes, and a

G(giga)byte is 230 = 1,024 x 1,024 x 1,024 = 1,073,741,824 bytes.

Data notation

• Byte: 8 bits

• Halfword: 2 contiguous bytes (16 bits)

Architecture

• Word: 4 contiguous bytes (32 bits)

• Doubleword: 8 contiguous bytes (64 bits)

Signal notation

• Low active signals are indicated by an asterisk (*) at the end of the signal name (e.g.: RESET*).

• Changing a signal to active level is to “assert” a signal, while changing it to a non-active level is to “de-

assert” the signal.

5

2.

Architecture

6

Chapter 2 Architecture

CPU core

R3900 Processor Core

2.1 Overview

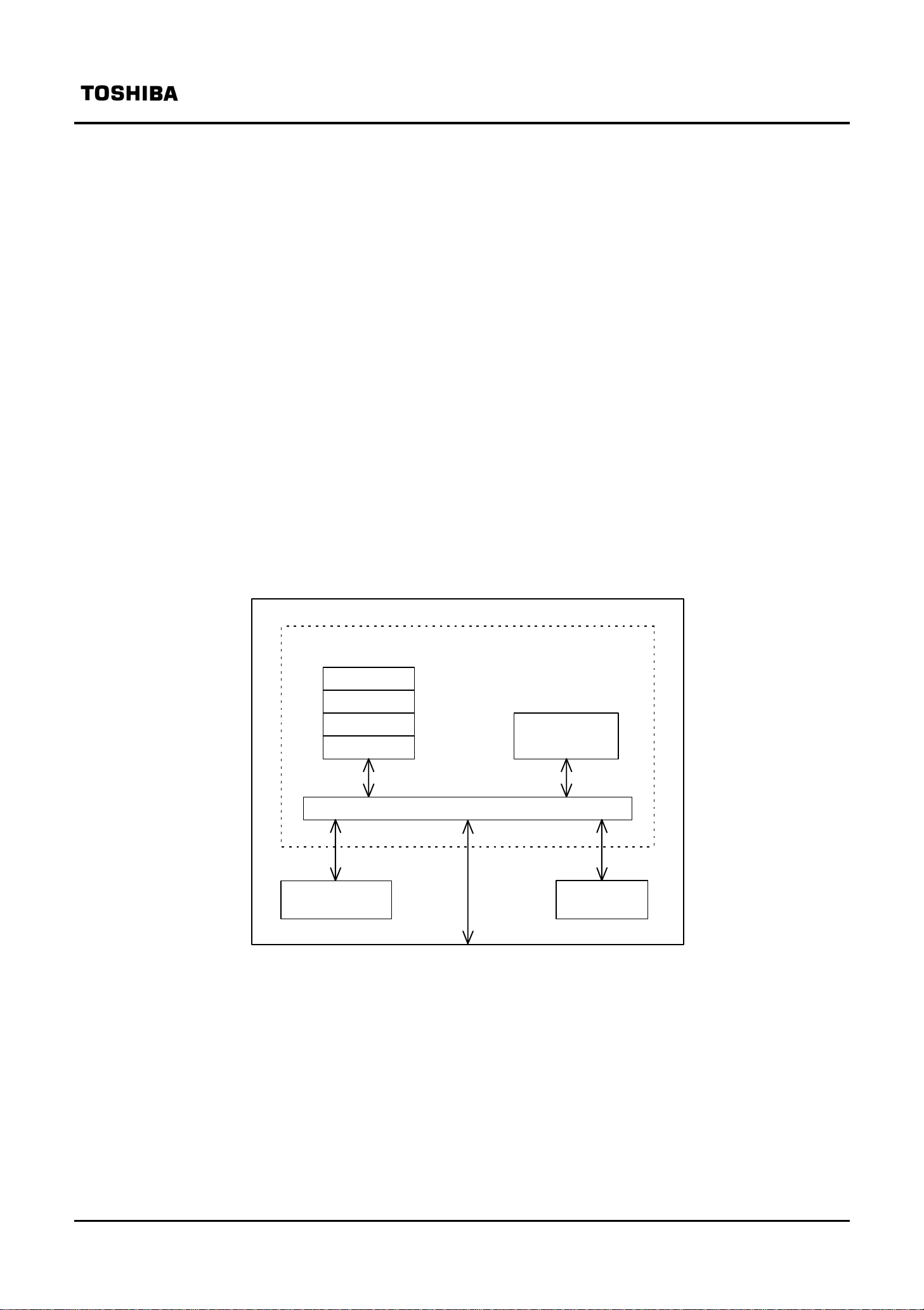

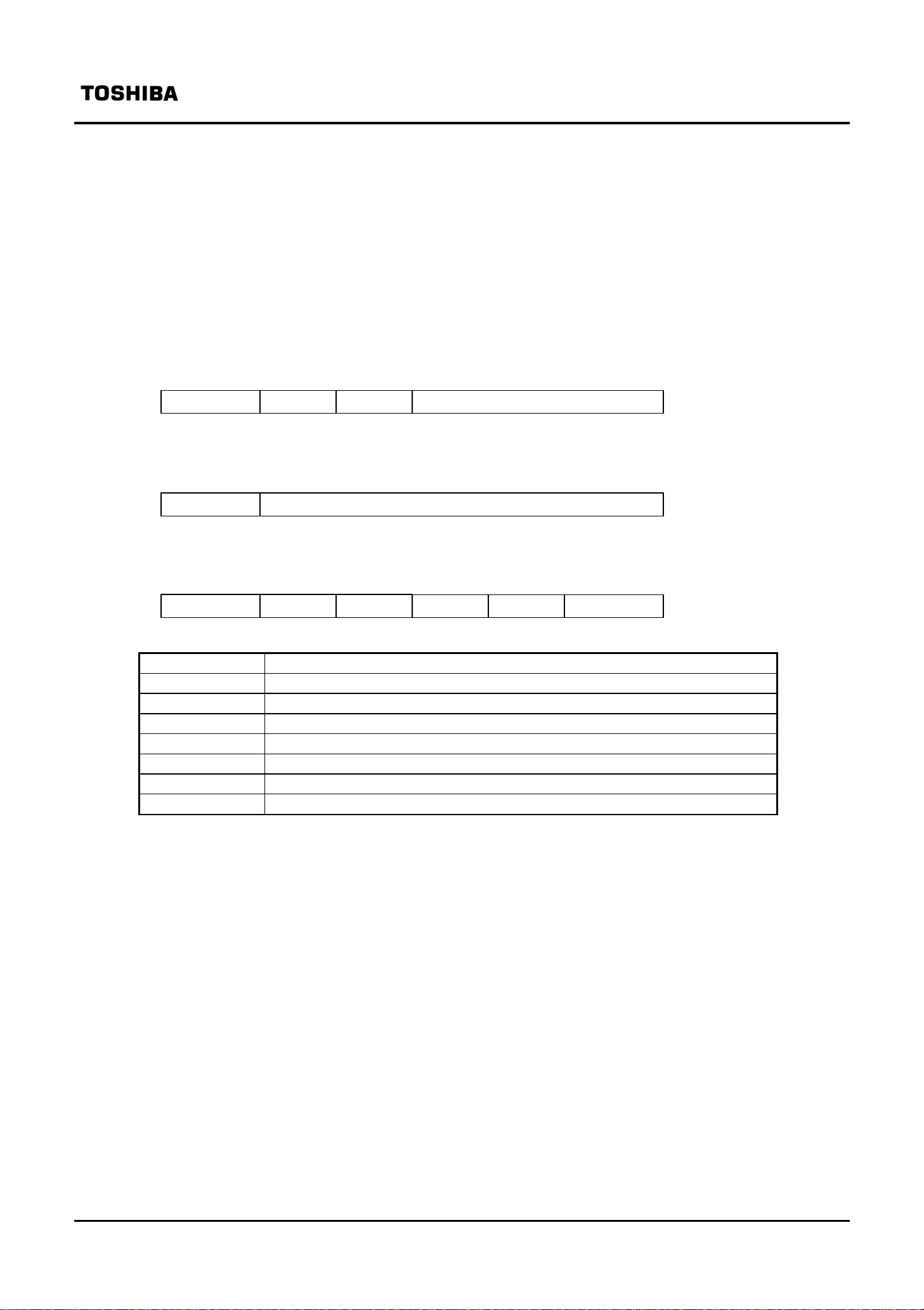

A block diagram of the R3900 Processor Core is shown in Figure 2-1. It includes the CPU core, an

instruction cache and a data cache. You can select an optimum data and instruction cache configuration for

your system from among a variety of possible configurations.

The CPU Core comprises the following blocks:

• CPU registers : General-purpose register, HI/LO register and program counter (PC).

• CP0 registers : Registers for system control coprocessor (CP0) functions.

Architecture

• ALU/Shifter : Computational unit.

• MAC : Computational unit for multiply/add.

• Bus interface unit : Control bus interface between CPU core and external circuit.

• Memory management unit : Direct segment mapping memory management unit.

CPU Register

CP0 Register

ALU/Shifter

MAC

Bus Interface Unit

Memory

Management Unit

Data CacheInstruction Cache

Figure 2-1. Block Diagram of the R3900 Processor Core

7

2.2 Registers

31 0

31 0

31 0

31 0

2.2.1 CPU registers

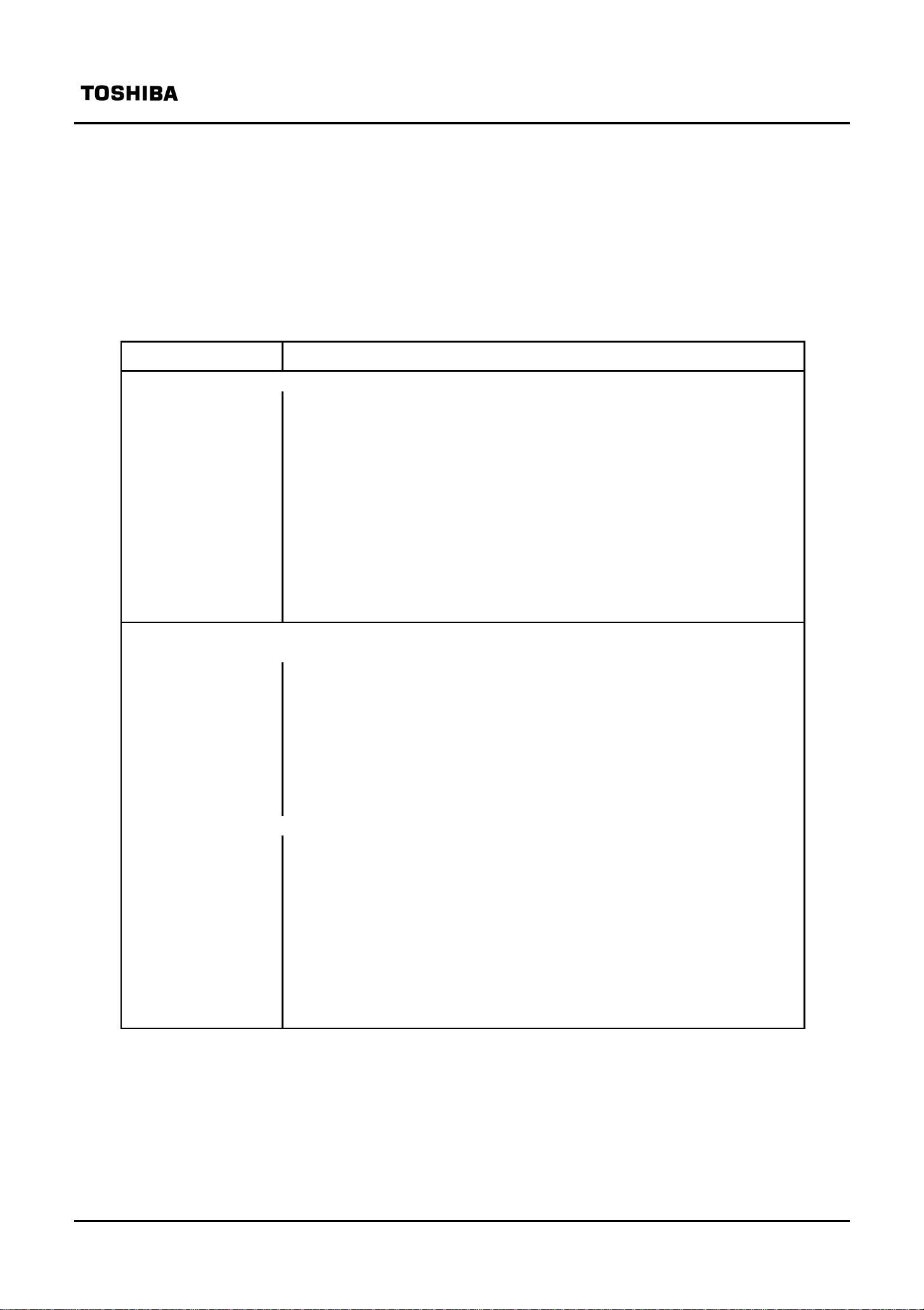

The R3900 Processor Core has the following 32-bit registers.

• Thirty-two general-purpose registers

• A program counter (PC)

• HI/LO registers for storing the result of multiply and divide operations

The configuration of the registers is shown in Figure 2-2.

Architecture

General-purpose registers

r0

r1

r2

.

.

.

.

r29

r30

r31

Multiply/Divide registers

HI

LO

Program counter

PC

Figure 2-2. R3900 Processor Core registers

The r0 and r31 registers have special functions.

• Register r0 always contains the value 0. It can be a target register of an instruction whose

operation result is not needed. Or, it can be a source register of an instruction that requires a value

of 0.

• Register r31 is the link register for the Jump And Link instruction. The address of the instruction

after the delay slot is placed in r31.

The R3900 Processor Core has the following three special registers that are used or modified

implicitly by certain instructions.

PC : Program counter

HI : High word of the multiply/divide registers

LO : Low word of the multiply/divide registers

The multiply/divide registers (HI, LO) store the double-word (64-bit) result of integer multiply

operations. In the case of integer divide operations, the quotient is stored in LO and the remainder in

HI.

8

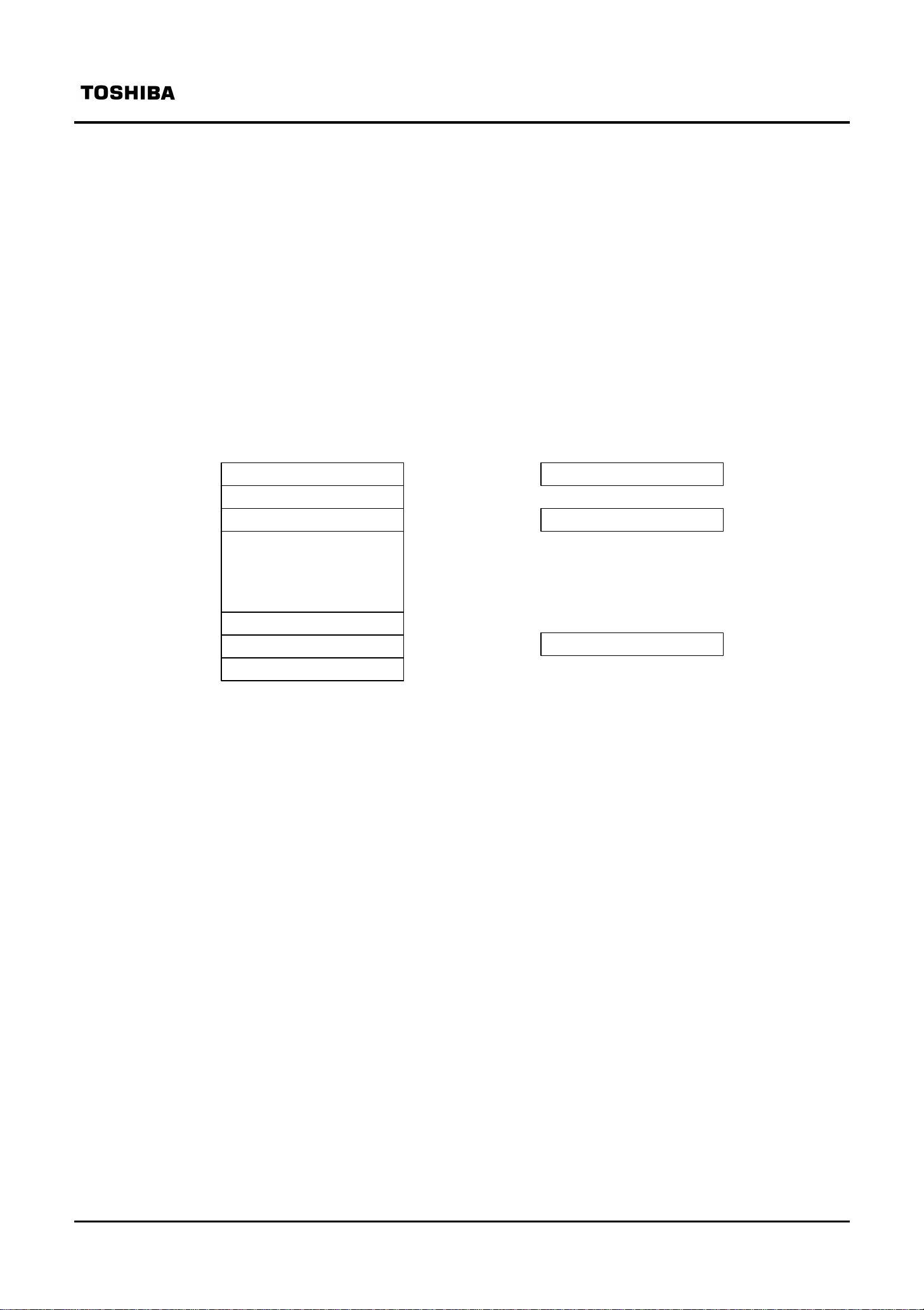

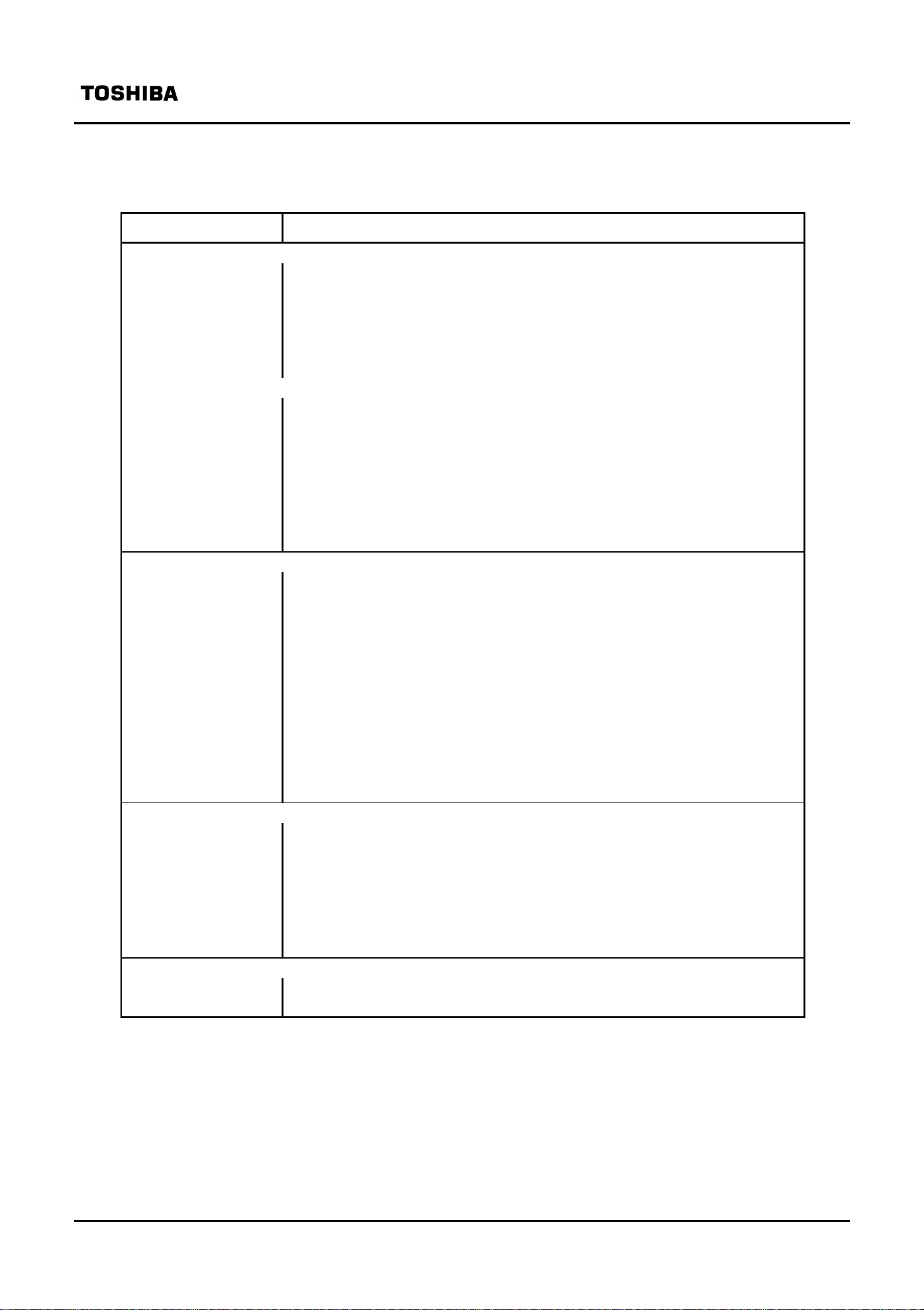

2.2.2 System control coprocessor (CP0) registers

The R3900 Processor Core can be connected to as many as three coprocessors, referred to as CP1,

CP2 and CP3. The R3900 also has built-in system control coprocessor (CP0) functions for exception

handling and for configuring the system. Figure 2-3 shows the functional breakdown of the CP0

registers.

<Exception Processing>

Architecture

Status register

EPC register

BadVAddr register

Config register

Cache register

<Debugging>

Debug register

†

†

†

Cause register

PRld register

DEPC register

†

Figure 2-3 CP0 registers

†

Additional R3900 Processor Core

registers not present in the

R3000A

9

Architecture

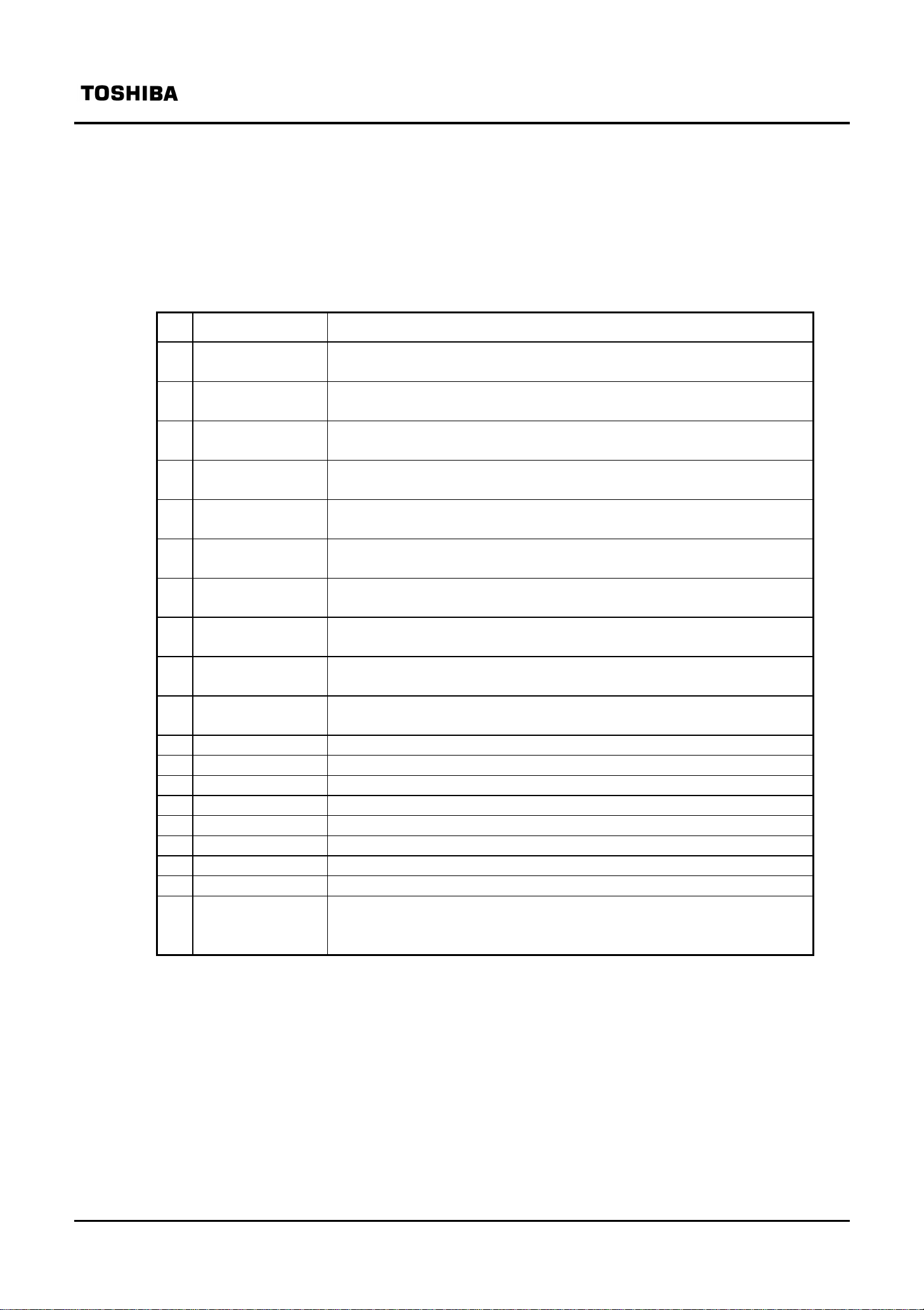

Table 2-1 lists the CP0 registers built into the R3900 Processor Core. Some of these registers are reserved

for use by an external memory management unit.

Table 2-1. List of system control coprocessor (CP0) registers

No Mnemonic Description

0

1

2

3Config

- (reserved)

- (reserved)

- (reserved)

††

Hardware configuration

†

†

†

- (reserved)

†

4

- (reserved)

†

5

- (reserved)

†

6

7Cache

††

Cache lock function

8BadVAddr Last virtual address triggering error

- (reserved)

†

9

10 - (reserved)

11 - (reserved)

†

†

12 Status Information on mode, interrupt enabled, diagnostic status

13 Cause Indicates nature of last exception

14 EPC Exception program counter

15 PRId Processor revision ID

16 Debug

17 DEPC

18

†††

†††

Debug exception control

Program counter for debug exception

- (reserved)

†

|

31

†

Reserved for external memory management unit, when direct segment mapping

MMU is not used.

††

Additional R3900 Processor Core register not present in R3000A.

†††

Additional R3900 Processor Core Debug register not present in R3000A.

10

2.3 Instruction Set Overview

31 26 25 21 20 16 15 0

31 26 25 0

31 26 25 21 20 16 15 11 10 6 5 0

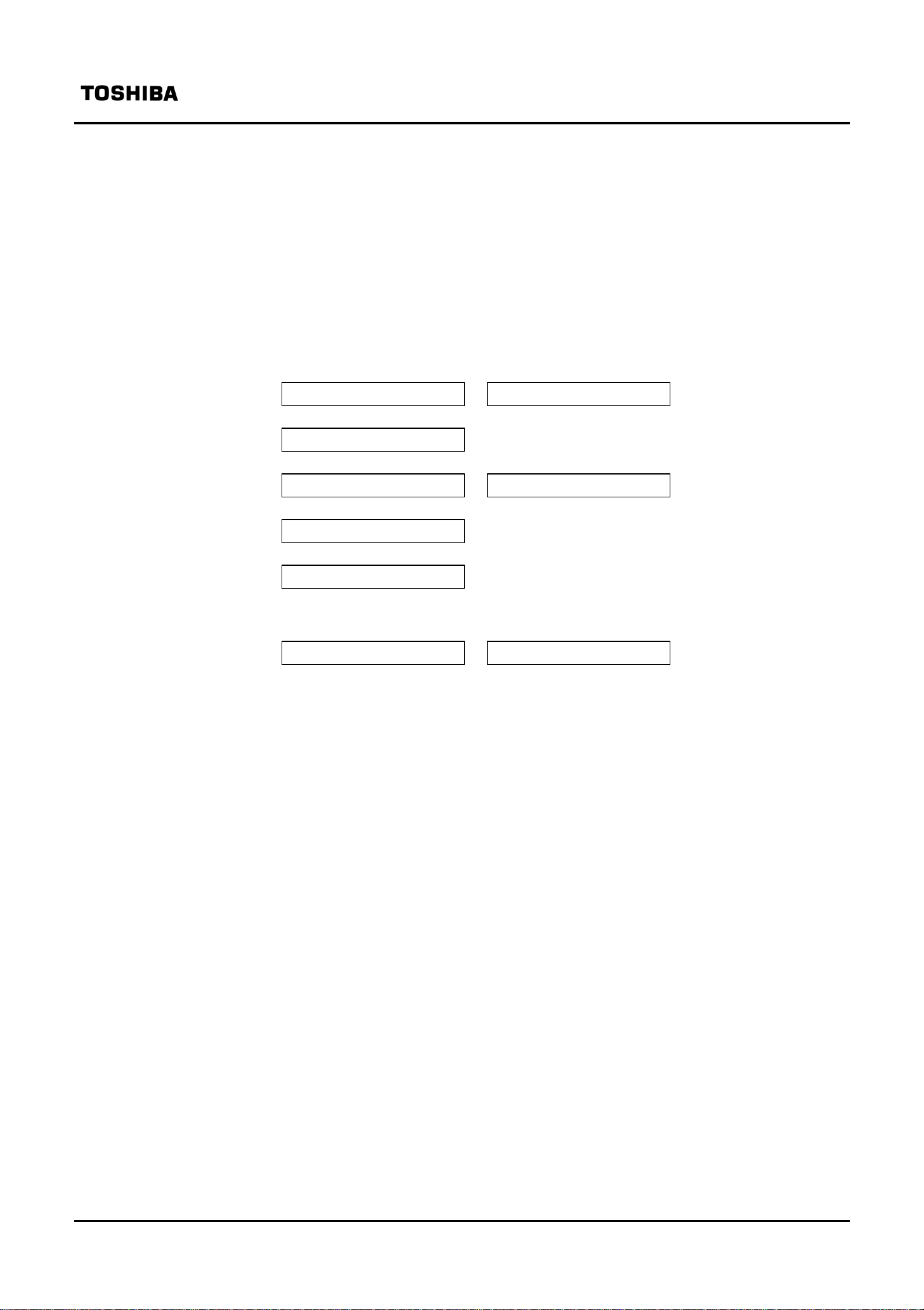

All R3900 Processor Core instructions are 32 bits in length. There are three instruction formats: immediate

(I-type), jump (J-type) and register (R-type), as shown in Figure 2-4. Having just three instruction formats

simplifies instruction decoding. If more complex functions or addressing modes are required, they can be

produced with the compiler using combinations of the instructions.

I-type (Immediate)

J-type (Jump)

Architecture

immediatertrsop

targetop

R-type (Register)

functrd sartrsop

op Operation code (6 bits)

rs Source register (5 bits)

rt Target (source or destination) register, or branch condition (5 bits)

rd Destination register (5 bits)

immediate Immediate, branch displacement, address displacement (16 bits)

target Branch target address (26 bits)

sa Shift amount (5 bits)

funct Function (6 bits)

Figure 2-4. Instruction formats and subfield mnemonics

11

The instruction set is classified as follows.

(1) Load/store

These instructions transfer data between memory and general registers. All instructions in this group

are I-type. “Base register + 16 bit signed immediate offset” is the only supported addressing mode.

(2) Computational

These instructions perform arithmetic, logical and shift operations on register values. The format can

be R-type (when both operands and the result are register values) or I-type (when one operand is 16bit immediate data).

(3) Jump/branch

These instructions change the program flow. A jump is always made to a 32 bit address contained in

Architecture

a register (R-type format ), or to a paged absolute address constructed by combining a 26-bit target

address with the upper 4 bits of the program counter (J-type format). In a branch instruction, the

target address is made up of the program counter value plus a 16 bit offset.

(4) Coprocessor

These instructions execute coprocessor operations. Each coprocessor has its own format for

computational instructions.

Note : Coprocessor load instruction LWCz and coprocessor store instruction SWCz are not

supported by the R3900 Processor Core. An attempt to execute either of these instructions

will trigger a Reserved Instruction exception.

(5) Coprocessor 0

These instructions are used for operations with system control coprocessor (CP0) registers, processor

memory management and exception handling.

Note : TLB (Translation Lookaside Buffer) instructions (TLBR, TLBWJ, TLBWR and TLBP) are

(6) Special

These instructions support system calls and breakpoint functions. The format is always R-type.

not supported by the R3900 Processor Core. These instructions will be treated by the R3900

as NOP(no operation).

12

Architecture

The instruction set supported by all MIPS R-Series processors is listed in Table 2-2. Table 2-3 shows

extended instructions supported by the R3900 Processor Core, and Table 2-4 lists coprocessor 0 (CP0)

instructions.

Table 2-5 shows R3000A instructions not supported by the R3900 Processor Core.

Table 2-2. Instructions supported by MIPS R-Series processors (ISA)

Instruction Description

Load/Store Instructions

LB Load Byte

LBU Load Byte Unsigned

LH Load Halfword

LHU Load Halfword Unsigned

LW Load Word

LWL Load Word Left

LWR Load Word Right

SB Store Byte

SH Store Halfword

SW Store Word

SWL Store Word Left

SWR Store Word Right

Computational Instructions

(ALU Immediate)

ADDI Add Immediate

ADDIU Add Immediate Unsigned

SLTI Set on Less Than Immediate

SLTIU Set on Less Than Immediate Unsigned

ANDI AND Immediate

ORI OR Immediate

XORI XOR Immediate

LUI Load Upper Immediate

(ALU 3-operand, register type)

ADD Add

ADDU Add Unsigned

SUB Subtract

SUBU Subtract Unsigned

SLT Set on Less Than

SLTU Set on Less Than Unsigned

AND AND

OR OR

XOR XOR

NOR NOR

13

Table 2-2(cont.). Instructions supported by MIPS R-Series processors (ISA)

Instruction Description

(Shift)

SLL Shift Left Logical

SRL Shift Right Logical

SRA Shift Right Arithmetic

SLLV Shift Left Logical Variable

SRLV Shift Right Logical Variable

SRAV Shift Right Arithmetic Variable

(Multiply/Divide)

MULT Multiply

MULTU Multiply Unsigned

DIV Divide

DIVU Divide Unsigned

MFHI Move from HI

MTHI Move to HI

MFLO Move from LO

MTLO Move to LO

Jump/Branch Instructions

J Jump

JAL Jump And Link

JR Jump Register

JALR Jump And Link Register

BEQ Branch on Equal

BNE Branch on Not Equal

BLEZ Branch on Less than or Equal to Zero

BGTZ Branch on Greater Than Zero

BLTZ Branch on Less Than Zero

BGEZ Branch on Greater than or Equal to Zero

BLTZAL Branch on Less Than Zero And Link

BGEZAL Branch on Greater than or Equal to Zero And Link

Coprocessor Instructions

MTCz Move to Coprocessor z

MFCz Move from Coprocessor z

CTCz Move Control Word to Coprocessor z

CFCz Move control Word from Coprocessor z

COPz Coprocessor Operation z

BCzT Branch on Coprocessor z True

BCzF Branch on Coprocessor z False

Special Instructions

SYSCALL System Call

BREAK Breakpoint

Architecture

14

Table 2-3. R3900 extended instructions

Instruction Description

Load/Store Instruction

SYNC Sync

Computational Instructions

MULT Multiply (3-operand instruction)

MULTU Multiply Unsigned (3-operand instruction)

MADD Multiply/ADD

MADDU Multiply/ADD Unsigned

Jump/Branch Instructions

BEQL Branch on Equal Likely

BNEL Branch on Not Equal Likely

BLEZL Branch on Less than or Equal to Zero Likely

BGTZL Branch on Greater Than Zero Likely

BLTZL Branch on Less Than Zero Likely

BGEZL Branch on Greater than or Equal to Zero Likely

BLTZALL Branch on Less Than Zero And Link Likely

BGEZALL Branch on Greater than or Equal to Zero And Link Likely

Coprocessor Instructions

BCzTL Branch on Coprocessor z True Likely

BCzFL Branch on Coprocessor z False Likely

Special Instruction

SDBBP Software Debug Breakpoint

Architecture

Table 2-4. CP0 instructions

Instruction Description

CP0 Instructions

MTC0 Move to CP0

MFC0 Move from CP0

RFE Restore from Exception

DERET Debug Exception Return

CACHE Cache Operation

Table 2-5. R3000A instructions not supported by the R3900

Instruction Description Operation

Coprocessor Instructions

LWCz Load Word from Coprocessor Reserved Instruction Exception

SWCz Store Word to Coprocessor Reserved Instruction Exception

CP0 Instructions

TLBR Read indexed TLB entry no operation(nop)

TLBWJ Write indexed TLB entry no operation(nop)

TLBWR Write Random TLB entry no operation(nop)

TLBP Probe TLB for matching entry no operation(nop)

15

2.4 Data Formats and Addressing

This section explains how data is organized in R3900 registers and memory.

The R3900 uses the following data formats: 64-bit doubleword, 32-bit word, 16-bit halfword and 8-bit byte.

The byte order can be set to either big endian or little endian.

Figure 2-5 shows how bytes are ordered in words, and how words are ordered in multiple words, for both the

big-endian and little-endian formats.

Architecture

Higher address

Lower address

Higher address

Lower address

31

24

8 9 10 11 8

4 5 6 7 4

0 1 2 3 0

23 16 15 8 7

0

Byte 0 is the most significant byte (bit 31-24).

A word is addressed beginning with the most significant byte.

(a) Big endian

31

24

11 10 9 8 8

7 6 5 4 4

3 2 1 0 0

23

16

Byte 0 is the least significant byte (bit 7-0).

15

8

7

0

Word address

Word address

A word is addressed beginning with the least significant byte.

(b) Little endian

Figure 2-5. Big endian and little endian formats

16

Architecture

17

Architecture

In this document (bit 0 is always the rightmost bit).

Byte addressing is used with the R3900 Processor Core, but there are alignment restrictions for halfword and

word access. Halfword access is aligned on an even byte boundary (0, 2, 4...) and word access on a byte

boundary divisible by 4 (0, 4, 8...) .

The address of multiple-byte data, as shown in Figure 2-5 above, begins at the most significant byte for the

big endian format and at the least significant byte for the little endian format.

There are special instructions (LWL, LWR, SWL, SWR) for accessing words not aligned on a word

boundary. They are used in pairs for addressing misaligned words, but involve an extra instruction cycle

which is wasted if used with properly aligned words. Figure 2-6 shows the byte arrangement when a

misaligned word is addressed at byte address 3 for the big and little endian formats.

Higher address

Lower address

Higher address

Lower address

31 24 23 16 15 8 7 0

4 5 6

3

(a) Big endian

31 24 23 16 15 8 7 0

6 5 4

3

(b)Little endian

Figure 2-6. Byte addresses of a misaligned word

18

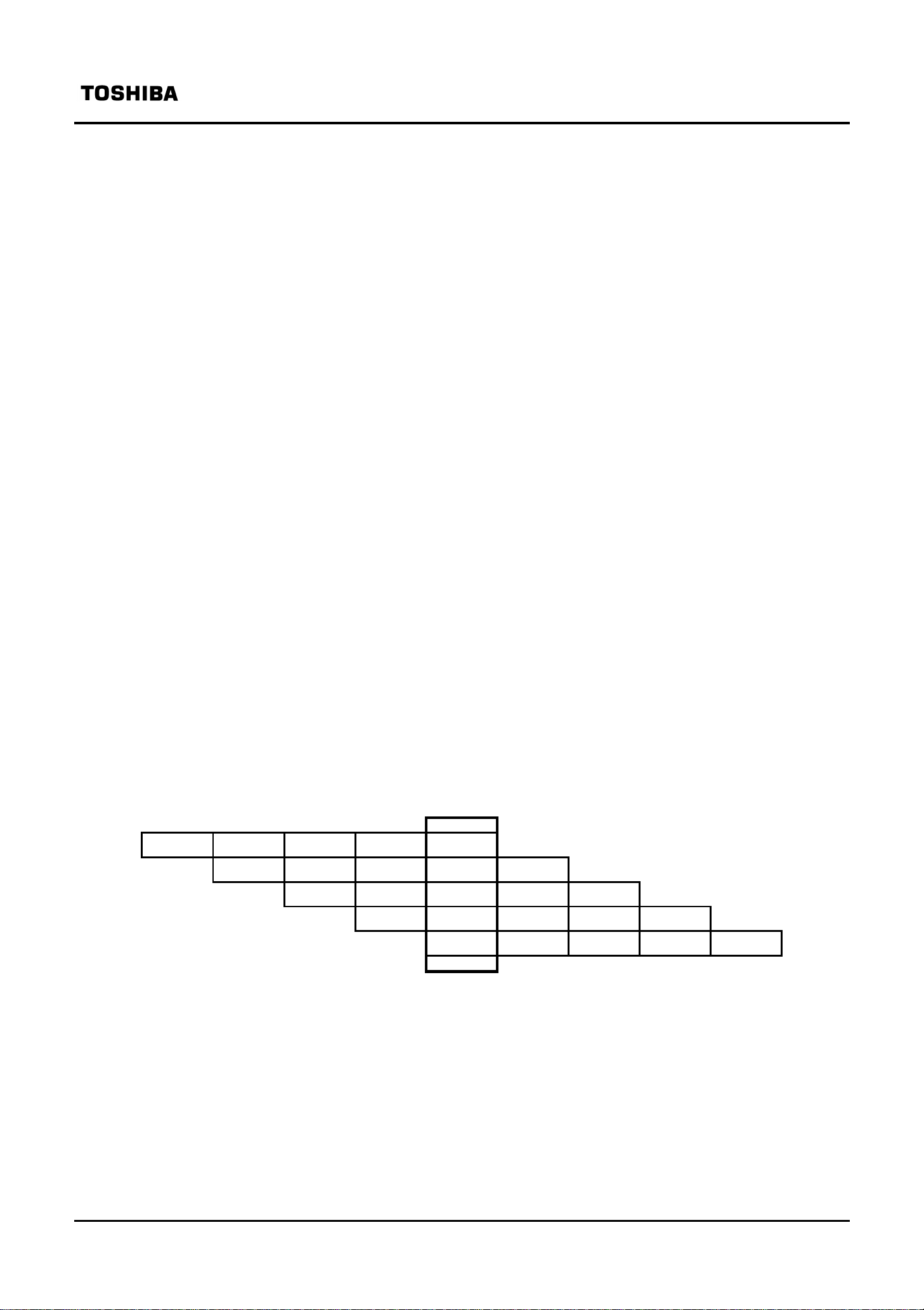

2.5 Pipeline Processing Overview

The R3900 Processor Core executes instructions in five pipeline stages (F: instruction fetch; D: decode; E:

execute; M: memory access; W: register write-back). Each pipeline stage is executed in one clock cycle.

When the pipeline is fully utilized, five instructions are executed at the same time resulting in an instruction

execution rate of one instruction per cycle.

With the R3900 Processor Core an instruction that immediately follows a load instruction can use the result of

that load instruction. Execution of the following instruction is delayed by hardware interlock until the result of

the load instruction becomes available. The instruction position immediately following the load instruction is

called the “load delay slot.”

Architecture

In the case of branch instructions, a one-cycle delay is required to generate the branch target address. This

delayed cycle is referred to as the “branch delay slot.” An instruction placed immediately after a branch

instruction (in the branch delay slot) can be executed prior to the branch while the branch target address is

being generated.

The R3900 Processor Core provides a Branch Likely instruction whereby an instruction to be executed at the

branch target can be placed in the delay slot of the Branch Likely instruction and executed only if the

conditions of the branch instruction are met. If the conditions are not met, and the branch is not taken, the

instruction in the delay slot is treated as a NOP. This makes it possible to place an instruction that would

normally be executed at the branch target into the delay slot for quick execution (if the conditions of the

branch are met).

F D E M W

F D E M W

F D E M W

F D E M W

F D E M W

Current CPU

cycle

Figure 2-7. Pipeline stages for execution of R3900 Processor Core instructions

19

2.6 Memory Management Unit (MMU)

2.6.1 R3900 Processor Core operating modes

The R3900 Processor Core has two operating modes, user mode and kernel mode. Normally the

processor operates in user mode. It switches to kernel mode if an exception is detected. Once in

kernel mode, it remains there until an RFE (Restore From Exception) instruction is executed.

(1) User mode

User mode makes available one of the two 2 Gbyte virtual address spaces (kuseg). In this

mode the most significant bit of each kuseg address in the memory map is 0. Attempting to

access an address whose MSB is 1 while in user mode returns an Address Error exception.

Architecture

(2) Kernel mode

Kernel mode makes available a second 2 Gbyte virtual address space (kseg), in addition to the

kuseg accessible in user mode. The MSB of each kseg address in the memory map is 1.

20

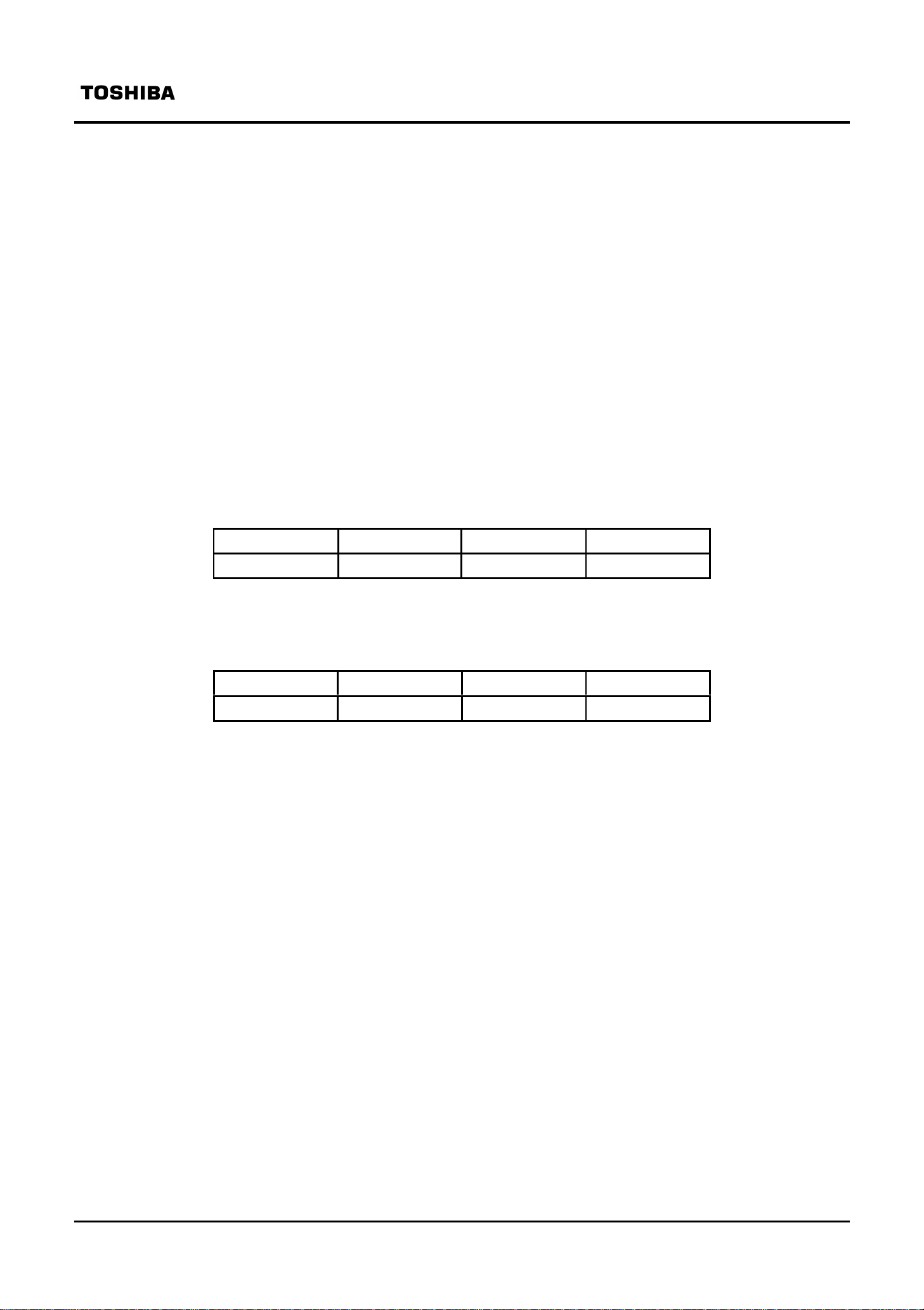

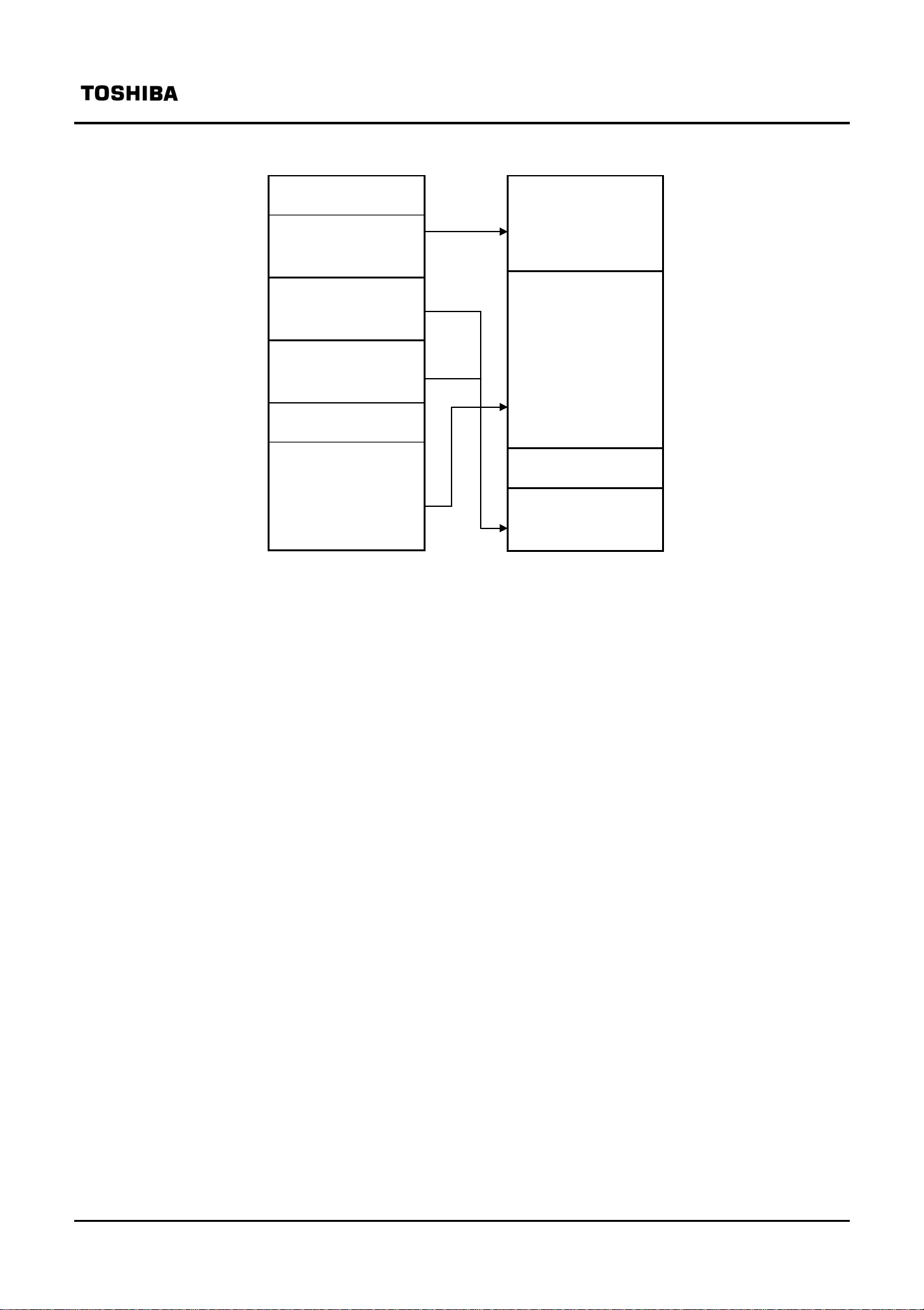

2.6.2 Direct segment mapping

The R3900 Processor Core includes a direct segment mapping MMU. The following virtual address

spaces are available depending on the processor mode (Figure 2-8 shows the address mapping).

(1) User mode

One 2 Gbyte virtual address space (kuseg) is available. Virtual addresses from 0x0000 0000

to 0x7FFF FFFF are translated to physical addresses 0x4000 0000 to 0xBFFF FFFF,

respectively.

(2) Kernel mode

The kernel mode address space is treated as four virtual address segments. One of these is

Architecture

the same as the kuseg space in user mode; the remaining three are the kernel segments kseg0,

kseg1 and kseg2.

(a) kuseg

This is the same as the virtual address space available in user mode. Address

translation is also the same as in user mode. The upper 16 Mbytes of kuseg is

reserved for on-chip resources and is not cacheable.

(b) kseg0

This is a 512 Mbyte segment spanning virtual addresses 0x8000 0000 to 0x9FFF

FFFF. Fixed mapping of this segment is made to physical addresses 0x0000 0000 to

0x1FFF FFFF, respectively. This area is cacheable.

(c) kseg1

This is a 512 Mbyte segment from virtual address 0xA000 0000 to 0xBFFF FFFF.

Fixed mapping of this segment is made to physical address 0x0000 0000 to 0x1FFF

FFFF, respectively. Unlike kseg0, this area is not cacheable.

(d) kseg2

This is a 1 Gbyte linear address space from virtual addresses 0xC000 0000 to 0xFFFF

FFFF. The upper 16 Mbytes of kseg2 are reserved for on-chip resources and are not

cacheable. Of this reserved area, 0xFF20 0000 to 0xFF3F FFFF is a 2 Mbyte

reserved area intended for use as a debugging monitor area and for testing.

21

0xFFFF FFFF

16MB Kernel Reserved

0xC000 0000

Kernel Cached

0xA000 0000

Kernel Uncached

0x8000 0000

Kernel Cached

0x0000 0000

Kernel/User Cached

(kuseg)

1024MB

Kernel/User

2048MB

512MB

Kernel Boot and I/O

512MB

(kseg2)

(kseg1)

Architecture

Physical address spaceVirtual address space

Kernel Cached Tasks

(kseg0)

16MB User Reserved

Figure 2-8. Address mapping

Cached Tasks

Inaccessible

Cached/uncached

22

Loading...

Loading...