32-Bit TX System RISC

TX19 Family

TMP1940CYAF/TMP1940FDBF

MIPS16, application Specific Extensions and R3000A are a trademark of MIPS

Technologies, Inc.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our

products. No responsibility is assumed by TOSHIBA for any infringements of patents or

other rights of the third parties which may result from its use. No license is granted by

implication or otherwise under any patent or patent rights of TOSHIBA or others.

The products described in this document contain components made in the United States

and subject to export control of the U.S. authorities. Diversion contrary to the U.S. law

is prohibited.

TOSHIBA is continually working to improve the quality and reliability of its products.

Nevertheless, semiconductor devices in general can malfunction or fail due to their

inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with

the standards of safety in making a safe design for the entire system, and to avoid

situations in which a malfunction or failure of such TOSHIBA products could cause loss

of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within

specified operating ranges as set forth in the most recent TOSHIBA products

specifications.

Also, please keep in mind the precautions and conditions set forth in the “Handling

Guide for Semiconductor Devices,” or “TOSHIBA Semiconductor Reliability

Handbook” etc..

The Toshiba products listed in this document are intended for usage in general

electronics applications ( computer, personal equipment, office equipment, measuring

equipment, industrial robotics, domestic appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that

requires extraordinarily high quality and/or reliability or a malfunction or failure of

which may cause loss of human life or bodily injury (“Unintended Usage”). Unintended

Usage include atomic energy control instruments, airplane or spaceship instruments,

transportation instruments, traffic signal instruments, combustion control instruments,

medical instruments, all types of safety devices, etc.. Unintended Usage of Toshiba

products listed in this document shall be made at the customer’s own risk.

The products described in this document may include products subject to the foreign

exchange and foreign trade laws.

© 2002 TOSHIBA CORPORATION

All Rights Reserved

Preface

Toshiba offers a broad range of microcontrollers targeted for both commercial and industrial

applications. The TX System RISC TX19 Family manual contains the detailed specifications of the

TX1940, including the architecture, programming, capabilities, operation, electrical characteristics,

packaging and so forth.

The TX1940 is a high-performance RISC processor based on the R3000A architecture and the MIPS16

Application Specific Extension pioneered by MIPS Technologies, Inc.

Recently, with the ever-growing market for lightweight portable devices, manufacturers of electronic

systems have been seeking cost-effective, single-chip solutions to processor-based applications.

Toshiba has designed the TX1940 to help customers achieve the best cost performance for their

products.

TMP1940

Contents

Handling Precaution

Part 1 TMP1940

TMP1940CYAF

1. Features...................................................................................................................................................................1

2. Signal Descriptions .................................................................................................................................................5

2.1 Pin Assignment..................................................................................................................................................5

2.2 Pin Usage Information.......................................................................................................................................6

3. Core Processor ........................................................................................................................................................9

3.1 Reset Operation.................................................................................................................................................9

4. Memory Map.........................................................................................................................................................10

5. Clock/Standby Control..........................................................................................................................................11

5.1 Clock Generation............................................................................................................ .................................12

5.1.1 Main System Clock.................................................................................................................................12

5.1.2 Subsystem Clock.....................................................................................................................................12

5.1.3 Clock Source Block Diagrams................................................................................................................13

5.2 Clock Generator (CG) Registers......................................................................................................................14

5.2.1 System Clock Control Registers..............................................................................................................14

5.2.2 ADC Conversion Clock ..........................................................................................................................16

5.2.3 STOP/SLEEP Wake-up Interrupt Control Registers (INTCG Registers) ...............................................16

5.2.4 Interrupt Request Clear Register.............................................................................................................18

5.3 System Clock Control Section.........................................................................................................................19

5.3.1 Oscillation Stabilization Time When Switching Between NORMAL and SLOW Modes......................19

5.3.2 System Clock Output..............................................................................................................................20

5.3.3 Reducing the Oscillator Clock Drive Capability.....................................................................................20

5.4 Prescalar Clock Control Section......................................................................................................................21

5.5 Clock Frequency Multiplication Section (PLL)...............................................................................................21

5.6 Standby Control Section..................................................................................................................................22

5.6.1 TMP1940CYAF Operation in NORMAL and Standby Modes...............................................................23

5.6.2 CG Operation in NORMAL and Standby Modes...................................................................................23

5.6.3 Processor and Peripheral Block Operation in Standby Modes................................................................23

5.6.4 Wake-up Signaling..................................................................................................................................24

5.6.5 STOP Mode............................................................................................................................................26

5.6.6 Returning from a Standby Mode.............................................................................................................26

6. Interrupts...............................................................................................................................................................29

6.1 Overview.........................................................................................................................................................29

6.2 Interrupt Sources..............................................................................................................................................31

6.3 Interrupt Detection...........................................................................................................................................33

6.4 Resolving Interrupt Priority.............................................................................................................................33

6.5 Register Description........................................................................................................................................34

6.1.1 Interrupt Vector Register (IVR)..............................................................................................................34

6.1.2 Interrupt Mode Control Registers (IMCF–IMC0) ..................................................................................35

6.1.3 Interrupt Request Clear Register (INTCLR)...........................................................................................35

7. I/O Ports................................................................................................................................................................36

7.1 Port 0 (P00–P07).............................................................................................................................................40

7.2 Port 1 (P10–P17).............................................................................................................................................42

7.3 Port 2 (P20–P27).............................................................................................................................................44

7.4 Port 3 (P30–P37).............................................................................................................................................46

7.5 Port 4 (P40–P44).............................................................................................................................................50

i

TMP1940

7.6 Port 5 (P50–P57).............................................................................................................................................53

7.7 Port 7 (P70–P77).............................................................................................................................................54

7.8 Port 8 (P80–P87).............................................................................................................................................58

7.9 Port 9 (P90–P97).............................................................................................................................................61

7.10 Port A (PA0–PA7) ...........................................................................................................................................66

7.11 Open-Drain Output Control.............................................................................................................................71

8. External Bus Interface...........................................................................................................................................72

8.1 Address and Data Buses..................................................................................................................................73

8.1.1 Supported Configurations.......................................................................................................................73

8.1.2 States of the Address Bus During On-Chip Address Accesses...............................................................73

8.2 External Bus Operation....................................................................................................................................74

8.2.1 Basic Bus Operation ...............................................................................................................................74

8.2.2 Wait Timing ............................................................................................................................................75

8.2.3 ALE Pulse Width....................................................................................................................................77

8.2.4 Read Recovery Time...............................................................................................................................78

8.3 Bus Arbitration................................................................................................................................................79

8.3.1 Bus Access Control.................................................................................................................................79

8.3.2 Bus Arbitration Flow..............................................................................................................................79

8.3.3 Relinquishing the bus ..............................................................................................................................80

9. Chip Select/Wait Controller..................................................................................................................................81

9.1 Programming Chip Select Ranges...................................................................................................................81

9.1.1 Base/Mask Address Registers (BMA0–BMA3).....................................................................................81

9.1.2 Base Address and Address Mask Value Calculations .............................................................................84

9.2 Chip Select/Wait Control Registers .................................................................................................................87

9.3 Application Example.......................................................................................................................................89

10. DMA Controller (DMAC).....................................................................................................................................90

10.1 Features............................................................................................................................................................90

10.2 Implementation................................................................................................................................................91

10.2.1 On-Chip DMAC Interface.......................................................................................................................91

10.2.2 DMAC Block..........................................................................................................................................92

10.2.3 Bus Snooping..........................................................................................................................................92

10.3 Register Description........................................................................................................................................93

10.3.1 DMA Control Register (DCR)................................................................................................................94

10.3.2 Channel Control Registers (CCRn)......................................................................................... ................95

10.3.3 Channel Status Registers (CSRn)............................................................................................................97

10.3.4 Source Address Registers (SARn)..........................................................................................................98

10.3.5 Destination Address Registers (DARn) ..................................................................................................99

10.3.6 Byte Count Registers (BCRn)...............................................................................................................100

10.3.7 DMA Transfer Control Registers (DTCRn)..........................................................................................101

10.3.8 Data Holding Register (DHR)...............................................................................................................102

10.4 Operation.......................................................................................................................................................103

10.4.1 Overview...............................................................................................................................................103

10.4.2 Transfer Request Generation.................................................................................................................106

10.4.3 DMA Address Modes...........................................................................................................................107

10.4.4 DMA Channel Operation......................................................................................................................108

10.4.5 DMA Channel Priority..........................................................................................................................110

10.4.6 Interrupts............................................................................................................................................... 110

10.4.7 Data Packing and Unpacking................................................................................................................ 111

10.5 DMA Transfer Timing................................................................................................................................... 112

10.5.1 Dual-Address Mode ..............................................................................................................................112

10.6 Programming Example..................................................................................................................................114

11. 8-Bit Timers (TMRAs)........................................................................................................................................ 115

11.1 Block Diagrams.............................................................................................................................................116

11.2 Timer Components ........................................................................................................................................118

ii

TMP1940

11.2.1 Prescaler................................................................................................................................................ 118

11.2.2 Up-Counters (UC0 and UC1)............................................................................................................... 119

11.2.3 Timer Registers (TA0REG and TA1REG)............................................................................................119

11.2.4 Comparators (CP0 and CP1).................................................................................................................120

11.2.5 Timer Flip-Flop (TA1FF)......................................................................................................................120

11.3 Register Description......................................................................................................................................121

11.4 Operating Modes...........................................................................................................................................126

11.4.1 8-Bit Interval Timer Mode....................................................................................................................126

11.4.2 16-Bit Interval Timer Mode..................................................................................................................128

11.4.3 8-Bit Programmable Pulse Generation (PPG) Mode ............................................................................129

11.4.4 8-Bit PWM Generation Mode...............................................................................................................131

11.4.5 Operating Mode Summary....................................................................................................................134

12. 16-Bit Timer/Event Counters (TMRBs)..............................................................................................................135

12.1 Block Diagrams.............................................................................................................................................136

12.2 Timer Components ........................................................................................................................................140

12.2.1 Prescaler................................................................................................................................................140

12.2.2 Up-Counter (UC0)................................................................................................................................141

12.2.3 Timer Registers (TB0RG0H/L and TB0RG1H/L)................................................................................141

12.2.4 Capture Registers (TB0CP0H/L and TB0CP1H/L)..............................................................................142

12.2.5 Capture Control Logic..........................................................................................................................143

12.2.6 Comparators (CP0 and CP1).................................................................................................................144

12.2.7 Timer Flip-Flop (TB0FF0)....................................................................................................................144

12.3 Register Description......................................................................................................................................145

12.4 Operating Modes...........................................................................................................................................155

12.4.1 16-Bit Interval Timer Mode..................................................................................................................155

12.4.2 16-Bit Event Counter Mode..................................................................................................................155

12.4.3 16-Bit Programmable Pulse Generation (PPG) Mode ..........................................................................156

12.4.4 Timing and Measurement Functions Using the Capture Capability......................................................158

13. Serial I/O (SIO)...................................................................................................................................................163

13.1 Block Diagrams.............................................................................................................................................165

13.2 SIO Components............................................................................................................................................169

13.2.1 Prescaler................................................................................................................................................169

13.2.2 Baud Rate Generator.............................................................................................................................170

13.2.3 Serial Clock Generator..........................................................................................................................173

13.2.4 Receive Counter....................................................................................................................................173

13.2.5 Receive Controller................................................................................................................................173

13.2.6 Receive Buffer......................................................................................................................................173

13.2.7 Transmit Counter ..................................................................................................................................174

13.2.8 Transmit Controller ...............................................................................................................................174

13.2.9 Transmit Buffer.....................................................................................................................................176

13.2.10 Parity Controller ...................................................................................................................................176

13.2.11 Error Flags (UART mode only)............................................................................................................176

13.2.12 Signal Generation Timing.....................................................................................................................177

13.3 Register Description......................................................................................................................................178

13.4 Operating Modes...........................................................................................................................................192

13.4.1 Mode 0 (I/O Interface Mode)................................................................................................................192

13.4.2 Mode 1 (7-Bit UART Mode) ................................................................................................................195

13.4.3 Mode 2 (8-Bit UART Mode) ................................................................................................................196

13.4.4 Mode 3 (9-Bit UART Mode) ................................................................................................................196

14. Serial Bus Interface (SBI)...................................................................................................................................199

14.1 Block Diagram...............................................................................................................................................199

14.2 Registers........................................................................................................................................................200

14.3 I

14.4 Description of the Registers Used in I

14.5 I

2

C Bus Mode Data Formats..........................................................................................................................200

2

C Bus Mode Configuration........................................................................................................................205

2

C Bus Mode.....................................................................................201

iii

TMP1940

14.5.1 Acknowledgment Mode........................................................................................................................205

14.5.2 Number of Bits Per Transfer.................................................................................................................205

14.5.3 Serial Clock...........................................................................................................................................205

14.5.4 Slave Addressing and Address Recognition Mode...............................................................................206

14.5.5 Configuring the SBI as a Master or a Slave..........................................................................................206

14.5.6 Configuring the SBI as a Transmitter or a Receiver..............................................................................207

14.5.7 Generating START and STOP Conditions............................................................................................207

14.5.8 Asserting and Deasserting Interrupt Requests.......................................................................................208

14.5.9 SBI Operating Modes ...........................................................................................................................208

14.5.10 Lost-Arbitration Detection Monitor......................................................................................................208

14.5.11 Slave Address Match Monitor..............................................................................................................209

14.5.12 General-Call Detection Monitor ...........................................................................................................209

14.5.13 Last Received Bit Monitor....................................................................................................................209

14.5.14 Software Reset......................................................................................................................................210

14.5.15 Serial Bus Interface Data Buffer Register (SBI0DBR).........................................................................210

14.5.16 I

14.5.17 Baud Rate Register 1 (SBI0DBR1)......................................................................................................210

14.5.18 Baud Rate Register 0 (SBI0BR0).........................................................................................................210

14.6 Programming Sequences in I

14.6.1 SBI Initialization................................................................................................................................... 211

14.6.2 Generating a START Condition and a Slave Address...........................................................................211

14.6.3 Transferring a Data Word......................................................................................................................212

14.6.4 Generating a STOP Condition..............................................................................................................216

14.6.5 Repeated START Condition..................................................................................................................217

14.7 Description of Registers Used in Clock-Synchronous 8-Bit SIO Mode........................................................218

14.8 Clock-Synchronous 8-Bit SIO Mode Operation............................................................................................220

14.8.1 Serial Clock...........................................................................................................................................220

14.8.2 SIO Transfer Modes..............................................................................................................................222

2

C Bus Address Register (I2C0AR)....................................................................................................210

2

C Bus Mode...................................................................................................211

15. Analog-to-Digital Converter (ADC).................................................................................................................... 227

15.1 Register Description......................................................................................................................................228

15.2 Operation.......................................................................................................................................................233

15.2.1 Analog Reference Voltages...................................................................................................................233

15.2.2 Selecting an Analog Input Channel (s)..................................................................................................233

15.2.3 Starting an A/D Conversion..................................................................................................................233

15.2.4 Conversion Modes and Conversion-Done Interrupts............................................................................234

15.2.5 Conversion Time...................................................................................................................................235

15.2.6 Storing and Reading the A/D Conversion Result..................................................................................235

15.3 Programming Examples.................................................................................................................................237

16. Watchdog Timer (WDT) .....................................................................................................................................238

16.1 Implementation..............................................................................................................................................238

16.2 Register Description......................................................................................................................................240

16.2.1 Watchdog Timer Mode Register (WDMOD)........................................................................................240

16.2.2 Watchdog Timer Control Register (WDCR).........................................................................................240

16.3 Operation.......................................................................................................................................................242

17. Real-Time Clock (RTC)......................................................................................................................................243

17.1 Implemention.................................................................................................................................................243

18. Electrical Characteristics.....................................................................................................................................245

18.1 Maximum Ratings..........................................................................................................................................245

18.2 DC Electrical Characteristics (1/2)................................................................................................................246

18.3 DC Electrical Characteristics (2/2)................................................................................................................247

18.4 AC Electrical Characteristics.........................................................................................................................248

18.5 ADC Electrical Characteristics......................................................................................................................254

18.6 SIO Timing ....................................................................................................................................................255

18.6.1 I/O Interface Mode................................................................................................................................255

iv

TMP1940

18.7 SBI Timing ....................................................................................................................................................256

18.7.1 I

2

C Mode..............................................................................................................................................256

18.7.2 Clock-Synchronous 8-Bit SIO Mode....................................................................................................257

18.8 Event Counters (TA0IN, TA2IN, TB0IN0, TB0IN1, TB2IN0).....................................................................258

18.9 Timer Capture (TB0IN0, TB0IN1, TB1IN0, TB1IN1, TB2IN0, TB2IN1) ..................................................258

18.10 General Interrupts..........................................................................................................................................258

18.11

and STOP/SLEEP Wake-up Interrupts................................................................................................258

NMI

18.12 SCOUT Pin....................................................................................................................................................258

18.13 Bus Request and Bus Acknowledge Signals..................................................................................................259

19. I/O Register Summary.........................................................................................................................................260

19.1 I/O Ports ........................................................................................................................................................266

19.2 Interrupt Controller........................................................................................................................................269

19.3 Chip Select/Wait Controller...........................................................................................................................281

19.4 Clock Generator (CG) ...................................................................................................................................285

19.5 DMA Controller (DMAC).............................................................................................................................287

19.6 8-Bit Timers (TMRAs)..................................................................................................................................303

19.7 16-Bit Timer/Event Counters (TMRBs)........................................................................................................304

19.8 Serial I/O (SIO) .............................................................................................................................................306

19.9 Serial Bus Interface (SBI)..............................................................................................................................309

19.10 A/D Converter (ADC)...................................................................................................................................310

19.11 Watchdog Timer (WDT)................................................................................................................................ 311

19.12 Real-Time Clock (RTC).................................................................................................................................311

19.13 Flash Control/Status (TMP1940FDBF Only)................................................................................................311

20. I/O Port Equivalent-Circuit Diagrams.................................................................................................................312

21. Notations, Precautions and Restrictions..............................................................................................................315

21.1 Notations and Terms......................................................................................................................................315

21.2 Precautions and Restrictions..........................................................................................................................315

v

TMP1940

TMP1940FDBF

1. Features...................................................................................................................................................................1

2. Signal Descriptions .................................................................................................................................................5

2.1 Pin Assignment..................................................................................................................................................5

2.2 Pin Usage Information.......................................................................................................................................6

3. Flash Memory.......................................................................................................................................................10

3.1 Features............................................................................................................................................................10

3.2 Block Diagram.................................................................................................................................................11

3.3 Operating Modes.............................................................................................................................................12

3.3.1 Overview.................................................................................................................................................12

3.3.2 Reset Operation.......................................................................................................................................13

3.3.3 Memory Maps.........................................................................................................................................13

3.3.4 Interleave Mode......................................................................................................................................16

3.3.5 Block Protection .....................................................................................................................................16

3.3.6 DSU-ICE Interface..................................................................................................................................17

3.4 User Boot Mode (Single-Chip Mode).............................................................................................................19

3.4.1 Method 1: Storing a Programming Routine in the Flash Memory..........................................................19

3.4.2 Method 2: Transferring a Programming Routine from an External Host................................................22

3.5 Single Boot Mode............................................................................................................................................25

3.5.1 General Procedure: Using the Program in the On-Chip Boot ROM.......................................................26

3.5.2 Host-to-Target Connection Examples.....................................................................................................29

3.5.3 Configuring for Single Boot Mode.........................................................................................................31

3.5.4 Memory Map..........................................................................................................................................31

3.5.5 Interface Specification............................................................................................................................32

3.5.6 Data Transfer Format..............................................................................................................................33

3.5.7 Overview of the Boot Program Commands ............................................................................................ 37

3.5.8 RAM Transfer Command........................................................................................................................38

3.5.9 Show Flash Memory Sum Command......................................................................................................41

3.5.10 Show Product Information Command.....................................................................................................42

3.5.11 Acknowledge Responses.........................................................................................................................44

3.5.12 Determination of a Serial Operation Mode.............................................................................................45

3.5.13 Password.................................................................................................................................................47

3.5.14 Calculation of the Show Flash Memory Sum Command ........................................................................48

3.5.15 Checksum Calculation ............................................................................................................................48

3.5.16 General Boot Program Flowchart ..........................................................................................................49

3.5.17 Relationships Between Baud Rates and Operating Frequencies.............................................................50

3.6 On-Board Programming and Erasure...............................................................................................................51

3.6.1 Key Features...........................................................................................................................................51

3.6.2 Block Architecture..................................................................................................................................51

3.6.3 CPU-to-Flash Interface...........................................................................................................................52

3.6.4 Read Mode and Embedded Operation Mode..........................................................................................53

3.6.5 Reading Array Data................................................................................................................................53

3.6.6 Writing Commands.................................................................................................................................53

3.6.7 Reset .......................................................................................................................................................53

3.6.8 Auto Program Command........................................................................................................................54

3.6.9 Auto Chip Erase Command.....................................................................................................................54

3.6.10 Auto Block Erase and Auto Multi-Block Erase Commands ...................................................................55

3.6.11 Block Protect Command.........................................................................................................................56

3.6.12 Verify Block Protect Command..............................................................................................................56

3.6.13 Write Operation Status............................................................................................................................56

3.6.14 Flash Control/Status Register..................................................................................................................58

3.6.15 Flash Security..........................................................................................................................................58

3.6.16 Command Definitions.............................................................................................................................60

3.6.17 Embedded Algorithms ............................................................................................................................63

vi

TMP1940

3.7 Programmer Mode...........................................................................................................................................69

3.7.1 Mode Setting...........................................................................................................................................69

3.7.2 Memory Maps.........................................................................................................................................70

3.7.3 Pin Functions and Settings......................................................................................................................71

3.7.4 Key Features...........................................................................................................................................73

3.7.5 Block Architecture..................................................................................................................................74

3.7.6 Read Mode and Embedded Operation Mode..........................................................................................75

3.7.7 Reading Array Data................................................................................................................................75

3.7.8 Writing commands..................................................................................................................................75

3.7.9 Reset .......................................................................................................................................................75

3.7.10 Auto Program Command ........................................................................................................................76

3.7.11 Auto Chip Erase Command.....................................................................................................................76

3.7.12 Auto Block Erase and Auto Multi-Block Erase Commands ...................................................................77

3.7.13 Block Protect Command.........................................................................................................................77

3.7.14 Block Unprotect Command.....................................................................................................................78

3.7.15 Verify Block Protect Command..............................................................................................................78

3.7.16 Write Operation Status............................................................................................................................78

3.7.17 Flash Security..........................................................................................................................................80

3.7.18 Command Definitions.............................................................................................................................81

3.7.19 Embedded Algorithms ............................................................................................................................83

4. Electrical Characteristics.......................................................................................................................................89

4.1 Maximum Ratings............................................................................................................................................89

4.2 DC Electrical Characteristics (1/3).................................................................................................................. 90

4.3 DC Electrical Characteristics (2/3).................................................................................................................. 91

4.4 DC Electrical Characteristics (3/3).................................................................................................................. 92

4.4.1 DC Electrical Characteristics in Modes Except Programmer Mode.......................................................92

4.4.2 DC Electrical Characteristics in Programmer Mode...............................................................................92

4.5 Precautions for Programming and Erasing the Flash Memory......................................................................... 92

4.6 AC Characteristics in Programmer Mode........................................................................................................93

Part 2 Applications

Part 3 Package Infomation

vii

TMP1940

viii

Handling Precautions

1 Using Toshiba Semiconductors Safely

1. Using Toshiba Semiconductors Safely

TOSHIBA are continually working to improve the quality and the reliability of their products.

Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent

electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer,

when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in

which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily

injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified

operating ranges as set forth in the most recent products specifications. A lso, please keep in mind

the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

1

2 Safety Precautions

2. Safety Precautions

This section lists important precautions which users of semiconductor devices (and anyone else)

should observe in order to avoid injury and damage to property, and to ensure safe and correct

use of devices.

Please be sure that you understand the meanings of the labels and the graphic symbol described

below before you move on to the detailed descriptions of the precautions.

[Explanation of labels]

Indicates an imminently hazardous situation which will result in death or

serious injury if you do not follow instructions.

Indicates a potentially hazardous situation which could result in death or

serious injury if you do not follow instructions.

Indicates a potentially hazardous situati on which if not avoided, may

result in minor injury or moderate injury.

[Explanation of graphic symbol]

Graphic symbol Meaning

Indicates that caution is required (laser beam is dangerous to eyes).

2

2 Safety Precautions

2.1 General Precautions regarding Semiconductor Devices

Do not use devices under conditions exceeding their absolute maximum ratings (e.g. current, volt age, power dissipation or

temperature).

This may cause the device to break down, degrade its performance, or cause it to catch fire or explode resulting in injury.

Do not insert devices in the wrong orientation.

Make sure that the positive and negative terminals of power supplies are connected correctly. Otherwise the rated maximum

current or power dissipation may be exceeded and the device may break down or undergo performance degradation, causing it

to catch fire or explode and resulting in injury.

When power to a device is on, do not touch the device’s heat sink.

Heat sinks become hot, so you may burn your hand.

Do not touch the tips of device leads.

Because some types of device have leads with pointed tips, you may prick your finger.

When conducting any kind of evaluation, inspection or testing, be sure to connect the testing equipment’s electrodes or probes to

the pins of the device under test before powering it on.

Otherwise, you may receive an electric shock causing injury.

Before grounding an item of measuring equipment or a soldering iron, check that there is no electrical leakage from it.

Electrical leakage may cause the device which you are testing or soldering to break down, or could give you an electric shock.

Always wear protective glasses when cutting the leads of a device with clippers or a similar tool.

If you do not, small bits of metal flying off the cut ends may damage your eyes.

3

2 Safety Precautions

2.2 Precautions Specific to Each Product Group

2.2.1 Optical semiconductor devices

When a visible semiconductor laser is operating, do not look directly into the laser beam or look through the optical system.

This is highly likely to impair vision, and in the worst case may cause blindness.

If it is necessary to examine the laser apparatus, for example to inspect its optical characteristics, always wear the appropriate

type of laser protective glasses as stipulated by IEC standard IEC825-1.

Ensure that the current flow ing in an LED device does not exceed the device’s maximum rated current.

This is particularly important for resin-packaged LED devices, as excessi ve current may cause the package resin to blow up,

scattering resin fragments and causing injury.

When testing the dielectric strength of a photocoupler, use testing equipment which can shut off the supply voltage to the

photocoupler. If you detect a leakage current of more than 100 µA, use the testing equipment to shut off the photocoupler’s

supply voltage; otherwise a large short-circuit current will flow continuously, and the device may break down or burst into

flames, resulting in fire or injury.

When incorporating a visible semiconductor laser into a design, use the device’s internal photodetect or or a separate

photodetector to stabilize the laser’s radiant power so as to ensure that laser beams exceeding the laser’s rated radiant power

cannot be emitted.

If this stabilizing mechanism does not work and the rated radiant power is exceeded, the device may break down or the

excessively powerful laser beams may cause injury.

2.2.2 Power devices

Never touch a power device while it is powered on. Also, after turning off a power device, do not touch it until it has thoroughly

discharged all remaining electrical charge.

Touching a power device while it is powered on or still charged could cause a severe electric shock, resulting in death or serious

injury.

When conducting any kind of evaluation, inspection or testing, be sure to connect the testing equi pm ent’s electrodes or probes to

the device under test before powering it on.

When you have finished, discharge any electrical charge remaining in the device.

Connecting the electrodes or probes of testing equipment to a device while it is powered on may result in electric shock, causing

injury.

4

2 Safety Precautions

Do not use devices under conditions which exceed their absolute maximum ratings (current, voltage, power dissipat i on,

temperature etc.).

This may cause the device to break down, causing a large short-circuit current to flow, which may in turn cause it to catch fire or

explode, resulting in fire or injury.

Use a unit which can detect short-circuit currents and which will shut off the power supply if a short-circuit occurs.

If the power supply is not shut off, a large short-circuit current will flow continuously, which may in turn cause the device to catc h

fire or explode, resulting in fire or injury.

When designing a case for enclosing your system, consider how best to protect the user from shrapnel in the event of the device

catching fire or exploding.

Flying shrapnel can cause injury.

When conducting any kind of evaluation, inspection or testing, al ways use prot ect i ve safety tools such as a cover for the device.

Otherwise you may sustain injury caused by the device catching fire or exploding.

Make sure that all metal casings in your design are grounded to earth.

Even in modules where a device’s electrodes and metal casing are insulated, capacitance in the module may cause the

electrostatic potential in the casing to rise.

Dielectric breakdown may cause a high voltage to be applied to the casing, causing electric shock and injury to anyone touching

it.

When designing the heat radiation and safety features of a system incorporating high-speed rectifi ers, remember to take the

device’s forward and reverse losses into account.

The leakage current in these devices is greater than that in ordinary rectifiers; as a result, if a high-speed rectifier is used in an

extreme environment (e.g. at high temperature or high voltage), its reverse l oss may inc rease, causing thermal runaway to occur.

This may in turn cause the device to explode and scatter shrapnel, resulting in injury to the user.

A design should ensure that, except when the main circuit of the device is active, reverse bias is applied to the device gate while

electricity is conducted to control circuits, so that the main circuit will become inactive.

Malfunction of the device may cause serious accidents or injuries.

When conducting any kind of evaluation, inspection or testing, either wear protect i ve gl oves or wait until the device has cooled

properly before handling it.

Devices become hot when they are operated. Even after the power has been turned off, the device will retain residual heat which

may cause a burn to anyone touching it.

2.2.3 Bipolar ICs (for use in automobiles)

If your design includes an inductive load such as a motor coil, incorporate diodes or similar devices into the design to prevent

negative current from flowing in.

The load current generated by powering the device on and off may cause it to function erratically or to break down, which could in

turn cause injury.

Ensure that the power supply to any device which incorporates protective functions is stable.

If the power supply is unstable, the device may operate erratically, preventing the protective functions from working correctly. If

protective functions fail, the device may break down causing injury to the user.

5

3 General Safety Precautions and Usage Considerations

3. General Safety Precautions and Usage Considerations

This section is designed to help you gain a better understanding of semiconductor devices, so as

to ensure the safety, quality and reliability of the devices which you incorporate into your

designs.

3.1 From Incoming to Shipping

3.1.1 Electrostatic discharge (ESD)

When handling individual devices (which are not yet mounted on a printed

circuit board), be sure that the environment is protected against

electrostatic electricity. Operators should wear anti-static clothing, and

containers and other objects which come into direct contact with devices

should be made of anti-static materials and should be grounded to earth via

an 0.5- to 1.0-MΩ protective resistor.

Please follow the precautions described below; this is particularly important for devices which are

marked “Be careful of static.”.

(1) Work environment

•

When humidity in the working environment decrea ses, the human body and other insulators

can easily become charged with static electricity due to friction. Maintain the recommended

humidity of 40% to 60% in the work environment, while also taking into account the fact that

moisture-proof-packed products may absorb moisture after unpacking.

•

Be sure that all equipment, jigs and tools in the working area are grounded to earth.

•

Place a conductive mat over the floor of the work area, or take other appropriate measures, so

that the floor surface is protected against static electricity and is grounded to earth. The

4

surface resistivity should be 10

5

× 10

to 108 Ω

•

Cover the workbench surface also with a conductive mat (with a surface resistivity of 104 to

8

Ω/sq, for a resistance between surface and ground of 7.5 × 105 to 10

10

is to disperse stati c electricity on the surface (through resistive components) and ground it to

earth. Workbench surfaces must not be constructed of low-resistance metallic materials that

allow rapid static discharge when a charged device touches them directly.

•

Pay attention to the following points when using automatic equipment in your workplace:

(a) When picking up ICs with a vacuum unit, use a conductive rubber fitting on the end of the

pick-up wand to protect against electrostatic charge.

(b) Minimize friction on IC package surfaces. If some rubbing is unavoidable due to the

device’s mechanical structure, minimize the friction plane or use material with a small

friction coefficient and low electrical resistance. Also, cons ider the use of an ionizer.

to 108 Ω/sq and the resistance between surface and ground, 7.5

8

Ω) . The purpose of this

(c) In sections which come into contact with device lead terminals, use a material which

dissipates static electricity.

(d) Ensure that no statically charged bodies (such as work clothes or the human body) touch

the devices.

6

3 General Safety Precautions and Usage Considerations

(e) Make sure that sections of the tape carrier which come into contact with installation

devices or other electrical machinery are made of a low-resistance material.

(f) Make sure that jigs and tools used in the assembly process do not touch devices.

(g) In processes in which packages may retain an electrostatic charge, use an ionizer to

neutralize the ions.

•

Make sure that CRT displays in the working area are protected against static charge, for

example by a VDT filter. As much as possible, avoid turning displays on and off. Doing so can

cause electrostatic induction in devices.

•

Keep track of charged potential in the working area by taking periodic measurements.

•

Ensure that work chairs are protected by an anti-static textile cover and are grounded to the

floor surface by a grounding chain. (Suggested resistance between the seat surface and

5

12

grounding chain is 7.5 × 10

to 10

Ω.)

•

Install anti-static mats on storage shelf surfaces. (Suggested surface resistivity is 104 to 10

Ω/sq; suggested resistance between surface and ground is 7.5 × 10

•

For transport and temporary storage of devices, use containers (boxes, jigs or bags) that are

made of anti-static materials or materials which dissipate electrostati c charge.

•

Make sure that cart surfaces which come into contact with device packaging are made of

materials which will conduct static electricity, and verify that they are grounded to the floor

surface via a grounding chain.

•

In any location where the level of static electricity is to be closely controlled, the ground

resistance level should be Class 3 or above. Use different ground wires for all items of

equipment which may come into physical contact with devices.

(2) Operating environment

•

Operators must wear anti-s tatic clothing and conductive shoes

(or a leg or heel strap).

•

Operators must wear a wrist strap grounded to earth via a

resistor of about 1 MΩ.

•

Soldering irons must be grounded from iron tip to earth, and must be used only at low voltages

(6 V to 24 V).

5

to 108 Ω.)

8

•

If the tweezers you use are lik ely to touch the device terminals, use anti-static tweezers and in

particular avoid metallic tweezers. If a charged device touches a low-resistance tool, rapid

discharge can occur. When using vacuum tweezers, attach a conductive chucking pat to the tip,

and connect it to a dedicated ground used especially for anti-static purposes (suggested

resistance value: 10

•

Do not place devices or their containers near sources of strong electrical fields (such as above a

CRT).

4

to 108 Ω).

7

3 General Safety Precautions and Usage Considerations

•

When storing printed circuit boards which have devices mounted on them, use a board

container or bag that is protected against static charge. To avoid the occurrence of static charge

or discharge due to friction, keep the boards separate from one other and do not stack them

directly on top of one another.

•

Ensure, if possible, that any articles (such as clipboards) which are brought to any location

where the level of static electricity must be closely controlled are constructed of anti-static

materials.

•

In cases where the human body comes into direct contact with a device, be sure to wear antistatic finger covers or gloves (suggested resistance value: 10

•

Equipment safety covers installed near devices should have resistance ratings of 109 Ω or less.

•

If a wrist strap cannot be used for some reason, and there is a possibility of imparting friction

to devices, use an ionizer.

•

The transport film used in TCP products is manufactured from materials in which static

charges tend to build up. When using these products, install an ionizer to prevent the film from

being charged with static electricity. Also, ensure that no static electricity will be applied to the

product’s copper foils by taking measures to prevent static occuring in the peripheral

equipment.

8

Ω or less).

3.1.2 Vibration, impact and stress

Handle devices and packaging materials with care. To avoid damage

to devices, do not toss or drop packages. Ensure that devices are not

subjected to mechanical vibration or shock during transportation.

Ceramic package devices and devices in canister-type packages which

have empty space inside them are subject to damage from vibration

and shock because the bonding wires are secured only at their ends.

Plastic molded devices, on the other hand, have a relatively hi gh level of resistance to vibration

and mechanical shock because their bonding wires are enveloped and fixed in resin. However,

when any device or package type is installed in target equipment, it is to some extent susceptible

to wiring disconnections and other damage from vibration, shock and stressed solder junctions.

Therefore when devices are incorporated into the design of equipment which will be subject to

vibration, the structural design of the equipment must be thought out careful ly.

If a device is subjected to especially strong vibration, mechanical shock or stress, the package or

the chip itself may crack. In products such as CCDs which incorporate window glass, this could

cause surface flaws in the glass or cause the connection between the glass and the ceramic to

separate.

Furthermore, it is known that stress applied to a semiconductor device through the package

changes the resistance characteristics of the chip because of piezoelectric effects. In analog circuit

design attention must be paid to the problem of package stress as well as to the dangers of

vibration and shock as described above.

Vibration

8

3.2 Storage

3.2.1 General storage

•

Avoid storage locations where devices will be exposed to moisture or direct sunlight.

•

Follow the instructions printed on the device cartons regarding

transportation and storage.

•

The storage area temperature should be kept within a

temperature range of 5°C to 35°C, and relative humidity

should be maintained at between 45% and 75%.

•

Do not store devices in the presence of harmful (especially

corrosive) gases, or in dusty conditions.

•

Use storage areas where there is minimal temperature fluctuation. Rapid temperature changes

can cause moisture to form on stored devices, resulting in lead oxidation or corrosion. As a

result, the solderability of the leads will be degraded.

•

When repacking devices, use anti-static containers.

3 General Safety Precautions and Usage Considerations

Humidity:

@@

Temperature:

•

Do not allow external forces or loads to be applied to devices while they are in storage.

•

If devices have been stored for more than two years, their electrical characteristics should be

tested and their leads should be tested for ease of soldering before they are used.

3.2.2 Moisture-proof packing

Moisture-proof packing should be handled with care. The handling

procedure specified for each packing type should be followed scrupulously.

If the proper procedures are not foll owed, the quality and reliability of

devices may be degraded. This section describes general precautions for

handling moisture-proof packing. Since the details may differ from device

to device, refer also to the relevant individual datasheets or databook.

(1) General precautions

Follow the instructions printed on the device cartons regarding transportation and storage.

•

Do not drop or toss device packing. The laminated alumi num material in it can be rendered

ineffective by rough handling.

•

The storage area temperature should be kept within a temperature range of 5°C to 30°C, and

relative humidity should be maintained at 90% (max). Use devices within 12 months of the

date marked on the package seal.

9

3 General Safety Precautions and Usage Considerations

•

If the 12-month storage period has expired, or if the 30% humidity indicator shown in Figure 1

is pink when the packing is opened, it may be advisable, depending on the device and packing

type, to back the devices at high temperature to remove any moisture. Please refer to the table

below. After the pack has been opened, use the devices in a 5°C to 30°C. 60% RH environment

and within the effective usage period listed on the moisture-proof package. If the effective

usage period has expired, or if the packing has been stored in a high-humidity environment,

bake the devices at high temperature.

Packing Moisture removal

Tray If the packing bears the “Heatproof” marking or indicates the maximum temperature which it can

withstand, bake at 125°C for 20 hours. (Some devices require a different procedure.)

Tube Transfer devices to trays bearing the “Heatproof” marking or indicating the temperature which

they can withstand, or to aluminum tubes before baking at 125°C for 20 hours.

Tape Deviced packed on tape cannot be baked and must be used within the effective usage period

after unpacking, as specified on the packing.

•

When baking devices, protect the devices from static electricity.

•

Moisture indicators can detect the approximate humidity level at a standard temperature of

25°C. 6-point indicators and 3-point indicators are currently in use, but eventually all

indicators will be 3-point indicators.

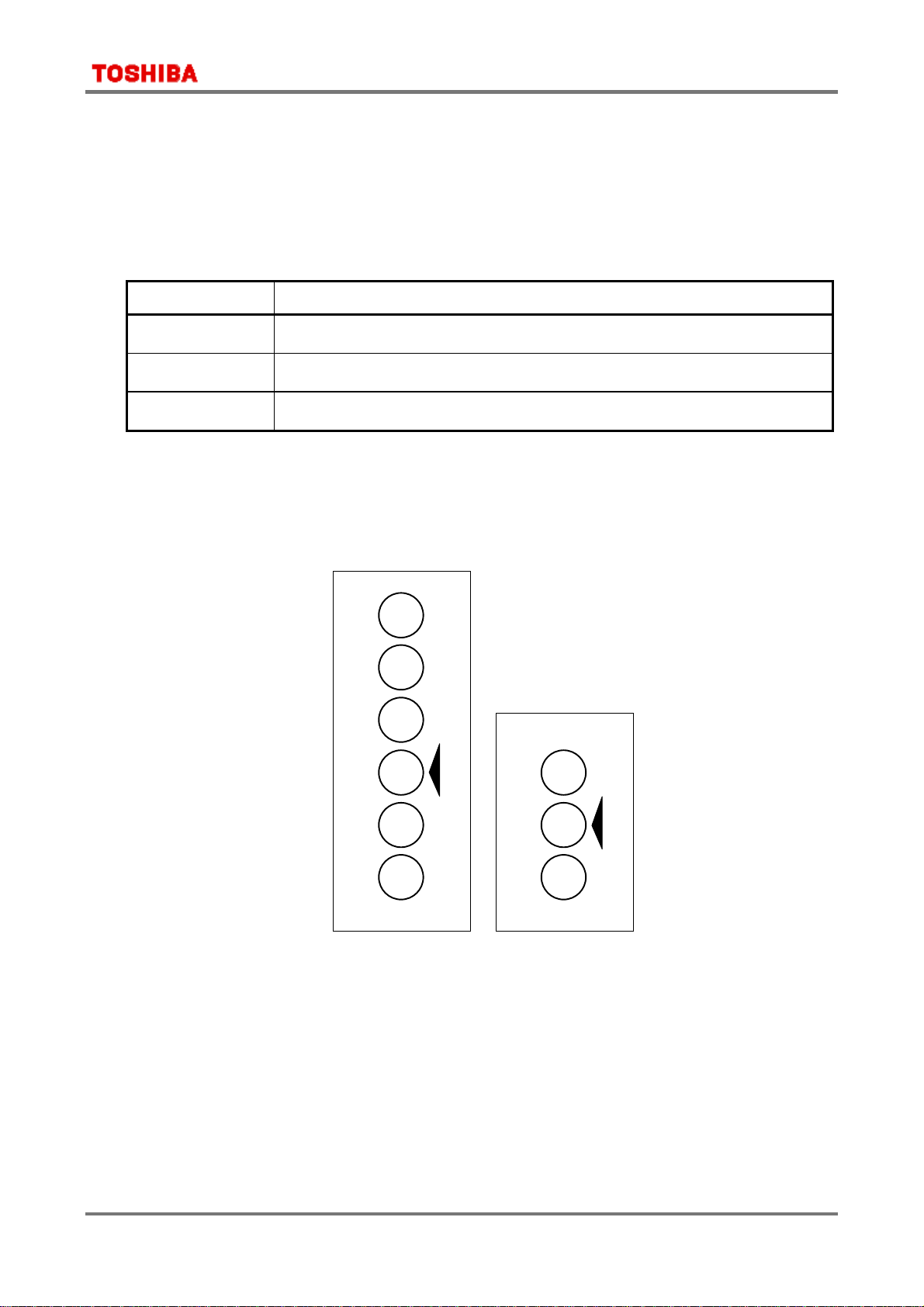

HUMIDITY INDICATOR

60%

50%

40%

30%

20%

10%

READ AT LAVENDER

BETWEEN PINK & BLUE

(a) 6-point indicator (b) 3-point indicator

DANGER IF PINK

HUMIDITY INDICATOR

CHANGE DESICCANT

READ AT LAVENDER

BETWEEN PINK & BLUE

40

30

20

Figure 1 Humidity indicator

DANGER IF PINK

10

3 General Safety Precautions and Usage Considerations

3.3 Design

Care must be exercised in the design of electronic equipment to achieve th e desired reliability. It

is important not only to adhere to specifications concerning absolute maximum ratings and

recommended operating conditions, it is also important to consider the overall environment in

which equipment will be used, including factors such as the ambient temperature, transient

noise and voltage and current surges, as well as mounting conditions which affect device

reliability. This section describes some general precautions which you should observe when

designing circuits and when mounting devices on printed circuit boards.

For more detailed information about each product family, refer to the relevant individual

technical datasheets available from Toshiba.

3.3.1 Absolute maximum ratings

Do not use devices under conditions in whic h their absolute maximum

ratings (e.g. current, voltage, power dissipation or temperature) will be

exceeded. A device may break down or its performance may be degraded,

causing it to catch fire or explode resulting in injury to the user.

The absolute maximum ratings are rated values which must not be

exceeded during operation, even for an instant. Although absolute

maximum ratings differ from product to product, they essentially

concern the voltage and current at each pin, the allowable power

dissipation, and the junction and storage temperatures.

If the voltage or current on any pin exceeds the absolute maximum

rating, the device’s internal circuitry can become degraded. In the worst case, heat generated in