Toshiba TMP96C141AF, TLCS-900 Series User Manual

TOSHIBA

TLCS-900 Series

CMOS 16-bit Microcontroller

TMP96C141AF

1. Outline and Device Characteristics

The TMP96C141AF is high-speed advanced 16-bit microcontroller developed for controlling medium to large-scale equipment.

The TMP96C141AF is housed in an 80-pin flat package.

Device characteristics are as follows:

(1) Original 16-bit CPU

• TLCS-90 instruction mnemonic upward compatible.

• 16M-byte linear address space

• General-purpose registers and register bank system

• 16-bit multiplication/division and bit transfer/arithmetic

instructions

• High-speed micro DMA

- 4 channels (1.6 µ s/2 bytes @ 20MHz)

(2) Minimum instruction execution time

- 200ns @ 20MHz

(3) Internal RAM: 1K byte

TMP96C141AF

Internal ROM: None

(4) External memory expansion

• Can be expanded up to 16M bytes (for both programs and

data).

• Can mix 8- and 16-bit external data buses.

(5) 8-bit timers: 2 channels

(6) 8-bit PWM timers: 2 channels

(7) 16-bit timers: 2 channels

(8) Pattern generators: 4 bits, 2 channels

(9) Serial interface: 2 channels

(10) 10-bit A/D converter: 4 channels

(11) Watchdog timer

(12) Chip select/wait controller: 3 blocks

(13) Interrupt functions

• 3 CPU interrupts

• 14 internal interrupts

• 6 external interrupts

(14) I/O ports

(15) Standby function : 3 halt modes (RUN, IDLE, STOP)

…

Dynamic data bus sizing

…

and Illegal instruction

…

SWI instruction, privileged violation,

7-level priority can be set.

The information contained here is subject to change without notice.

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties

which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic

equipments (office equipment, communication equipment, measuring equipment, domestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types

of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments without prior consultation with TOSHIBA.

TOSHIBA CORPORATION

1

TMP96C141AF

2

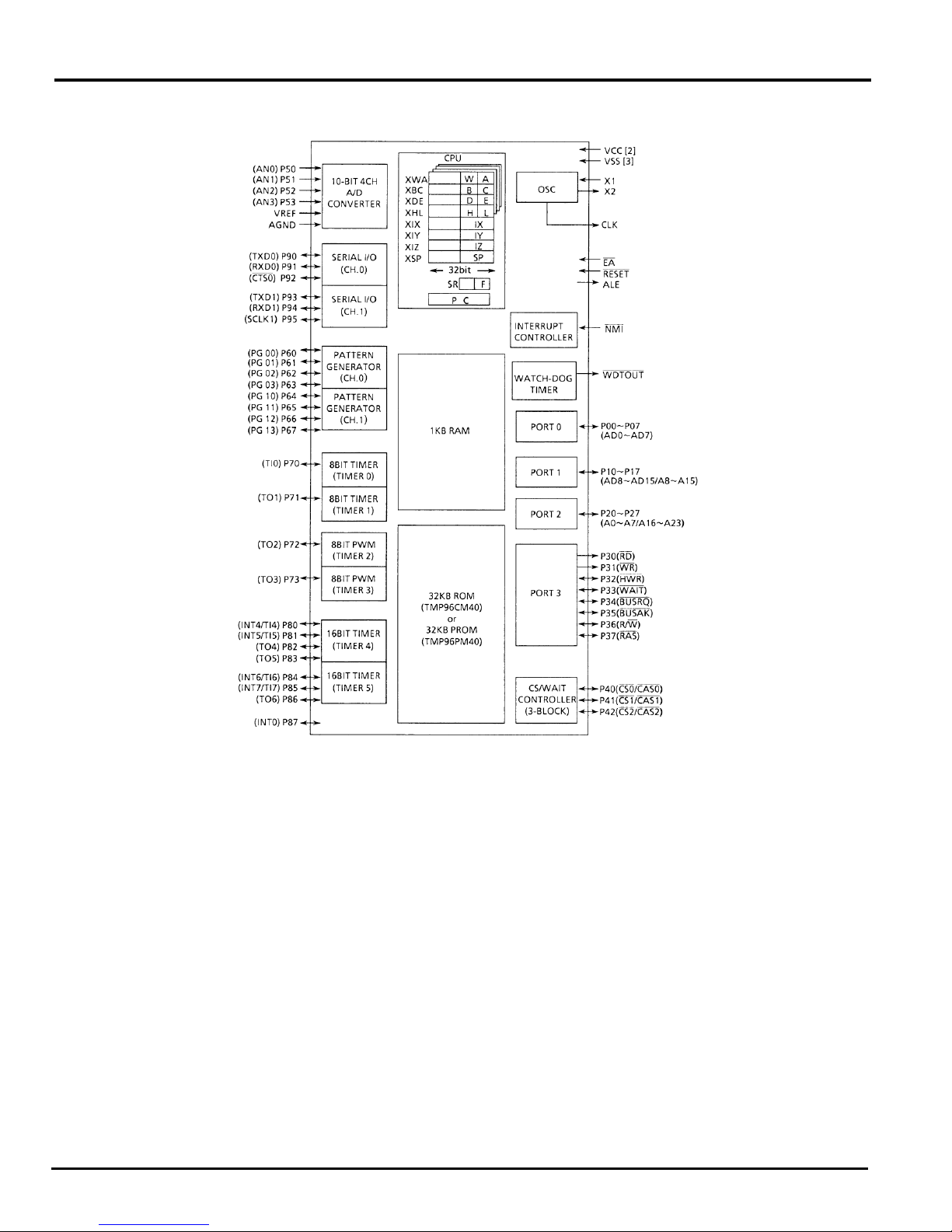

Figure 1. TMP96C141AF Block Diagram

TOSHIBA CORPORATION

TMP96C141AF

2. Pin Assignment and Functions

The assignment of input/output pins for TMP96C141AF, their

name and outline functions are described below.

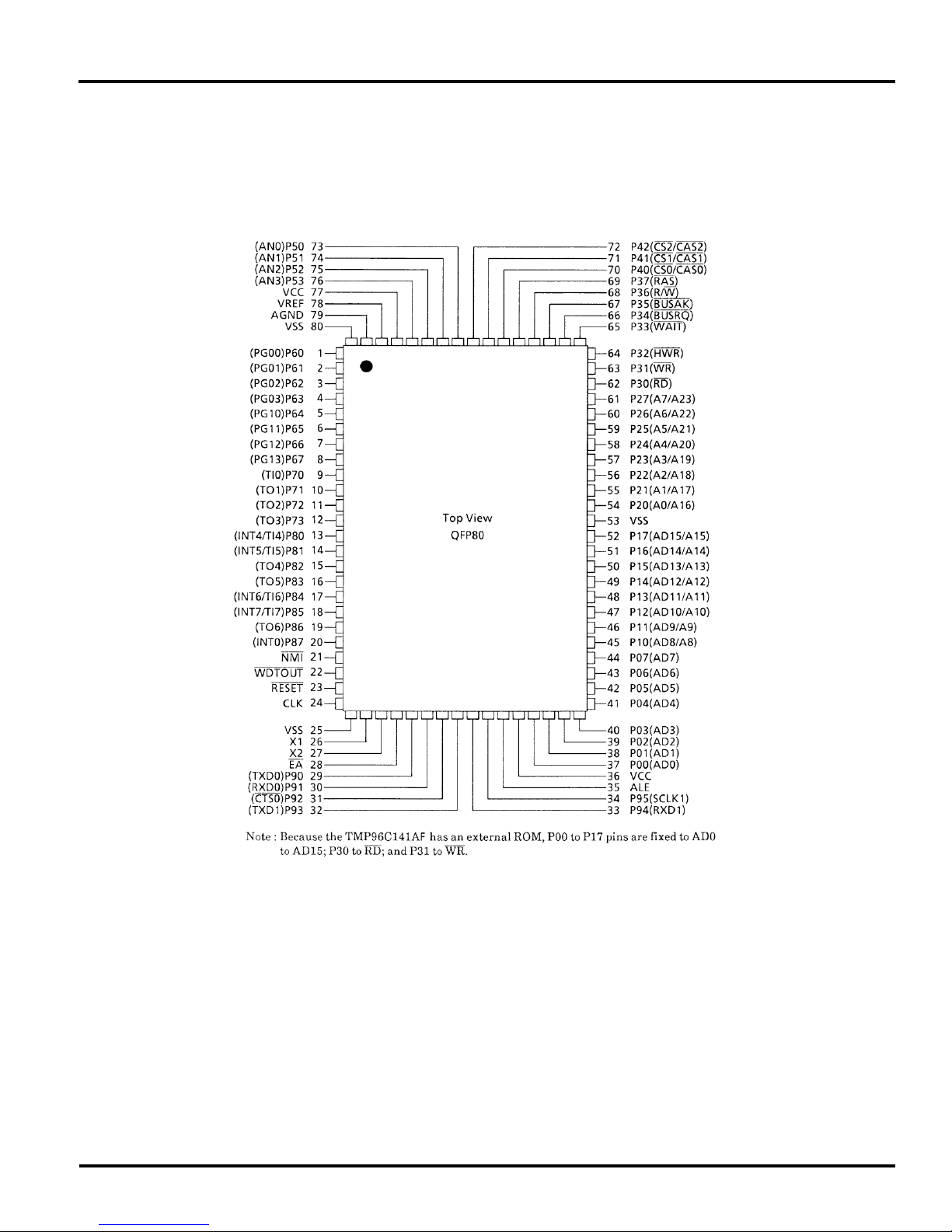

2.1 Pin Assignment

Figure 2.1 shows pin assignment of TMP96C141AF.

TOSHIBA CORPORATION

Figure 2.1 Pin Assignment (80-pin QFP)

3

TMP96C141AF

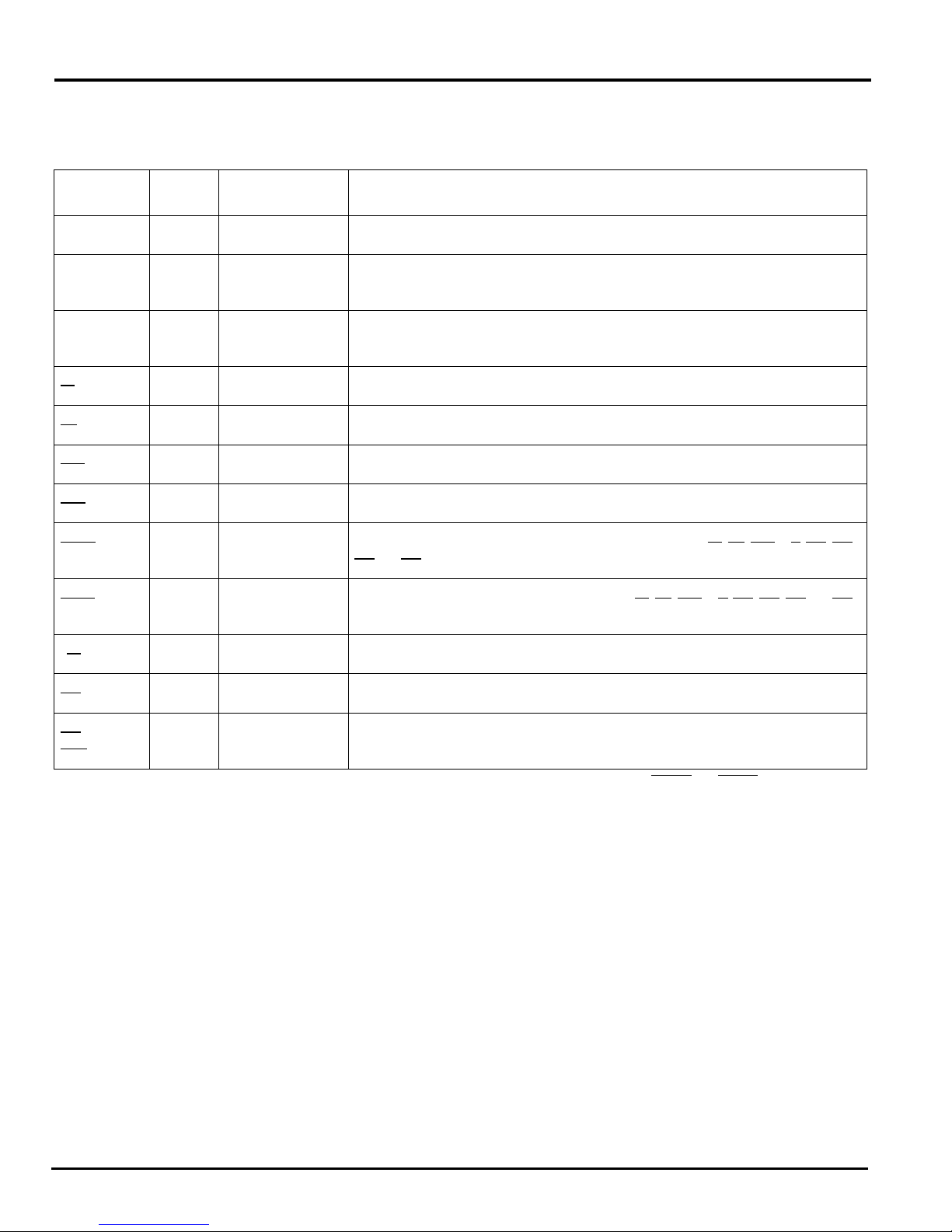

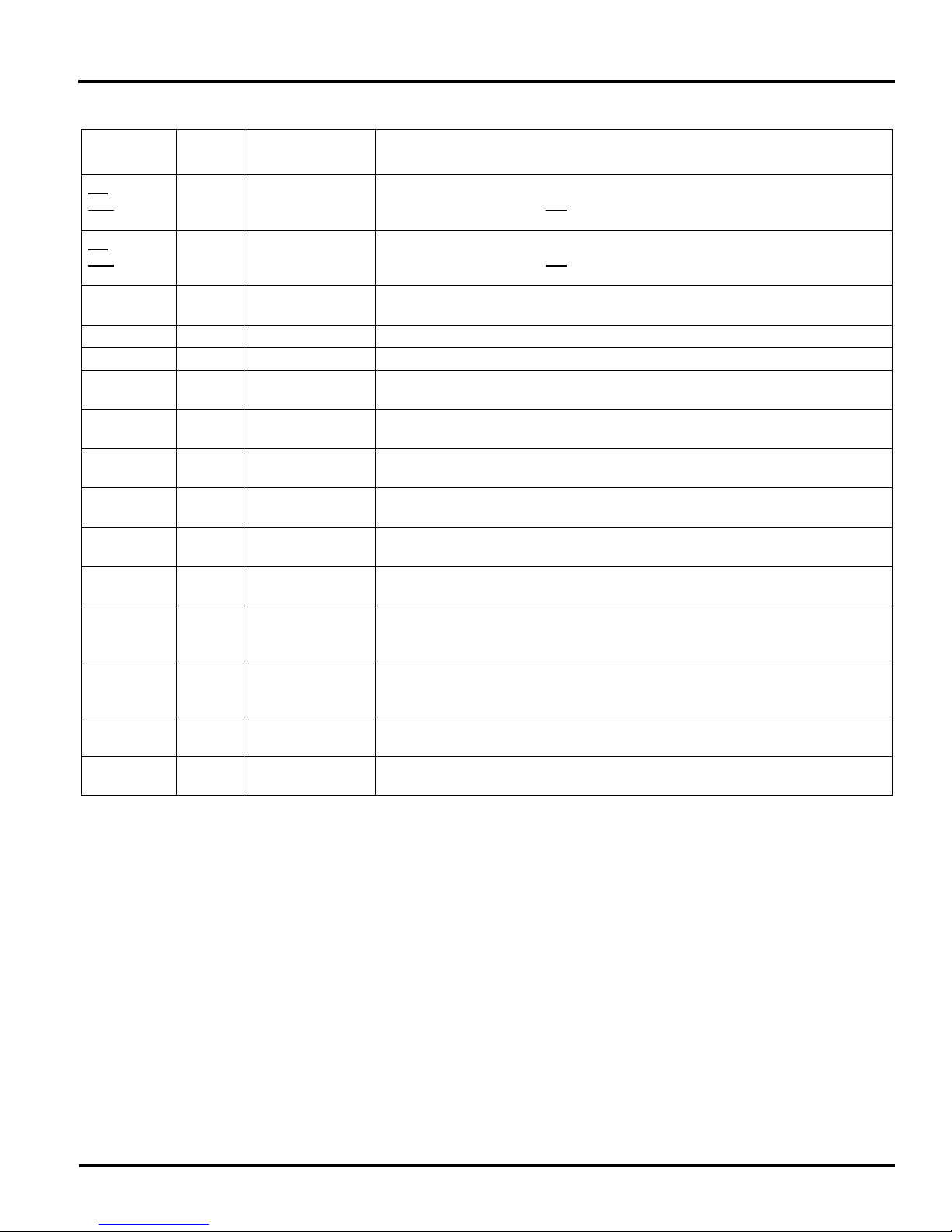

2.2 Pin Names and Functions

The names of input/output pins and their functions are described below.

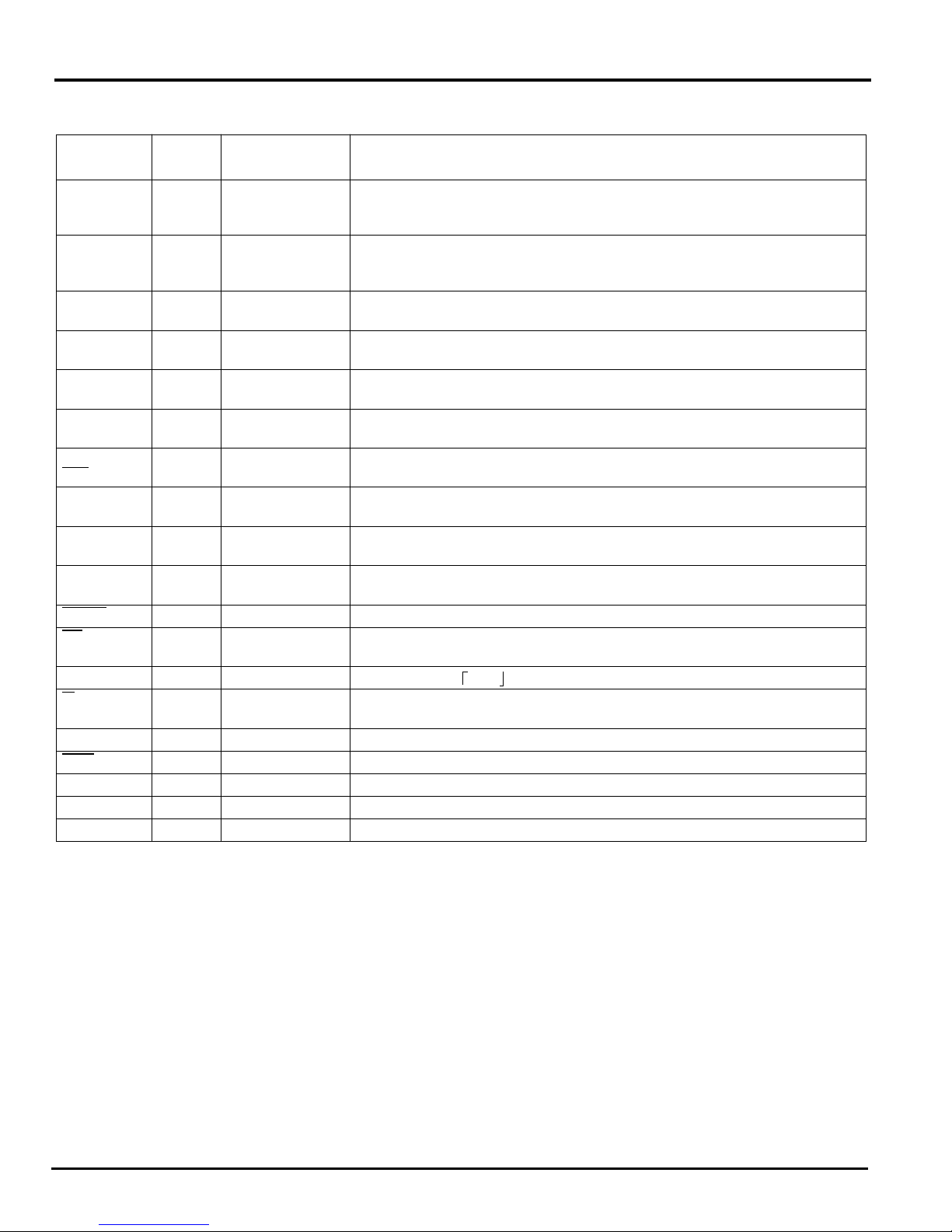

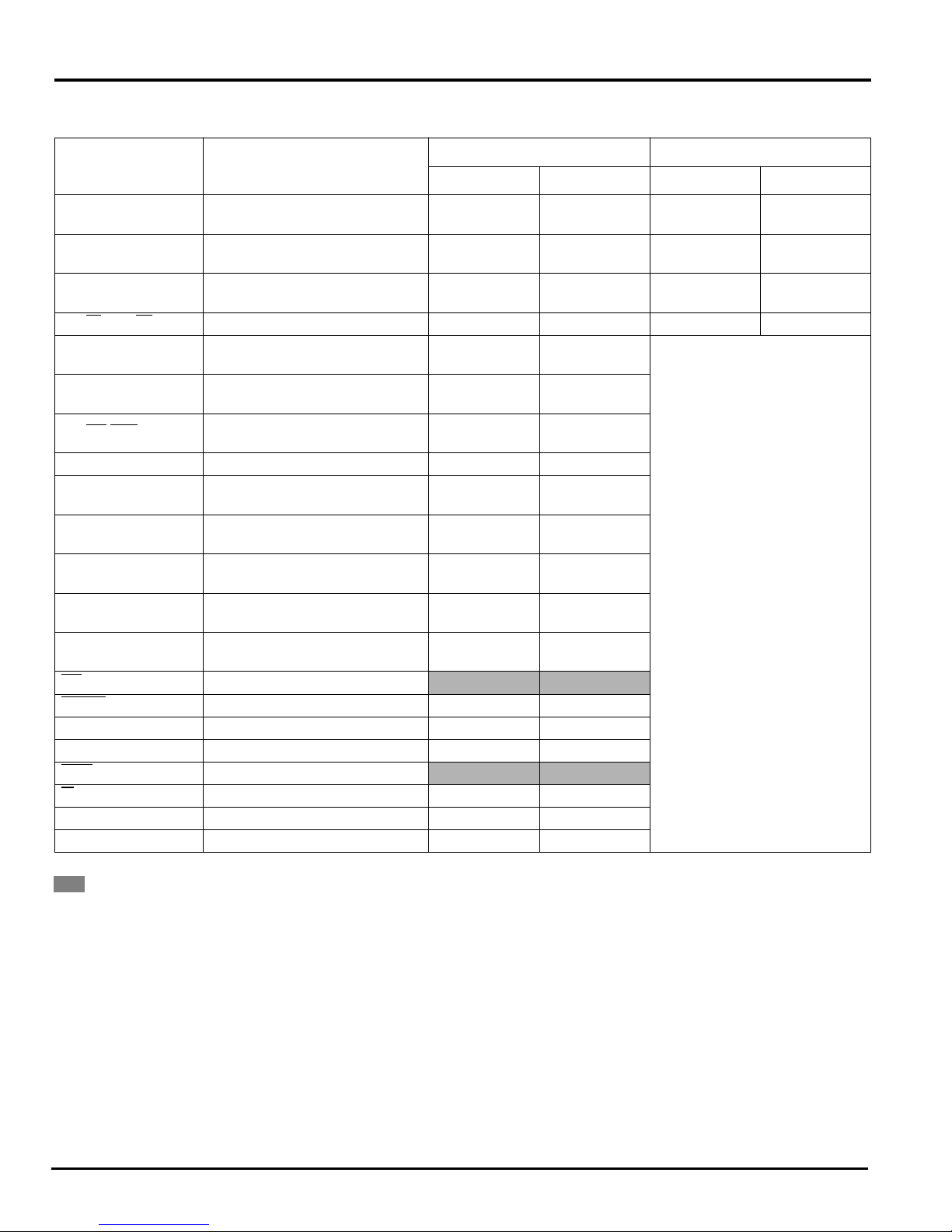

Table 2.2. Pin Names and Functions

Pin Name

P00 ~ P07

AD0 ~ AD7

P10 ~ P17

AD8 ~ AD15

A8 ~ A15

P20 ~ P27

A0 ~ A7

A16 ~ A23

P30

RD

P31

WR

P32

HWR

P33

WAIT

P34

BUSRQ 1

P35

BUSAK

P36

R/W

P37

RAS

P40

CS0

CAS0

Note: With the external DMA controller, this device’s built-in memory or built-in I/O cannot be accessed using the BUSRQ

Number

of Pins

8

8

8

1

1

1

1

1

1

1

1

I/O Functions

I/O

Tri-state

I/O

Tri-state

Output

I/O

Output

Output

Output

Output

Output

Output

I/O

Output

I/O

Input

I/O

Input

I/O

Output

I/O

Output

I/O

Output

I/O

Output

Output

Port 0: I/O port that allows I/O to be selected on a bit basis

Address / data (lower): 0 - 7 for address / data bus

Port 1: I/O port that allows I/O to be selected on a bit basis

Address data (upper): 8 - 15 for address / data bus

Address: 8 to 15 for address bus

Port 2: I/O port that allows selection of I/O on a bit basis (with pull-down resistor)

Address: 0 - 7 for address bus

Address: 16 - 23 for address bus

Port 30: Output port

Read: Strobe signal for reading external memory

Port 31: Output port

Write: Strobe signal for writing data on pins AD0 -7

Port 32: I/O port (with pull-up resistor)

High write: Strobe signal for writing data on pins AD8 - 15

Port 33: I/O port (with pull-up resistor)

Wait: Pin used to request CPU bus wait

Port 34: I/O port (with pull-up resistor)

Bus request: Signal used to request high impedance for AD0 - 15, A0 - 23, RD, WR, HWR, R/W, RAS, CS0,

CS1

, and CS2 pins. (For external DMAC)

Port 35: I/O (with pull-up resistor)

Bus acknowledge: Signal indicating that AD0 - 15, A0 - 23, RD, WR, HWR, R/W, RAS, CS0, CS1, and CS2

pins are at high impedance after receiving BUSRQ. (For external DMAC)

Port 36: I/O port (with pull-up resistor)

Read/write: 1 represents read or dummy cycle; 0, write cycle.

Port 37: I/O port (with pull-up resistor)

Row address strobe: Outputs RAS strobe for DRAM.

Port 40: I/O port (with pull-up resistor)

Chip select 0: Outputs 0 when address is within specified address area.

Column address strobe 0: Outputs CAS strobe for DRAM when address is within specified address area.

and BUSAK pins.

4

TOSHIBA CORPORATION

TMP96C141AF

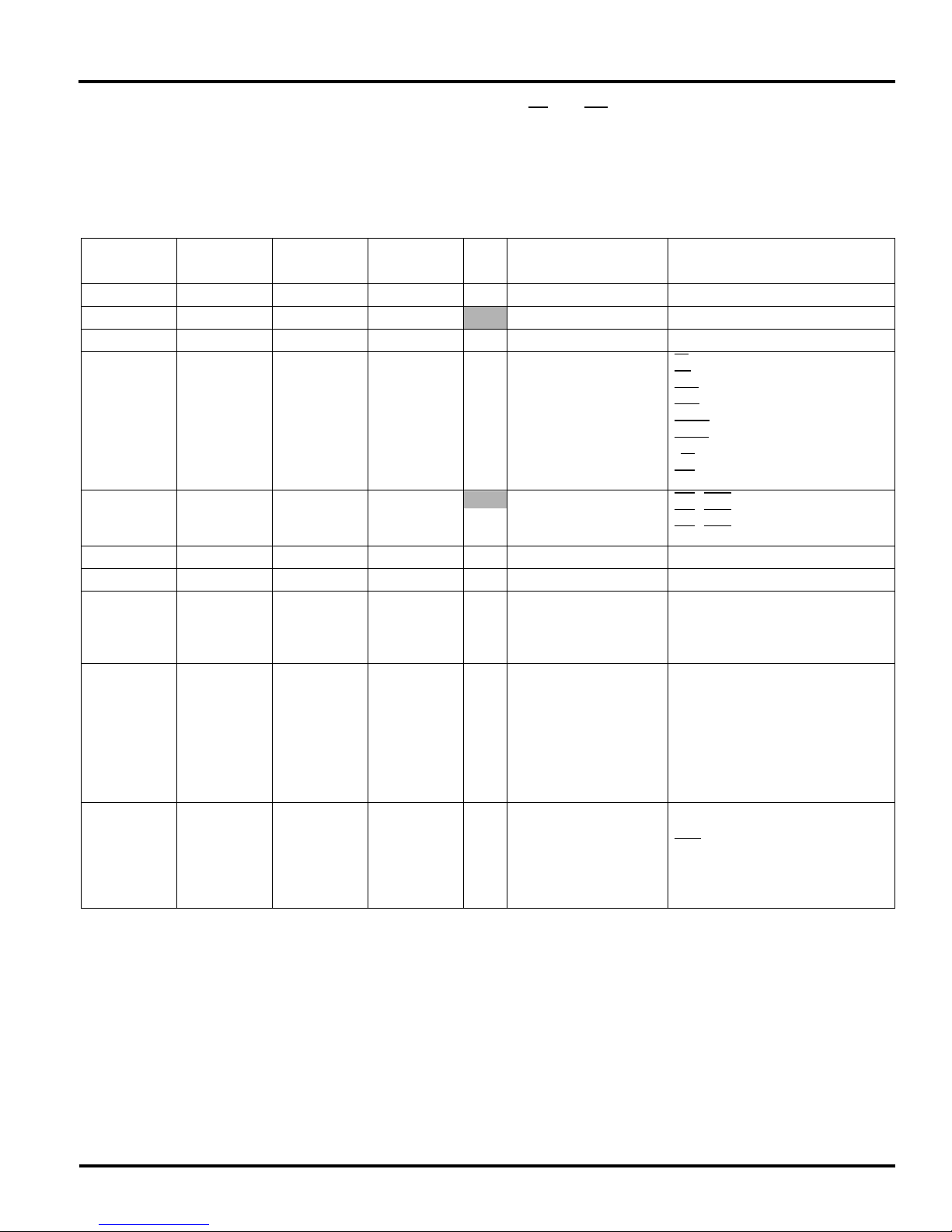

Pin Name

P41

CS1

CAS1

P42

CS2

CAS2

P50 ~ P53

AN0 ~ AN3

Number

of Pins

1

1

4

I/O Functions

I/O

Output

Output

I/O

Output

Output

Input

Input

Port 41: I/O port (with pull-up resistor)

Chip select 1: Outputs 0 if address is within specified address area.

Column address strobe 1: Outputs CAS

strobe for DRAM if address is within specified address area.

Port 42: I/O port (with pull-up resistor)

Chip select 2: Outputs 0 if address is within specified address area.

Column address strobe 2: Outputs CAS

strobe for DRAM if address is within specified address area.

Port 5: Input port

Analog input: Input to A/D converter

VREF 1 Input Pin for reference voltage input to A/D converter

AGND 1 Input Ground pin for A/D converter

P60 ~ P63

PG00 ~ PG03

P64 ~ P67

PG10 ~ PG13

P70

T10

P71

T01

P72

T02

P73

T03

P80

TI4

INT4

P81

TI5

INT5

P82

TO4

P83

TO5

4

4

1

1

1

1

1

1

1

1

I/O

Output

I/O

Output

I/O

Input

I/O

Output

I/O

Output

I/O

Output

I/O

Input

Input

I/O

Input

Input

I/O

Output

I/O

Output

Ports 60 - 63: I/O ports that allow selection of I/O on a bit basis (with pull-up resistor)

Pattern generator ports: 00 - 03

Ports 64 - 67: I/O ports that allow selection of I/O on a bit basis (with pull-up resistor)

Pattern generator ports: 10 - 13

Port 70: I/O port (with pull-up resistor)

Timer input 0: Timer 0 input

Port 71: I/O port (with pull-up resistor)

Timer output 1: Timer 0 or 1 output

Port 72: I/O port (with pull-up resistor)

PWM output 2: 8-bit PWM timer 2 output

Port 73: I/O port (with pull-up resistor)

PWM output 3: 8-bit PWM timer 3 output

Port 80: I/O port (with pull-up resistor)

Timer input 4: Timer 4 count/capture trigger signal input

Interrupt request pin 4: Interrupt request pin with programmable rising/falling edge

Port 81: I/O port (with pull-up resistor)

Timer input 5: Timer 4 count/capture trigger signal input

Interrupt request pin 5: Interrupt request pin with rising edge

Port 82: I/O port (with pull-up resistor)

Timer output 4: Timer 4 output pin

Port 83: I/O port (with pull-up resistor)

Timer output 5: Timer 4 output pin

TOSHIBA CORPORATION

5

TMP96C141AF

Pin Name

P84

TI6

INT6

P85

TI7

INT7

P86

TO6

P87

INT0

P90

TXD0

P91

RXD0

P92

CTS0

P93

TXD1

P94

RXD1

P95

SCLK1

WDTOUT

NMI

Number

of Pins

1

1

1

1

1

1

1

1

1

1

I/O Functions

I/O

Input

Input

I/O

Input

Input

I/O

Output

I/O

Input

I/O

Output

I/O

Input

I/O

Input

I/O

Output

I/O

Input

I/O

I/O

Port 84: I/O port (with pull-up resistor)

Timer input 6: Timer 5 count/capture trigger signal input

Interrupt request pin 6: Interrupt request pin with programmable rising/falling edge

Port 85: I/O port (with pull-up resistor)

Timer input 7: Timer 5 count/capture trigger signal input

Interrupt request pin 7: Interrupt request pin with rising edge

Port 86: I/O port (with pull-up resistor)

Timer output 6: Timer 5 output pin

Port 87: I/O port (with pull-up resistor)

Interrupt request pin 0: Interrupt request pin with programmable level/rising edge

Port 90: I/O port (with pull-up resistor)

Serial send data 0

Port 91: I/O port (with pull-up resistor)

Serial receive data 0

Port 92: I/O port (with pull-up resistor)

Serial data send enable 0 (Clear to Send)

Port 93: I/O port (with pull-up resistor)

Serial send data 1

Port 94: I/O port (with pull-up resistor)

Serial receive data 1

Port 95: I/O port (with pull-up resistor)

Serial clock I/O 1

1 Output Watchdog timer output pin

1 Input

Non-maskable interrupt request pin: Interrupt request pin with falling edge.

Can also be operated at rising edge by program.

CLK 1 Output Clock output: Outputs X1 ÷ 4 clock. Pulled-up during reset.

EA

1 Input

External access: 0 should be inputted with TMP96C141AF

1, with TMP96CM40F/TMP96PM40F.

ALE 1 Output Address latch enable

RESET

1 Input Reset: Initializes LSI. (With pull-up resistor)

X1/X2 2 I/O Oscillator connecting pin

VCC 2 Power supply pin (+ 5V)

VSS 3 GND pin (0V)

Note: Pull-up/pull-down resistor can be released from the pin by software.

6

TOSHIBA CORPORATION

TMP96C141AF

3. Operation

This section describes in blocks the functions and basic operations of the TMP96C141AF device.

Check the chapter Guidelines and Restrictions for proper

care of the device.

3.1 CPU

The TMP96C141AF device has a built-in high-performance

16-bit CPU. (For CPU operation, see TLCS-900 CPU in the

book Core Manual Architecture User Manual.)

This section describes CPU functions unique to

TMP96C141AF that are not described in that manual.

3.1.1 Reset

To reset the TMP96C141AF, the RESET

0 for at least 10 system clocks (10 states: 1 µ s with a 20MHz

system clock) within an operating voltage range and with a

stable oscillation.

When reset is accepted, the CPU sets as follows:

• Program counter (PC) to 8000H.

input must be kept at

• Stack pointer (XSP) for system mode to 100H.

• SYSM bit of status register (SR) to 1. (Sets to system mode.)

• IFF2 to 0 bits of status register to 111. (Sets mask register to

interrupt level 7.)

• MAX bit of status register to 0. (Sets to minimum mode.)

• Bits RFP2 to 0 of status register to 000. (Sets register banks

to 0.)

When reset is released, instruction execution starts from

address 8000H. CPU internal registers other than the above

are not changed.

When reset is accepted, processing for built-in I/Os,

ports, and other pins is as follows:

• Initializes built-in I/O registers as per specifications.

• Sets port pins (including pins also used as built-in I/Os) to

general-purpose input/output port mode (sets I/O ports to

input ports).

• Sets the WDTOUT pin to 0. (Watchdog timer is set to enable

after reset.)

• Pulls up the CLK pin to 1.

• Sets the ALE pin to 0.

TOSHIBA CORPORATION

7

TMP96C141AF

3.2 Memory Map

Figure 3.2 is a memory map of the TMP96C141AF.

8

Figure 3.2 Memory Map

TOSHIBA CORPORATION

TMP96C141AF

3.3 Interrupts

The TLCS-900 interrupts are controlled by the CPU interrupt

mask flip-flop (IFF2 to 0) and the built-in interrupt controller.

The TMP96C141AF have altogether the following 23

interrupt sources:

• Interrupts from the CPU

…

3

(Software interrupts, privileged violations, and Illegal (undefined) instruction execution)

• Interrupts from external pins (NMI, INT0, and INT4 to 7)

• Interrupts from built-in I/Os

…

14

sends the value of the priority of the interrupt source to the

CPU. When more than one interrupt is generated simultaneously, the interrupt controller sends the value of the highest

priority (7 for non-maskable interrupts is the highest) to the

CPU.

The CPU compares the value of the priority sent with the

value in the CPU interrupt mask register (IFF2 to 0). If the value

is greater than that of the CPU interrupt mask register, the

interrupt is accepted. The value in the CPU interrupt mask register (IFF2 to 0) can be changed using the EI instruction (contents of the EI num/IFF<2:0> = num). For example,

programming EI 3 enables acceptance of maskable interrupts

with a priority of 3 or greater, and non-maskable interrupts

which are set in the interrupt controller. The DI instruction

A fixed individual interrupt vector number is assigned to

each interrupt source; six levels of priority (variable) can also

be assigned to each maskable interrupt. Non-maskable interrupts have a fixed priority of 7.

When an interrupt is generated, the interrupt controller

…

6

(IFF<2:0> = 7) operates in the same way as the EI 7 instruction. Since the priority values for maskable interrupts are 0 to 6,

the DI instruction is used to disable maskable interrupts to be

accepted. The EI instruction becomes effective immediately

after execution. (With the TLCS-90, the EI instruction becomes

effective after execution of the subsequent instruction.)

In addition to the general-purpose interrupt processing

mode described above, there is also a high-speed micro DMA

processing mode. High-speed micro DMA is a mode used by

the CPU to automatically transfer byte or word data. It enables

the CPU to process interrupts such as data saves to built-in I/Os

at high speed.

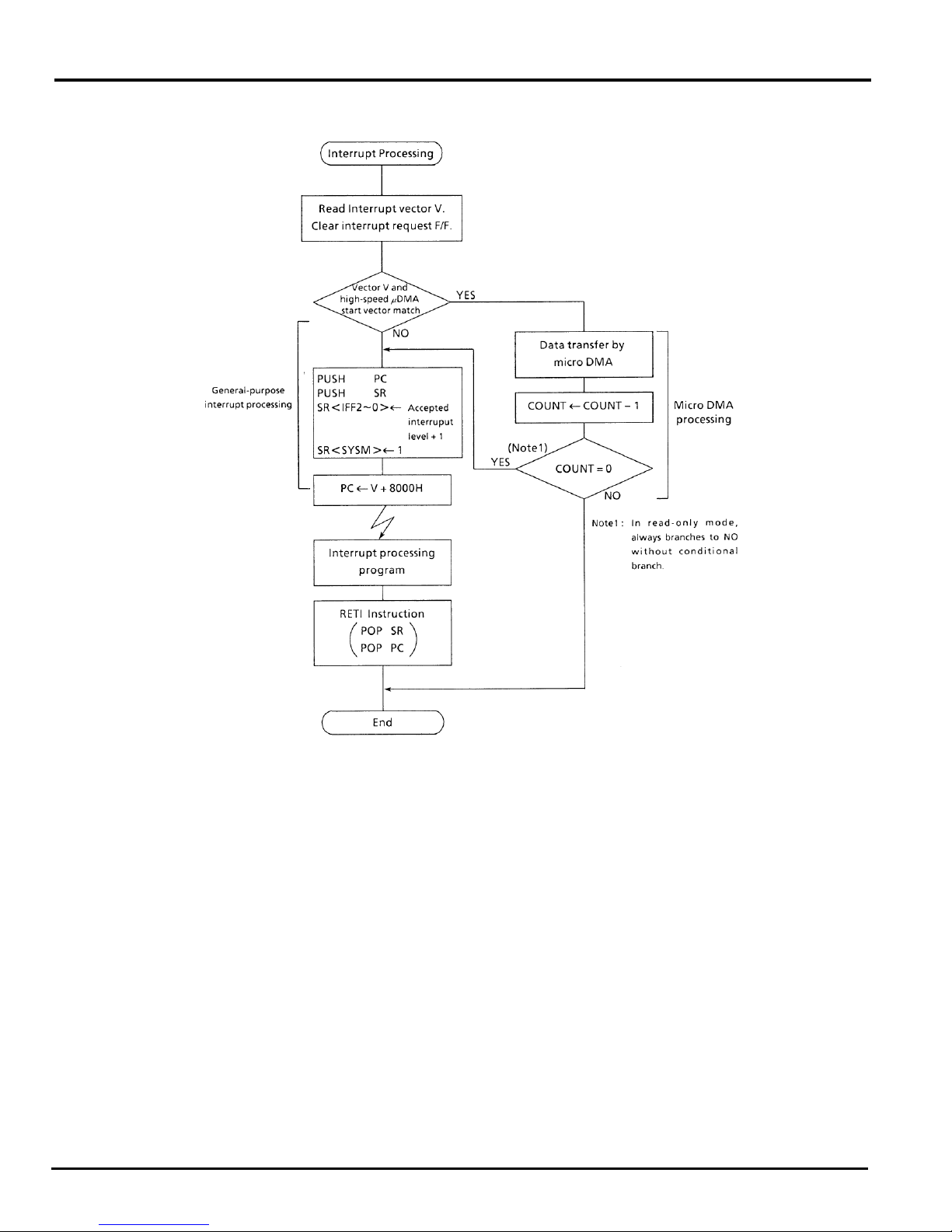

Figure 3.3 (1) is a flowchart showing overall interrupt

processing.

TOSHIBA CORPORATION

9

TMP96C141AF

Figure 3.3 (1) Interrupt Processing Flowchart

10

TOSHIBA CORPORATION

3.3.1 General-Purpose Interrupt Processing

When accepting an interrupt, the CPU operates as follows:

(1) The CPU reads the interrupt vector from the interrupt

controller. When more than one interrupt with the same

level is generated simultaneously, the interrupt controller

generates interrupt vectors in accordance with the

default priority (which is fixed as follows: the smaller the

vector value, the higher the priority), then clears the interrupt request.

(2) The CPU pushes the program counter and the status

register to the system stack area (area indicated by the

system mode stack pointer).

(3) The CPU sets a value in the CPU interrupt mask register

<IFF2 to 0> that is higher by 1 than the value of the

accepted interrupt level. However, if the value is 7, 7 is

set without an increment.

(4) The CPU sets the <SYSM> flag of the status register to 1

and enters the system mode.

(5) The CPU jumps to address 8000H + interrupt vector,

then starts the interrupt processing routine.

TMP96C141AF

Bus Width of Stack

Area

8 bit 23 19

16 bit 17 15

To return to the main routine after completion of the interrupt processing, the RETI instruction is usually used. Executing

this instruction restores the contents of the program counter

and the status registers.

Though acceptance of non-maskable interrupts cannot

be disabled by program, acceptance of maskable interrupts

can. A priority can be set for each source of maskable interrupts. The CPU accepts an interrupt request with a priority

higher than the value in the CPU mask register <IFF2 to 0>.

The CPU mask register <IFF2 to 0> is set to a value higher by

1 than the priority of the accepted interrupt. Thus, if an interrupt with a level higher than the interrupt being processed is

generated, the CPU accepts the interrupt with the higher level,

causing interrupt processing to nest. The CPU does not

accept an interrupt request of the same level as that of the

interrupt being processed.

Resetting initializes the CPU mask registers <IFF2 to 0>

to 7; therefore, maskable interrupts are disabled.

The addresses 008000H to 0081FFH (512 bytes) of the

TLCS-900 are assigned for interrupt processing entry area.

Interrupt Processing State Number

MAX mode Min mode

In minimum mode, all the above processing is completed

15 states

in (1.5

µ

s @ 20MHz). In maximum mode, it is com-

pleted in 17 states.

TOSHIBA CORPORATION

11

TMP96C141AF

Table 3.3 (1) TMP96C141AF Interrupt Table

Default Priority Type Interrupt Source

1

2 INTPREV: Privileged violation, or SWI1 0010H 8010H –

3 INTUNDEF: Illegal instruction, or SWI2 0020H 8020H –

4 SWI 3 Instruction 0030H 8030H –

5 SWI 4 Instruction 0040H 8040H –

6 SWI 5 Instruction 0050H 8050H –

7 SWI 6 Instruction 0060H 8060H –

8 SWI 7 Instruction 0070H 8070H –

9 NMI

10 INTWD: Watchdog timer 0090H 8090H 09H

11

12 INT4 pin 00B0H 80B0H 0BH

13 INT5 pin 00C0H 80C0H 0CH

14 INT6 pin 00D0H 80D0H 0DH

15 INT7 pin 00E0H 80E0H 0EH

- (Reserved) 00F0H 80F0H 0FH

16 INTT0: 8-bit timer 0 0100H 8100H 10H

17 INTT1: 8-bit timer 1 0110H 8110H 11H

18 INTT2: 8-bit timer 2/PWM0 0120H 8120H 12H

19 INTT3: 8-bit timer 3/PWM1 0130H 8130H 13H

20 INTTR4: 16-bit timer 4 (TREG4) 0140H 8140H 14H

21 INTTR5: 16-bit timer 4 (TREG5) 0150H 8150H 15H

22 INTTR6: 16-bit timer 5 (TREG6) 0160H 8160H 16H

23 INTTR7: 16-bit timer 5 (TREG7) 0170H 8170H 17H

24 INTRX0: Serial receive (Channel.0) 0180H 8180H 18H

25 INTTX0: Serial send (Channel.0) 0190H 8190H 19H

26 INTRX1: Serial receive (Channel.1) 01A0H 81A0H 1AH

27 INTTX1: Serial send (Channel.1) 01B0H 81B0H 1BH

28 INTAD: A / D conversion completion 0 1 C 0 H 81C0H 1CH

– (Reserved) 01D0H 81D0H 1DH

– (Reserved) 01E0H 81E0H 1EH

– (Reserved) 01F0H 81F0H 1FH

Non-

Maskable

Maskable

Reset , or SW10 instruction 0000H 8000H –

Pin 0080H 8080H 08H

INTO pin 00A0H 80A0H 0AH

Vector Value

“V”

Start Address

High-Speed

Micro DMA

Start Vector

3.3.2 High-Speed Micro DMA

In addition to the conventional interrupt processing, the TLCS900 also has a high-speed micro DMA function. When an

interrupt is accepted, in addition to an interrupt vector, the CPU

receives data indicating whether processing is high-speed micro

DMA mode or general-purpose interrupt. If high-speed micro

DMA mode is requested, the CPU performs high-speed micro

DMA processing.

12

The TLCS-900 can process at very high speed compared with the TLCS-90 micro DMA because it has transfer

parameters in dedicated registers in the CPU. Since those

dedicated registers are assigned as CPU control registers, they

can only be accessed by the LDC (privileged) instruction.

TOSHIBA CORPORATION

TMP96C141AF

(1) High-Speed Micro DMA Operation

High-speed micro DMA operation starts when the accepted

interrupt vector value matches the micro DMA start vector

value set in the interrupt controller. The high-speed micro DMA

has four channels so that it can be set for up to four types of

interrupt source.

When a high-speed micro DMA interrupt is accepted,

data is automatically transferred from the transfer source

address to the transfer destination address set in the control

register, and the transfer counter is decremented. If the value in

the counter after decrementing is other than 0, high-speed

micro DMA processing is completed. If the value in the counter

after decrementing is 0, general-purpose interrupt processing

is performed. In read-only mode, which is provided for DRAM

refresh, the value in the counter is ignored and dummy read is

repeated.

The 32-bit control registers are used for setting transfer

source/destination addresses. However, the TLCS-900 has

only 24 address pins for output. A 16M-byte space is available

for the high-speed micro DMA. Also in normal mode operation,

the all address space (in other words, the space for system

mode which is set by the CS/WAIT controller) can be

accessed by high-speed micro DMA processing.

There are two data transfer modes: one-byte mode and

one-word mode. Incrementing, decrementing, and fixing the

transfer source/destination address after transfer can be done

in both modes. Therefore data can easily be transferred

betweenI/O and memory and between I/Os. For details of

transfer modes, see the description of transfer mode registers.

The transfer counter has 16 bits, so up to 65536 transfers (the maximum when the initial value of the transfer counter

is 0000H) can be performed for one interrupt source by highspeed micro DMA processing.

A the data transferred by the µ DMA function, the transfer

nter was decreased.

When this counter is “0”H, the processor operates general interrupt processing. At this time if the same channel of

interrupt is required next interrupt, the transfer counter starts

from 65536.

Interrupt sources processed by high-speed micro DMA

processing are those with the high-speed micro DMA start

vectors listed in Table 3.3 (1).

TOSHIBA CORPORATION

13

TMP96C141AF

The following timing chart is a high-speed µ DMA cycle of

the Transfer Address Increment mode (the other mode exe-

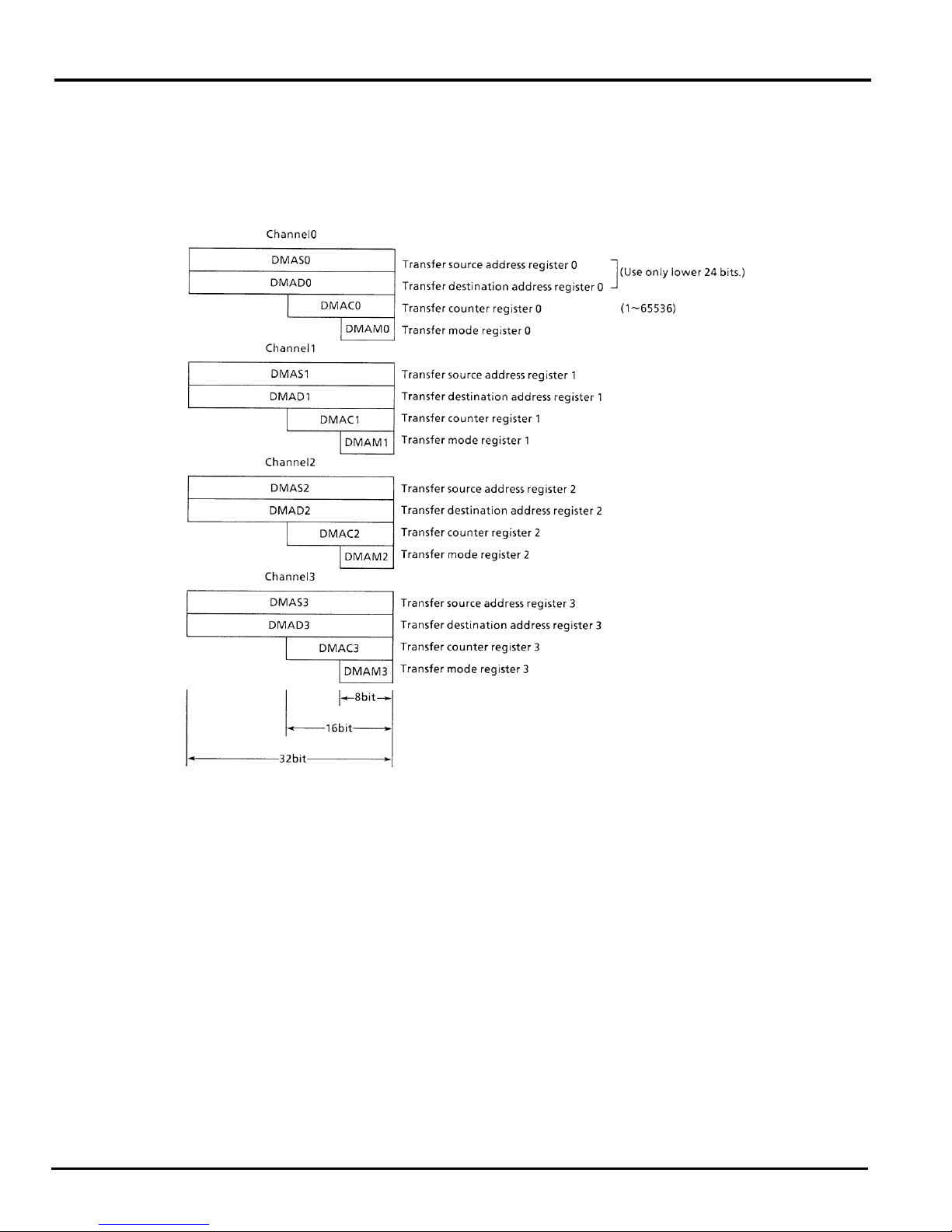

(2) Register Configuration (CPU Control Register)

cept the Read-only mode is same as this)

(Condition: MIN mode, 16bit Bus width for 16M Byte, 0 wait)

These Control Registers cannot be set only “LCD cr, r” instruction.

14

TOSHIBA CORPORATION

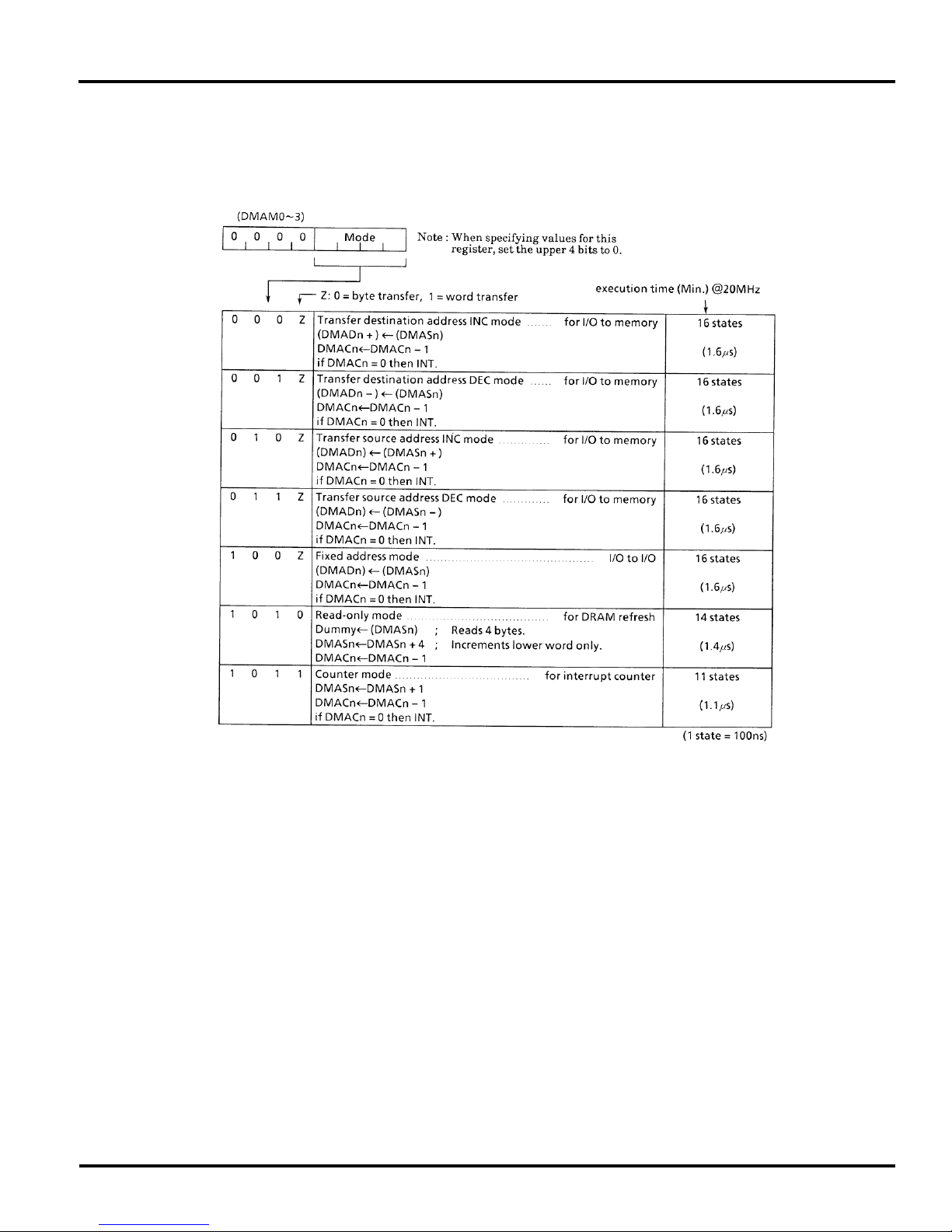

(3) Transfer Mode Register Details

TMP96C141AF

This condition is 16-bit bus width and 0 wait of source/destination address space.

Note: n: corresponds to high-speed µ DMA channels 0 - 3.

DMADn +/DMASn + : Post-increment (Increments register value after transfer.)

DMADn -/DMASn - : Post-decrement (Decrement register value after transfer.)

All address space (the space for system mode) can be

accessed by high-speed µ DMA. Do not use undefined codes

TOSHIBA CORPORATION

for transfer mode control.

15

TMP96C141AF

➀

➁

➂

<Usage of read only mode (DRAM refresh)>

When the hardware configuration is as follows:

DRAM mapping size: = 1MB

DRAM data bus size: = 8 bits

DRAM mapping address range: = 100000H to

1FFFFFH

Set the following registers first; refresh is performed

automatically.

Register initial value setting

LD XIX, 100000H

LDC DMAS0,XIX

LD A, 00001010B

LDC DMAM0, A

…

mapping start address

…

read only mode (for

DRAM refresh)

Timer Setting

Set the timers so that interrupts are generated at

intervals of 62.5 µ s or less.

Interrupt controller setting

Set the timer interrupt mask h other interrupt mask.

Write the above timer interrupt vector value in the

High-Speed µ DMA start vector register, DMA0V.

(Operation description)

The DRAM data bus is an 8-bit bus and the micro

DMA is in read-only mode (4 bytes), so refresh is performed four times per interrupt.

When a 512 refresh/8ms DRAM is connected, DRAM

refresh is performed sufficiently if the micro DMA is

started every 15.625 µ s x 4 = 62.4 µ s or less, since the

timing is 15.625 µ s/refresh.

(Overhead)

Each processing time by the micro DMA is 1.8 µ s (18

states) @ 20MHz with an 8-bit data bus.

In the above example, the micro DMA is started every

62.5 µ s, 1.8 µ s/62.5 µ s = 0.029; thus, the overhead is

2.9%.

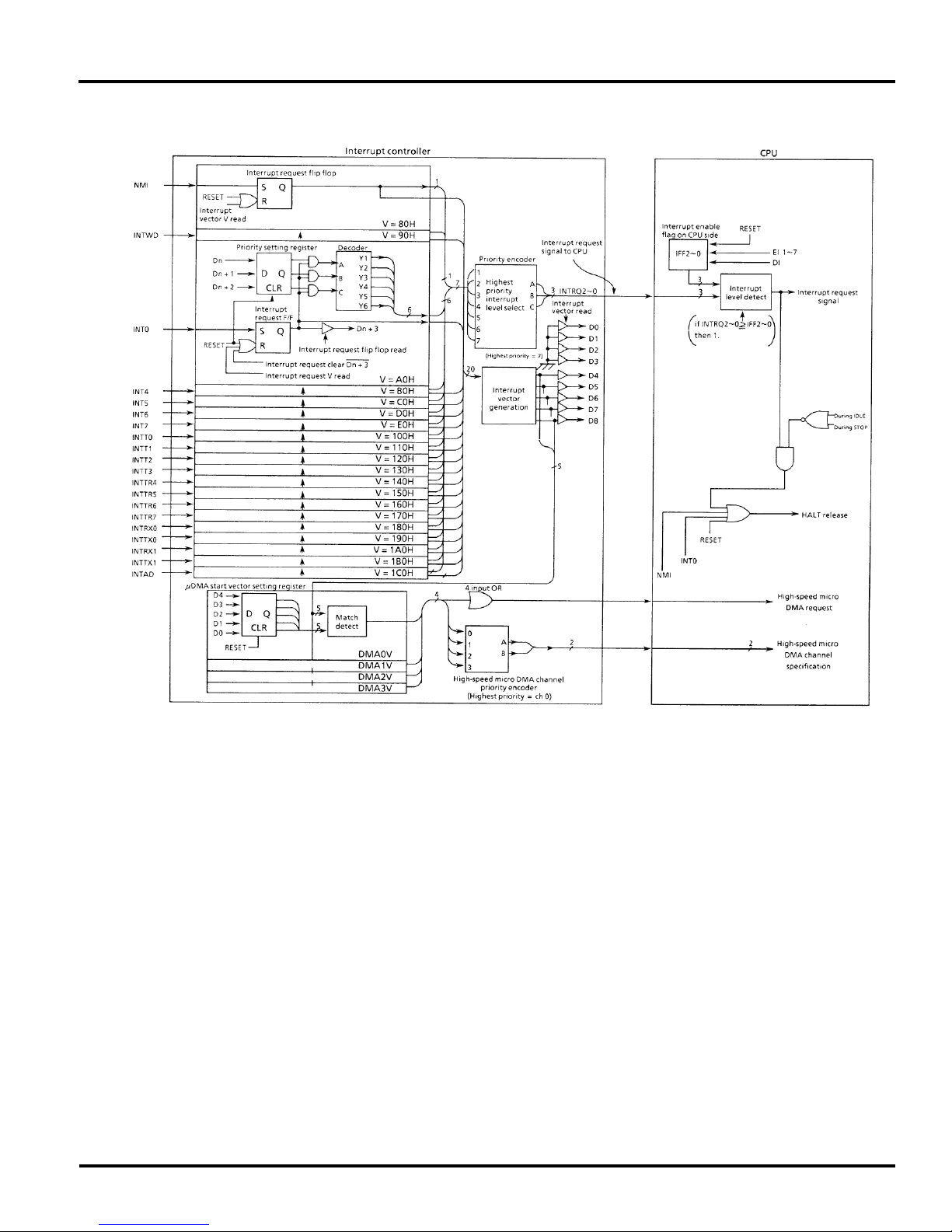

3.3.3 Interrupt Controller

Figure 3.3.3 (1) is a block diagram of the interrupt circuits. The

left half of the diagram shows the interrupt controller; the right

half includes the CPU interrupt request signal circuit and the

HALT release signal circuit.

Each interrupt channel (total of 20 channels) in the inter-

rupt controller has an interrupt request flip-flop, interrupt prior-

ity setting register, and a register for storing the high-speed

micro DMA start vector. The interrupt request flip-flop is used

to latch interrupt requests from peripheral devices. The flip-flop

is cleared to 0 at reset, when the CPU reads the interrupt

channel vector after the acceptance of interrupt, or when the

CPU executes an instruction that clears the interrupt of that

channel (writes 0 in the clear bit of the interrupt priority setting

register).

For example, to clear the INT0 interrupt request, set the

register after the as follows.

DI instruction

INTE0AD ← ---- 0 --- Zero-clears the INT0 Flip-Flop.

The status of the interrupt request flip-flop is detected by

reading the clear bit. Detects whether there is an interrupt

request for an interrupt channel.

The interrupt priority can be set by writing the priority in

the interrupt priority setting register (e.g., INTE0AD, INTE45,

etc.) provided for each interrupt source. Interrupt levels to be

set are from 1 to 6. Writing 0 or 7 as the interrupt priority disables the corresponding interrupt request. The priority of the

non-maskable interrupt (NMI

pin, watchdog timer, etc.) is fixed

to 7. If interrupt requests with the same interrupt level are generated simultaneously, interrupts are accepted in accordance

with the default priority (the smaller the vector value, the higher

the priority).

The interrupt controller sends the interrupt request with

the highest priority among the simultaneous interrupts and its

vector address to the CPU. The CPU compares the priority

value <IFF2 to 0> set in the Status Register by the interrupt

request signal with the priority value sent; if the latter is higher,

the interrupt is accepted. Then the CPU sets a value higher

than the priority value by 1 in the CPU SR<IFF2 to 0>. Interrupt

requests where the priority value equals or is higher than the

set value are accepted simultaneously during the previous

interrupt routine. When interrupt processing is completed (after

execution of the RETI instruction), the CPU restores the priority

value saved in the stack before the interrupt was generated to

the CPU SR<IFF2 to 0>.

The interrupt controller also has four registers used to

store the high-speed micro other DMA start vector. These are I/

O registers; unlike other DMA registers (DMAS, DMAD, DMAM,

and DMAC), they can be accessed in either normal or system

mode. Writing the start vector of the interrupt source for the

micro DMA processing (see Table 3.3 (1)), enables the corresponding interrupt to be processed by micro DMA processing.

The values must be set in the micro DMA parameter registers

(e.g., DMAS and DMAD) prior to the micro DMA processing.

16

TOSHIBA CORPORATION

TMP96C141AF

TOSHIBA CORPORATION

Figure 3.3.3 (1) Block Diagram of Interrupt Controller

17

TMP96C141AF

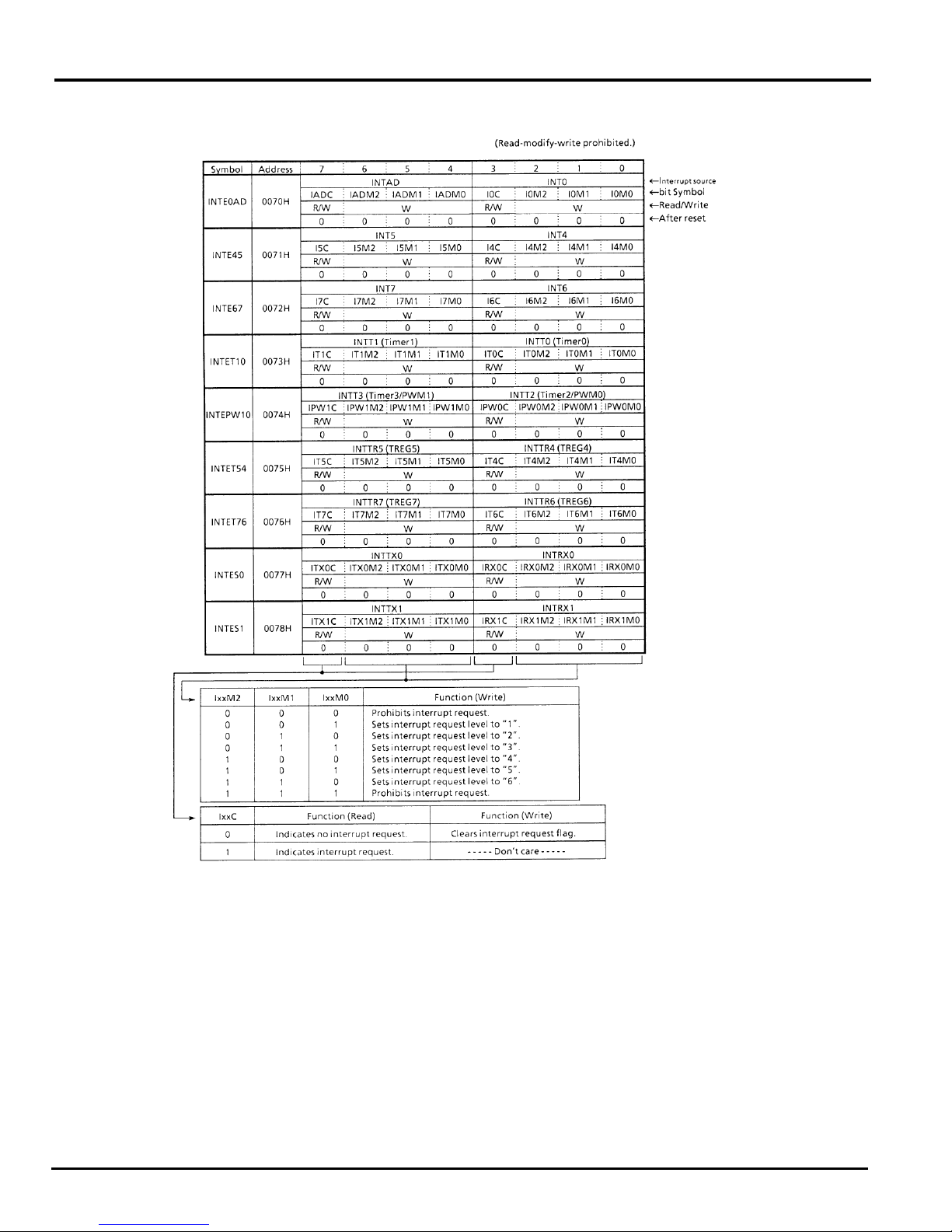

(1) Interrupt Priority Setting Register

18

TOSHIBA CORPORATION

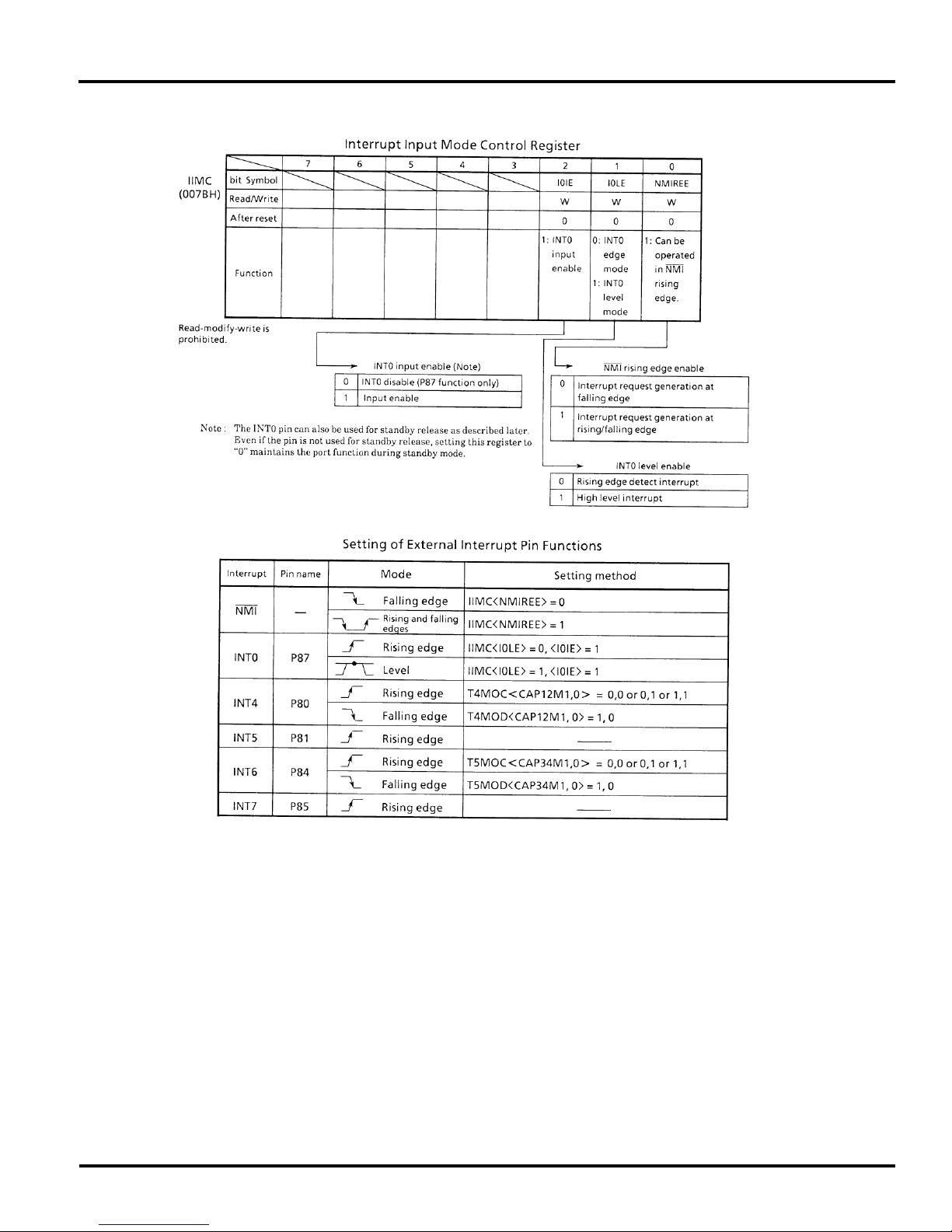

(2) External Interrupt Control

TMP96C141AF

TOSHIBA CORPORATION

19

TMP96C141AF

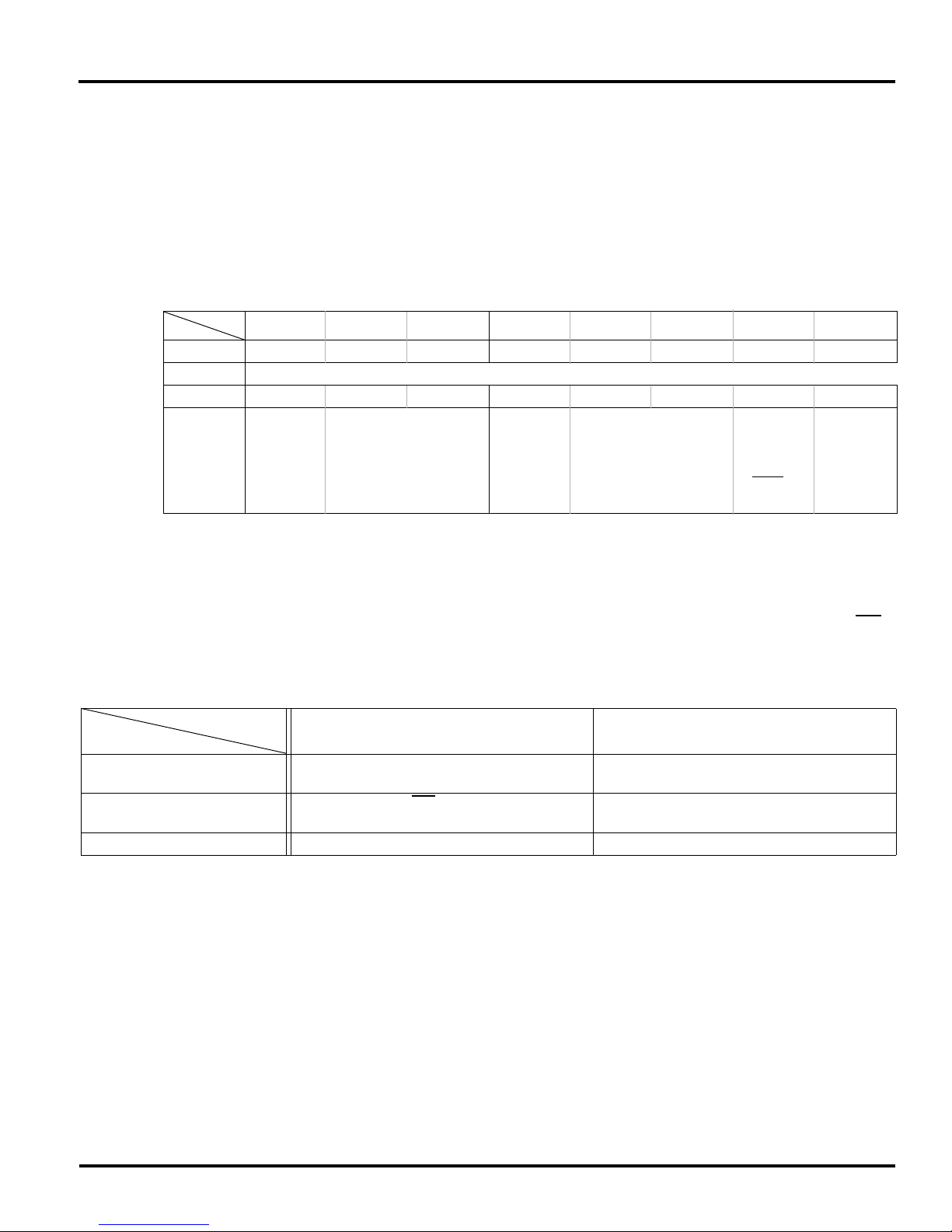

(3) High-Speed Micro DMA Start Vector

When the CPU reads the interrupt vector after accepting an interrupt, it simultaneously compares the interrupt vector with each

channel’s micro DMA start vector (bits 4 to 8 of the interrupt vec-

Micro DMA0 Start Vector

76543210

DMA0V

(007CH)

bit Symbol DMA0V8 DMA0V7 DMA0V6 DMA0V5 DMA0V4

Read / Write W

After reset 00000

Micro DMA1 Start Vector

76543210

DMA1V

(007DH)

bit Symbol DMA1V8 DMA1V7 DMA1V6 DMA1V5 DMA1V4

Read / Write W

After reset 00000

Micro DMA2 Start Vector

76543210

DMA2V

(007EH)

bit Symbol DMA2V8 DMA2V7 DMA2V6 DMA2V5 DMA2V4

Read / Write W

After reset 00000

Micro DMA3 Start Vector

76543210

DMA3V

(007FH)

bit Symbol DMA3V8 DMA3V7 DMA3V6 DMA3V5 DMA3V4

Read / Write W

After reset 00000

tor). When both match, the interrupt is processed in micro

DMA mode for the channel whose value matched.

If the interrupt vector matches more than one channel, the channel with the lower channel number has a

higher priority.

(read-modify-write is not possible.)

(read-modify-write is not possible.)

(read-modify-write is not possible.)

(read-modify-write is not possible.)

(4) Notes

The instruction execution unit and the bus interface unit of this

CPU operate independently of each other. Therefore, if the instruction used to clear an interrupt request flag of an interrupt is fetched

before the interrupt is generated, it is possible that the CPU might

execute the fetched instruction to clear the interrupt request flag

20

while reading the interrupt vector after accepting the interrupt. If so, the CPU would read the default vector 00A0H

and start the interrupt processing from the address

80A0H.

To avoid this, make sure that the instruction used to

clear the interrupt request flag comes after the DI instruction.

TOSHIBA CORPORATION

TMP96C141AF

≤

3.4 Standby Function

When the HALT instruction is executed, the TMP96C141AF

enters RUN, IDLE, or STOP mode depending on the contents

of the HALT mode setting register.

(1) RUN : Only the CPU halts; power consumption

remains unchanged.

(2) IDLE : Only the built-in oscillator operates, while all

76543210

WDMOD

(005CH)

Bit Symbol WDTE WDTP1 WDTP0 WARM HALTM1 HALTM0 RESCR DRVE

Read/Write R/W

After reset 10000000

1 : WDT

Enable

Function

16

00 : 2

/ fc

18

01 : 2

/ fc

20

10 : 2

/ fc

22

11 : 2

/ fc

Detection time

other built-in circuits halt. Power consumption is reduced to 1/10 or less than that during normal operation.

(3) STOP : All internal circuits including the built-in oscil-

lator halt. This greatly reduces power consumption. The states of the port pins in

STOP mode can be set as listed in Table 3.4

(1) using the I/O register

WDMOD<DRVE>bit.

Warming up

time

16

0 : 2

/fc

18

1 : 2

/fc

Standby mode

00 : RUN mode

01 : STOP mode

10 : IDLE mode

11 : Don’t care

1: Connects

watchdog

timer

output to

RESET

pin

internally.

1: Drive pin

even in

STOP

mode.

When STOP mode is released by other than a reset, the

system clock output starts after allowing some time for warming up set by the warming-up counter fro stabilizing the bulit-in

oscillator. To release STOP mode by reset, it is necessary to

Standby Release by Interrupt

Standby Mode

Interrupt Level

Can be released by any interrupt.

RUN

IDLE Can only be released by NMI

STOP ↑ (Note) ↑

After standby mode is released, interrupt processing starts.

is released, interrupt processing starts.

Interrupt Mask (IFF2 to 0)

Interrupt Request Level

or INT0 pin. After standby mode

allow the oscillator to stabilize.

To release standby mode, a reset or an interrupt is used.

To release IDLE or STOP mode, only an interrupt by the NMI or

INT0 pin, or a reset can be used. The details are described

below:

Interrupt Mask (IFF2 to 0)

> Interrupt Request Level

Can only be released by INT0 pin.

Processing resumes from address next to HALT instruction.

↑

TOSHIBA CORPORATION

21

TMP96C141AF

Table 3. 4 (1) Pin States in STOP Mode

Pin Name I/O

96C141AF 96CM40/96PM40

DRVE = 0 DRVE = 1 DRVE = 0 DRVE = 1

P0

P1

P2

P30 (RD

), P31 (WR) Output – “1” Output – Output

P32 ~ P37

P40, P41

P42 (CS2

/CAS2)

Input mode/AD0 ~ 7

Output mode

Input mode/AD8 ~ 15

Output mode/A8 ~ 15

Input mode

Output mode/A0 ~ 7, A16 ~ 23

Input mode

Output mode

Input mode

Output mode

Input mode

Output mode

–

x

–

x

PD*

PD*

PU

PU

PU*

PU*

PD*

PD*

–

x

–

x

PD*

Output

PU

Output

PU

Output

PD

Output

–

–

–

–

PD*

PD*

P5 Input – –

P6

P7

P80 ~ P86

P87 (INT0)

P9

NMI

WDTOUT

Input mode

Output mode

Input mode

Output mode

Input mode

Output mode

Input mode

Output mode

Input mode

Output mode

Input Input Input

Output Output Output

PU*

PU*

PU*

PU*

PU*

PU*

PU

PU

PU*

PU*

PU

Output

PU

Output

PU

Output

PU

Output

PU

Output

ALE Output “0” “0”

CLK Output – “1”

RESET

EA

Input Input Input

Input Input Input

X1 Input – –

X2 Output “1” “1”

–

Output

–

Output

PD*

Output

←

–: Input for input mode/input pin is invalid; output mode/output pin is at high impedance.

Input: Input enable state

Input: Input gate in operation. Fix input voltage to 0 or 1 so that input pin stays constant.

Output: Output state

PU: Programmable pull-up pin. Fix the pin to avoid through current since the input gate operates when a pull-up resistor is not set.

PD: Programmable pull-down pin. Fix the pin like a pull-up pin when a pull-down resistor is not set.

*: Input gate disable state. No through current even if the pin is set to high impedance.

x: Cannot set.

Note: Port registers are used for controlling programmable pull-up/pull-down. If a pin is also used for an output function (e.g., TO1) and the output function

is specified, whether pull-up or pull-down is selected depends on the output function data. If a pin is also used for an input function, whether pull-up or

pull-down is selected depends on the port register setting value only.

22 TOSHIBA CORPORATION

TMP96C141AF

3.5 Functions of Ports

The TMP96CM40F/TMP96PM40F has 65 bits for I/O ports.

The TMP96C141AF, TMP96C041AF has 47 bits for I/O ports

because Port0, Port1, P30, and P31 are dedicated pins for

AD0 to 7, AD8 to

15, RD, and WR.

These port pins have I/O functions for the built-in CPU

and internal I/Os as well as general-purpose I/O port functions. Table 3.5 lists the function of each port pin.

(R: ↑ = With programmable pull-up resistor

↓ = WIth programmable pull-down

Table 3.5 Functions of Ports

Port Name Pin Name

Port0 P00 ~ P07 8 I/O – Bit AD0 ~ AD7

Port1 P10 ~ P17 8 I/O

Port2 P20 ~ P27 8 I/O ↓ Bit A0 ~ A7/ A16 ~ A23

Port 3 P30

P31

P32

P33

P34

P35

P36

P37

Port4 P40

P41

P42

Port5 P50 ~ P53 4 Input – (Fixed) AN0 ~ AN3

Port6 P60 ~ P67 8 I/O ↑ Bit PG00 ~ PG03, PG10 ~ PG13

Port7 P70

P71

P72

P73

Port8 P80

P81

P82

P83

P84

P85

P86

P87

Port9 P90

P91

P92

P93

P94

P95

Number of

Pins

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Direction R Direction Setting Unit Pin Name for Built-in Function

– Bit AD8 ~ AD15/ A8 ~ A15

Output

Output

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

–

–

↑

↑

↑

↑

↑

↑

↑

↑

↓

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

(Fixed)

(Fixed)

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

Bit

RD

WR

HWR

WAIT

BUSRQ

BUSAK

R/W

RAS

CS0 / CAS0

CS1 / CAS1

CS2 / CAS2

T10

TO1

TO2

TO3

T14/INT4

T15/INT5

TO4

TO5

T16 / INT6

T17 / INT7

TO6

INT0

TXD0

RXD0

CTS0

TXD1

RXD1

SCLK1

TOSHIBA CORPORATION 23

TMP96C141AF

Resetting makes the port pins listed below function as

general-purpose I/O ports.

I/O pins programmable for input or output function as

input ports.

To set port pins for built-in functions, a program is

required.

Since the TMP96C141AF has an external ROM, some

ports are permanently assigned to the CPU.

Pin Name

P00 - P07

(AD0 - AD7)

P10 - P17

(AD8 - AD15)

P30 (RD

)

P31 (WR

)

P32 (HWR

P37 (RAS

P36 (R/W

P40 (CS0

P41 (CS1

P42 (CS2

P20 - P27

(A16 - A23)

P42 (CS2

)

) ↑

)

/CAS0)

/CAS1)

/CAS2) ↑ (*) ↑

/CAS2)

No status change (these pins are not “Hz”) These pins are “Hz”.

• P00 ~ P07 →AD0 ~ AD7

• P10 ~ P17 →AD8 ~ AD15

• P30 →RD

• P31 →WR

Bus release function

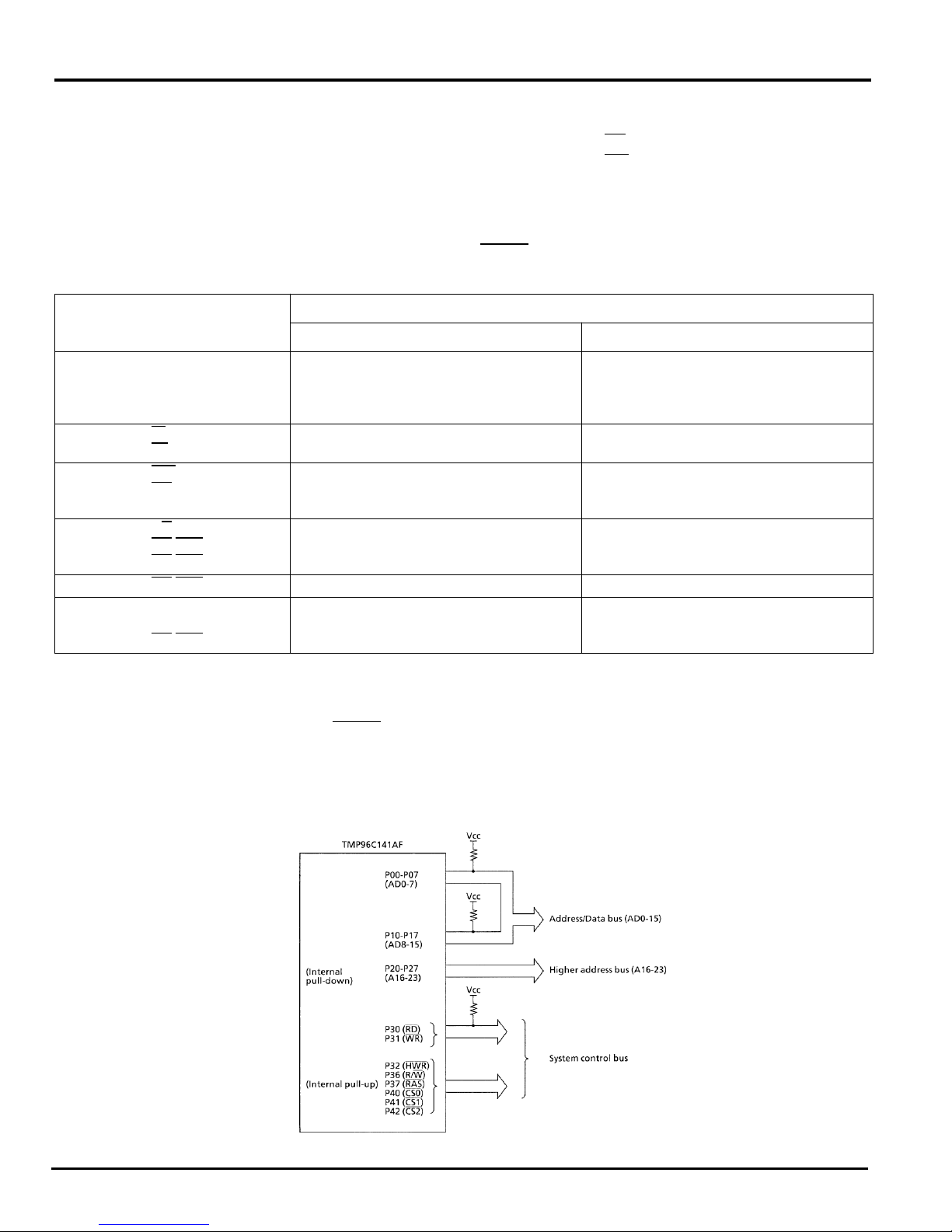

The TMP96C141AF has the internal pull-up and pull-

down resistors to fix the bus control signals at bus release.

Table 3.5 (1) shows the pin condition at bus release

(BUSAK) = “L”).

Pin state at bus release

Port mode Function mode

↑

↑↑

↑

These pins are “Hz”.

(“Hz” status after these pins are driven to high level.)

The output buffer is “OFF” after these pins are drinen high.

These pins are added in the internal resistor of pull-up. It’s

no relation for the value of output latch.

The output buffer is “OFF” after these pins are drinen high.

These pins are added in the internal resistor of pull-down.

It’s no relation for the value of output latch.

(*) P42 has the resistor of programmable pull-down, but

when the bus are released, P42 pin is added a resistor of pullup.

That is, when it is used for bus release (BUSAK = “0”), the

pins of below need pull-up or pull-down resistor for an external

circuit.

P00 - P07 (AD07)

P10 - P17 (AD8 - AD15)

P30 (RD)

P31 (WR)

When the bus is released, both internal memory and

internal I/O cannot be accessed. But the internal I/O continues

to run. Therefore, be careful about releasing time and set the

setection time WDT.

Figure 3.5. Example of external bus interface using bus release function.

24 TOSHIBA CORPORATION

TMP96C141AF

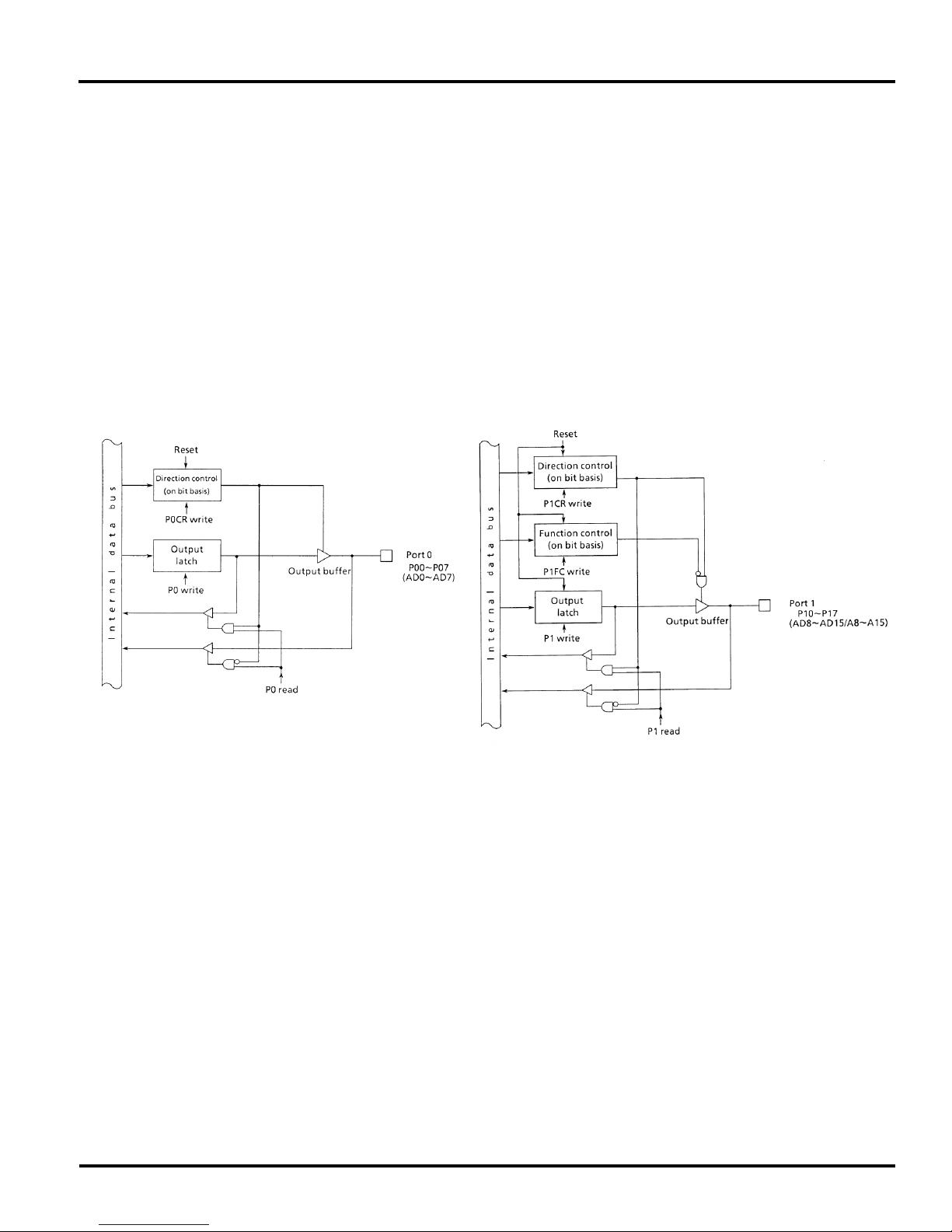

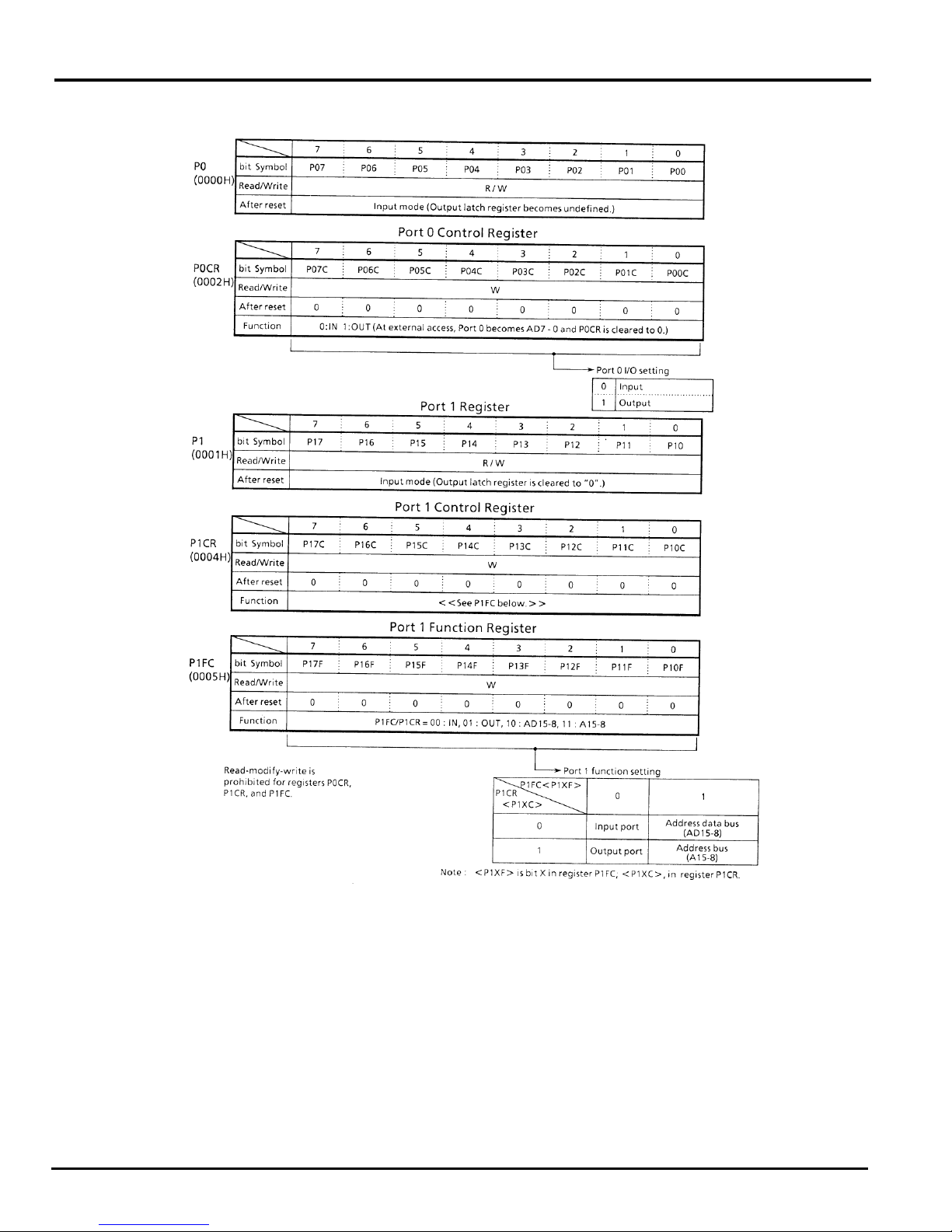

3.5.1 Port 0 (P00 - P07)

Port 0 is an 8-bit general-purpose I/O port. I/O can be set on a

bit basis using control register P0CR to 0 and sets Port 0 to

input mode.

In addition to functioning as a general purpose I/O port,

Port 0 also functions as an address data bus (AD0 to 7). To

access external memory, Port 0 functions as an address data

bus (AD 0 to 7) and all bits of the control register P0CR are

cleared to 0.

With the TMP96C141AF/TMP96C041AF, which comes

with an external ROM, Port 0 always functions as an address

data bus (AD0 to 7) regardless of the value set in control register P0CR.

3.5.2 Port 1 (P10 - P17)

Port 1 is an 8-bit general-purpose I/O port. I/O can be set on a

bit basis using control register P1CR and function register

P1FC. Resetting resets all bits of output latch P1, control register P1CR, and function register P1FC to 0 and sets Port 1 to

input mode.

In addition to functioning as a general purpose I/O port,

Port 1 also functions as an address data bus (AD8 to 15) or an

address bus (A8 to 15).

With the TMP96C141AF/TMP96C041AF, which comes

with an external ROM, Port 1 always functions as an address

data bus (AD8 to 15) regardless of the value set in control register P1CR.

Figure 3.5 (1). Port 0 Figure 3.5 (2). Port 1

TOSHIBA CORPORATION

25

TMP96C141AF

Port 0 Register

Figure 3.5 (3). Registers for Ports 0 and 1

26

TOSHIBA CORPORATION

TMP96C141AF

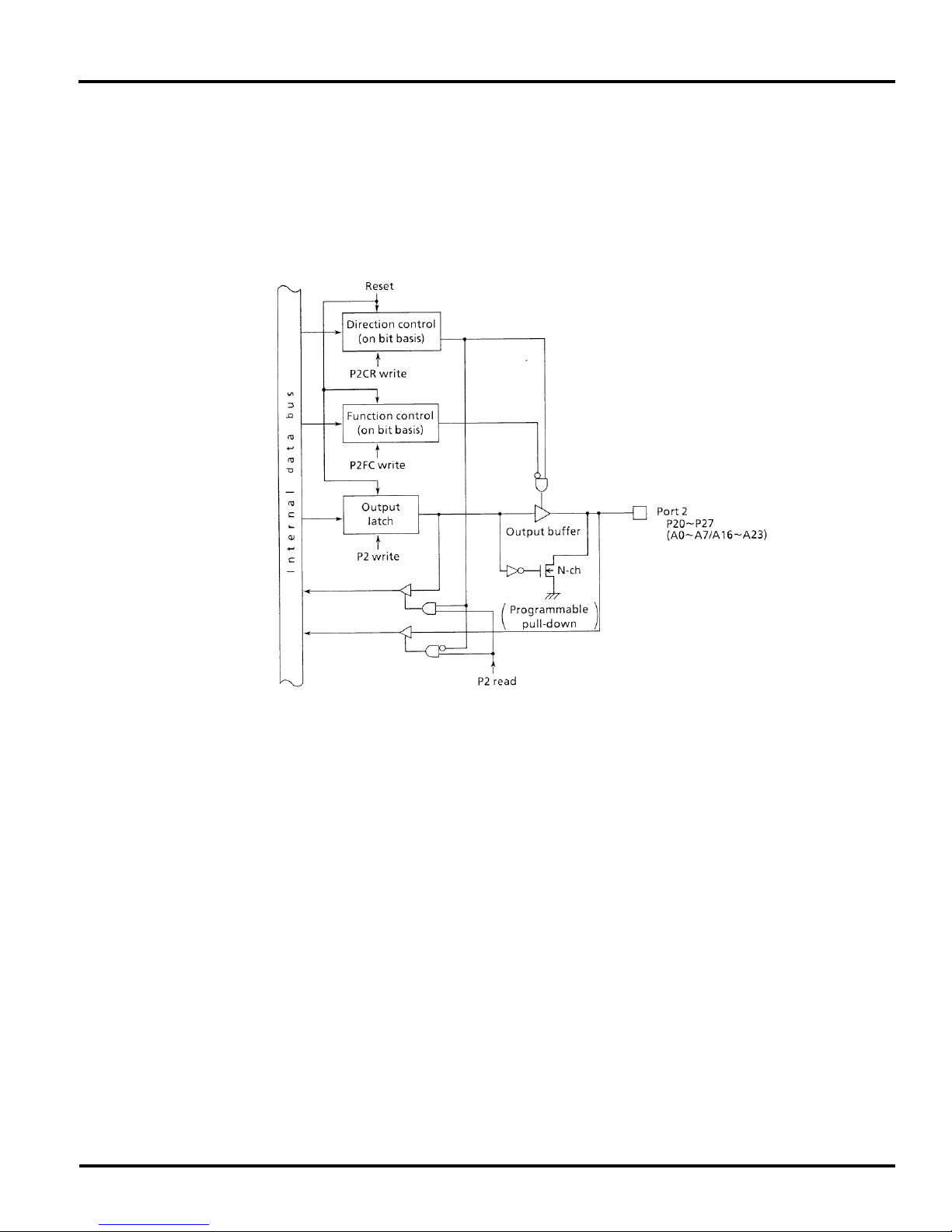

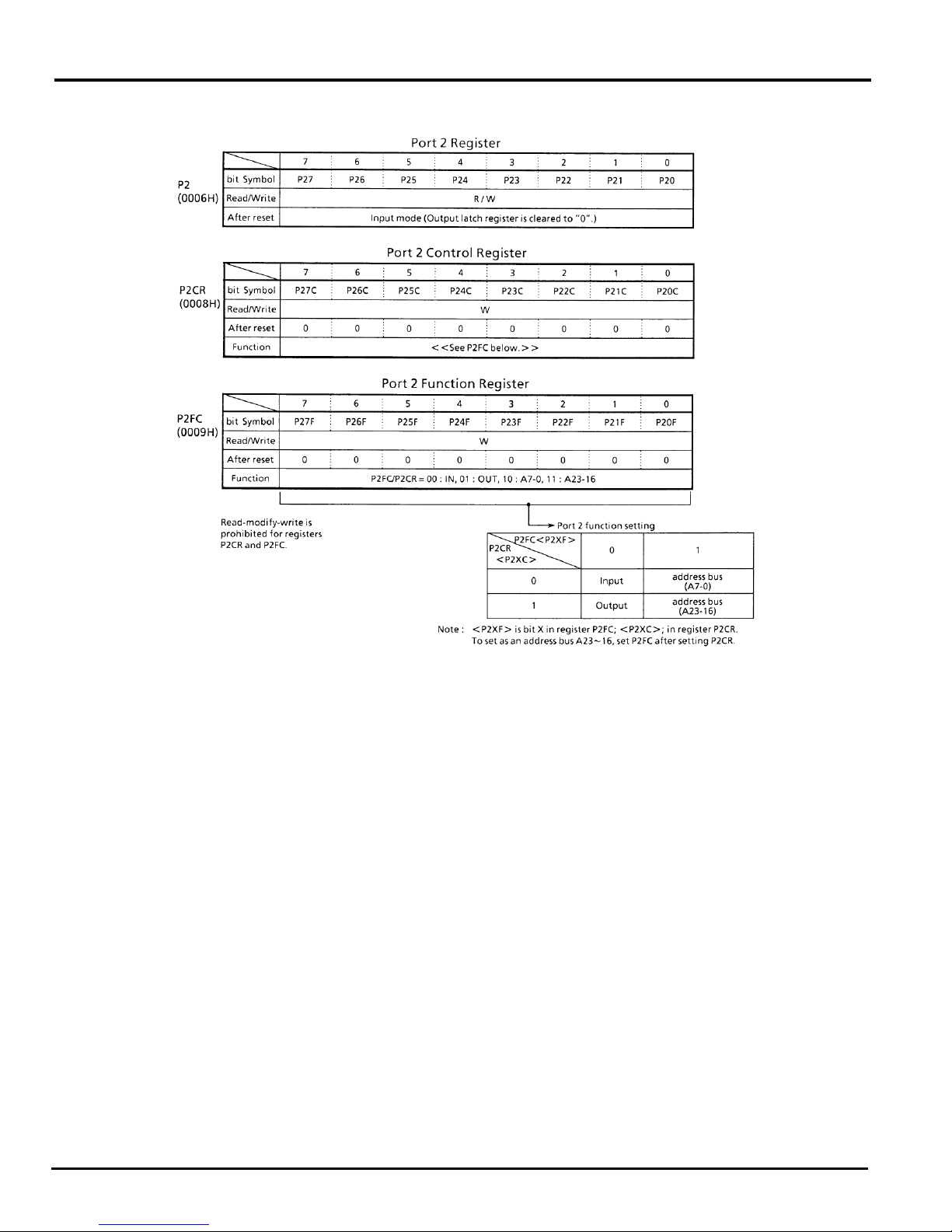

3.5.3 Port 2 (P20 - P27)

Port 2 is an 8-bit general-purpose I/O port. I/O can be set on

bit basis using the control register P2CR and function register

P2FC. Resetting resets all bits of output latch P2, control register P2CR and function register P2FC to 0. It also sets Port 2 to

input mode and connects a pull-down resistor. To disconnect

the pull-down resistor, write 1 in the output latch.

In addition to functioning as a general-purpose I/O port,

Port 2 also functions as an address data bus (A0 to 7) and an

address bus (A16 to 23).

TOSHIBA CORPORATION

Figure 3.5 (4). Port 2

27

TMP96C141AF

28

Figure 3.5 (5). Registers for Port 2

TOSHIBA CORPORATION

TMP96C141AF

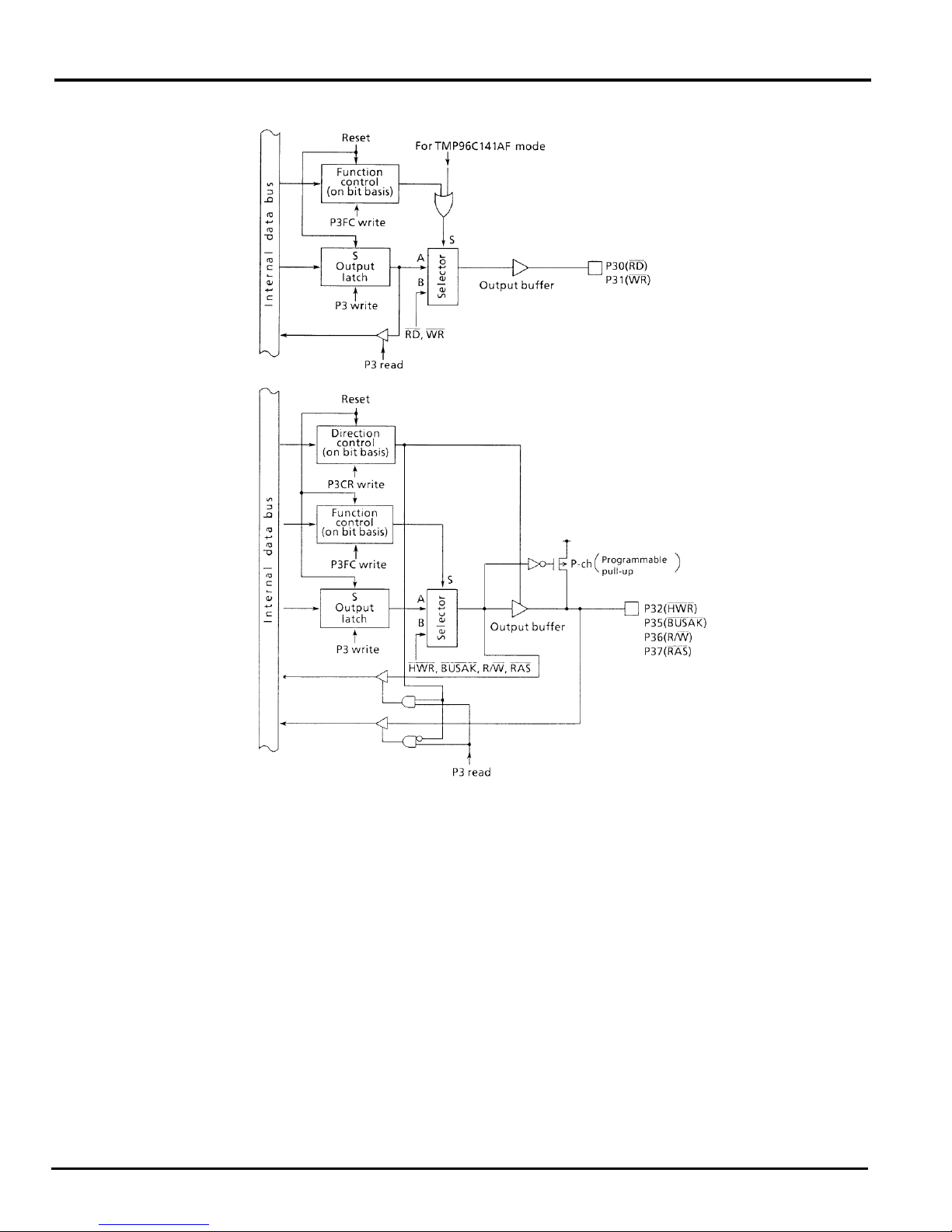

3.5.4 Port 3 (P30 - P37)

Port 3 is an 8-bit general-purpose I/O port.

I/O can be set on a bit basis, but note that P30 and P31

are used for output only. I/O is set using control register P3CR

and function register P3FC. Resetting resets all bits of output

latch P3, control register P3CR (bits 0 and 1 are unused), and

function register P3FC to 0. Resetting also outputs 1 from P30

and P31, sets P32 to P37 to input mode, and connects a pullup resistor.

In addition to functioning as a general-purpose I/O port,

Port 3 also functions as an I/O for the CPU’s control/status signal.

With the TMP96C141AF, when P30 pin is defined as RD

signal output mode (<P30F> = 1), clearing the output latch

register <P30> to 0 outputs the RD strobe (used for the

pseudo static RAM) from the P30 pin even when the internal

address area is accessed.

If the output latch register <P30> remains 1, the RD

strobe signal is output only when the external address area is

accessed.

With the TMP96C141AF/TMP96C041AF, which comes

with an external ROM, Port 30 outputs the RD signal; P31, the

WR signal, regardless of the values set in function registers

P30F and P31F.

TOSHIBA CORPORATION

29

TMP96C141AF

Figure 3.5 (6). Port 3 (P30, P31, P32, P35, P36, P37)

30

TOSHIBA CORPORATION

Loading...

Loading...