Page 1

東芝 オリジナル CMOS 16ビット マイクロコントローラ

TLCS-900/L1 シリーズ

TMP91C025

セミコンダクター社

Page 2

はじめに

この度は弊社 16 ビットマイクロコントローラ TLCS-900/L1 シリーズ、

TMP91C025をご利用いただき、誠にありがとうございます。

本 LSI をご利用になる前に、「使用上の注意、制限事項」の章を参照されます

ことをお願いいたします。

特に下記に示す注意事項に関しましては、十分にご注意願います。

ホルト状態からの解除に関する注意事項

通常は、割り込みによってホルト状態を解除することができますが、HALT モ

ードが IDLE1、STOP モードに設定されている状態 (IDLE2 は対象外) で、CPU

が HALTモードに移行しようとしている期間(f

約 5 クロックの間)に、HALT

FPH

モードを解除可能な割り込み (INT0~INT3, INTRTC, INTALM0~INTALM4,

INTKEY) が入力されても、ホルトが解除できない場合があります (割り込み要求

は内部に保留されます)。

HALT モードへ完全に移行された後に、再度割り込みが発生すれば、問題なく

HALT モードを解除できますが、割り込み処理は内部に保留された割り込みと現

在の割り込みを比較し、その優先順位に従って順次処理されます。

Page 3

ご

機

低電圧/低消費電力

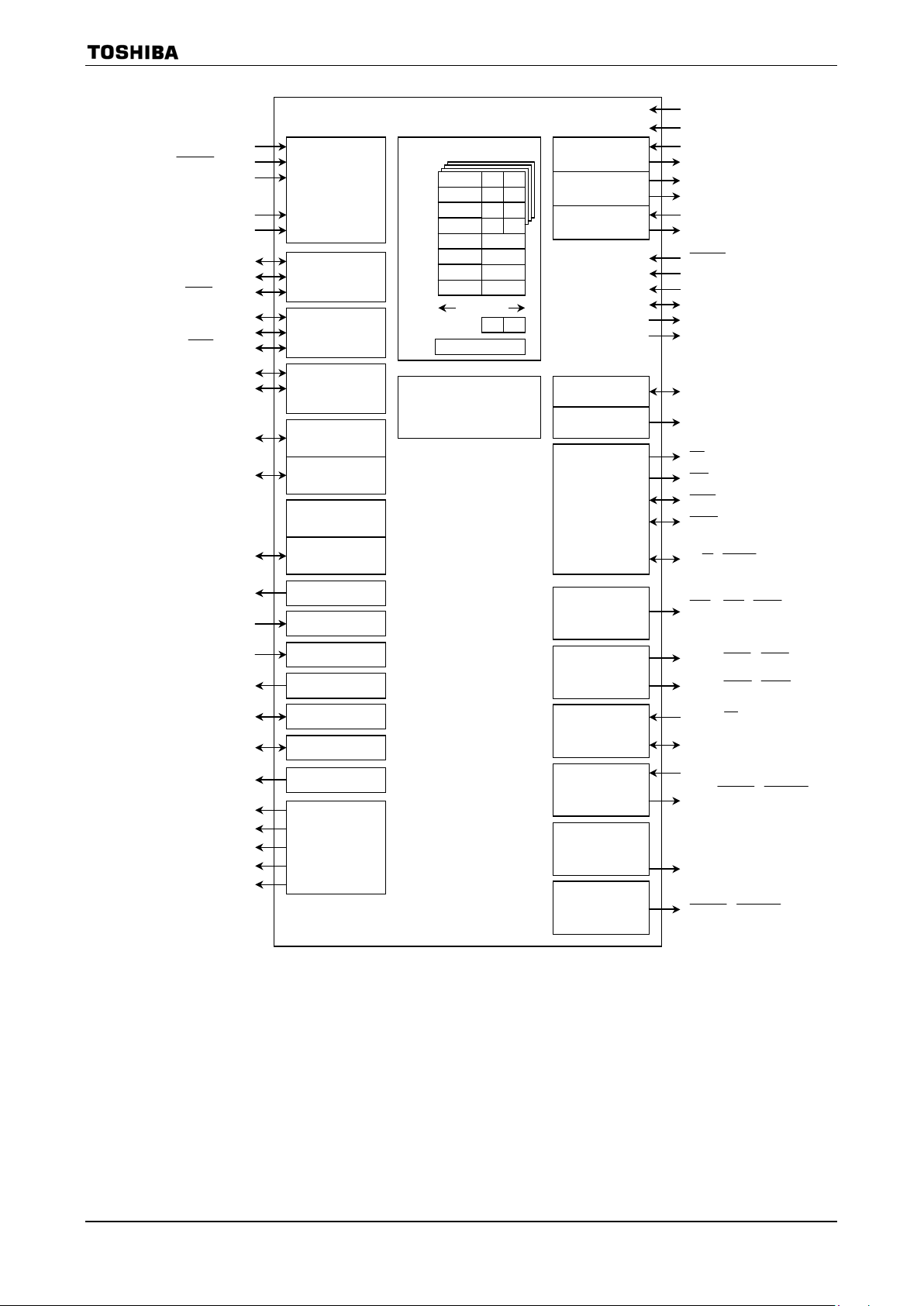

1. 概要と特長

TMP91C025 は、低電圧/低消費電力動作が可能な高速・高機能 16 ビットマイクロコントローラです。

TMP91C025F は、100 ピンミニフラットパッケージ製品です。JTMP91C025-S は 100 パッドチッ

プ製品です。特長は次のとおりです。

(1) オリジナル 16 ビット CPU (900/L1-CPU 使用)

• TLCS-90 と命令ニモニックで上位互換

• 16 M バイトのリニアアドレス空間

• 汎用レジスタ&レジスタバンク方式

• 16 ビット乗除算命令、ビット転送/演算命令

• マイクロ DMA: 4 チャネル (432 ns/2 バイト@36 MHz)

(2) 最小命令実行時間: 111 ns (@36 MHz)

TMP91C025

CMOS 16 ビット マイクロコントローラ

TMP91C025F/JTMP91C025-S

(3) 内蔵 RAM: なし

内蔵 ROM: なし

(4) 外部メモリ拡張

• 104 M バイト (プログラム, データ) まで拡張可能

• 外部データバス 8/16 ビット幅共存可能

… ダイナミックデータバスサイジング

• セパレートバスシステム

(5) 8 ビットタイマ: 4 チャネル

(6) 汎用シリアルインタフェース: 2 チャネル

• UART/同期両モード対応

: 2 チャネル

• IrDA ver1.0 (115.2 kbps) 対応モード選択可能: 1 チャネル

(7) LCD コントローラ

• シフトレジスタ型, RAM 内蔵型の両 LCD ドライバに対応

030519TBP1

• マイコン製品の信頼性予測については、「品質保証と信頼性 / 取り扱い上のご注意とお願い」の 1.3 項に記載されておりますので必ず

お読みください。

• 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当社半導体製品を

使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責任におい

て、機器の安全設計を行うことをお願いします。

なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべき注意事項や条件

について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」などでご確認ください。

• 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電

器など) に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり人体

に危害を及ぼす恐れのある機器 (原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置な

ど) にこれらの製品を使用すること (以下 “特定用途” という) は意図もされていませんし、また保証もされていません。本資料に掲

載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。

• 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。

• 本資料に掲載されている技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社および第三者の知的

財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 本資料に掲載されている製品を、国内外の法令、規則および命令により製造、販売を禁止されている応用製品に使用することはで

きません。

• 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

91C025-1

2003-12-05

Page 4

(8) RTC (リアルタイムクロック)

• TC8521A を基本とした仕様

(9) キーオンウェイクアップ (キー入力割り込み)

(10) 10 ビット AD コンバータ (サンプルホールド回路内蔵): 4 チャネル

(11) タッチスクリーンインタフェース (X 軸 Y 軸切り替え用スイッチング回路内蔵)

(12) ウォッチドッグタイマ

(13)メロディ/アラームジェネレータ

• メロディ: 4~5461 Hz のクロックを出力

• アラーム: 8 種類のアラームパターンを出力

• 5 種類のインターバル割り込みを出力

(14) チップセレクト/ウェイトコントローラ: 4 チャネル

(15) MMU

• 4 ローカルエリア/8 バンク方式により 104 M バイトまで拡張可能

(16) 割り込み機能: 37 本

• CPU 9 本 …… ソフトウエア割り込み命令、未定義命令実行違反

• 内部 23 本 …… 7レベルの優先順位の設定が可能

TMP91C025

• 外部 5 本 …… 7レベルの優先順位の設定が可能

(4 本はエッジの極性選択可能)

(17) 入出力ポート: 38 端子 (外部 16 ビットデータバスメモリ接続時)

(18) スタンバイ機能

3 種類の HALT モード (プログラマブル IDLE2, IDLE1, STOP)

(19) ハードウエアスタンバイ機能 (パワーセーブ機能)

(20) トリプルクロック制御機能

• クロック逓倍回路 (DFM) 内蔵

• クロックギア機能: 高周波クロック fc∼fc/16 まで切り替え可能

• 低速クロック機能 (fs = 32.768 kHz)

(21) 動作電圧

• Vcc = 3.0∼3.6 V (fc max = 36 MHz)

• Vcc = 2.7∼3.6 V (fc max = 27 MHz)

• Vcc = 2.4∼3.6 V (fc max = 16 MHz)

(22) パッケージ: P-LQFP100-1414-0.50F、またはチップ供給。

詳細は当社営業窓口までお問い合わせください。

91C025-2

2003-12-05

Page 5

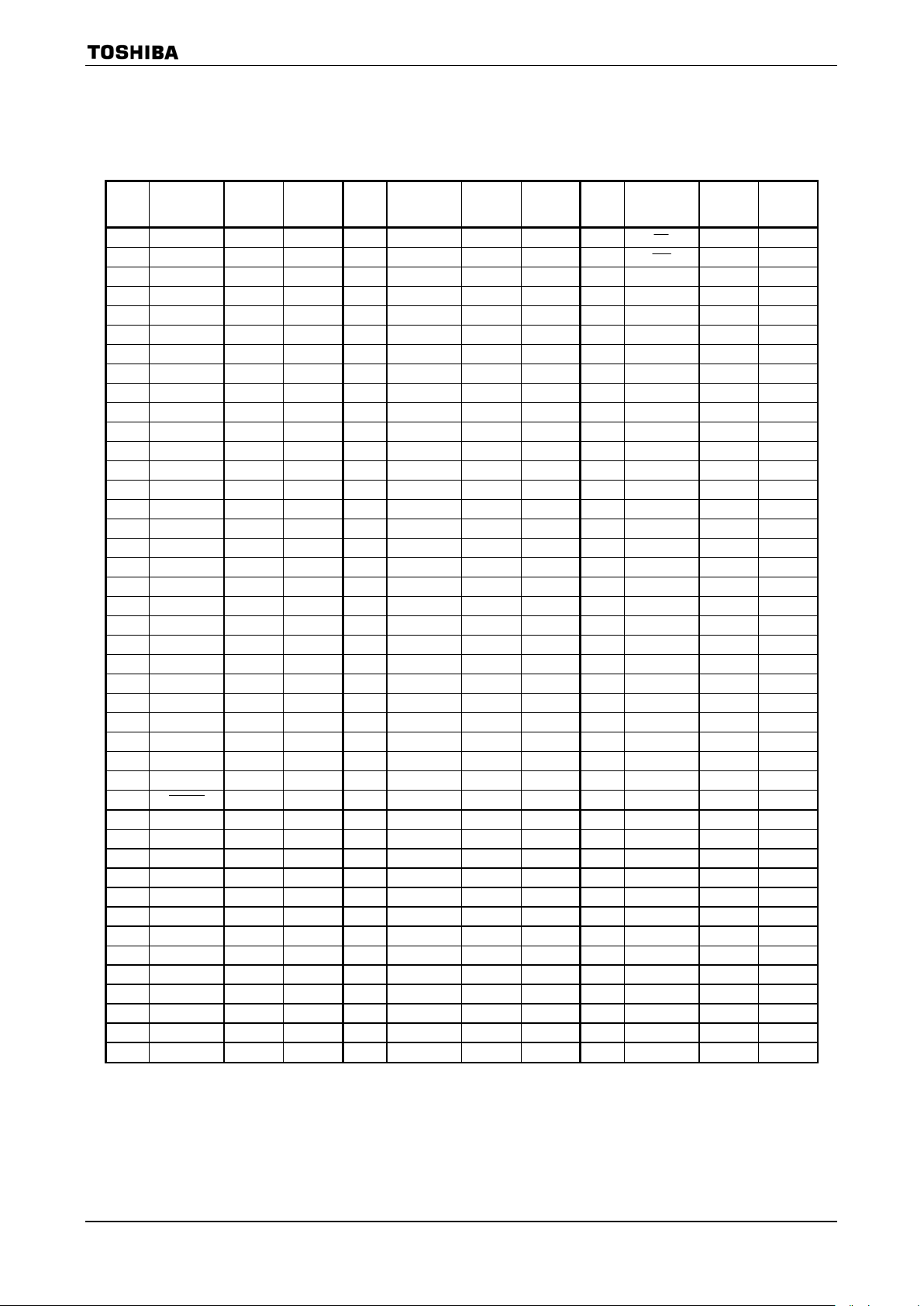

X

A

A

A

A

(

(

TMP91C025

AN3/MY/ADTRG (P83)

AN0, AN1 (P80, P81)

VREFH, VREFL

SCLK0/ 0CTS (PC2)

SCLK1/ 1CTS (PC5)

TA0IN/INT1 (PB4)

TA1OUT/KO1 (PA1)

TA3OUT/KO2 (PA2)

D1BSCP (PD0)

DLEBCD (PD3)

( ): リセット後の初期状態

AN2/MX (P82)

AVCC, AVSS

TXD0 (PC0)

RXD0 (PC1)

TXD1 (PC3)

RXD1 (PC4)

PX/INT2 (PB5)

PY/INT3 (PB6)

D2BLP (PD1)

D3BFR (PD2)

DOFFB (PD4)

10-bit 4-ch

AD

converter

SIO/UART/IrDA

(SIO0)

SIO/UART

(SIO1)

Touch screen

I/F(TSI)

8-bit timer

(TMRA0)

8-bit timer

(TMRA1)

8-bit timer

(TMRA2)

8-bit timer

(TMRA3)

Port 6

Port 8

Port 9

Port A

Port B

Port C

Port D

LCD controller

CPU (TLCS-900/L1)

XWA

XBC

XDE

XHL

XIX

XIY

XIZ

XSP

(Watchdog timer)

W A

B C

D E

H L

32ビット

SR

PC

WDT

I

IY

IZ

SP

DVCC [2]

DVSS [2]

H-OSC

Clock gear,

Clock doubler

L-OSC

F

Port 1

Port 2

Port 5

Port Z

CS/WAIT

controller

(4 blocks)

MMU

Interrupt

controller

Key Board

I/F

Melody/

Alarm-Out

RTC

X1

X2

EMU0

EMU1

XT1

XT2

RESET

M0

M1

D0~D7

0~A7

8~A15

P10~P17 (D8~D15)

P20~P27 (A16~A23)

RD

WR

HWR (PZ2)

WAIT (P56)

R/ W /SRWR (PZ3)

0CS ~ 3CS , A2CS

(P60~P63)

EA24/ B2CS /SRLB (P64)

EA25/ C2CS /SRUB (P65)

INT0 (PS )

INT0~INT3

(PB3~PB6)

KI0~KI7 (P90~P97) (PS)

KO0/ ALARM /MLDALM

(PA0)

KO1/TA1OUT (PA1)

KO2/TA3OUT (PA2)

KO3

PA3)

MLDALM (PD7)

ALARM /MLDALM /KO0

PA0)

図 1.1 TMP91C025 ブロック図

91C025-3

2003-12-05

Page 6

/

/

/

/

/

/

/

/

/

/

/

/

X

A

A

A

A

A

R

/

/

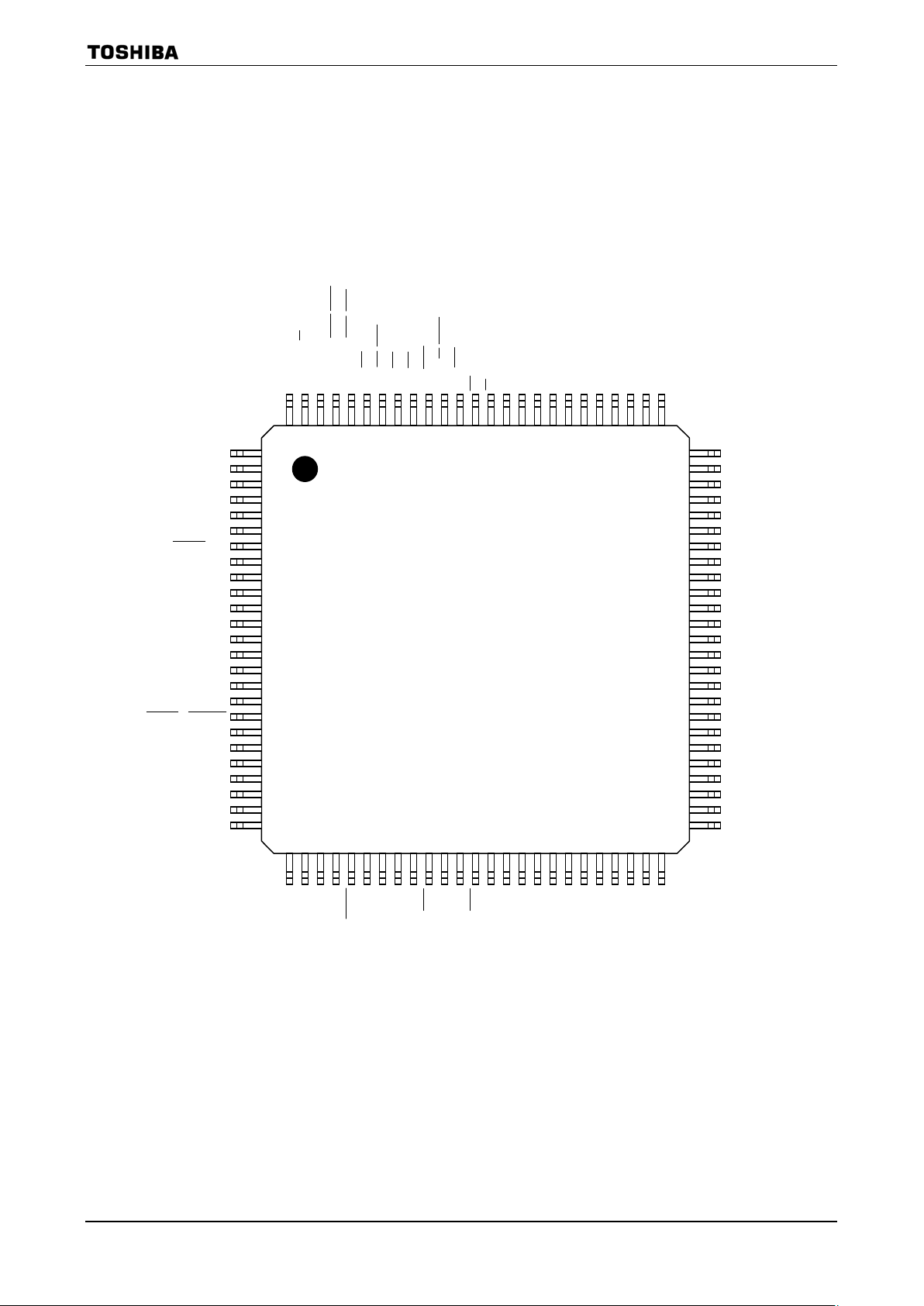

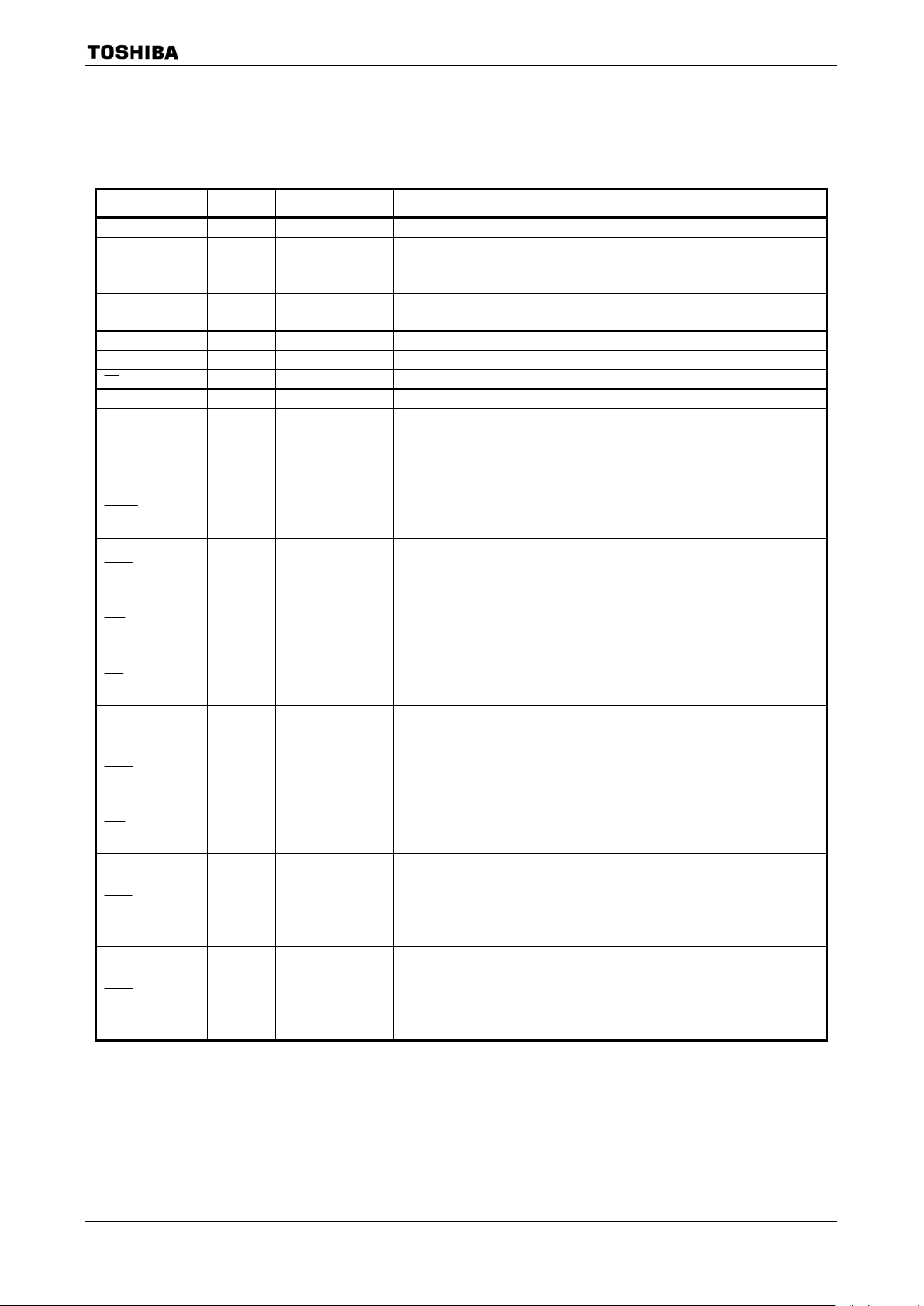

2. ピン配置とピン機能

TMP91C025 のピン配置図および入出力ピンの名称と概略機能を示します。

2.1 ピン配置図

TMP91C025F ピン配置図は、図 2.1.1のとおりです。

P83/AN3/

PA0/KO0/ ALARM / MLDALM

PA1/KO1/TA1OUT

PA2/KO2/TA3OUT

PA3/KO3/SCOUT

VREFL

AVSS

AVCC

P80/AN0

P81/AN1

P82/AN2/M

ADTRG /MY

PB5/PX/INT2

PB6/PY/INT3

P90/KI0

P91/KI1

P92/KI2

P93/KI3

P94/KI4

P95/KI5

P96/KI6

P97/KI7

PC0/TXD0

PC1/RXD1

DVCC1

AM0

PS

VREFH

PB3/INT0

100

1

5

10

15

20

25

X2

DVSS1

X1

PD7/MLDALM

SRLB

CS2B

CS2C/SRUB

P64/EA24

P65/EA25

AM1

RESET

TMP91C025

SRWR

W

CS3

CS2/CS2A

CS1

P63

P62

P61

95

30

XT2

XT1

EMU0

HWR

CS0

WAIT

P60

P56

PZ3/R

PZ2

90

TMP91C025F

QFP100

Top view

35

CTS0

EMU1

PC3/TXD1

PC4/RXD1

PC2/SCLK0

WR

CTS1

PC5/SCLK1

RD

A0

40

PD1/D2BLP

PD0/D1BSCP

A1

85

PD2/D3BF

A2

A3

PD4/DOFFB

PD3/DLEBCD

A4

D0

A5

45

D1

A6

80

D2

A7

D3

A8

D4

A9

D5

A10

D6

75

70

65

60

55

50

11

12

13

14

15

P20/A16

P21/A17

P22/A18

P23/A19

P24/A20

P25/A21

DVCC2

PB4/INT1/TA0IN

DVSS2

P26/A22

P27/A23

P17/D15

P16/D14

P15/D13

P14/D12

P13/D11

P12/D10

P11/D9

P10/D8

D7

図 2.1.1 ピン配置図 (100 ピン QFP)

91C025-4

2003-12-05

Page 7

TMP91C025

2.2 PAD座標値

表 2.2.1 PAD 座標値

(チップサイズ 4.58 mm × 4.63 mm) 単位 (µm)

ピン

No.

10 P90 −2151 336 53 P11 2151 −1359 96 P64 −926 2175

11 P91 −2151 211 54 P12 2151 −1228 97 P65 −1051 2175

12 P92 −2151 86 55 P13 2151 −1096 98 PD7 −1177 2175

13 P93 −2151 −38 56 P14 2151 −965 99 PB3 −1302 2175

14 P94 −2151 −163 57 P15 2151 −834 100 VREFH −1606 2175

15 P95 −2151 −289 58 P16 2151 −703

16 P96 −2151 −414 59 P17 2151 −571

17 P97 −2151 −539 60 P27 2151 −440

18 PA0 −2151 −664 61 P26 2151 −309

19 PA1 −2151 −789 62 DVSS2 2151 −153

20 PA2 −2151 −914 63 PB4 2151 2

21 PA3 −2151 −1040 64 DVCC2 2151 158

22 PC0 −2151 −1165 65 P25 2151 315

23 PC1 −2151 −1290 66 P24 2151 446

24 AM0 −2151 −1415 67 P23 2151 577

25 DVCC1 −2151 −1636 68 P22 2151 708

26 X2 −1603 −2175 69 P21 2151 839

27 DVSS1 −1438 −2175 70 P20 2151 971

28 X1 −1273 −2175 71 A15 2151 1102

29 AM1 −1147 −2175 72 A14 2151 1233

30

31 XT1 −897 −2175 74 A12 2151 1495

32 XT2 −649 −2175 75 A11 2151 1627

33 EMU0 −524 −2175 76 A10 1603 2175

34 EMU1 −398 −2175 77 A9 1477 2175

35 PC2 −273 −2175 78 A8 1350 2175

36 PC3 −148 −2175 79 A7 1224 2175

37 PC4 −23 −2175 80 A6 1097 2175

38 PC5 −101 −2175 81 A5 970 2175

39 PD0 −226 −2175 82 A4 844 2175

40 PD1 352 −2175 83 A3 717 2175

41 PD2 477 −2175 84 A2 590 2175

42 PD3 602 −2175 85 A1 464 2175

43 PD4 727 −2175 86 A0 337 2175

名称 X座標 Y 座標

1 VREFL −2151 1627 44 D0 852 −2175 87

2 AVSS −2151 1502 45 D1 977 −2175 88

3 AVCC −2151 1376 46 D2 1103 −2175 89 PZ2 −42 2175

4 P80 −2151 1251 47 D3 1228 −2175 90 PZ3 −169 2175

5 P81 −2151 1126 48 D4 1353 −2175 91 P56 −296 2175

6 P82 −2151 1001 49 D5 1478 −2175 92 P60 −421 2175

7 P83 −2151 876 50 D6 1603 −2175 93 P61 −548 2175

8 PB5 −2151 751 51 D7 2151 −1636 94 P62 −674 2175

9 PB6 −2151 625 52 P10 2151 −1490 95 P63 −801 2175

RESET

−1022 −2175 73 A13 2151 1364

ピン

No.

名称 X座標 Y 座標

ピン

No.

名称 X座標 Y座標

RD

WR

210 2175

83 2175

91C025-5

2003-12-05

Page 8

2.3 ピン名称と機能

入出力ピンの名称と機能は、表 2.3.1~表 2.3.3のとおりです。

表 2.3.1 ピン名称と機能 (1/3)

ピン名称 ピン数 入出力 機能

D0∼D7 8

P10∼P17

D8∼D15

P20∼P27

A16∼A23

A8∼A15 8

A0∼A7 8

RD

WR

PZ2

HWR

PZ3

R/

W

SRWR

P56

WAIT

P60

CS0

P61

CS1

P62

CS2

CS2A

P63

CS3

P64

EA24

CS2B

SRLB

P65

EA25

CS2C

SRUB

8

8

1

1

1

1

1

1

1

1

1

1

1

入出力 データ (下位): データ・バス 0∼7 です。

入出力

入出力

出力

出力

出力 アドレス: アドレス・バス 8∼15です。

出力 アドレス: アドレス・バス 0∼7です。

出力 リード: 外部メモリをリードするためのストローブ信号です。

出力 ライト: D0∼D7端子のデータをライトするためのストローブ信号です。

入出力

出力

入出力

出力

出力

入出力

入力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

ポート 1: ビット単位で入出力の設定ができる入出力ポートです。

外部 8 ビットバスで使用する際に使用できます。

データ (上位): データ・バス 8∼15です。

ポート 2: 出力ポートです。

アドレス: アドレス・バス 16∼23 です。

ポート Z2: 入出力ポートです。(プルアップ付き)

上位ライト: D8∼D15端子のデータをライトするためのストローブ信号です。

ポート Z3: 入出力ポートです。(プルアップ付き)

リード/ライト: “1” でリードサイクルまたはダミーサイクルを、“0” でライト

サイクルを示します。

ライト: D0∼D15 端子のデータを外部 SRAMにライトするためのストローブ

信号です。

ポート 56: 入出力ポートです。(プルアップ付き)

ウェイト: CPU へのバスウェイト要求端子です。

(0, (1 + N) WAIT モード)

ポート 60: 出力ポートです。

チップセレクト 0: アドレスが指定したアドレス領域内なら “0” を出力しま

す。

ポート 61: 出力ポートです。

チップセレクト 1: アドレスが指定したアドレス領域内なら “0” を出力しま

す。

ポート 62: 出力ポートです。

チップセレクト 2: アドレスが指定したアドレス領域内なら “0” を出力しま

す。

拡張チップセレクト 2A: アドレスが特定のアドレス領域内なら “0” を出力し

ます。

ポート 63: 出力ポートです。

チップセレクト 3: アドレスが指定したアドレス領域内なら “0” を出力しま

す。

ポート 64: 出力ポートです。

拡張アドレス 24: データエリアを拡張する際に使用するアドレスバスです。

拡張チップセレクト 2B: アドレスが特定のアドレス領域内なら “0” を出力し

ます。

外部 SRAM用の下位バイト D0∼D7 端子のデータイネーブル信号です。

ポート 65: 出力ポートです。

拡張アドレス 25: データエリアを拡張する際に使用するアドレスバスです。

拡張チップセレクト 2C: アドレスが特定のアドレス領域内なら “0” を出力し

ます。

外部 SRAM用の上位バイト D8∼D15 端子のデータイネーブル信号です。

TMP91C025

91C025-6

2003-12-05

Page 9

表 2.3.2 ピン名称と機能 (2/3)

ピン名称 ピン数 入出力 機能

P80∼P81

AN0∼AN1

P82

AN2

MX

P83

AN3

ADTRG

MY

P90∼P97

KI0∼KI7

PA0

KO0

ALARM

MLDALM

PA1

KO1

TA1OUT

PA2

KO2

TA3OUT

PA3

KO3

SCOUT

PB3

INT0

PS

PB4

INT1

TA0IN

PB5

INT2

PX

PB6

INT3

PY

PC0

TXD0

PC1

RXD0

注) リセットにより、PB3 (INT0,

2

1

1

8

1

1

1

1

1

1

1

1

1

1

入力

入力

入力

入力

入力

入力

入力

入力

入力

入力

入力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

入出力

入力

入力

入出力

入力

入力

入力

入力

出力

入力

入力

出力

入出力

出力

入出力

入力

PS ) 端子は PS 入力端子となるため、“1” を入力してください。

ポート 80~81: 入力専用ポートです。

アナログ入力 0~1: AD コンバータの入力です。

ポート 82: 入力専用ポートです。

アナログ入力 2: AD コンバータの入力です。

X-: 外部タッチパネルの X-端子に接続します。

ポート 83: 入力専用ポートです。

アナログ入力 3: AD コンバータの入力です。

ADトリガ: AD コンバータの外部スタート要求端子です。

Y-: 外部タッチパネルの Y-端子に接続します。

ポート 90~97: 入力専用ポートです。

キー入力 0~7: キーオンウェイクアップ端子 0~7 です。

(シュミット入力, プルアップ付き)

ポート A0: 出力専用ポートです。

キー出力 0: キースキャン用ストローブ端子 0 です。プログラムによりオー

プンドレイン出力端子となります。

RTC アラーム出力端子です。

メロディ/アラーム用出力の論理反転出力端子です。

ポート A1: 出力専用ポートです。

キー出力 1: キースキャン用ストローブ端子 1 です。プログラムによりオー

プンドレイン出力端子となります。

8ビットタイマ 1 出力: タイマ 0 またはタイマ 1 の出力です。

ポート A2: 出力専用ポートです。

キー出力 2: キースキャン用ストローブ端子 2 です。プログラムによりオー

プンドレイン出力端子となります。

8ビットタイマ 3 出力: タイマ 2 またはタイマ 3 の出力です。

ポート A3: 出力専用ポートです。

キー出力 3: キースキャン用ストローブ端子 3 です。プログラムによりオー

プンドレイン出力端子となります。

システムクロック出力: f

ポート B3: 入出力ポートです。

割り込み要求端子 0: レベル/立ち上がり/立ち下がりエッジを選択可能な割

り込み要求端子です。

ハードウェアスタンバイ機能を実行するときに、“0” を入力します。

ポート B4: 入出力ポートです。

割り込み要求端子 1: 立ち上がり/立ち下がりエッジを選択可能な割り込み要

求端子です。

8ビットタイマ 0 入力: タイマ 0 の入力です。

ポート B5: 入力ポートです。

割り込み要求端子 1: 立ち上がり/立ち下がりエッジを選択可能な割り込み要

求端子です。

X+: 外部タッチパネルの X+端子に接続します。

ポート B6: 入力ポートです。

割り込み要求端子 1: 立ち上がり/立ち下がりエッジを選択可能な割り込み要

求端子です。

Y+: 外部タッチパネルの Y+端子に接続します。

ポート C0: 入出力ポートです。

シリアル 0 送信データ

プログラムによりオープンドレイン出力端子となります。

ポート C1: 入出力ポートです。

シリアル 0 受信データ

を出力します。

FPH

TMP91C025

91C025-7

2003-12-05

Page 10

表 2.3.3 ピン名称と機能 (3/3)

ピン名称 ピン数 入出力 機能

PC2

SCLK0

CTS0

PC3

TXD1

PC4

RXD1

PC5

SCLK1

CTS1

XT1 1

XT2 1

PD0

D1BSCP

PD1

D2BLP

PD2

D3BFR

PD3

DLEBCD

PD4

DOFFB

PD7

MLDALM

AM0~AM1

EMU0 1

EMU1 1

RESET

VREFH 1

VREFL 1

AVCC 1

AVSS 1

X1, X2 2

DVCC

DVSS

1

1

1

1

1

1

1

1

1

1

2

1

2

2

入出力

入出力

入力

入出力

出力

入出力

入力

入出力

入出力

入力

入力 低周波発振器接続端子です。

出力 低周波発振器接続端子です。

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

出力

入力

出力 “開放” してください。

出力 “開放” してください。

入力 リセット: LSIを初期化します。(シュミット入力、プルアップ付き)

入力 ADコンバータ用基準電源入力端子です。 (H)

入力 ADコンバータ用基準電源入力端子です。 (L)

入出力 発振子接続端子

ポート C2: 入出力ポートです。(プルアップ付き)

シリアル 0 クロック入出力

シリアル 0 データ送信可能 (Clear to send)

ポート C3: 入出力ポートです。

シリアル 1 送信データ

プログラムによりオープンドレイン出力端子となります。

ポート C4: 入出力ポートです。

シリアル 1 受信データ

ポート C5: 入出力ポートです。(プルアップ付き)

シリアル 1 クロック入出力

シリアル 1 データ送信可能 (Clear to send)

ポート D0: 出力ポートです。

LCD ドライバ用出力端子です。

ポート D1: 出力ポートです。

LCD ドライバ用出力端子です。

ポート D2: 出力ポートです。

LCD ドライバ用出力端子です。

ポート D3: 出力ポートです。

LCD ドライバ用出力端子です。

ポート D4: 出力ポートです。

LCD ドライバ用出力端子です。

ポート D7: 出力ポートです。

メロディ/アラーム用出力端子です。

動作モード:

(外部 16 ビットバス固定、もしくは外部 8/16 ビットバス混在時)

AM1 = “0”, AM0 = “1” に固定してください。

(外部 8 ビットバス固定時)

AM1 = “0”, AM0 = “0” に固定してください。

ADコンバータ電源端子

ADコンバータ GND 端子 (0 V)

電源端子 (全 DVCC 端子を電源に接続してください)

GND 端子 (全 DVSS 端子を GND (0 V) に接続してください)

TMP91C025

91C025-8

2003-12-05

Page 11

3. 動作説明

ここでは、TMP91C025 の機能および基本動作について、ブロックごとに説明します。

なお、本章の最後に 6.「使用上の注意、制限事項」としてブロック別の注意、制限事項などを掲載

していますのでご確認ください。

3.1 CPU

TMP91C025 には、高性能な 16 ビット CPU (900/L1-CPU) が内蔵されています。CPU の動作

については、前章の “TLCS-900/L1 CPU” を参照してください。

ここでは、“TLCS-900/L1 CPU” にて説明されていない TMP91C025 独自の CPU 機能について

説明します。

3.1.1 リセット動作

本デバイスにリセットをかけるには、電源電圧が動作範囲内であり、内部高周波発振器の発

振が安定した状態で少なくとも 10 システムクロック間 (4 MHz クロック発振時で 80 µs)、

RESET 入力を “Low” にしてください。また、電源投入時は RESET 入力が “Low” レベルで電

源電圧が動作範囲内になり、内部高周波発振器の発振が安定した状態で少なくとも 10 システ

ムクロック間、

なお、リセット動作にてクロックギアは 1/16 モードに初期化されるので、システムクロッ

ク f

SYS

リセットが受け付けられると、CPU は、

TMP91C025

RESET 入力の “Low” レベルを保持してください。

は、fc/32 (= fc/16 × 1/2)となります。

• プログラムカウンタ PC をアドレス FFFF00H∼FFFF02H に格納されているリセット

ベクタに従いセット

PC (7:0) ← アドレス FFFF00H の値

PC (15:8) ← アドレス FFFF01H の値

PC (23:16) ← アドレス FFFF02H の値

• スタックポインタ XSP を 100H にセット

• ステータスレジスタ SR の IFF2∼IFF0 ビットを “111” にセット (割り込みレベルのマ

スク・レジスタをレベル 7 にセット)

• ステータスレジスタ SR の MAX ビットを “1” にセット (マキシマムモードにセット)

注) この製品では、“0” を書かないでください。ミニマムモードはサポートしていま

せん。

• ステータスレジスタ SR の RFP2∼RFP0 ビットを “000” にクリア (レジスタバンクを

0 にセット)

を行い、リセットが解除されると、セットされた PC

上記以外の CPU 内部のレジスタは、変化しません。

また、リセットが受け付けられると、内蔵 I/O およびポート、その他の端子は、下記のとお

りとなります。

• 内蔵 I/O のレジスタを初期化

に従い命令の実行を開始します。なお、

• ポート端子 (内蔵 I/O 用にも使える兼用端子を含む) を、汎用入力ポートまたは汎用出

力ポートのモードにセット

注) リセット動作により、CPU の PC、SR、XSP 以外のレジスタは変化しません。

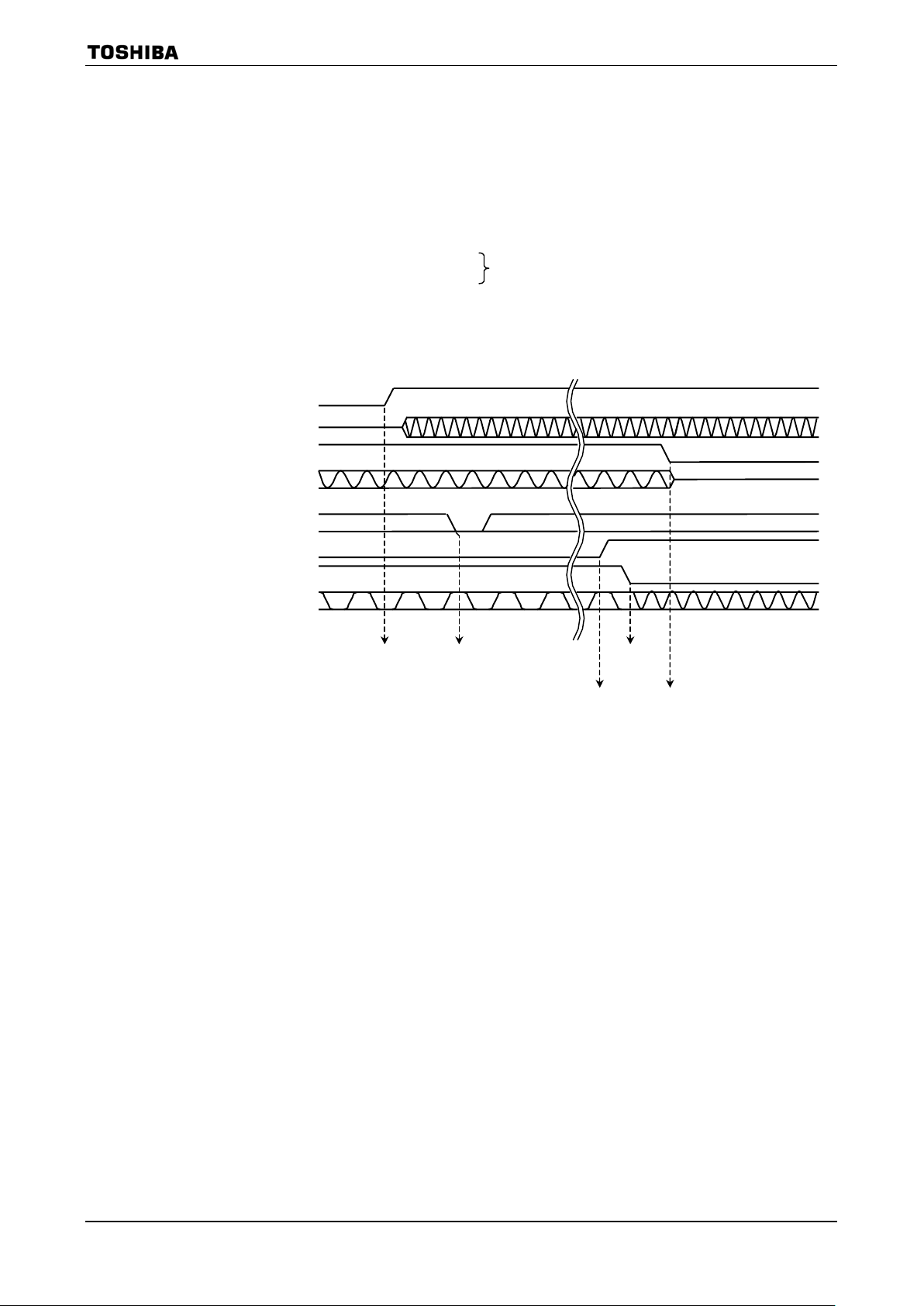

図 3.1.1に TMP91C025 のリセットタイミングチャートを示します。

91C025-9

2003-12-05

Page 12

R

R

TMP91C025

リード

ライト

0FFFF00H

Data-in

リードサイクルで始まる)

(リセット解除後は、2ウェイトの

サンプリング

(PZ2 入力モード)

サンプリング

Data-in

Data-out

は 内部でプルアップを示す。

は ハイインピーダンスを示す。

FPH

f

RESET

A23∼A0

CS2

CS0, CS1, CS3

D0∼D15

RD

D0∼D15

W

HW

XT1,XT2

図 3.1.1 リセットタイミングチャート

91C025-10

2003-12-05

Page 13

(n)

(

)

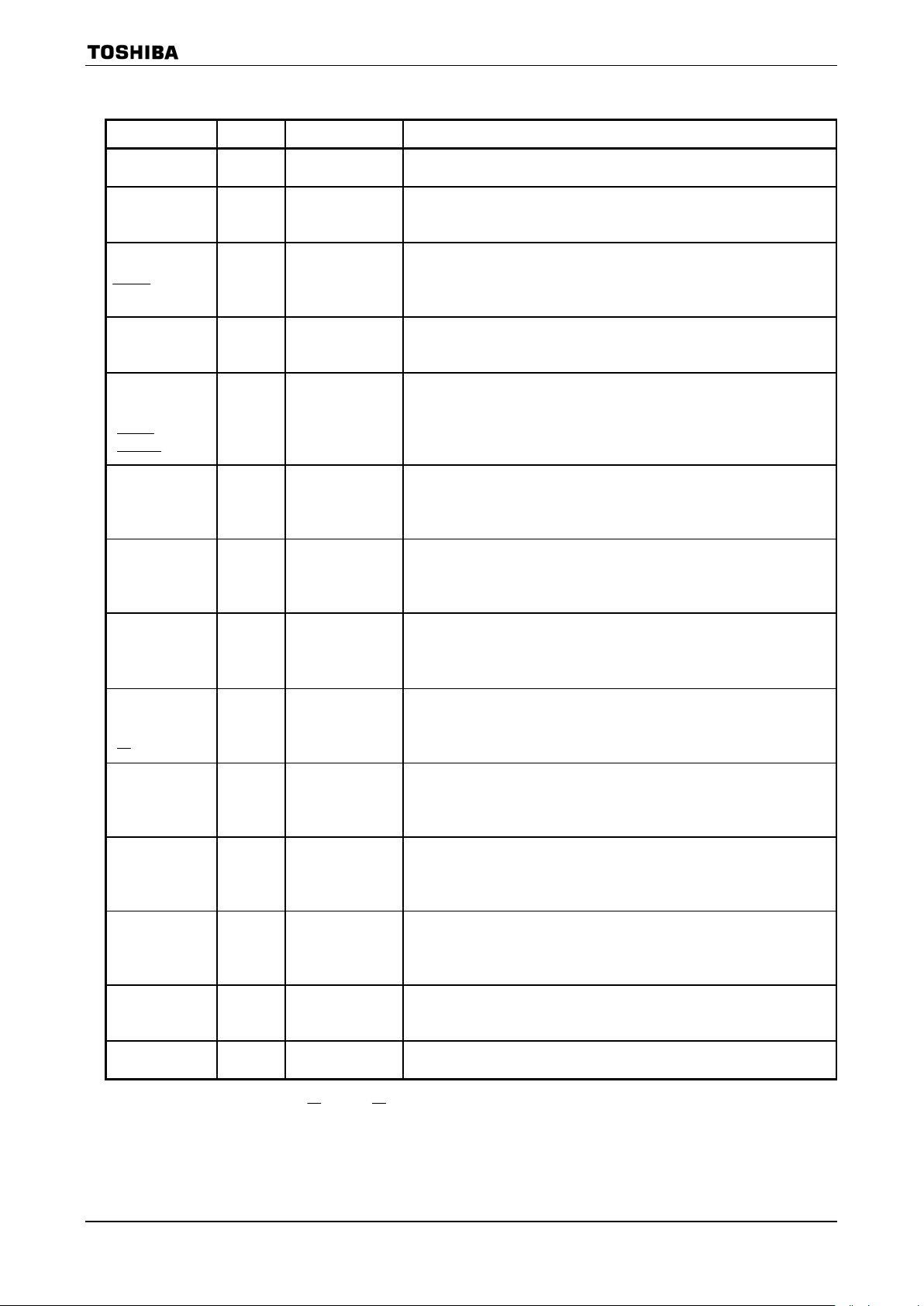

3.2 メモリマップ

TMP91C025 のメモリマップを、図 3.2.1に示します。

000000H

000100H

000FE0H

001000H

010000H

FFFF00H

FFFFFFH

内蔵I/O

(4 Kバイト)

外部メモリ

ベクタテーブル

TMP91C025

ダイレクト

エリア

64 Kバイトエリア

(nn)

16 Mバイトエリア

(R)

(−R)

(R+)

(R + R8/16)

(R + d8/16)

(nnn)

256 バイト

( = 内部エリア)

図 3.2.1 メモリマップ

注) アドレス 000FE0H~000FEFH のエリアは、RAM 内蔵 LCD ドライバにアサインしているため外部

エリアです。

アドレス 000FF0H~000FFFH のエリアは、予約領域としてアサインしているため外部エリアです。

91C025-11

2003-12-05

Page 14

3.3 トリプルクロック/スタンバイ制御、ノイズ低減機能

低消費電力、低ノイズ化のためにクロックギア、クロック逓倍回路 (DFM)、スタンバイ制御回

路、ノイズ低減回路などを内蔵しています。

この章は下記のような構成になっています。

3.3.1 クロック系統ブロック図

3.3.2 SFR 説明

3.3.3 システムクロック制御部

3.3.4 プリスケーラクロック制御部

3.3.5 クロック逓倍回路 (DFM)

3.3.6 ノイズ低減回路

3.3.7 スタンバイ制御部

TMP91C025

91C025-12

2003-12-05

Page 15

クロックモード (X1, X2 と XT1, XT2 端子) と (c) トリプルクロックモード (X1, X2 と XT1, XT2 端

子と DFM) の 3 モードがあります。

IDLE2モード

(I/O動作)

IDLE1モード

(発振器 + DFM動作)

注1) SLOW モードから DFM 使用 NORMAL モードへの移行時に、SLOW モードからの DFM 制御はできません。

注2) DFM 使用の NORMAL モードから NORMAL モードへの移行時には CPU クロック切替え → DFM 回路停止の順

注3) DFM 使用の NORMAL モードから直接 STOP モードへは移行できません。必ず一度 NORMAL モードを経由して

TMP91C025

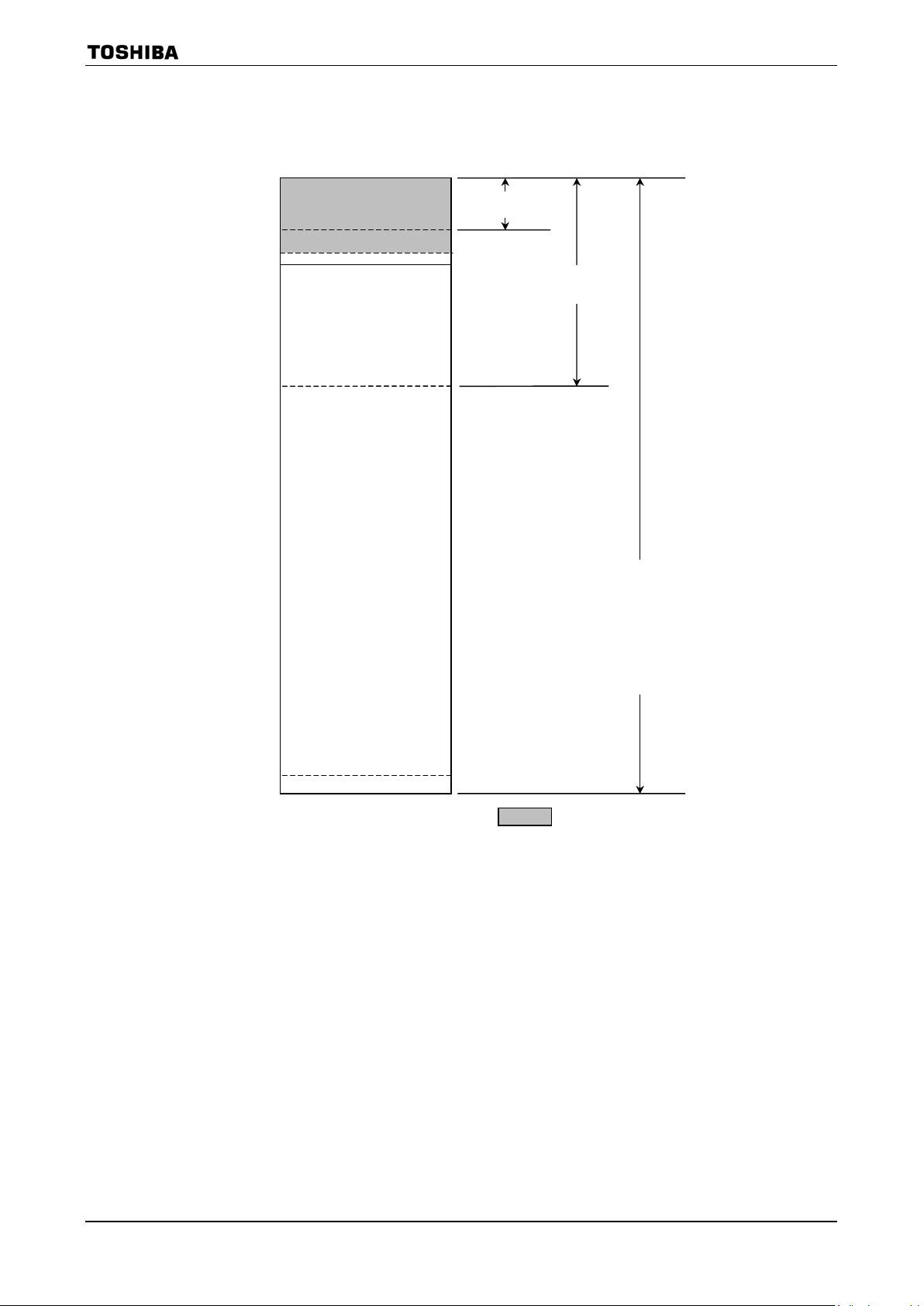

クロックの動作モードとしては、(a) シングルクロックモード (X1, X2 端子のみ) と (b) デュアル

図 3.3.1に動作モード別状態遷移図を示します。

リセット

/32)

(f

OSCH

/ギア値/2)

リセット

(f

OSCH

/ギア値/2)

命

令

(fs/2)

リセット

(f

OSCH

/ギア値/2)

命令

命 令

注)

リセット解除

/32)

リセット解除

命

/32)

リセット解除

割り

込み

割

り

命

令

SLOWモード

命 令

割り込み

命

令

割り込み

令

命

令

込

み

(fs/2)

STOPモード

(全回路停止)

STOPモード

(全回路停止)

IDLE2モード

(I/O動作)

IDLE1モード

(発振器のみ動作)

命

IDLE2モード

(I/O動作)

IDLE1モード

(発振器のみ動作)

IDLE2モード

(I/O動作)

IDLE1モード

(発振器のみ動作)

IDLE2モード

(I/O動作)

IDLE1モード

(発振器のみ動作)

IDLE2モード

(I/O動作)

IDLE1モード

(発振器のみ動作)

(4 × f

(DFM 起動・停止・内部クロック切り替え、DFMCR0<ACT1:0>レジスタへの書き込み)

序で 2 回に分けて命令を行ってください。

から STOP モードへ移行して下さい。(高周波発振停止は DFM を停止した後で行ってください)

令

割

り

込

令

命

込

り

割

(a) シングルクロックモード状態遷移図

命

令

割

り

込

命 令

込

り

割

命

令

割

り

込

命 令

込

り

割

(b) デュアルクロックモード状態遷移図

命

令

割

り

込

命 令

込

り

割

命

令

NORMALモード

/ギア値/2)

OSCH

(DFM使用)

(c) トリプルクロックモード状態遷移図

み

み

み

み

み

み

み

み

注)

NORMALモード

(f

OSCH

NORMALモード

(f

OSCH

SLOWモード

NORMALモード

(f

OSCH

STOPモード

(全回路停止)

図 3.3.1 動作モード別状態遷移図

X1, X2 端子より入力されるクロック周波数を f

波数を fs、SYSCR1<SYSCK>で選択されたクロックを f

をシステムクロック f

と定義します。また、この f

SYS

91C025-13

、XT1, XT2 端子より入力されるクロック周

OSCH

FPH、fFPH

の 1 周期を 1 ステートと定義します。

SYS

を 2 分周したクロック周波数

2003-12-05

Page 16

3.3.1 クロック系統ブロック図

TMP91C025

SYSCR0

<XTEN, RXTEN>

XT1

XT2

低 速

発振器

fs

SYSCR0

<XEN, RXEN>

X1

X2

高 速

発振器

DFM (クロック

f

OSCH

SYSCR0<WUEF>

SYSCR2<WUPTM1:0>

DFMCR0<ACT1:0, DLUPTM>

ウォームアップ (高, 低速発振器用)/

ロックアップ (DFM用)タイマ

fc

f

DFM

逓倍回路)

= f

OSCH

セレクタ

DFMCR0<ACT1:0>

× 4

fc/2

÷2 ÷16÷4 ÷8

クロックギア

fc/4

fc/8

fc/16

SYSCR1<GEAR2:0>

SYSCR0

<PRCK1:0>

fc/16

f

FPH

÷2

SYSCR1<SYSCK>

÷2 ÷4

φT

φT0

fs

f

SYS

f

SYS

φT0

TMRA0∼TMRA3

プリスケーラ

SIO0∼SIO1

プリスケーラ

CPU

割り込み

コントローラ

ADC

WDT

I/Oポート

TSI

fs

RTC

LCDC

MLD/ALM

図 3.3.2 デュアルクロック、スタンバイ関連のブロック図

91C025-14

2003-12-05

Page 17

3.3.2 SFR 説明

SYSCR0

(00E0H)

SYSCR1

(00E1H)

SYSCR2

(00E2H)

Bit symbol XEN XTEN RXEN RXTEN RSYSCK WUEF PRCK1 PRCK0

Read/Write R/W

リセット後

機 能

Bit symbol SYSCK GEAR2 GEAR1 GEAR0

Read/Write R/W

リセット後

機 能

Bit symbol PSENV WUPTM1 WUPTM0 HALTM1 HALTM0 SELDRV DRVE

Read/Write R/W R/W R/W R/W R/W R/W R/W

リセット後

機 能 パワー

TMP91C025

7 6 5 4 3 2 1 0

1 1 1 0 0 0 0 0

高速

発振器

0: 停止

1: 発振

0 1 0 0

セーブ

モード

0: 有効

1: 無効

低速

発振器

0: 停止

1: 発振

注 1)

STOP モード

解除後の

高速

発振器

0: 停止

1: 発振

STOP モード

解除後の

低速

発振器

0: 停止

1: 発振

STOP モード

解除後の

クロック

選択

0: 高速

1: 低速

システム

クロック

選択

0: 高速 (fc)

1: 低速 (fs)

発振器用

ウォーム

アップタイ

マ (WUP)

制御

0 ライト:

Don’t care

1 ライト:

WUP

スタート

0 リード:

WUP 終了

1 リード

WUP 中

プリスケーラクロック

選択

00: f

FPH

01: Reserved

10: fc/16

11: Reserved

高速クロックのギア選択

000: 高速クロック

001: 高速クロック /2

010: 高速クロック /4

011: 高速クロック /8

100: 高速クロック /16

101:

110: Reserved

111:

0 1 0 1 1 0 0

HALT モード選択

00: Reserved

01: STOP モード

10: IDLE1 モード

11: IDLE2 モード

<DRVE>

使用モー

ド選択

0: IDLE1

1: STOP

注 3)

1: STOP/

IDLE1

モード中

も端子を

ドライブ

します

注 2)

発振器用WUP時間選択

00: Reserved

8

/入力周波数

01: 2

14

10: 2

16

11: 2

注 1) 低速発振器はリセットにより発振許可となります。

注 2) ハードウエアスタンバイモードに入ると、HALT モード選択 SYSCR2<HALTM1, 0 = 11>

でも、状態は IDLE1 となります。

注 3) 0: IDLE1, 1: STOP となっています。ほかの製品と異なる場合がありますので注意が必要です。

図 3.3.3 クロック関係 SFR

91C025-15

2003-12-05

Page 18

TMP91C025

記号 名称 アドレス 7 6 5 4 3 2 1 0

ACT1 ACT0 DLUPFG DLUPTM

R/W R/W R R/W

0 0 0 0

f

選択

DFM LUP

00

STOP

STOP

01

RUN

RUN

10

RUN

STOP

11

RUN

STOP

FPH

f

OSCH

f

OSCH

f

DFM

f

OSCH

ロックアップ

(LUP)フラグ

0: LUP 終了

1: LUP 中

ロックアップ

時間選択

0: 212/f

OSCH

1: 210/f

OSCH

DFMCR0

DFM

control

register 0

E8H

D7 D6 D5 D4 D3 D2 D1 D0

R/W R/W R/W R/W R/W R/W R/W R/W

0 0 0 1 0 0 1 1

DFM 補正

入力周波数 4~9 MHz (@3.0 V~3.6 V) では 0BH をライトしてください。

DFMCR1

DFM

control

register1

E9H

入力周波数 4~6.75 MHz (@2.7 V~3.6 V) では 0BH をライトしてください。

図 3.3.4 DMF 関係 SFR

DFM 使用に関する制約

1. DFM の起動・停止等の制御は、SLOW モード (f

) では行わないでください。

S

(DFMCR0<ACT 1:0> レジスタへの書き込み)

制御は、必ず NORMAL モードから行うようにしてください。

2. DFM を使用している状態 (DFMCR0<ACT1:0> = “10”) から DFM動作を停止する場合は、f

→ f

切り替えと DFM 停止を同時に行わず、2 回に分けた手順にて行ってください。

OSCH

LD (DFMCR0),C0H ; f

DFM

→ f

OSCH

切り替え

LD (DFMCR0),00H ; DFM 停止

3. DFM を使用している状態 (DFMCR0<ACT1:0> = “10”) から高周波発振器を停止する場合は、

DFM を停止してから高周波発振器を停止してください。

詳細は 3.3.5 クロック逓倍回路 (DFM) を参照してください。

DFM

91C025-16

2003-12-05

Page 19

EMCCR0

(00E3H)

EMCCR1

(00E4H)

EMCCR2

(00E5H)

EMCCR3

(00E6H)

TMP91C025

7 6 5 4 3 2 1 0

Bit symbol PROTECT TA3LCDE AHOLD TA3MLDE − EXTIN

Read/Write R R/W R/W R/W R/W R/W R/W R/W

リセット後

機 能

0 0 0 0 0 0 1 1

プロテクト

フラグ

0: OFF

1: ON

LCDC

ソースクロ

ック選択

0: 32 kHz

1: TA3OUT

アドレス

ホールド

0: OFF

1: ON

MLD ソース

クロック

選択

0: 32 kHz

1: TA3OUT

“0” をライト

してくださ

い。

1: fc 外部

クロック

Bit symbol

Read/Write

リセット後

機 能

Bit symbol

1st-KEY, 2nd-KEY の書き込みによりプロテクト ON/OFF が切り替わります。

1st-KEY: EMCCR1 = 5AH, EMCCR2 = A5H を連続ライト

2nd-KEY: EMCCR1 = A5H, EMCCR2 = 5AH を連続ライト

Read/Write

リセット後

機 能

Bit symbol ENFROM ENDROM ENPROM FFLAG

Read/Write R/W R/W R/W R/W R/W R/W

リセット後

機 能

0 0 0 0 0 0

CS1A エリア

検出許可

0: 禁止

1: 許可

CS2B-2G

エリア検出

許可

0: 禁止

1: 許可

CS2A エリア

検出許可

0: 禁止

1: 許可

CS1A

ライト動作

フラグ

リード時

“0”: ライトなし

“1”: ライトあり

DRVOSCH DRVOSCL

fc 発振器

ドライブ

能力

1: Normal

0: Weak

DFLAG PFLAG

CS2B-2G

ライト動作

フラグ

fs 発振器

ドライブ

能力

1: Normal

0: Weak

CS2A

ライト動作

フラグ

ライト時

“0”: フラグクリア

注) アドレス 000000H~000FDFH のエリアをアクセスした場合、A23~A0 端子は直前の外部アク

セスのアドレスを保持します。

図 3.3.5 ノイズ関係 SFR

91C025-17

2003-12-05

Page 20

3.3.3 システムクロック制御部

TMP91C025

システムクロック制御部は、CPU コアおよび内蔵 I/O へ供給されるシステムクロック (f

SYS

)

を生成する回路です。高速/低速 2 つの発振回路と、DFM (クロック逓倍回路) から出力される

fc, fs クロックを入力として、SYSCR1<SYSCK> レジスタにて高速/ 低速の切り替え、

SYSCR0<XEN>, <XTEN> でそれぞれ高速, 低速発振器の発振制御、さらに

SYSCR1<GEAR2:0>で高速クロックのギアを 1, 2, 4, 8, 16 段 (fc, fc/2, fc/4, fc/8, fc/16) に切り

替え、消費電力の低減を図ることができます。

リセットにより、デュアルクロックモードになり<XEN> = “1”、<XTEN> = “1”、<SYSCK>

= “0”、<GEAR2:0> = “100” に初期化されますのでシステムクロック f

となります。例えば、X1, X2 端子に 16 MHz の発振子を接続していると、リセットにより f

は fc/32 (= fc/16 × 1/2)

SYS

SYS

は 0.5 MHz となります。

(1) NORMAL ↔ SLOW モードの切り替え

発振子接続端子に発振子を接続している場合、発振子の発振安定を確認してから切り替

えるためにウォームアップタイマがあります。ウォームアップ時間は発振子の特性に合わ

せて、SYSCR2<WUPTM1:0> により選択できます。このスタート, 終了確認は

SYSCR0<WUEF>を使用し、ソフト (命令) により設定例 1、2 のように行ってください。

表 3.3.1に切り替え時のウォームアップ時間を示します。

注 1) 切り替えようとするクロックが発振器などを使用していて発振安定している場合

は、ウォームアップさせる必要はありません。

注 2) ウォームアップタイマは発振クロックで動作しているため、発振周波数にゆらぎ

がある場合は誤差を含みます。従って概略時間としてとらえる必要があります。

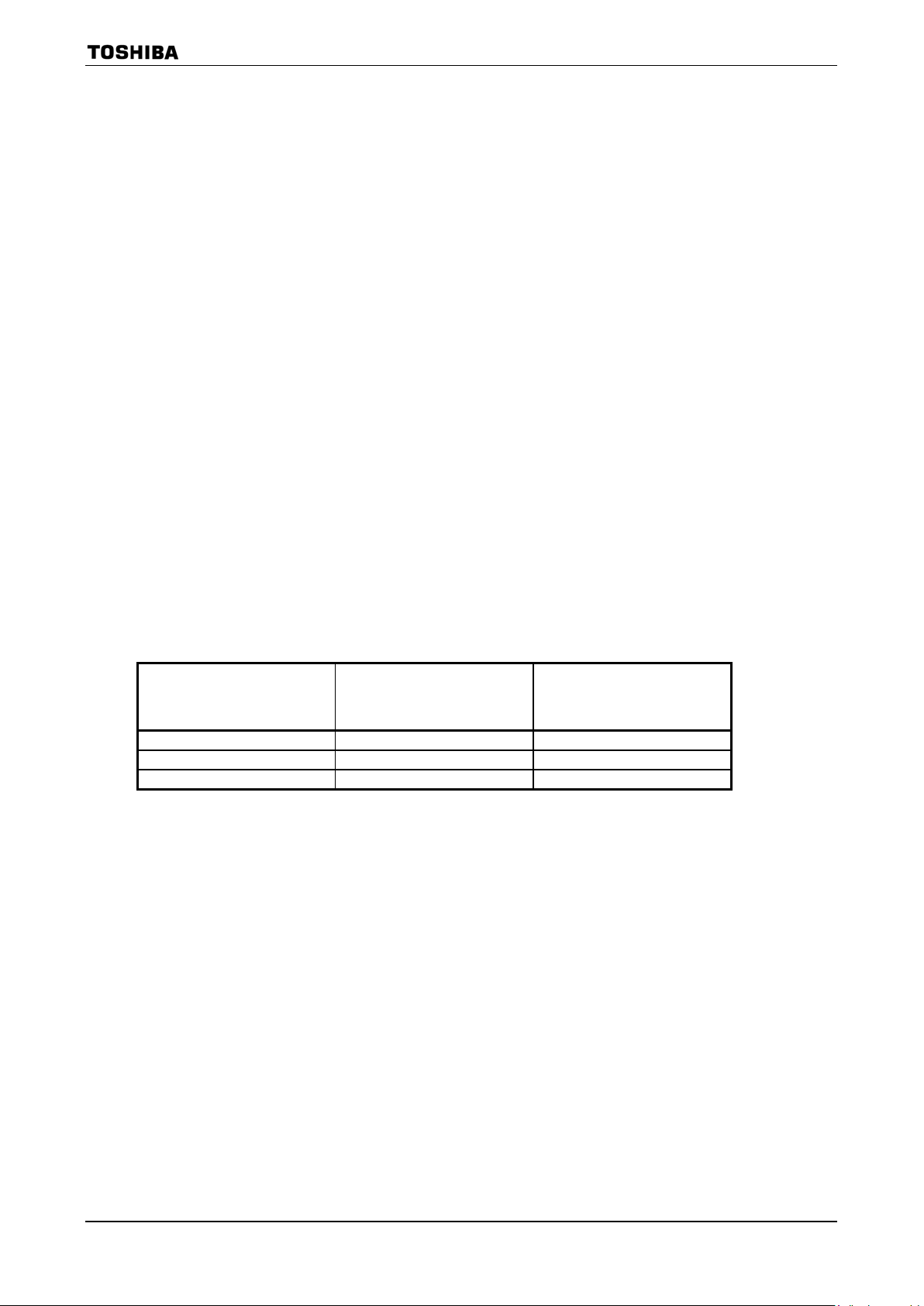

表 3.3.1 ウォームアップ時間 (クロック切り替え時)

ウォームアップ

タイム選択

SYSCR2<WUPTM1:0>

01 (28/発振周波数)

10 (214/発振周波数)

11 (216/発振周波数)

NORMAL へ切り替え時 (fc) SLOW へ切り替え時 (fs)

16 [µs] 7.8 [ms]

1.024 [ms] 500 [ms]

4.096 [ms] 2000 [ms]

計算値は

= 16 MHz,

f

OCSH

fs = 32.768 kHzの

場合です。

91C025-18

2003-12-05

Page 21

TMP91C025

設定例 1

高速クロック (fc) から低速クロック (fs) へ切り替える場合

SYSCR0 EQU 00E0H

SYSCR1 EQU 00E1H

SYSCR2 EQU 00E2H

LD (SYSCR2), −X11−−−−B;

SET 6, (SYSCR0) ;

SET 2, (SYSCR0) ;

WUP: BIT 2, (SYSCR0) ;

JR NZ, WUP ;

SET 3, (SYSCR1) ;

RES 7, (SYSCR0) ;

X: Don’t care、−: No change

ウォームアップ時間を 2

低速発振イネーブル

ウォームアップタイマクリア&スタート

ウォームアップ終了検出

高速 → 低速へ切り替え

高速発振ディセーブル

16

/fs に設定

<XEN>

X1, X2端子

<XTEN>

XT1, XT2端子

ウォームアップタイマ

ウォームアップ終了

<SYSCK>

システムクロックf

SYS

f

でカウントアップ

SYS

fsでカウントアップ

高速

低速

低速発振

イネーブル

ウォームアップタイマ

クリア&スタート

高速 → 低速

切り替え

ウォームアップ

終了

高速発振

ディセーブル

91C025-19

2003-12-05

Page 22

TMP91C025

設定例 2

低速クロック (fs) から高速クロック (fc) へ切り替える場合

SYSCR0 EQU 00E0H

SYSCR1 EQU 00E1H

SYSCR2 EQU 00E2H

LD (SYSCR2), −X10−−−−B ;

SET 7, (SYSCR0) ;

SET 2, (SYSCR0) ;

WUP: BIT 2, (SYSCR0) ;

JR NZ, WUP ;

RES 3, (SYSCR1) ;

RES 6, (SYSCR0) ;

X: Don’t care、−: No change

ウォームアップ時間を 2

高速発振イネーブル

ウォームアップタイマクリア&スタート

ウォームアップ終了検出

低速 → 高速へ切り替え

低速発振ディセーブル

14

/fc に設定

<XEN>

X1, X2端子

<XTEN>

XT1, XT2端子

ウォームアップタイマ

ウォームアップ終了

<SYSCK>

システムクロックf

SYS

f

でカウントアップ

SYS

fcでカウント アップ

低速

高速

高速発振

イネーブル

ウォームアップ

タイマクリア&スタート

ウォームアップ

終了

低速 → 高速

切り替え

低速発振

ディセーブル

91C025-20

2003-12-05

Page 23

TMP91C025

(2) クロックギア切り替え

SYSCR1<SYSCK> = “0” にて高速クロック fc を選択した場合、クロックギア選択レジ

スタ SYSCR1<GEAR2:0> により f

す。クロックギアを使用して f

FPH

を fc, fc/2, fc/4, fc/8, fc/16 のいずれかに設定できま

FPH

を切り替えることにより、消費電力の低減が図れます。

下記に、クロックギアの切り替え例を示します。

設定例 3

高速クロックのギア切り替え

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0000B ;

X: Don’t care

システムクロック f

を fc/2 へ切り替え

SYS

(高速クロックギア切り替え時の注意点)

クロックギアの切り替えは、設定例のように SYSCR1<GEAR2:0>レジスタへ値を書き込むこと

により実行されますが、書き込んだ後すぐには切り替わらず、数クロックの実行時間が必要となり

ます。よって、クロックギア切り替え命令の次の命令は、切り替え前のクロックギアで実行する場

合があります。クロックギア切り替え命令の次の命令から切り替え後のクロックで実行すべき場合

は、下記例のようなダミーの命令 (ライトサイクルが実行される命令) を挿入してください。

(例)

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0001B ;

LD (DUMMY), 00H ;

を fc/4 へ切り替え

f

SYS

ダミー命令

切り替え後のクロックギア

で実行すべき命令

(3) 内部クロックの端子出力機能

内部クロック f

を PA3 /SCOUT 端子から出力できます。

FPH

ポート A 関係のレジスタ PAFC2<PA3F2> = “1” に設定することにより PA3 端子は

SCOUT 出力端子になります。

91C025-21

2003-12-05

Page 24

A

3.3.4 プリスケーラ クロック制御部

内蔵 I/O (TMRA01∼TMRA23, SIO0∼SIO1) には、それぞれにクロックを分周するプリス

ケーラがあります。

TMP91C025

これらのプリスケーラへ入力するクロックφT0 は f

SYSCR0<PRCK1:0>で選択されたクロックを 4 分周したクロックです。

3.3.5 クロック逓倍回路 (DFM)

高速発振器の出力クロック f

より、発振器の周波数は低く内部クロックは高速にすることが可能です。

リセットにより DFM は停止状態となりますので、DFM を使用する場合は DFMCR0 レジ

スタへの設定が必要です。

この DFM はアナログ回路で構成されるため、動作許可後に発振器と同じように安定時間 (ロ

ックアップタイム) が必要となります。また、使用条件によって補正が必要です。(注 参照)

下記に DFM を使用し、fc を 4 逓倍したクロックに切り替える場合の設定例を示します。

設定例: f

DFMCR0 EQU 00E8H

DFMCR1 EQU 00E9H

LD (DFMCR1), 00001011B

LD (DFMCR0), 01X0XXXXB ;

LUP: BIT 5, (DFMCR0) ;

JR NZ, LUP ;

LD (DFMCR0), 10X0XXXXB ;

X: Don’t care

CT1:0

DFM出力: f

ロックアップタイマ

<DLUPFG>

システムクロックf

= 4 MHz で fc を 4 MHz から 16 MHz へ切り替える場合

OSCH

DFM

SYS

を 4 逓倍した f

OSCH

f

をカウントアップ

OSCH

DFM動作スタート、

ロックアップスタート

FPH,

クロックを出力する回路です。これに

DFM

DFM パラメータ決定

ロックアップ時間を 2

DFM 動作許可、ロックアップスタート

ロックアップ終了検出

fc を 4 → 16 MHz へ切り替え

を 2 → 8 MHz へ切り替え)

(f

SYS

ロックアップ中

12

/4 MHz にし、

4 → 16 MHz

切り替え

ロックアップ

終了

ロックアップ終了

fc/16 の 2 種類から

10 01

注) DFM への入力周波数制限および補正

DFM への入力周波数 (高速発振器の周波数) は下記の範囲内で使用してください。

• f

• f

= 4~9 MHz (VCC = 3.0 V~3.6 V): DFMCR1 に 0BH を書き込み

OSCH

= 4~6.75 MHz (VCC = 2.7 V~3.6 V): DFMCR1 に 0BH を書き込み

OSCH

91C025-22

2003-12-05

Page 25

TMP91C025

DFM 使用に関する制約

1. DFM の起動・停止等のコマンドは SLOW モード (f

(DFMCR0 <ACT1:0> レジスタへの書き込み)

制御はノーマルモードから行う必要があります。

2. DFM を使用している状態 (DFMCR0<ACT1:0> = “10”) から DFM動作を停止する場合は、f

→ f

OSCH

LD (DFMCR0),C0H ; f

LD (DFMCR0),00H ; DFM 停止

3. DFM を使用している状態 (DFMCR0<ACT1:0> = “10”) から高周波発振器を停止する場合は、

DFM を停止してから高周波発振器を停止してください。

設定例を下記に示します。

(1) 起動/切り替え制御

(OK) 低周波発振動作モード (f

LD (SYSCR0), 11−−−1−−B ;

WUP: BIT 2, (SYSCR0) ;

JR NZ, WUP ;

LD (SYSCR1), −−−−0−−−B ;

LD (DFMCR0), 01−0−−−−B;

LUP: BIT 5, (DFMCR0) ;

JR NZ, LUP ;

LD (DFMCR0), 10−0−−−−B;

(OK) 低周波発振動作モード (f

LD (SYSCR1), −−−−0−−−B ;

LD (DFMCR0), 01−0−−−−B;

LUP: BIT 5, (DFMCR0) ;

JR NZ, LUP ;

LD (DFMCR0), 10−0−−−−B;

(Error) 低周波発振動作モード (f

LD (SYSCR0), 11−−−1−−B ;

WUP: BIT 2, (SYSCR0) ;

JR NZ, WUP ;

LD (DFMCR0), 01−0−−−−B;

LUP: BIT 5, (DFMCR0) ;

JR NZ, LUP ;

LD (DFMCR0), 10−0−−−−B;

LD (SYSCR1), −−−−0−−−B ;

) では行わないでください。

S

切り替えと DFM 停止を同時に行わず、2 回に分けた手順にて行ってください。

→ f

DFM

) (高周波発振停止) → 高周波発振起動

S

→ 高周波発振動作モード (f

OSCH

) (高周波発振停止) → 高周波発振動作モード (f

S

→ DFM 起動 → DFM 使用モード (f

) (高周波発振停止) → 高周波発振起動 → DFM 起動

S

→ DFM 使用モード (f

DFM

)

切り替え

OSCH

) → DFM 起動 → DFM 使用モード(f

高周波発振起動/ウォームアップスタート

ウォームアップ終了フラグチェック

OSCH

から f

S

OSCH

から f

S

OSCH

から f

から f

S

システムクロックを f

DFM 起動/ロックアップスタート

ロックアップフラグ終了チェック

システムクロックを f

)

DFM

システムクロックを f

DFM 起動/ロックアップスタート

ロックアップフラグ終了チェック

システムクロックを f

高周波発振起動/ウォームアップスタート

ウォームアップ終了フラグチェック

DFM 起動/ロックアップスタート

ロックアップフラグ終了チェック

内部クロックを f

システムクロックを f

OSCH

から f

OSCH

から f

DFM

DFM

へ切り替え

へ切り替え

DFM

へ切り替え

へ切り替え

DFM

へ切り替え

へ切り替え

DFM

)

OSCH

DFM

)

91C025-23

2003-12-05

Page 26

(2) 停止/切り替え制御

TMP91C025

(OK) DFM 使用モード (f

→ 低周波発振動作モード (f

) → 高周波発振動作モード (f

DFM

) → 高周波発振器停止

S

) → DFM 停止

OSCH

LD (DFMCR0), 11−−−−−−B;

LD (DFMCR0), 00−−−−−−B;

LD (SYSCR1), −−−−1−−−B ;

LD (SYSCR0), 0−−−−−−−B ;

システムクロックを f

DFM 停止

システムクロックを f

高周波発振器停止

から f

DFM

OSCH

OSCH

から fSへ切り替え

へ切り替え

(Error) DFM 使用モード (f

) → 低周波発振動作モード (fS) → DFM 停止

DFM

→ 高周波発振器停止

LD (SYSCR1), −−−−1−−−B ;

LD (DFMCR0), 11−−−−−−B;

LD (DFMCR0), 00−−−−−−B;

LD (SYSCR0), 0−−−−−−−B ;

システムクロックを f

内部クロック (f

DFM 停止

高周波発振器停止

C

) を f

から fSへ切り替え

DFM

から f

DFM

OSCH

へ切り替え

(OK) DFM 使用モード (f

) → STOP モード設定 → 高周波発振動作モード (f

DFM

OSCH

)

→ DFM 停止 → ホルト (高周波発振器停止)

LD (SYSCR2), −−−−01−−B ;

LD (DFMCR0), 11−−−−−−B;

LD (DFMCR0), 00−−−−−−B;

HALT ;

STOP モード設定

(設定順番は DFM 使用以前でも OK)

から f

f

DFM

DFM 停止

STOP モードへ移行

OSCH

へ切り替え

(Error) DFM 使用モード (f

) → STOP モード設定 → ホルト (高周波発振器停止)

DFM

LD (SYSCR2), −−−−01−−B ;

HALT ;

STOP モード設定

(設定順番は DFM 使用以前でも OK)

STOP モードへ移行

91C025-24

2003-12-05

Page 27

3.3.6 ノイズ低減回路

EMI (不要輻射ノイズ) の低減、EMS (耐ノイズ対策) の強化を目的として、以下のような特

長を実現する回路を内蔵しています。

(1) 高速発振器のドライブ能力低減

(2) 低速発振器のドライブ能力低減

(3) 高速発振器のシングルドライブ化

(4) SFR プロテクトレジスタによる暴走対策

(5) ROM プロテクトレジスタによる暴走対策

(1)∼(5) は、EMCCR0~EMCCR3 レジスタによる設定が必要です。

以下に (1)∼(5) について説明します。

(1) 高速発振器のドライブ能力低減

(目 的)

外部に発振子を接続する場合に、発振器から出力される発振ノイズの抑制、発振器

の低消費電力化。

TMP91C025

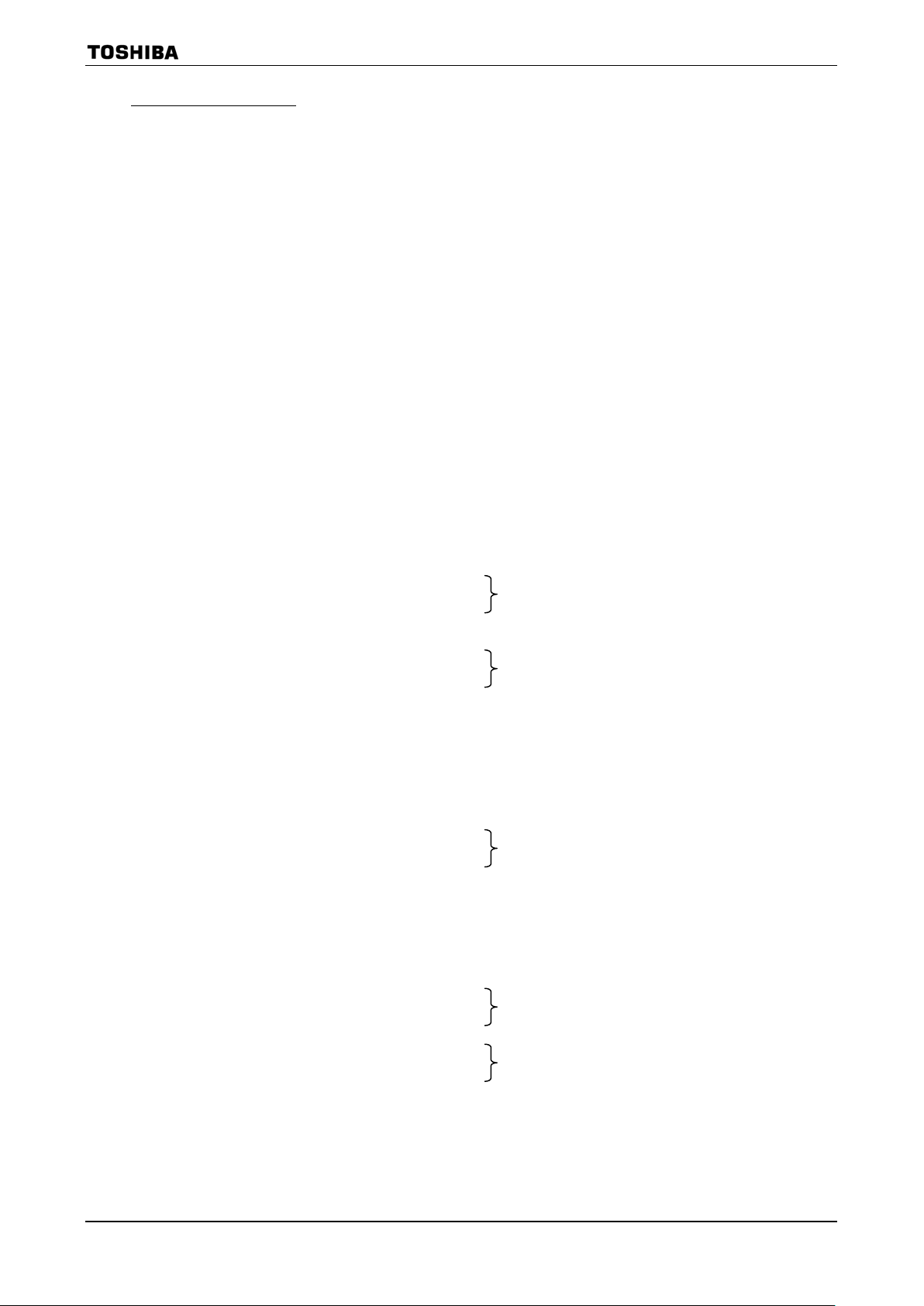

(ブロック図)

C1

発振子

C2

X1端子

発振イネーブル

EMCCR0<DRVOSCH>

X2端子

f

OSCH

(STOP+EMCCR0<EXTIN>)

(設定方法)

EMCCR0<DRVOSCH>に “0” を書き込むことにより発振器のドライブ能力は低減

します。リセットにより、<DRVOSCH>は “1” に初期化されますので、電源投入時

はノーマルのドライブ能力で発振開始します。

91C025-25

2003-12-05

Page 28

X

TMP91C025

(2) 低速発振器のドライブ能力低減

(目 的)

外部に発振子を接続する場合に、発振器から出力される発振ノイズの抑制、発振器

の低消費電力化。

(ブロック図)

C1

発振子

C2

T1端子

XT2端子

発振イネーブル

EMCCR0<DRVOSCL>

f

S

(設定方法)

EMCCR0<DRVOSCL>に “0” を書き込むことにより発振器のドライブ能力は低減

します。リセットにより、<DRVOSCL>は “1” に初期化されますので、電源投入時は

ノーマルのドライブ能力で発振開始します。

(3) 高速発振器のシングルドライブ化

(目 的)

外部に発振器を接続する場合に、ツインドライブの不要化、X2 端子開放時にノイ

ズ混入による誤動作防止。

(ブロック図)

X1端子

発振イネーブル(STOP+EMCCR0<EXTIN>)

f

OSCH

EMCCR0<DRVOSCH>

X2端子

(設定方法)

EMCCR0<EXTIN>に “1” を書き込むことにより発振回路は発振禁止となり、バッ

ファとして機能を開始します。X2 端子は “1” を出力状態となります。

リセットにより、<EXTIN>は “0” に初期化されます。

91C025-26

2003-12-05

Page 29

(4) SFR プロテクトレジスタによる暴走対策

(目 的)

ノイズ混入などによるプログラムの暴走時の対策。

暴走時の対策プログラムがクロックの停止、メモリ制御レジスタ (CS/WAIT コン

トローラ, MMU) の変更などによりフェッチ不可能な状態になることを防止するた

め、プロテクトをかけると特定の SFR をライト動作禁止にします。

また、INTP0 割り込みにより暴走時のエラー処理を容易にします。

特定の SFR 一覧

1. CS/WAIT コントローラ

B0CS, B1CS, B2CS, B3CS, BEXCS,

MSAR0, MSAR1, MSAR2, MSAR3,

MAMR0, MAMR1, MAMR2, MAMR3

2. MMU

LOCAL 0/1/2/3

3. クロックギア (EMCCR1, EMCCR2 は書き込み可能で

す)

TMP91C025

SYSCR0, SYSCR1, SYSCR2, EMCCR0, EMCCR3

4. DFM

DFMCR0, DFMCR1

(動作説明)

EMCCR1 と EMCCR2 レジスタに 2 重の鍵を設定することによりプロテクト (特

定の SFR へのライト動作) の実行、解除が可能となります。

(2 重の鍵)

1st-KEY: EMCCR1 に 5AH, EMCCR2 に A5H を連続ライト

2nd-KEY: EMCCR1 に A5H, EMCCR2 に 5AH を連続ライト

プロテクトの状態は、EMCCR0<PROTECT>をリードすることにより確認できま

す。

リセットにより、プロテクト OFF 状態となります。

また、プロテクト ON 状態にて特定の SFR へのライト動作が実行された場合に

INTP0 割り込みを出力します。これにより暴走時のエラー処理を容易にします。

91C025-27

2003-12-05

Page 30

(5) ROM プロテクトレジスタによる暴走対策

(目 的)

ノイズ混入などによるプログラムの暴走時の対策。

(動作説明)

プログラムの暴走により外部 3 種類の ROM に対しライト動作が実行された場合、

INTP1 割り込みを発生して暴走したことを CPU に知らせることが可能です。

3 種類の ROM は、フラッシュ ROM (オプションプログラム ROM)、データ ROM、

プログラム ROM で論理アドレスメモリマップ上、下記のように固定しています。

1. フラッシュ ROM: アドレス 400000H~7FFFFFH

2. データ ROM: アドレス 800000H~BFFFFFH

3. プログラム ROM: アドレス C00000H~FFFFFFH

これらのアドレスに対し、ライト動作検出の許可/禁止は EMCCR3<ENFROM,

ENDROM, ENPROM>で設定します。また、INTP1 割り込みが発生した際に、どの

ROM で発生したかは EMCCR3<FFLAG, DFLAG, PFLAG>で、それぞれモニタで

きます。このフラグは “0” を書き込むとクリアされます。

TMP91C025

91C025-28

2003-12-05

Page 31

3.3.7 スタンバイ制御部

(1) HALT モード

HALT 命令を実行すると、SYSCR2<HALTM1:0>の設定により、IDLE2, IDLE1, STOP

のいずれかの HALT モードになります。

IDLE2, IDLE1, STOP モードの特長は、次のとおりです。

a. IDLE2: CPU のみ停止するモードです。

表 3.3.2 IDLE2 モードでの内蔵 I/O 設定レジスタ

TMP91C025

内蔵 I/O は、SFR の中に IDLE2 モード時の動作/停止設定レジスタを 1

ビット持ち IDLE2 モードでの動作設定が可能です。

表 3.3.2に IDLE2 設定レジスタの表を示します。

内蔵 I/O

TMRA01 TA01RUN<I2TA01>

TMRA23 TA23RUN<I2TA23>

SIO0 SC0MOD1<I2S0>

SIO1 SC1MOD1<I2S1>

AD コンバータ

WDT WDMOD<I2WDT>

ADMOD1<I2AD>

SFR

b. IDLE1: 内部発振器と RTC、MLD のみ動作します。

c. STOP: すべての内部回路が停止します。

ホルト状態での各ブロックの動作を表 3.3.3に示します。

表 3.3.3 ホルト状態での各ブロックの動作

HALT モード

IDLE2 IDLE1 STOP

SYSCR2<HALTM1:0> 11 10 01

CPU

I/O ポート HALT 命令実行時の状態を保持 表 3.3.6, 表 3.3.7参照

動

TMRA

作

SIO

ブ

ロ

AD コンバータ

ッ

WDT

ク

LCDC, 割り込みコントローラ 動作

RTC, MLD

動作するブロックをプログラマ

ブルに選択可

停止

動作可

停止

91C025-29

2003-12-05

Page 32

(2) ホルト状態からの解除

ホルト状態からの解除は、割り込み要求、または、リセットにより行うことができます。

使用できるホルト解除ソースは、CPU のステータスレジスタ SR に割り付けられている割

り込みマスクレジスタ<IFF2:0> の状態と、HALT モードの組み合わせにより決まります。

詳細を表 3.3.4に示します。

• 割り込み要求による解除

割り込み要求によるホルト状態からの解除動作は、割り込み許可状態により異なり

ます。HALT 命令実行前に設定されている割り込み要求レベルが割り込みマスクレジ

スタの値以上であれば、ホルト解除後、その要因による割り込み処理を行い、 HALT

命令の次の命令から処理をスタートします。割り込み要求レベルが割り込みマスクレ

ジスタの値より小さい場合は、ホルト解除を行いません (ノンマスカブル割り込みで

は、マスクレジスタの値に関係なくホルト解除後、割り込み処理を行います)。

ただし、INT0∼INT3, INTKEY, INTRTC, INTALM0~INTALM4割り込みに限り、

割り込み要求レベルが割り込みマスクレジスタの値より小さい場合でも、ホルト状態

からの解除を行うことができます。この場合、割り込み処理は行わず HALT 命令の

次の命令から処理をスタートします (割り込み要求フラグは “1” を保持します)。

TMP91C025

注) 通常は割り込みによってホルト状態を解除することができますが、HALT モー

ドが IDLE1, STOP モードに設定されている状態 (IDLE2 は対象外) で、CPU

が HALT モードに移行しようとしている期間 (f

HALT モードを解除可能な割り込み (INT0~INT3, INTKEY, INTRTC,

INTALM0~INTALM4) が入力されても、ホルトが解除できない場合があります

(割り込み要求は内部に保留されます)。

HALT モードへ完全に移行された後に再度割り込みが発生すれば、問題なく

HALT モードを解除できますが、割り込み処理は内部に保留された割り込み

と現在の割り込みを比較し、その優先順位に従って順次処理されます。

• リセットによる解除

リセットにより、すべてのホルト状態からの解除を行うことができます。

ただし、STOP モードの解除では、発振器動作が安定するための十分なリセット時

間 (表 3.3.5を参照) が必要です。

約 5 クロックの間) に、

FPH

91C025-30

2003-12-05

Page 33

TMP91C025

表 3.3.4 ホルト解除ソースとホルト解除の動作

割り込み受け付け状態

HALT モード

INTWDT

ホルト解除ソース

INT0∼INT3 注)

INTALM0~INTALM4

割り込み

INTTA0∼INTTA3

INTRX0∼INTRX1, TX0∼TX1

INTAD

INTKEY

INTRTC

INTLCD

RESET

割り込み許可

(割り込みレベル) ≧ (割り込みマスク)

プログラマブル IDLE2

♦

♦

♦

♦

♦

♦

♦

♦

♦

IDLE1 STOP

×

♦

♦

♦

×

×

×

♦

♦

♦

×

LSI を初期化します。

(割り込みレベル) < (割り込みマスク)

プログラマブル IDLE2

×

1

*

×

×

×

×

1

*

×

×

割り込み禁止

IDLE1 STOP

−

○

○

×

×

×

○

○

×

○

○

○

○

−

○

×

×

×

○

×

♦: ホルト解除後、割り込み処理を開始します。

○: ホルト解除後、HALT 命令の次のアドレスから処理を開始します (割り込み処理は行いません)。

×: ホルト解除に使用できません。

−: ノンマスカブル割り込みの優先順位レベル (割り込み要求レベル) は最優先の “7” に固定されているた

め、この組み合わせはありません。

*1: ウォームアップ時間経過後にホルト解除を行います。

注) 割り込み許可状態において、レベルモードの INT0 割り込みによるホルト解除を行う場合、割り込み

処理が開始されるまで “H” レベルを保持してください。それ以前で “L” レベルにした場合は、正しい

割り込み処理を開始できません。

(ホルト状態からの解除例)

−

1

*

×

×

×

×

1

*

×

×

IDLE1 モードのホルト状態をエッジモードの INT0 割り込みにより解除する場合。

アドレス

8203H LD (IIMC), 00H ;

8206H LD (INTE0AD), 06H ;

8209H EI 5 ;

820BH LD (SYSCR2), 88H ;

820EH HALT ;

INT0

RETI

820FH LD XX, XX

INT0 割り込み立ち上がりエッジを選択

INT0 割り込みレベルを “6” に設定

CPU 割り込みレベルを “5” に設定

IDLE1 モードに設定

CPU 停止

INT0 割り込み処理

91C025-31

2003-12-05

Page 34

TMP91C025

(3) 各モードの動作

a. IDLE2 モード

IDLE2 モードでは、各内蔵 I/O の SFR 中にある IDLE2 設定レジスタで指定した

内蔵 I/O のみ動作し、CPU の命令実行動作は停止します。

IDLE2 モードの割り込みによるホルト解除のタイミング例を図 3.3.6に示します。

X1

A0∼A23

D0∼D15

RD

データ データ

WR

ホルト解除

割り込み

IDLE2

モード

図 3.3.6 割り込みによるホルト解除のタイミング例 (IDLE2 モード時)

b. IDLE1 モード

IDLE1 モードでは、内部発振器と RTC, MLD のみ動作し、システムクロックは停

止します。また、IDLE1 モード時の端子状態は、SYSCR2<SELDRV,DRVE>の設定

により異なります。IDLE1 モード時の端子状態を表 3.3.6、表 3.3.7に示します。

ホルト状態での割り込み要求のサンプリングは、システムクロックと非同期に行わ

れますが、解除 (動作の再開) は同期して行われます。

IDLE1 モードの割り込みによるホルト解除のタイミング例を図 3.3.7に示します。

X1

A0∼A23

D0∼D15

RD

WR

ホルト解除

割り込み

データ データ

IDLE1

モード

図 3.3.7 割り込みによるホルト解除のタイミング例 (IDLE1 モード時)

91C025-32

2003-12-05

Page 35

TMP91C025

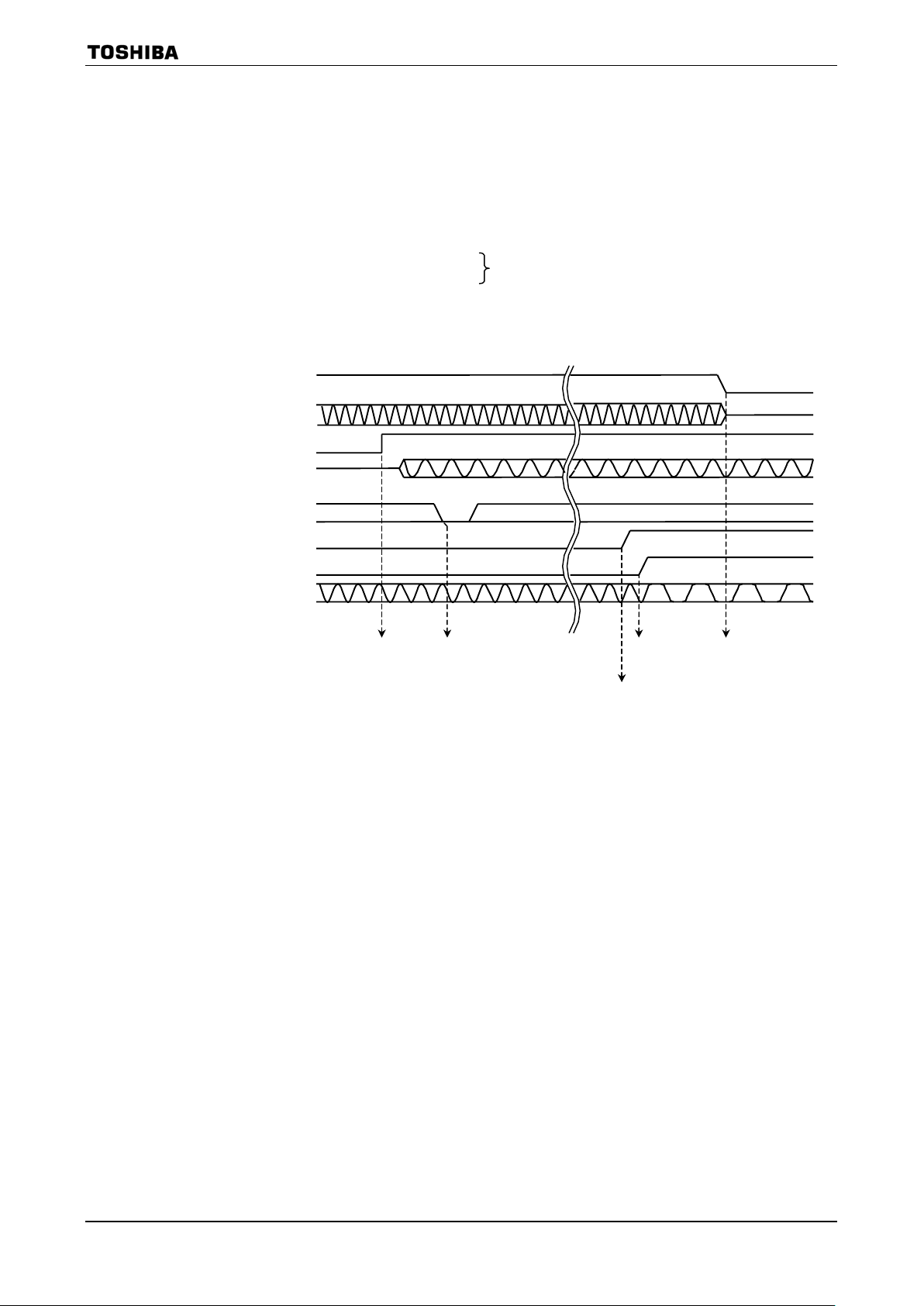

c. STOP モード

STOP モードでは、内部発振器も含めてすべての内部回路が停止します。また、STOP

モード時の端子状態は、SYSCR2<SELDRV,DRVE>の設定により異なります。STOP モー

ド時の端子状態を表 3.3.6、表 3.3.7に示します。

STOP モードを解除する場合は、内部発振器の安定化のため、ウォームアップ用カウン

タによるウォームアップ時間経過後に、システムクロックの出力を開始します。STOP

モード解除後は、SYSCR0<RXEN, RXTEN, RSYSCK>の設定に従い動作を開始します

(ホルト解除後の動作モード (NORMAL/SLOW) を選択できます)。この設定は HALT 命令

実行前に行う必要があります。このウォームアップ時間の設定は、SYSCR2<WUPTM1:0>

で行います。表 3.3.5に設定例を示します。

STOP モードの割り込みによるホルト解除のタイミング例を図 3.3.8に示します。

X1

ウォーム

アップ時間

A0∼A23

D0∼D15

RD

データ データ

WR

ホルト解除

割り込み

STOP

モード

図 3.3.8 割り込みによるホルト解除のタイミング例 (STOP モード時)

表 3.3.5 ウォームアップ時間の設定例 (STOP モード解除時)

@ f

SYSCR0

<RSYSCK>

0 (fc) 16 µs 1.024 ms 4.096 ms

1 (fs) 7.8 ms 500 ms 2000 ms

8

) 10 (214) 11 (216)

01 (2

SYSCR2<WUPTM1:0>

= 16 MHz, fs = 32.768 kHz

OSCH

91C025-33

2003-12-05

Page 36

(設定例) 低速クロックで動作している状態で STOP モードに入り、INTx 割り込みによる解除

後、高速クロックで動作させる場合。

アドレス

SYSCR0 EQU 00E0H

SYSCR1 EQU 00E1H

SYSCR2 EQU 00E2H

8FFDH LD (SYSCR1), 08H ;

9000H LD (SYSCR2), −X1001−1B ;

9002H LD (SYSCR0), 011000 − −B;

9005H HALT

INTx 端子入力

9006H LD XX, XX RETI

= fs/2

f

SYS

ウォームアップ時間 2

解除後、高速クロック

14

/f

OSCH

ウォームアップタイマ

クリア&スタート

(高速クロック)

INT 割り込み処理

−: No change

TMP91C025

終了

注) 上記のように STOP モードの前後で異なる動作モードを使用する場合、HALT 命令を実行

中 (6 ステート期間) にホルト解除割り込みが受け付けられると、動作モードの変更が行

われないままホルト解除を行うことがあります。HALT 命令実行中に割り込みが入力され

るようなシステムでは、STOP モードの前後で同じ動作モードを設定してください。

91C025-34

2003-12-05

Page 37

TMP91C025

OFF

OFF

OFF

ON

HALT中 (IDLE1/STOP)

条件 A 設定時(注) 条件 B 設定時(注)

機能

設定時

OFF

ON ON

OFF ON

入力ポート

設定時

OFF

OFF

IDLE1

でON, STOPでOFF

機能

設定時

OFF

入力ポート

設定時

OFF

ON ON

OFF

OFF

ON

- OFF

/RESET,

表 3.3.6 入力バッファ状態表

入力バッファ状態

ポート名

D0-7 - - - - -

P10-17 D8-15

P56 (*1) /WAIT ON ON

P80-82 (*2) - - - - -

P83 (*2) /ADTRG

P90 (*1) KI0

P91 (*1) KI1

P92 (*1) KI2

P93 (*1) KI3

P94 (*1) KI4

P95 (*1) KI5

P96 (*1) KI6

P97 (*1) KI7

PB3 INT0,/PS

PB4 INT1,TA0IN

PB5 INT2

PB6 INT3

PC0 -

PC3 (*1) -

PC1 RXD0

PC2 SCLK0,/CTS0

PC4 RXD1

PC5 (*1) SCLK1,/CTS1

PZ2-Z3 - -

AM0,AM1

X1,XT1 -

注)条件 A / B の設定を示します。

入力

機能名

- ON - ON -

:常時バッファがONしているため,、入力端子がドラ

ON

イブされてないと入力バッファに貫通電流が流れま

す。

:常時バッファがOFFしています *2:AIN入力では貫通電流が流れません

OFF

-:対象なし

(SYSCR2)

<DRVE> <SELDRV> IDLE1 STOP

0 0 条件 A

0 1

1 0

1 1

リセット中

OFF

OFF

ON ON ON ON

OFF

ON

レジスタ設定 HALT モード

CPU動作中 HALT中 (IDLE2)

機能

設定時

外 部 リード

で

ON ON

ON ON

ON - ON -

入力ポート

設定時

ON

- - - -

条件 B

ON

ポートリード

で

ON

ON

機能

設定時

OFF

*1

:Pull-Up/Down抵抗付きポートです。

条件 A

条件 B

入力ポート

設定時

ON ON

- OFF -

91C025-35

2003-12-05

Page 38

TMP91C025

表 3.3.7 出力バッファ状態表

出力バッファ状態

ポート名

D0-7 - - - - -

P10-17 D8-15

A0-15 - - - - -

P20-27 A16-23

P56 (*1) - OFF - - - -

P60 /CS0

P61 /CS1

P62 /CS2,/CS2A

P63 /CS3

P64 EA24,/CS2B,/SRLB

P65 EA25,/CS2C,/SRUB

PA0

PA1 KO1,TA1OUT

PA2 KO2,TA3OUT

PA3 KO3,SCOUT

PB3-B4 - -

PB5 PX

PB6 PY

PC0 TXD0

PC1,C4 - - - - -

PC2 SCLK0

PC3 (*1) TXD1

PC5 SCLK1

PD0 (*1) D1BSCP

PD1 D2BLP

PD2 D3BFR

PD3 DLEBCD

PD4 DOFFB

PD7 MLDALM

/RD,/WR -

PZ2 (*1) /HW R

PZ3 (*1) R/W,/SRWR

X2 -

XT2 -

出力

機能名

KO0,/ALARM,

/MLDALM

:常時バッファがONしています。ただし、バス開放時は

ON

特定の端子の出力バッファはOFFします。

:常時バッファがOFFしています

OFF

-:対象なし

リセット中

OFF

ON ON ON

ON ON ON OFF ON

OFF

ON

OFF

ON ON - ON -

CPU動作中

機能

設定時

外部 ライト

で

出力ポート

設定時

ON

ON ON

ON

ON

ON

- - ON - -

ON ON OFF ON

- - - -

ON

HALT中 (IDLE2) HALT中 (IDLE1/STOP)

機能

設定時

OFF

*1

:Pull-Up/Down抵抗付きポートです。

出力ポート

設定時 機能設定時

ON OFF

ON

-

ON

ON

条件 A 設定時(注) 条件 B 設定時(注)

OFF

-

OFF

OFF

出力ポート

設定時

OFF

OFF

でON, STOPで”H”レベル出力

IDLE1

でON, STOPでHigh-Z

IDLE1

機能

設定時

OFF

ON

-

ON

ON

出力ポート

設定時

ON

ON

ON

注)条件 A / B の設定を示します。

(SYSCR2)

<DRVE> <SELDRV> IDLE1 STOP

レジスタ設定 HALT モード

0 0 条件 A

0 1

1 0

1 1

条件 B

条件 A

条件 B

91C025-36

2003-12-05

Page 39

3.4 割り込み

割り込みは、CPU の割り込みマスクレジスタ SR<IFF2:0>と、内蔵の割り込みコントローラに

よって制御されます。

割り込み要因には、下記に示す合計 37 本があります。

• CPU からの割り込み ・・・ 9 本

• 外部端子 (INT0∼INT3, INTKEY) ・・・5 本

• 内蔵 I/O からの割り込み ・・・ 23 本

各割り込み要因ごとに、個別の割り込みベクタ番号 (固定) が割り当てられており、マスカブル割

り込みのそれぞれに、6 レベルの優先順位 (可変) を割り付けることができます。ノンマスカブル割

り込みの優先順位は、最優先の “7” に固定されています。

割り込みが発生すると、割り込みコントローラは、その割り込み要因の優先順位値を CPU に送

ります。同時に複数の割り込みが発生した場合は、最も高い優先順位値(最高はノンマスカブル割

り込みの “7”)を CPU に送ります。

TMP91C025

(ソフトウエア割り込み、未定義命令実行違反)

CPU は、その送られてきた優先順位値と、CPU の割り込みマスクレジスタ<IFF2:0>の値を比較

し、送られてきた優先順位値が割り込みマスクレジスタの値以上であれば、その割り込みを受け付

けます。<IFF2:0>の値は EI 命令 (EI num/IFF <2:0> の内容が num) を使用して書き替えること

ができます。例えば、“EI 3” とプログラムすると、割り込みコントローラに設定された優先順位値

3 以上のマスカブル割り込みと、ノンマスカブル割り込みが受け付け可能となります。また、DI

命令 (<IFF2:0> が 7) は動作的には “EI 7” と同じですが、マスカブル割り込みの優先順位値が 0∼6

であるため、マスカブル割り込みの受け付け禁止用として使用されます。なお、EI 命令は実行後

直ちに有効となります。

上記汎用割り込み処理モードに加えて、「マイクロ DMA」処理モードがあります。マイクロ DMA

は、CPU が自動的にデータの転送 (1/2/4 バイト) を行うモードです。内部/外部メモリおよび内蔵

I/O に対するデータ転送を、高速に行うことができます。

さらに、このマイクロ DMA 要求を割り込み要因から与えられる以外に、ソフトで要求をかける

“ソフトスタート機能” があります。

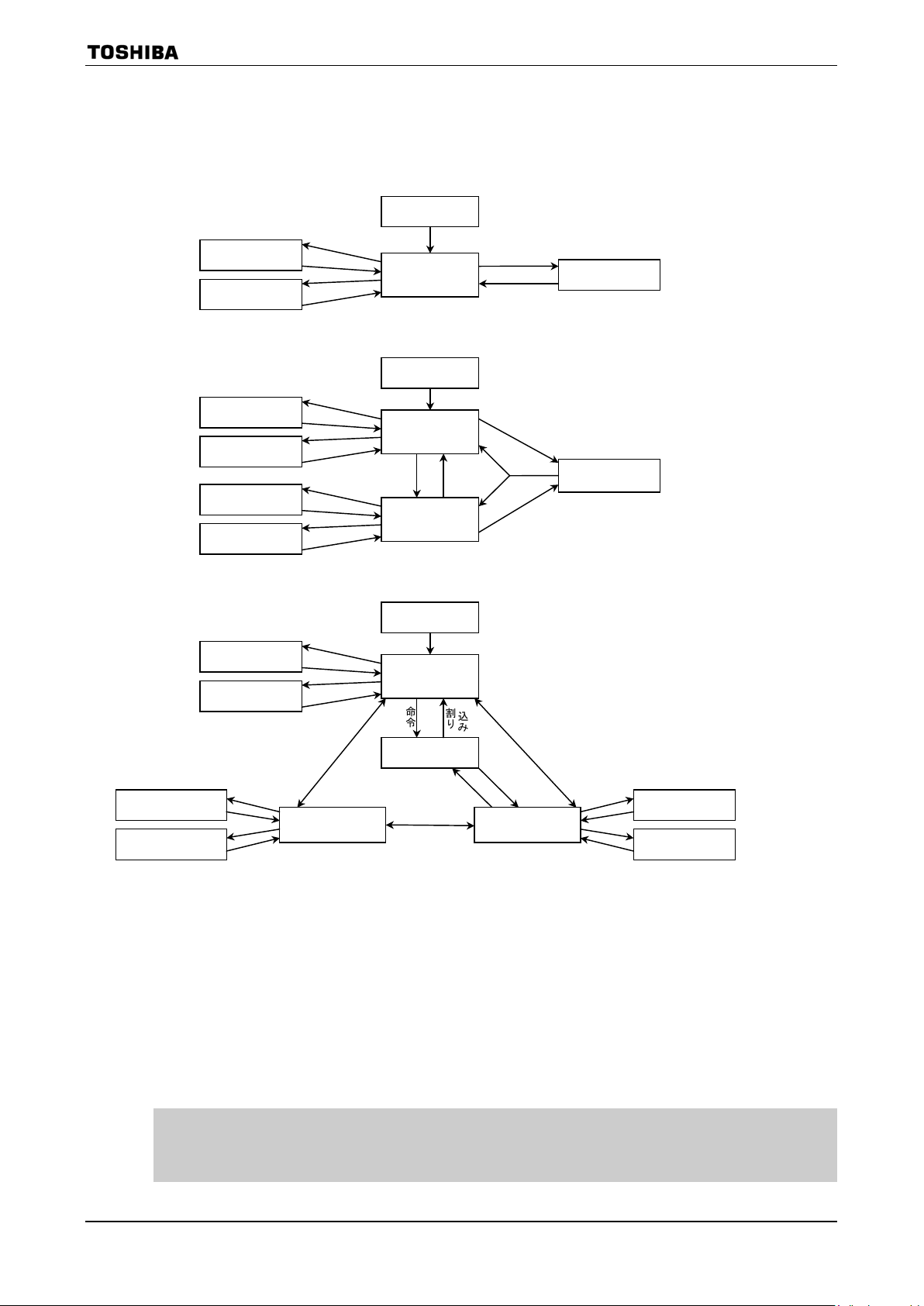

図 3.4.1に割り込み処理全体のフローを示します。

91C025-37

2003-12-05

Page 40

汎用割り込み

処 理

割り込み処理

マイクロDMA

マイクロDMA

起動ベクタで指定された

割り込み?

No

割り込みベクタVのリード

割り込み要求フラグ のクリア

PUSH PC

PUSH SR

SR<IFF2:0> ←受け付けた

割り込み

レベル + 1

INTNEST ← INTN EST + 1

PC ← (FFFF00H + V)

割り込み処理

プログラム

RETI 命令

POP SR

POP PC

INTNEST←INTNEST − 1

終 了

Yes

割り込み要求F/Fのクリア

マイクロDMAによる

データ転送

COUNT ← COUNT − 1

COUNT = 0

No

Yes

ソフトスタート要求

マイクロDMA

処 理

INTTC割り込み発生

マイクロDMA起動ベクタ

レジスタのクリア

TMP91C025

図 3.4.1 割り込み処理全体のフロー

91C025-38

2003-12-05

Page 41

3.4.1 汎用割り込み処理

CPU が割り込みを受け付けると、下記の動作をします。なお、この動作は TLCS-900/L,

TLCS-900/H と同様です。

(1) CPU は、割り込みコントローラから、割り込みベクタをリードします。

割り込みコントローラは、同一レベルに設定された割り込みが同時に発生した場合、

デフォルト・プライオリティ (固定: ベクタ値が小さいほど優先順位が高い) に従って

割り込みベクタを発生し、その割り込み要求をクリアします。

(2) CPU は、プログラムカウンタ「PC」とステータスレジスタ「SR」を、スタック領

域 (XSP が示す領域) へ PUSH します。

(3) CPU の割り込みマスクレジスタ <IFF2:0> の値を、受け付けた割り込みレベルより

“1” だけ高い値にセットします。ただし、値が “7” のときは、インクリメントせず “7”

をセットします。

(4) 割り込みネスティングカウンタ INTNEST を、+1 します。

(5) CPU は、「FFFF00H + 割り込みベクタ」のデータで示されるアドレスへジャンプし、

割り込み処理ルーチンを開始します。

上記の処理時間は、ベストケース (メモリは 16 ビットデータバス幅 0 ウェイト) の場合、18

ステート (2.25 ns @ 16 MHz) です。

割り込み処理が終了し、メインルーチンに戻るときは、通常「RETI」命令で行います。こ

の命令を実行すると、スタックからプログラムカウンタ PC とステータスレジスタ SR の内容

を復帰し、割り込みネスティングカウンタ INTNEST を−1 します。

ノンマスカブル割り込みは、プログラムによって割り込み受け付けを禁止することができま

せん。マスカブル割り込みはプログラムによって割り込みの許可/禁止が選択できるとともに、

各割り込みソースごとに優先順位を設定することができます。CPU が持つ <IFF2:0> の値以

上の優先順位値をもつ割り込み要求があると、割り込みを受け付けます。そして、CPU の

<IFF2:0> に、受け付けた優先順位に “1” を加えた値を、セットします。従って、割り込み処

理中に、現在実行している割り込みよりも高いレベルの割り込みが発生した場合には、その割

り込み要求を受け付け、割り込み処理のネスティング状態になります。

TMP91C025

なお、CPU が割り込みを受け付け、前記 (1)∼(5) までの処理をしている間に発生した別の

割り込み要求は、その割り込み処理ルーチンの先頭命令が実行された直後にサンプリングさ

れます。先頭命令を DI 命令にすると、マスカブル割り込みのネスティングを禁止することが

できます。

リセット後、CPU の <IFF2:0> は、“7” に初期化されているため、マスカブル割り込み禁止

状態になっています。

アドレス FFFF00H∼FFFFFFH (256 バイト) が、割り込みベクタ領域に割り当てられてい

ます。表 3.4.1に割り込みテーブルを示します。

91C025-39

2003-12-05

Page 42

TMP91C025

表 3.4.1 TMP91C025 の割り込みテーブル

デフォルト

プライオリティ

1

2

3

4

5

6

7

8

9

−

10

11

12

13

14 INTALM0: ALM0 (8 kHz) 0038H FFFF38H 0E H

15 INTALM1: ALM1 (512 Hz) 003CH FFFF3CH 0FH

16 INTALM2: ALM2 (64 Hz) 0040H FFFF40H 10H

17 INTALM3: ALM3 (2 Hz) 0044H FFFF44H 11H

18 INTALM4: ALM4 (1 Hz) 0048H FFFF48H 12H

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

タイプ 割り込み要因 ベクタ値

ノン

マスカブル

マスカブル

“リセット”「SWI 0」命令

「SWI 1」命令

INTUNDEF: 未定義命令実行違反、または「SWI 2」命令

「SWI 3」命令

「SWI 4」命令

「SWI 5」命令

「SWI 6」命令

「SWI 7」命令

INTWD: ウォッチドッグタイマ

(マイクロ DMA)

INT0 端子

INT1 端子

INT2 端子

INT3 端子

INTTA0: 8ビットタイマ 0

INTTA1: 8ビットタイマ 1

INTTA2: 8ビットタイマ 2

INTTA3: 8ビットタイマ 3

INTRX0: シリアル受信 (チャネル 0)

INTTX0: シリアル送信 (チャネル 0)

INTRX1: シリアル受信 (チャネル 1)

INTTX1: シリアル送信 (チャネル 1)

INTAD: AD変換終了

INTKEY: キーウェイクアップ

INTRTC: RTC (アラーム割り込み)

INTLCD: LCDC/LP 端子

INTP0: プロテクト 0 (特定 SFR への WR)

INTP1: プロテクト 1 (ROM への WR)

INTTC0: マイクロ DMA 終了 (チャネル 0)

INTTC1: マイクロ DMA 終了 (チャネル 1)

INTTC2: マイクロ DMA 終了 (チャネル 2)

INTTC3: マイクロ DMA 終了 (チャネル 3)

(Reserved)

:

(Reserved)

0000H FFFF00H −

0004H FFFF04H −

0008H FFFF08H −

000CH FFFF0CH −

0010H FFFF10H −

0014H FFFF14H −

0018H FFFF18H −

001CH FFFF1CH −

0024H FFFF24H −

− − −

0028H FFFF28H 0AH

002CH FFFF2CH 0BH

0030H FFFF30H 0CH

0034H FFFF34H 0DH

004CH FFFF4CH 13H

0050H FFFF50H 14H

0054H FFFF54H 15H

0058H FFFF58H 16H

005CH FFFF5CH 17H

0060H FFFF60H 18H

0064H FFFF64H 19H

0068H FFFF68H 1AH

006CH FFFF6CH 1BH

0070H FFFF70H 1CH

0074H FFFF74H 1DH

007CH FFFF7CH 1FH

0080H FFFF80H 20H

0084H FFFF84H 21H

0088H FFFF88H −

008CH FFFF8CH −

0090H FFFF90H −

0094H FFFF94H −

0098H

:

00FCH

ベクタ参照

アドレス

FFFF98H

:

FFFFFCH

マイクロ

DMA 起動

ベクタ

−

:

−

91C025-40

2003-12-05

Page 43

3.4.2 マイクロ DMA

汎用割り込み処理に加えて、マイクロ DMA 機能があります。マイクロ DMA に設定された

割り込み要求は、設定された割り込みレベルにかかわらず、マスカブル割り込みの中で最も高

い割り込みレベルで処理を行います。

マイクロ DMA は 4 チャネル用意されており、バースト指定により連続転送が可能です。

なお、マイクロ DMA 機能は CPU の協調動作によって実現されているため、CPU が HALT

命令を実行しスタンバイ状態になると、マイクロ DMA の要求は無視 (保留) されます。

(1) マイクロ DMA の動作

マイクロ DMA は、マイクロ DMA 起動ベクタレジスタで指定された割り込み要求が発

生すると、割り込み要求元の割り込みレベルにかかわらず、CPU に対しマスカブル割り

込みの中で最も優先順位の高いレベルでデータ転送処理を行います。<IFF2:0> = “7” のと

きは、マイクロ DMA の要求は受け付けられません。

マイクロ DMA は 4 チャネル用意されており、同時に 4 種類までの割り込み要因に対し

て、マイクロ DMA を設定することができます。

マイクロ DMA が受け付けられると、そのチャネルに割り当られている割り込み要求フ

ラグをクリアし、コントロールレジスタに設定された、転送元アドレスから転送先アドレ

スに、データ転送が一回 (1/2/4 バイト) 行われ、転送数カウンタをデクリメントします。

デクリメントした結果が “0” ならば、CPU はマイクロ DMA 転送終了を割り込みコントロ

ーラに伝え、割り込みコントローラは、マイクロ DMA 転送終了割り込み (INTTCn) を発

生させ、かつ、マイクロ DMA 起動ベクタレジスタ DMAnV の値を “0” クリアして、次の

マイクロ DMA 起動を禁止し、マイクロ DMA 処理を終了します。デクリメントした結果

が “0” でない場合、バースト指定がなければ、マイクロ DMA 処理は終了します。この場

合、転送終了割り込み

割り込み要因をマイクロ DMA 起動のみに使用する場合は、割り込みレベルを “0” にし

ておく必要があります。これは、マイクロ DMA 起動ベクタに設定されるまでの間に、そ

の割り込み要求が発生すると、割り込みレベルが 1∼6 の場合、CPU は汎用割り込み処理

を行うためです。割り込み要因をマイクロ DMA と汎用割り込みの起動で兼用する場合は、

その割り込み要因の割り込みレベルを、ほかのすべての割り込み要因の割り込みレベルよ

り低くする必要があります。なお、その割り込み要因は、エッジ割り込みに限られます。

マイクロ DMA 転送終了割り込みは、ほかのマスカブル割り込みと同様に割り込みレベ

ルとデフォルトプライオリティにより、優先順位が決まります。

TMP91C025

(INTTCn) は発生しません。

また、複数チャネルのマイクロ DMA 要求が、同時に発生した場合の優先順位は、割り

込みレベルに無関係で、チャネル番号の若い方が高くなります。(CH0 (高) → CH3 (低))

転送元/転送先アドレスを設定するレジスタは、32 ビット幅のコントロールレジスタに

なっていますが、アドレスは 24 本しか出力されていないため、マイクロ DMA で取り扱

える空間は、16 M バイトとなります。

91C025-41

2003-12-05

Page 44

TMP91C025

転送モードは、1/2/4 バイト転送の 3 種類があり、それぞれの転送モードに対して、転

送後、転送元/転送先アドレスをインクリメント、デクリメント、固定するモードを用意し

ています。このモードにより、メモリからメモリ、I/O からメモリ、メモリから I/O、I/O

から I/O のデータ転送を簡単に行えます。転送モードの詳細は、3.4.2 (4)「転送モードレ

ジスタ」を参照してください。

転送数カウンタは、16 ビット幅で構成されているため、1 つの割り込み要因に対して最

大 65536 回 (転送カウンタの初期値が 0000H のとき最大) の、マイクロ DMA 処理を行う

ことができます。

マイクロ DMA 処理を行うことのできる割り込み要因は、表 3.4.1でマイクロ DMA 起

動ベクタのある 24 種類の割り込みとソフトスタートによる計 25 種類です。

転送先アドレス INC モード 2 バイト転送 (カウンタモード以外は同様) のマイクロ DMA

サイクルを図 3.4.2に示します。(全アドレスエリア 16 ビットバス, 0 ウェイト, ソース/デ

スティネーションアドレスとも偶数の場合)

1ステート

注1) 注2)

A0∼A23

DM1 DM2 DM3 DM4 DM5 DM6 DM7 DM8

X1

ソース

RD

デスティネーション

WR , HWR

D0∼D15

出力 入力

図 3.4.2 マイクロ DMA サイクル図

第 1∼3ステート: 命令フェッチ・サイクル (次の命令コードを先取りします)

命令キューバッファに 3

バイト以上の命令コードが入ると、

このサイクルはダミーサイクルになります。

第 4∼5ステート: マイクロ DMA リード・サイクル

第 6ステート: ダミーサイクル (アドレスバスは第 5 ステート状態のままです)

第 7∼8ステート: マイクロ DMA ライトサイクル

注 1) ソースアドレスエリアが 8ビットバスの場合、+2 ステートされます。

また、ソースアドレスエリアが 16 ビットバスで奇数アドレスから始まる場合も、

+2 ステートされます。

注 2) デスティネーションアドレスエリアが 8 ビットバスの場合、+2 ステートされます。

また、デスティネーションアドレスエリアが 16 ビットバスで奇数アドレスから始

まる場合も、+2 ステートされます。

91C025-42

2003-12-05

Page 45

TMP91C025

(2) ソフトスタート機能

割り込み要因によるマイクロ DMA の起動以外に、DMAR レジスタへの書き込みサイク

ルが発生したことによりマイクロ DMA を起動する “マイクロ DMA ソフトスタート機能”

があります。

DMAR レジスタの各ビットに “1” を書き込むことにより、マイクロ DMA を一回起動す

ることができます。転送が終了すると、終了したチャネルに対応する DMAR レジスタの

ビットが、自動的に “0” クリアされます。なお、仕様書の制限として一度に1チャネルし

か起動できません。(複数のビットに “1” を書き込まないでください)

また、再度 DMAR レジスタに “1” を書き込む場合は、そのビットが “0” であることを

確認してから行ってください。

DMAB レジスタでバースト指定されている場合は、マイクロ DMA を起動するとマイク

ロ DMA 転送カウンタが “0” になるまで、連続的にデータ転送されます。

記号 名称 アドレス 7 6 5 4 3 2 1 0

DMA 要求

DMAR

DMA

request

register

89H

DMAR3 DMAR2 DMAR1 DMAR0

R/W

0 0 0 0

(3) 転送制御レジスタ

転送元アドレス, 転送先アドレスは、下記の CPU 内レジスタで設定します。これらのレ

ジスタは「LDC cr, r」命令を使用して、データの設定を行います。

チャネル 0

DMAS0

DMAD0

DMAC0

DMAM0

チャネル 3

DMAS3

DMAD3

DMAC3

DMAM3

32ビット

8ビット

16 ビット

転送元アドレスレジスタ 0 ; 下位 24 ビットのみ使用

転送先アドレスレジスタ 0 ; 下位 24 ビットのみ使用

転送数カウンタレジスタ 0 ; 1∼65536

転送モードレジスタ 0

転送元アドレスレジスタ 3

転送先アドレスレジスタ 3

転送数カウンタレジスタ 3

転送モードレジスタ 3

91C025-43

2003-12-05

Page 46

(DMAM0∼DMAM3)

0 0 0

0 0 Z Z

0

0 0 1 Z Z

0 1 0 Z Z

0 1 1 Z Z

1 0 0 Z Z

1 0 1 0 0

(4) 転送モードレジスタ: DMAM0∼DMAM3

モード

注) このレジスタに値を設定するとき、

上位 3ビットは “0” にしてください。

ZZ: 0 = バイト転送、1 = ワード転送、2 = 4 バイト転送、3 = Reserved

転送先アドレス INCモード.......................................I/O toメモリ用

(DMADn+) ← (DMASn)

DMACn ← DMACn − 1

if DMACn = 0 then INTTC 発生

転送先アドレス DEC モード .....................................I/O toメモリ用

(DMADn−) ← (DMASn)

DMACn ← DMACn − 1

if DMACn = 0 then INTTC 発生

転送元アドレス INCモード......................................メモリ to I/O 用

(DMADn) ← (DMASn+)

DMACn ← DMACn − 1

if DMACn = 0 then INTTC 発生

転送元アドレス DEC モード ....................................メモリ to I/O用

(DMADn) ← (DMASn−)

DMACn ← DMACn − 1

if DMACn = 0 then INTTC 発生

アドレス固定モード...................................................... I/O to I/O用

(DMADn) ← (DMASn)

DMACn ← DMACn − 1

if DMACn = 0 then INTTC 発生

カウンタ・モード................................割り込み発生回数カウント用

DMASn ← DMASn + 1

DMACn ← DMACn − 1

if DMACn = 0 then INTTC 発生

TMP91C025

実行時間

8ステート(1000 ns)

@バイト/ワード転送

12 ステート(1500 ns)

@4バイト転送

8ステート(1000 ns)

@バイト/ワード転送

12 ステート(1500 ns)

@4バイト転送

8ステート(1000 ns)

@バイト/ワード転送

12 ステート(1500 ns)

@4バイト転送

8ステート(1000 ns)

@バイト/ワード転送

12 ステート(1500 ns)

@4バイト転送

8ステート(1000 ns)

@バイト/ワード転送

12 ステート(1500 ns)

@4バイト転送

5ステート

(625 ns)

注 1) n: 対応するマイクロ DMA チャネル 0∼3

DMADn+/DMASn+: ポストインクリメント (転送後レジスタの値をインクリメント)

DMADn−/DMASn−: ポストデクリメント (転送後レジスタの値をデクリメント)

表中の I/Oとは固定されたアドレス、メモリとは INC, DECされるアドレスを意味します。

注 2) 実行時間: 転送元/転送先アドレス空間が 16 ビットバス幅、0 ウェイトに設定されている場合を示

します。

クロック条件は fc = 16 MHz、高速クロックギア: 1倍 (fc) です。

注 3) 転送モードレジスタへは上記以外のコードを設定しないでください。

91C025-44

2003-12-05

Page 47

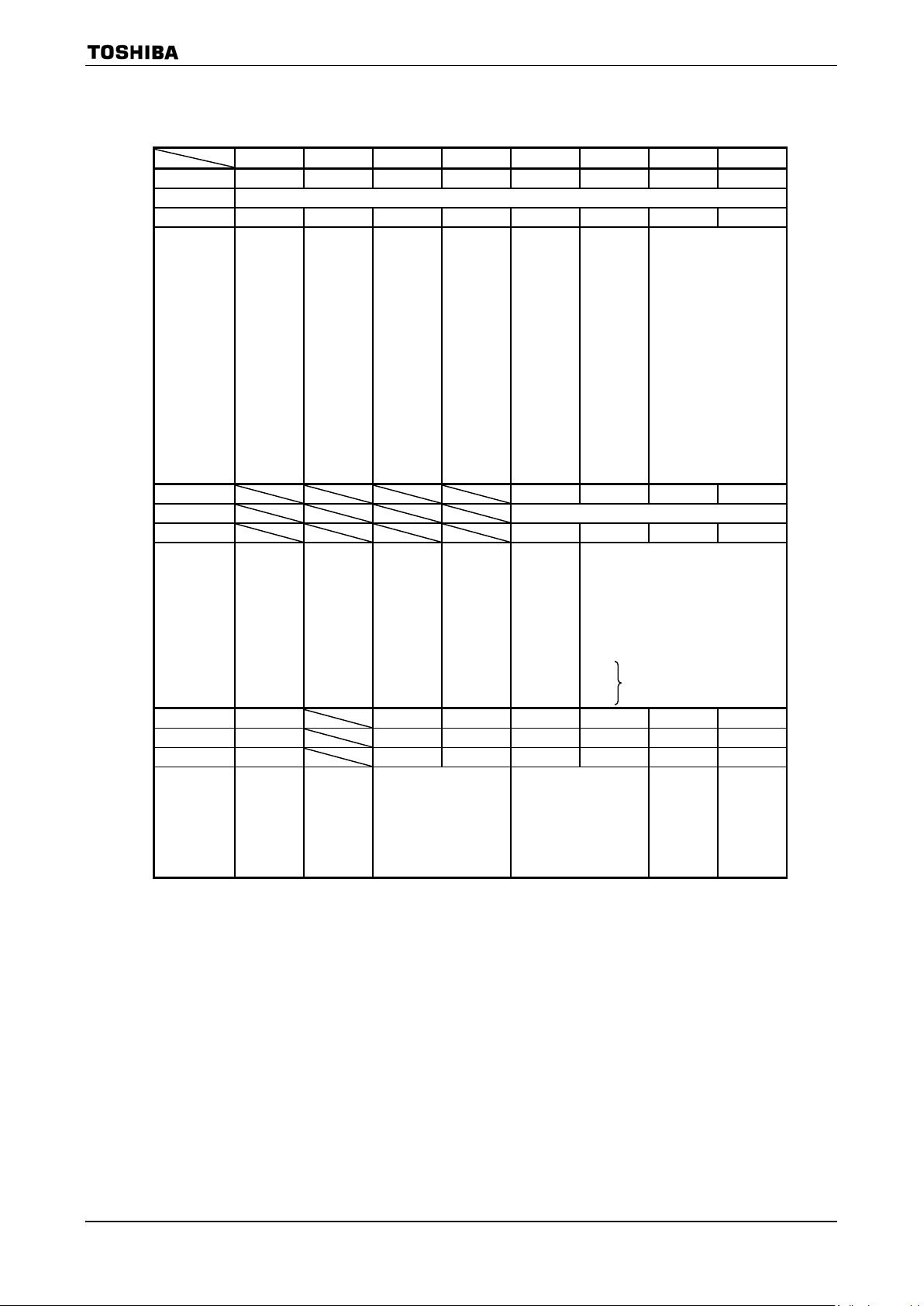

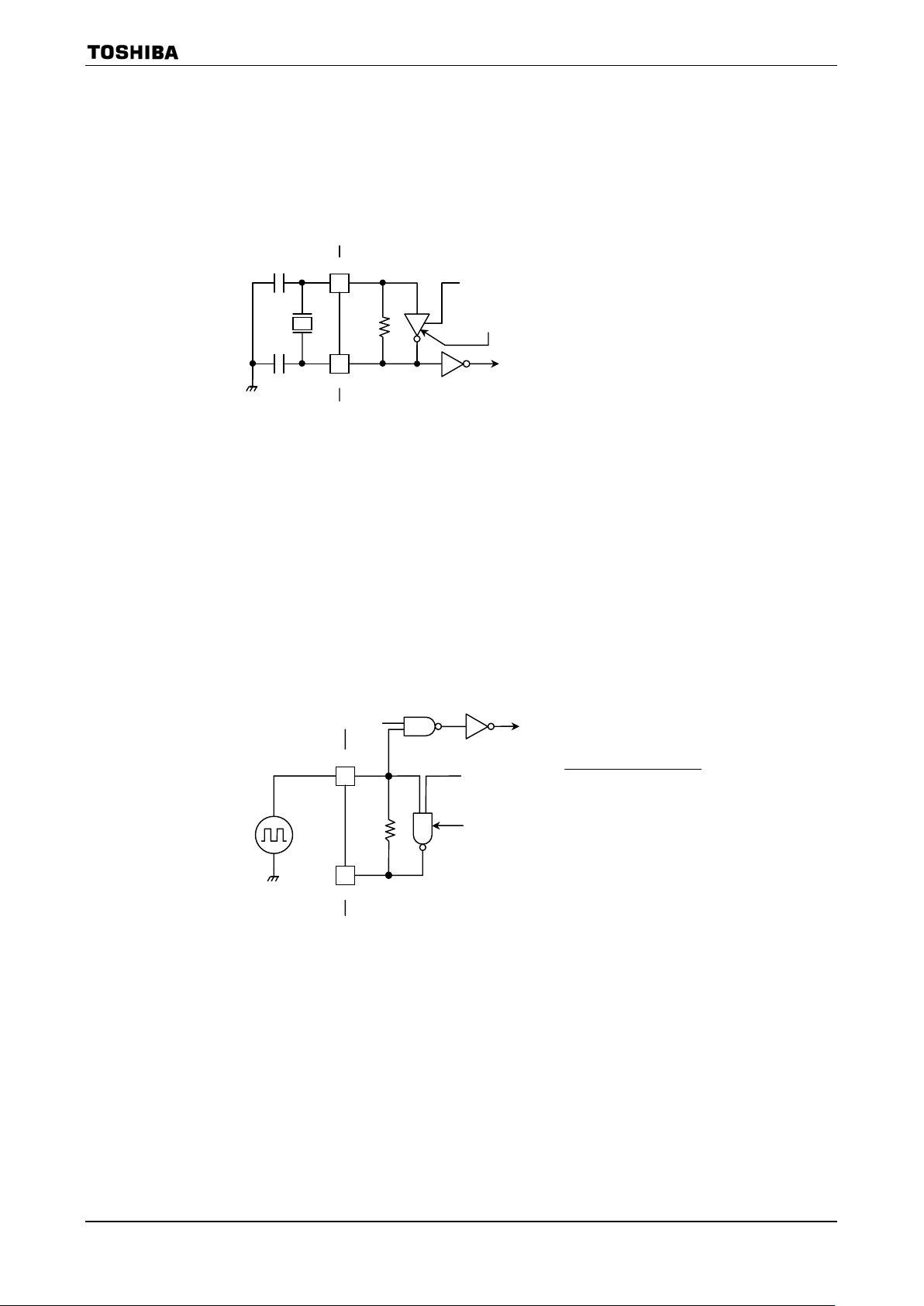

3.4.3 割り込みコントローラの制御

図 3.4.3に割り込み回路のブロック図を示します。この図の左半分は割り込みコントローラ

を示し、右半分は CPU の割り込み要求信号回路と、ホルト解除回路を示しています。

割り込みコントローラは各割り込みチャネルごと (合計 36 チャネル) に、割り込み要求フラ

グ, 割り込みレベルレジスタ, マイクロ DMA 起動ベクタ設定レジスタを持っています。割り込

み要求フラグは、周辺からの割り込み要求をラッチするためのものです。

このフラグは以下の場合にクリアされます。

• リセット動作

• CPU が割り込みを受け付け、その割り込みのベクタをリード

• 割り込みをクリアする命令の実行 (INTCLR レジスタに DMA 起動ベクタをライト)

• CPU がその割り込みでのマイクロ DMA を受け付けたとき

• その割り込みでのマイクロ DMA バースト転送が終了したとき

割り込みの優先順位は、各割り込み要因ごとに準備されている割り込みレベルレジスタ

(INTE0AD, INTE12 … など) にそれぞれのレベルを設定できます。設定できる割り込みレベ

ルは、1 から 6 までの 6 レベルです。レベルを “0” (または “7”) にすることにより、該当する

割り込み要求は禁止されます。なお、ノンマスカブル割り込み (ウォッチドッグタイマ) のレベ

ルは “7” に固定されています。また、同時に同一レベルの割り込み要求が発生した場合はデフ

ォルトプライオリティに従い、割り込みを受け付けます。なお、割り込みレベルレジスタのビ

ット 3, ビット 7 を読むと、割り込み要求フラグの状態が読み出され、各チャネルの割り込み

要求の有無がわかります。

TMP91C025

割り込みコントローラは同時に発生した割り込みの中で、最も優先順位の高い割り込みレベ

ルと、そのベクタアドレスを CPU へ送ります。CPU は、ステータスレジスタ (SR) に割り付

けられている割り込みマスクレジスタ<IFF2:0>と割り込みレベルを比較し、割り込みのレベ

ルが高ければ、この割り込みを受け付けます。そして、SR<IFF2:0>に受け付けた割り込みレ

ベル+1 の値をセットし、この値以上の割り込み要求だけが、多重に受け付けられる割り込み

要因となります。割り込み処理の終了 (RETI 命令の実行) により、SR<IFF2:0>には、スタッ

クに退避されていた、割り込み発生以前の割り込みマスクレジスタの値が、リストアされます。

割り込みコントローラには、マイクロ DMA の起動ベクタを格納するレジスタ (4 チャネル)

が用意されています。このレジスタに起動ベクタ (表 3.4.1参照) を書き込むことにより、該当

する割り込み要求が発生することによって、マイクロ DMA が起動されます。なお、このマイ

クロ DMA 処理の前に、マイクロ DMA パラメータ用レジスタ (DMAS, DMAD など) に値を設

定しておく必要があります。

91C025-45

2003-12-05

Page 48

割

り込み

7

TMP91C025

CPU

∼7

EI1

リセット

割り込み要求信号

DI

割り込み

レベル判定

If INTRQ2~0 ≧ IFF

3

3

2~0 then 1.

STOP中

IDLE1中

ホルト解除

マイクロDMA要求

マイクロDMA

チャネル指定

2

RESET

INT0, INT1, INT2, INT3 , KEY ,

RTC, ALM

If IFF = 7 then 0

IFF2:0

CPU側の割り込み

許可フラグ

CPUに対する

INTRQ2~0

3

割り込み要求信号

A

B

C

1

エンコーダ

プライオリティ

最上位の

割り込み

レベル選定 (7が最優先)

1 2 3 4 5

7

6

1

6

D0

D1

36

D2

D3

D4

割り込みベクタ

D5

生成

D6

D7

2

割り込みベクタ

Vリード

A B

4入力OR

0 1 2

4

3

マイクロDMAチャネル

プライオリティエンコーダ

V = 20H

V = 24H

割り込みコントローラ

Y1

Y2

A

デコーダ

S Q

R

割り込み要求フラグ

ベクタVリード

リセット

優先順位設定レジスタ

Dn

Dn + 1

6

Y3

Y4

Y5

Y6

B

C

CLR

D Q

り込み

Dn + 2

V = 84H

V = 88H

V = 90H

V = 28H

V = 30H

V = 34H

V = 38H

V = 40H

V = 44H

V = 2CH

Dn + 3

割り込み要求F/Fリード

割り込み受け付け

R

リセット

マイクロDMA受け付け

S Q

要求フラグ

V = 3CH

V = 48H

V = 4CH

V = 8CH

V = 94H

DMA0V

DMA1V

DMA2V

ソフト

スタート

S

セレクタ

6

34

CLR

D Q

D5

D4

D3

D2

D1

D0

DMA3V

INTTC0

リセット

マイクロDMA起動ベクタ設定レジスタ

INTWD

INT0

INTP1

INTTC0

INTTC1

INTTC2

INT1

INT2

INT3

INTALM0

INTALM1

INTALM2

INTALM3

INTALM4

INTTA0

INTTC3

マイクロ

DMAカウンタ・

ゼロ割り込み

図 3.4.3 割り込みコントローラブロック図

91C025-46

2003-12-05

Page 49

TMP91C025

(1) 割り込みレベル設定レジスタ

記号 名称 アドレス 7 6 5 4 3 2 1 0

INTAD INT0

INT2 INT1

INTALM4 INT3

INTALM1 INTALM0

INTALM3 INTALM2

INTTA1 (TMRA1) INTTA0 (TMRA0)

INTTA3 (TMRA3) INTTA2 (TMRA2)

INTKEY INTRTC

INTE0AD

INTE12

INTE3ALM4

INTEALM01

INTEALM23

INTETA01

INTETA23

INTERTCKEY

INT0 &

INTAD

enable

INT1 &

INT2

enable

INT3&

INTALM4

enable

INTALM0 &

INTALM1

enable

INTALM2 &

INTALM3

enable

INTTA0 &

INTTA1

enable

INTTA2 &

INTTA3

enable

INTRTC &

INTKEY

enable

90H

91H

92H

93H

94H

95H

96H

97H

IADC IADM2 IADM1 IADM0 I0C I0M2 I0M1 I0M0

R R/W R R/W

0 0 0 0 0 0 0 0

I2C I2M2 I2M1 I2M0 I1C I1M2 I1M1 I1M0

R R/W R R/W

0 0 0 0 0 0 0 0

IA4C IA4M2 IA4M1 IA4M0 I3C I3M2 I3M1 I3M0

R R/W R R/W

0 0 0 0 0 0 0 0

IA1C IA1M2 IA1M1 IA1M0 IA0C IA0M2 IA0M1 IA0M0

R R/W R R/W

0 0 0 0 0 0 0 0

IA3C IA3M2 IA3M1 IA3M0 IA2C IA2M2 IA2M1 IA2M0

R R/W R R/W

0 0 0 0 0 0 0 0

ITA1C ITA1M2 ITA1M1 ITA1M0 ITA0C ITA0M2 ITA0M1 ITA0M0

R R/W R R/W

0 0 0 0 0 0 0 0

ITA3C ITA3M2 ITA3M1 ITA3M0 ITA2C ITA2M2 ITA2M1 ITA2M0

R R/W R R/W

0 0 0 0 0 0 0 0

IKC IKM2 IKM1 IKM0 IRC IRM2 IRM1 IRM0

R R/W R R/W

0 0 0 0 0 0 0 0

割り込み要求フラグ

lxxM2 lxxM1 lxxM0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

91C025-47

機能 (ライト)

割り込み要求を禁止に設定

割り込みレベルを “1” に設定

割り込みレベルを “2” に設定

割り込みレベルを “3” に設定

割り込みレベルを “4” に設定

割り込みレベルを “5” に設定

割り込みレベルを “6” に設定

割り込み要求を禁止に設定

2003-12-05

Page 50

記号 名称 アドレス

Interrupt

INTES0

INTES1

INTLCD

INTETC01

INTETC23

INTEP01

enabel

serial 0

INTRX1 &

INTTX1

enable

INTLCD

enable

INTTC0 &

INTTC1

enable

INTTC2 &

INTTC3

enable

INTP0 &

INTP1

enable

98H

99H

9AH

9BH

9CH

9DH

TMP91C025

7 6 5 4 3 2 1 0

INTTX0 INTRX0

ITX0C ITX0M2 ITX0M1 ITX0M0 IRX0C IRX0M2 IRX0M1 IRX0M0

R R/W R R/W

0 0 0 0 0 0 0 0

INTTX1 INTRX1

ITXT1C ITX1M2 ITX1M1 ITX1M0 IRX1C IRX1M2 IRX1M1 IRX1M0

R R/W R R/W

0 0 0 0 0 0 0 0

INTLCD −

ILCD1C ILCDM2 ILCDM1 ILCDM0 − − − −

R R/W − −

0 0 0 0 − − − −

INTTC1 INTTC0

ITC1C ITC1M2 ITC1M1 ITC1M0 ITC0C ITC0M2 ITC0M1 ITC0M0

R R/W R R/W

0 0 0 0 0 0 0 0

INTTC3 INTTC2

ITC3C ITC3M2 ITC3M1 ITC3M0 ITC2C ITC2M2 ITC2M1 ITC2M0

R R/W R R/W

0 0 0 0 0 0 0 0

INTP1 INTP0

IP1C IP1M2 IP1M1 IP1M0 IP0C IP0M2 IP0M1 IP0M0

R R/W R R/W

0 0 0 0 0 0 0 0

割り込み要求フラグ

lxxM2 lxxM1 lxxM0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

機能 (ライト)

割り込み要求を禁止に設定

割り込みレベルを “1” に設定

割り込みレベルを “2” に設定

割り込みレベルを “3” に設定

割り込みレベルを “4” に設定

割り込みレベルを “5” に設定

割り込みレベルを “6” に設定

割り込み要求を禁止に設定

91C025-48

2003-12-05

Page 51

TMP91C025

(2) 外部割り込みの制御

記号 名称 アドレス 7 6 5 4 3 2 1 0

− − I3EDGE I2EDGE I1EDGE I0EDGE I0LE −

Interrupt

IIMC

input mode

control

INT0 level enable

0 edge detect INT

1 “H” level INT

8CH

(RMW 禁)

0 0 0 0 0 0 0 0

“0” をライ

トしてくだ

さい。

“0”

トしてくだ

さい。

をライ

INT3

エッジ

0: 立ち上がり

1: 立ち下がり

INT2エッジ

0: 立ち上がり

1: 立ち下がり

W

INT1エッジ

0: 立ち上がり

1: 立ち下がり

INT0エッジ

0: 立ち上がり

1: 立ち下がり

INT0

0: エッジ

1: レベル

“0” をライ

トしてくだ

さい。

(3) 割り込み要求フラグクリアレジスタ

割り込み要求フラグのクリアは、INTCLR レジスタにマイクロ DMA 起動ベクタを書く

ことで行います。

例えば INT0 割り込みフラグをクリアする場合、DI 命令後に下記のレジスタ操作を行

います。

INTCLR ← 0AH: INT0 割り込み要求フラグのクリア

記号 名称 アドレス

INTCLR

Interrupt

clear

control

88H

(RMW 禁)

7 6 5 4 3 2 1 0

CLRV5 CLRV4 CLRV3 CLRV2 CLRV1 CLRV0

0 0 0 0 0 0

W

割り込みベクタ

(4) マイクロ DMA 起動ベクタレジスタ

マイクロ DMA 処理をどの割り込み要因に割り当てるかを選択するレジスタです。この

レジスタに設定されたベクタ値と一致する、マイクロ DMA 起動ベクタを持つ割り込み要

因をマイクロ DMA 起動要因として割り当てます。

マイクロ DMA 転送カウンタが “0” になると、割り込みコントローラにそのチャネルに

相当するマイクロ DMA 転送終了割り込みが伝えられるとともに、このマイクロ DMA 起

動ベクタレジスタはクリアされ、そのチャネルのマイクロ DMA 起動要因がクリアされま

すので、引き続きマイクロ DMA 処理をさせたい場合は、マイクロ DMA 転送終了割り込

み処理の中で、再度このマイクロ DMA 起動ベクタレジスタをセットする必要があります。

また、複数チャネルのマイクロ DMA 起動ベクタレジスタに同一ベクタが設定されてい

る場合は、チャネル番号の小さい方が優先されます。

従って、2 チャネルのマイクロ DMA 起動ベクタレジスタに同一ベクタが設定されてい

る場合、チャネル番号の小さいチャネルがマイクロ DMA 転送終了になるまで実行され、

そのチャネルのマイクロ DMA 起動ベクタを再度設定しなければ、その後のマイクロ DMA

起動はチャネル番号の大きいチャネルに移行します。(マイクロ DMA のチェーン)

91C025-49

2003-12-05

Page 52

TMP91C025

記号 名称 アドレス 7 6 5 4 3 2 1 0

DMA0 開始ベクタ

DMA1 開始ベクタ

DMA2 開始ベクタ

DMA3 開始ベクタ

DMA0V

DMA1V

DMA2V

DMA3V

DMA0

start

vector

DMA1

start

vector

DMA2

start

vector

DMA3

start

vector

80H

81H

82H

83H

R/W

R/W

R/W

R/W

DMA0V5 DMA0V4 DMA0V3 DMA0V2 DMA0V1 DMA0V0

0 0 0 0 0 0

DMA1V5 DMA1V4 DMA1V3 DMA1V2 DMA1V1 DMA1V0

0 0 0 0 0 0

DMA2V5 DMA2V4 DMA2V3 DMA2V2 DMA2V1 DMA2V0

0 0 0 0 0 0

DMA3V5 DMA3V4 DMA3V3 DMA3V2 DMA3V1 DMA3V0

0 0 0 0 0 0

(5) マイクロ DMA のバースト指定

マイクロ DMA 処理はバースト指定を行うことにより、1 回のマイクロ DMA 起動で転

送カウンタ・レジスタがゼロになるまで連続転送を行うことが可能です。DMAB レジスタ

のマイクロ DMA チャネルに対応するビットを “1” にすることで、バースト指定できます。

記号 名称 アドレス

DMA

DMAR

DMAB

software

request

register

DMA

burst

register

89H

8AH

7 6 5 4 3 2 1 0

DMAR3 DMAR2 DMAR1 DMAR0

0 0 0 0

DMAB3 DMAB2 DMAB1 DMAB0

0 0 0 0

R/W R/W R/W R/W

R/W

1: DMA のソフト要求

1: DMA のバースト要求

91C025-50

2003-12-05

Page 53

TMP91C025

(6) 注意事項

CPU は、命令実行ユニットとバスインタフェースユニットが分かれています。そのた

め、割り込みが発生する直前に、その割り込みコントローラの割り込み要求フラグをクリ

アする命令をフェッチした場合、CPU が割り込みを受け付けて割り込みベクタをリード

するまでの間に、その割り込み要求フラグをクリアする命令 (注)

を実行するということが

あり得ます。この場合、CPU は要因消滅ベクタ “0008H” を読み込み、アドレス FFFF08H

の割り込みベクタをリードします。

上記の現象を回避するため、割り込み要求フラグをクリアするときは、DI 命令の後に

クリアする命令を書き込むようにしてください。クリアする命令を実行した後、再び EI

命令で割り込みをイネーブルにするときは、クリア命令後必ず 1 命令以上間をおいてから

EI 命令を実行してください。クリア命令後すぐに EI 命令を実行すると、割り込み要求フ

ラグがクリアされる前に、割り込みイネーブルになってしまうことがあります。

また、POP SR 命令により割り込みマスクレベル (ステータスレジスタ SR の<IFF2:0>)

を書き替えるときは、必ず DI 命令により割り込みを禁止した後に POP SR 命令を実行し

てください。

その他、以下の 2 点は例外の回路になっていますので注意が必要です。

INT0のレベルモード

INTRX

エッジタイプの割り込みではないため、割り込み要求用フリップフ

ロップ機能はキャンセルされ、周辺割り込み要求がそのままフリッ

プフロップの S 入力を素通りし、Q出力になります。モード変更 (エ

ッジ → レベル) を行った場合、以前の割り込み要求フラグは自動的

にクリアされます。

INT0を “0” から “1” にすることによって CPU が割り込み応答シーケ

ンスに入ったときは、その割り込み応答シーケンスが完了するまで

INT0を “1” のままにしておく必要があります。また、INT0のレベル

モードをホルトの解除に使用する場合も、一度 “0” から “1” にして、

ホルトが解除されるまで必ず “1” を保持しておく必要があります (ノ

イズによって途中で “0” が入ることがないようにしてください)。

レベルモードからエッジモードへ切り替えたとき、レベルモード時

に受け付けた割り込み要求フラグはクリアされません。そのため、

割り込み要求フラグを以下のシーケンスでクリアしてください。

DI

LD (IIMC), 00H; レベルからエッジへ切り替える

LD (INTCLR), 0AH; INT0割り込み要求フラグをクリア

NOP; EI実行待ち

EI

割り込み要求用フリップフロップをクリアするには、リセット動作

またはシリアルチャネルの受信バッファをリードする必要がありま

す。命令によるクリアはできません。

注) 下記の命令および端子変化も、この割り込み要求フラグをクリアする命令に相当します。

INT0: エッジモードで割り込み要求発生後のレベルモードへの切り替え命令

レベルモードでの割り込み要求発生後の端子入力変化 (“H” → “L”)

INTRX: 受信バッファをリードする命令

91C025-51

2003-12-05

Page 54

TMP91C025

3.5 ポート機能

合計 38 ビットの入出力ポートがあります。

また、これらのポート端子は汎用入出力ポート機能だけでなく、内部の CPU や内蔵 I/O の入出

力機能と兼用になっています。表 3.5.1に各ポート端子の機能を、表 3.5.2, 表 3.5.3に各端子の設定

方法を示します。

表 3.5.1 ポート機能

(R: PU = プログラマブルプルアップ抵抗付き、U = プルアップ抵抗付き)

ポート名 ピン名称 ピン数 方向

ポート 1

ポート 2

ポート 5

ポート 6

P61 1

P62 1

P63 1

P64 1

P65 1

ポート 8

ポート 9

ポート A

ポート B

PB4 1

PB5 1

PB6 1

ポート C

PC1 1

PC2 1

PC3 1

PC4 1

PC5 1

ポート D

PD1 1

PD2 1

PD3 1

PD4 1

PD7 1

ポート Z

P10∼P17 8

P20∼P27 8

P56 1

P60 1

P80

P81

P82

P83

P90∼P97 8

PA0

PA1

PA2

PA3

PB3 1

PC0 1

PD0 1

PZ2 1

PZ3 1

1

1

1

1

1

1

1

1

入出力

出力

入出力

出力

出力

出力

出力

出力

出力

入力

入力

入力

入力

入力

出力

出力

出力

出力

入出力

入出力

入力

入力

入出力

入出力

入出力

入出力

入出力

入出力

出力

出力

出力

出力

出力

出力

入出力

入出力

方向設定単位 内蔵機能用ピン名称

R

−

−

PU

−

−

−

−

−

−

−

−

−

−

U

−

−

−

−

−

−

−

−

−

−

PU

−

−

PU

−

−

−

−

−

−

PU

PU

ビット

(固定)

ビット

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

ビット

ビット

(固定)

(固定)

ビット

ビット

ビット

ビット

ビット

ビット

(固定)

(固定)

(固定)

(固定)

(固定)

(固定)

ビット