Page 1

東芝 オリジナル CMOS 16ビット マイクロコントローラ

TLCS-900/L シリーズ

TMP93CS20

セミコンダクター社

Page 2

ご

機

低電圧/低消費電力

CMOS 16 ビット マイクロコントローラ

TMP93CS20F

1. 概要と特長

TMP93CS20 は、低電圧/低消費電力動作が可能な高速・高機能 16 ビットマイクロコントローラです。

TMP93CS20F は 144 ピンフラットパッケージ製品です。

特長は、次のとおりです。

(1) オリジナル 16 ビット CPU (900/L CPU 使用)

• TLCS-90 と命令ニモニックで上位互換

• 16 M バイトのリニアアドレス空間

• 汎用レジスタ、レジスタバンク方式

• 16 ビット乗除算命令、ビット転送/演算命令

• マイクロ DMA: 4 チャネル (1.6 µs/2 バイト@20 MHz)

(2) 最小命令実行時間: 200 ns (20 MHz 発振時)

TMP93CS20

(3) 内蔵 RAM: 2 K バイト

内蔵 ROM: 64 K バイト

(4) LCD ドライバ

• 昇圧回路内蔵 (基準電圧外部入力)

• 最大 40 segment × 4 common

• 1/4、1/3、1/2 デューティ、スタティック駆動の選択

(5) 時計用専用タイマ: 1 チャネル

(6) 8 ビットタイマ: 4 チャネル

(7) 16 ビットタイマ: 4 チャネル

(8) 汎用シリアルインタフェース: 2

チャネル

• UART/同期両モード対応: 1 チャネル

• UART 専用: 1 チャネル

• マイコン製品の信頼性予測については、「品質保証と信頼性 / 取り扱い上のご注意とお願い」の 1.3 項に記載されておりますので必ず

お読みください。

• 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当社半導体製品を

使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることのないように、購入者側の責任におい

て、機器の安全設計を行うことをお願いします。

なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべき注意事項や条件

について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」などでご確認ください。

• 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電

器など) に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や誤作動が直接人命を脅かしたり人体

に危害を及ぼす恐れのある機器 (原子力制御機器、航空宇宙機器、輸送機器、交通信号機器、燃焼制御、医療機器、各種安全装置な

ど) にこれらの製品を使用すること (以下 “特定用途” という) は意図もされていませんし、また保証もされていません。本資料に掲

載されている製品を当該特定用途に使用することは、お客様の責任でなされることとなります。

• 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されているものです。

• 本資料に掲載されている技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社および第三者の知的

財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 本資料に掲載されている製品を、国内外の法令、規則および命令により製造、販売を禁止されている応用製品に使用することはで

きません。

• 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

030519TBP1

Purchase of TOSHIBA I2C components conveys a license under the Philips I2C Patent Rights to use

these components in an I

Specification as defined by Philips.

2

C system, provided that the system conforms to the I2C Standard

93CS20-1

2004-02-10

Page 3

(9) シリアルバスインタフェース: 1 チャネル

2

• I

C バスモード/クロック同期式 8 ビット SIO モード

(10) 10 ビット AD コンバータ: 8 チャネル

(11) 大電流駆動対応ポート: 8 ポート (ポート A)

(12) ウォッチドッグタイマ

(13) キーオンウェイクアップ(キー入力割り込み)

(14) 割り込み機能

• CPU 9 本 ……… ソフトウエア割り込み命令、未定義命令実行違反

TMP93CS20

• 内部 24 本

• 外部 12 本

(15) 入出力ポート: 88 端子 (XT1/XT2 を含む)

• 大電流出力: 8 端子、LED 直接駆動可能

(16) スタンバイ機能

• 4 種類の HALT モード (RUN、IDLE2、IDLE1、STOP)

(17) クロックギア選択機能

• クロックギア: 高周波クロック fc~fc/16 まで切り替え可能

• デュアルクロック

(18) 低電圧動作

• Vcc = 2.7~5.5 V

(19) パッケージ: P-LQFP144-1616-0.40

7レベルの優先順位の設定が可能

93CS20-2

2004-02-10

Page 4

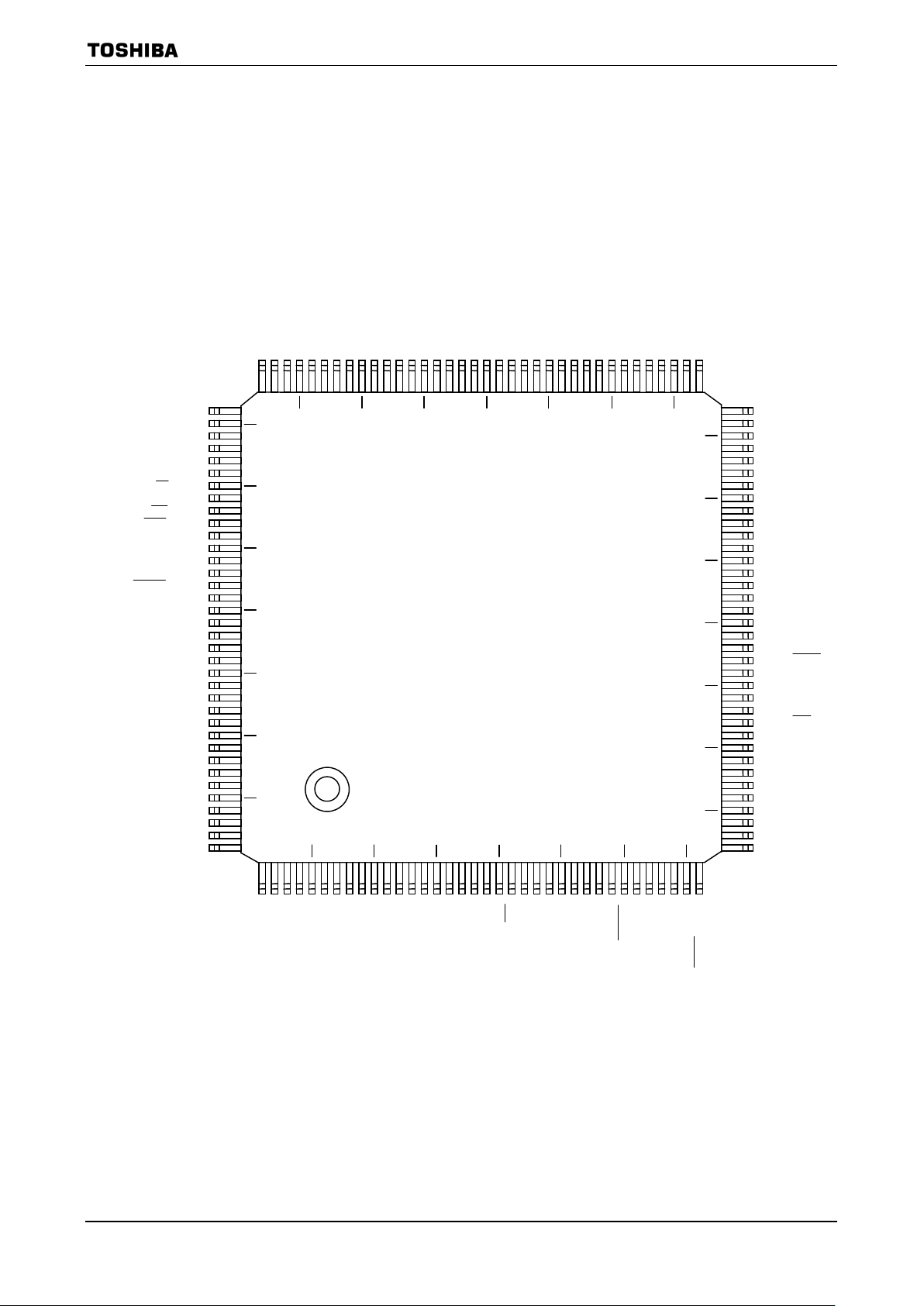

X

X

A

ADTRG (P37)

AN0~AN7 (P50~P57)

AVCC

AVSS

VREFH

VREFL

SCK (P60)

SO/SDA (P61)

SI/SCL (P62)

TXD0 (P63)

RXD0 (P64)

SCLK0/

0CTS (P65)

TXD1 (P80)

RXD1 (P81)

TI0 (P66)

TO1 (P67)

TI2 (P82)

TO3 (P83)

TI4 (P40)

TO4 (P41)

TI6 (P42)

TO6 (P43)

KEY0~ (P40)

KEY7 (P47)

注) リセット後、兼用端子は ( ) 内の機能が選択されています。

10-bit 8-ch

AD

converter

Serial bus

interface

Serial I/O

(Channel 0)

Serial I/O

(Channel 1)

8-bit timer

(Timer 0)

8-bit timer

(Timer 1)

8-bit timer

(Timer 2)

8-bit timer

(Timer 3)

16-bit timer

(Timer 4)

16-bit timer

(Timer 6)

Key-on wakeup

(KEY0~KEY7)

Real time

counter

XWA

XBC

XDE

XHL

XI

XIY

XIZ

XSP

2-Kbyte RAM

64-Kbyte ROM

Watchdog

timer

CPU (900/L)

WA

BC

DE

HL

I

IY

IZ

SP

32ビット

F

SR

P C

Clock gear

16-bit timer

(Timer 8)

16-bit timer

(Timer A)

Interrupt

controller

LCD driver

OSC1

OSC2

Port 0

Port 1

Port 2

TMP93CS20

VCC [3]

VSS [8]

X1

X2

XT1 (P86)

XT2 (P87)

CLK

LE

SCOUT (P73)

EA

RESET

RD (P30)

WR (P31)

HWR (P32)

WAIT (P84)

P00~P07 (AD0~AD7)

P10~P17

(AD8/A8~AD15/A15)

P20~P27

(A0/A16~A7/A23)

TI8/INT8 (P70)

TI9/INT9 (P71)

TO8 (P72)

TIA/INTA (P74)

TIB/INTB (P75)

TOA (P76)

NMI (P77)

INT0 (P33)~INT4 (P37)

INT7 (P66)

V1~V3

C0~C1

SEG0~SEG23

SEG24 (P90)~SEG39 (PA7)

COM0~COM3

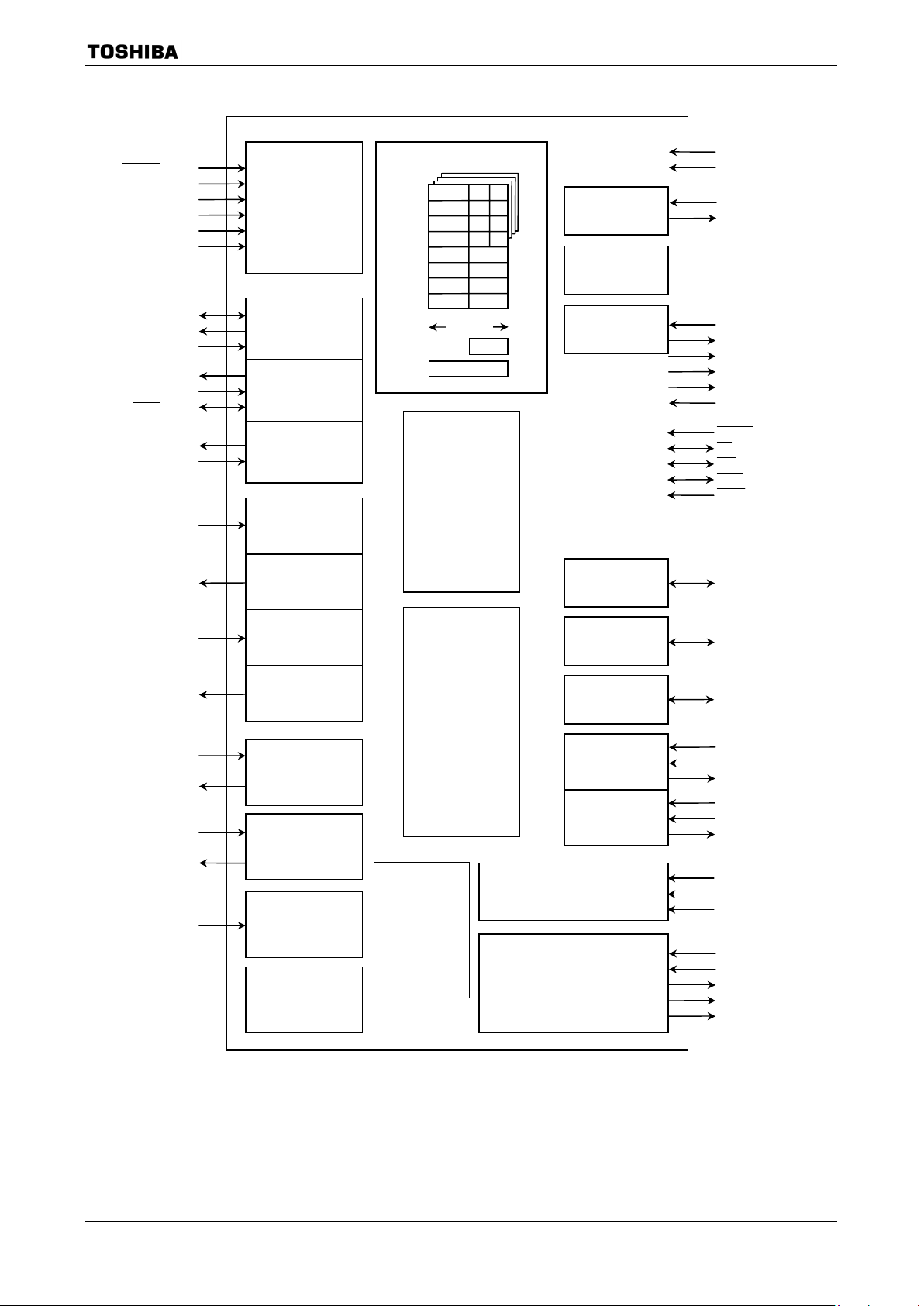

図 1.1 TMP93CS20 ブロック図

93CS20-3

2004-02-10

Page 5

K

A

T

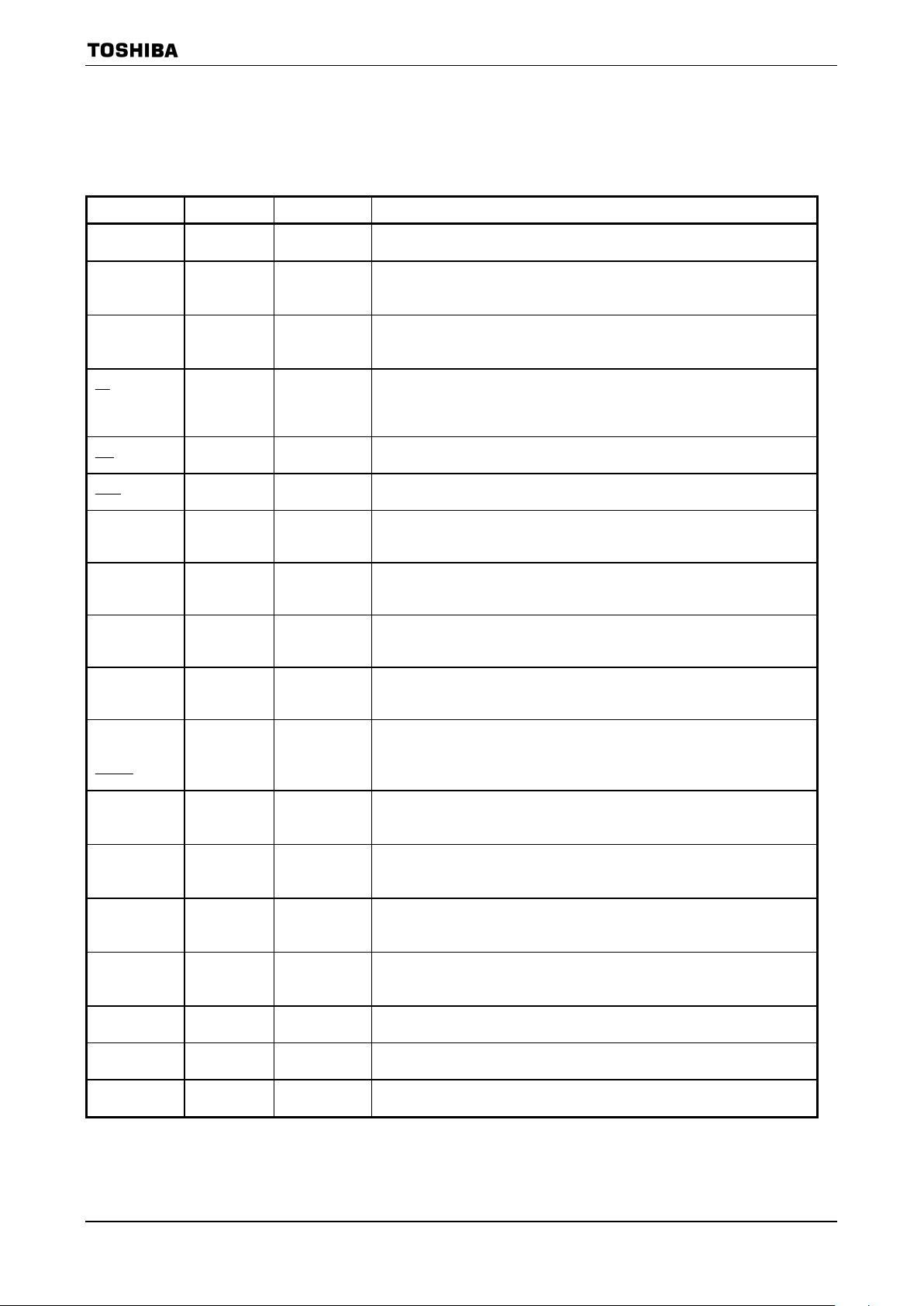

2. ピン配置とピン機能

TMP93CS20 のピン配置図および入出力ピンの名称と概略機能を示します。

2.1 ピン配置図

ピン配置図は、図 2.1.1 のとおりです。

(INT4/

(SEG34) PA2

(SEG35) PA3

(SEG36) PA4

(SEG37) PA5

(SEG38) PA6

(SEG39) PA7

RD ) P30

(

VSS

WR ) P31

(

(HWR ) P32

(INT0) P33

(INT1) P34

(INT2) P35

(INT3) P36

ADTRG ) P37

VREFH

VREFL

(AN7) P57

(AN6) P56

(AN5) P55

(AN4) P54

(AN3) P53

(AN2) P52

(AN1) P51

(AN0) P50

AVCC

AVSS

VSS

VCC

(AD0) P00

(AD1) P01

(AD2) P02

(AD3) P03

(AD4) P04

(AD5) P05

(AD6) P06

109

144

108

PA1 (SEG33)

PA0 (SEG32)

P97 (SEG31)

P96 (SEG30)

P95 (SEG29)

105 100 95 90 85 80 75

110

115

120

125

130

135

140

5 10 15 20 25 30 35

1

(AD7) P07

(AD8/A8) P10

(AD9/A9) P11

(AD11/A11) P13

(AD10/A10) P12

P94 (SEG28)

(AD12/A12) P14

P93 (SEG27)

(AD13/A13) P15

P92 (SEG26)

VSS

TMP93CS20

VSS

P91 (SEG25)

P90 (SEG24)

SEG23

SEG22

SEG21

SEG20

SEG19

SEG18

SEG17

SEG16

SEG15

SEG14

SEG13

SEG12

SEG11

SEG10

SEG9

SEG8

SEG7

VSS

SEG6

SEG5

SEG4

SEG3

SEG2

SEG1

SEG0

73

72

COM3

70

65

60

TMP93CS20F

LQFP144

55

Top view

50

45

40

36

X1

X2

E

ALE

CL

(A4/A20) P24

(A5/A21) P25

(A6/A22) P26

(A0/A16) P20

(A1/A17) P21

(A2/A18) P22

(A3/A19) P23

(AD14/A14) P16

(AD15/A15) P17

(A7/A23) P27

TEST1

VSS

VCC

TEST2

(XT1) P86

RESE

(XT2) P87

(SCK) P60

(TXD0) P63

(RXD0) P64

(SI/SCL) P62

(SO/SDA) P61

(SCLK0/CTS0) P65

COM2

COM1

COM0

C1

C0

V3

VCC

VSS

V2

V1

P47 (KEY7)

P46 (KEY6)

P45 (KEY5)

P44 (KEY4)

P43 (TO6/KEY3)

P42 (TI6/KEY2)

P41 (TO4/KEY1)

P40 (TI4/KEY0)

P85

P84 (

P83 (TO3)

P82 (TI2)

P81 (RXD1)

P80 (TXD1)

P77 (

P76 (TOA)

P75 (TIB/INTB)

VSS

P74 (TIA/INTA)

P73 (SCOUT)

P72 (TO8)

P71 (TI9/INT9)

P70 (TI8/INT8)

P67 (TO1)

P66 (TI0/INT7)

37

WAIT )

NMI )

図 2.1.1 ピン配置図 (144 ピン LQFP)

2004-02-10 93CS20-4

Page 6

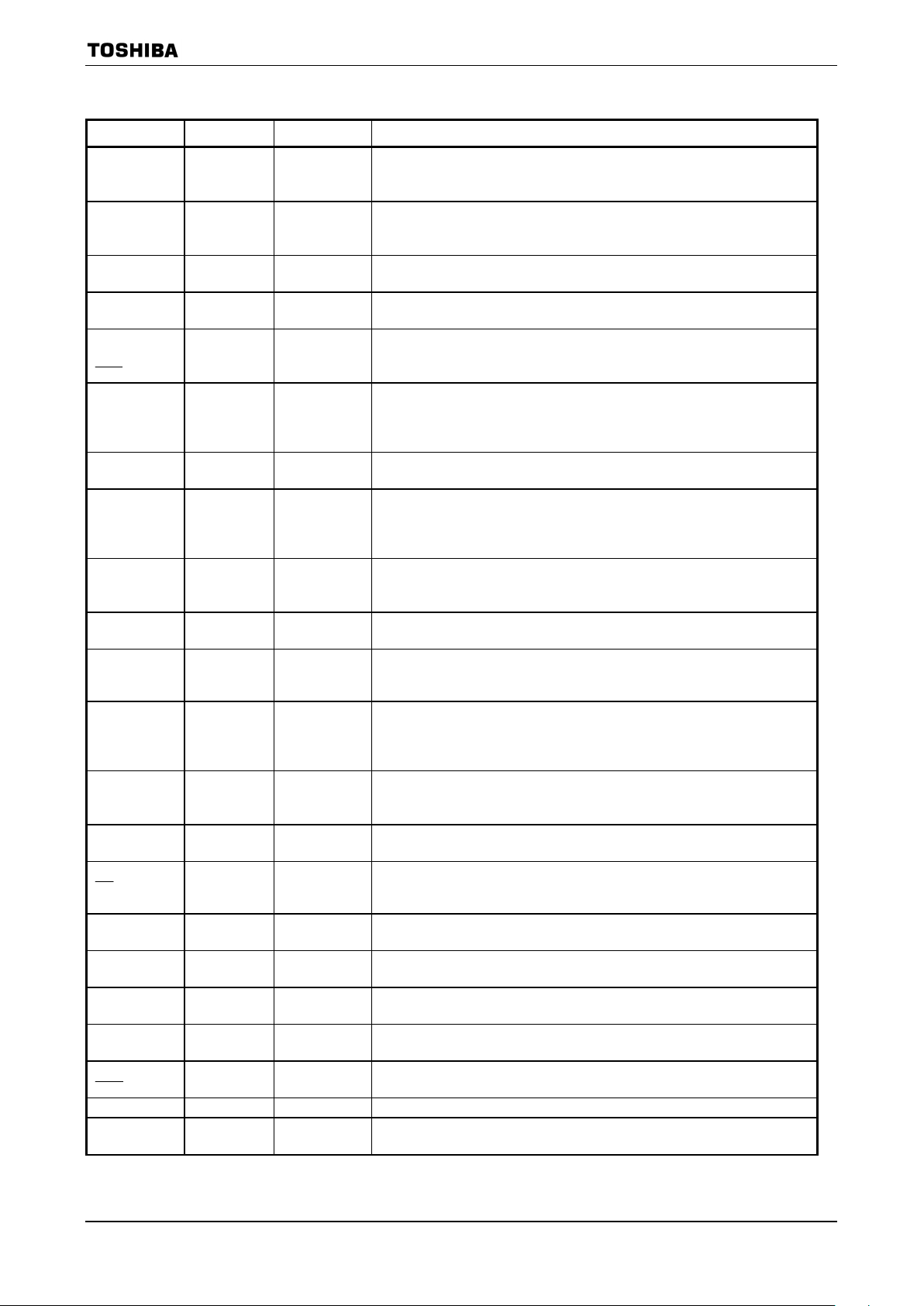

2.2 ピン名称と機能

入出力ピンの名称と機能は、表 2.2.1 のとおりです。

表 2.2.1 ピン名称と機能 (1/3)

ピン名称 ピン数 入出力 機 能

P00~P07

AD0~AD7

P10~P17

AD8~AD15

A8~A15

P20~P27

A0~A7

A16~A23

P30

RD

P31

WR

P32

HWR

P33

INT0

P34

INT1

P35

INT2

P36

INT3

P37

INT4

ADTRG

P40

TI4

KEY0

P41

TO4

KEY1

P42

TI6

KEY2

P43

TO6

KEY3

P44~P47

KEY4~KEY7

P50~P57

AN0~AN7

P60

SCK

8

8

8

1

1

1

1

1

1

1

1

1

1 入出力

1 入出力

1 入出力

4 入出力

8 入力

1 入出力

入出力

入出力

入出力

入出力

出力

入出力

出力

出力

出力

出力

出力

出力

入出力

出力

入出力

入力

入出力

入力

入出力

入力

入出力

入力

入出力

入力

入力

入出力

入力

入力

出力

入力

入力

入力

出力

入力

入力

入力

入出力

ポート 0: ビット単位で入出力の設定ができる入出力ポート

アドレスデータ (下位) : アドレス/データバス 0~7

ポート 1: ビット単位で入出力の設定ができる入出力ポート

アドレスデータ (上位) : アドレス/データバス 8~15

アドレス: アドレスバス 8~15

ポート 2: ビット単位で入出力の設定ができる入出力ポート (プルアップ付き)

アドレス: アドレスバス 0~7

アドレス: アドレスバス 16~23

ポート 30: 出力専用ポート

リード: 外部メモリをリードするためのストローブ信号

(P3<P30> = 0, P3FC<P30F> = 1 にすることにより、内部エリアをリー

ドしたときも RD が出ます。)

ポート 31: 出力専用ポート

ライト: AD0~AD7端子のデータをライトするためのストローブ信号

ポート 32: 入出力ポート (プルアップ付き)

上位ライト: AD8~AD15 端子のデータをライトするためのストローブ信号

ポート 33: 入出力ポート (プルアップ付き)

割り込み要求端子 0: プログラマブル割り込み (レベルまたは立ち上がり/立ち

下がりエッジ) 要求端子

ポート 34: 入出力ポート (プルアップ付き)

割り込み要求端子 1: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

ポート 35: 入出力ポート (プルアップ付き)

割り込み要求端子 2: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

ポート 36: 入出力ポート (プルアップ付き)

割り込み要求端子 3: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

ポート 37: 入出力ポート (プルアップ付き)

割り込み要求端子 4: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

AD 外部トリガ端子: AD 変換開始用外部トリガ端子

ポート 40: 入出力ポート (プルアップ付き)

タイマ入力 4: 16 ビットタイマ 4 の入力

キー入力 0: キーオンウェイクアップ端子 0

ポート 41: 入出力ポート (プルアップ付き)

タイマ出力 4: 16 ビットタイマ 4 の出力

キー入力 1: キーオンウェイクアップ端子 1

ポート 42: 入出力ポート (プルアップ付き)

タイマ入力 6: 16 ビットタイマ 6 の入力

キー入力 2: キーオンウェイクアップ端子 2

ポート 43: 入出力ポート (プルアップ付き)

タイマ出力 6: 16 ビットタイマ 6 の出力

キー入力 3: キーオンウェイクアップ端子 3

ポート 44~47: 入出力ポート (プルアップ付き)

キー入力 4~7: キーオンウェイクアップ端子 4~7

ポート 50~57: 入力専用ポート

アナログ入力 0~7

ポート 60: 入出力ポート

シリアルバスインタフェースの SIOモード時クロック入出力端子

TMP93CS20

2004-02-10 93CS20-5

Page 7

TMP93CS20

表 2.2.1 ピン名称と機能 (2/3)

ピン名称 ピン数 入出力 機 能

P61

SO

SDA

P62

SI

SCL

P63

TXD0

P64

RXD0

P65

SCLK0

CTS0

P66

TI0

INT7

P67

TO1

P70

TI8

INT8

P71

TI9

INT9

P72

TO8

P73

SCOUT

P74

TIA

INTA

P75

TIB

INTB

P76

TOA

P77

NMI

P80

TXD1

P81

RXD1

P82

TI2

P83

TO3

P84

WAIT

P85 1 入出力 ポート 85: 入出力ポート (プログラマブルオープンドレイン機能付き)

P86

XT1

1 入出力

出力

入出力

1 入出力

入力

入出力

1 入出力

出力

1 入出力

入力

1 入出力

入出力

入力

1 入出力

入力

入力

1 入出力

出力

1 入出力

入力

入力

1 入出力

入力

入力

1 入出力

出力

1 入出力

出力

1 入出力

入力

入力

1 入出力

入力

入力

1 入出力

出力

1 入出力

入力

1 入出力

出力

1 入出力

入力

1 入出力

入力

1 入出力

出力

1 入出力

入力

1 入出力

入力

ポート 61: 入出力ポート (プログラマブルオープンドレイン機能付き)

シリアルバスインタフェースの SIOモード時データ送信チャネル

シリアルバスインタフェースの I

ポート 62: 入出力ポート (プログラマブルオープンドレイン機能付き)

シリアルバスインタフェースの SIOモード時データ受信チャネル

シリアルバスインタフェースの I

ポート 63: 入出力ポート (プログラマブルオープンドレイン機能付き)

シリアル送信データ 0

ポート 64: 入出力ポート

シリアル受信データ 0

ポート 65: 入出力ポート

シリアルクロック入出力 0

シリアルデータ送信可能 0 (Clear to send)

ポート 66: 入出力ポート

タイマ入力 0: 8 ビットタイマ 0 の入力

割り込み要求端子 7: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

ポート 67: 入出力ポート

タイマ出力 1: 8 ビットタイマ 0 またはタイマ 1 の出力

ポート 70: 入出力ポート (プルアップ付き)

タイマ入力 8: 16 ビットタイマ 8 の入力

割り込み要求端子 8: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

ポート 71: 入出力ポート (プルアップ付き)

タイマ入力 9: 16 ビットタイマ 8 の入力

割り込み要求端子 9: 立ち上がりエッジの割り込み要求端子

ポート 72: 入出力ポート (プルアップ付き)

タイマ出力 8: 16 ビットタイマ 8 の出力

ポート 73: 入出力ポート (プルアップ付き)

システムクロック出力: 外部回路同期用にシステムクロックまたはその 2倍の

クロックを出力します

ポート 74: 入出力ポート (プルアップ付き)

タイマ入力 A: 16 ビットタイマ A の入力

割り込み要求端子 A: プログラマブル割り込み (立ち上がり/立ち下がりエッジ)

要求端子

ポート 75: 入出力ポート (プルアップ付き)

タイマ入力 B: 16 ビットタイマ B の入力

割り込み要求端子 B: 立ち上がりエッジの割り込み要求端子

ポート 76: 入出力ポート (プルアップ付き)

タイマ出力 A: 16 ビットタイマ A の出力

ポート 77: 入出力ポート (プルアップ付き)

ノンマスカブル割り込み要求端子: 立ち下がり/両エッジがプログラマブルな割

ポート 80: 入出力ポート (プログラマブルオープンドレイン機能付き)

シリアル送信データ 1

ポート 81: 入出力ポート (プログラマブルオープンドレイン機能付き)

シリアル受信データ 1

ポート 82: 入出力ポート (プログラマブルオープンドレイン機能付き)

タイマ入力 2: 8 ビットタイマ 2 の入力端子

ポート 83: 入出力ポート (プログラマブルオープンドレイン機能付き)

タイマ出力 3: 8 ビットタイマ 2, 3 の出力端子

ポート 84: 入出力ポート (プログラマブルオープンドレイン機能付き)

ウェイト: CPU へのバスウェイト要求端子

ポート 86: 入出力ポート (オープンドレイン)

低周波発振器接続端子

2

C バスモード時データ入出力端子

2

C バスモード時クロック入出力端子

り込み要求端子

2004-02-10 93CS20-6

Page 8

TMP93CS20

表 2.2.1 ピン名称と機能 (3/3)

ピン名称 ピン数 入出力 機 能

P87

XT2

P90~P97

SEG24~SEG31

PA0~PA7

SEG32~SEG39

SEG0~SEG23 24 出力 LCD セグメント出力

COM0~COM3 4 出力 LCD コモン出力

AVCC 1 電源 AD コンバータ電源端子

AVSS 1 電源 AD コンバータ GND 端子 (0 V)

VREFH 1 入力 AD コンバータ用基準電源入力端子 (H)

VREFL 1 入力 AD コンバータ用基準電源入力端子 (L)

X1 1 入力 発振子接続端子

X2 1 出力 発振子接続端子

RESET 1 入力 リセット: LSI を初期化します。

ALE 1 出力 アドレスラッチイネーブル (ノイズ削減のため、出力禁止に設定できます。)

CLK 1 出力

EA 1 入力 VCC に接続

VCC 3 電源 電源端子 (全 VCC 端子を電源に接続)

VSS 8 電源 GND 端子 (全 VSS 端子を GND (0 V) に接続)

TEST1

TEST2

C0, C1,

V1~V3

1 入出力

出力

8 出力

出力

8 出力

出力

2 出力

入力

5 LCD 用

端子

ポート 87: 入出力ポート (オープンドレイン)

低周波発振器接続端子

ポート 90~97: 出力専用ポート (オープンドレイン)

セグメントデータ出力端子

ポート A0~A7: 出力専用ポートで、大電流ポート (オープンドレイン)

セグメントデータ出力端子

クロック出力: 「外部入力クロック X1÷4」のクロックが出力されます。リセッ

ト期間中は、プルアップされます (ノイズ削減のため出力禁止

に設定できます)。

テスト用端子 (両端子を基盤上で接続)

その他の端子とは接続しないでください。

LCD 駆動用昇圧端子。C0、C1 間および V1、V2、V3 と GND 間にコンデンサ

を接続。

注) プルアップ抵抗付き端子は、ソフトウエアによりその抵抗を端子から電気的に切り離すことができま

す。

2004-02-10 93CS20-7

Page 9

3. 動作説明

ここでは、TMP93CS20 の機能および基本動作について、ブロックごとに説明します。

なお、本章の最後に 7.「使用上の注意、制限事項」としてブロック別の注意、制限事項などを掲載

していますので、ご確認ください。

3.1 CPU

本デバイスには、高性能な 16 ビット CPU (TLCS-900/L CPU) が内蔵されています。CPU の動

作については、前章の “TLCS-900/L CPU” を参照してください。

ここでは、“TLCS-900/L CPU” にて説明されていない、TMP93CS20 独自の CPU 機能について

説明します。

3.1.1 リセット動作

本デバイスにリセットをかけるには電源電圧が動作範囲内であり、内部高周波発振器の発振

が安定した状態で少なくとも 10 システムクロック間 (20 MHz クロック発振時で 16 µs)、

RESET 入力をLow レベルにしてください。また、電源投入時は RESET 入力が Lowレベルで、

電源電圧が動作範囲内になり、内部高周波発振器の発振が安定した状態で、少なくとも 10 シ

ステムクロック間、

なお、リセット動作にてクロックギアは 1/16 モードに初期化されるので、システムクロッ

ク f

• プログラムカウンタ PC をアドレス FFFF00H~FFFF02H に格納されているリセットベク

• スタックポインタ XSP を 100H にセット

• ステータスレジスタ SR<IFF2:0>を 111 にセット (割り込みレベルのマスクレジスタをレ

• ステータスレジスタ SR<MAX>を 1 にセット (マキシマムモードにセット)

• ステータスレジスタ SR<RFP2:0>を 000 にクリア (レジスタバンクを 0 にセット)

外の CPU 内部のレジスタは、変化しません。

す。

• 仕様で決められているとおりに、内蔵 I/O のレジスタを初期化

• ポート端子 (内蔵 I/O にも使用できる兼用端子を含む) を、汎用入力ポートまたは汎用出

•

• ALE 端子を “ハイインピーダンス” にセット

は fc/32 (= fc/16 × 1/2) となります。

SYS

タに従いセット

PC<7:0> ←

PC<15:8> ←

PC<23:16> ←

ベル 7 にセット)

リセットが解除されると、セットされた PC に従い命令の実行を開始します。なお、上記以

また、リセットが受け付けられると、内蔵 I/O およびその他の端子は、下記の動作を行いま

力ポートにセット

CLK 端子を 1 レベルにプルアップ

TMP93CS20

RESET 入力の Low レベルを保持してください。

アドレス FFFF00H の値

アドレス FFFF01H の値

アドレス FFFF02H の値

注 1) リセット動作により、CPU の PC, SR, XSP 以外のレジスタ、内蔵 RAM のデータは変化しません。

注 2) リセット中、CLK 端子は H レベルにプルアップされますが、外部にて電圧レベルを下げないよう

にしてください。それにより誤動作する可能性があります。

図 3.1.1 にリセットタイミング例を示します。

2004-02-10 93CS20-8

Page 10

K

R

R

省略

省略

ド

ド

ド

ド

ド

TMP93CS20

リー

ライト

合計 X1 を 220 回

X1 を 45 回

)

サンプリング

)

)

)

(P20∼27 入力モー

(P32 入力モー

(入力モー

(入力モー

(出力モード : オープンドレイン出力)

アドレス

アドレス

サンプリング

データ出力

アドレス

アドレス

X1

CL

ALE

RESET

A16∼A23

RD

AD0∼AD15

W

HW

AD0∼AD15

P60∼P67

P20∼P27, P32,

P80∼P85

PA0∼PA7

P90∼P97,

P86, P87,

P33∼P37, P40∼P47,

P50∼P57, P70∼P77,

は内部でプルアップされていることを示します。

はハイインピーダンスを示します。

図 3.1.1 TMP93CS20 リセットタイミング図

2004-02-10 93CS20-9

Page 11

ダ

=

3.2 メモリマップ

図 3.2.1 に、TMP93CS20 のメモリマップと、CPU の各アドレッシングモードのアクセス範囲

を示します。

000000H

0000A0H

000100H

0008A0H

010000H

FF0000H

FFFF00H

FFFFFFH

内蔵 I/O (128 バイト)

内蔵 RAM (2 K バイト)

外部メモリ

内蔵 ROM

(64 K バイト)

ベクタテーブル (256 バイト)

イレクト

エリア (n)

(

64 Kバイト

エリア(nn)

内部エリア)

16 Mバイトエリア

(r32)

(−r32)

(r32+)

(r32 + d8/16)

(r32 + r8/16)

(nnn)

TMP93CS20

図 3.2.1 TMP93CS20 メモリマップ

2004-02-10 93CS20-10

Page 12

TMP93CS20

4. 電気的特性

4.1 最大定格 (TMP93CS20F)

計算式に使用している “X” は、SYSCR1 <SYSCK> で選択されたク

ロック f

択すると “X” の値が異なります。なお、例としての計算値は fc, ギア

= fc/1 (SYSCR1 <SYSCK, GEAR2:0> = 0000) のときの値です。

の周期を示しますので、クロックギアや低速発振器を選

FPH

項目 記号 定格 単位

電源電圧 Vcc −0.5~6.5 V

入力電圧 V

出力電流 (1 端子当たり), 大電流ポート I

出力電流 (1 端子当たり) I

出力電流 (大電流ポート合計) ∑I

出力電流 (全端子合計) ∑IOL 120 mA

出力電流 (全端子合計) ∑IOH −80 mA

消費電力 (Ta = 85°C) PD 600 mW

はんだ付け温度 (10 s) T

保存温度 T

動作温度 T

−0.5~Vcc + 0.5 V

IN

20 mA

OL1

2 mA

OL2

80 mA

OL1

260 °C

SOLDER

−65~150 °C

STG

−40~85 °C

OPR

注) 最大定格とは、瞬時たりとも超えてはならない規格であり、どの 1 つの項目も超えることができ

ない規格です。最大定格を超えると、破壊や劣化の原因となり、破裂・燃焼による傷害を負うこと

があります。従って、必ず最大定格を超えないように、応用機器の設計を行ってください。

4.2 DC 電気的特性 (1/2)

Ta = −40~85°C

項目 記号 条件 Min Typ. (注) Max 単位

AVss = Vss = 0 V

低レベル入力電圧

AD0~AD15

ポート V

KEY0~KEY7, NMI, INT0~INT4 V

EA V

X1 V

RESET V

高レベル入力電圧

AD0~AD15

ポート V

KEY0~KEY7, NMI , INT0~INT4 V

EA V

X1 V

RESET V

VCC

VIL Vcc ≧ 4.5 V 0.8

V

IL1

IL1

IL2

IL3

IL4

IL5

VIH V

V

IH

IH1

IH2

IH3

IH4

IH5

fc = 4~20 MHz 4.5 電源電圧 AVcc = Vcc

fc = 4~12.5 MHz

Vcc < 4.5 V 0.6

0.3 Vcc

0.25 Vcc

V

0.3

0.2 Vcc

V

0.7 Vcc

0.75 Vcc

Vcc − 0.3

0.8 Vcc

= 2.7~5.5 V

CC

≧ 4.5 V 2.2

CC

≧ 4.5 V 2.0

CC

Vcc = 2.7~5.5 V

fs = 30~

34 kHz

2.7

−0.3

0.6 Vcc

5.5 V

0.1 Vcc

Vcc + 0.3

V

注) Typ.値は特に指定のない限り、Ta = 25℃、Vcc = 5 V です。

2004-02-10 93CS20-227

Page 13

TMP93CS20

4.2 DC 電気的特性 (2/2)

項目 記号 条件 Min Typ.(注 1) Max 単位

= 1.6 mA

I

低レベル出力電圧 V

低レベル出力電流 (PA0~PA7) I

高レベル出力電圧

出力ポート電流

(8 出力ピン max)

入力リーク電流 I

出力リーク電流 I

パワーダウン電圧

(@STOP, RAM バックアップ)

端子容量 C

シュミット幅

KEYx,

NMI , INT0~INT4, RESET

プログラマブル

プルアップ抵抗

NORMAL 25 28

RUN 20 25

IDLE2 14 17

IDLE1

NORMAL 11 14

RUN 9 12

IDLE2 6 7.5

IDLE1

SLOW 28 37

RUN 21 27

IDLE2 14 19

IDLE1

STOP

OL

OLA

V

OH1

V

OH2

I

DAR

(注 2)

0.0 ≦ VIN ≦ VCC 0.02 ±5

LI

0.2 ≦ VIN ≦ VCC − 0.2 0.05 ±10

LO

V

STOP

IO

VTH 0.4 1.0 V

R

KH

I

CC

OL

V

=

OL

1.0 V

I

= −400 µA

OH

I

= −400 µA

OH

V

EXT

R

EXT

V

= 0.2 Vcc,

IL2

V

IH2

fc = 1 MHz 10 pF

Vcc = 5 V ± 10% 50 150

Vcc = 3 V ± 10% 100 300

Vcc = 5 V ± 10%

fc = 20 MHz

Vcc = 3 V ± 10%

fc = 12.5 MHz

Vcc = 3 V ± 10%

fs = 32.768 kHz

昇圧周波数 1 kHz 時

Ta ≦ 50°C 10

Ta ≦ 70°C 20

Ta ≦ 85°C

(Vcc = 2.7~5.5 V)

(Vcc = 5 V ± 10%) 16

(Vcc = 3 V ± 10%) 7

(Vcc = 3 V ± 10%)

(Vcc = 5 V ± 10%)

= 1.5 V

= 1.1 kΩ

(Vcc = 5 V ± 10%のみ)

= 0.8 Vcc

(Typ.値は Vcc = 3.0 V)

(Typ.値は Vcc = 3.0 V)

0.45 V

2.4

4.2

−1.0 −3.5 mA

2.0 6.0 V

3.5 5

1.5 2.0

7 9

0.2

50

mA

V

µA

kΩ

mA

mA

µA

µA

注 1) Typ.値は特に指定のない限り、Ta = 25°C、Vcc = 5 V です。

注 2) I

は、任意の出力ポートについて合計 8 本までこのスペックを保証します。

DAR

注 3) セグメント/コモン出力に無負荷の場合です。

注 4) I

NORMAL, SLOW の測定条件: CPU のみ動作、出力端子は開放、入力端子はレベル固定。

CC

(参) I

DAR

の定義図

I

DAR

R

EXT

V

EXT

2004-02-10 93CS20-228

Page 14

4.3 AC 電気的特性

(1) Vcc = 5 V ± 10%

TMP93CS20

No. 項目 記号

計算式 16 MHz 20 MHz

Min Max Min Max Min Max

1 発振周期 (= x) t

2 CLK パルス幅 t

3 A0~A23 有効 → CLK 保持 t

4 CLK 有効 → A0~A23保持 t

5 A0~A15 有効 → ALE 立ち下がり t

6 ALE 立ち下がり → A0~A15保持 t

7 ALE High パルス幅 t

8 ALE 立ち下がり → RD / WR 立ち下がり tLC 0.5x − 25 6 0 ns

9 RD / WR 立ち上がり → ALE立ち上がり tCL 0.5x − 20 11 5 ns

10 A0~A15 有効 → RD / WR 立ち下がり t

11 A0~A23 有効 → RD / WR 立ち下がり t

12 RD / WR 立ち上がり → A0~ A2 3保持 t

13 A0~A15 有効 → D0~D15 入力 t

14 A0~A23 有効 → D0~D15 入力 t

15 RD 立ち下がり → D0~D15入力 t

16 RD Low パルス幅 t

17 RD 立ち上がり → D0~D15保持 t

18 RD 立ち上がり → A0~A15出力 t

19 WR Low パルス幅 t

20 D0~D15 有効 → WR 立ち上がり t

21 WR 立ち上がり → D0~D15 保持 t

22 A0~A23 有効 → WAIT 入力 t

23 A0~A15 有効 → WAIT 入力 t

(1+ N) WAIT

モード

(1+ N) WAIT

モード

(1+ N) WAIT

モード

24 RD / WR 立ち下がり → WAIT 保持 tCW 2.0x + 0 125 100 ns

25 A0~A23 有効 → ポート入力 t

26 A0~A23 有効 → ポート保持 t

27 WR 立ち上がり → ポート有効 t

50 31250 62.5 50 ns

OSC

2x − 40 85 60 ns

CLK

0.5x − 20 11 5 ns

AK

1.5x − 70 24 5 ns

KA

0.5x − 15 16 10 ns

AL

0.5x − 20 11 5 ns

LA

x − 40 23 10 ns

LL

x − 25 38 25 ns

ACL

1.5x − 50 44 25 ns

ACH

0.5x − 25 6 0 ns

CA

3.0x − 55 133 95 ns

ADL

3.5x − 65 154 110 ns

ADH

2.0x − 60 65 40 ns

RD

2.0x − 40 85 60 ns

RR

0 0 0 ns

HR

x − 15 48 35 ns

RAE

2.0x − 40 85 60 ns

WW

2.0x − 55 70 45 ns

DW

0.5x − 15 16 10 ns

WD

3.5x − 90 129 85 ns

AWH

3.0x − 80 108 70 ns

AWL

2.5x − 120 36 5 ns

APH

2.5x + 50 206 175 ns

APH2

200 200 200 ns

CP

AC 測定条件

• 出力レベル : High 2.2 V/Low 0.8 V, CL = 50 pF

(ただし, AD0~AD15, A0~A23, ALE,

RD , WR , HWR , CLK は, CL = 100 pF)

単位

• 入力レベル : High 2.4 V/Low 0.45 V (AD0~AD15)

High 0.8 × Vcc/Low 0.2 × Vcc (AD0~AD15 を除く)

2004-02-10 93CS20-229

Page 15

(2) Vcc = 3 V ± 10%

TMP93CS20

No. 項目 記号

計算式 12.5 MHz

Min Max Min Max

1 発振周期 (= x) t

2 CLK パルス幅 t

3 A0~A23 有効 → CLK 保持 t

4 CLK 有効 → A0~A23保持 t

5 A0~A15 有効 → ALE 立ち下がり t

6 ALE 立ち下がり → A0~A15保持 t

7 ALE Highパルス幅 t

8 ALE 立ち下がり → RD / WR 立ち下がり tLC 0.5x − 35 5 ns

9 RD / WR 立ち上がり → ALE立ち上がり tCL 0.5x − 40 0 ns

10 A0~A15 有効 → RD / WR 立ち下がり t

11 A0~A23 有効 → RD / WR 立ち下がり t

12 RD / WR 立ち上がり → A0~A23保持 t

13 A0~A15 有効 → D0~D15 入力 t

14 A0~A23 有効 → D0~D15 入力 t

15 RD 立ち下がり → D0~D15 入力 t

16 RD Low パルス幅 t

17 RD 立ち上がり → D0~D15 保持 t

18 RD 立ち上がり → A0~A15出力 t

19 WR Low パルス幅 t

20 D0~D15 有効 → WR 立ち上がり t

21 WR 立ち上がり → D0~D15 保持 t

22 A0~A23 有効 → WAIT 入力 t

23 A0~A15 有効 → WAIT 入力 t

24 RD / WR 立ち下がり → WAIT 保持 tCW 2.0x + 0 160 ns

(1+ N) WAIT

モード

(1+ N) WAIT

モード

(1+ N) WAIT

モード

25 A0~A23 有効 → ポート入力 t

26 A0~A23 有効 → ポート保持 t

27 WR 立ち上がり → ポート有効 t

80 31250 80 ns

OSC

2x − 40 120 ns

CLK

0.5x − 30 10 ns

AK

1.5x − 80 40 ns

KA

0.5x − 35 5 ns

AL

0.5x − 35 5 ns

LA

x − 60 20 ns

LL

x − 50 30 ns

ACL

1.5x − 50 70 ns

ACH

0.5x − 40 0 ns

CA

3.0x − 110 130 ns

ADL

3.5x − 125 155 ns

ADH

2.0x − 115 45 ns

RD

2.0x − 40 120 ns

RR

0 0 ns

HR

x − 25 55 ns

RAE

2.0x − 40 120 ns

WW

2.0x − 120 40 ns

DW

0.5x − 40 0 ns

WD

3.5x − 130 150 ns

AWH

3.0x − 100 140 ns

AWL

2.5x − 120 80 ns

APH

2.5x + 50 250 ns

APH2

200 200 ns

CP

AC 測定条件

単位

• 出力レベル : High 0.7 × V

• 入力レベル : High 0.9 × V

/Low 0.3 × VCC, CL = 50 pF

CC

/Low 0.1 × V

CC

CC

2004-02-10 93CS20-230

Page 16

A

注

)

A

A

TMP93CS20

(1) リードサイクル

t

OSC

X1/XT1

t

CLK

CLK

Port input

0~A23

WAIT

RD

D0~AD15

LE

tAK t

t

AWH

t

AWL

t

APH

t

APH2

t

ADH

t

ACH

t

LL

t

ACL

A0~A15

tLC

t

CW

t

RR

t

RD

t

ADL

KA

D0~D15

tCA

t

HR

t

CL

t

RAE

tLA tAL

注) ポートのデータリードは内蔵エリアへのアクセスとなるため、外部端子の制御信号

などはイネーブル出力されません。上記波形は内部信号の動きとして認識してください。

また、上記ポート入出力タイミングおよび AC 特性は、代表的なタイミングを示しています。詳細

は弊社営業担当までお問い合わせください。

RD、 CS信号

2004-02-10 93CS20-231

Page 17

tWWt

A

注

A

A

(2) ライトサイクル

X1/XT1

CLK

0~A23

WAIT

TMP93CS20

Port output

WR , HWR

D0~AD15

LE

)

t

CP

t

DW

A0~A15 D0~D15

WD

注) ポートのデータライトは内蔵エリアへのアクセスとなるため、外部端子の制御信号

などはイネーブル出力されません。上記波形は内部信号の動きとして認識してください。

また、上記ポート入出力タイミングおよび AC 特性は、代表的なタイミングを示しています。詳細

は弊社営業担当までお問い合わせください。

WR 、CS 信号

2004-02-10 93CS20-232

Page 18

データ

Y

データ

4.4 シリアルチャネルタイミング

(1) I/O インタフェースモード

1. SCLK 入力モード

TMP93CS20

項目 記号

計算式 32.768 MHz 12.5 MHz 20 MHz

注)

Min Max Min Max Min Max Min Max

SCLK 周期 t

出力データ →

SCLK 立ち上がり/立ち下がり*

SCLK 立ち上がり/立ち下がり*

→

SCLK 立ち上がり/立ち下がり*

→

SCLK 立ち上がり/立ち下がり*

→

出力データ保持

入力データ保持

有効データ入力

16x 488 µs 1.28 0.8 µs

SCY

t

OSS

t

/2−5x−50 91.5 µs 190 100 ns

SCY

t

OHS

t

HSR

t

SRD

− 100 152 µs 300 150 ns

5x

0 0 0 0 ns

t

−5x−100 336 µs 780 450 ns

SCY

注) システムクロックを fs、またはプリスケーラへの入力クロックとして、fs の分周クロックを使用した場合。

*) SCLK立ち上がり/立ち下がり … SCLK 立ち上がりモードの場合は SCLK 立ち上がり、SCLK 立ち下がりモードの場合は SCLK

立ち下がりのタイミングです。

2. SCLK 出力モード

項目 記号

計算式 32.768 MHz 12.5 MHz 20 MHz

Min Max Min Max Min Max Min Max

SCLK 周期 (プログラマブル) t

出力データ → SCLK 立ち上がり t

SCLK 立ち上がり →

出力データ保持

SCLK 立ち上がり →

入力データ保持

SCLK 立ち上がり →

有効データ入力

16x 8192x 488 µs 250 ms 1.28 655.36 0.8 409.6 µs

SCY

t

OSS

t

2x-80

OHS

0

t

HSR

t

t

SRD

− 2x − 150 427 µs 970 550 ns

SCY

− 2x − 150 428 µs 970 550 ns

SCY

60 µs 80 20 ns

0 0 0 ns

注) システムクロックを fs、またはプリスケーラへの入力クロックとして、fs の分周クロックを使用した場合。

注)

単位

SCLK

(出力モード/

入力立ち上がりモード)

SCLK

(入力立ち下がりモード)

出力

入力

TXD

RXD

t

SC

t

t

OSS

OHS

0

t

123

SRD

t

HSR

3 2 10

Valid Valid Valid Valid

(2) UART モード (SCLK0, SCLK1 外部入力)

単

位

項目 記号

計算式 32.768 MHz 12.5 MHz 20 MHz

注)

Min Max Min Max Min Max Min Max

SCLK 周期 t

SCLK 低レベルパルス幅 t

SCLK 高レベルパルス幅 t

4x + 20 122 µs 340 220 ns

SCY

2x + 5 6 µs 165 105 ns

SCYL

2x + 5 6 µs 165 105 ns

SCYH

注) システムクロックを fs、またはプリスケーラへの入力クロックとして、fs の分周クロックを使用した場合。

単

位

2004-02-10 93CS20-233

Page 19

TMP93CS20

4.5 AD 変換特性 (Vss = 0 V, Avcc = Vcc, A vss = Vss, T a = −40~85°C)

項目 記号 条 件 Min Typ. Max 単位

アナログ基準電圧 (+) V

アナログ基準電圧 (−) V

アナログ入力電圧 V

アナログ基準電圧電源電流 V

<VREFON> = 1 VCC = 3 V ± 10% 1.0 1.5

<VREFON> = 0

総合誤差

(量子化誤差を含みません)

REFH

REFL

V

AIN

I

REF

(V

= 0 V)

REFL

−

VCC = 5 V ± 10 % V

VCC = 3 V ± 10% V

VCC = 5 V ± 10% VSS

VCC = 3 V ± 10% VSS

= 5 V ± 10% 1.6 2.0

CC

V

= 2.7~5.5 V 0.02 5.0 µ A

CC

VCC = 5 V ± 10% ± 1.0 ± 3.0

= 3 V ± 10% ± 1.0 ± 5.0

V

CC

− 1.5 V V

CC

− 0.2 V V

CC

V

REFL

CC

CC

VCC

VCC

REFH

V

mA

LSB

注 1) 1LSB = (V

REFH

− V

REFL

)/210 [V]

注 2) 最低動作周波数について

AD コンバータの動作は、fc 使用時にクロックギアで選択されたクロックの周波数が 4 MHz 以上で

保証します。

注 3) AVCC 端子より流れる電源電流は、VCC 端子の電源電流 I

4.6 LCD ドライバ特性

チャージポンプ特性 記号 Min Typ. Max 単位

リファレンス入力電圧 V

出力電圧 V2 端子 V

V3 端子 V

外付け容量 C0~C1 間 C

V1 端子 C

V2 端子 C

V3 端子 C

注) 出力電圧、外付け容量は無負荷の場合です。

0.9 1.83 V

L1

2 × VL1 V

L2

3 × VL1 V

L3

0.1 1.0 µF

PMP

0.1 1.0 µF

VL1

0.1 1.0 µF

VL2

0.1 1.0 µF

VL3

に含みます。

CC

2004-02-10 93CS20-234

Page 20

4.7 イベントカウンタ (TI0, TI2, TI4 , TI6 , TI8∼TIB)

TMP93CS20

項目 記号

クロック周期 t

クロック低レベルパルス幅 t

クロック高レベルパルス幅 t

8X + 100 740 500 ns

VCK

4X + 40 360 240 ns

VCKL

4X + 40 360 240 ns

VCKH

4.8 割り込み、キャプチャ

(1) NMI , INT0∼ΙΝΤ4 割り込み, INTKEY 割り込み

項目 記号

低レベルパルス幅 t

高レベルパルス幅 t

(2) INT7~INTB 割り込み、キャプチャ

項目 記号

低レベルパルス幅 t

高レベルパルス幅 t

4X 320 200 ns

INTAL

4X 320 200 ns

INTAH

4X + 100 420 300 ns

INTBL

4X + 100 420 300 ns

INTBH

計算式 12.5 MHz 20 MHz

Min Max Min Max Min Max

計算式 12.5 MHz 20 MHz

Min Max Min Max Min Max

計算式 12.5 MHz 20 MHz

Min Max Min Max Min Max

単位

単位

単位

4.9 SCOUT 端子 AC 特性

項目 記号

高レベルパルス幅

V

= 5 V ± 10%

CC

VCC = 3 V ± 10%

低レベルパルス幅

V

= 5 V ± 10%

CC

VCC = 3 V ± 10%

測定条件

• 出力レベル : High 2.2 V/Low 0.8 V, CL = 10 pF

t

SCH

t

SCL

SCOUT

計算式 12.5 MHz 20 MHz

Min Max Min Max Min Max

0.5X − 10

0.5X − 20 20 − −

0.5X − 10

0.5X − 20 20 − −

t

SCH

t

SCL

30

30

15

15

単位

ns

ns

2004-02-10 93CS20-235

Page 21

命令

A

4.10 シリアルバスインタフェースタイミング

(1) I2C バスモード

TMP93CS20

項目 記号

START命令 → SDA立ち下がり t

開始条件のホールド時間 t

SCL 低レベルパルス幅 t

SCL 高レベルパルス幅 t

データのホールド時間 (入力) t

データのセットアップ時間 (入力) t

データのホールド時間 (出力) t

データ有効 → SCL立ち上がり t

STOP 命令 → SDA立ち下がり t

SDA 立ち下がり → SCL立ち上がり t

停止条件のホールド時間 t

3X s

GSTA

2

HD:STA

2

LOW

2

HIGH

0 ns

HD:IDAT

250 ns

SU:IDAT

7X 11X s

HD:ODAT

2

ODAT

3X s

FSDA

2

FDRC

2

SU:STO

注) n は SBICR1<SCK2:0> で設定してください。

スタート

SDA

t

HD:ODAT

t

HD:IDAT

t

HIGH

SCL

t

GSTA

t

HD:STA

t

LOW

計算式

単位

Min Typ. Max

n

X s

n

X s

n

X+12X s

n

X − t

n

X s

n

X + 16X s

t

ODAT

t

SU:IDAT

s

HD:ODAT

ストップ命令

t

FSD

t

FDRC

t

SU:STO

2004-02-10 93CS20-236

Page 22

TMP93CS20

(2) クロック同期式 8 ビット SIO モード (シリアルバスインタフェース)

1. SCK 入力モード

SCK 周期 t

SCK 立ち下がり → 出力データ保持 t

出力データ有効 → SCK立ち上がり t

SCK 立ち上がり → 入力データ保持 t

入力データ有効 → SCK立ち上がり t

SCK 周期 t

SCK 立ち下がり → 出力データ保持 t

出力データ有効 → SCK立ち上がり t

SCK 立ち上がり → 入力データ保持 t

入力データ有効 → SCK 立ち上がり t

SCK

(入力/出力モード)

SO

(出力データ)

SI

(入力データ)

項目 記号

2. SCK 出力モード

項目 記号

t

OHS2

計算式

単位

Min Max

SCY2

6X s

OHS2

t

OSS2

6X ns

HSR2

0 ns

ISS2

25X s

- 6X s

SCY2

計算式

単位

Min Max

2

SCY2

2X s

OHS2

t

OSS2

2X s

HSR2

0 ns

ISS2

t

SCY2

t

HSR2

5

X 211X s

- 2X s

SCY2

t

OSS2

t

ISS2

2004-02-10 93CS20-237

Loading...

Loading...