TC74VCX162823FT

東芝 CMOS デジタル集積回路 シリコン モノリシック

TC74VCX162823FT

Low-Voltage 18-Bit D-Type Flip-Flop with 3.6 V Tolerant Inputs and Outputs

TC74VCX162823FT は、低電圧駆動の CMOS 18 ビットフリップ

フロップです。CMOS の特長である低消費電力で 1.8 V、2.5 V、3.3

V システムにおける高速動作が可能です。

すべての入力端子および出力端子 (出力オフ時だけ) には電源電

圧にかかわらず 3.6 V までの信号入力が許容されるため、2 電源を持

つシステムでのインタフェースに最適です。

コントロール入力 (CK、CKEN、CLR、OE) は 9 ビット単位で共

通であり、デュアル 9 ビット構成、シングル 18 ビット構成のいずれ

でも使用できます。CKEN 入力が “L” の状態で D 入力に与えられ

た信号は、CK 入力の立ち上がりで Q 出力に伝えられます。CKEN

入力が “H” の状態では CK は受け付けられなくなります。CLR 入力

は CK に非同期に Q 出力の状態を決定 (“L” レベル) し、これは “L”

レベルで有効です。“H” レベルの OE 信号により、内部フリップフ

ロップの動作とは無関係に出力を高インピーダンス状態にできるため、バスラインへのインタフェースが容易です。

すべての出力には 26 Ω の直列抵抗が付加されており、これにより外付け抵抗なしで反射などによるノイズを抑えるこ

とができます。

また、すべての入力には、静電破壊から素子を保護するための保護回路が付加されています。

特

特 長長長長

特特

質量: 0.25 g (標準)

· 出力に 26 Ω の抵抗が付加されています。

· 動作電源電圧 : V

· 高速動作 : tpd = 4.4 ns (最大) (VCC = 3.0~3.6 V)

: tpd = 5.8 ns (最大) (VCC = 2.3~2.7 V)

: t

· 出力電流 : IOH/IOL = ±12 mA (最小) (VCC = 3.0 V)

: I

: I

· 高ラッチアップ耐量 : ±300 mA 以上

· 高静電破壊耐量 : ±200 V 以上 (JEITA 方式)

: ±2000 V 以上 (MIL-STD 方式)

· パッケージ : TSSOP (Thin Shrink Small Outline Package)

· 全入出力ともに 3.6 V トレラント機能およびパワーダウンプロテクション機能あり

= 1.8~3.6 V

CC

= 9.8 ns (最大) (VCC = 1.8 V)

pd

OH/IOL

OH/IOL

= ±8 mA (最小) (VCC = 2.3 V)

= ±4 mA (最小) (VCC = 1.8 V)

1

2001-09-20

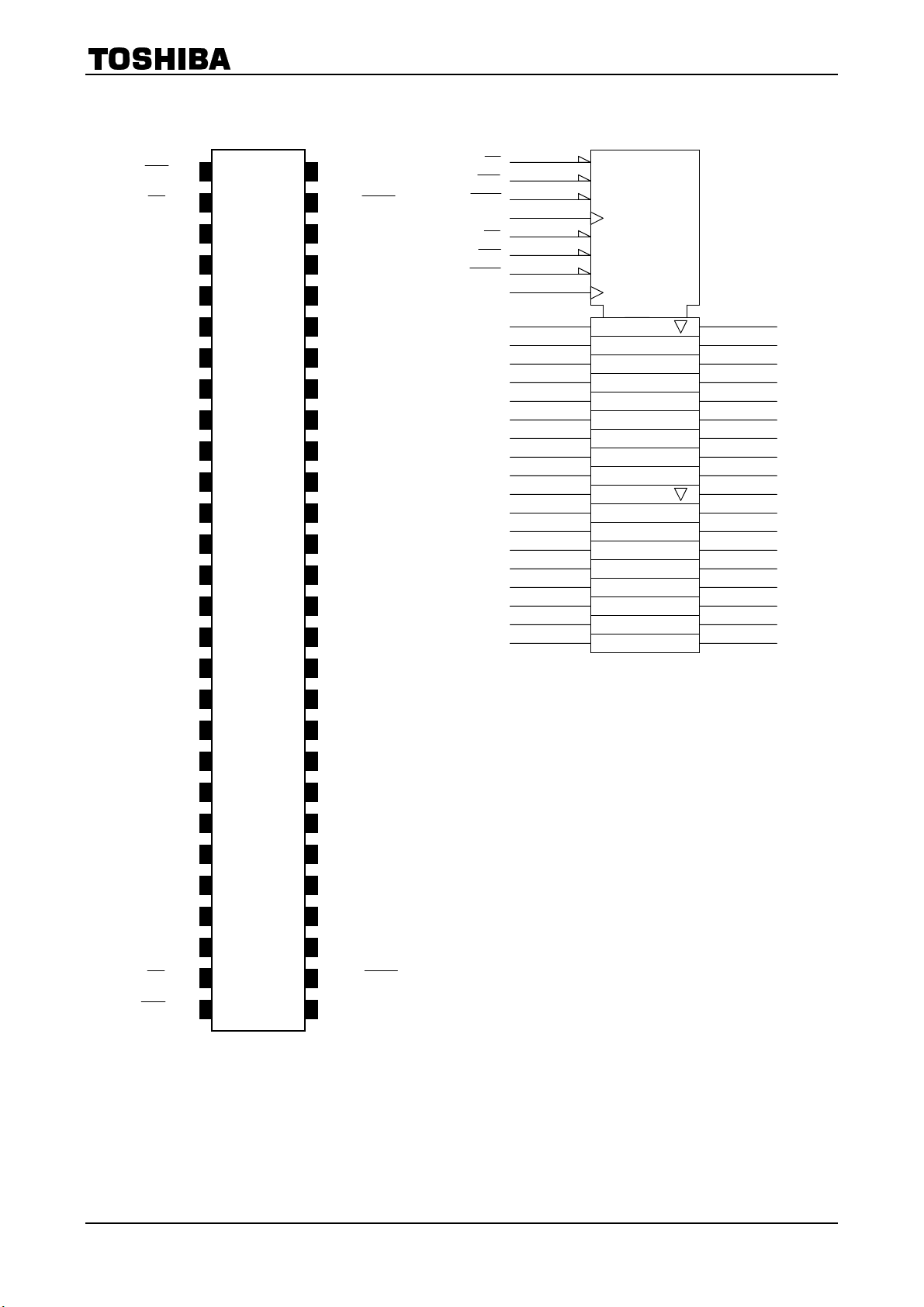

ピン接続図

K1CK

ピン接続図

ピン接続図ピン接続図

CLR1

OE1

1Q1

GND

1Q2

1Q3

V

CC

1Q4

1Q5

1Q6

GND 11

1Q7

1Q8

1Q9

2Q1

2Q2

2Q3

(top vi ew)

1

2

3

4

5

6

7

8

9

10

12

13

14

15

16

17

論理図

56

1CK

55

CKEN1

54

1D1

53

GND

52

1D2

51

1D3

V

CC

1D4

1D5

1D6

GND

1D7

1D8

1D9

2D1

2D2

2D3

50

49

48

47

46

45

44

43

42

41

40

論理図

論理図論理図

OE1

CLR1

CKEN1

OE2

CLR2

CKEN2

1D1

1D2

1D3

1D4

1D5

1D6

1D7

1D8

1D9

2D1

2D2

2D3

2D4

2D5

2D6

2D7

2D8

2D9

TC74VCX162823FT

2

1

55

56

27

28

30

29

54

52

51

49

48

47

45

44

43

42

41

40

38

37

36

34

33

31

EN1

R2

G3

3C4

EN5

R6

G7

7C8 2C

4D 1, 2

8D 5, 6

3

5

6

8

9

10

12

13

14

15

16

17

19

20

21

23

24

26

1Q1

1Q2

1Q3

1Q4

1Q5

1Q6

1Q7

1Q8

1Q9

2Q1

2Q2

2Q3

2Q4

2Q5

2Q6

2Q7

2Q8

2Q9

GND

2Q4

2Q5

2Q6

V

CC

2Q7

2Q8

18

19

20

21

22

23

24

25GND

262Q9

27OE2

28CLR2

39

38

37

36

35

34

33

32

31

30

29

GND

2D4

2D5

2D6

VCC

2D7

2D8

GND

2D9

CKEN2

2CK

2

2001-09-20

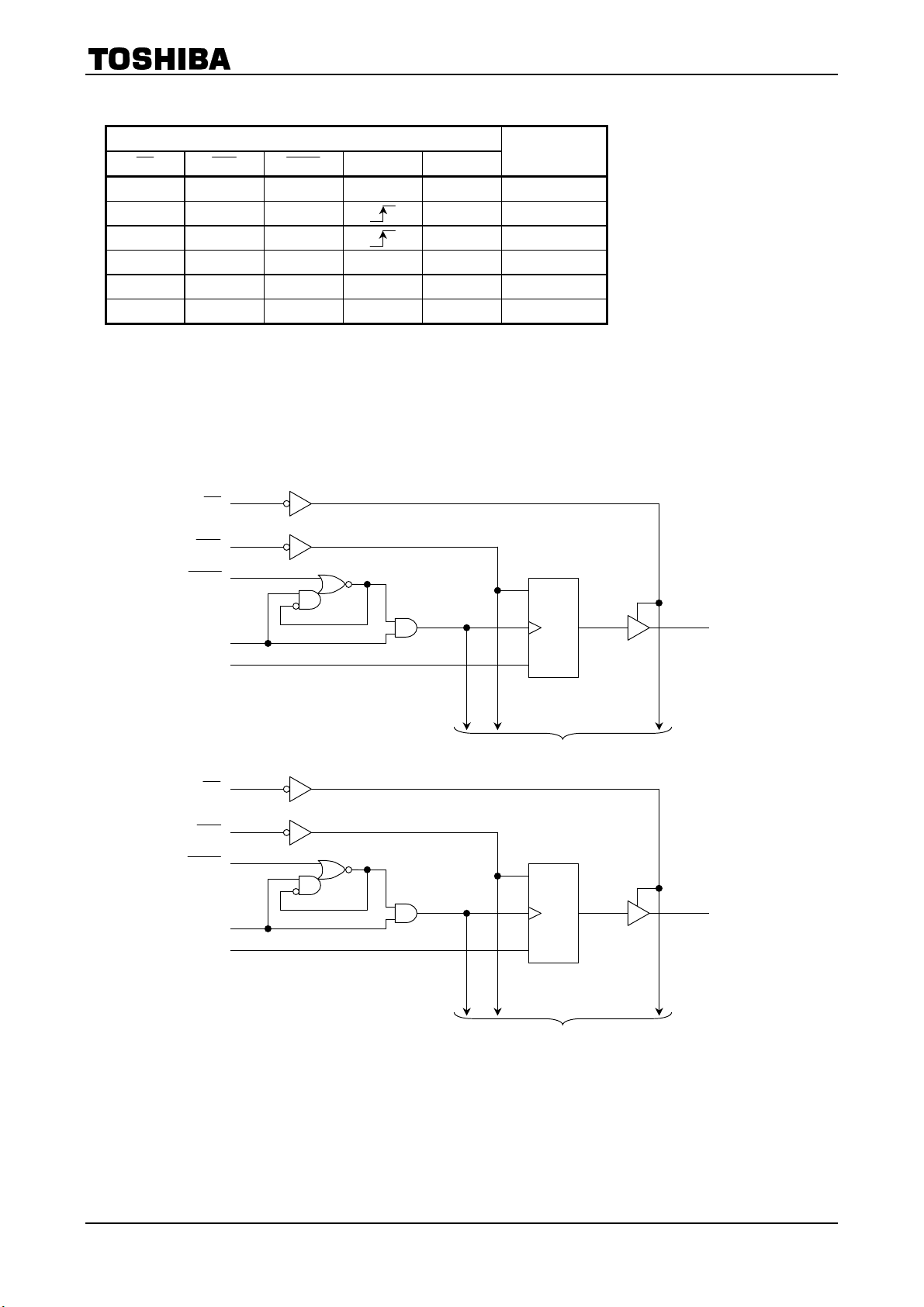

真理値表

K

K

真理値表

真理値表真理値表

(each 9-bit flip flop)

TC74VCX162823FT

OE CLR CKEN CK D

L L X X X L

L H L H H

L H L L L

L H L L X Qn

L H H X X Qn

H X X X X Z

X : Don’t care

Z : High impedance

Qn : 変化しない

システム

システム図

システムシステム

図

図図

CKEN1

CLR1

OE1

1C

1D1

2

1

55

56

54

Inputs

Outputs

Q

R

CK

D

3

1Q1

To eight other channels

27

OE2

2D1

28

30

29

42

R

CK

D

To eight other channels

15

2Q1

CLR2

CKEN2

2C

3

2001-09-20

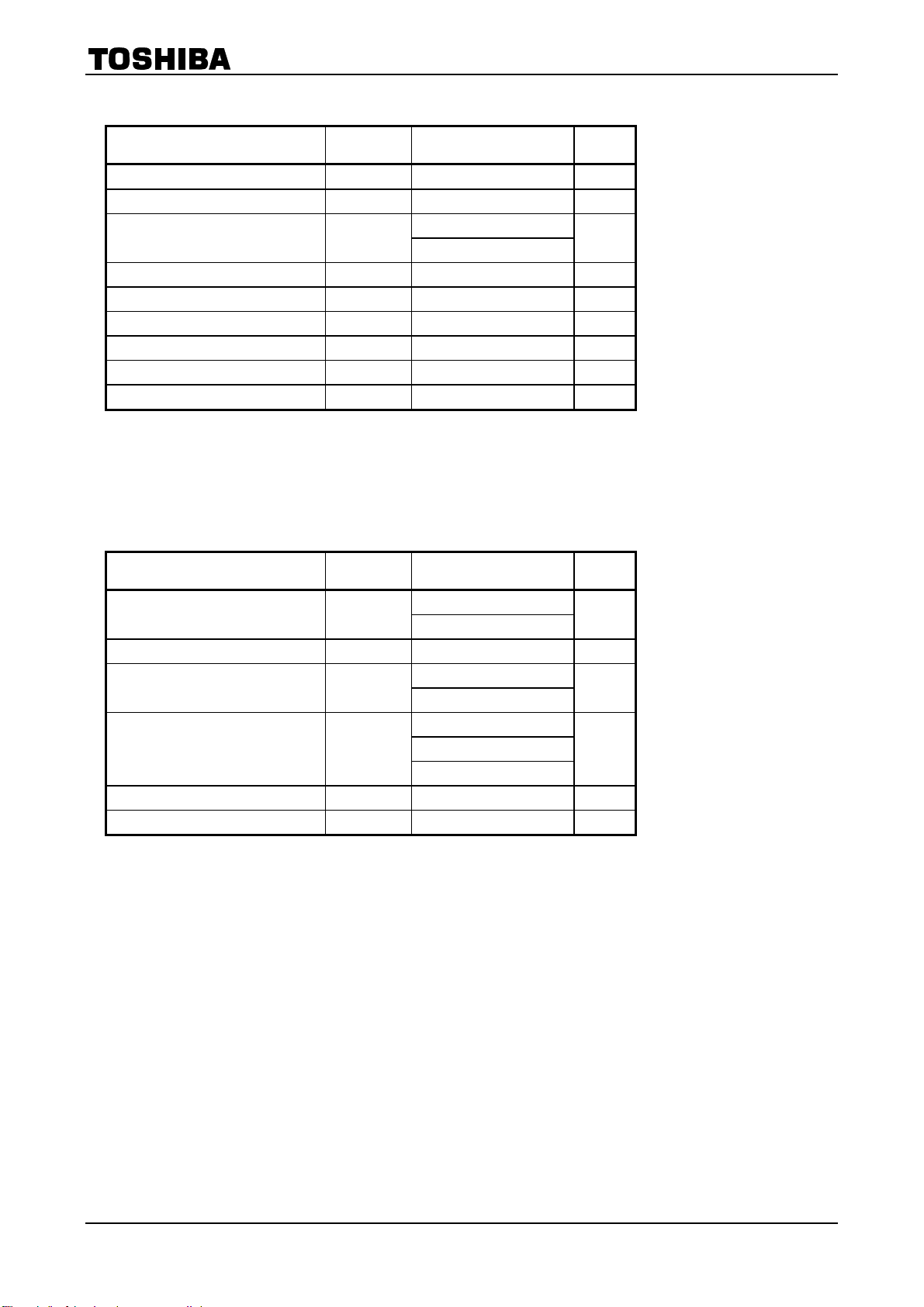

最大定格

最大定格

最大定格最大定格

TC74VCX162823FT

項目 記号 定格 単位

電源電圧 V

入力電圧 V

出力電圧 V

入力保護ダイオード電流 I

出力寄生ダイオード電流 I

出力電流 I

許容損失 P

電源/GND 電流 (1 電源端子当たり) ICC/I

保存温度 T

CC

IN

OUT

IK

OK

OUT

D

GND

stg

-0.5~4.6 (注 1)

-0.5~VCC + 0.5 (注 2)

±50 (注 3) mA

-0.5~4.6 V

-0.5~4.6 V

-50 mA

±50 mA

400 mW

±100 mA

-65~150 °C

注 1: オフ状態

注 2: “H” または “L” 状態、I

注 3: V

OUT

< GND, V

OUT

> VCC

の最大定格を超えないこと。

OUT

推奨動作条件

推奨動作条件

推奨動作条件推奨動作条件

項目 記号 定格 単位

電源電圧 V

入力電圧 V

出力電圧 V

出力電流 IOH/IOL

動作温度 T

入力上昇、下降時間 dt/dv 0~10 (注 10) ns/V

CC

IN

OUT

opr

1.2~3.6 (注 4)

0~3.6 (注 5)

0~VCC (注 6)

±12 (注 7)

±8 (注 8)

±4 (注 9)

1.8~3.6

-0.3~3.6 V

-40~85 °C

V

V

V

mA

注 4: データ保持

注 5: オフ状態

注 6: “H” または “L” 状態

注 7: V

= 3.0~3.6 V

CC

注 8: VCC = 2.3~2.7 V

注 9: VCC = 1.8 V

注 10: VIN = 0.8~2.0 V, VCC = 3.0 V

4

2001-09-20

電気的特性

<

<

電気的特性

電気的特性電気的特性

DC 特性

特性

特性特性

(Ta ==== ----40~85°C, 2.7 V <<<< V

CC

<<<<

3.6 V)

=

=

TC74VCX162823FT

項目 記号 測定条件

入力電圧

出力電圧

入力電流 I

スリーステート

オフリーク電流

電源オフリーク電流 I

静的消費電流

“H” レベル VIH ¾ 2.7~3.6 2.0 ¾

“L” レベル V

“H” レベル V

“L” レベル VOL VIN = VIH or VIL

DC 特性

特性

特性特性

(Ta ==== ----40~85°C, 2.3 V

V

CC

¾ 2.7~3.6 ¾ 0.8

IL

IOH = -100 mA 2.7~3.6

V

OH

IN

I

OZ

OFF

ICC

DICC VIH = VCC - 0.6 V (1 入力当たり) 2.7~3.6 ¾ 750

= VIH or VIL

IN

VIN = 0~3.6 V 2.7~3.6 ¾ ±5.0 mA

V

= VIH or V

IN

V

= 0~3.6 V

OUT

VIN, V

VIN = VCC or GND 2.7~3.6 ¾ 20.0

V

CC

<<<<

V

CC

=

=

IL

= 0~3.6 V 0 ¾ 10.0 mA

OUT

(VIN, V

OUT

<<<<

2.7 V)

=

=

IOH = -6 mA 2.7 2.2 ¾

IOH = -8 mA 3.0 2.4 ¾

I

= -12 mA 3.0 2.2 ¾

OH

IOL = 100 mA 2.7~3.6 ¾ 0.2

IOL = 6 mA 2.7 ¾ 0.4

IOL = 8 mA 3.0 ¾ 0.55

= 12 mA 3.0 ¾ 0.8

I

OL

2.7~3.6 ¾ ±10.0 mA

)<3.6 V 2.7~3.6 ¾ ±20.0

最小 最大 単位

(V)

V

CC

- 0.2

¾

V

V

mA

項目 記号 測定条件

入力電圧

出力電圧

入力電流 I

スリーステート

オフリーク電流

電源オフリーク電流 I

静的消費電流 ICC

“H” レベル VIH ¾ 2.3~2.7 1.6 ¾

“L” レベル V

“H” レベル V

“L” レベル VOL VIN = VIH or VIL

V

CC

¾ 2.3~2.7 ¾ 0.7

IL

IOH = -100 mA 2.3~2.7

V

OH

IN

I

OZ

OFF

= VIH or VIL

IN

VIN = 0~3.6 V 2.3~2.7 ¾ ±5.0 mA

V

= VIH or V

IN

V

= 0~3.6 V

OUT

VIN, V

VIN = VCC or GND 2.3~2.7 ¾ 20.0

V

CC

IL

= 0~3.6 V 0 ¾ 10.0 mA

OUT

(VIN, V

OUT

IOH = -4 mA 2.3 2.0 ¾

IOH = -6 mA 2.3 1.8 ¾

I

= -8 mA 2.3 1.7 ¾

OH

IOL = 100 mA 2.3~2.7 ¾ 0.2

IOL = 6 mA 2.3 ¾ 0.4

IOL = 8 mA 2.3 ¾ 0.6

2.3~2.7 ¾ ±10.0 mA

)<3.6 V 2.3~2.7 ¾ ±20.0

最小 最大 単位

(V)

V

CC

- 0.2

V

¾

V

mA

5

2001-09-20

TC74VCX162823FT

<

DC 特性

特性

特性特性

入力電圧

出力電圧

入力電流 I

スリーステート

オフリーク電流

電源オフリーク電流 I

静的消費電流 ICC

(Ta ==== ----40~85°C, 1.8 V

項目 記号 測定条件

“H” レベル VIH ¾ 1.8~2.3

“L” レベル V

“H” レベル V

“L” レベル VOL VIN = VIH or VIL

<<<<

V

<<<< 2.3 V)

CC

=

=

¾ 1.8~2.3 ¾

IL

V

OH

IN

I

OZ

OFF

= VIH or VIL

IN

VIN = 0~3.6 V 1.8 ¾ ±5.0 mA

V

= VIH or V

IN

V

= 0~3.6 V

OUT

VIN, V

OUT

VIN = VCC or GND 1.8 ¾ 20.0

(VIN, V

V

CC

V

CC

IOH = -100 mA 1.8

= -4 mA 1.8 1.4 ¾

I

OH

IOL = 100 mA 1.8 ¾ 0.2

= 4 mA 1.8 ¾ 0.3

I

OL

IL

= 0~3.6 V 0 ¾ 10.0 mA

)<3.6 V 1.8 ¾ ±20.0

OUT

最小 最大 単位

(V)

0.7

´

VCC

V

CC

- 0.2

1.8 ¾ ±10.0 mA

0.2

V

¾

CC

¾

V

´

V

mA

6

2001-09-20

AC 特性

特性

特性特性

TC74VCX162823FT

(Ta ==== ----40~85°C, Input: tr ==== tf ==== 2.0 ns, CL ==== 30 pF, RL ==== 500 WWWW)

項目 記号 測定条件

最大クロック周波数 f

伝搬遅延時間

(CK-Q)

伝搬遅延時間

CLR -Q)

(

出力イネーブル時間

出力ディセーブル時間

最小パルス幅

CLR )

(CK,

最小セットアップ時間

CKEN )

(D,

最小ホールド時間

CKEN )

(D,

最小リムーバル時間 t

出力ピン間スキュー

max

t

pLH

t

pHL

t

pHL

t

pZL

t

pZH

t

pLZ

t

pHZ

t

W (H)

t

W (L)

t

t

rem

t

osLH

t

osHL

図 1, 図 2

図 1, 図 2

図 1, 図 3

図 1, 図 4

図 1, 図 4

図 1, 図 2, 図 3

図 1, 図 2, 図 5

s

図 1, 図 2, 図 5

h

図 1, 図 6

V

(V)

CC

1.8 100 ¾

2.5 ± 0.2 200 ¾

3.3 ± 0.3 250 ¾

1.8 1.5 9.8

2.5 ± 0.2 0.8 5.8

3.3 ± 0.3 0.6 4.4

1.8 1.5 9.8

2.5 ± 0.2 0.8 6.0

3.3 ± 0.3 0.6 4.6

1.8 1.5 9.8

2.5 ± 0.2 0.8 5.9

3.3 ± 0.3 0.6 4.3

1.8 1.5 8.8

2.5 ± 0.2 0.8 4.9

3.3 ± 0.3 0.6 4.3

1.8 4.0 ¾

2.5 ± 0.2 1.5 ¾

3.3 ± 0.3 1.5 ¾

1.8 2.5 ¾

2.5 ± 0.2 1.5 ¾

3.3 ± 0.3 1.5 ¾

1.8 1.0 ¾

2.5 ± 0.2 1.0 ¾

3.3 ± 0.3 1.0 ¾

1.8 4.0 ¾

2.5 ± 0.2 2.0 ¾

3.3 ± 0.3 2.0 ¾

1.8 ¾ 0.5

(注 11)

2.5 ± 0.2 ¾ 0.5

3.3 ± 0.3 ¾ 0.5

最小 最大 単位

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

負荷容量 (CL) が 50 pF の場合の最大値は、上記値におよそ 300 ps を加えた値となります。

注 11: この項目は、設計的に保証される項目です。

(t

osLH

= |t

pLHm

- t

pLHn

|, t

osHL

= |t

pHLm

- t

pHLn

|)

7

2001-09-20

スイッチングノイズ特性

スイッチングノイズ特性

スイッチングノイズ特性スイッチングノイズ特性

TC74VCX162823FT

(Ta ==== 25°C, Input: tr ==== tf ==== 2.0 ns, CL ==== 30 pF, RL ==== 500 WWWW)

項目 記号 測定条件

非動作出力最大ダイナミック V

非動作出力最小ダイナミック VOL V

非動作出力最小ダイナミック VOH V

OL

V

OLP

OLV

OHV

VIH = 1.8 V, VIL = 0 V (注 12) 1.8 0.15

VIH = 2.5 V, VIL = 0 V (注 12) 2.5 0.25

= 3.3 V, VIL = 0 V (注 12) 3.3 0.35

V

IH

VIH = 1.8 V, VIL = 0 V (注 12) 1.8 -0.15

VIH = 2.5 V, VIL = 0 V (注 12) 2.5 -0.25

V

= 3.3 V, VIL = 0 V (注 12) 3.3 -0.35

IH

VIH = 1.8 V, VIL = 0 V (注 12) 1.8 1.55

VIH = 2.5 V, VIL = 0 V (注 12) 2.5 2.05

VIH = 3.3 V, VIL = 0 V (注 12) 3.3 2.65

V

CC

標準 単位

(V)

注 12: この項目は、設計的に保証される項目です。

容量特性

容量特性

容量特性容量特性

入力容量

出力容量

等価内部容量 CPD fIN = 10 MHz (注 13) 1.8, 2.5, 3.3 20 pF

(Ta ==== 25°C)

項目 記号 測定条件

V

(V)

CC

CIN ¾ 1.8, 2.5, 3.3 6 pF

CO ¾ 1.8, 2.5, 3.3 7 pF

標準 単位

V

V

V

注 13: C

動作消費電流から算出した IC 内部の等価容量です。

は、

PD

無負荷時の平均動作消費電流は、次式から求められます。

I

CC (opr)

= CPD・VCC・fIN + ICC/18 (1 回路当たり)

8

2001-09-20

AC 電気的特性測定回路

電気的特性測定回路

電気的特性測定回路電気的特性測定回路

スイッチ

Output Measure

AC 電気的特性測定

電気的特性測定波形

電気的特性測定電気的特性測定

波形

波形波形

L

C

tr 2.0 ns

TC74VCX162823FT

6.0 V or VCC ´ 2

Open

R

L

R

L

GND

C

= 30 pF

L

R

= 500 W

L

tf 2.0 ns

図

図 1

図図

項 目 スイッチ

t

, t

pLH

t

t

pHZ

pLZ

Open

pHL

6.0 V @VCC = 3.3 ± 0.3 V

, t

pZL

, t

pZH

V

´ 2 @VCC = 2.5 ± 0.2 V

GND

CC

@V

= 1.8 V

CC

Input

(CK)

Input

(D)

Output

(Q)

10%

90%

V

M

2.0 ns tf 2.0 ns

t

r

90%

V

10%

V

t

pHL

図

図 2 t

図図

M

t

(H) th (H) th (L) ts (L)

s

M

pLH

, t

t

pLH

, tw, ts, th

pHL

tw (H) tw (L)

VIH

GND

V

IH

GND

V

OH

V

OL

Input

(

CLR )

t

(L)

w

VIH

GND

Output

(Q)

V

M

t

pHL

図

図 3 t

図図

pLH

9

, t

pHL

V

OH

V

OL

2001-09-20

TC74VCX162823FT

tr 2.0 ns

Output Enable

Control (

Output (Q)

High to Off to High

OE )

Output (Q)

Low to Off to Low

t

pLZ

t

pHZ

Outputs

enabled

図

図 4 t

図図

pLZ

t

2.0 ns tf 2.0 ns

r

Input

(

CKEN )

Output

(CK)

10%

VM

90%

t

(H)

s

t

2.0 ns

f

90%

V

M

10%

t

pZL

V

X

V

Y

Outputs

disabled

, t

pHZ

2.0 ns

t

r

VM

th (H) ts (L) th (L)

, t

t

pZL

pZH

, t

pZH

V

M

VM

Outputs

enabled

V

IH

GND

3.0 V or V

VOL

V

OH

GND

V

GND

V

GND

CC

IH

IH

図

図 5 ts, th

図図

t

2.0 ns

r

Input

(

CLR )

Output

(CK)

記号

VIH 2.7 V VCC V

VM 1.5 V VCC/2 VCC/2

VX VOL + 0.3 V VOL + 0.15 V VOL + 0.15 V

VY VOH - 0.3 V VOH - 0.15 V VOH - 0.15 V

10%

3.3 ± 0.3 V 2.5 ± 0.2 V 1.8 V

90%

VM

図

図 6 t

図図

t

rem

10%

tr 2.0 ns

rem

VCC

90%

V

M

VIH

GND

V

IH

GND

CC

10

2001-09-20

外形図

外形図

外形図外形図

TC74VCX162823FT

質量: 0.25 g (標準)

11

2001-09-20

TC74VCX162823FT

当社半導体製品取り扱い上のお願い

当社半導体製品取り扱い上のお願い

当社半導体製品取り扱い上のお願い当社半導体製品取り扱い上のお願い

· 当社は品質、信頼性の向上に努めておりますが、一般に半導体製品は誤作動したり故障することがあります。当

社半導体製品をご使用いただく場合は、半導体製品の誤作動や故障により、生命・身体・財産が侵害されることの

ないように、購入者側の責任において、機器の安全設計を行うことをお願いします。

なお、設計に際しては、最新の製品仕様をご確認の上、製品保証範囲内でご使用いただくと共に、考慮されるべ

き注意事項や条件について「東芝半導体製品の取り扱い上のご注意とお願い」、「半導体信頼性ハンドブック」など

でご確認ください。

· 本資料に掲載されている製品は、一般的電子機器 (コンピュータ、パーソナル機器、事務機器、計測機器、産業用

ロボット、家電機器など) に使用されることを意図しています。特別に高い品質・信頼性が要求され、その故障や

誤作動が直接人命を脅かしたり人体に危害を及ぼす恐れのある機器 (原子力制御機器、航空宇宙機器、輸送機器、

交通信号機器、燃焼制御、医療機器、各種安全装置など) にこれらの製品を使用すること (以下 “特定用途” とい

う) は意図もされていませんし、また保証もされていません。本資料に掲載されている製品を当該特定用途に使用

することは、お客様の責任でなされることとなります。

· 本資料に掲載されている製品は、外国為替および外国貿易法により、輸出または海外への提供が規制されている

ものです。

· 本資料に掲載されている技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社お

よび第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

· 本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

000629TBA

12

2001-09-20

Loading...

Loading...