TOSHIBA TC74HC597AP, TC74HC597AF Technical data

TC74HC597AP/AF

東芝CMOSデジタル集積回路 シリコン モノリシック

TC74HC597AP,TC74HC597AF

8-Bit Shift Register/Latch

TC74HC597 は、シリコンゲート CMOS 技術を用いた高速 CMOS

8 ビットシフトレジスタです。CMOS の特長である低い消費電力で、

LSTTL に匹敵する高速動作を実現できます。

回路は、パラレルロードの可能な 8 ビットデータレジスタと、デー

タレジスタに接続された 8 ビットのシリアルアウトシフトレジスタ

より構成されます。データの直並列変換に使用する場合、シフトレジ

スタの動作中に、ストレージレジスタに次のデータを保持させるこ

とが可能となります。A~H の 8 本のパラレル入力は、RCK の立ち上

がりで入力レジスタ内に保持されます。

ると入力レジスタのデータはシフトレジスタに蓄えられます。

SLOAD

はシフト動作を行います。

フトレジスタをリセットします。

オードによる保護回路が付加されています。

が “H” レベルのとき SCK の立ち上がりでシフトレジスタ

SCLR

また、すべての入力には静電破壊から素子を保護するために、ダイ

SLOAD

端子は、SCK には非同期に直接シ

を “L” レベルにす

特 長

TC74HC597AP

TC74HC597AF

• 高速動作 : f

• 低消費電流 : I

• 高雑音余裕度 : V

• 高ファンアウト : LSTTL 10 個を直接駆動可能

• 対称出力インピーダンス : |I

• バランスのとれた遅延時間 : t

• 広い動作電圧範囲 : V

• LSTTL (74LS597) と同一ピン接続、同一ファンクション

= 60 MHz (標準) (VCC = 5 V)

max

= 4 μA (最大) (Ta = 25°C)

CC

= V

NIH

| = IOL = 4 mA (最小)

OH

∼

−

pLH

(opr) = 2~6 V

CC

= 28% VCC (最小)

NIL

t

pHL

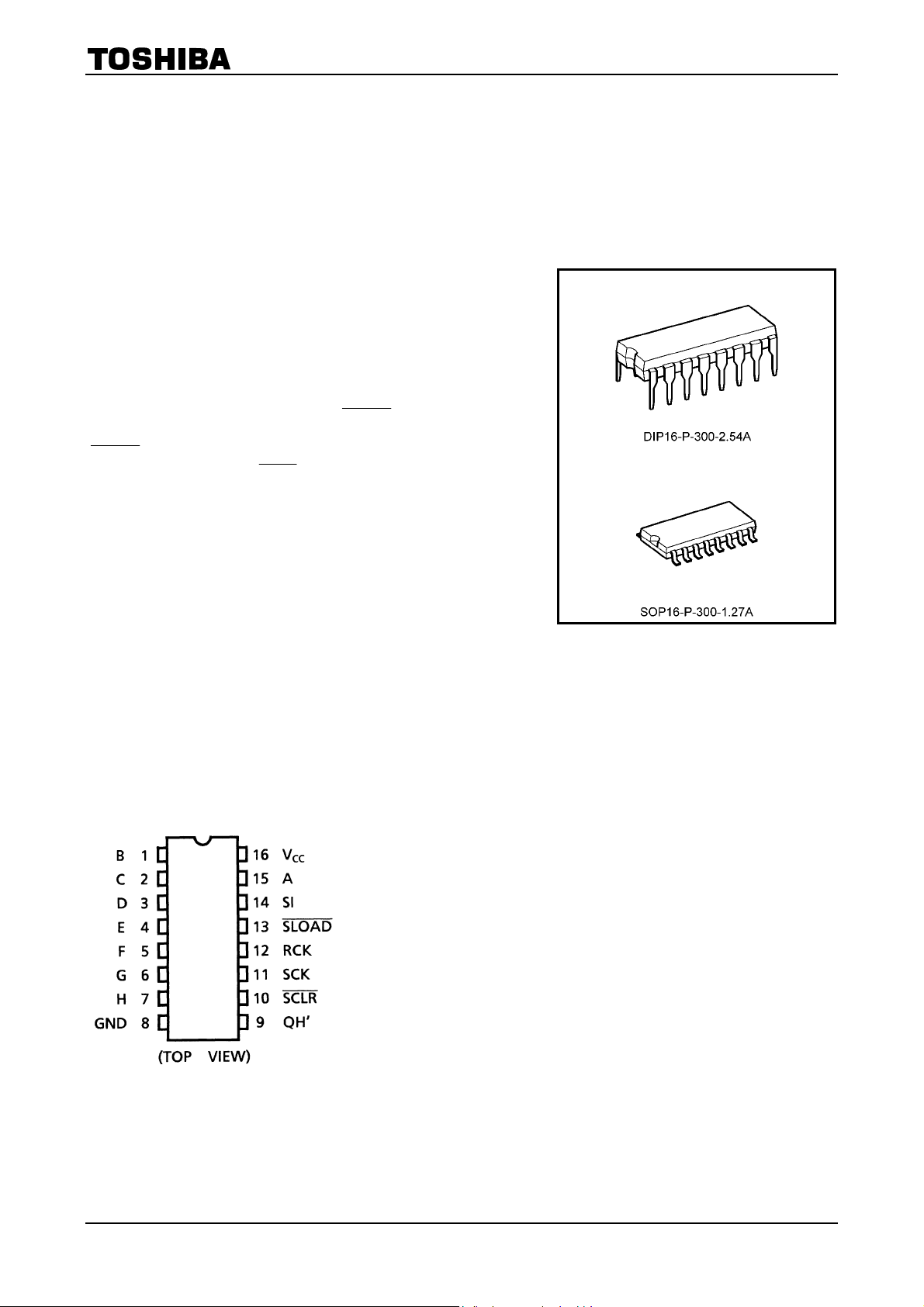

ピン接続図

質量

DIP16-P-300-2.54A : 1.00 g (標準)

SOP16-P-300-1.27A : 0.18 g (標準)

1

2007-10-01

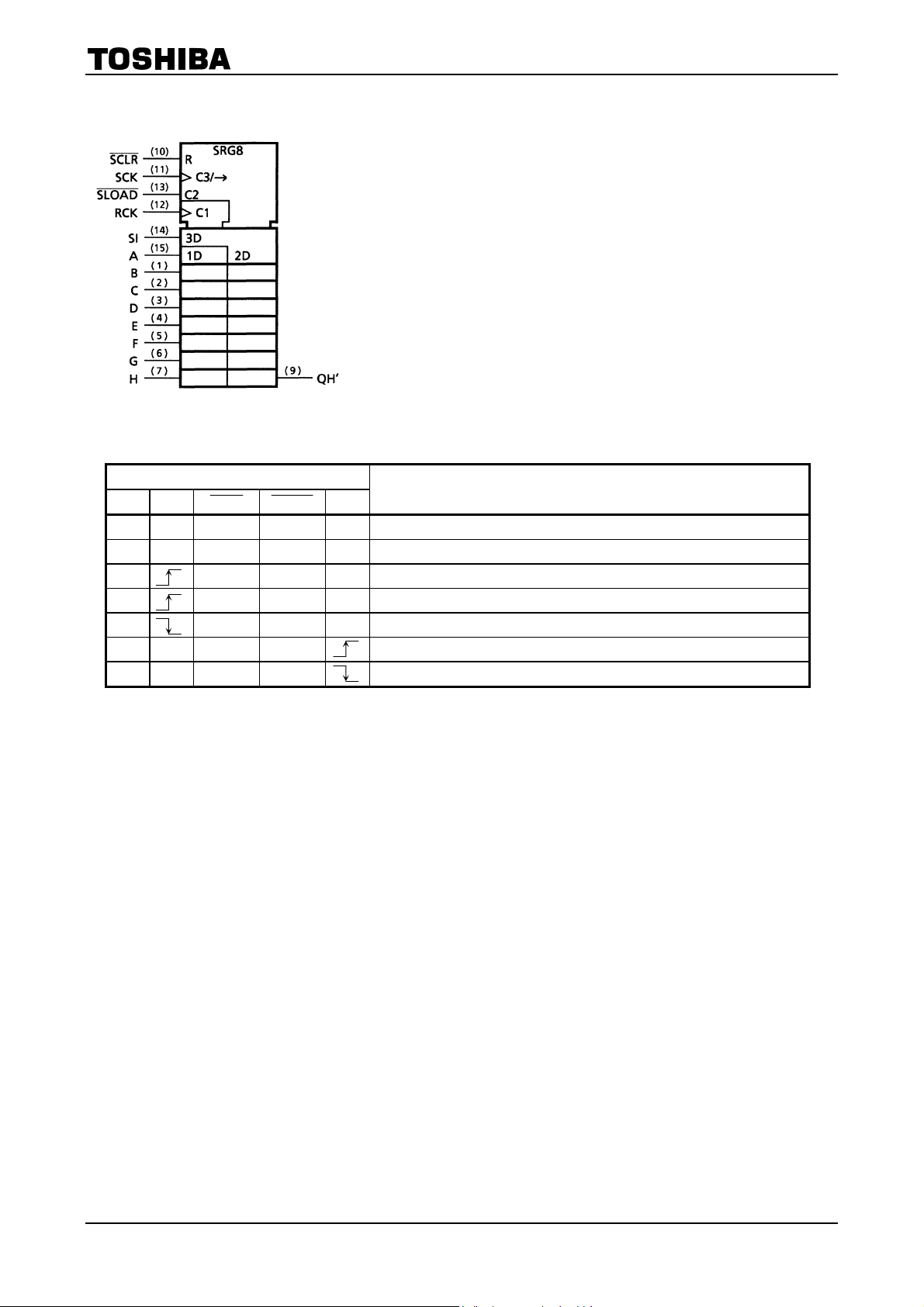

論理図

真理値表

TC74HC597AP/AF

Inputs

SI SCK SCLR SLOAD RCK

X X L H X シフトレジスタはクリアされる

X X H L X 入力レジスタのデータはシフトレジスタ内にストアされる。

L H H X シフトレジスタの初段の状態は “L” 他はおのおの前段のデータをストアする

H H H X シフトレジスタの初段の状態は “H” 他はおのおの前段のデータをストアする

X H H X シフトレジスタの状態は変化しない

X X X X A~H の 8 本の入力データは入力レジスタ内にストアされる

X X X X 入力レジスタの状態は変化しない

X: Don’t care

Function

2

2007-10-01

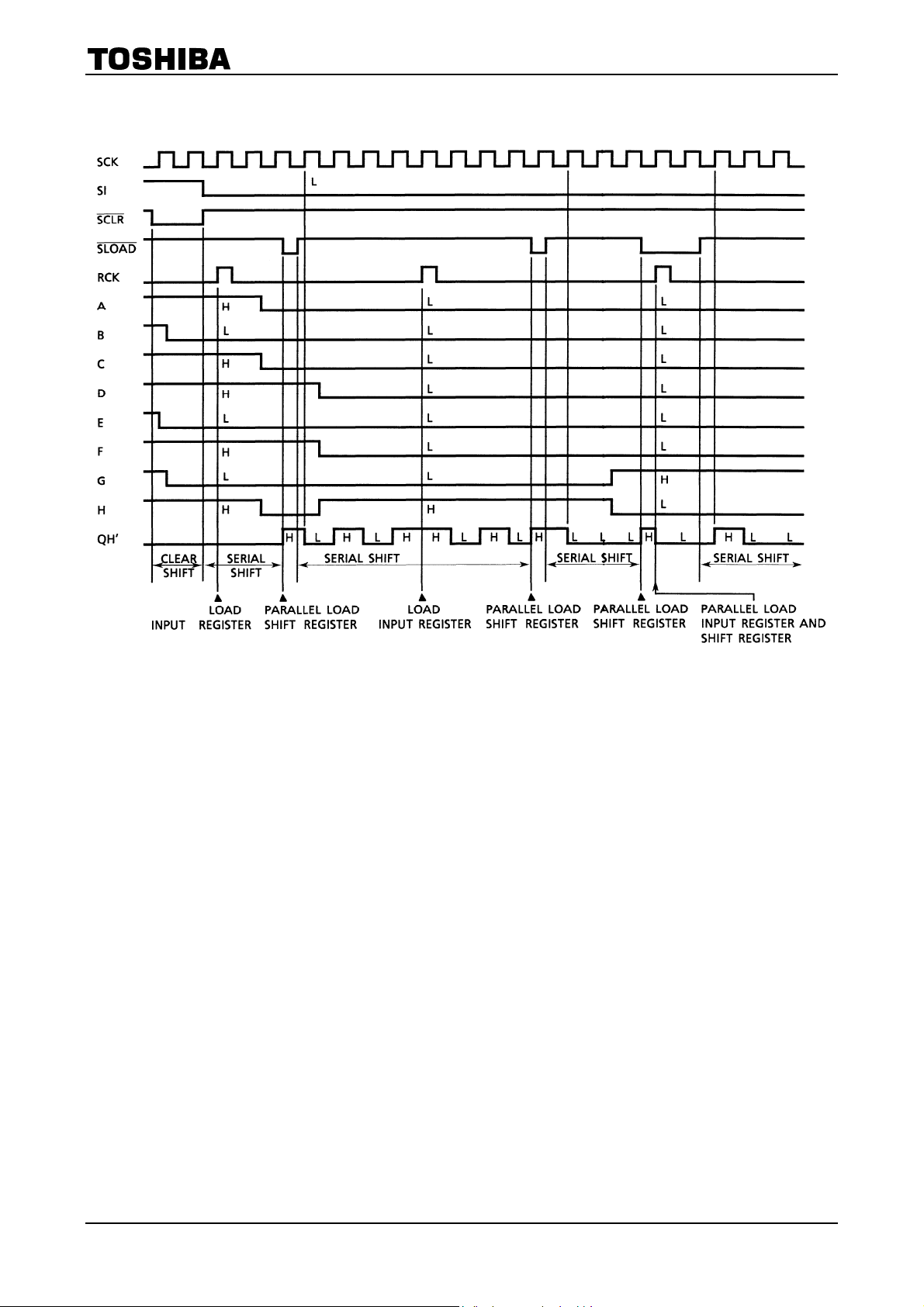

タイミング図

TC74HC597AP/AF

3

2007-10-01

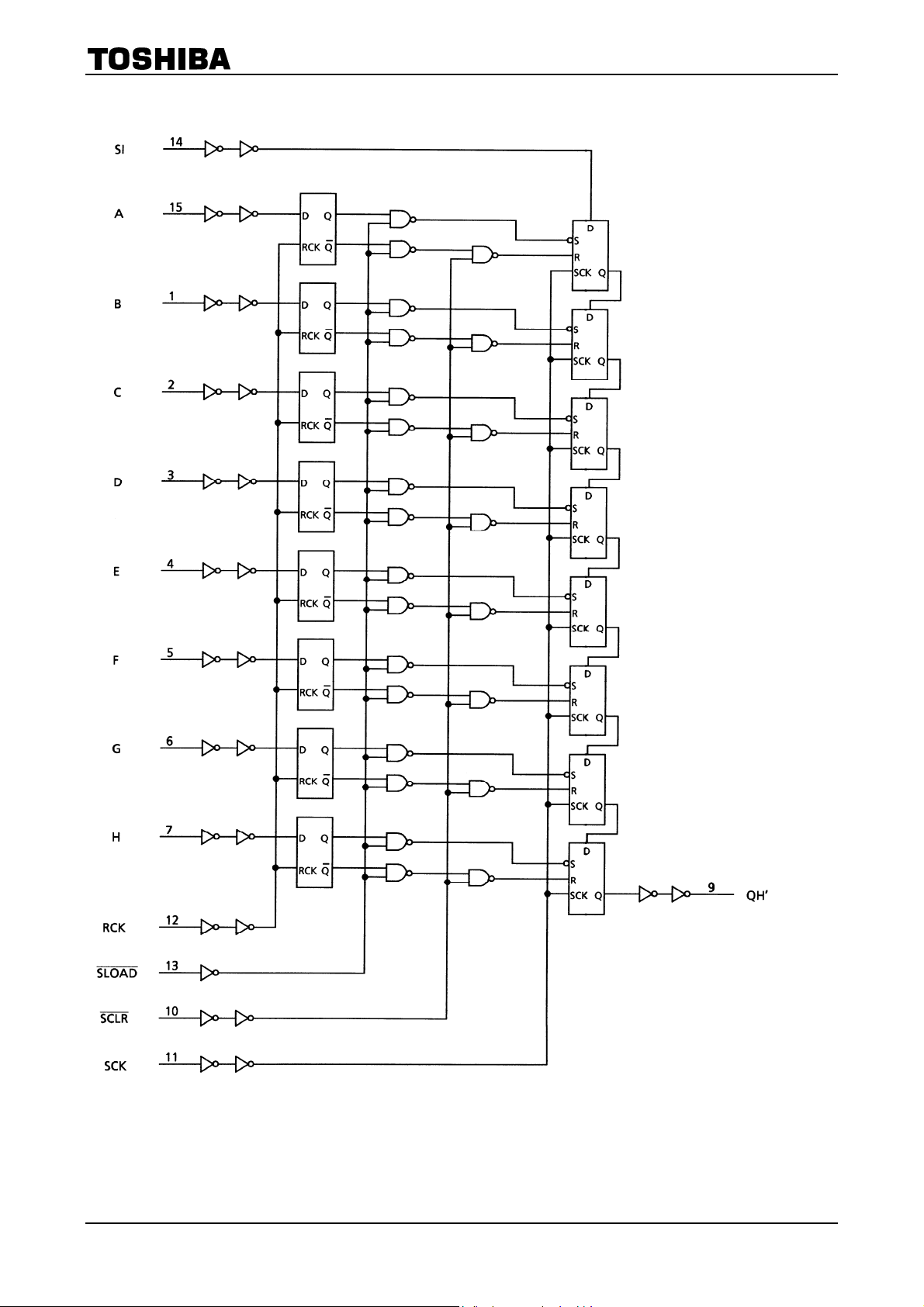

システム図

TC74HC597AP/AF

4

2007-10-01

Loading...

Loading...