TB62212FTAG

東芝 BiCD プロセス集積回路 シリコン モノリシック

TB62212FTAG

PWMチョッパ方式 デュアルステッピングモータドライバ

TB62212FTAGは、PWMチョッパ方式のデュアルステ

ッピングモータドライバです。

2つのステッピングモータドライバ部は、最大4つのブラシつき

DCモータを駆動でき、2組のHスイッチを組み合わせる事により、

DualDCモータ、もしくは、シングルステッピングモータを

駆動することができます。

特 長

・バイポーラ型ステッピングモータを 1 チップにて、駆動コントロ

ール可能。

・BiCD プロセスによる、モノリシック IC です

・低On抵抗R

ラージモードでは重ねあわせにより R

・内部回路用 VCC レギュレータ内蔵のため、外部からの LOGIC 電源(5V)が不要な単一電源対応です

・パッケージ :裏面ヒートシンク付きクワッド・リードレス・パッケージ ( QFN48-P-0707-0.50 : ピンピッチ 0.5mm )

・出力耐圧 : 40 V (max)

・出力電流 : 2.0A (max):DC_S 時、1.5A(MAX):Stepper_S 時

・チョッピング周波数は外部コンデンサにて設定可能です。

100 kHz 以上での、高速チョッピングも可能です。

・過熱検出回路(TSD)、過電流検出回路(ISD)、パワーオンリセット回路(POR)を内蔵しています

(注):本製品はサージ耐量の低い端子がありますので、製品取り扱いにはご注意願います。

= 2.2 Ω (出力部上下 Pch + Nch の和:Tj = 25ºC @0.6 A: typ.) を実現

on

=1.1 Ω (上下 Pch + Nch の和:Tj=25ºC@0.6A:typ.)として組み合わせ可能

on

ESD 試験 弱い端子 耐量値 条件

HBM 4,6,8,10,27,29,31,33 -1.2kV 19 ピン(VM)基準

QFN48-P-0707-0.50

質 量 : 0.14 (g) (標準)

1

2010-07-09

TB62212FTAG

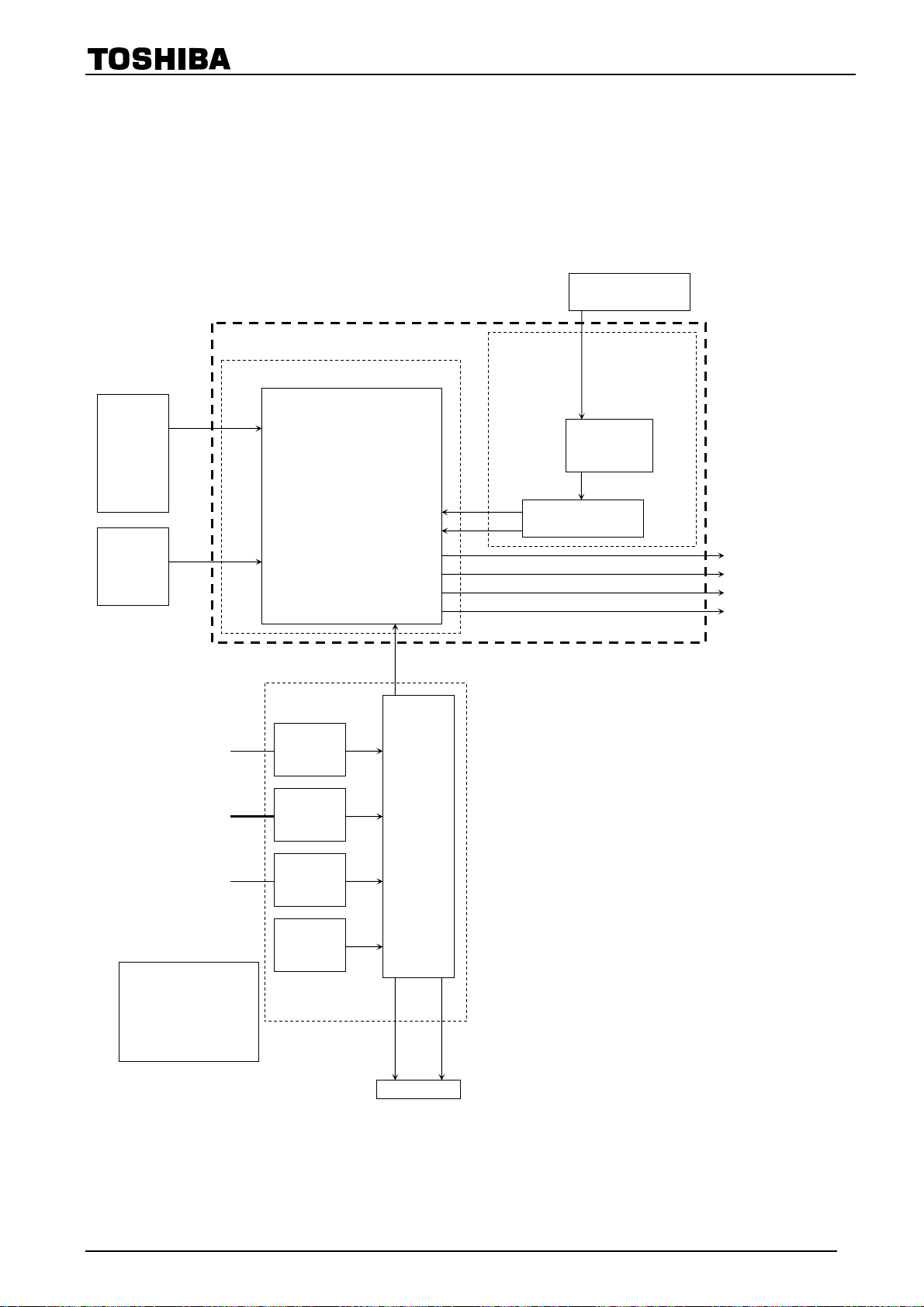

ブロック図/端子配置図(ブラシ付

ENABLE_B

ENABLE_B

ENABLE_A

ENABLE_A

Rs_D

注:GND配線:GNDとヒートシンク部分はベタ接続とし、基板から取り出し部は 1 点接地になるよう

お願いするとともに、放熱設計を考慮したパターンになるように設計してください。

各モードなどの設定端子を SW で制御する場合、Hi-z にならないように VCC 等の電源にプルアップもしくは GND

にプルダウンしていただけますようお願いいたします。

出力間のショートおよび出力の天絡、地絡時に IC の破壊の恐れがありますので、出力ライン、VM ライン、GND

ラインの設計は十分注意してください。

このICにおいては、特に大電流が流れる電源系の端子 (VM、RS、OUT、GND など) が正常に

配線されていない場合、破壊も含む不具合が生ずる可能性があります。

また、ロジックの入力端子についても正常に配線が行われていない場合、異常動作がおこり IC が破壊すること

があります。この場合、規定以上の大電流が流れるなどによって IC が破壊する可能性もあります。

IC のパターンの設計や実装については十分ご注意願います。

Rs_D

Rs_D

Rs_D

OSCM

OSCM

Vcc

Vcc

Rs_A

Rs_A

Rs_A

Rs_A

PHASE_A

PHASE_A

PHASE_B

PHASE_B

NC

NC

NC

NC

36 35 34 33 32 31 30 29 28 27 26 25

36 35 34 33 32 31 30 29 28 27 26 25

36 35 34 33 32 31 30 29 28 27 26 25

37

37

37

38

38

38

39

39

39

40

40

40

41

41

41

42

42

42

43

43

43

44

44

44

45

45

45

46

46

46

47

47

47

48

48

48

1 2

1 2

1 2

Reg

Reg

NC

NC

NC

NC

ENABLE_C

ENABLE_C

ENABLE_D

ENABLE_D

コンパレータ

コンパレータ

コンパレータ

コンパレータ

3 4 5 6

3 4 5 6

3 4 5 6

PHASE_C

PHASE_C

PHASE_D

PHASE_D

モータ

DC

OUT_D-

OUT_D-

OUT_A-

OUT_A-

(S)×4

GND

GND

プリ ドライバ

プリ ドライバプリ ドライバ

プリ ドライバ プリ ドライバ

プリ ドライバプリ ドライバ プリ ドライバ

GND

GND

軸モード使用時の場合)

OUT_C+

GND

OUT_D+

OUT_D+

TSD

TSD

コントロール

コントロール

7

7

7

OUT_A+

OUT_A+

OUT_C+

GND

プリ ドライバ

プリ ドライバ

ISDISD

ISDISD

ISDISD

ISDISD

8

8

8

GND

GND

OUT_B+

OUT_B+

GND

GND

コンパレータ

コンパレータ

コンパレータ

コンパレータ

10 11 12

10 11 12

10 11 12

9

9

9

GND

GND

OUT_C-

OUT_C-

Mode(2,1,0)

Mode(2,1,0)

OUT_B-

OUT_B-

Mode 1

Mode 0

Mode 1

Mode 0

(H,H,H)=stepper_S×2

(H,H,H)=stepper_S×2

(H,H,L)=DC_L×2

(H,H,L)=DC_L×2

(H,L,H)=stepper_L

(H,L,H)=stepper_L

(H,L,L)=DC_S×4

(H,L,L)=DC_S×4

(L,H,H)=DC_L+stepper_s

(L,H,H)=DC_L+stepper_s

(L,H,L)=D C_S×2+stepper_s

(L,H,L)=D C_S×2+stepper_s

3

3

Vref_A

Vref_A

Vref_B

Vref_B

24

24

24

Mode 2

Mode 2

23

23

23

デジタル TBlank_CD

デジタル TBlank_CD

22

22

22

デジタル TBlank_AB

デジタル TBlank_AB

21

21

21

Rs_C

Rs_C

20

20

20

Rs_C

Rs_C

19

19

19

VM

VM

18

18

18

ロジック GND

ロジック GND

17

17

17

Rs_B

Rs_B

16

16

16

Rs_B

Rs_B

15

15

15

Vref_D

Vref_D

14

14

14

Vref_C

Vref_C

13

13

13

NC

NC

2

2010-07-09

ピン配置

TB62212FTAG

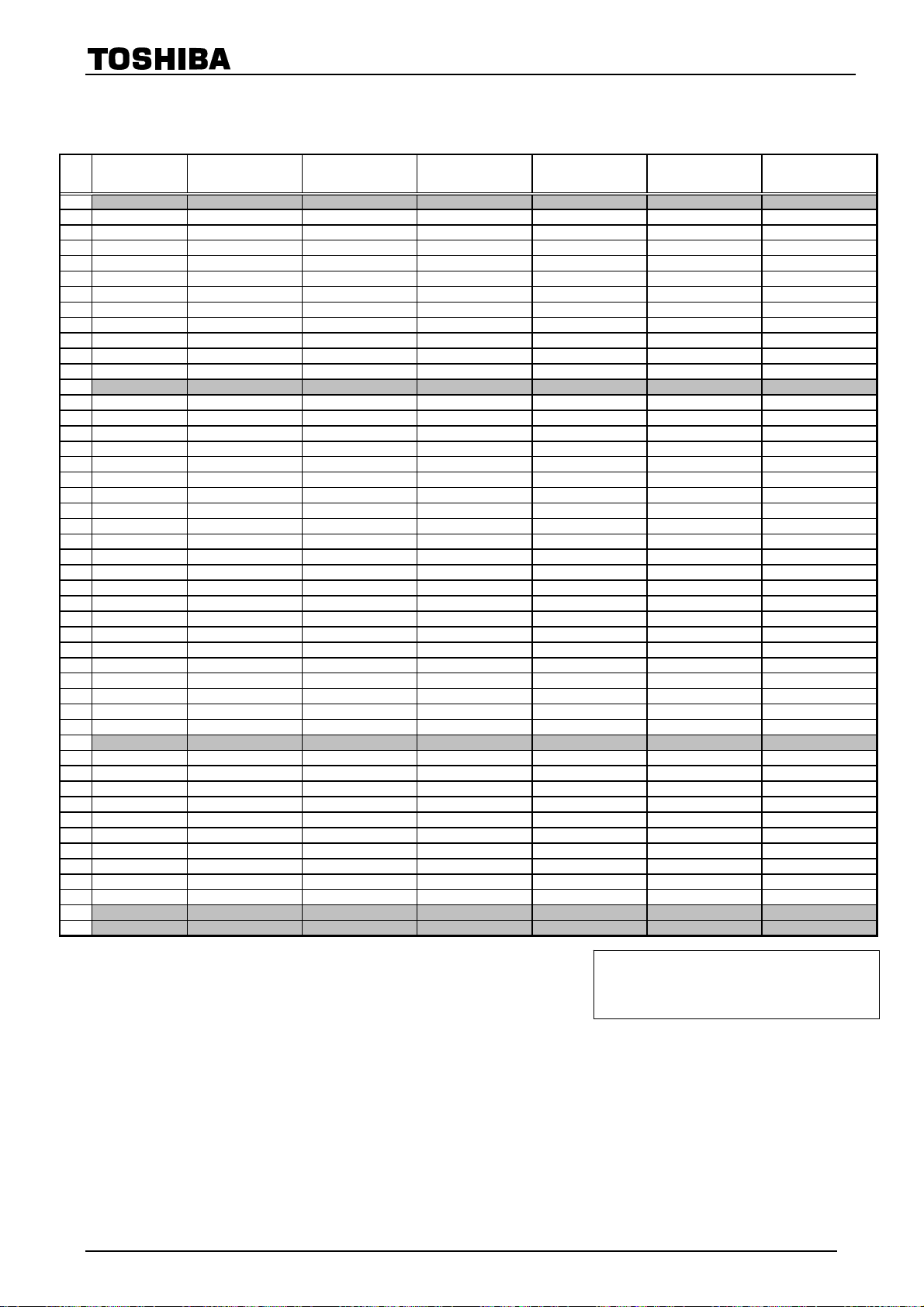

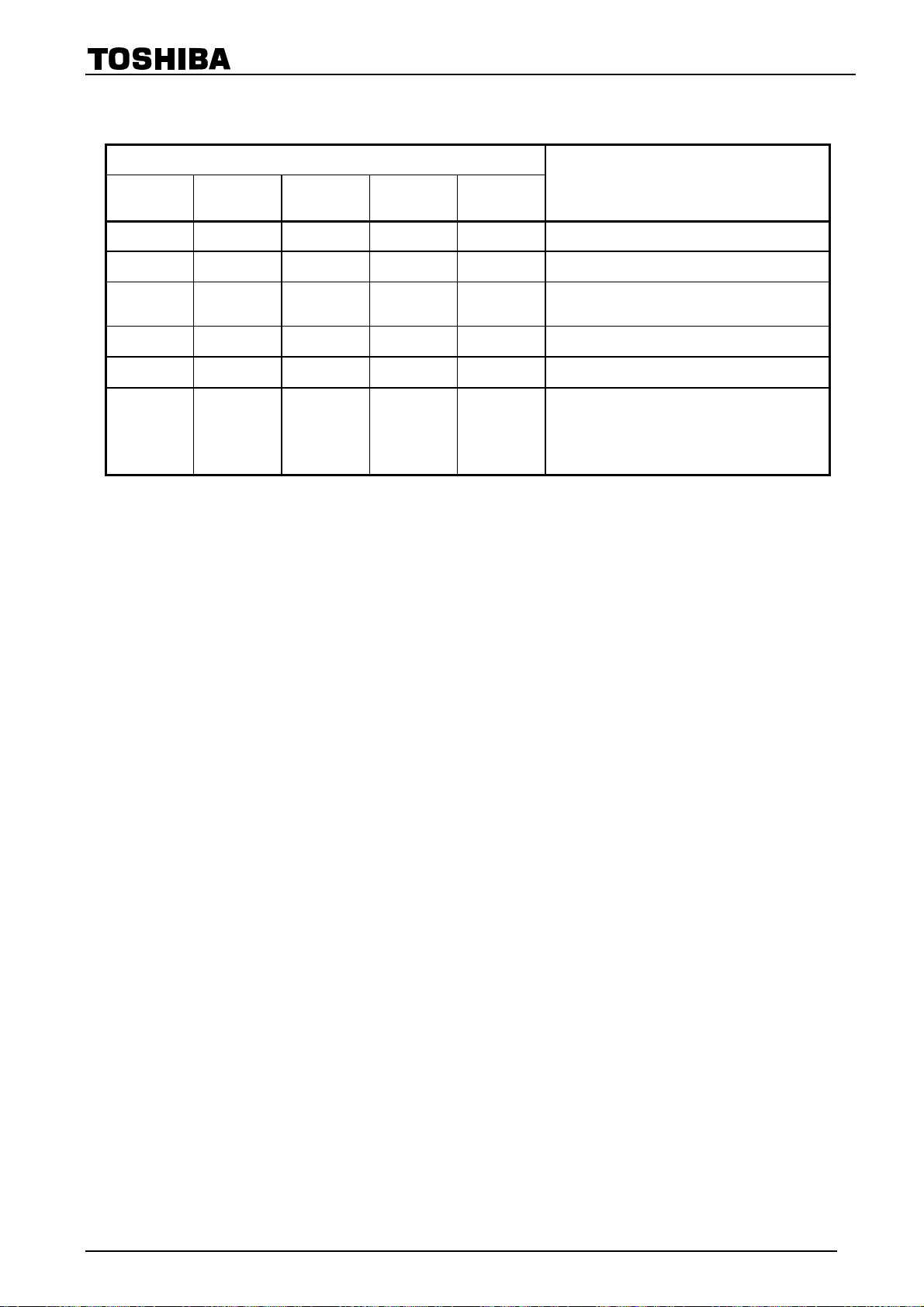

端子 端子名 ① Stepping(S)×2 ② DC(L)×2 ③ Stepping(L) ④ DC(S)×4 ⑤ DC(L)+Stepping(S) ⑥

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

デジタルTBlank_AB

22

デジタルTBlank_CD

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

NC

PHASE_C

PHASE_D

OUT_A-

GND

OUT_A+

GND

OUT_B+

GND

OUT_BVref_A

Vref_B

NC

Vref_C

Vref_D

Rs_B

Rs_ B

GND

VM

Rs_C

Rs_C

MODE 2

MODE 1

MODE 0

OUT_C-

GND

OUT_C+

GND

OUT_D+

GND

OUT_D-

ENABLE_D

ENABLE_C

NC

ENABLE_B

ENABLE_A

Rs_D

Rs_D

OSCM

VCC

Rs_A

Rs_A

PHASE_A

PHASE_B

NC

NC

NC NC NC NC

C軸Phase入力 CD軸IN1入力 CD軸Phase入力 C軸IN1入力 C軸Phase入力

D軸Phase入力

モータA-出力

GND A

モータA+出力

GND

モータB+出力

GND B

モータB-出力

A軸Vref

B軸Vref

NC

C軸Vref

D軸Vref

B軸電源端子

B軸電源端子

ロジックGND

VM基準モニタ

C軸電源端子

C軸電源端子

-

-

Hに設定

Hに設定

Hに設定

モータC-出力

GND C

モータC+出力

GND

モータD+出力

GND D

モータD-出力

D軸イネーブル入力

C軸イネーブル入力

NC

B軸イネーブル入力

A軸イネーブル入力

D軸電源端子

D軸電源端子

OSCM

レギュレータモニタ

A軸電源端子

A軸電源端子

A軸Phase入力

B軸Phase入力

NC

NC

CD軸PWM

モータAB-出力

GND A

モータAB+出力

GND

ータAB+出力

モ

GND B

モータAB-出力

AB軸Vref

-

NC

--

AB軸電源端子 AB軸電源端子

AB軸電源端子

ロジックGND ロジックGND

VM基準モニタ VM基準モニタ

C軸電源端子

C軸電源端子 C軸電源端子

TBlank幅設定(注) -

TBlank幅設定(注)

Hに設定 Hに設定

Lに設定 Hに設定

モータCD-出力 モータCD-出力

GND C GND C

モータCD+出力 モータCD+出力

GND GND

モータCD+出力 モータCD+出力

モータCD-出力

-

CD軸IN2入力

NC

AB軸IN2入力

CD軸電源端子

CD軸電源端子 CD軸電源端子

レギュレータモニタ

軸電源端子

A

A軸電源端子

AB軸IN1入力

AB軸PWM

NC

NC

-

モータAB-出力

GND A

モータAB+出力

GND

モータAB+出力

GND B

モータAB-出力

AB軸Vref

-

NC

AB軸電源端子

C軸電源端子

-

Lに設定Hに設定

GND DGND D

モータCD-出力

-

CD軸イネーブル入力

NC

--

AB軸イネーブル入力

CD軸電源端子

OSCMOSCM

レギュレータモニタ

A軸電源端子

A軸電源端子

AB軸Phase入力

-

NC

NC

D軸IN1入力

モータA-出力

GND A

モータA+出力

GND

モータB+出力

GND B

モータB-出力

A軸Vref

B軸Vref

NC

C軸VrefCD軸VrefCD軸Vref

D軸Vref

B軸電源端子

B軸電源端子

ロジックGND

VM基準モニタ

C軸電源端子

C軸電源端子

TBlank幅設定(注)

TBlank幅設定(注)

Hに設定

Lに設定

Lに設定

モータC-出力

GND C

モータC+出力

GND

モータD+出力

GND D

モータD-出力

D軸IN2入力

C軸IN2入力

NC

B軸IN2入力

A軸IN2入力

D軸電源端子

D軸電源端子

OSCM

レギュレータモニタ

A軸電源端子

A軸電源端子

A軸IN1入力

B軸IN1入力

NC

NC

NC NC

D軸Phase入力

モータAB-出力

GND A

モータAB+出力

GND

モータAB+出力

GND B

モータAB-出力

AB軸Vref

-

NC

C軸Vref

D軸Vref

B軸電源端子

B軸電源端子

ロジックGND

VM基準モニタ

C軸電源端子

C軸電源端子

TBlank幅設定(注)

-

Lに設定

Hに設定

Hに設定

モータC-出力

GND C

モータC+出力

GND

モータD+出力

GND D

モータD-出力

D軸イネーブル入力

C軸イネーブル入力

NC

-

AB軸IN2入力

D軸電源端子

D軸電源端子

OSCM

レギュレータモニタ

A軸電源端子

A軸電源端子

ABIN1入力

AB軸PWM

NC

NC

DC(S)×2

+

Stepping(S)

C軸Phase入力

D軸Phase入力

モータA-出力

GND A

モータA+出力

GND

モータB+出力

GND B

モータB-出力

A軸Vref

B軸Vref

NC

C軸Vref

D軸Vref

B軸電源端子

B軸電源端子

ロジックGND

VM基準モニタ

C軸電源端子

C軸電源端子

TBlank幅設定(注)

Lに設定

Hに設定

Lに設定

モータC-出力

GND C

モータC+出力

GND

モータD+出力

GND D

モータD-出力

D軸イネーブル入力

C軸イネーブル入力

NC

B軸IN2入力

A軸IN2入力

D軸電源端子

D軸電源端子

OSCM

レギュレータモニタ

A軸電源端子

A軸電源端子

A軸IN1入力

B軸IN1入力

NC

NC

(注)

L に設定 TBlank無し

H に設定 TBlank幅:OSCM×3

3

2010-07-09

TB62212FTAG

■モータ駆動モード説明

①Stepping(S)× 2軸モード時の端子名及び端子機能 Mode(2,1,0)=(H,H,H)

②DC(L)×2軸モード時の端子名及び端子機能 Mode(2,1,0)=(H,H,L)

③Stepping(L)× 1軸モード時の端子名及び端子機能 Mode(2,1,0)=(H,L,H)

④DC(S)×4 軸モード時の端子名及び端子機能 Mode(2,1,0)=(H,L,L)

⑤DC(L)×1軸+Stepping(S)×1 軸モード時の端子名及び端子機能 Mode(2,1,0)=(L,H,H)

⑥DC(S)×2軸モード+Stepping(S)×1軸モード時の端子名及び端子機能 Mode(2,1,0)=(L,H,L)

※DC(S)を含むモードでは、A 軸と B 軸とのペア、C 軸と D 軸とのペアで1つの D_TBLANK 設定となります。

DC(S)×4では、外部ショートブレーキモードを使用できません。IN1・IN2 の組み合わせでショートブレーキ

動作してください。

モータモード(2,1,0)=(L,L,H)は弊社テストに使うモードです。このモードにはしないでください。

(注1)ステッピングモータのラージモード、DC モータのラージモードなど、重ねあわせのモードを使用する時は、

IC外部でのインピーダンスに差がないようにして下さい。

(注2)ラージモードで使用する場合に端子をショート使用する出力トランジスタへの配線インピーダンス

が崩れた場合、流れる電流が 2 つのトランジスタにて、アンバランスになり絶対最大定格以上の電流が

流れると該当トランジスタが破壊することが考えられます。

4

2010-07-09

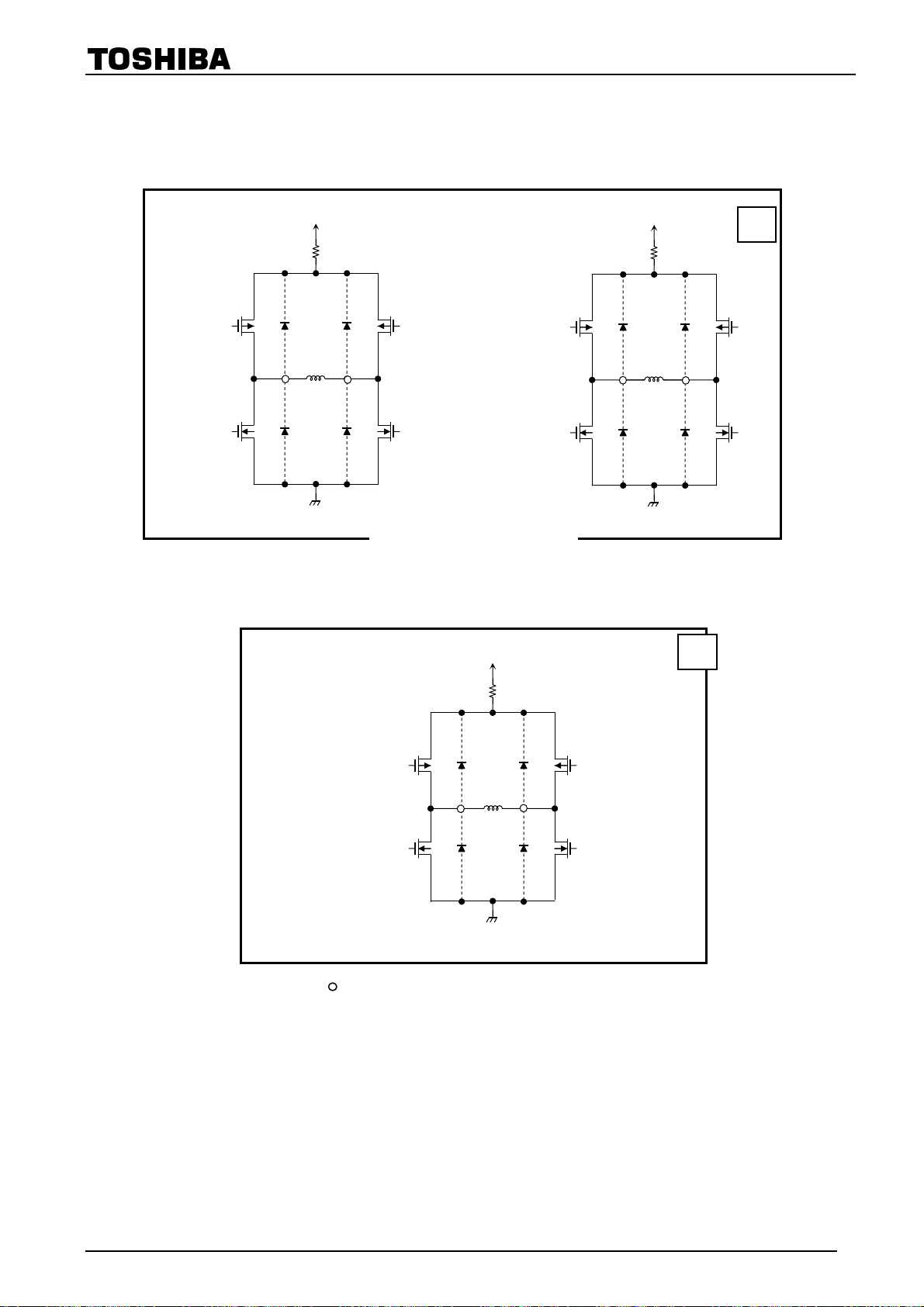

■各モータ駆動における H ブリッジの組み合わせ例(接続方法)

●Stepping Motor(S) の組み合わせ

V

A軸 B軸

M

R

RS

R

端子

S

TB62212FTAG

V

M

R

RS

R

端子

S

例

●DC Motor(S)の組み合わせ

負荷

A軸

OUT_SA-OUT_SA+

GND

Stepping Motor(S)1軸駆動

R

RS

RS端子

OUT_SA+

負荷

VM

OUT_SB-OUT_SB+

負荷

GND

例

OUT_SA-

GND

DC(S)1 軸駆動

…白丸は IC のモータ出力端子を示します

5

2010-07-09

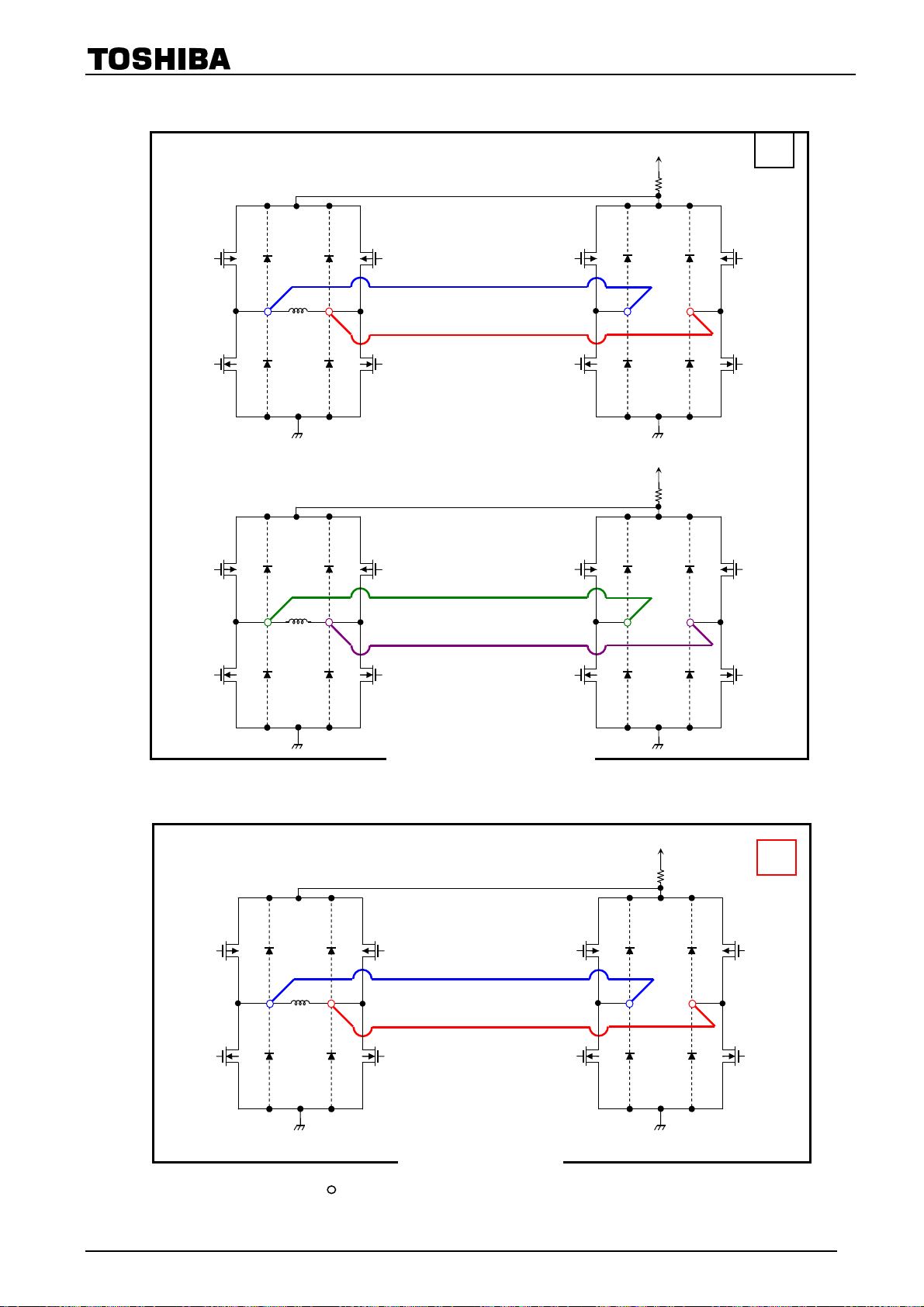

●Stepping Motor(L) の組み合わせ

A軸

OUT_LAB+

(OUT_SA+)

C軸

OUT_LCD+

(OUT_SC+)

R

端子

S

負荷

R

端子

S

負荷

GND

GND

●DC Motor(L)の組み合わせ

A軸

OUT_LAB+

(OUT_SA+)

R

端子

S

負荷

OUT_LAB(OUT_SA-)

OUT_LCD(OUT_SC-)

Stepping Motor(L)1軸駆動

OUT_LAB(OUT_SA-)

OUT_LAB+

(OUT_SB+)

OUT_LCD+

(OUT_SD+)

OUT_LAB+

(OUT_SB+)

B軸

D軸

B軸

TB62212FTAG

V

M

R

RS

R

端子

S

GND

V

M

R

RS

R

端子

S

GND

V

M

R

RS

R

端子

S

例

OUT_LAB(OUT_SB-)

OUT_LCD(OUT_SD-)

例

OUT_LAB(OUT_SB-)

GND

DC Motor(L)1軸駆動

…白丸は IC のモータ出力端子を示します

6

GND

2010-07-09

出力制御回路電流値帰還回路、電流値設定回路

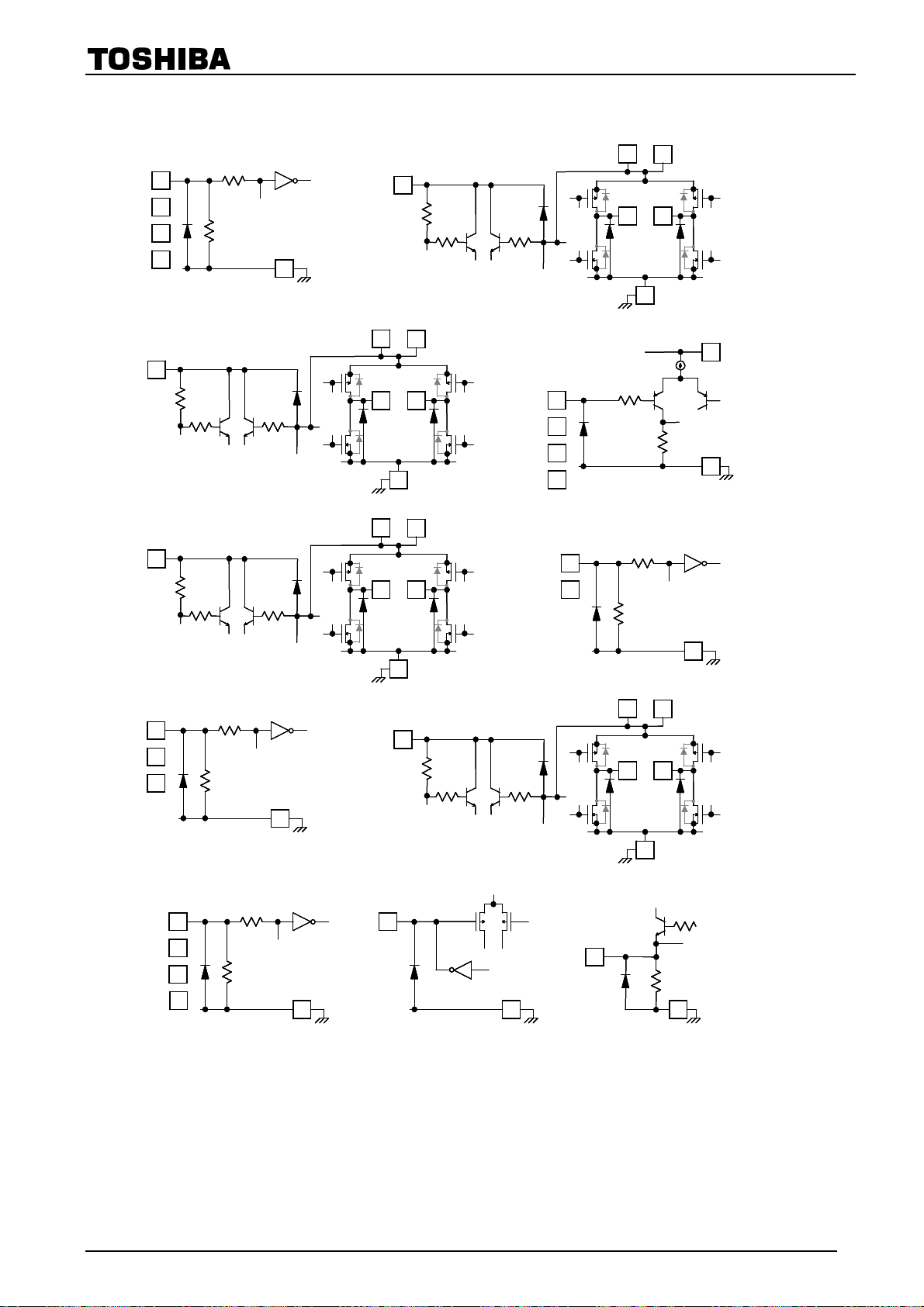

注: Logic 入力 Pin は、IC 内部で約 100 kΩ の抵抗でプルダウンしています。

ただし、これらの端子の機能を使用しない場合は、必ず GND に接続してください。

誤動作の可能性があります。

TB62212FTAG

チョッピング基準

作成回路

電流

帰還

回路

電流

設定

回路

出力回路

VM

VCC

出力制御回路

NF 設定電流

到達信号

出力停止信号

出力制御回路

チャージスタート

ISD

回路

VMR

回路

VCCR

回路

Phase

Mixed

Decay

Timing

U1

U2

L1

L2

出力 Stop 信号

停止

信号

選択

回路

Decay

Mode

Mixed

Decay

Timing

回路

OSC_M

カウンタ

OSC セレクタ

出力回路

VCCR:VCC 電源監視

VMR

:VM 電源監視

ISD : 過電流検出回路

TSD : 過温度検出回路

TSD

回路

検出回路

検出回路

ラッチクリア

信号

Logic

7

2010-07-09

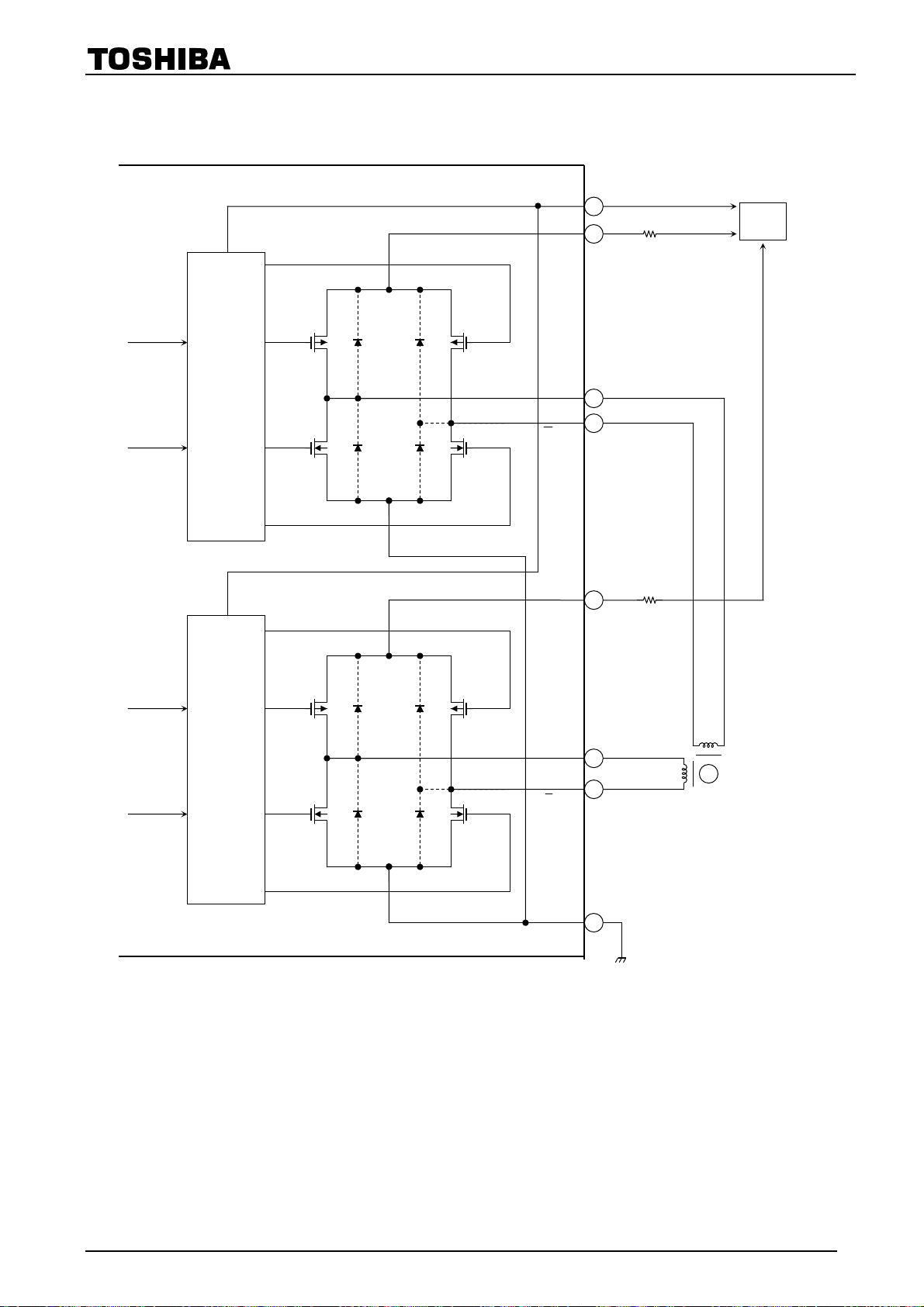

出力等価回路 A/B (C/D は A/B と同様)

出力上側

ドライブ

電源

U1

L1

出力制御

回路より

(UGATE)

U1

U2

L1

L2

出力

駆動

回路

A 相

L2

U2

RSA

A 出力

A

出力

TB62212FTAG

VM

VM へ

RRSA

出力制御

回路より

出力上側

ドライブ

電源

(UGATE)

U1

U2

L1

L2

出力

駆動

回路

B 相

U1

L1

L2

U2

RSB

B 出力

B 出力

RRSB

M

GND

8

2010-07-09

入力等価回路

PHASE

PHASE

PHASE

2

2

2

3

3

3

45

45

45

46

46

46

VM

VM

VM

19

19

19

8kΩ

8kΩ

8kΩ

150Ω

150Ω

150Ω

100kΩ

100kΩ

100kΩ

TB62212FTAG

Rs_A

Rs_A

Rs_A

43

43

43

44

44

44

VM

VM

VM

19

19

19

3kΩ3kΩ

3kΩ3kΩ

8kΩ

8kΩ

8kΩ

18

18

18

Rs_B

Rs_B

Rs_B

16

16

16

17

17

17

OUT_B+

OUT_B+

OUT_B+

8 10

8 10

3kΩ3kΩ

3kΩ3kΩ

3kΩ3kΩ

8 10

OUT_B-

OUT_B-

OUT_B-

GND

GND

GND

9

9

9

3kΩ3kΩ

Vref

Vref

Vref

11

11

11

12

12

12

14

14

14

15

15

15

OUT_A-

OUT_A-

OUT_A-

4 6

4 6

4 6

1kΩ

1kΩ

1kΩ

OUT_A+

OUT_A+

OUT_A+

GND

GND

GND

5

5

5

Vcc

Vcc

Vcc

42

42

42

18

18

18

19

19

19

Mode

Mode

Mode

24

24

24

25

25

25

26

26

26

VM

VM

VM

8kΩ

8kΩ

8kΩ

ENABLE

ENABLE

ENABLE

34

34

34

35

35

35

37

37

37

38

38

38

150Ω

150Ω

150Ω

100kΩ

100kΩ

100kΩ

150Ω

150Ω

150Ω

100kΩ

100kΩ

100kΩ

20

20

20

Rs_C

Rs_C

Rs_C

3kΩ3kΩ

3kΩ3kΩ

3kΩ3kΩ

18

18

18

18

18

18

OUT_C-

OUT_C-

OUT_C-

27 28

27 28

27 28

OUT_C+

OUT_C+

OUT_C+

28

28

28

19

19

19

OSCM

OSCM

OSCM

41

41

41

21

21

21

GND

GND

GND

8kΩ

8kΩ

8kΩ

VM

VM

VM

18

18

18

゙タル

゙タル

゙タル

デシ

TBlank

デシ

TBlank

デシ

TBlank

22

22

22

23

23

23

Rs_D

Rs_D

Rs_D

3kΩ3kΩ

3kΩ3kΩ

3kΩ3kΩ

Vcc

Vcc

Vcc

42

42

42

150Ω

150Ω

150Ω

100kΩ

100kΩ

100kΩ

39

39

39

OUT_D+

OUT_D+

OUT_D+

31 33

31 33

31 33

OUT_D-

OUT_D-

OUT_D-

32

32

32

40

40

40

GND

GND

GND

18

18

18

18

18

18

9

2010-07-09

1 . 入力信号系のファンクション(Stepping Motor Mode 時)

入力

TSD/ISD の

動作(注 2)

PHASE ENABLE M_MODE

H H STEP H L 出力+側が H,出力-側が L

L H STEP H L 出力-側が H,出力+側が L

VCCR(注 1)

Or VMR

TB62212FTAG

結 果

H L STEP H L

H H STEP H L 通常動作を継続します。

H H - L L スタンバイモードになります。

H H - H H

注 1:VCCR と VMR について

VCCR と VMR が動作しない領域 (typ.で 3 V) 以上を H、それ未満を L としています。

VCCR と VMR の関係はどちらかが動作すれば停止状態になります。(OR の関係です。)

注 2:過熱検出回路(TSD)/ 過電流検出回路(ISD)が動作している状態をを H と記載しています。

TSD と ISD の関係は、いずれかが動作すればシャットダウン状態・スタンバイ状態になります。

(TSD と ISD の動作は、OR の関係です。)

注 3:過熱検出回路(TSD)/ 過電流検出回路(ISD)のファンクションについて

過熱検出回路(TSD)/ 過電流検出回路(ISD)が動作後、再度 POR が解除されるまで、検出回路

は動作したままになり、IC は動作を停止します。

ENABLE=L を入力した相の出力電流を

OFF します。

TSD/ISD が動作すると

スタンバイモードになります。

電源の再投入までその状態を継続します

10

2010-07-09

TB62212FTAG

1.PHASE のファンクション (Stepping Motor Mode 時)

ステッピングモータを駆動する時に、電流のポラリティを決定します。2 相励磁の駆動時は

A相および、B相のこの端子をシーケンシャルに変更することによってモータを回転させることができます。

入力 ファンクション

H 正極 (例 A: H, A : L)

L 負極 (例 A: L, A : H)

2.ENABLE のファンクション (Stepping Motor Mode 時)

ステッピングモータを駆動する場合に、その相に電流を流すか流さないかを指定します。

モータを OFF モードで停止させる場合や、1-2 相励磁モードでモータを駆動する場合は、この端子を制御することに

よって動作を行います。

電源の立ち上げや立ち下げの時は、誤動作をさけるため、この端子を必ず L に固定してください。

入力 ファンクション

H 該当チャンネルの出力動作(ON)

L 該当チャンネルの出力 OFF

3.Motor Mode Selectのファンクション

駆動するモータの種類をセレクトする機能です。

H スイッチの構成と、制御カテゴリの変更を行います

基本的には、モータのモードを駆動中に変更することはあり得ないため、動的なモードの変更に対しては対応

していません。

この端子の設定を変更した場合、制御端子に対するファンクションとタイミングが変更されます。

モータセレクト端子の組み合わせは、電源投入後は変更しないでください。

Mode 2 Mode 1 Mode 0 モータ駆動モード

H H H Stepping S×2

H H L DC_L(重ねあわせ)×2

H L H Stepping L(重ねあわせ)×1

H L L DC_S×4

L H H DC_L(重ねあわせ)×1+Stepper S

L H L DC_S×2+Stepper S

L L H 使 用 禁 止 (弊社テスト用)

L L L スタンバイモード

11

2010-07-09

TB62212FTAG

● ステッピングモータMODE

ステッピングモータを駆動するのに有効なモードです。

tBLANK は、アナログの固定値(約 300ns)になります。

制御は、1 モータあたり、「PHASE(電流方向)」+「ENABLE(ON・OFF)」の 2 線による Logic 制御

および、Vref 入力による定電流値制御になります。

● ブラシ付きDCモータMODE

ブラシ付きDCモータを駆動するのに有効なモードです。

tBLANK は、アナログの固定値もしくは、チョッピング基準の OSC 周波数を元に、その 3CLK 分を不感帯と

するデジタル tBLANK モードを切り替える事ができます。

デジタル tBLANK は、DC モータを PWM 制御の際にバリスタ成分等によって発生する放電スパイク電流を、

定電流検出回路が検出してしまう事をさけるため、OSC 信号を基準に不感帯時間を設けます。

この機能を使うことによって、外部からの PWM 制御に加えて、定電流リミッタ制御が可能になりますが、

不感帯幅の時間だけ、電流が Over する現象が発生します。

● 重ねあわせモードについて

DC_L モード及び、Stepper_L モードでは、同特性の H スイッチを 2 ユニットパラレル動作させることに

よって実現するモードです。

このことによって、実質の Ron が 1/2 に減少し、電流能力もほぼ 2 倍にする事ができます。(実際には熱容量も含めて

Spec 化していますので、電気的特性部をご確認ください。)

このモードを使用する場合は、電源・GND、及び出力端子において、同一名称を持った端子同士を基板上で

ショートする必要が有ります。

この時、各端子へのインピーダンスが崩れると、片方の端子に電流が偏る可能性が有りますので、なるべく

インピーダンスバランスが平均化するように基板配線を行ってください。

4.D_TBLANK のファンクション (ブラシ付きDCモータMODEのみ)

D_TBLANK モータ駆動モード

L OFF:Digital Blanking Time = OSC×0

H ON:Digital Blanking Time = OSC×3

※ "L"の時は、アナログの tBLANK 幅のみとなります。

12

2010-07-09

TB62212FTAG

5.ブラシ付きDCモータモード時の信号制御ファンクション 1(DC_L×2 軸モード使用の場合)

Control 入力 出力段状態

IN1

(Phase 端子)

H H

L H

H L

L L

DC(S)×4などのショートブレーキ端子を使わないモードの場合では、上記「PWM」は=H 固定相当となります。

IN2

(Enable 端子)

PWM

(Short Brake)

H

L

H L H 正転/逆転

L L L ショートブレーキ

H H L 逆転/正転

L L L ショートブレーキ

H

L

OUT1 OUT2 モード

L L ショートブレーキ

OFF

(Hi-z)

OFF

(Hi-z)

ストップ

6.ブラシ付きDCモータモード時の信号制御ファンクション 2(DC_S×4 軸モード使用の場合)

Control 入力 出力段状態

IN1

(Phase 端子)

H H L L ショートブレーキ

L H L H 正転/逆転

IN2

(Enable 端子)

OUT1 OUT2 モード

H L H L 逆転/正転

L L

OFF

(Hi-z)

OFF

(Hi-z)

ストップ

● 外部 PWM 制御機能について

PWM端子に 0/5V(TTL レベル以上)の PWM 信号を入力する事により、速度制御が可能です。

PWM制御時には、通常動作とショートブレーキの繰り返しになります。

PWM信号による制御を使用しない場合は、PWM端子(ショートブレーキ端子)をHレベルに固定してください。

また定電流リミッタ機能を使用する場合には、定電流値に到達以降、37.5%の Mixed Decay 制御になり

ます。特に貫通電流防止のためのデッドタイムの設定など内部で設定されているため、特別に設定は不要です。

ステッピングモータ駆動モード(Large、Small)時にはショートブレーキ機能は働きません。

ブラシ付きDCモータ駆動モードにて、ステッピングモータの駆動も可能です。

ただし、その時はショートブレーキ機能を使わず、且つデジタル tBLANK も OFF にして駆動してください。

また、入力のファンクションが異なりますので、確認の上ご使用ください。

13

2010-07-09

● 絶対最大定格 (Ta=25ºC)

項 目 記 号 定 格 単位 備 考

TB62212FTAG

Logic 電源電圧 内部 VCC

出力電圧 VM

6 V

40 V

Iout(ST_S) 1.5 A/相 (注 1)

Iout(ST_L) 1.8 A/相

出力電流

Iout(DC_S) 2.0 A/相

Iout(DC_L) 4.0 A/相

電流検知端子電圧 VRS

Logic 入力電圧 VIN

VM ± 4.5 V

-0.4~6.0 V

定電流基準電圧入力端子 Vref GND~4.2V V

1.4 (注 2)

許容損失 PD

動作温度 Topr

保存温度 Tstg

接合部温度 Tj

3.2

−40~85 ºC

−55~150 ºC

150 ºC

W

(注 3)

注 1: 通常時の最大電流値は熱計算の上、1 相あたり絶対最大定格に対してマージンを持った上でご使用ください。

注 2: 単体測定時 (Ta = 25ºC)

注 3: 専用実装基板へ実装時 (Ta = 25ºC)

Ta :IC 周囲温度です。

Topr:動作させる時の IC 周囲温度です。

Tj :動作中の IC チップ温度です。Tj 最大値は TSD (サーマルシャットダウン回路) の温度で制限されます。

● 絶対最大定格について

絶対最大定格については、どのような状況においても、一瞬たりとも越えてはいけない限界特性規格です。

絶対最大定格を越えた場合、IC の破壊や劣化、損傷の原因となり、IC 以外の周辺回路・部品についても破壊や損傷、

劣化を与える可能性が有ります。

いかなる動作条件においても、必ず、絶対最大定格を越えないように動作環境及び使用環境を設計してください。

実際のアプリケーションにおいても、記載された動作範囲でのご使用をお願いします。

14

2010-07-09

回路

動作範囲(Ta=0~85ºC)

項目 記号

内部 Logic 電源電圧 VCC - (内部自動発生) 4.5 5.0 5.5 V

モータ電源電圧 VM - 10 24 38 V

Iout

(ST_S)

Iout

モータ出力電流値

Logic 入力電圧 VIN - - GND 3.3 5.0 V

(ST_L)

Iout

(DC_S)

Iout

(DC_L)

測定

- Ta=25ºC,1 相あたり - 0.3 1.0

- Ta=25ºC,1 相あたり - 0.6 1.5

- Ta=25 ºC,1 相あたり - 1.0 1.9

- Ta=25 ºC,1 相あたり - 2.0 3.8

測定条件 最小 標準 最大 単位

TB62212FTAG

A

チョッピング周波数

設定範囲

Vref 電圧 Vref - VM=24V GND 3.0 4.0 V

電流検知端子電圧 VRS - VM=24V 0 ±1.0 ±1.5 V

注:Tj の最大値は、120ºC を目処にお使いください。熱条件によっては最大電流を流せない場合があります。

fchop - VCC=5.0V 40 100 150 kHz

15

2010-07-09

電気的特性 1 (特に指定がない項目は, Ta=25ºC, VM=24V)

項目 記号

測定

回路

測定条件 最小 標準 最大 単位

TB62212FTAG

High VIN(H)

Logic 端子入力電圧

Low VIN(L)

Logic 入力ヒステリシス電圧 His

IIN(H)

Logic 端子入力電流

IIN(L)

消 費 電 流 (VM ライン)

出力端子

上側 IOH

リーク電流

下側 IOL

出力電流チャネル間誤差 ⊿Iout1

出力電流設定値誤差 ⊿Iout2

RS 端 子 電 流 IRS

IM1

IM2

-

-

-

Logic の各端子

Logic の各端子 0.1 0.2 0.5 V

VIN=5V、抵抗つき入力端子

2.0 3.3 5.4

GND

-0.4

GND 0.8

- 50 70

- - 1.0

V

μA

出力 OPEN

(ENABLE ALL=L),

- 1.0 2.0

出力段全非動作

-

OUT OPEN,fPWM=100kHz

Logic 動作, 出力段非動作

-

-

-

VRS=VM=24V, Vout=0V,

ENABLE ALL=L

VRS=VM=Vout=24V,

ENABLE ALL=L

出力電流のチャネル間

誤差 Iout=0.6A

Iout=0.6A −5 - 5 %

- 8 10

−1 - - μA

- - 1.0 μA

−5 - 5 %

mA

VRS=24V,VM=24V,

-

ENABLE ALL=L

- - 10 μA

(全停止状態)

Iout=0.6A,

Tj=25ºC,順方向

(上+下)Small Mode

Iout=0.6A,

Tj=25ºC,順方向

(上+下)Large Mode 時

- 2.2 2.6

Ω

- 1.1 1.3

出力トランジスタ

ドレインソース間

オン抵抗(上下和)

Ron(DS:

上下和)S

Ron(DS:

上下和)L

-

16

2010-07-09

TB62212FTAG

電気的特性 2 (特に指定がない項目は, Ta=25ºC, VM=24V)

項 目 記号

Vref 入力電圧 Vref -

Vref 入力電流 Iref -

Vref 減衰比 Vref(gain) -

TSD 温度

内部 VCC 復帰電圧 VCCR - ENABLE=H 2.0 3.0 4.0 V

VM 復帰電圧 VMR - ENABLE=H 7.0 8.0 9.0 V

過電流検出回路動作電流

注 1: サーマルシャットダウン (TSD) 回路について

この回路はイレギュラーな条件にて IC のジャンクション温度が規定温度に達し、過温度状態になり検出回路

が動作した場合、内部停止回路が動作、全出力部をシャットダウンし OFF 状態(Hi-Z)にします。

TSDの動作温度の設定は 130ºC(min) から 170ºC(max) で動作します。

TSDが動作した場合、次に POR が解除されるまで、出力を停止します。

注 2: 過電流検出回路について

この回路はイレギュラーな条件にて出力に規定値以上の電流が流れた場合、内部停止回路が働き、全出力部を

OFF状態にします。

PORが再度解除されるまで動作したままになります。

ただし、恒久的なフェールセーフのためには、VM 電源ラインには必ずヒューズの挿入をお願いいたします。

TjTSD

(注 1)

ISD

(注 2)

測定

回路

- - 130 - 170

- fchop=100kHz 設定時 - 2.8 - A

測定条件 最小 標準 最大 単位

ENABLE=H,

出力動作

ENABLE=L,

出力非動作,Vref=3.0V

ENABLE=H,

出力動作,Vref=2.0V

GND 2.0 4.0 V

0 - 10 μA

1/4.8 1/5.0 1/5.2 -

ºC

17

2010-07-09

AC 電気的特性 (Ta=25ºC, VM=24V, 負荷 6.8 mH/5.7 Ω)

項目 記号

Logic 入力周波数 fLogic

tw(tLogic) 100 - -

測定

回路

-

測定条件 最小 標準 最大 単位

-

TB62212FTAG

- 1.0 - 200 kHz

最小信号パルス幅

出力トランジスタ

スイッチング特性

PWM ON Duty 最小幅 tPWM(Min)

ノイズ除去用不感帯時間

OSC_M 基準信号発振周波数 fOSC_M

チョッピング

可能周波数範囲

チョッピング設定周波数 fchop

twp

twn

tr

tf

tpLH(INX) - 1 -

tpHL(INX)

tpLH(OSC) - 0.5 -

tpHL(OSC)

-

6.8mH/5.7 Ω負荷時

Signal~OUT 間

6.8mH/5.7 Ω負荷時

OSC_M~OUT 間

6.8mH/5.7 Ω負荷時

-

DC モータモード時

-

50 - -

50 - -

- 0.1 -

- 0.1 -

- 1.5 -

- 1 -

2 - - μs

6.8mH/5.7 Ω負荷時

tBLANK_AB(L)

-

Iout=0.6A,VM=24V にて

200 300 400 ns

BLANK_CD(L)

t

BLANK_AB(H)

t

アナログ t

-

Iout=0.6A,OSC=800kHz にて

BLANK 値

4.0 5.0 6.0 μs

BLANK_CD(H)

t

3×OSC 周期時間の時

-

Cosc=220pF 600 800 1000 kHz

-

fchop

出力動作 (Iout=1.0A) 40 100 150 kHz

-

出力動作 (Iout=0.6A)

- 100 - kHz

OSC=800kHz

ns

μs

18

2010-07-09

TB62212FTAG

● Mixed Decay Mode の電流波形と設定について

「NF」は出力電流が設定電流値に到達したポイントをいいます。

定電流制御の際、電流のふれ幅 (電流脈流分) を決定する Mixed Decay Mode の割合は、37.5%に設定して

います。

CR 端子

内部 CLK

波形

Decay Mode

37.5%

Mixed

Decay

Mode

NF

Charge Mode → NF:設定電流値到達 → Slow Mode →

Mixed Decay Timing → Fast Mode → Charge Mode

MDT (Mixed Decay Timing)ポイント: 37.5%固定

fchop

設定電流値

MDT

19

2010-07-09

● Mixed Decay Mode の波形 (電流波形)

内部 CR

CLK 信号

Iout

設定電流値

25%

Mixed

Decay

Mode

NF

1/fchop

設定電流値

RNF

MDT (Mixed Decay Timing) ポイント

・NF ポイントが Mixed Decay Timing より後の場合

Iout

設定電流値

25%

Mixed

Decay

Mode

1/fchop 1/fchop

MDT (Mixed Decay Timing) ポイント

NF

NF

Vref 変化

Charge の後は Fast になります。

設定電流値

・Mixed Decay Mode にて出力電流値 > 設定電流値の場合

設定電流値

Iout

25%

Mixed

Decay

Mode

NF

1/fchop 1/fchop 1/fchop

NF

設定電流値

MDT (Mixed Decay Timing) ポイント

Vref 変化

TB62212FTAG

1/fchop

NF

NF

RNF

20

2010-07-09

● 設定電流の計算式について

設定電流の値については、R

Vref(gain):Vref 減衰比は、内部固定で 1 / 5.0 (typ.) です。

例えば、Vref = 1.5 V、R

とした場合、モータの定電流制御出力値(Peak 電流)は以下の値になります。

I

OUT

gainVI

refOUT

1

5

V

×=

Ω

RS と Vref を決定すると決まります。

)(

VV

ref

)(

×=

R

)(5.1

=

)(

Ω

RS

RS = 1.0 Ω

)(3.0

A

)(0.1

● OSC 発振周波数 (チョッピング基準周波数) の計算式について

OSC 発振周波数 (fosc) とチョッピング周波数 (fchop) は以下の式で計算できます。

TB62212FTAG

fosc = 61820×C(pF)^-0.8043 (kHz)

Cosc = 220pF で約 810kHz となります。

この時、ステッピングモータの実チョッピング周波数は、OSC 発振周波数の 1 / 8 の周波数である

810 / 8 = 101(KHz)になります。

21

2010-07-09

TB62212FTAG

IC の消費電力について

IC が消費する電力については、大枠、出力部のトランジスタが消費する電力とロジック部およびチャージ

ポンプ回路の消費する電力の 2 つの部分に分けることができます。

パワートランジスタ部の消費電力 (Ron=上下和で 2.2 Ωで、計算しています)

出力に電流を電力は H ブリッジ上下のトランジスタによって消費されます。

1 つの H ブリッジのトランジスタ部の電力は以下の式で表すことができます。

P (out) = Iout (A) × V

2 相励磁動作を行い、出力電流波形が完全な方形波波形になる場合での出力の平均消費電力は、以下のように

計算できます。

Ron 上下= 2.2 Ω (@1.0 A)、Iout(peak) = 0.6 A、VM = 24 V とすると下記の様に計算できます。

P (out Unit) = 0.6 (A)

= 1.584 (W)

DS (V) × H スイッチ × 2 = Iout

2

× 2.2 (Ω) × H スイッチ × 2 ................................. (2)

ロジックと IM 系の消費電力

ロジックと IM 系の消費電力は動作時と停止時に分けて計算します。

I (IM2) = 8.0 mA (typ.) : 動作時

出力系は、VM (24 V) に接続されています。(出力系: VM に接続される回路により消費される電流と出力段

がスイッチングすることにより消費される電流の合計)

消費電力は以下のように見積もることができます。

P (IM)= 24 (V) × 0.008 (A) .............................................................. (3)

= 0.192 (W)

消費電力

1 と 2 の結果から、片軸での消費電力 P は、以下のように計算できます。

P = P (out unit) + P (IM) = 1.776 (W) となります。

実際のモータ電流は回転数などによって、実効電流が変化するため消費電流も変化します。

また、基板などにおける熱設計に関しては十分実装評価を行った上、マージンをもって設定してください。

2

× Ron 上下 × H スイッチ × 2 .. (1)

22

2010-07-09

動作時の出力段トランジスタ動作モードについて

VM へ

VM へ

RRS

RRS

U1

Rs 端子

(注)

U2

U1

Rs 端子

(

注)

L1

負荷

L2

負荷

L1

GND

GND GND

コイルへの電力の Charge を行います。

Charge モード

Slow モード

コイル電力の弱い減衰を行います。

出力段トランジスタ動作のファンクション

L2

U2

TB62212FTAG

VM へ

RRS

Rs 端子

U1

(注)

負荷

L1

Fast モード

コイル電力の強い減衰を行います。

U2

L2

Mode U1 U2 L1 L2

Charge ON OFF OFF ON

Slow OFF OFF ON ON

Fast OFF ON ON OFF

注: 上表は、例として上の図中の矢印の方向に電流を流す場合です。

逆方向の場合は、下表のようになります。

Mode U1 U2 L1 L2

Charge OFF ON ON OFF

Slow OFF OFF ON ON

Fast ON OFF OFF ON

23

2010-07-09

出力段トランジスタ動作モード 2

Mixed Decay Mode のシーケンス

U1

OUT A

L1

出力電圧A

出力電圧A

設定電流

出力電流

H

L

H

L

L

VM へ

RRS

U2

OUT A

L2

GND

Charge Mode

50%

U1

L1

VM へ

R

RS

U2

OUT AOUT A

L2

U1

OUT A

L1

GND

50%

Slow Mode Fast Mode

TB62212FTAG

VM へ

RRS

U2

OUT A

L2

GND

50%

Charge → Slow → Fast の各モードを切り替えることによって定電流制御を行います。

24

2010-07-09

PD – Ta(パッケージの許容損失)

(W)

D

許容損失 P

パッケージの熱抵抗 Rth(j-a)

①単体 :113ºC/W

②専用基板実装時 (100mm × 200mm × 1.6mm) :37ºC/W

3.5

2.5

1.5

0.5

3

2

①

1

0

0

25 50 75 100 125 150

TB62212FTAG

PD – Ta

②

周囲温度 Ta (°C)

25

2010-07-09

TB62212FTAG

過電流検出回路の動作時間

ISD 不感帯時間と ISD 動作時間について

過電流検出回路には、irr やスイッチング時のスパイク電流による誤検出を防ぐために不感帯時間を設定

しています。

この不感帯時間は、チョッピング周波数設定用 OSC 周波数に同期しており、以下のように設定しています。

不感帯時間 = 4 × OSC 周期

過電流が出力段に流れてから出力が停止するまでの時間は、次のとおりです。

最小 : 5 × OSC 時間 (同期時間の最大値1OSC 時間を含む)

最大 : 8 × OSC 時間

ただし、この動作時間は理想的に過電流が流れたときの動作時間であり、出力の制御モードタイミングに

よっては、過電流回路が働かないことがあります。

したがいまして安全のためには、モータ電源ラインへの保護用ヒューズの挿入をお願いいたします。

ヒューズの容量は使用条件によって異なりますので、動作に問題がなく IC の許容損失を超えない容量を

持ったヒューズを選定してください。

26

2010-07-09

TB62212FTAG

● tBLANK(ノイズ除去用不感帯時間)について

駆動モータの種類にあわせ、主にスイッチング時のノイズ誤動作防止を目的として、2 種類の

不感帯時間(ブランキング時間)を内蔵しています。

①アナログ tBLANK(Stepping Motor Mode 時)

モータ部 AC 特性で値を規定している“ノイズ除去用不感帯時間(アナログ tBLANK) ”は、IC 内部で

持つ固定時間です。主に Stepping Motor を定電流駆動している時の irr(ダイオードリカバリ電流)

を誤判断しない為に使用いたします。

この時間は、IC の固有値であるため、変更はできません。

②デジタル tBLANK(ブラシ付き DC Motor Mode 時)

“

アナログ tBLANK”とは別に初期モードセレクトによって規定している"tBLANKK 時間"は、外付け

チョッピング周期よりデジタル的に作成される不感帯時間であり、"DC モータ駆動モード"にて、

DC モータを PWM 駆動する時に発生する“バリスタリカバリ電流”を誤判定しないために使用します。

“Motor Select”にて“Stepping Motor”が選択された場合は、“デジタル tBLANK”は無し(0 μs)に

設定され、内部で固定に持つアナログ値の tBLANK 時間だけが有効になります。

OSC_M を基準に時間を作成しているため、OSC_M を変更した場合、時間を変更することができます。

(ただし、OSC_M を変更した場合、他にも変更される項目(モータチョッピング周波数や起動時不感帯

時間等)がありますのでご注意下さい)

● ブラシ付きDCモータ駆動時のデジタル tBLANK のタイミングについて

Charge

Digital

Digital

tBLANK

Decay

定電流制御のChargeスタートタイミング

Decay

Digital

tBLANK

Decay

Iout=0

PWM切り替わりポイント

PWM

Iout

外部から入力されるPWM信号(IN1、IN2、SB)の切り替え直後(ショートブレーキからチャージのタイミング等)、

および定電流チョッパ時の Charge 開始タイミングにデジタルの“tBLANK”が入ります。

デジタルの tBLANK はDCモータモードのみ有効です。

DCモータ駆動時の Decay Mode は、37.5%の Mixed Decay によりますが、一周期の中の 3CLK までがデジタル tBLANK

による Charge の時間になりますので、タイミングによっては、そのまま Fast Decay に移行する可能性もあります。

Digital

tBLANK

PWMの切り替わりポイント

27

2010-07-09

TB62212FTAG

推奨応用回路

各素子のところにある数値は推奨値です。

各入力条件の数値につきましては、前述の動作範囲をご確認ください。

0V

0V

0V

0V

0V

0V

5V/3.3V

5V/3.3V

5V/3.3V

5V/3.3V

5V/3.3V

5V/3.3V

36 35 34 33 32 31 30 29 28 27 26 25

36 35 34 33 32 31 30 29 28 27 26 25

36 35 34 33 32 31 30 29 28 27 26 25

37

37

37

ENABLE_B

ENABLE_B

38

38

38

ENABLE_A

ENABLE_A

220pF

220pF

1Ω

1Ω

39

39

39

40

40

40

41

41

41

Rs_D

Rs_D

Rs_D

Rs_D

OSCM

OSCM

0.1µF

0.1µF

1Ω

1Ω

0V

0V

0V

0V

0V

0V

5V/3.3V

5V/3.3V

5V/3.3V

5V/3.3V

5V/3.3V

5V/3.3V

42

42

42

43

43

43

44

44

44

45

45

45

46

46

46

Vcc

Vcc

Rs_A

Rs_A

Rs_A

Rs_A

PHASE_A

PHASE_A

PHASE_B

PHASE_B

NC

NC

47

47

47

NC

NC

48

48

48

1 2

1 2

1 2

注:必要に応じてパスコンの追加を推奨いたします。

GND 配線はできる限り 1 点接地になるようお願い致します。また、各 VM 端子は必ずショートしてください。

入力するデータに関しましては入力ファンクションの項目をご参照の上、入力してください。

信号の設定等を誤りますと、思いがけない大電流などが流れ IC が破損するおそれがあります。

出力間のショート、および出力の天絡、地絡時に IC 破壊の恐れがありますので、出力ライン、VCC(VM) ライン、

GND ラインの設計は十分注意してください。

NC

NC

NC

NC

0V

0V

0V

0V

5V/3.3V

5V/3.3V0V5V/3.3V5V/3.3V

5V/3.3V

5V/3.3V0V5V/3.3V5V/3.3V

ENABLE_C

ENABLE_C

ENABLE_D

ENABLE_D

PHASE_C

PHASE_D

PHASE_C

PHASE_D

3 4 5 6

3 4 5 6

3 4 5 6

5V/3.3V

5V/3.3V0V5V/3.3V

5V/3.3V

5V/3.3V0V5V/3.3V

0V

0V

0V

0V

M

MM

GND

GND

OUT_D-

OUT_D-

OUT_A-

OUT_A-

GND

GND

M M

MMM MMM

GND

GND

OUT_D+

OUT_D+

OUT_A+

OUT_A+

GND

GND

7

7

7

0.1µF

0.1µF

GND

GND

OUT_C+

OUT_C+

OUT_B+

OUT_B+

GND

GND

8

8

8

10 11 12

10 11 12

10 11 12

9

9

9

Mode 0

Mode 0

OUT_C-

OUT_C-

Digital TBlank_CD

Digital TBlank_CD

Digital TBlank_AB

Digital TBlank_AB

OUT_B-

OUT_B-

Vref_A

Vref_A

0.1µF

0.1µF

0~4V

0~4V

Mode 2

Mode 2

Vref_D

Vref_D

Vref_C

Vref_C

0.1µF

0.1µF

Mode 1

Mode 1

Rs_C

Rs_C

Rs_C

Rs_C

VM

VM

GND

GND

Rs_B

Rs_B

Rs_B

Rs_B

NC

NC

Vref_B

Vref_B

0~4V

0~4V

24

24

24

23

23

23

22

22

22

21

21

21

20

20

20

19

19

19

18

18

18

17

17

17

16

16

16

15

15

15

14

14

14

13

13

13

0.1µF

0.1µF

100µF

100µF

0.1µF

0.1µF

1Ω

1Ω

1Ω

1Ω

0.1µF

0.1µF

0~4V

0~4V

24V

24V

28

2010-07-09

外形図

QFN48-P-0707-0.5

TB62212FTAG

単位: mm

裏面ヒートシンク形状 :5.4mm×5.4mm

コーナー部の面取り寸法:C0.5

コーナー部のR寸法 :3-R0.2

29

2010-07-09

記載内容の留意点

ブロック図

ブロック図内の機能ブロック/回路/定数などは、機能を説明するため、一部省略・簡略化している場合があります。

等価回路

等価回路は、回路を説明するため、一部省略・簡略化している場合があります。

タイミングチャート

タイミングチャートは機能・動作を説明するため、単純化している場合があります。

応用回路例

応用回路例は、参考例であり、量産設計に際しては、十分な評価を行ってください。

また、工業所有権の使用の許諾を行うものではありません。

測定回路図

測定回路内の部品は、特性確認のために使用しているものであり、応用機器の誤動作や故障が発生しないことを保

証するものではありません。

使用上のご注意およびお願い事項

TB62212FTAG

使用上の注意事項

絶対最大定格は複数の定格の、どの一つの値も瞬時たりとも超えてはならない規格です。

複数の定格のいずれに対しても超えることができません。

絶対最大定格を超えると破壊、損傷および劣化の原因となり、破裂・燃焼による傷害を負うことがあります。

デバイスの逆差し、差し違い、または電源のプラスとマイナスの逆接続はしないでください。電流や消費電力が絶

対最大定格を超え、破壊、損傷および劣化の原因になるだけでなく、破裂・燃焼により傷害を負うことがあり

ます。なお、逆差しおよび差し違いのままで通電したデバイスは使用しないでください。

過電流の発生や IC の故障の場合に大電流が流れ続けないように、適切な電源ヒューズを使用してください。IC は

絶対最大定格を超えた使い方、誤った配線、および配線や負荷から誘起される異常パルスノイズなどが原因で

破壊することがあり、この結果、IC に大電流が流れ続けることで、発煙・発火に至ることがあります。破壊

における大電流の流出入を想定し、影響を最小限にするため、ヒューズの容量や溶断時間、挿入回路位置など

の適切な設定が必要となります。

モータの駆動など、コイルのような誘導性負荷がある場合、ON 時の突入電流や OFF 時の逆起電力による負極性の電

流に起因するデバイスの誤動作あるいは破壊を防止するための保護回路を接続してください。IC が破壊した

場合、傷害を負ったり発煙・発火に至ることがあります。

保護機能が内蔵されている IC には、安定した電源を使用してください。電源が不安定な場合、保護機能が動

作せず、IC が破壊することがあります。IC の破壊により、傷害を負ったり発煙・発火に至ることがあります。

パワーアンプおよびレギュレータなどの外部部品 (入力および負帰還コンデンサなど) や負荷部品 (スピーカな

ど) の選定は十分に考慮してください。

入力および負帰還コンデンサなどのリーク電流が大きい場合には、IC の出力 DC 電圧が大きくなります。この

出力電圧を入力耐電圧が低いスピーカに接続すると、過電流の発生や IC の故障によりスピーカの発煙・発火

に至ることがあります。(IC 自体も発煙・発火する場合があります。) 特に出力 DC 電圧を直接スピーカに入

力する BTL (Bridge Tied Load) 接続方式の IC を用いる際は留意が必要です。

30

2010-07-09

使用上の留意点

過電流検出回路

過電流検出回路 (通常: カレントリミッタ回路) はどのような場合でも過電流検出するわけではありません。

動作後は、速やかに過電流の原因を除くようお願いします。

絶対最大定格を超えた場合など、ご使用方法や状況により、過電流検出回路が正常に動作しなかったり、動作

する前に IC が破壊したりすることがあります。また、動作後、長時間過電流が流れ続けた場合、ご使用方法

や状況によっては、IC が発熱などにより破壊することがあります。

過熱検出回路

過熱検出回路 (通常: サーマルシャットダウン回路) は、どのような場合でも過熱検出するわけではありませ

ん。動作後は、速やかに発熱状態を解除するようお願いします。

絶対最大定格を超えて使用した場合など、ご使用法や状況により、過熱検出回路が正常に動作しなかったり、

動作する前に IC が破壊したりすることがあります。

放熱設計

パワーアンプ、レギュレータ、ドライバなどの、大電流が流出入する IC の使用に際しては、適切な放熱を行

い、規定接合温度 (Tj) 以下になるように設計してください。これらの IC は通常使用時においても、自己発

熱をします。IC 放熱設計が不十分な場合、IC の寿命の低下・特性劣化・破壊が発生することがあります。ま

た、IC の発熱に伴い、周辺に使用されている部品への影響も考慮して設計してください。

逆起電力

モータを逆転やストップ、急減速を行った場合に、モータの逆起電力の影響でモータから電源へ電流が流れ込

みますので、電源の Sink 能力が小さい場合、IC の電源端子、出力端子が定格以上に上昇する恐れがあります。

逆起電力により電源端子、出力端子が定格電圧を超えないように設計してください。

TB62212FTAG

31

2010-07-09

TB62212FTAG

製品取り扱い上のお願い

• 本資料に掲載されているハードウェア、ソフトウェアおよびシステム(以下、本製品という)に関する情報

等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

• 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得

て本資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

• 当社は品質、信頼性の向上に努めていますが、半導体製品は一般に誤作動または故障する場合があります。

本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、

お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うことをお

願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシー

ト、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明

書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、

表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お

客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

• 本製品は、一般的電子機器(コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家電

機器など)または本資料に個別に記載されている用途に使用されることが意図されています。本製品は、特

別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産

損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下“特定用途”という)に

使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇

宙機器、医療機器、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連

機器、昇降機器、電力機器、金融関連機器などが含まれます。本資料に個別に記載されている場合を除き、

本製品を特定用途に使用しないでください。

• 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

• 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することは

できません。

• 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当

社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に

関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情

報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

• 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、ある

いはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、

「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行っ

てください。

• 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず弊社営業窓口までお問合せください。本製

品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査

の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害

に関して、当社は一切の責任を負いかねます。

32

2010-07-09

Loading...

Loading...