Page 1

MANUAL DE SERVIÇO

DVD VIDEO RECORDER

SD RX38D

ESPECIFICAÇÕES TÉCNICAS

GERAIS

Alimentação ........................................................... 100-220V ~ 50 - 60Hz

Consumo ................................................... <1W (stand by)/18W (médio)

Dimensões aprox. (LxAxP) ................................................ 360x45x249mm

Peso aprox. ........................................................................................2,2kg

SISTEMA

Laser ...................................................................... Laser a semicondutor,

comprimento de onda

650/780nm

Sistema de sinal de cor ............................................ NTSC/PAL-M/PAL-N

Faixa de frequências de áudio ......................................... 20Hz a 20kHz

Relação Sinal/Ruído .....................................>65dB (Saídas analógicas)

Distorção harmônica ...................................................................... <0,1%

Faixa dinâmica ................................................................................ >75dB

Canais Recebidos ....................................................................... TV: 2~69,

CATV: 1~125

Tempo de Backup ........................................ >12h, com bateria interna

Relógio digital ...................................................................... Formato 24h

Condições de operação ........................................................... 5 ~ 40°C

ENTRADAS

Terminal de Antena (RF IN) ............ Conector F, 75ohm, VHF/UHF/CATV

• Projeto e especificações estão sujeitos a alterações sem aviso prévio.

• Aviso: a cópia não autorizada de materiais áudio visuais para uso doméstico pode infringir os direitos de terceiros.

Entradas de Vídeo: .........................................................1,0V (p-p), 75ohm,

......................................................... sincronismo negativo, 1 tomada RCA

Entrada de S-VÍDEO .................................................. (Y) 1,0V (p-p), 75ohm,

....................................................... sincronismo negativo, (C) 0,286V (p-p),

......................................................... 75ohm, 1 tomada Mini DIN de 4 pinos

Entradas de Áudio (áudio analógico) ....................................... 2,0V (rms),

............................................................................. 47 kohm, 2 tomadas RCA

............................................................................... (L - esquerda, R - direita)

Entrada DV .......................................................... 1 tomada DV (IEEE 1394)

SAÍDAS

Terminal de Antena ........................... Conector F, 75ohm, VHF/UHF/CATV

Saída de Vídeo ............................................................... 1,0V (p-p), 75ohm,

......................................................... sincronismo negativo, 1 tomada RCA

Saída de Vídeo Componente/Progressive ......................... (Y) 1,0V (p-p),

............................................................................................................ 75ohm,

................................................................................... sincronismo negativo,

............................................................................. (PR)/(PB) 0,7 (p-p), 75ohm

Saída de Áudio (digital coaxial) ................................... 0,5V (p-p), 75ohm,

............................................................................................... 1 tomada RCA

Saída de Áudio (áudio analógico) ............................ 2,0V (rms), 10 kohm,

................................................... 2 tomadas RCA (L - esquerda, R - direita)

SEMP

1

Page 2

ÍNDICE

ESPECIFICAÇÕES TÉCNICAS ............................................................................................................................................CAPA

1- DESCRIÇÃO GERAL DO PROCESSADOR DO SISTEMA ................................................................................................... 3

2- DIAGRAMA DE BLOCOS ................................................................................................................................................. 6

3- DIAGRAMAS DE CIRCUITOS............................................................................................................................................ 7

4- LAY-OUT DAS PLACAS DE CIRCUITO IMPRESSO ........................................................................................................... 21

5- PINAGEM DOS PRINCIPAIS COMPONENTES ................................................................................................................ 25

6- FORMAS DE ONDA ........................................................................................................................................................ 42

7- VISTA EXPLODIDA .......................................................................................................................................................... 45

8- LISTA DE COMPONENTES............................................................................................................................................... 46

CUIDADO ! COMPONENTES SENSÍVEIS A DESCARGAS ELETROSTÁTICAS

Alguns semicondutores (estado sólido) podem ser facilmente danificados pela eletricidade estática. Tais

componentes são comumente chamados de “componentes sensíveis eletrostaticamente”

Sensitive Devices - ESD)

e

chips

semicondutores. As técnicas a seguir devem ser utilizadas para ajudar a reduzir a incidência de danos

aos componentes causados por eletricidade estática.

1. Mantenha o componente em sua embalagem original até o momento de sua utilização. Se necessário

armazená-lo de outro modo, acondicione-o exclusivamente em material anti-estático.

2. Prepare uma estação de trabalho anti-estática para manuseio da placa montada e/ou componente

2.1. Disponha de uma manta dissipativa sobre a bancada/mesa de trabalho.

2.2. Providencie uma pulseira para descarga de eletricidade estática disponível no comércio.

Efetue diariamente a aferição da pulseira.

2.3. Aterre ambos, manta e pulseira, a uma malha reconhecidamente aterrada.

2.4. Disponha todo o material necessário ao trabalho sobre a manta; minimize os movimentos.

No momento em que for manusear a placa/componente, coloque a pulseira.

Assegure-se de que não haja qualquer potencial que seja aplicado ao chassi ou circuito bem como

retire a pulseira antes de energizar a unidade sob teste/reparo a fim de evitar riscos de choque elétrico.

3. Use somente ferros-de-soldar com a ponta aterrada para soldar ou retirar componentes sensíveis à

eletrostática.

4. Não utilize produtos químicos cujo propelente usado seja freon. Eles podem gerar cargas elétricas suficientes

para danificar componentes

. Exemplos típicos de

ESD

.

ESD’s

são os circuitos integrados, transistores de efeito de campo

IMPORTANTE !

(Electrostatically

ESD

:

2

Page 3

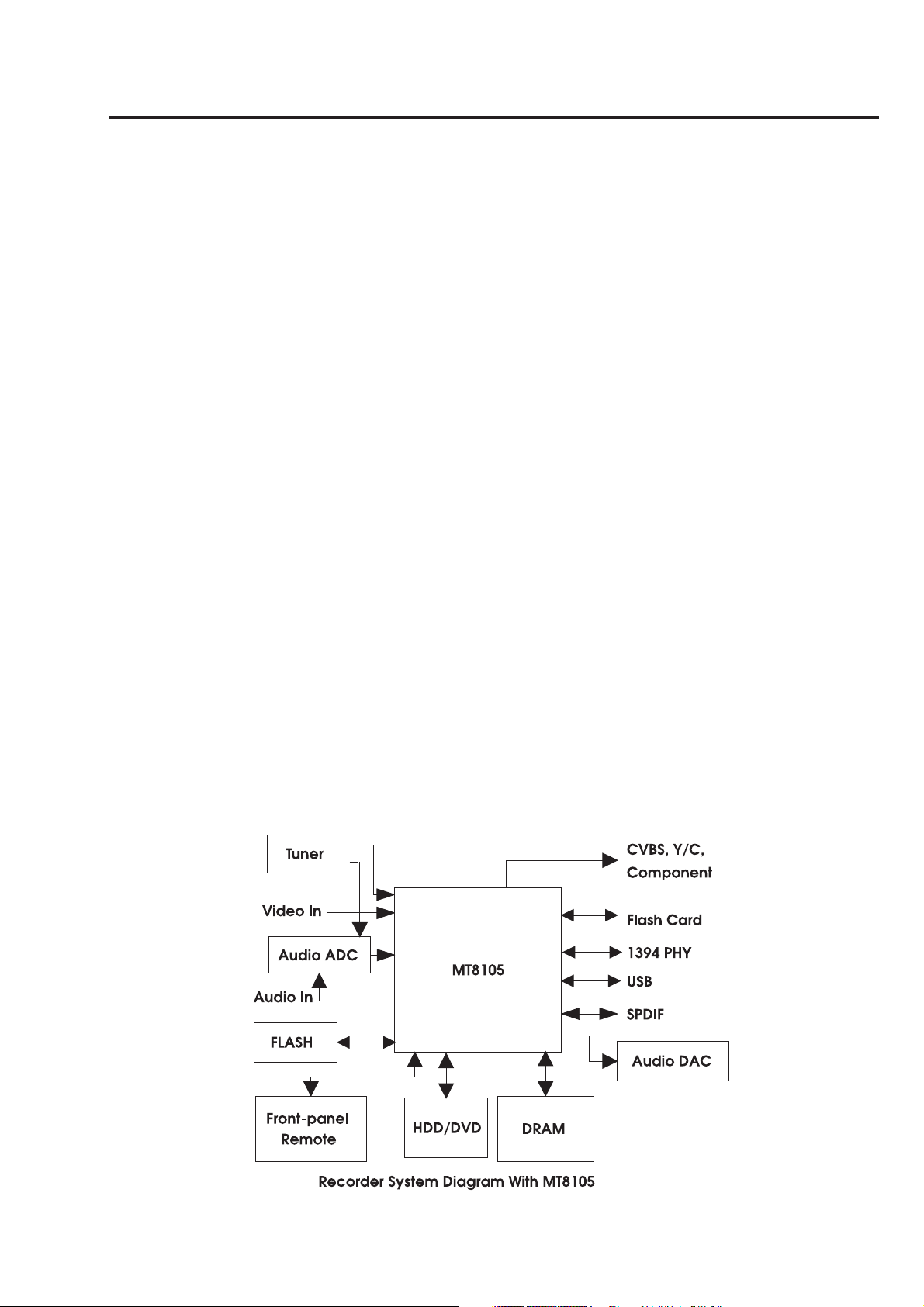

1- DESCRIÇÃO GERAL DO PROCESSADOR DO SISTEMA

1.1- Descrição geral

O MT8105DE/DO da Media Tek é um sistema em

chip (SOC) Codec MPEG que incorpora recursos

avançados, como o decodificador de vídeo

MPEG-2/4, codificador de vídeo MPEG-2/4, DV

Codec, decodificador de TV, codificador de TV

de alta definição, USB, 1394, interface de cartão

de memória versátil, e processamento de

desentrelaçamento de última geração. O MT8105

possibilita aos fabricantes de equipamentos

eletrônicos de consumo construir gravadores de

DVD econômicos e de alta qualidade, gravadores

de vídeo digitais (DVR) ou quaisquer outros

dispositivos de áudio/vídeo de entretenimento

para uso doméstico.

Proporcionando o recurso de gravação e

reprodução simultâneas, o MT8105 fornece

facilmente a função time-shift aos produtos finais.

O MT8105 também suporta drive IDE dual,

incluindo HDD, DVD-ROM, DVD+R/RW, DVD-R/RW

e DVD-RAM. Com tal flexibilidade, os fabricantes

de produtos eletrônicos de consumo podem

produzir diferentes produtos com base na mesma

experiência.

Com a controladora embutida 1394, o MT8105

pode controlar os dispositivos 1394, como DV, e

grava o conteúdo para DVD ou HDD. O MT8105

também fornece interface “glueless”

(incorporada) para Compact Flash, Memory-Stick

e Secure Disk, usada no intercâmbio de dados

com outros dispositivos. Além disso, o MT8105

suporta a USB OTG (on-the-go) para atender

futuras necessidades de conectividade, tais

como modem ou WLAN. Tudo isso torna o MT8105

adequado para os servidores de mídia

doméstica.

Para enriquecer o recurso de reprodução, o

MT8105 equipa um decodificador de vídeo MPEG4, suportando o perfil simples avançado (ASP) do

MPEG-4/DivX1. Torna os produtos baseados no

MT8105 capazes de reproduzir o conteúdo de

MPEG-4 que se torna cada vez mais popular.

A varredura progressiva do MT8105 utiliza o

avançado algoritmo de desentrelaçamento

adaptável ao movimento MDDi™ da Media Tek

para obter a melhor reprodução de filmes e

vídeos. Pode detectar facilmente a fonte de pulldown 3:2/2:2 e restaurar as imagens originais

corretas. Suporta ainda o algoritmo preservador

de bordas, atualmente em processo de

patenteamento, para remover o efeito dente de

serra.

Principais características

• MPEG-2(4) Codec

• DV Codec

• Decodificador de TV 4 canais, 10 bits/27MHz

• Camada de link 1394

• USB OTG

• E/S Direta de Compact Flash, Memory Stick, e

Secure Digital

• Desentrelaçamento de Preservação de Bordas,

Adaptável ao Movimento

• Codificador de TV 6 Canais, 108MHz/12 bits

Aplicações

• Gravadores de DVD autônomos

• Gravadores combinados HDD/DVD

• Servidores de Mídia Doméstica

(*) Algumas das funções descritas não são aplicáveis ao modelo SD RX38D.

3

Page 4

1.2- Lista de Características Gerais

DVD player com super-integração usando um único

chip

• Vídeo MPEG-1/MPEG-2/JPEG

• Vídeo MPEG-4 ASP

• Dolby AC-3/DTS/DVD-Áudio

• Interface para USB/CF/MS/SD

• Escalagem e aprimoramento da qualidade do DVD

• OSD & Subimagem

• Acelerador Gráfico 2-D

• Gerador de clock embutido

• Decodificador de TV embutido de alta qualidade

• Codificador de TV embutido de alta qualidade

• Processador embutido de vídeo progressivo

• Pós-processador de efeitos de áudio

• Clock de Tempo Real

• RISC de 32 bits embutido, Cache/M MU/InstructionRAM suportada

• Suporta resolução de movimento half pel

Decodificador de TV

• Suporta 4 entradas de vídeo analógicas (4 CVBS ou 2

CVBS e 1 Vídeo S)

• Suporta NTSC, PAL-BDGHIK, PAL-M, PAL-N, SECAM,

NTSC-4.43, PAL-60

• Detecção automática de sinal

• Detecção automática padrão de TV.

• Controle de ganho automático.

• Controle de cor automático.

• Comb-filter 2D adaptável 5H.

• Ajustes e aprimoramentos na qualidade do vídeo.

• Compensação de 2D, CTI, e ajuste de tom de pele

(flesh tone)

• Detecta automaticamente a proteção Macrovision

• VBI slicer incorporado que suporta closed caption,

Teletext, CGMS-A/WSS, e outros serviços VB para

sistemas de 525 e 625 linhas

Codificador MPEG

• Suporta codificação de perfil simples MPEG-1 /

MPEG-2 / MPEG-4

• Suporta CBR e VBR

• Redução do nível de ruído de vídeo

• Suporta a detecção da mudança de cena

• Suporta recuperação de filme

• Suporta NTSC/PAL

• Suporta I/IP/IPB/IBBP com tamanho de GOP

programável

- 314M: DV25-NTSC

- 314M: DV25-PAL

- 314M: DV50-NTSC

- 314M: DV50-PAL

Codificação de Áudio

• Codificador para Dolby Digital

• Codificação de áudio MPEG-1 camada 2

• Codificação de áudio DV

• Codificação PCM

Controladora de Memória

• Suporta 16MB/32MB/64MB/128MB, SDRAM e DDRDRAM

• Suporta interface de barramento de dados de 16/32

bits SDRAM

• Proporciona o modo SDRAM de auto-atualização

• Endereçamento de setores baseados em bloco

• Suporta Interface de DRAM de 3,3/2,5 V

• Suporta até 16MBytes Flash

• Atualização de Flash por meio de RS232 ou CD-R

Decodificação de vídeo

• Decodifica vídeo MPEG1 e o nível principal de MPEG2,

vídeo do perfil principal (720/480 e 720x576)

• Decodifica Perfil Simples Avançado MPEG-4

• Suporta DivX 3.11/4.x/5.x

• Função “digest view” suave com decodificação de

imagem I, P e B

• Decodificação de imagem JPEG de referência,

seqüencial estendida e progressiva

• Suporta títulos CD-G

Processador de Video/OSD/SPU/HLI

• Escalagem de vídeo vertical/ horizontal com relação

arbitrária de 0,25 a 256X

• OSD formato bitmap de 65535/256/16/4/2 cores,

• OSD formato RLC de 256/16 cores

• Rolagem automática da imagem OSD

• Transição de apresentação de slides como

Especificação de DVD-Áudio

Acelerador Gráfico 2-D

• Suporta decodificação de texto e bitmap

• Suporta preenchimento de linha, retângulo e

gradiente

• Suporta bitblt

• Operação de cópia chroma key

• Máscara de recorte

Decodificador DV

• suporta os seguintes seis formatos:

- 61834: DV25-NTSC

- 61834: DV25-PAL

Processamento de Áudio

• Decodificação Dolby Digital (AC-3)

• Decodificação DTS

4

Page 5

• Decodificação MLP para DVD-Audio.

• Decodificação de áudio MPEG-1 camada 1/camada 2

• Decodificação de áudio multicanal MPEG-2

camada1 / camada2

• Decodificação de áudio DV

• Decodificação Dolby Pro Logic-II

• Decodificação HDCD (High Definition Compatible

Digital)

• Função Downmix

• Suporta saída IEC 60958/61937

- PCM / bit stream / mute mode

- Latência IEC até 2 quadros, customizada

• Gerador de ruído rosa e gerador de ruído branco

• Funções de Karaokê

- Eco de microfone

- Controle de tonalidade do microfone

- Assistente vocal/mute vocal

Mudança de tom (key shift) até +/- 8 tons controlados

por 1/2 tom

• Equalizador de canais

• O processamento de 3D Surround inclui Surround virtual

e separação de alto-falantes

• Processamento espacial multicanal.

• Interface para Cartão Secure Digital (Cartão SD)

• Acelerador VFD de alto desempenho

• Receptor de infravermelho para formatos Versatile

Perfil

• Encapsulamento LQFP de 256 pinos

• Tensões operacionais duais 3,3/1,8V

Codificador de TV

• Seis DACs de 108MHz/12bits

• Suporta NTSC, PAL-BDGHINM, PAL-60

• Suporta formato de TV progressivo 525p, 625p

• Desliga automaticamente canal(ais) não

conectado(s).

• Suporta monitor de PC (VGA)

• Suporta Macrovision 7.1 L1, Macrovision 525P e 625P

• CGMS-A/WSS

• Closed Caption

Saída Progressiva

• Detecção automática de filme ou vídeo

• Detecção de fonte pull-down 3:2

• Desentrelaçamento adaptável avançado de

movimento

• Preservação de bordas

• Memória externa mínima necessária

Entradas de Áudio/Vídeo

• Line-in/SP DIF-in para processamento de áudio versátil

• Suporta picture-in-picture para decodificação de

vídeo e fonte de entrada

Interface Externa

• USB 1.1 OTG (On-the-Go)

• Link 1394

• Interface Flash Compacta

• Interface para Memory Stick

5

Page 6

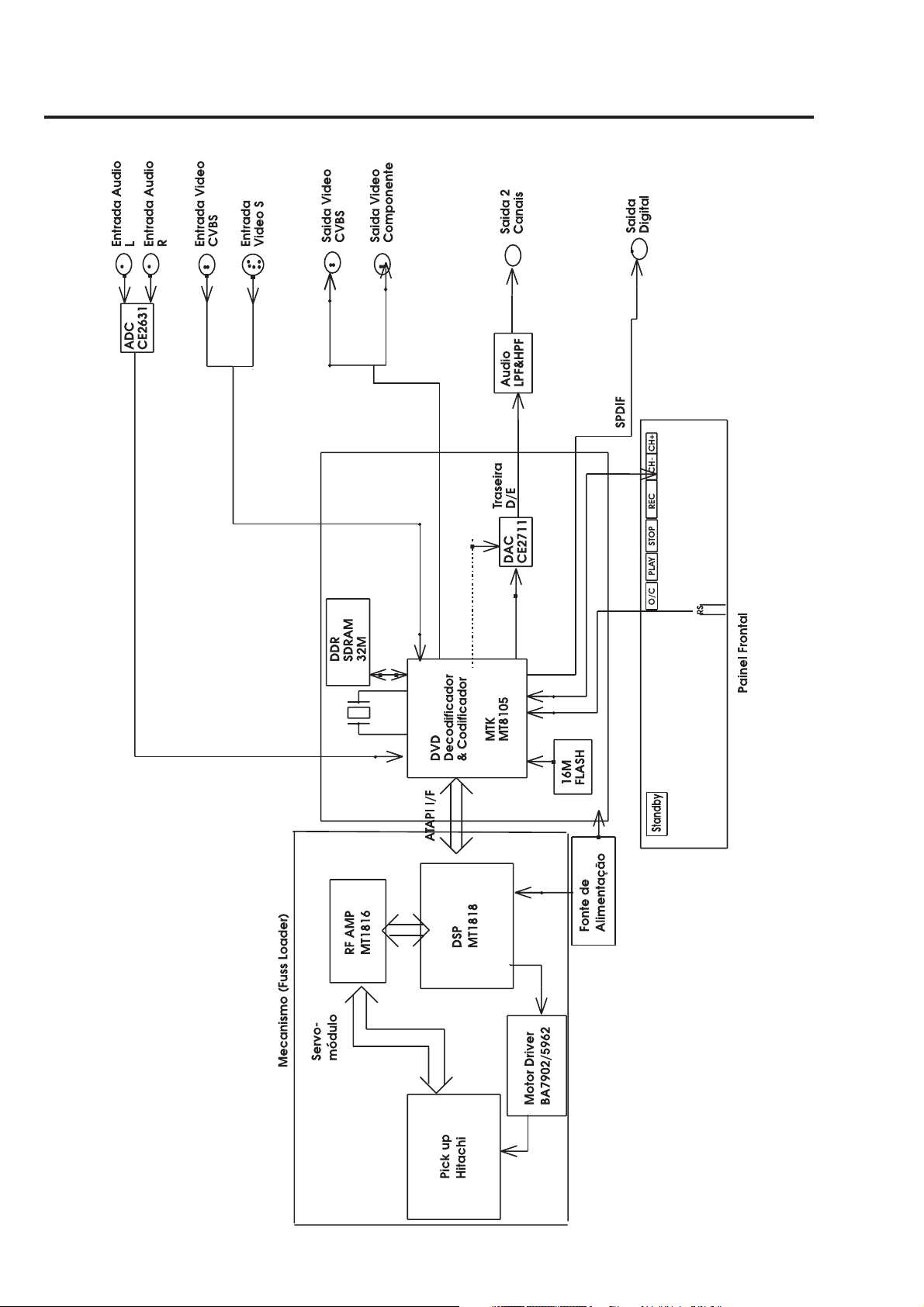

1- DIAGRAMA DE BLOCOS

2.1- Diagrama de Blocos Geral do Sistema

6

Page 7

3- DIAGRAMAS DE CIRCUITOS

3.1- PCI Principal - Alimentação

7

Page 8

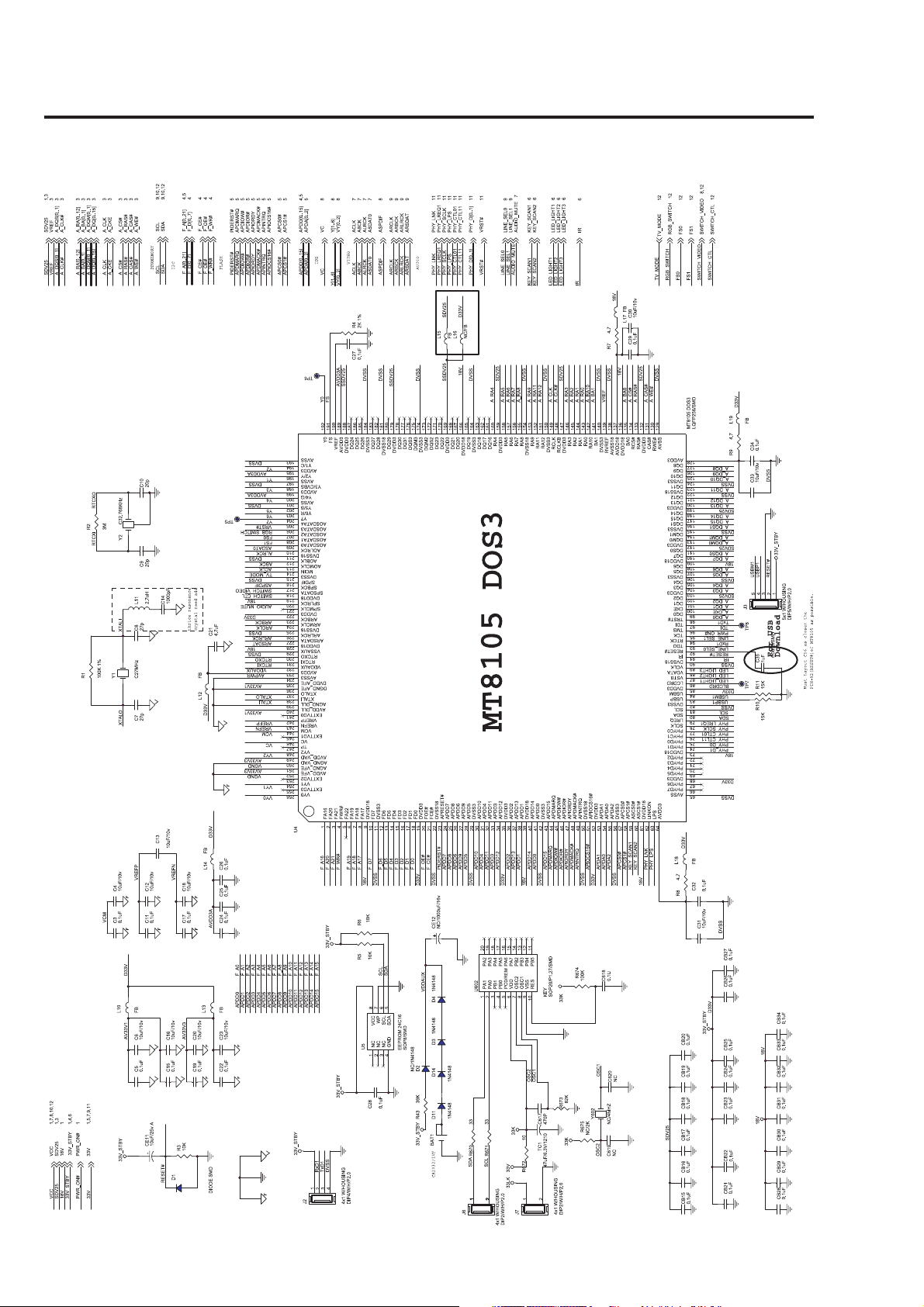

3.2 - PCI Principal - Processador MPEG

8

Page 9

3.3 - PCI Principal - Memória DDR SDRAM

9

Page 10

3.4 - PCI Principal - Memória Flash

10

Page 11

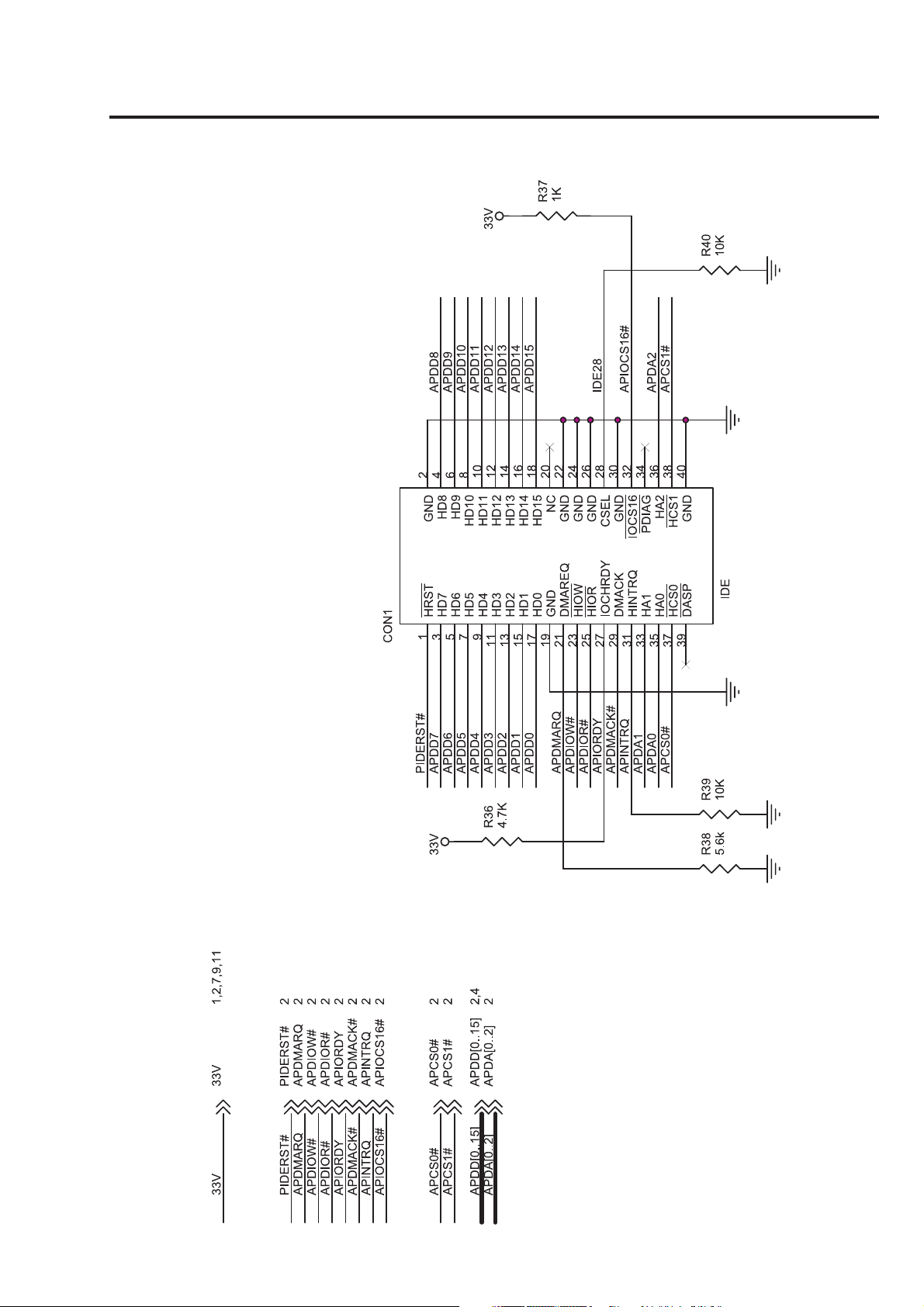

3.5 - PCI Principal - Conector IDE

11

Page 12

3.6 - PCI Principal - Conexões com Painel Frontal

12

Page 13

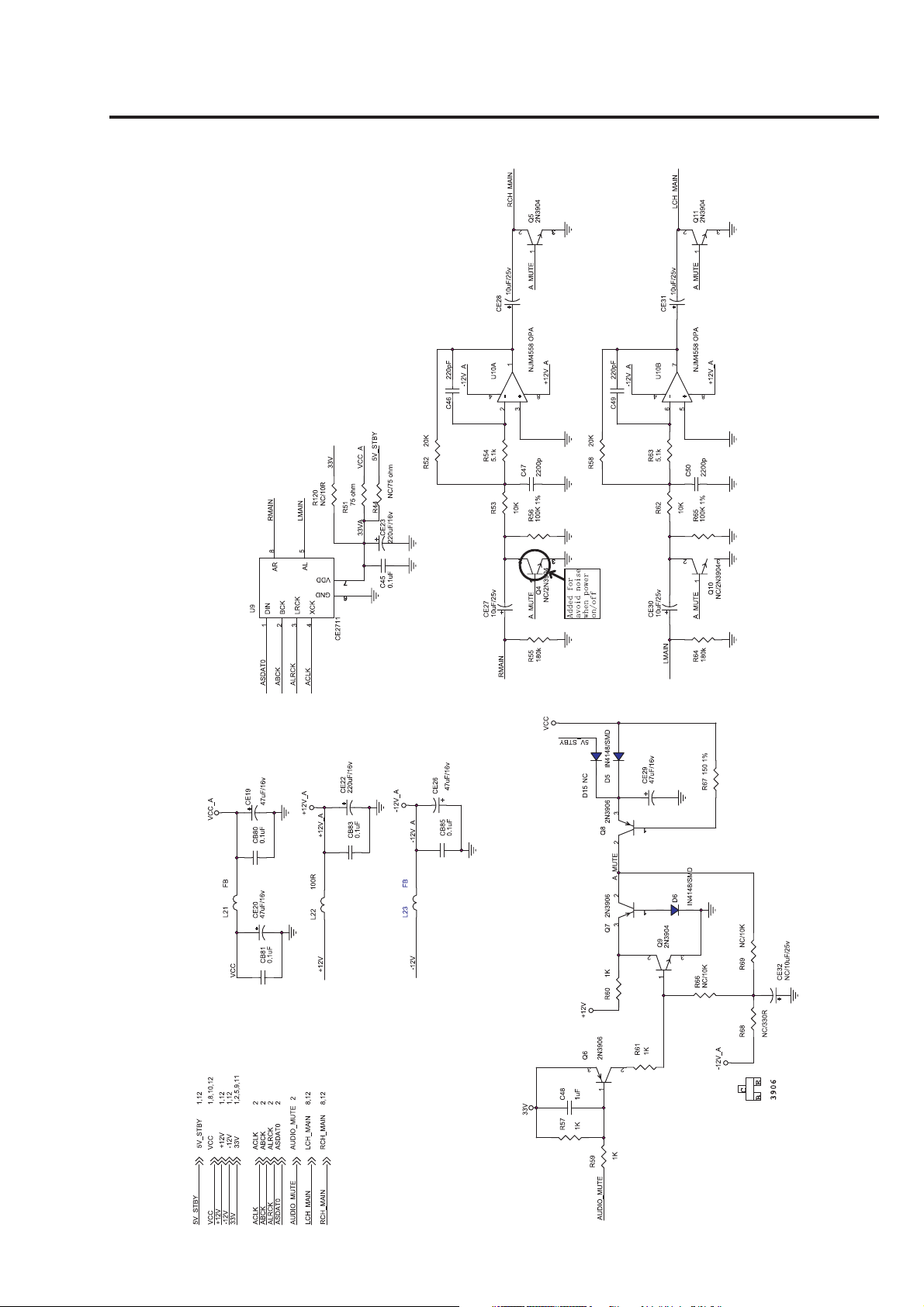

3.7 - PCI Principal - DAC de áudio

13

Page 14

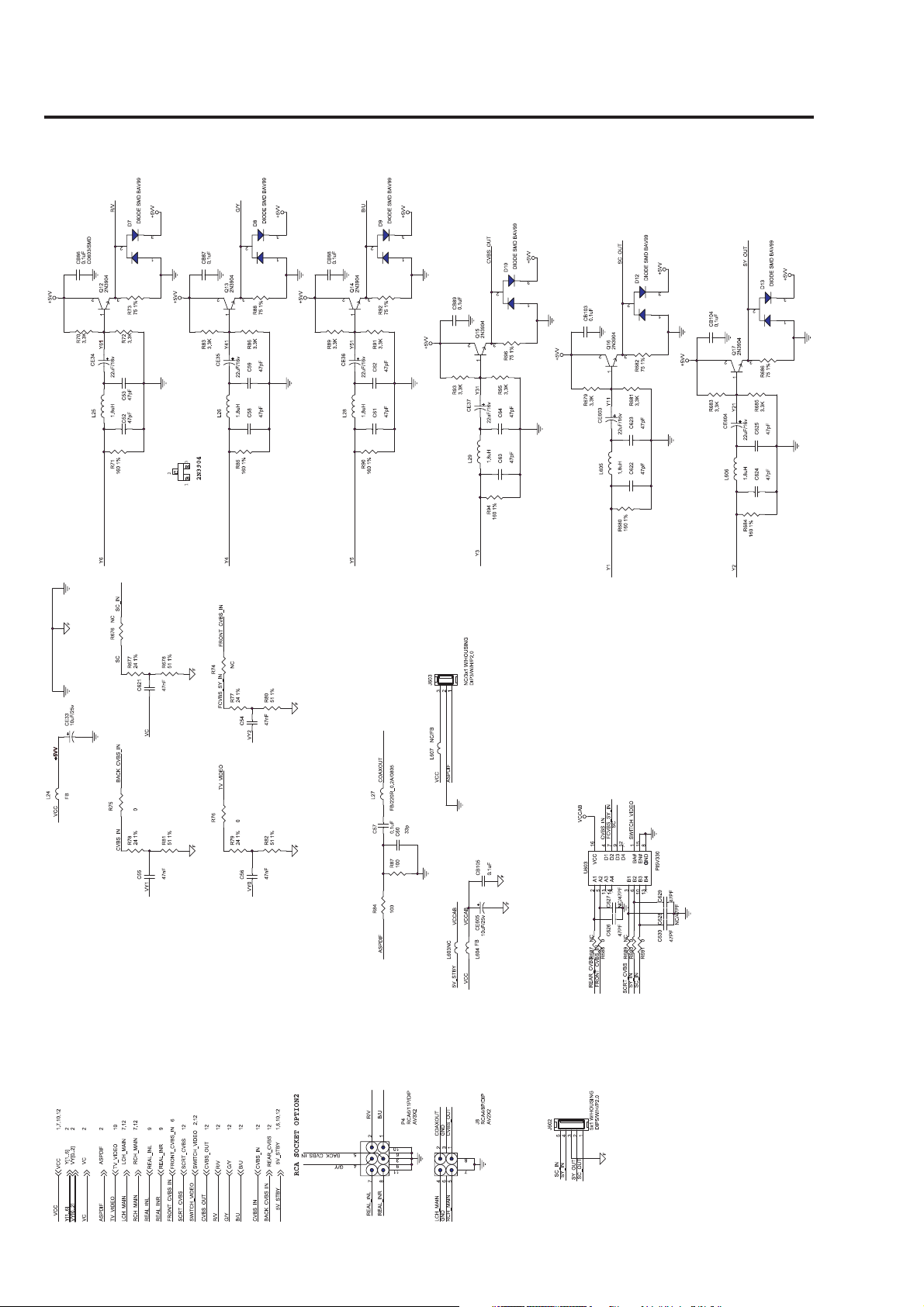

3.8 - PCI Principal - Filtro de Vídeo & SPDIF

14

Page 15

3.9 - PCI Principal - Comutação do áudio

15

Page 16

3.10 - PCI Principal - Sintonizador de TV

16

Page 17

3.11 - PCI Principal - Transceptor IEEE 1394 (DV IN)

17

Page 18

3.12- PCI Controles/Display

18

Page 19

3.13 - PCI Stand by

19

Page 20

3.14 - PCI Fonte de Alimentação (SMPS)

20

Page 21

4- LAY-OUT DAS PLACAS DE CIRCUITO IMPRESSO

4.1 - Placa de circuito impresso Fonte de Alimentação

21

Page 22

4.2 - Placa de circuito impresso - Principal

Vista superior23Vista inferior

22

Page 23

Page 24

4.3 - PCI Controles/Display & Standby

Vista Superior Vista Inferior

24

Page 25

5- PINAGEM DOS PRINCIPAIS COMPONENTES

5.1 - Processador MPEG MT8105 (U4)

Pinagem

FA16

FA20

FA2 1

FWR_

FA22

FA19

FA18

FA1 7

DVDD18

FD7

DVSS3

FD6

FD5

FD4

FD3

FD2

FD1

FD0

DVDD3

FOE_

FCE_

DVSS18

APRESET_

APDD7

APDD8

APDD6

APDD9

APDD5

DVSS3

APDD10

APDD4

APDD11

APDD3

APDD12

DVDD3

APDD2

APDD13

APDD1

DVDD18

APDD14

APDD0

DVSS3

APDD15

APDMARQ

APDIOW_

APDIOR_

APIORDY

APDMACK_

APINTRQ

DVSS18

APIOCS16_

DVDD3

APDA1

APDA0

APDA2

DVSS3

APCS0_

APCS1_

ASCS0_

ASCS1_

DVDD18

LINKON

LPS

AVDD3

EXTTVD0

VREFP

AGND_VFE

VY1

EXTTVD3

AGND_VAD

AVD D_ VFE

VY0

EXTTVD2

251

255

252

256

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

250

253

254

69

70

71

66

67

68

VCM

EXTTVD1

VY2

VREFN

TP

VC

AVDD_VAD

249

248

247

246

72

73

74

75

AVD D_ DLL

AGND_DLL

XTALI

XTALO

243

244

241

245

242

240

239

237

238

76

77

78

81

82

79

80

83

84

RTCXI

AVD D3

VDDAUX

AVSS3

DGND_AFE

236

RTCXO

DVDD_AFE

235

233

231

234

232

230

MPEG codec

85

86

89

90

87

88

91

ARLRCK

DVDD18

VSSAUX

ARSDATA

DVSS18

ARMCLK

228

227

225

226

229

224

MT8105

SOC

92

93

94

95

96

97

ARBCK

223

98

DVDD3

222

99

YUV3/CVBS

AVD D3

AVSS

AVSS

YUV5/B

YUV4/G

YUV6/R

AOSDATA2

SPDIF

SPMCLK

DVDD18

SPBCK

MCIN

DVSS3

SPLRCK

SPSDATA

219

220

218

221

100

101

102

103

AOBCK

AOMCLK

212

217

216

215

213

214

104

105

106

107

108

109

AOSDATA3

AOSDATA0

AOSDATA1

AOLRCK

DVSS18

211

110

AOSDATA4

YUV7

209

210

111

112

203

204

208

207

205

202

206

113

114

115

116

117

118

119

YUV2/C

AVDD 3

YUV1/Y

AVSS

196

195

201

199

200

121

122

120

193

194

198

197

192

YUV0/CIN

191

FS

190

VREF

189

AVDD 3

188

DVDD2

187

DQ24

186

DQ25

185

DQ26

184

DVSS2

183

DQ27

182

DQ28

181

DVSS18

180

DQ29

179

DVDD2

178

DQ30

177

DQ31

176

DQS3

175

DQM3

174

DVSS2

173

DQM2

172

DQS2

171

DQ23

170

DQ22

169

DVDD2

168

DQ21

167

DQ20

166

DVDD18

165

DQ19

164

DVSS2

163

DQ18

162

DQ17

161

DQ16

160

RA4

159

DVDD2

158

RA5

157

RA6

156

RA7

155

RA8

154

DVSS18

153

RA9

152

RA11

151

RA12

150

DVSS2

149

RCLK

148

RCLKB

147

DVDD2

146

RA3

145

RA2

144

RA1

143

RA0

142

RA10

141

BA1

140

DVSS2

139

RVREF

138

AVSS18

137

AVDD 18

136

DVDD18

135

BA0

134

RCS_

RAS_

133

132

DVDD2

131

CAS_

130

RWE_

AVSS

129

123

124

125

126

127

128

AVSS

PHYD7

PHYD6

SCL

SDA

USBP

LREQ

DVDD

PHYD5

PHYD4

PHYD3

PHYD2

SCLK

PHYD1

PHYD0

PHYC1

PHYC0

DVSS18

USBM

DVSS3

DVDD3

LCDRD

IR

VCLK

VSTB

VDATA

DVSS18

TDI

TCK

TMS

TDO

RTCK

RESET_

TRST_

DQ3

DQ4

DQ6

DQ1

DQ0

CKE

DQ5

DQ2

DVDD2

DQ7

DQS0

DVSS2

DVDD18

DQ15

DQ14

DQ12

DQ13

DQS1

DQM1

DQM0

DVSS2

DVDD2

DVDD2

DQ8

DQ9

DQ11

DQ10

DVSS2

DVSS18

AVDD3

25

Page 26

DESCRIÇÃO DOS PINOS - MT8105

Pino Símbolo Tipo Descrição

Alimentação/Terra

64,128, 189,195,199,23 AVDD3 Alimentação Alimentação Analógica 3,3V

3, 235, 240, 249, 251

65,129, 138,193,197,201, AVSS Terra Terra analógico

234, 236, 239, 250,252

137 AVDD18 Alimentação Alimentação analógica1,8V

10,19,35, 52,68, DVDD3 Alimentação Tensão de E/S Digital 3,3V

85, 222

11, 29, 42, 56, 82, 215 DVSS3 Terra Terra digital

103,112,119,132,147,159, DVDD2 Alimentação Tensão de E/S Digital de 2,5V para DDR

169, 179,188 Tensão de E/S Digital de 3,3V para SDR

106,115,124,140,150,164, DVSS2 Terra Terra Digital

174, 184

9,39,61, 73,109, 136,166, DVDD18 Alimentação Alimentação digital para circuito interno

219,228

22,50,90,122,154,181, DVSS18 Terra Alimentação digital para circuito interno

211,225

232 VDDAUX Alimentação Alimentação aux para RTC

229 VSSAUX Terra Alimentação aux para RTC

Interface de Áudio

213 AOMCLK E/S Clock mestre da saída do áudio

2 ~ 16 mA

210 AOLRCK O, SR Clock esquerdo da saída do áudio

2 mA

212 AOBCK E/S, SR Clock do bit da saída de áudio

2 ~ 16 mA

209 AOSDATA0 E/S Função múltipla

2 mA (1) Linha de dados da saída de áudio 0

(2) GPIO

208 AOSDATA1 E/S Função múltipla

2 mA (1) Linha de dados da saída de áudio 1

(2) GPIO

207 AOSDATA2 E/S Função múltipla

2 mA (1) Linha de dados da saída de áudio 2

(2) GPIO

26

Page 27

Pino Símbolo Tipo Descrição

206 AOSDATA3 E/S Função múltipla:

2 mA (1) Linha de dados da saída de áudio 3

(2) VSYN

(3) GPIO

205 AOSDATA4 E/S Função múltipla:

2 mA (1) Linha de dados da saída de áudio 4

(2) HSYN_

(3) GPIO

214 MCIN E/S Função múltipla:

2 mA (1) Microfone - Entrada

(2) GPIO

216 PDIF O, SR Audio Digital - Saída

2 ~ 16 mA

221 SPMCLK E/S Função múltipla:

2 ~ 16 mA (1) Clock mestre do SPDIF

(2) MSCLK

3) EXTRD_

(4) GPIO

220 SPLRCK E/S Função múltipla:

2 ~ 16 mA (1) Clock dos canais esquerdo-direito SPDIF

(2) SDCLK

(3) EXTWR_

(4) GPIO

217 SPBCK E/S, (PU) Função múltipla:

2 ~ 16 mA (1) Clock de bit SPDIF

(2) VSYN_

(3) FCCTL

(4) EXTINT_

(5) GPIO

218 SPSDATA E/S (PU/PD) Função múltipla:

2 ~ 16 mA (1) Linha de dados SPDIF

(2) HSYN_

(3) FCDATA

(4) GPIO

223 ARBCK E/S, SR Clock de bit de entrada da gravação de áudio

2 ~ 16 mA

224 ARMCLK E/S, SR Clock mestre de entrada da gravação de áudio

2 ~ 16 mA

226 ARLRCK E/S, SR Clock esquerdo/direito da entrada da gravação

2 mA de áudio

227 ARSDATA E/S, SR Dados seriais da entrada de gravação de áudio

2mA

Interface de Vídeo

204 YUV7 E/S Função múltipla:

2 mA (1) YUV bit de dados 7

(2) GPIO

203 YUV6/R E/S Função múltipla :

(1) Saída - Vermelho

(2) YUV bit de dados 6

202 YUV5/B E/S Função múltipla:

(1) Saída - Azul

(2) YUV bit de dados 5

200 YUV4/G E/S Função múltipla :

(1) Saída - Verde

(2) YUV bit de dados 4

198 YUV3/CVBS E/S Função múltipla :

(1) Composto - Saída

(2) YUV bit de dados 3

27

Page 28

Pino Símbolo Tipo Descrição

196 YUV2/C E/S Função múltipla:

(1) Chroma - Saída

(2) YUV bit de dados 2

194 YUV1/Y E/S Função múltipla:

(1) Luminância - Saída

(2) YUV bit de dados 1

192 YUV0/CIN E/S Função múltipla :

(1)

(2) YUV bit de dados 0

191 FS E/S Resistor externo para ajuste de escala plena do DAC de vídeo

190 VREF E/S Capacitor de desacoplamento para tensão de referência interna do

DAC de vídeo

242

243

244

256 VY0 E Função múltipla :

254 VY1 E Função múltipla :

248 VY2 E Função múltipla :

246 VC E Função múltipla:

241 EXTTVD0 E Função múltipla :

245 EXTTVD1 E Função múltipla:

253 EXTTVD2 E Função múltipla :

255 EXTTVD3 E Função múltipla :

247 TP E Função múltipla:

21 FCE_ E/S, Seleção de chip de Flash

20 FOE_ E/S, Saída de flash - habilitação

4 FWR_ E/S, Flash - write

18 FD0 E/S, Bit 0 do barramento de dados Flash

17 FD1 E/S, Bit 1 do barramento de dados Flash

16 FD2 E/S, Bit 2 do barramento de dados Flash

15 FD3 E/S, Bit 3 do barramento de dados Flash

14 FD4 E/S, Bit 4 do barramento de dados Flash

13 FD5 E/S, Bit 5 do barramento de dados flash 5

12 FD6 E/S, Bit 6 do barramento de dados flash 6

VREFP

VREFN

VCM

E/S Tensão de referência positiva para ADC de vídeo

E/S Tensão de referência negativa para ADC de vídeo

E/S Tensão de referência de modo comum para ADC de vídeo

(1) Luminância - Entrada - Canal 0

(2) entrada do CCIR externo (bit 3)

(1) Luminância - Entrada - Canal 1

(2) entrada do CCIR externo (bit 5)

(1) Luminância - Entrada - Canal 2

(2) entrada do CCIR externo (bit 7)

(1) Chroma - Entrada

(2) entrada do CCIR externo (bit2)

(1) Clock do CCIR externo

(1) entrada do CCIR externo (bit 0)

(1) entrada do CCIR externo (bit 4)

(1) entrada do CCIR externo (bit 6)

(1) Ponto de teste analógico

(2) entrada do CCIR externo (bit 1)

Interface para Flash

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

2 ~ 16 mA

28

Page 29

Pino Símbolo Tipo Descrição

10 FD7 E/S, Bit 7 do barramento de dados flash 7

2 ~ 16 mA

1 FA16 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 16 do barramento de endereços Flash

(2) ALE Baixa para extensão de Flash E373/E/S

(3) Valor de interrupção na reinicialização

1: Modo ICE

0: Modo Não-ICE

8 FA17 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 17 do barramento de endereços Flash

(2) ALE Média para extensão de Flash E373/E/S

(3) Valor de interrupção na reinicialização

1: Bit 0 do modo de teste

0: Modo normal

7 FA18 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 18 do barramento de endereços Flash

(2) ALE Alto para Flash E373

(3) Valor de interrupção na reinicialização

1: bit 1 do modo de teste

0: Modo normal

6 FA19 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 19 do barramento de endereços Flash 19

(2) RD da extensão de E/S

(3) GPIO

(4) Valor de interrupção na reinicialização

2 FA20 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 20 do barramento de endereços Flash

(2) WR da extensão de E/S

(3) GPIO

(4) Valor de interrupção na reinicialização

1: Flash E373

0: Compartilhamento de Flash a ATA

3 FA21 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 21 do barramento de Flash

(2) HSYN_

(3) GPIO

5 FA22 E/S, Função múltipla:

2 ~ 16 mA (1) Bit 21 do barramento de endereço de Flash

(2) TXD

(3) Entrada da linha de áudio

(4) GPIO

MISC

92 RESET_ E, Reinicialização

PU, SMT

238 XTALI E Cristal de 27M - Entrada

237 XTALO S Cristal de 27M - Saída

91 IV E/S Função múltipla:

2 mA (1) infravermelho - Entrada

(2) GPIO

81 SCL E/S, Função múltipla:

2 mA (1) linha de controle da interface serial

(2) GPIO

80 SDA E/S, Função múltipla:

2 mA (1) linha de controle da interface serial

(2) GPIO

89 VCLK E/S, PU Função múltipla :

2 mA (1) Clock de VFD

(2) GPIO

88 VDATA E/S, PU Função múltipla :

2 mA (1) Dados de VFD

(2) GPIO

29

Page 30

Pino Símbolo Tipo Descrição

87 VSTB E/S, PU Função múltipla :

2 mA (1) VFD strobe

(2) GPIO

86 LCDRD E/S, Função múltipla :

2 mA (1) VFD strobe

(2) RXD

(3) Entrada da linha de áudio

(4) GPIO

231 RTCXI E Cristal de 32,768K - Entrada

230 RTCXO S Cristal de 32,768K - Saída

Interface do 1394

75 PHYD0 E/S, Função múltipla :

2 ~ 16 mA (1) Bit 0 do barramento de dados 1394

(2) MSCLK

(3) GPIO

74 PHYD1 E/S, Função múltipla :

2 ~ 16 mA (1) Bit 1 do barramento de dados 1394

(2) MSBS

(3) GPIO

72 PHYD E/S (PD), Função múltipla :

2 ~ 16 mA (1) Bit 2 do barramento de dados 1394

(2) MSSDIO

(3) GPIO

71 PHYD3 E/S (PU), Função múltipla :

2 ~ 16 mA (1) Bit 3 do barramento de dados 1394

(2) SDCLK

(3) GPIO

70 PHYD4 E/S (PU) , Função múltipla

30

Page 31

5.2- Transceptor IEEE 1394 - MT8162 (U601)

Pinagem

DGND_IO

DGND

LREQ

48

DVDD

47

46

45

44XO43XI42

DVDD_IO

PLLVDD

PLLGND

41

ATE ST N

RESET_B

ATESTP

40

39

38

37

SCLK 1

CTL0 2

CTL1 3

D0 4

D1 5

D2/GPIO0 6

D3/GPIO1 7

D4/GPIO2 8

D5/GPIO3 9

D6/GPIO4 10

D7/GPIO5 11

PD 12

13

LPS

14

15

DGND

C/LINKON

MT8162

PC0/GPIO716PC1/GPIO817PC2/GPIO9

MT8162

TRANSCEPTOR DE CABO PARA UMA PORTA IEEE 1394a2000

MediaTek MT 8162 fornece a função de transceptor

para nó de uma porta em uma rede de cabo I EEE 1394a2000 incorporando um transceptor diferencial. O MT8162

suporta taxas de dados de velocidades S100, S200, e

S400. Foi projetado para fazer a interface com uma

controladora de camadas LLC. A largura do barramento

de dados da interface de LLC aumenta com a

velocidade do barramento serial - dois sinais suportam

velocidades de até 100 Mbit/s, enquanto, a velocidades

maiores, um total de dois sinais por 100 Mbit/s é

necessário. A taxa de clock dos sinais nesta interface

permanece constante em 49,152 MHz, independentemente da velocidade do barramento serial.

Durante a transmissão, os dados recebidos do LLC ficam

definidos pelo clock do sistema 49,152 MHz e são

serializados, codificados e transmitidos a 98, 304, 196,

608, ou 393, 216 Mbits/s (modo S100, S200, S400,

respectivamente). Os dados codificados são transmitidos pelo par de cabos diferenciais, e a amostragem

codificada é transmitida pelo par de cabos diferenciais

TPA. Durante a recepção, os dados são recebidos no

TPA, e a seleção é recebida no TPB. A amostragem dos

dados recebidos é decodificada para recuperar o clock

e dados seriais. Os dados seriais são combinados em

duas, quatro ou oito correntes de bits paralelas (depende

da velocidade de recepção), resincronizadas para o

clock do sistema de 49,152 MHz e enviadas ao LLC.

AGND36

AVD D35

VREF34

ATEST33

AGND32

TPBIAS31

TPA+30

TPA-29

TPB+28

TPB-27

AGND26

AVD D25

18

19

20

21

22

24

CPS

DVDD

DIRECT

TESTM_B

TEST_M0/GPIO1223TEST_M1/GPIO13

Características

• Atende às especificações da IEEE1394a-2000

• Velocidades de dados de 100, 200, 400 Mbps

• Interoperável com IEEE1394-1995 PHY e liga dispositivos

de camadas

• Suporta concatenação mutivelocidade

• Suporta reset de barramento arbitrado

• Melhoria da arbitração

• Suporta arbitração com ACK acelerado

• Atende às exigências da OHC (Open Host Controller)

• Contender programável do reset e bits de classe de

potência

• Suporta concatenação “fly-by”

• Suporta o pacote de ping PHY

• Gerenciamentos avançados de energia conforme

especificado na IEEE1394a-2000

• Suporta novos estados de porta, desabilitados e

suspensos para economizar energia

• Suporta pacote de comandos remotos para

suspender, reiniciar, desabilitar e habilitar outra porta

do PHY

• Gerenciamento de energia adicional através do PD

(desativação do chip)

• Suporta a conexão direta ou de barreira de isolação

com o o LLC

• Operação simples com fonte de alimentação de 3,3V

• Cristal de baixo custo de 24,576 MHz

• Encapsulamento LQFP de 48 pinos e baixo custo

31

Page 32

DESCRIÇÃO DOS PINOS - MT8162

Nº do Pino Símbolo Tipo Descrição

1 SCLK S Clock do Sistema

2-3 CTL0 E/S Linhas de Controle. Os sinais controlam a comunicação entre os LLC.

CTL1 Os suportes de barramento são construídos para esses sinais.

4-11 D0 E/S Linhas de dados. Sinais de dados entre o MT8162 e o LLC. Os suportes de

D1 barramento são construídos para esses sinais.

D2/GPIO0 D2~D3 podem ser usados como GPIOs no modo S100 e D4~D5 podem ser usados

D3/GPIO1 como GPIOs no modo S100/S200. Os GPIOs são controlados pelos registros GPIO_O,

D4/GPIO2 GPIO_I, e GPIO_OE.

D5/GPIO3

D6/GPIO4

D7/GPIO5

12 PD E Sinal de Ultra power-down. Todo o circuito interno, exceto os monitores ativados

por cabo se desliga declarando a entrada PD.

13 LPS E Status de Potência do Link. Indica que o link está ativo e funcional Quando o MT8162

detecta que a entrada de LPS permanece baixa por mais de 25,6us, a interface

do LLC é colocada no estado de baixa potência e a saída do SCLK fica inativa

14,47 DGND Terra digital

15 C/LINKON E/S Ao reinicializar, o valor fica definido como a entrada do contender. Após a

reinicialização, o pino funciona como o sinal LinkOn. Ele sinaliza a ocorrência do

evento link-on. A frequência deste sinal é 6MHz.

16-18 PC0/GPIO7 E/S Entradas da programação classe potência. Esses sinais estabelecem a classe de

PC1/GPIO8 potência default do PHY na reinicialização. Após a reinicialização, esses terminais

PC2/GPIO9 podem ser usados como GPIOs controlados pelos registros.

19 DIRETO E Controle de isolação da interface do link. O sinal se eleva para desativar as saídas

do diferenciador para o sinais de CTLO, CTL1, D0~D7, e LREQ.

20 CPS E Entrada do status da energia do cabo. Este terminal é normalmente ligado ao

cabo de tensão através de um resistor de 400K. Ele ativa um comparador interno

usado para detectar a situação da tensão do cabo.

21,45 DVDD VDD Alimentação do circuito digital.

22 TESTEN_B E Sinal de habilitação do modo de teste. Usado no teste de fabricação.É um sinal

baixo ativo. Para operação normal, este sinal deve ser ligado como alto

23-24 TEST_M0/ E/S Seleção do modo de teste. Esses sinais são usados no teste de fabricação.

GPIO12 Os sinais colocam o modo de teste do MT8162 em ativação mediante

TEST_M1/ reinicialização. Para a operação normal, ambos ficam ligados ao terra através de

GPIO13 resistores de 10K e podem ser usados como GPIO controlados por registradores

25, 35 AVDD VDD Alimentação do circuito analógico.

26, 36 AGND GND Terra do circuito analógico.

27 TPB- E/S Par diferencial trançado B

28 TPB E/S

29 TPA- E/S Par diferencial trançado A

30 TPA+ E/S

31 TPBIAS E/S Saída polarizada de par trançado. Este sinal fornece a tensão polarizada nominal

de 1,86V necessária para a operação adequada do transceptor de cabo de par

trançado.

32 AGND GND Terra do circuito analógico.

33 ATEST E/S Terminal de teste analógico. Este sinal é usado no teste de fabricação.

34 VREF E/S Entrada de tensão de referência analógica.

37 RESET_B E Reinicialização. E um sinal baixo ativo.

38,39 ATESTN E/S Terminal de teste analógico

ATESTP

40 PLLVDD VDD Alimentação do Circuito PLL

41 PLLGND DNG Terra do circuito PLL

42 XI E/S Entradas dos cristais. Esses terminais se ligam a um cristal de modo resonante

43 paralelo de 24,576 MHz

44 DVDD_IO VDD Alimentação de E/S Digital

46 DGND_IO DNG Terra da E/S Digital

48 LREQ E Solicitação de link. O LLC usa este sinal para indicar uma solicitação de serviço ao

MT8162. O suporte do barramento fica embutido.

32

Page 33

5.3- Memória DDR SDRAM (U6)

Pinagem

Tabela de endereços de linhas e colunas

ITENS 64Mx4 32Mx8 16Mx16

Organização Bancos de 16M x 4 x 4 Bancos de 8M x 8 x 4 Bancos de 4M x 16 x 4

Endereço de Linhas A0 - A12 A0 - A12 A0 - A12

Endereço de Colunas A0-A9, A11 A0-A9 A0-A8

Endereço do Banco BA0, BA1 BA0, BA1 BA0, BA1

Sinalizador de

Pré-carga Automático A10 A10 A10

Atualização 8K 8K 8K

33

Page 34

Descrição dos Pinos

PINO TIPO DESCRIÇÃO

CK, /CK Entrada Clock: CK e /CK são entradas de clock diferenciais. Todos os sinais de entrada de

controle e endereço são amostrados no cruzamento da borda positiva do CK e

borda negativo do /CK. Dados de saída (read) são encaminhados aos cruzamentos

de CK e /CK (ambas as direções do cruzamento).

CKE Entrada Ativação do Clock: CKE HIGH ativo, e CKE LOW desativa os sinais do clock interno, e

os buffers de entrada do dispositivo e drivers da saída. O uso do CKE LOW desativa

a PRÉ-CARGA e a operação de AUTO-ATUALIZAÇÃO (SELF REFRESH) (todos os bancos

em repouso), ou DESATIVAÇÃO ATIVA (ACTIVE POWER DOWN) (linha ATIVA em qualquer

banco). CKE é síncrono para a entrada e saída da desativação (POWER DOWN), e

para a entrada de auto-atualização (SELF REFRESH). CKE é síncrono para a saída de

auto-atualização (SELF REFRESH), e para desativação de saída. CKE deve ser mantido

alto no decorrer dos acessos de READ e WRITE. Buffers de entrada, excluindo CK, /CK

e CKE são desativadas durante a desativação (POWER DOWN). Buffers de entrada,

excluindo CKE, são desativados durante a auto-atualização (SELF REFRESH). CKE é

uma entrada SSTL_2, mas irá detectar um nível LVCMOS LOW após o VDD ser

aplicado.

/CS Entrada Seleção de Chip: Habilita ou desabilita todas as entradas, exceto CK, /CK, CKE, DQS

e DM. Todos os comandos são mascarados quando CS for registrado alto. CS

proporciona a seleção de bancos externos em sistemas com bancos múltiplos. CS é

considerado parte do código de comando.

BA0, BA1 Entrada Entradas dos Endereços dos Bancos BA0 e BA1 definem para qual banco está sendo

aplicado um comando ACTIVE, Read, Write ou PRECHARGE.

A0 ~ A12 Entrada Entradas de Endereços: Forneça o endereço da linha para os comandos ACTIVE, e

o bit de AUTO PRECHARGE e endereço de coluna para os comandos READ/WRITE e

selecione um local da memória no banco respectivo. A10 é amostrado durante um

comando de pré-carga para determinar se a pré-carga (PRECHARGE) se aplica a

um banco (A10 LOW) ou todos os bancos (A10 HIGH). Se apenas um banco tiver de

ser pré-carregado, o banco será selecionado por BA0, BA1. As entradas de

endereço também fornecem o código de operação durante um comando MODE

REGISTER SET. BA0 e BA1 definem qual registro de modo é carregado durante o

comando MODE REGISTER SET (MRS ou EMRS).

/RAS, /CAS, Entrada Entradas de Comando: /RAS, /CAS e /WE (juntamente com /CS) definem o comando

/ WE que está sendo digitado.

DM Entrada Máscara de Dados de Entrada: DM é um sinal de máscara de entrada para dados

(LDM,UDM) WRITE. Os dados de entrada são mascarados quando DM for amostrado como

HIGH juntamente com os dados de entrada durante um acesso WRITE. DM é

amostrado em ambas as bordas do DQS. Embora os pinos DM sejam apenas de

entrada, o carregamento de DM faz o casamento com o carregamento de DQ e

DQS. Para o x16, LDM corresponde aos dados no DQ0-Q7; UDM corresponde aos

dados no DQ8-Q115.

DQS E/S Amostragem de Dados: Saída com dados READ, entrada com dados WRITE. Alinhados

(LDQS,UDQS) pela borda com dados READ, centrados nos dados WRITE. Usados para capturar

dados WRITE. Para o x16, LDM corresponde aos dados no DQ0-Q7; UDQS corresponde

aos dados no DQ8Q15.

DQ E/S Entrada de dados / pino de saída: Barramento de dados

VDD/VSS Alimentação Fonte de alimentação para circuitos internos e buffers de entrada.

Elétrica

VDDQ/VSSQ Alimentação Fonte de alimentação dos buffers de saída para imunidade a ruído.

Elétrica

VREF Alimentação Tensão de referência de entradas para a interface SSTL.

Elétrica

NC NC Sem conexão.

34

Page 35

5.4 - Memória Flash (U8)

Pinagem

48 TSOP (Tipo Padrão) (12mm x 20mm)

DESCRIÇÃO DOS PINOS

SÍMBOLO NOME DO PINO

AO-A19 Entrada de Endereços

Q0-Q14 Entrada/Saída de Dados

Q15/A-1 Q15(Modo palavra)/LSB addr (Modo Byte)

CE Entrada de Habilitação do Chip

WE Entrada de Habilitação do Write

BYTE Entrada da Seleção Palavra/Byte

RESET Destravamento da Proteção do Setor/Pino de Reiniciação do Hardware

OE Entrada da Habilitação da Saída

RY/BY Saída Ready/Busy

VCC Pino da Fonte de Alimentação (2,7V-3,6V)

GND (TERRA) Pino do Terra

35

Page 36

5.5 - Conversor A-D de Áudio CE2631 (U11)

Pinagem

DESCRIÇÃO DOS PINOS

Nome do Pino Pino Nº Tipo Descrição

DGND 1 TERRA Terra digital

XCK 2 E Entrada do Clock Mestre Externo.

DOUT 3 S PD A saída de dados PCM áudio serial possui internamente um resistor pull-down

de 30K. Durante a ativação, este pino é amostrado para determinar se o

áudio serial deve operar como mestre ou escravo.

BCK 4 E/S Clock de Dados da Serial do Áudio. Entrada no modo escravo e saída no

modo mestre, dependendo do registro REG1[4].

LRCK 5 E/S Pino do clock do canal esquerdo/direito. Entrada no modo escravo e saída

no modo mestre, dependendo do registro REG1[4]

AGND 6 TERRA Terra analógico

AGND 7 TERRA Terra analógico

CAP 8 E/S Saída de tensão de referência com buffer do ADC. Deve ser ligada a um

capacitor de 22 µF em paralelo com um 0,1 µF. O nível de sinal é AVDD/2.

AGND 9 TERRA Terra analógico

VCM 10 E/S A tensão de referência deve ser ligada a um capacitor de 22 µF em paralelo

com outro de 0,1 µF, bem como dois resistores de 390Ω, um para AVDD e

outro para AGND

L0 11 E Entrada esquerda do canal analógico 0

R0 12 E Entrada direita do canal analógico 0

L3 13 E Entrada esquerda do canal analógico 3.

R3 14 E Entrada direita do canal analógico 3

L1 15 E Entrada esquerda do canal analógico 1.

R1 16 E Entrada direita do canal analógico 1

L2 17 E Entrada esquerda do canal analógico 2.

R2 18 E Entrada direita do canal analógico 2

AVDD 19 VDD Fonte de alimentação analógica de 3,3V.

N/C 20 Sem ligação interna. Pode-se ligar ao terra (GND).

MOD 21 E PD Quando MOD for ‘1’, o pino SL1 e SL0 serão o controle do multiplexador para

os canais de entrada analógica. Quando MOD for ‘0’, o barramento I2C

será usado para programar o registro interno e selecionar os canais de entrada

analógica. O pino tem um resistor pull-down interno de 30K.

SDA/SL1 22 PU de E/S Seleção do canal de entrada de hardware ou SDA do barramento I2C, SL1,

baseada no nível do pino MOD. Possui um resistor pull-up interno de 8K.

SCL/SL0 23 PU de E/S Seleção do canal de entrada de hardware ou SDA do barramento I2C, SL1,

baseada no nível do pino MOD. Possui um resistor pull-up de 30 K

DVDD 24 VDD Fonte de alimentação digital, 3,3V.

36

Page 37

CE2631

ADC de Áudio Estéreo de 4 Canais, 24 bits, 96K - 32KHz

DESCRIÇÃO

O CE2631 é um ADC (conversor digital/analógico) de

áudio estéreo de 4 entradas, formado por um circuito

integrado monolítico CMOS de sinal misto. Contém um

par de multiplexadores de 4 entradas e um conjunto de

ADCs estéreos sigma delta de 1 bit. É o ideal para

aplicações multimídia

A superamostragem do ADC é feita 128 vezes. Os dados

amostrados são então filtrados e decimados

digitalmente antes de serem enviados. Um filtro passaaltos chaveável foi também incluído para remover o

deslocamento DC (DC offset). Foi incluído também um

circuito auto-mute. Quando ativado, este circuito

remove o ruído de chiado de baixo nível. O ADC utiliza

arquitetura Σ

∆ de 4 ordens. O conversor Σ ∆ de 1 bit

oferece uma linearidade diferencial superior com um

mínimo de distorção que possa ser causada por

componentes com problemas de compatibilidade e

uma alta tolerância a clock jitter. Além disso, inclui um

circuito mute de emudecimento que pode ser

selecionado. O filtro digital interno tem uma largura de

banda de 20K. Este filtro suporta freqüências de

amostragem de até 96 Khz e, com 1 vrms de entrada,

cobre toda a escala digital. Valores maiores que a escala

total serão cortados.

CARACTERÍSTICAS

• ADC de Áudio Estéreo.

- 96dB SNR (A Ponderado).-

- Relação 72 dB THD + N (A Ponderado).

- Taxas de amostragem de 32K - 96 KHz.

- Separação de canais de 91 dB.

- Auto mute

• Chaves Estéreo de 4 Entradas.

2

S, Formatos I/F Digitais Justificados à Esquerda e

•I

Direita.

• Interface de Controle Serial de 2 vias ou Seleção de

Entradas Cabeadas

• Fonte de Alimentação de 3,3V.

Aplicações

• Som “Digital Surround” para Home Theater

• Receptor AV

• Áudio para carro

Desempenho do CE2631

Item ESPECIFICAÇÕES DE DESEMPENHO DO ADC Espec.

1 Nível Máximo de Entrada 4 Vpp

2 Nível de Entrada de Áudio 0 dB 1 Vrms

3 Largura de Banda de Áudio 20Hz - 20 KHz +/- 0.5 dB

4 SNR (Weight A) >96 dB

5 Distorção Harmônica Total (THD) + Ruído (Weight A, entrada 0 dB) < -72 dB

6 Faixa Dinâmica 89 dB

7 Separação de Canais < -90 dB

8 Distorção Não Linear < 0,5 dB

9 Erro de Ganho do Canal < 0,5 dB

37

Page 38

5.6 - Conversor D-A de Áudio CE2711 (U9)

PINAGEM

Descrição dos pinos

NOME

DO PINO

DIN 1 E Entrada de Dados do Áudio Serial

BCK 2 E Clock de Dados da Serial do Áudio.

LRCk 3 E Pino do Clock do Canal Esquerdo/Direito. Para o modo justificado

XCK 4 E Entrada do clock mestre.

AL 5 S Saída analógica do canal esquerdo

GND 6 TERRA (GND) Terra

VDD 7 +3,3V Fonte de alimentação analógica de 3,3V.

AR 8 S Saída analógica do canal direito

PINO Nº TIPO DESCRIÇÃO

à esquerda, um SF alto indica Dados do Canal Esquerdo, um SF

baixo indica Dados do Canal Direito. Para o modo justificado à

esquerda, um SF alto indica Dados do Canal Esquerdo, um SF

baixo indica Dados do Canal Direito.

38

Page 39

CE271X

DAC de Áudio Estéreo, 24 bits, 192kHz

DESCRIÇÃO

O CE271X é um conversor digital analógico de áudio

estéreo formado por um circuito integrado monolítico

CMOS de sinal misto. Contém um DAC sigma delta dual

multibit. O sistema consiste de filtros de interpolação de

128 vezes, moduladores de 3

a

ordem multibit Σ ∆ ,

capacitores de comutação e filtros de reconstrução

analógica. O conversor multibit Σ ∆ oferece alta

tolerância a clock jitter e linearidade.

O CE271X suporta a conversão de dados de 32K para

192KHz. Este chip opera com tensão de 3,3V para reduzir

o consumo de energia e o ruído causado pelo

chaveamento do circuito digital interno. O CE271X é

ideal para tocadores de DVD, receptor de AV e

aplicações em decodificadores de TV a cabo.

O CE271X usa encapsulamento SOIC de 8 pinos 150 mm.

Exige um mínimo de componentes externos, sendo a

escolha ideal para aplicações de baixa potência e com

pouca disponibilidade de espaço.

CARACTERÍSTICAS

• DAC para Áudio Estéreo.

-100 dB SNR (A Ponderado)

- Relação THD + Ruído (A Ponderado).

- Taxas de Amostragem: 32K - 192 KHz.

- Filtros de Reconstrução no Chip.

• Fonte de Alimentação de 3,3V. Ideal para aplicações

portáteis.

2

S Formato de Entrada Digital (CE2711)

•I

• Formato de Entrada Digital Justificado à Direita

(CE2712).

Aplicações

• Som “Digital Surround” para Home Theater.

• Tocador de DVD.

• Áudio para Carro

• CD Portátil

• DVB, Decodificador para TV a cabo

Desempenho do DAC

Item ESPECIFICAÇÕES DE DESEMPENHO Espec.

1 Nível de Saída de Áudio (Vdd= 3,3 volt) 1,0 Vrms

2 Largura da Banda de Áudio 20Hz - 20 KHz +/- 0,04 dB

3 SNR (Weight A) >100dB

4 THD + Ruído (0dB, Weight A) <84 dB

5 Faixa Dinâmica (Weight A) 90 dB

6 Separação de Canais < -90 dB

7 Distorção Não Linear < 0,25 dB

8 Erro de Ganho do Canal < 0,1 dB

39

Page 40

5.7 - Sintonizador JS-6SNF/13F2-F2

CARACTERÍSTICAS

• Sistema PLL

• Sistema Padrão NTSC-PAL-M/N

• Canais fora do ar, cabo de banda plena

• Alimentação +5V

40

Page 41

1. Sistema Receptor: NTSC/PAL-M/N

2. Condições de Uso e Teste

CONDIÇÕES DE USO CONDIÇÕES DE TESTE

Temperatura -10 ~+60°C 25±5ºC

Umidade Relativa <95% 60±15%

Atmosfera 86 ~106kPa 86 ~ 106kPa

3. Impedância de entrada 75Ω Desbalanceada

4. Condições de Trabalho

TERMINAL Nº. NOME DO TERMINAL TENSÃO

1 VCC 5V

2 BT ABERTO

3 VCC1 5,0V (MAX 150mA)

4 SCL

5 SDA

6AS

7NC

8NC

9NC

10 NC

11 Segundo SIF

12 Saída de Vídeo

13 VCC2 5,0v (MAX 170mA)

14 Saída de Áudio Circuito RC interno

Tabela 1

Tabela 2

5. Desempenho do divisor de antena de RF –entrada para RF-saída

Ganho: 1,5dB (tipo) (min. 0,5 dB) VCC1

2,5dB (tipo) (max. -3,5 dB) VCC1

6. Faixa de freqüências

Tabela 3

FAIXA FREQÜÊNCIA (MHz)

VHF Baixo 55~160MHz

VHF Alto 155~442MHz

UHF 442~801,25MHz

7. Freqüências Intermediárias

Tabela 4

PIF 45,75 MHz

CIF 42,17 MHz

SIF 41,25 MHz

8. Dados Elétricos (Para a Seção do Sintonizador:)

Temperatura Ambiente: 25±5°C

Umidade Relativa: 60±15%

Tensão de Alimentação: 5V±0,25V

Impedância de Entrada: 75Ω Desbalanceado

Faixa de Cobertura de Freqüências do Oscilador Local 2MHz ( 5 )

A faixa min. ajustável das freqüências locais, incluindo todas as freqüências dos canais altos - baixos, freq. local

nominal de cada faixa e as extremidades, fica acima de 2MHz (veja a tabela 5)

Tabela 5

Faixa Canal Faixa de cobertura

das freqüências do oscilador local

VHF Baixo 55~160MHz 98,75~207,75MHz

VHF Alto 155~442MHz 198,75~489,75MHz

UHF 442~801,25MHz 485,75~849MHz

41

Page 42

6- FORMAS DE ONDA

Y1 27MHz

Y601 24.576Mhz

Y2 32.769K

RESET SYSTEM (U4 92PIN)

COAXIAL

CVBS

42

Page 43

Y

Pb

Pr

AUDIO ALRCLK

AUDIO ACK

AUDIO ABCK

43

Page 44

AUDIO DATA

44

Page 45

7- VISTA EXPLODIDA

7.1 - Aparelho

45

Page 46

8- LISTA DE COMPONENTES

8.1 - Mecânicos

Observação importante: A tabela à seguir apresenta-se ordenada alfa numericamente em função da

posição do componente. Alguns componentes, ainda que eletromecânicos ou elétricos, aparecem

nesta tabela em função de sua presença na "Vista Explodida" deste manual.

Posição N.E. Descrição

1 208530 TAMPA SUPERIOR RX38D, PINTADA

2 208594 PCI FONTE SDRX38D MONTADA

3 208512 MECANISMO LP-9871H3S2-BH MONT

4 208601 PCI PRINCIPAL SDRX38D MONTADA

4A 208585 PCI S-VIDEO RX38D MONTADA

5 208790 PAINEL FRONTAL SDRX38D MONT

5A 208399 PAINEL FRONTAL RX38D C/ SERIG

5B 208406 TECLAS FUNÇÕES, DE PLASTICO

5C 208415 TECLA STANDBY/ON, DE PLÁSTICO

5D 208424 VISOR FRONTAL SDRX38D C/ SERIG

5E 208433 PCI CONTROLES/DISPLAY, MONTADA

5F 208442 PCI STANDBY/ON, MONTADA

6 208549 CHASSI METALICO INF SDRX38D

6A 190692 PÉ BORRACHA 17X17X3MM

7 208521 PORTA DVD REC C/ GRAFISMO

13 205506 TAMPA TRASEIRA C/ IMPRESSAO

AE301 205472 CAIXA EMBALAGEM

AE302 205481 CALÇO DIREITO (POLPA)

AE303 205490 CALÇO ESQUERDO (POLPA)

AE309 208638 MANUAL INSTRUÇÃO SDRX38D

46

Page 47

8.2 - Eletro-eletrônicos

NOTA DE SEGURANÇA: As partes marcadas com o símbolo possuem características especiais importantes para segurança. Antes de substituir qualquer

um desses componentes, certifique-se que o está fazendo apenas por componentes com as mesmas características. Não comprometa a segurança do

produto pela utilização de componentes duvidosos durante o serviço.

Tabela de tolerâncias:

Símbolo F G J K M N Z P Símbolo C D

% ± 1 ± 2 ± 5 ± 10 ± 20 ± 30 -20 +80 0 +100 pF ± 0,25 ± 0,5

Observação importante: A tabela à seguir apresenta-se ordenada alfa-numericamente em função da posição do componente.

Posição N.E. Descrição

AE305 208610 CONTROLE REMOTO DVD3180

AE324 208451 CABO RF F-F 75OHM, 1.5M

AE361 156958 CABO AUDIO L=1,5M C/ PLUG

AE362 156967 CABO VIDEO L=1,5M C/ PLUG

BAT1 226262 BATERIA CR2032/1VG 3V

C2 226413 CAP CERA 103 M 1KV Y5V RG050

C6 226413 CAP CERA 103 M 1KV Y5V RG050

CN1 208503 CABO FORCA 2VIAS 1,5M C/ CONEC

CN1 226440 CONECTOR 2P 8MM VH3A2T

CN1 226583 CONECTOR C/ CABO 7P 120MM

CN2 226570 CONECTOR CABO BLIND 6P 150MM

CN3 226455 CONECTOR C/ CABO 4P 60MM

CN3 226556 CONECTOR C/ CABO 4P 170MM

CN4 208488 CONECTOR 3V C/ CABO 360MM CJ

CN4 226468 CONECTOR 3P 2.54MM RAD

CN4 226565 CONECTOR C/ CABO 4P 195MM

CN5 208479 CONECTOR 6V C/ CABO 360MM CJ

CN5 226495 CONECTOR 4P 2.0MM RAD

CN6 226473 CONECTOR 6P 2.54MM RAD

CON1 226235 CONECTOR 2X20 2.54MM ATAPI

CP1 226543 TOMADA AV3-8.4-6A-A RCA 3X1

CP2 226538 TOMADA 4P RV-ST4D-F16N-D16 DIP

CX1 226400 CAP PMET 104 K 275V X2 150

CY1 226397 CAP CERA 222 M 400V Y1 100K

D1 226333 DIODO RET 1N4007 DO204AL-TB

D10 226075 DIODO RET BAV99 SOT23 08180

D10 226315 DIODO SCH 1N5822 DO201AD-B

D11 226333 DIODO RET 1N4007 DO204AL-TB

D12 226333 DIODO RET 1N4007 DO204AL-TB

D2 226333 DIODO RET 1N4007 DO204AL-TB

D3 226333 DIODO RET 1N4007 DO204AL-TB

D4 226333 DIODO RET 1N4007 DO204AL-TB

D5 226342 DIODO SCH FR107 DO204AL-TB

D6 226351 DIODO SCH FR104 DO204AL-TB

D7 226075 DIODO RET BAV99 SOT23 08180

D7 226351 DIODO SCH FR104 DO204AL-TB

D8 226075 DIODO RET BAV99 SOT23 08180

D8 226324 DIODO SCH HER303 DO201AD-B

D9 226075 DIODO RET BAV99 SOT23 08180

D9 226315 DIODO SCH 1N5822 DO201AD-B

F1 226482 FUSI FILA T 2A 250V 150

IC1 226286 CIRC INT TOP244PN DIP8

IC2 226388 CIRC INT LTV-817-CN DIP4

IC3 226277 CIRC INT AZ431AZ-BTRE1 TO92

IR1 226501 RECEPTOR REMOTO PIC-427LM

J1 226155 CONECTOR 3P 2.54MM RAD

J4 226173 CONECTOR 7P 2.0MM RAD

Posição N.E. Descrição

J5 226191 CONECTOR 4P 2.0MM RAD

J601 226188 CONECTOR 6P 2.0MM RAD

J602 226204 CONECTOR 3P 2.0MM RAD

J8 226217 TOMADA RX-4013K RCA 4X1

J9 208497 CONECTOR 40V C/ CABO 280MM CJ

LED1 226529 DISPLAY LED ZDC-G40C02YGB-15

LF1 226437 FILTRO LINHA LB1025-8433 UT-20

P4 226226 TOMADA RX-6013P RCA 6X1

PWR1 226164 CONECTOR 6P 2.54MM RAD

Q1 226360 TRANS 2N5551 TO92 PACK5

Q11 226084 TRANS 2N3904 SOT23 08180

Q12 226084 TRANS 2N3904 SOT23 08180

Q13 226084 TRANS 2N3904 SOT23 08180

Q14 226084 TRANS 2N3904 SOT23 08180

Q15 226084 TRANS 2N3904 SOT23 08180

Q2 226299 CIRC INT KIA78R12PI TO220

Q3 226306 TRANS AP40N03GP TO220 L2525

Q5 226084 TRANS 2N3904 SOT23 08180

Q6 226093 TRANS 2N3906 SOT23 08180

Q7 226093 TRANS 2N3906 SOT23 08180

Q8 226093 TRANS 2N3906 SOT23 08180

Q9 226084 TRANS 2N3904 SOT23 08180

SW1 190117 CHAVE TACT 6*6*5 AXIAL 12V

T1 226428 TRAFO FORCA KB1025-8616A EEL25

TU1 226066 SINTONIZADOR JS-6SNF/13F2-F2

U1 225955 CIRC INT AZ1117-1.8V TO223 SMD

U1 226510 CIRC INT AP6928 SOP28

U10 226020 CIRC INT NJM4558 SOP8 SMD

U11 225973 CIRC INT CE2631 TSSOP28

U2 225968 CIRC INT AZ1117-2.5V TO223 SMD

U3 225940 CIRC INT LT1084 TO263

U4 226011 CIRC INT MT8105 DOS3 QFP256

U5 225995 CIRC INT ATMEL24C16 SOP8 SMD

U6 226002 CIRC INT HY5DU561622CT TSOP66

U601 226039 CIRC INT MT8162 TQFP48

U603 226057 CIRC INT PT2328-X QSOP16

U7 226048 CIRC INT LP2996 SOP8 SMD

U8 225937 CIRC INT MBMZPDL160BE TSOP48

U9 225986 CIRC INT CE2711 SOIC16 SMD

Y1 226100 CRISTAL 27MHZ +-30PPM 20PF

Y2 226146 CRISTAL 32.768KHZ

Y601 226119 CRISTAL 24.576MHZ +-20PPM 20PF

ZD1 226379 DIODO ZEN BZX55C12V-TB 1/2W

47

Page 48

SEMP TOSHIBA

Administração Geral:

Av. João Dias, 2476 - CEP 04724-003 - São Paulo - SP

PABX (0xx11) 5645-2100

NE 738802

Rev. A - Jun. / 07

48

Loading...

Loading...