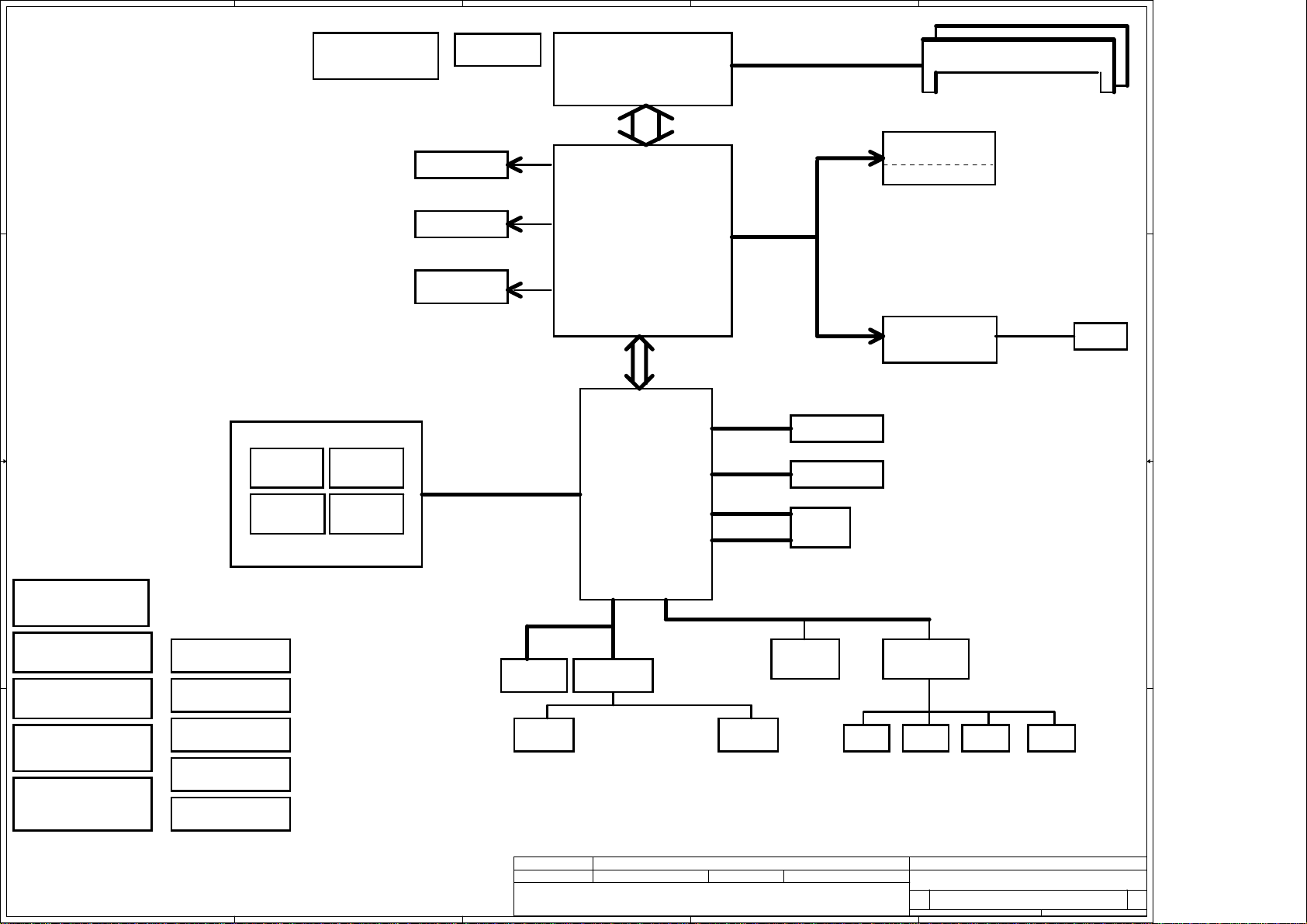

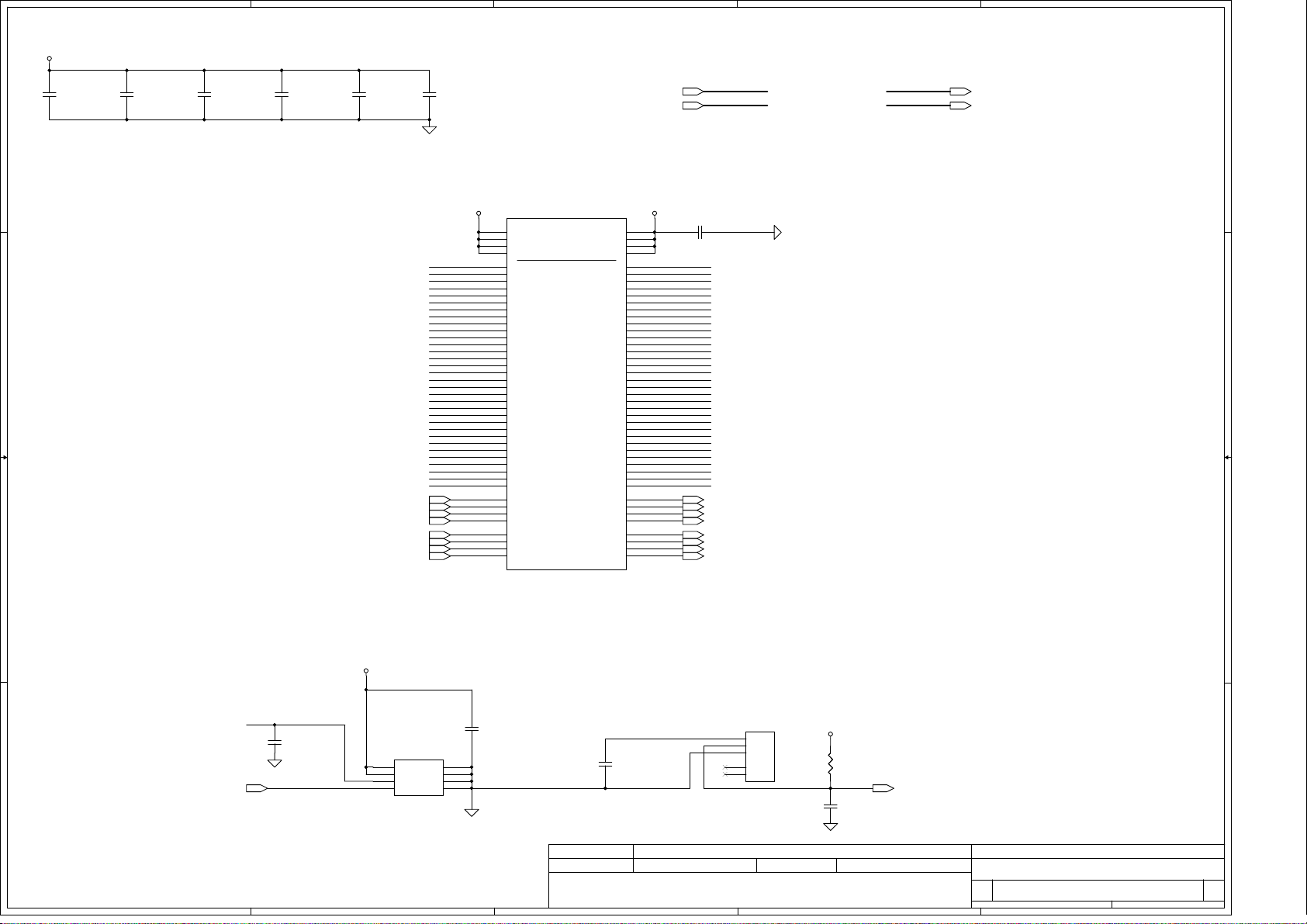

Toshiba Satellite L670D, SATELLITE L675D AMD Schematic

A

1 1

B

C

D

E

Compal confidential

2 2

Hamburg 10AD

NALAE LA-6053P Schematics Document

Mobile AMD S1G4/ RS880M / SB820M

3 3

2009-02-04 Rev. 0.2

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

142Wednesday, May 19, 2010

142Wednesday, May 19, 2010

142Wednesday, May 19, 2010

E

B

B

B

of

of

of

A

B

C

D

E

Compal Confidential

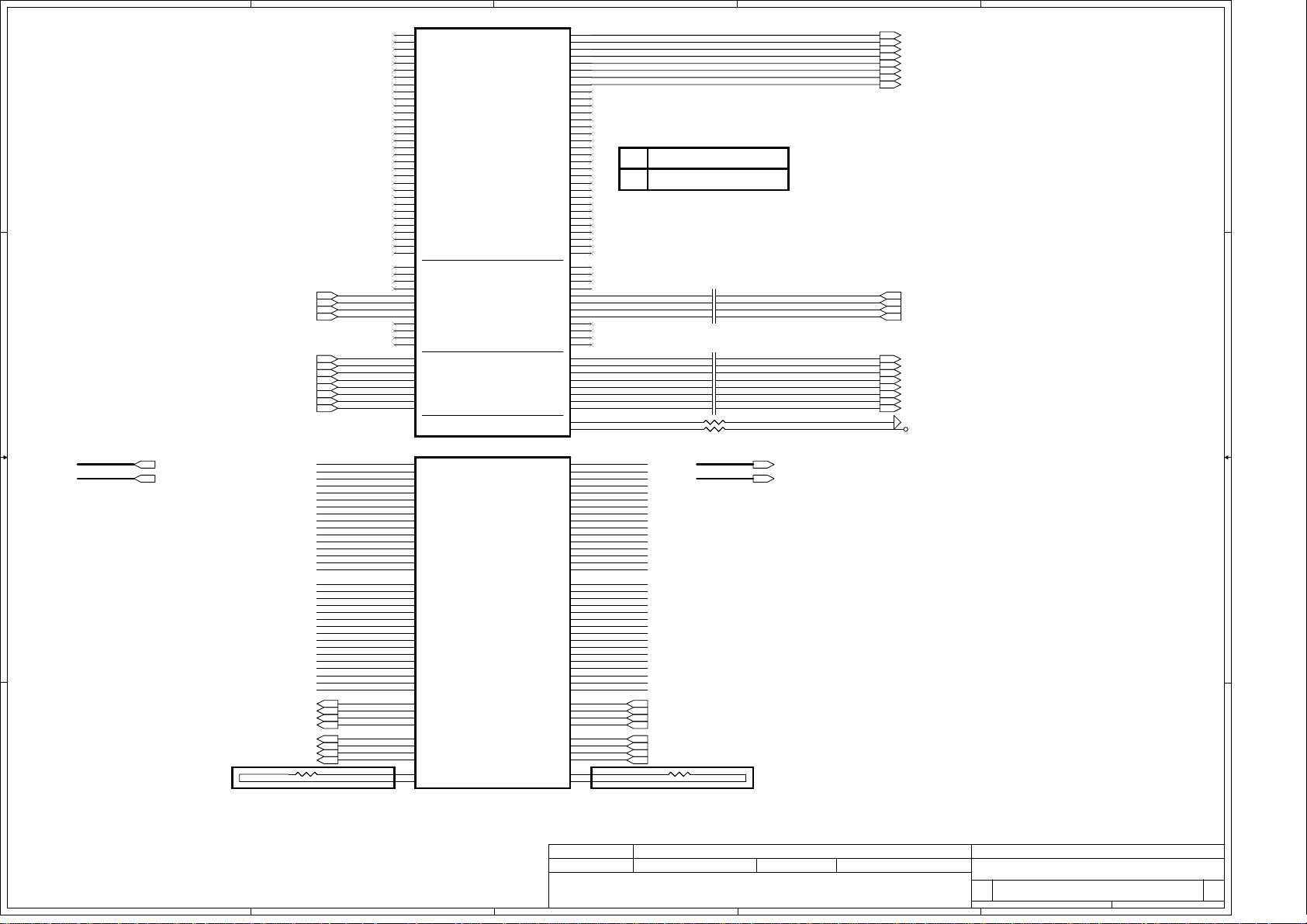

Model Name : NALAE

File Name : LA-6053P

1 1

Thermal Sensor Fan Control

ADM1032ARMZ

page 7

CRT

page 5

page 17

AMD S1G4 CPU

uFCPGA-638 Package

page 5,6,7,8

Hyper Transport Link 2.6GHz

16X16

AMD

LCD Conn.

page 18

HDMI Conn.

page 19

2 2

A-Link Express II

RS880M

page 11,12,13,14,15

Memory BUS(DDRIII)

Dual Channel

1.5V DDRIII 1066/1333MHZ

PCIe 4x

1.5V 2.5GHz(250MB/s)

200pin DDRIII-SO-DIMM X2

BANK 0, 1, 2, 3

PCI-e Mini Card WLAN

USB Port 8

RTL 8105E 10/100M

PCIe Port 2

page 28

PCIe port 3

page 26

page 9,10

RJ45

page 26

4X PCI-E

SATA port 0

5V 1.5GHz(150MB/s)

AMD

page 28

page 28

Card Reader

USB port 5

page 27

Int. Camera

USB port 9

page 18

USB

5V 480MHz

SB820M

page 20,21,22,23,24

SATA port 1

5V 1.5GHz(150MB/s)

SATA port 3

5V 1.5GHz(150MB/s)

USB port 2

5V 480MHz

USB/B

USB port 0,1

BT conn

USB port 6

3 3

SATA HDD

page 25

SATA ODD

page 25

eSATA

page 25

Clock Generator

3.3V 24.576MHz/48Mhz

SLG8SP626

RTC CKT.

Power On/Off CKT.

DC/DC Interface CKT.

Power Circuit DC/DC

4 4

page 35,36,37.38,39

40,41

page 16

page 20

page 33

page 34

ODD/B

Page 25

Power/B

Page 33

Audio & USB/B

Page 33

LED/B

Page 33

Touch Pad/B

Page 33

Debug Port

page 32

Int.KBD

page 32

LPC BUS

3.3V 33 MHz

ENE KB926 D3

page 31

HD Audio

SPI ROM

page 32

Int.

MIC CONN

page 18

HDA Codec

ALC259Q

MDC 1.5 Conn

page 32 page 29

MIC CONN

page 30

HP CONN

page 30

SPK CONN

page 30

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2008/04/14 2009/04/14

2008/04/14 2009/04/14

2008/04/14 2009/04/14

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

242Wednesday, May 19, 2010

242Wednesday, May 19, 2010

242Wednesday, May 19, 2010

E

B

B

B

of

of

of

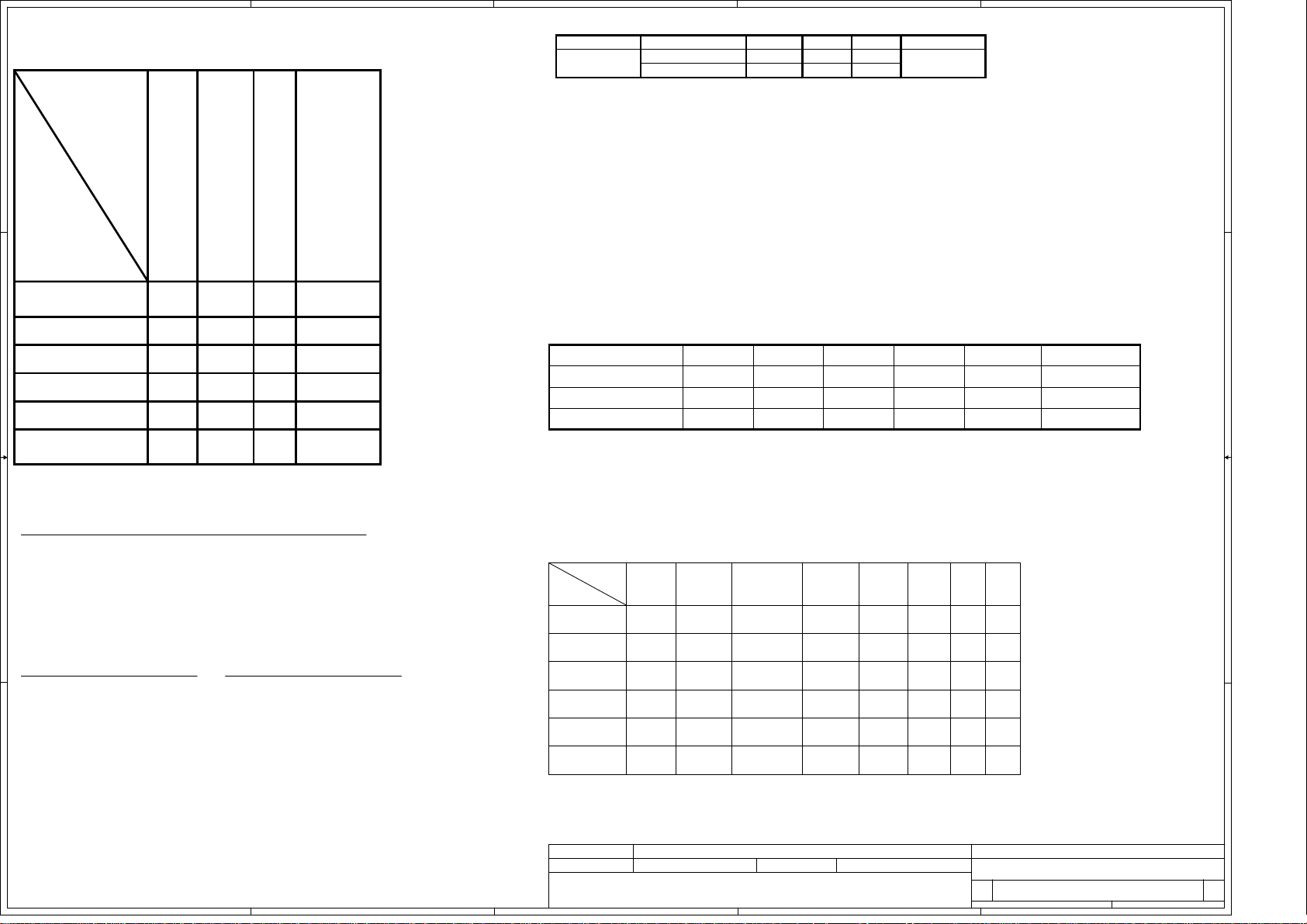

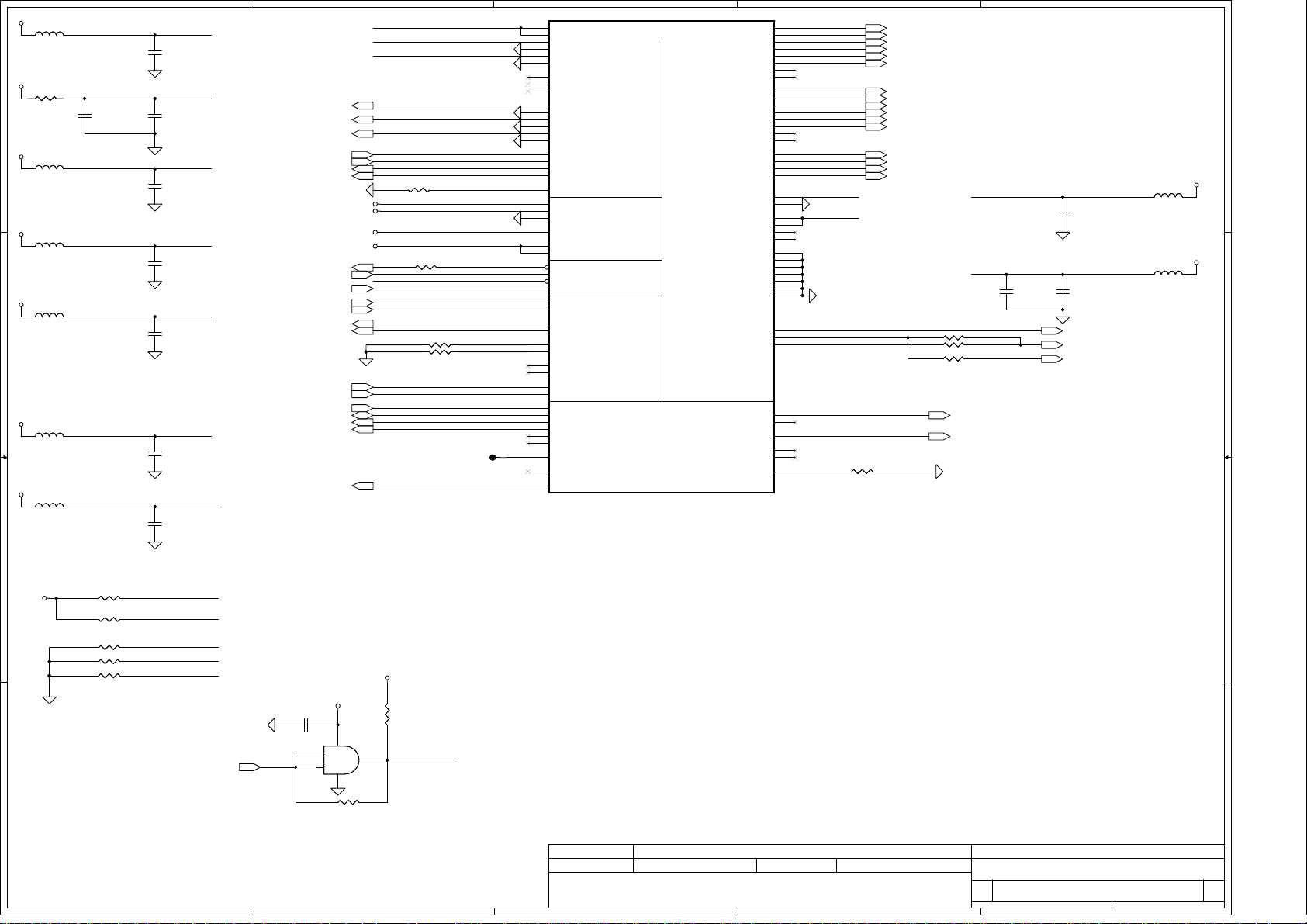

5

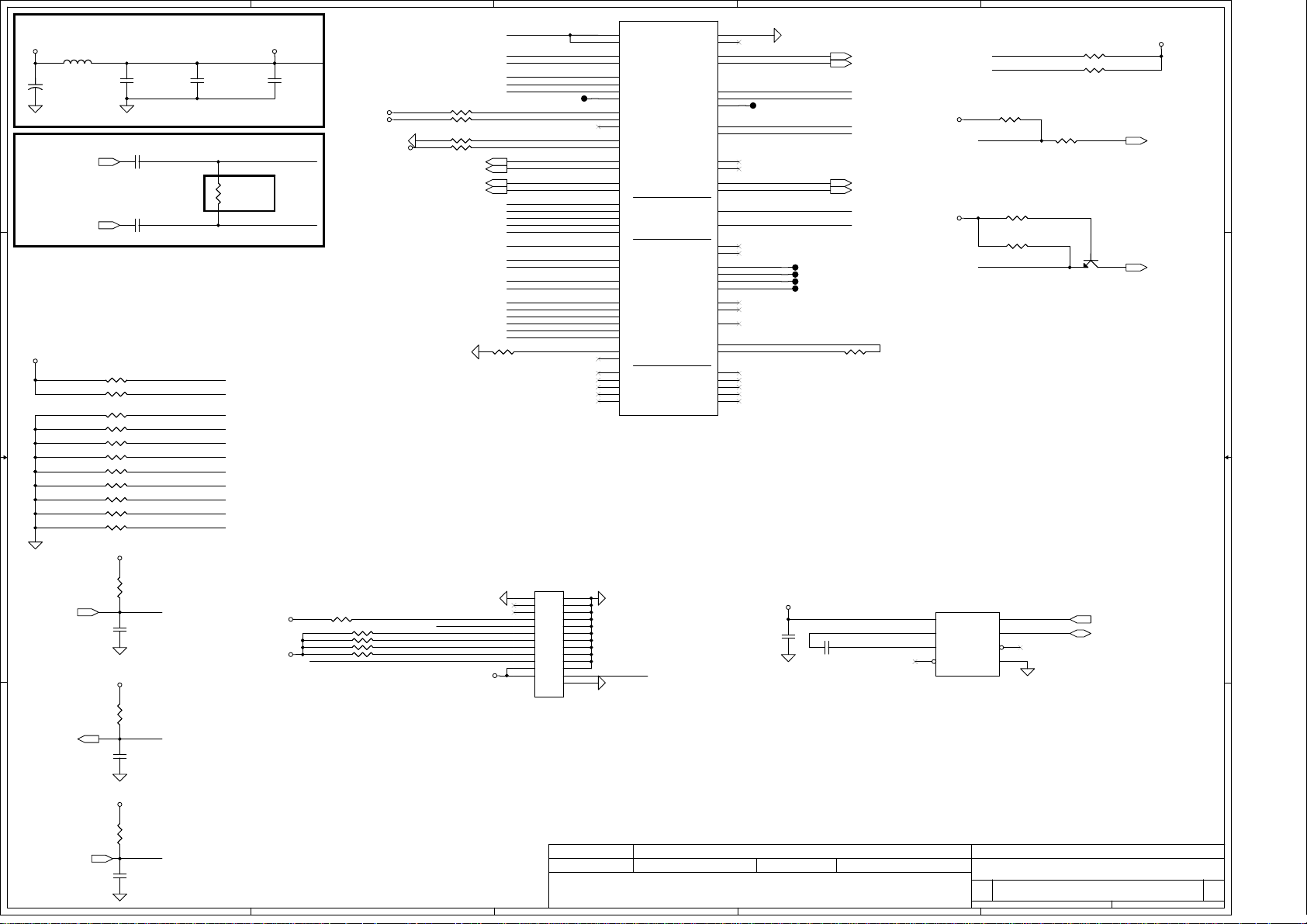

B+

D D

4

RT8205EGQW

3

Ipeak = 5A, Imax = 3.5A, Iocp_min = 7.7A

Ipeak = 5A, Imax = 3.5A, Iocp_min = 7.9A

SUSP

N-CHANNEL

2

DESIGN CURRENT 0.1A

DESIGN CURRENT 0.1A

DESIGN CURRENT 5A

DESIGN CURRENT 5A

DESIGN CURRENT 2A

1

+3VL

+5VL

+3VALW

+5VALW

+5VS

SI4800

SUSP#

MP2121DQ

DESIGN CURRENT 2.5A

+1.8VS

WOL_EN#

P-CHANNEL

DESIGN CURRENT 330mA

+3V_LAN

AO-3413

SUSP

N-CHANNEL

SI4800

C C

NALAE Hamburg AMD UMA

ENVDD

P-CHANNEL

AO-3413

BT_PWR#

P-CHANNEL

DESIGN CURRENT 1.5A

DESIGN CURRENT 1A

DESIGN CURRENT 180mA

+3VS

+LCD_VDD

+BT_VCC

AO-3413

POK

RT8209BGQW

APL5508

Ipeak = 12A, Imax = 8.4A, Iocp_min = 18.7A

VLDT_EN#

N-CHANNEL

DESIGN CURRENT 300mA

DESIGN CURRENT 12A

DESIGN CURRENT 3.5A

+2.5VS

+1.1VALW

+1.1VS

IRF8113

B B

VR_ON

N-CHANNEL

IRF8113

Ipeak = 36A, Imax = 25.2A, Iocp_min = 54A

ISL6265A

VLDT_EN#

DESIGN CURRENT 6A

DESIGN CURRENT 36A

DESIGN CURRENT 4A

+NB_CORE

+CPU_CORE0

+VDDNB

SYSON

RT8209BGQW

Ipeak = 7.5A, Imax = 5.25A, Iocp_min = 8.7A

SUSP

N-CHANNEL

DESIGN CURRENT 7.5A

DESIGN CURRENT 1A

+1.5V

+1.5VS

IRF8113

SUSP

APL5331KAC

DESIGN CURRENT 1A

+0.75VS

VR_ON#

A A

5

4

APL5331KAC

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Compal Secret Data

Compal Secret Data

DESIGN CURRENT 1.5A

Deciphered Date

Deciphered Date

Deciphered Date

+1.05VS

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

342Wednesday, May 19, 2010

342Wednesday, May 19, 2010

342Wednesday, May 19, 2010

1

B

B

B

of

of

of

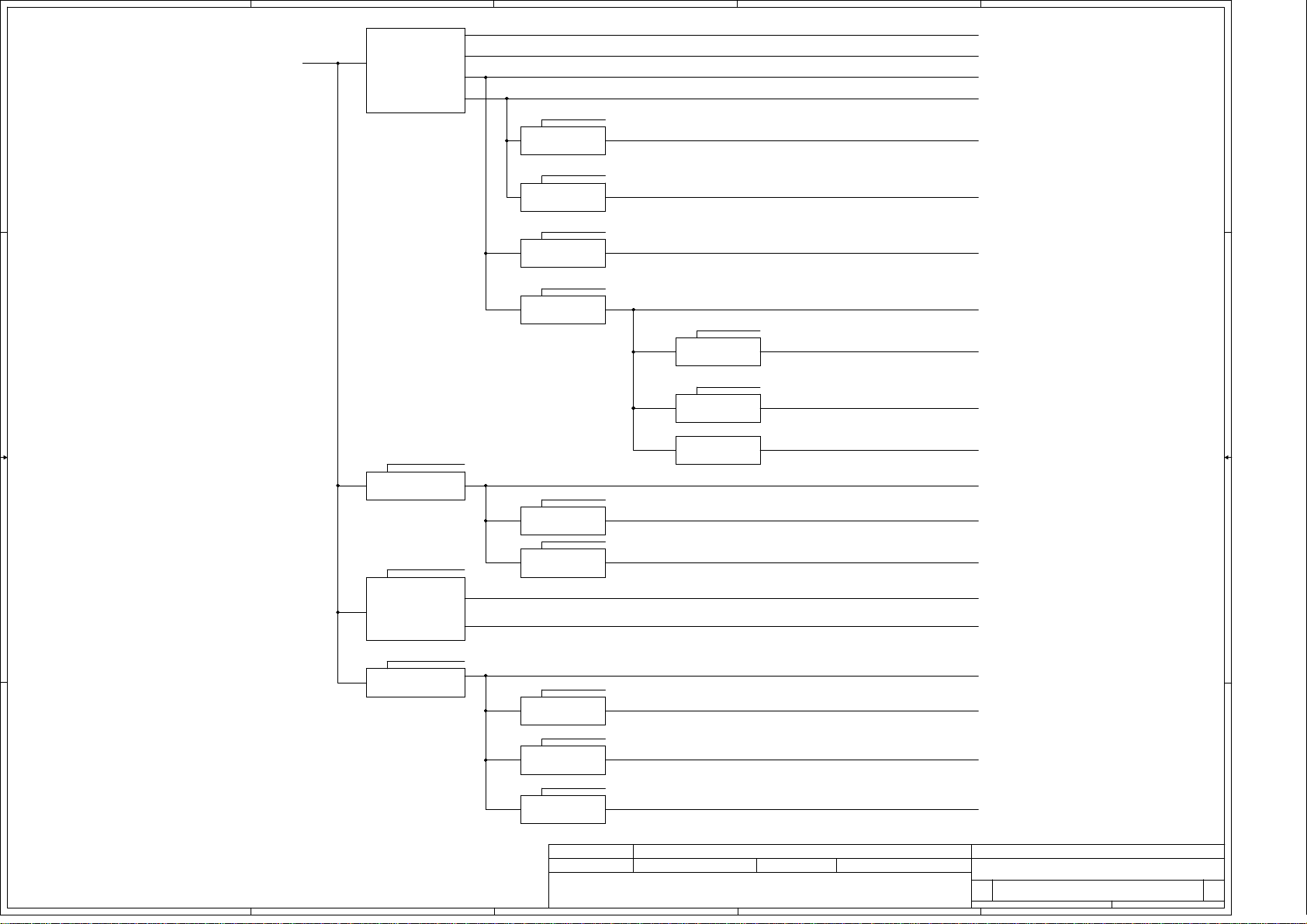

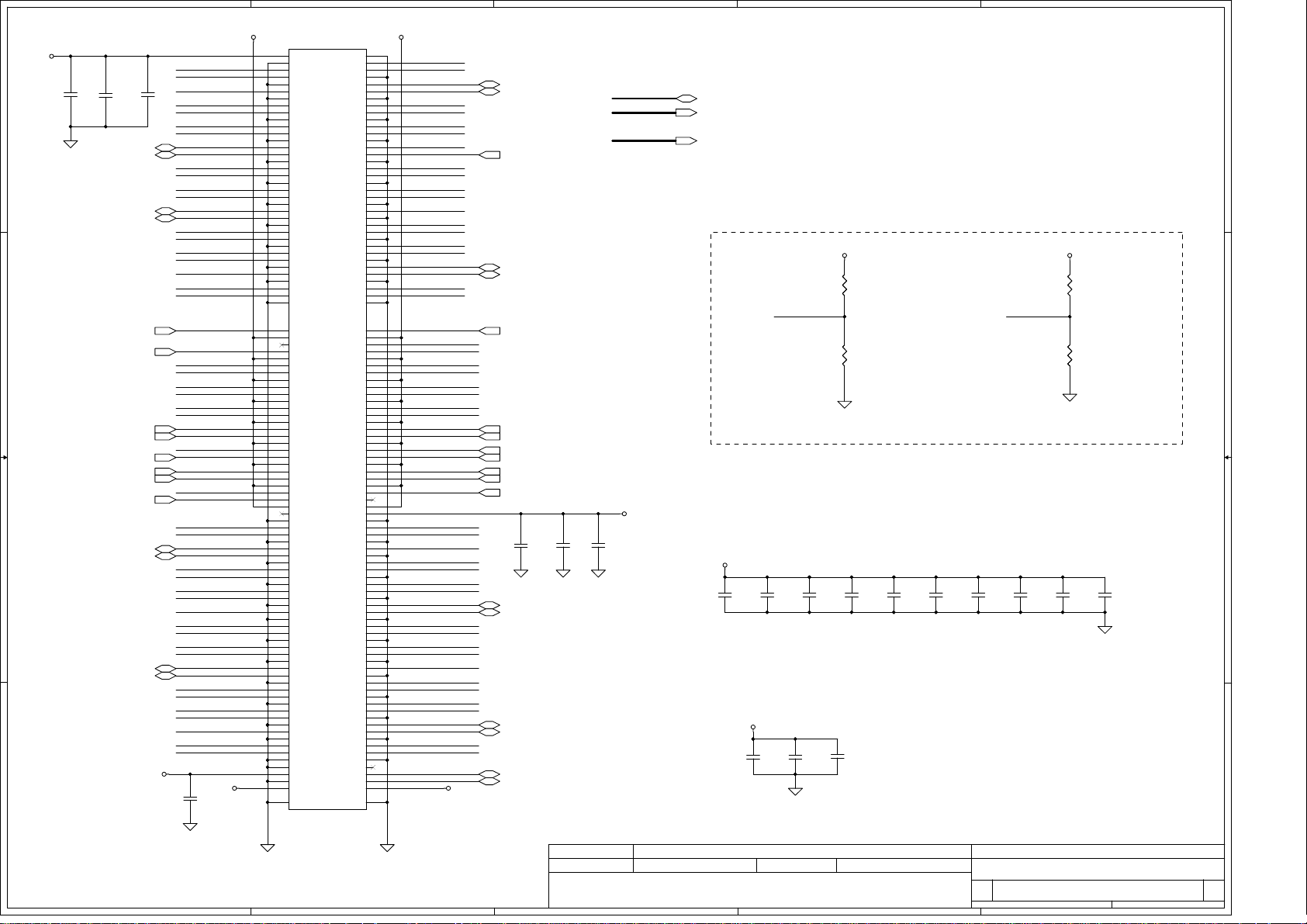

Voltage Rails

O : ON

X : OFF

A

B

Platform

Danube

C

CPU SB

S1G4 SB820M

NB

RS880M

VGA

NA

D

Comment

E

1 1

2 2

S5 S4/ Battery only

S5 S4/AC & Battery

don't exist

State

S0

S1

S3

S5 S4/AC

power

plane

B+

+RTCVCC

O

O

O

O

O

X

+5VALW

+3VALW

+1.1VALW +VDDNB

O

O

O

O

X

XX X

+5VS

+3VS

+2.5VS

+1.8VS

+1.5VS

+1.1VS

+1.05VS+3VL

+1.5V

+0.75VS+5VL

+CPU_CORE

+NB_CORE

OO

OO

O

X

XX

X

X

@ : just reserve , no build

BTO (Build-To-Order) Option Table

Function

Description (Y)

Explain

BTO

BLUE TOOTH

( B )

BT@

HDMI

H@

I2C / SMBUS ADDRESSING

DEVICE

DDR SO-DIMM 0

3 3

DDR SO-DIMM 1

CLOCK GENERATOR (EXT.)

HEX

A0

D2

EC SM Bus1 address

Device Address

Smart Battery

HDMI-CEC 34H

EC KB926D3

HEX

16H

0001 011X b

0011 010X b

ADDRESS

1 0 1 0 0 0 0 0

1 0 1 0 0 0 1 0A2

1 1 0 1 0 0 1 0

EC SM Bus2 address

Device

ADI1032-1 CPU

ADI1032-2 VGA

EC KB926D3

HEX

98H

9AH

Address

1001 100X b

1001 101X b

SMBUS Control Table

SOURCE

EC_SMB_CK1

EC_SMB_DA1

EC_SMB_CK2

EC_SMB_DA2

I2C_CLK

I2C_DATA

DDC_CLK0

DDC_DATA0

SCL0

SDA0

SCL1

SDA1

KB926

KB926

RS880M

RS880M

SB820

SB820

BATT

V

CPU

THERMAL

SENSOR

V

SODIMM

I / II

CLK

GEN

VV

WLAN

V

LCD

DDC

ROM

V

HDMI

DDC

ROM

V

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

442Wednesday, May 19, 2010

442Wednesday, May 19, 2010

442Wednesday, May 19, 2010

E

B

B

B

of

of

of

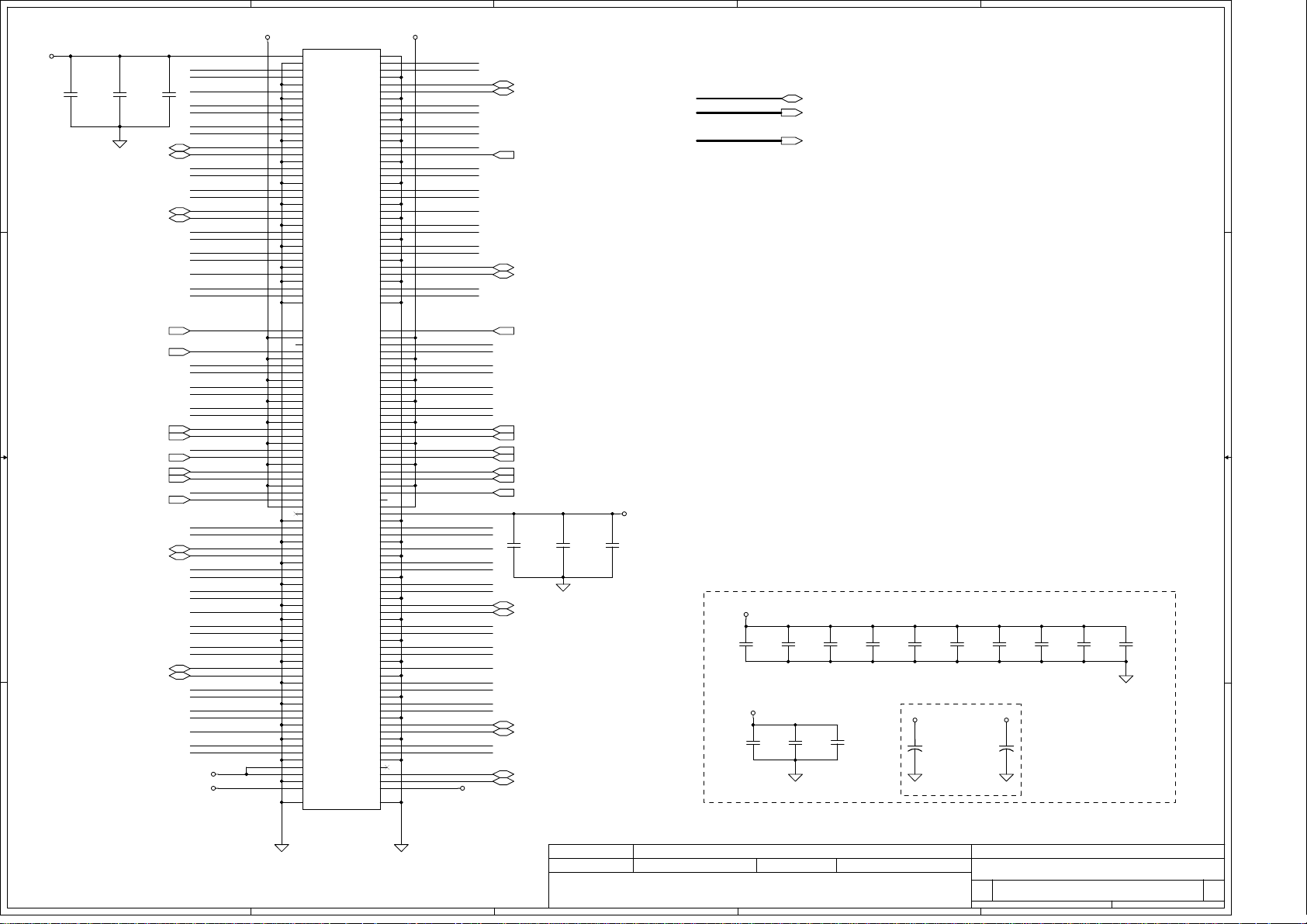

A

+1.1VS

250 mil

1

C1

C1

10U_0805_10V4Z

10U_0805_10V4Z

1 1

2

1

C2

C2

10U_0805_10V4Z

10U_0805_10V4Z

2

Near CPU SocketVLDT CAP.

1

C3

C3

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C4

C4

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

B

1

C5

C5

180P_0402_50V8J

180P_0402_50V8J

2

1

C6

C6

180P_0402_50V8J

180P_0402_50V8J

2

C

H_CADIP[0..15]<11>

H_CADIP[0..15]

H_CADIN[0..15]

D

H_CADOP[0..15]

H_CADON[0..15]

H_CADOP[0..15] <11>

H_CADON[0..15] <11>H_CADIN[0..15]<11>

E

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

+1.1VS

+VLDT_B

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

C7

C7

10U_0805_10V4Z

10U_0805_10V4Z

1 2

C7 close to cpu pin

H_CADOP0

H_CADON0

H_CADOP1

H_CADON1

H_CADOP2

H_CADON2

H_CADOP3

H_CADON3

H_CADOP4

H_CADON4

H_CADOP5

H_CADON5

H_CADOP6

H_CADON6

H_CADOP7

H_CADON7

H_CADOP8

H_CADON8

H_CADOP9

H_CADON9

H_CADOP10

H_CADON10

H_CADOP11

H_CADON11

H_CADOP12

H_CADON12

H_CADOP13

H_CADON13

H_CADOP14

H_CADON14

H_CADOP15

H_CADON15

< To NB >< From NB >

H_CLKOP0 <11>

H_CLKON0 <11>

H_CLKOP1 <11>

H_CLKON1 <11>

H_CTLOP0 <11>

H_CTLON0 <11>

H_CTLOP1 <11>

H_CTLON1 <11>

< VLDT_A & VLDT_B : HyperTransport I/O ring power >

+1.1VS

JCPUA

JCPUA

D1

VLDT=500mA

H_CADIP0

H_CADIN0

H_CADIP1

H_CADIN1

H_CADIP2

H_CADIN2

H_CADIP3

H_CADIN3

H_CADIP4

H_CADIN4

H_CADIP5

2 2

3 3

H_CADIN5

H_CADIP6

H_CADIN6

H_CADIP7

H_CADIN7

H_CADIP8

H_CADIN8

H_CADIP9

H_CADIN9

H_CADIP10

H_CADIN10

H_CADIP11

H_CADIN11

H_CADIP12

H_CADIN12

H_CADIP13

H_CADIN13

H_CADIP14

H_CADIN14

H_CADIP15

H_CADIN15

H_CLKIP0<11>

H_CLKIN0<11>

H_CLKIP1<11>

H_CLKIN1<11>

H_CTLIP0<11>

H_CTLIN0<11>

H_CTLIP1<11>

H_CTLIN1<11>

D2

D3

D4

E3

E2

E1

F1

G3

G2

G1

H1

J1

K1

L3

L2

L1

M1

N3

N2

E5

F5

F3

F4

G5

H5

H3

H4

K3

K4

L5

M5

M3

M4

N5

P5

J3

J2

J5

K5

N1

P1

P3

P4

HT LINK

HT LINK

VLDT_A0

VLDT_A1

VLDT_A2

VLDT_A3

L0_CADIN_H0

L0_CADIN_L0

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H15

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

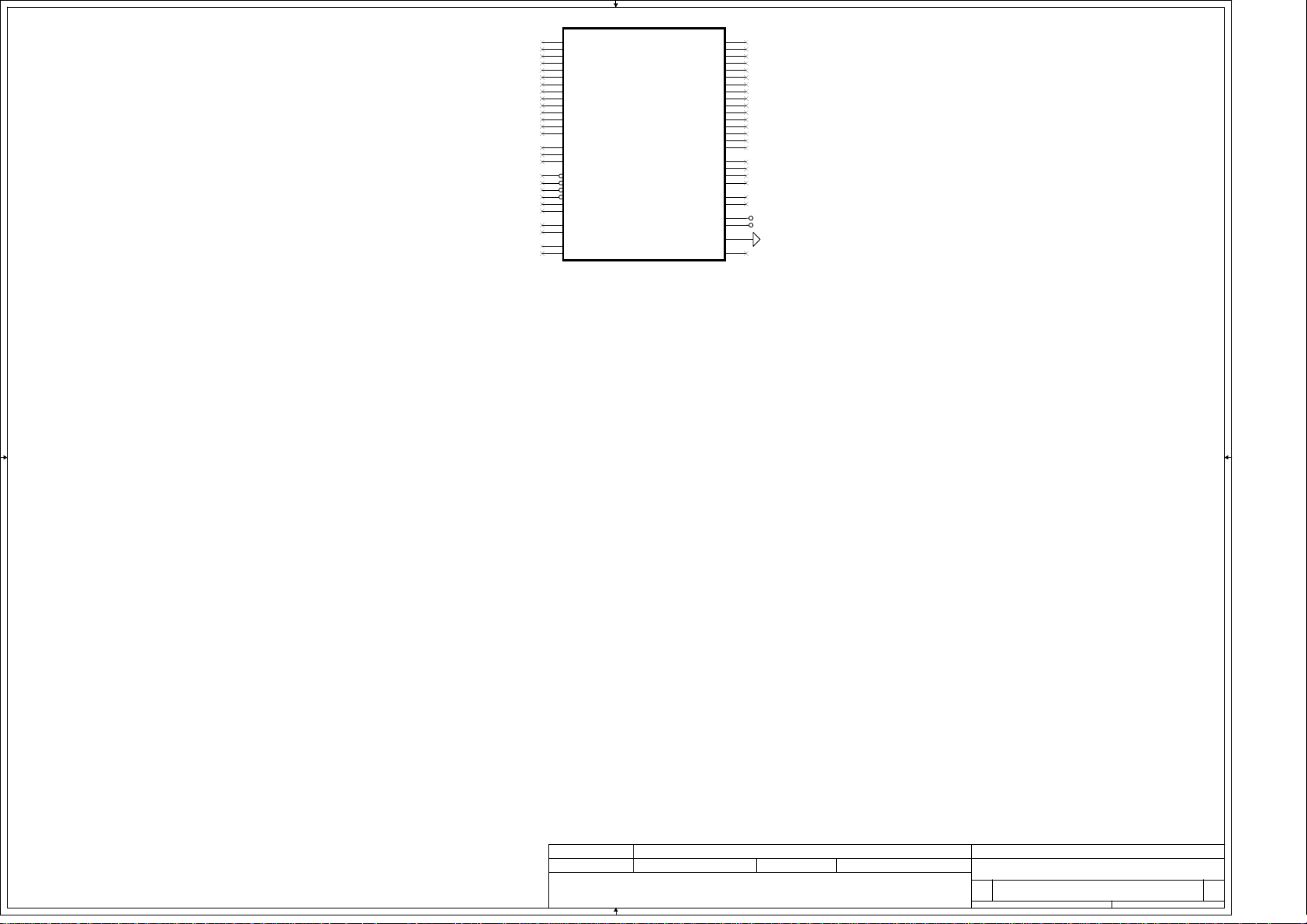

< FAN Control Circuit : Vout = 1.6 x Vset >

+5VS

1A

GND

GND

GND

GND

C1119

C1119

8

7

6

5

2

1

Security Classification

Security Classification

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

@

@

Issued Date

Issued Date

Issued Date

2

C1121

C1121

1000P_0402_25V8J

1000P_0402_25V8J

1

C

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

+FAN1

1

2

3

4

5

Compal Secret Data

Compal Secret Data

Compal Secret Data

JFAN

JFAN

ACES_85204-0300N@

ACES_85204-0300N@

1

2

3

GND

GND

Deciphered Date

Deciphered Date

Deciphered Date

+3VS

@

@

12

R795

R795

10K_0402_5%

10K_0402_5%

2

C1122

C1122

0.01U_0402_25V7K

0.01U_0402_25V7K

1

D

FAN_SPEED1 <30>

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

542Wednesday, May 19, 2010

542Wednesday, May 19, 2010

542Wednesday, May 19, 2010

E

of

of

of

B

B

B

+FAN1

1

C1120

C1120

10U_0805_10V4Z

10U_0805_10V4Z

2

4 4

A

EN_DFAN1<30>

U31

U31

1

EN

2

VIN

3

VOUT

4

VSET

APL5607KI-TRG_SO8

APL5607KI-TRG_SO8

B

10U_0805_10V4Z

10U_0805_10V4Z

A

< DDR3 VREF is 0.5 ratio >

+1.5V

R1

R1

1K_0402_1%

1K_0402_1%

1 2

R2

R2

1 1

1K_0402_1%

1K_0402_1%

1 2

2 2

+1.5V

< To SO_DIMMA >

< To SO_DIMMA >

< To SO_DIMMA >

< To SO_DIMMA >

< To SO_DIMMA >

3 3

< To SO_DIMMA >

< To SO_DIMMA >

Close to CPU

+MCH_REF

1 2

1 2

MEM_MA_RST#<9>

1

C8

C8

1000P_0402_25V8J

1000P_0402_25V8J

2

JCPUB

JCPUB

D10

VDDR1

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

C10

VDDR2

B10

VDDR3

AD10

MEM_P

MEM_N VTT_SENSE

MEM_MA_RST#

DDR_A_ODT0

DDR_A_ODT1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA# DDR_CS0_DIMMB#

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_CLK1

DDR_A_CLK#1

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_RAS#

DDR_A_CAS#

DDR_A_WE#

VDDR4

AF10

MEMZP

AE10

MEMZN

H16

MA_RESET_L

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U19

MA0_CS_L1

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

AA16

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

1

C9

C9

0.1U_0402_16V7K

0.1U_0402_16V7K

2

Place them close to CPU within 1"

R4 39.2_0402_1%R4 39.2_0402_1%

R5 39.2_0402_1%R5 39.2_0402_1%

DDR_A_ODT0<9>

DDR_A_ODT1<9>

DDR_CS0_DIMMA#<9>

DDR_CS1_DIMMA#<9> DDR_CS0_DIMMB# <10>

DDR_CKE0_DIMMA<9>

DDR_CKE1_DIMMA<9>

DDR_A_CLK0<9>

DDR_A_CLK#0<9>

DDR_A_CLK1<9>

DDR_A_CLK#1<9>

DDR_A_MA[15..0]<9>

DDR_A_BS#0<9>

DDR_A_BS#1<9>

DDR_A_BS#2<9>

DDR_A_RAS#<9>

DDR_A_CAS#<9>

DDR_A_WE#<9>

B

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

VDDR_SENSE

MEMVREF

MB_RESET_L

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

+1.05VS+1.05VS

W10

AC10

AB10

< VTT regulator voltage >

AA10

A10

Y10

+MCH_REF

W17

MEM_MB_RST#

B18

DDR_B_ODT0

W26

DDR_B_ODT1

W23

Y26

V26

DDR_CS1_DIMMB#

W25

U22

DDR_CKE0_DIMMB

J25

DDR_CKE1_DIMMB

H26

DDR_B_CLK0

P22

DDR_B_CLK#0

R22

A17

A18

AF18

AF17

DDR_B_CLK1

R26

DDR_B_CLK#1

R25

DDR_B_MA0

P24

DDR_B_MA1

N24

DDR_B_MA2

P26

DDR_B_MA3

N23

DDR_B_MA4

N26

DDR_B_MA5

L23

DDR_B_MA6

N25

DDR_B_MA7

L24

DDR_B_MA8

M26

DDR_B_MA9

K26

DDR_B_MA10

T26

DDR_B_MA11

L26

DDR_B_MA12

L25

DDR_B_MA13

W24

DDR_B_MA14

J23

DDR_B_MA15

J24

DDR_B_BS#0

R24

DDR_B_BS#1

U26

DDR_B_BS#2

J26

DDR_B_RAS#

U25

DDR_B_CAS#

U24

DDR_B_WE#

U23

T1PAD T1PAD

MEM_MB_RST# <10>

DDR_B_ODT0 <10>

DDR_B_ODT1 <10>

DDR_CS1_DIMMB# <10>

DDR_CKE0_DIMMB <10>

DDR_CKE1_DIMMB <10>

DDR_B_CLK0 <10>

DDR_B_CLK#0 <10>

DDR_B_CLK1 <10>

DDR_B_CLK#1 <10>

DDR_B_MA[15..0] <10>

DDR_B_BS#0 <10>

DDR_B_BS#1 <10>

DDR_B_BS#2 <10>

DDR_B_RAS# <10>

DDR_B_CAS# <10>

DDR_B_WE# <10>

C

< To SO_DIMMB >

< To SO_DIMMB >

< To SO_DIMMB >

< To SO_DIMMB >

< To SO_DIMMB >

< To SO_DIMMB >

< To SO_DIMMB >

D

E

< Processor DDR3 Memory Interface >

JCPUC

DDR_B_D[63..0]<10>

< From/To SO_DIMMB >

DDR_B_DM[7..0]<10> DDR_A_DM[7..0] <9>

< To SO_DIMMB > < To SO_DIMMA >

DDR_B_DQS0<10>

DDR_B_DQS#0<10>

DDR_B_DQS1<10>

DDR_B_DQS#1<10>

DDR_B_DQS2<10>

DDR_B_DQS#2<10>

DDR_B_DQS3<10>

DDR_B_DQS#3<10>

DDR_B_DQS4<10>

DDR_B_DQS#4<10>

DDR_B_DQS5<10>

DDR_B_DQS#5<10>

DDR_B_DQS6<10>

DDR_B_DQS#6<10>

DDR_B_DQS7<10>

DDR_B_DQS#7<10>

< From/To SO_DIMMB > < From/To SO_DIMMA >

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS#0

DDR_B_DQS1

DDR_B_DQS#1

DDR_B_DQS2

DDR_B_DQS#2

DDR_B_DQS3

DDR_B_DQS#3

DDR_B_DQS4

DDR_B_DQS#4

DDR_B_DQS5

DDR_B_DQS#5

DDR_B_DQS6

DDR_B_DQS#6

DDR_B_DQS7

DDR_B_DQS#7

JCPUC

MEM:DATA

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MEM:DATA

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

Y11

AE14

AF14

AF11

AD11

A12

B16

A22

E25

AB26

AE22

AC16

AD12

C12

B12

D16

C16

A24

A23

F26

E26

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS#0

DDR_A_DQS1

DDR_A_DQS#1

DDR_A_DQS2

DDR_A_DQS#2

DDR_A_DQS3

DDR_A_DQS#3

DDR_A_DQS4

DDR_A_DQS#4

DDR_A_DQS5

DDR_A_DQS#5

DDR_A_DQS6

DDR_A_DQS#6

DDR_A_DQS7

DDR_A_DQS#7

DDR_A_D[63..0] <9>

< From/To SO_DIMMA >

DDR_A_DQS0 <9>

DDR_A_DQS#0 <9>

DDR_A_DQS1 <9>

DDR_A_DQS#1 <9>

DDR_A_DQS2 <9>

DDR_A_DQS#2 <9>

DDR_A_DQS3 <9>

DDR_A_DQS#3 <9>

DDR_A_DQS4 <9>

DDR_A_DQS#4 <9>

DDR_A_DQS5 <9>

DDR_A_DQS#5 <9>

DDR_A_DQS6 <9>

DDR_A_DQS#6 <9>

DDR_A_DQS7 <9>

DDR_A_DQS#7 <9>

4 4

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

642Wednesday, May 19, 2010

642Wednesday, May 19, 2010

642Wednesday, May 19, 2010

E

B

B

B

of

of

of

A

< Filtered PLL Supply Voltage >

12

R10

R10

169_0402_1%

169_0402_1%

+2.5VDDA+2.5VS

1

C14

C14

2

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

+1.5V

+1.5V

+2.5VDDA

0.22U_0603_16V4Z

0.22U_0603_16V4Z

R40 300_0402_5%R40 300_0402_5%

1 2

R39 220_0402_5%R39 220_0402_5%

R38 220_0402_5%R38 220_0402_5%

R37 220_0402_5%R37 220_0402_5%

R36 220_0402_5%R36 220_0402_5%

L1 FBM_L11_201209_300L_0805L1 FBM_L11_201209_300L_0805

1 2

1

+

+

C11

C11

@

@

150U_B2_6.3VM_R45M

150U_B2_6.3VM_R45M

2

1 1

< 200-MHz PLL Reference Clock >

CLK_CPU_BCLK<19>

CLK_CPU_BCLK#<19>

2 2

+1.5V

R22 510_0402_5%R22 510_0402_5%

R28 1K_0402_5%R28 1K_0402_5%

R27 510_0402_5%R27 510_0402_5%

R29 1K_0402_5%R29 1K_0402_5%

R30 1K_0402_5%R30 1K_0402_5%

R31 1K_0402_5%R31 1K_0402_5%

R32 1K_0402_5%R32 1K_0402_5%

R33 1K_0402_5%R33 1K_0402_5%

R34 1K_0402_5%R34 1K_0402_5%

R265 1K_0402_5%R265 1K_0402_5%

R35 1K_0402_5%R35 1K_0402_5%

3 3

LDT_RST#<19>

H_PWRGD<19,40>

1

C12

C12

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

C16

C16

3900P_0402_50V7K

3900P_0402_50V7K

1 2

C15

C15

3900P_0402_50V7K

3900P_0402_50V7K

1 2

Address:100_1100 Place close to CPU wihtin 1.5"

12

12

1 2

12

12

12

12

12

12

12

12

+1.5VS

R17

R17

300_0402_5%

300_0402_5%

1 2

LDT_RST#

1

C17

C17

@

@

0.01U_0402_25V7K

0.01U_0402_25V7K

2

+1.5VS

R21

R21

300_0402_5%

300_0402_5%

1 2

H_PWRGD

1

C19

C19

@

@

0.1U_0402_16V7K

0.1U_0402_16V7K

2

VDDA=300mA

1

C13

C13

3300P_0402_50V7K

3300P_0402_50V7K

2

CPU_TEST25H

CPU_TEST27

CPU_TEST25L

CPU_TEST12

CPU_TEST18

CPU_TEST19

CPU_TEST20

CPU_TEST21

CPU_TEST22

CPU_TEST23

CPU_TEST24

+1.5V

+1.5V

1 2

1 2

1 2

1 2

B

R12 1K_0402_5%R12 1K_0402_5%

R14 1K_0402_5%R14 1K_0402_5%

R15 44.2_0402_1%R15 44.2_0402_1%

R16 44.2_0402_1%R16 44.2_0402_1%

+1.1VS

CPU_VDD0_RUN_FB_H<40>

CPU_VDD0_RUN_FB_L<40>

CPU_VDD1_RUN_FB_H<40>

CPU_VDD1_RUN_FB_L<40>

1 2

1 2

1 2

1 2

CPU_DBREQ#

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST#

CPU_TDO

+1.5V

+2.5VDDA

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

LDT_RST#

H_PWRGD

LDT_STOP#

T2 PADT2 PAD

CPU_SIC

CPU_SID

CPU_HTREF0

CPU_HTREF1

CPU_VDD0_RUN_FB_H

CPU_VDD0_RUN_FB_L

CPU_VDD1_RUN_FB_H

CPU_VDD1_RUN_FB_L

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST23

CPU_TEST18

CPU_TEST19

CPU_TEST25H

CPU_TEST25L

CPU_TEST21

CPU_TEST20

CPU_TEST24

CPU_TEST22

CPU_TEST12

CPU_TEST27

R24

R24

1 2

0_0402_5%

0_0402_5%

< HDT Connector >

JP2

JP2

1

3

5

7

9

11

13

15

17

19

21

SAMTEC_ASP-68200-07

@ SAMTEC_ASP-68200-07

@

C

JCPUD

JCPUD

F8

VDDA1

F9

VDDA2

A9

CLKIN_H

A8

CLKIN_L

B7

RESET_L

A7

PWROK

F10

LDTSTOP_L

C6

LDTREQ_L

AF4

SIC

AF5

SID

AE6

ALERT_L

R6

HT_REF0

P6

HT_REF1

F6

VDD0_FB_H

E6

VDD0_FB_L

Y6

VDD1_FB_H

AB6

VDD1_FB_L

G10

DBRDY

AA9

TMS

AC9

TCK

AD9

TRST_L

AF9

TDI

AD7

TEST23

H10

TEST18

G9

TEST19

E9

TEST25_H

E8

TEST25_L

AB8

TEST21

AF7

TEST20

AE7

TEST24

AE8

TEST22

AC8

TEST12

AF8

TEST27

C2

TEST9

AA6

TEST6

A3

RSVD1

A5

RSVD2

B3

RSVD3

B5

RSVD4

C1

RSVD5

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

2

4

6

8

10

12

14

16

18

20

22

2423

26

LDT_RST#

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

VSS

RSVD11

SVC

SVD

MEMHOT_L

THERMDC

THERMDA

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

M11

W18

CPU_SVC

A6

CPU_SVD

A4

< Serial VID Interface clock & data >

CPU_THERMTRIP#_R

AF6

CPU_PROCHOT#

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

0.1U_0402_16V7K

0.1U_0402_16V7K

T3PAD T3PAD

THERMDC_CPU

THERMDA_CPU

route as differential

as short as possible

testpoint under package

CPU_VDDNB_RUN_FB_H

CPU_VDDNB_RUN_FB_L

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

+3VS

1

C20

C20

2

CPU_DBREQ#

D

CPU_SVC <40>

CPU_SVD <40>

CPU_VDDNB_RUN_FB_H <40>

CPU_VDDNB_RUN_FB_L <40>

CPU_TDO

T4PAD T4PAD

T5PAD T5PAD

T6PAD T6PAD

T7PAD T7PAD

R25 80.6_0402_1%R25 80.6_0402_1%

C21

C21

1 2

3300P_0402_50V7-K

3300P_0402_50V7-K

@

@

12

THERMDA_CPU

THERMDC_CPU

CPU_SVC

CPU_SVD

R11 300_0402_5%R11 300_0402_5%

+1.5V

+1.5V

< Thermal Sensor >

U1

U1

1

VDD

2

D+

3

DTHERM#4GND

ADM1032ARM-1 ZREEL_MSOP8

ADM1032ARM-1 ZREEL_MSOP8

1 2

CPU_PROCHOT#

R6 10K_0402_5%R6 10K_0402_5%

1 2

R7 1K_0402_5%R7 1K_0402_5%

1 2

CPU_THERMTRIP#_R

8

SCLK

7

SDATA

6

ALERT#

5

@R13

@

1 2

EC_SMB_CK2

EC_SMB_DA2

E

1 2

1 2

R13

0_0402_5%

0_0402_5%

B

B

2

Q1

Q1

E

E

3 1

C

C

MMBT3904_NL_SOT23-3

MMBT3904_NL_SOT23-3

EC_SMB_CK2 <30>

EC_SMB_DA2 <30>

+1.5V

R191K_0402_5% R191K_0402_5%

R201K_0402_5% R201K_0402_5%

H_PROCHOT# <19>

H_THERMTRIP# <20>

4 4

LDT_STOP#<12,19>

+1.5VS

R18

R18

300_0402_5%

300_0402_5%

1 2

LDT_STOP#

1

C18

C18

@

@

0.01U_0402_25V7K

0.01U_0402_25V7K

2

A

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

742Wednesday, May 19, 2010

742Wednesday, May 19, 2010

742Wednesday, May 19, 2010

E

B

B

B

of

of

A

VDD decoupling : +CPU_CORE

+CPU_CORE

1

2

C89

C89

330U_X_2VM_R6M

330U_X_2VM_R6M

1

C45

C45

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C51

C51

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C67

C67

180P_0402_50V8J

180P_0402_50V8J

2

1

C72

C72

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C58

C58

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C77

C77

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C43

C43

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

+

+

C25

C25

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1

+

C24

@+C24

@

2

A

1

+

+

C26

C26

330U_X_2VM_R6M

330U_X_2VM_R6M

2

1 1

+CPU_CORE

1

+

+

+

+

@

@

C23

C23

2

330U_2.5V_M

330U_2.5V_M

Near CPU Socket

330U_X_2VM_R6M

330U_X_2VM_R6M

VDDIO decoupling : DDR SDRAM I/O ring power

+1.5V

1

C44

C44

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Under CPU Socket

+1.5V

2 2

1

C54

C54

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

Between CPU Socket and DIMM

+1.5V

1

C64

C64

0.01U_0402_25V7K

0.01U_0402_25V7K

2

Between CPU Socket and DIMM

+1.5V

180PF Qt'y follow the distance between CPU socket and DIMM0. <2.5inch>

1

C66

C66

180P_0402_50V8J

180P_0402_50V8J

2

Between CPU Socket and DIMM

+1.5V

3 3

1

C71

C71

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

Between CPU Socket and DIMM

+1.05VS

VTT decoupling.

1

C57

C57

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

Near CPU Socket Right side

+1.05VS

1

C76

C76

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

Near CPU Socket Left side

4 4

+VDDNB decoupling : Northbridge power

+VDDNB

1

C42

C42

22U_0805_6.3V6M

22U_0805_6.3V6M

2

+CPU_CORE +CPU_CORE

1

C35

C35

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C34

C34

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Under CPU Socket

+CPU_CORE +CPU_CORE

1

+

+

2

330U_2.5V_M

330U_2.5V_M

1

2

1

2

1

C30

C30

C90

C90

22U_0805_6.3V6M

22U_0805_6.3V6M

2

Under CPU Socket

1

C46

C46

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C52

C52

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C65

C65

0.01U_0402_25V7K

0.01U_0402_25V7K

2

1

C68

C68

180P_0402_50V8J

180P_0402_50V8J

2

1

C73

C73

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

C59

C59

0.22U_0603_16V4Z

0.22U_0603_16V4Z

C78

C78

0.22U_0603_16V4Z

0.22U_0603_16V4Z

1

C49

C49

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

2

1

C47

C47

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C53

C53

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C69

C69

180P_0402_50V8J

180P_0402_50V8J

2

1

C74

C74

4.7U_0805_10V4Z

4.7U_0805_10V4Z

2

1

C60

C60

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

1

C79

C79

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

C31

C31

22U_0805_6.3V6M

22U_0805_6.3V6M

1

C48

C48

180P_0402_50V8J

180P_0402_50V8J

2

C75

@+C75

@

1

C61

C61

1000P_0402_25V8J

1000P_0402_25V8J

2

1

C80

C80

1000P_0402_25V8J

1000P_0402_25V8J

2

B

1

C28

C28

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C32

C32

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C50

C50

180P_0402_50V8J

180P_0402_50V8J

2

C56 Co-layout with C75

330U_D2E_2.5VM_R6M

1

2

330U_D2E_2.5VM_R6M

+

+1.5V

1

C56

C56

2

1

C62

C62

1000P_0402_25V8J

1000P_0402_25V8J

2

1

C81

C81

1000P_0402_25V8J

1000P_0402_25V8J

2

B

+

+

390U_2.5V_M_R10

390U_2.5V_M_R10

1

C29

C29

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

C33

C33

22U_0805_6.3V6M

22U_0805_6.3V6M

2

1

2

1

2

1

C36

C36

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

Under CPU SocketNear CPU Socket

1

C39

C39

0.22U_0603_16V4Z

0.22U_0603_16V4Z

2

Under CPU Socket

C63

C63

180P_0402_50V8J

180P_0402_50V8J

C82

C82

180P_0402_50V8J

180P_0402_50V8J

C

1

C37

C37

0.01U_0402_25V7K

0.01U_0402_25V7K

2

1

C40

C40

0.01U_0402_25V7K

0.01U_0402_25V7K

2

1

C70

C70

180P_0402_50V8J

180P_0402_50V8J

2

1

C83

C83

180P_0402_50V8J

180P_0402_50V8J

2

C1124 Co-layout with C1125

C1125

C1125

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

1

C38

C38

180P_0402_50V8J

180P_0402_50V8J

2

1

C41

C41

180P_0402_50V8J

180P_0402_50V8J

2

+1.05VS +1.05VS

330U_D2E_2.5VM

330U_D2E_2.5VM

1

+

+

2

@

@

1

C1124

C1124

+

+

2

C

+1.5V

390U_2.5V_M_R10

390U_2.5V_M_R10

Compal Secret Data

Compal Secret Data

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

+CPU_CORE +CPU_CORE

+VDDNB

D

JCPUE

JCPUE

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17

VDDIO12

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

JCPUF

JCPUF

AA4

VSS1

AA11

VSS2

AA13

VSS3

AA15

VSS4

AA17

VSS5

AA19

VSS6

AB2

VSS7

AB7

VSS8

AB9

VSS9

AB23

VSS10

AB25

VSS11

AC11

VSS12

AC13

VSS13

AC15

VSS14

AC17

VSS15

AC19

VSS16

AC21

VSS17

AD6

VSS18

AD8

VSS19

AD25

VSS20

AE11

VSS21

AE13

VSS22

AE15

VSS23

AE17

VSS24

AE19

VSS25

AE21

VSS26

AE23

VSS27

B4

VSS28

B6

VSS29

B8

VSS30

B9

VSS31

B11

VSS32

B13

VSS33

B15

VSS34

B17

VSS35

B19

VSS36

B21

VSS37

B23

VSS38

B25

VSS39

D6

VSS40

D8

VSS41

D9

VSS42

D11

VSS43

D13

VSS44

D15

VSS45

D17

VSS46

D19

VSS47

D21

VSS48

D23

VSS49

D25

VSS50

E4

VSS51

F2

VSS52

F11

VSS53

F13

VSS54

F15

VSS55

F17

VSS56

F19

VSS57

F21

VSS58

F23

VSS59

F25

VSS60

H7

VSS61

H9

VSS62

H21

VSS63

H23

VSS64

J4

VSS65

FOX_PZ6382A-284S-41F_Champlian

FOX_PZ6382A-284S-41F_Champlian

D

E

P8

VDD1_1

P10

VDD1_2

R4

VDD1_3

R7

VDD1_4

R9

VDD1_5

R11

VDD1_6

T2

VDD1_7

T6

VDD1_8

T8

VDD1_9

T10

VDD1_10

T12

VDD1_11

T14

VDD1_12

U7

VDD1_13

U9

VDD1_14

U11

VDD1_15

U13

VDD1_16

U15

VDD1_17

V6

VDD1_18

V8

VDD1_19

V10

VDD1_20

V12

VDD1_21

V14

VDD1_22

W4

VDD1_23

Y2

VDD1_24

AC4

VDD1_25

AD2

VDD1_26

Y25

VDDIO27

V25

VDDIO26

V23

VDDIO25

V21

VDDIO24

V18

VDDIO23

U17

VDDIO22

T25

VDDIO21

T23

VDDIO20

T21

VDDIO19

T18

VDDIO18

R17

VDDIO17

P25

VDDIO16

P23

VDDIO15

P21

VDDIO14

P18

VDDIO13

J6

VSS66

J8

VSS67

J10

VSS68

J12

VSS69

J14

VSS70

J16

VSS71

J18

VSS72

K2

VSS73

K7

VSS74

K9

VSS75

K11

VSS76

K13

VSS77

K15

VSS78

K17

VSS79

L6

VSS80

L8

VSS81

L10

VSS82

L12

VSS83

L14

VSS84

L16

VSS85

L18

VSS86

M7

VSS87

M9

VSS88

AC6

VSS89

M17

VSS90

N4

VSS91

N8

VSS92

N10

VSS93

N16

VSS94

N18

VSS95

P2

VSS96

P7

VSS97

P9

VSS98

P11

VSS99

P17

VSS100

R8

VSS101

R10

VSS102

R16

VSS103

R18

VSS104

T7

VSS105

T9

VSS106

T11

VSS107

T13

VSS108

T15

VSS109

T17

VSS110

U4

VSS111

U6

VSS112

U8

VSS113

U10

VSS114

U12

VSS115

U14

VSS116

U16

VSS117

U18

VSS118

V2

VSS119

V7

VSS120

V9

VSS121

V11

VSS122

V13

VSS123

V15

VSS124

V17

VSS125

W6

VSS126

Y21

VSS127

Y23

VSS128

N6

VSS129

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

+1.5V

Compal Electronics, Inc.

Compal Electronics, Inc.

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

842Wednesday, May 19, 2010

842Wednesday, May 19, 2010

842Wednesday, May 19, 2010

E

B

B

B

of

of

of

A

B

C

D

E

+1.5V +1.5V

+VREF_DQ

4.7U_0805_10V4Z

4.7U_0805_10V4Z

0.01U_0402_25V7K

0.01U_0402_25V7K

1000P_0402_25V8J

1000P_0402_25V8J

1

2

C84

C84

C85

C85

2

1 1

2 2

3 3

4 4

1

DDR_A_DQS#1<6>

DDR_A_DQS1<6>

DDR_A_DQS#2<6>

DDR_A_DQS2<6>

DDR_CKE0_DIMMA<6>

DDR_A_BS#2<6>

DDR_A_CLK0<6>

DDR_A_CLK#0<6>

DDR_A_BS#0<6>

DDR_A_WE#<6>

DDR_A_CAS#<6> DDR_A_ODT0 <6>

DDR_CS1_DIMMA#<6>

DDR_A_DQS#4<6>

DDR_A_DQS4<6>

DDR_A_DQS#6<6>

DDR_A_DQS6<6>

0.1U_0402_16V4Z

0.1U_0402_16V4Z

DDR_A_D0

DDR_A_D1

1

DDR_A_DM0

C10

C10

DDR_A_D2

2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

DDR_A_DM3

DDR_A_D26

DDR_A_D27

DDR_CKE0_DIMMA

DDR_A_BS#2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

DDR_A_MA3

DDR_A_MA1

DDR_A_CLK0

DDR_A_CLK#0

DDR_A_MA10

DDR_A_BS#0

DDR_A_WE#

DDR_A_CAS# DDR_A_ODT0

DDR_A_MA13

DDR_CS1_DIMMA#

DDR_A_D32

DDR_A_D33

DDR_A_DQS#4

DDR_A_DQS4

DDR_A_D34

DDR_A_D35

DDR_A_D40

DDR_A_D41

DDR_A_DM5

DDR_A_D42

DDR_A_D43

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_DM7

DDR_A_D58

DDR_A_D59

+3VS

1

+0.75VS

C91

C91

2

JDDRL

JDDRL

VREF_DQ1VSS1

3

VSS2

5

DQ0

7

DQ1

9

VSS4

11

DM0

13

VSS5

15

DQ2

17

DQ3

19

VSS7

21

DQ8

23

DQ9

25

VSS9

27

DQS#1

DQS129RESET#

31

VSS11

33

DQ10

35

DQ11

37

VSS13

39

DQ16

41

DQ17

43

VSS15

45

DQS#2

47

DQS2

49

VSS18

51

DQ18

53

DQ19

55

VSS20

57

DQ24

59

DQ25

61

VSS22

63

DM3

65

VSS23

67

DQ26

69

DQ27

71

VSS25

73

CKE0

75

VDD1

77

NC1

79

BA2

81

VDD3

83

A12/BC#

85

A9

87

VDD5

89

A8

91

A5

93

VDD7

95

A3

97

A1

99

VDD9

101

CK0

103

CK0#

105

VDD11

107

A10/AP

109

BA0

111

VDD13

113

WE#

115

CAS#

117

VDD15

119

A13

121

S1#

123

VDD17

125

NCTEST

127

VSS27

129

DQ32

131

DQ33

133

VSS29

135

DQS#4

137

DQS4

139

VSS32

141

DQ34

143

DQ35

145

VSS34

147

DQ40

149

DQ41

151

VSS36

153

DM5

155

VSS37

157

DQ42

159

DQ43

161

VSS39

163

DQ48

165

DQ49

167

VSS41

169

DQS#6

171

DQS6

173

VSS44

175

DQ50

177

DQ51

179

VSS46

181

DQ56

183

DQ57

185

VSS48

187

DM7

189

VSS49

191

DQ58

193

DQ59

195

VSS51

197

SA0

199

VDDSPD

201

SA1

203

VTT1

205

G1

TYCO_2-2013289-1

TYCO_2-2013289-1

DQ4

DQ5

VSS3

DQS#0

DQS0

VSS6

DQ6

DQ7

VSS8

DQ12

DQ13

VSS10

DM1

VSS12

DQ14

DQ15

VSS14

DQ20

DQ21

VSS16

DM2

VSS17

DQ22

DQ23

VSS19

DQ28

DQ29

VSS21

DQS#3

DQS3

VSS24

DQ30

DQ31

VSS26

CKE1

VDD2

VDD4

VDD6

VDD8

VDD10

CK1#

VDD12

RAS#

VDD14

ODT0

VDD16

ODT1

VDD18

VREF_CA

VSS28

DQ36

DQ37

VSS30

DM4

VSS31

DQ38

DQ39

VSS33

DQ44

DQ45

VSS35

DQS#5

DQS5

VSS38

DQ46

DQ47

VSS40

DQ52

DQ53

VSS42

DM6

VSS43

DQ54

DQ55

VSS45

DQ60

DQ61

VSS47

DQS#7

DQS7

VSS50

DQ62

DQ63

VSS52

EVENT#

SDA

VTT2

CK1

BA1

S0#

NC2

SCL

2

DDR_A_D4

4

DDR_A_D5

6

8

DDR_A_DQS#0

10

DDR_A_DQS0

12

14

DDR_A_D6

16

DDR_A_D7

18

20

DDR_A_D12

22

DDR_A_D13

24

26

DDR_A_DM1

28

MEM_MA_RST#

30

32

DDR_A_D14

34

DDR_A_D15

36

38

DDR_A_D20

40

DDR_A_D21

42

44

DDR_A_DM2

46

48

DDR_A_D22

50

DDR_A_D23

52

54

DDR_A_D28

56

DDR_A_D29

58

60

DDR_A_DQS#3

62

DDR_A_DQS3

64

66

DDR_A_D30

68

DDR_A_D31

70

72

DDR_CKE1_DIMMA

74

76

DDR_A_MA15

78

A15

A14

A11

A7

A6

A4

A2

A0

G2

DDR_A_MA14

80

82

DDR_A_MA11

84

DDR_A_MA7

86

88

DDR_A_MA6

90

DDR_A_MA4

92

94

DDR_A_MA2

96

DDR_A_MA0

98

100

DDR_A_CLK1

102

DDR_A_CLK#1

104

106

DDR_A_BS#1

108

DDR_A_RAS#

110

112

DDR_CS0_DIMMA#

114

116

118

DDR_A_ODT1

120

122

124

126

128

DDR_A_D36

130

DDR_A_D37

132

134

DDR_A_DM4

136

138

DDR_A_D38

140

DDR_A_D39

142

144

DDR_A_D44

146

DDR_A_D45

148

150

DDR_A_DQS#5

152

DDR_A_DQS5

154

156

DDR_A_D46

158

DDR_A_D47

160

162

DDR_A_D52

164

DDR_A_D53

166

168

DDR_A_DM6

170

172

DDR_A_D54

174

DDR_A_D55

176

178

DDR_A_D60

180

DDR_A_D61

182

184

DDR_A_DQS#7

186

DDR_A_DQS7

188

190

DDR_A_D62

192

DDR_A_D63

194

196

198

200

202

204

206

+0.75VS

DDR_A_DQS#0 <6>

DDR_A_DQS0 <6>

MEM_MA_RST# <6>

DDR_A_DQS#3 <6>

DDR_A_DQS3 <6>

DDR_CKE1_DIMMA <6>

DDR_A_CLK1 <6>

DDR_A_CLK#1 <6>

DDR_A_BS#1 <6>

DDR_A_RAS# <6>

DDR_CS0_DIMMA# <6>

DDR_A_ODT1 <6>

1000P_0402_25V8J

1000P_0402_25V8J

0.01U_0402_25V7K

0.01U_0402_25V7K

2

C680

C680

1

DDR_A_DQS#5 <6>

DDR_A_DQS5 <6>

DDR_A_DQS#7 <6>

DDR_A_DQS7 <6>

SMB_CK_DAT0 <10,20>

SMB_CK_CLK0 <10,20>

DDR_A_D[0..63]

DDR_A_DM[0..7]

DDR_A_MA[0..15]

DDR_A_D[0..63] <6>

DDR_A_DM[0..7] <6>

DDR_A_MA[0..15] <6>

+1.5V

R48

R48

1K_0402_1%

1K_0402_1%

1 2

R49

R49

1K_0402_1%

1K_0402_1%

1 2

+1.5V

R310

R310

1K_0402_1%

1K_0402_1%

+VREF_CA+VREF_DQ

1 2

R315

R315

1K_0402_1%

1K_0402_1%

1 2

< Close to JDDRH & JDDRL >

+VREF_CA

4.7U_0805_10V4Z

4.7U_0805_10V4Z

1

1

C351

C351

C235

C235

2

2

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+1.5V

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C87

C87

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

+0.75VS

2

1

2

C88

C88

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C665

C665

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C640

C640

1

1

C664

C664

2

4.7U_0603_6.3V6K

4.7U_0603_6.3V6K

C961

C961

2

1

C641

C641

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C642

C642

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C643

C643

1

2

C644

C644

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

Place near DIMM1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C645

C645

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C646

C646

1

0.1U_0402_16V4Z

0.1U_0402_16V4Z

2

C647

C647

1

Security Classification

Security Classification

Security Classification

Issued Date

Issued Date

DIMM_A STD H:5.2 mm

<Address: 00>

A

B

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

2009-02-12 2009-02-12

2009-02-12 2009-02-12

2009-02-12 2009-02-12

Compal Secret Data

Compal Secret Data

Compal Secret Data

Deciphered Date

Deciphered Date

Deciphered Date

Compal Electronics, Inc.

Compal Electronics, Inc.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

D

Date: Sheet

Compal Electronics, Inc.

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

SCHEMATIC,MB A6053

401870

401870

401870

942Wednesday, May 19, 2010

942Wednesday, May 19, 2010

942Wednesday, May 19, 2010

E

B

B

B

of

of

of

A

B

C

D

E

DQ4

DQ5

VSS3

VSS6

DQ6

DQ7

VSS8

DM1

DM2

CKE1

CK1

CK1#

BA1

RAS#

S0#

NC2

DM4

DM6

SDA

SCL

VTT2

+1.5V+1.5V

2

DDR_B_D4

4

DDR_B_D5

6

8

DDR_B_DQS#0

10

DDR_B_DQS0

12

14

DDR_B_D6

16

DDR_B_D7

18

20

DDR_B_D12

22

DDR_B_D13

24

26

DDR_B_DM1

28

MEM_MB_RST#

30

32

DDR_B_D14

34

DDR_B_D15

36

38

DDR_B_D20

40

DDR_B_D21

42

44

DDR_B_DM2

46

48

DDR_B_D22

50

DDR_B_D23

52

54

DDR_B_D28

56

DDR_B_D29

58

60

DDR_B_DQS#3

62

DDR_B_DQS3

64

66

DDR_B_D30

68

DDR_B_D31

70

72

DDR_CKE1_DIMMB

74

76

DDR_B_MA15

78

A15

A14

A11

A7

A6

A4

A2

A0

G2

80

82

84

86

88