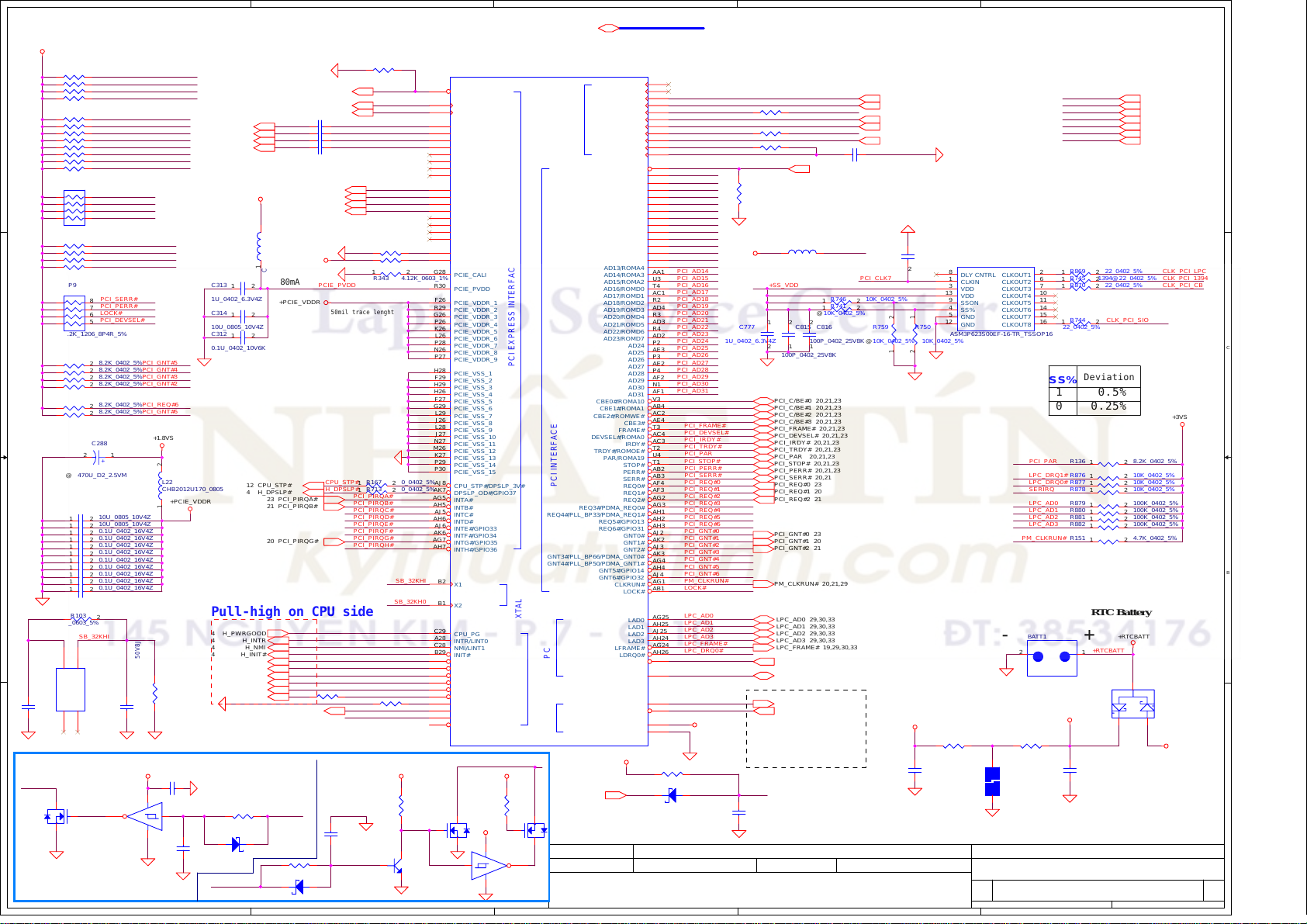

Toshiba Satellite A135-S2686, Compal LA-3391P Schematic

A

Digitally signed by

nhat tin

DN: cn=nhat tin, o, ou,

email=support@kythu

atvitinh.com, c=VN

Date: 2010.07.13

15:56:29 +07'00'

1 1

B

C

D

E

IAYAA

2 2

LA-3391P

3 3

REV 0.3

Schematic

UFC-PGA Yonah/ RC410MD(ME)/ SB450

2006-10-05 Rev. 0.3

4 4

A

B

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/05/18 2007/05/18

C

Compal Secret Data

Deciphered Date

D

Compal Electronics, Inc.

Title

Black Diagram

Size Document Number Rev

IAYAA (LA-3391P) 0.3

B

Wednesday, October 11, 2006

Date: Sheet

148

E

of

A

B

C

D

E

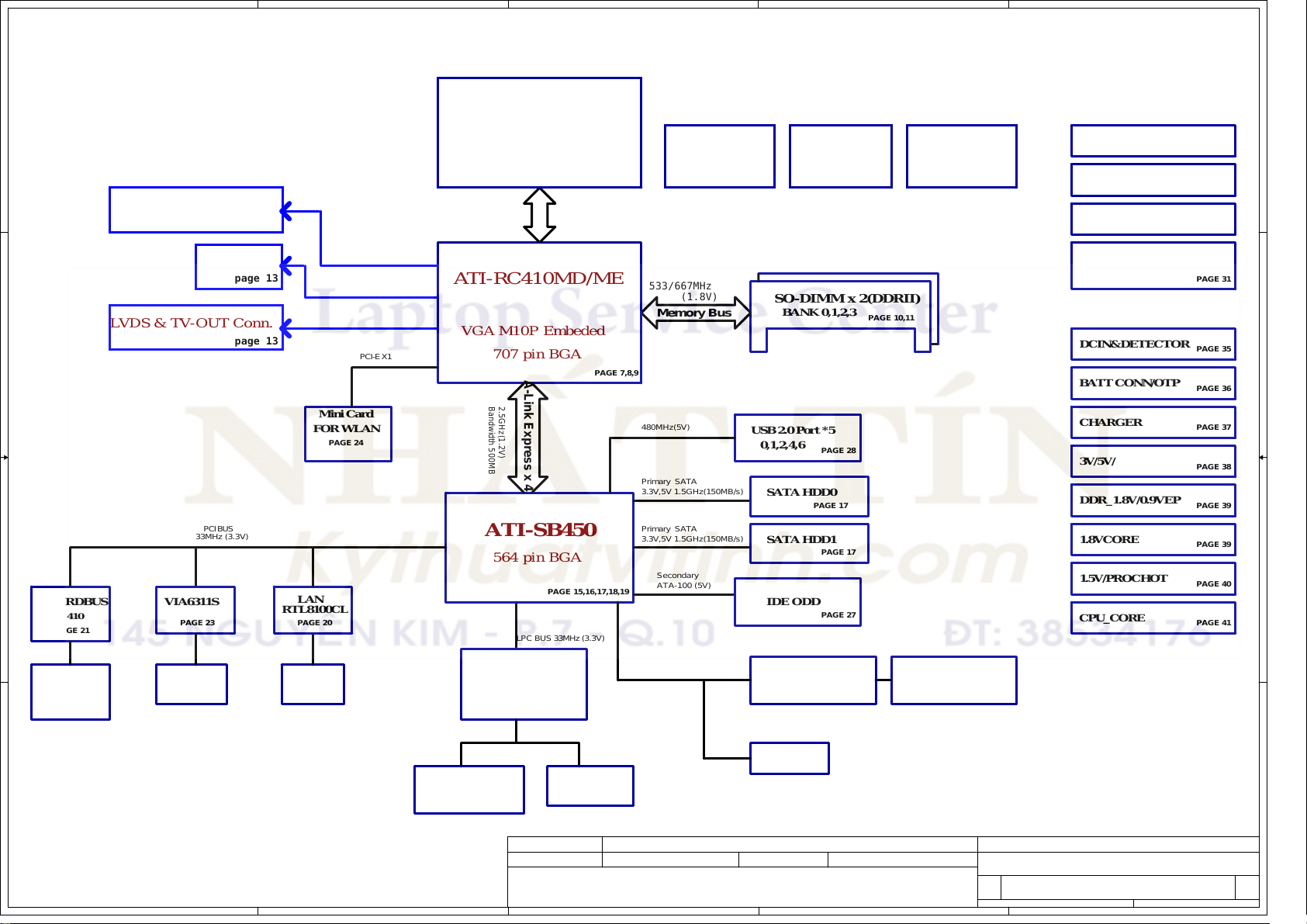

IVYAA LA-3391P FUNCTION BLOCK DIAGRAM

4 4

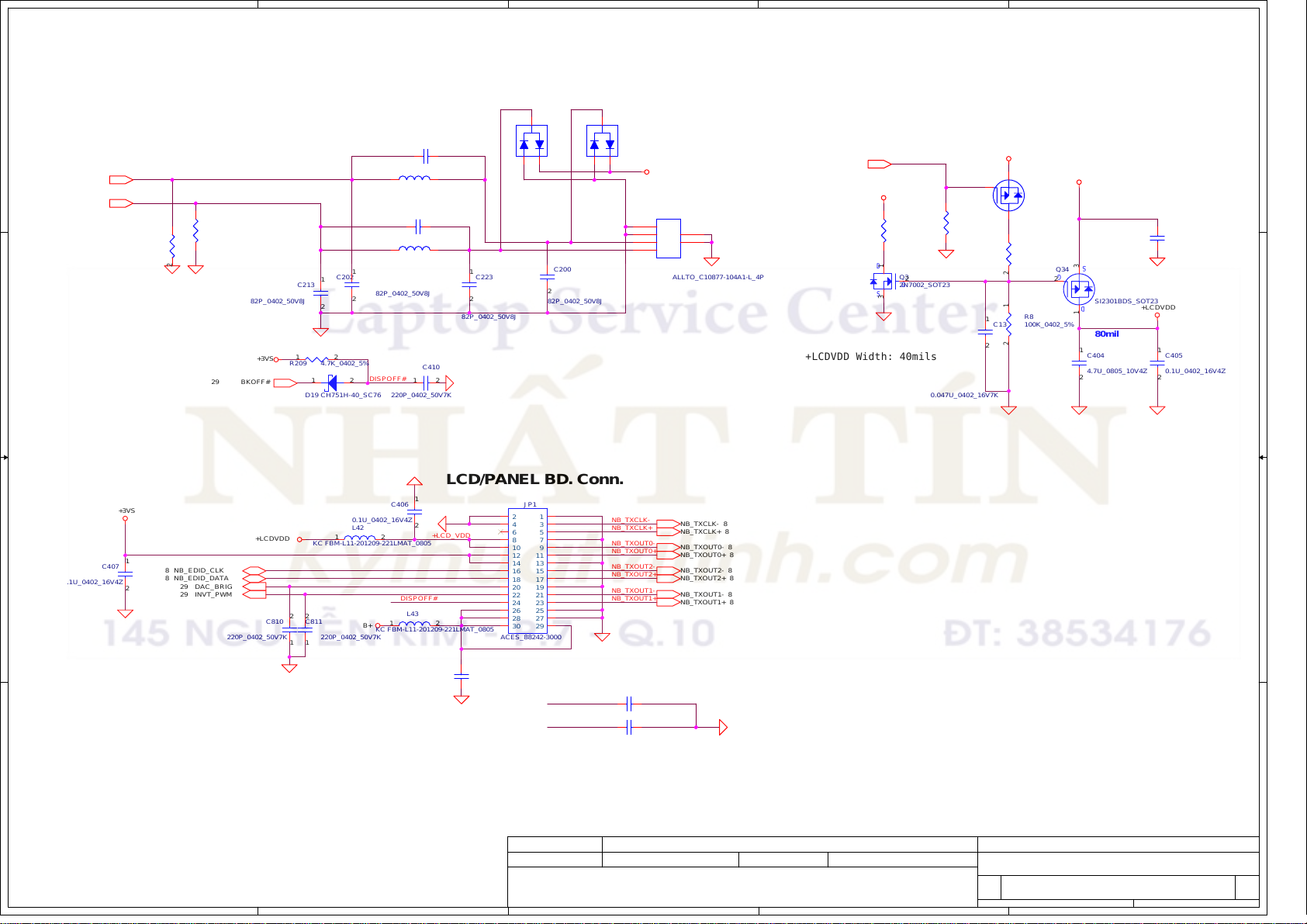

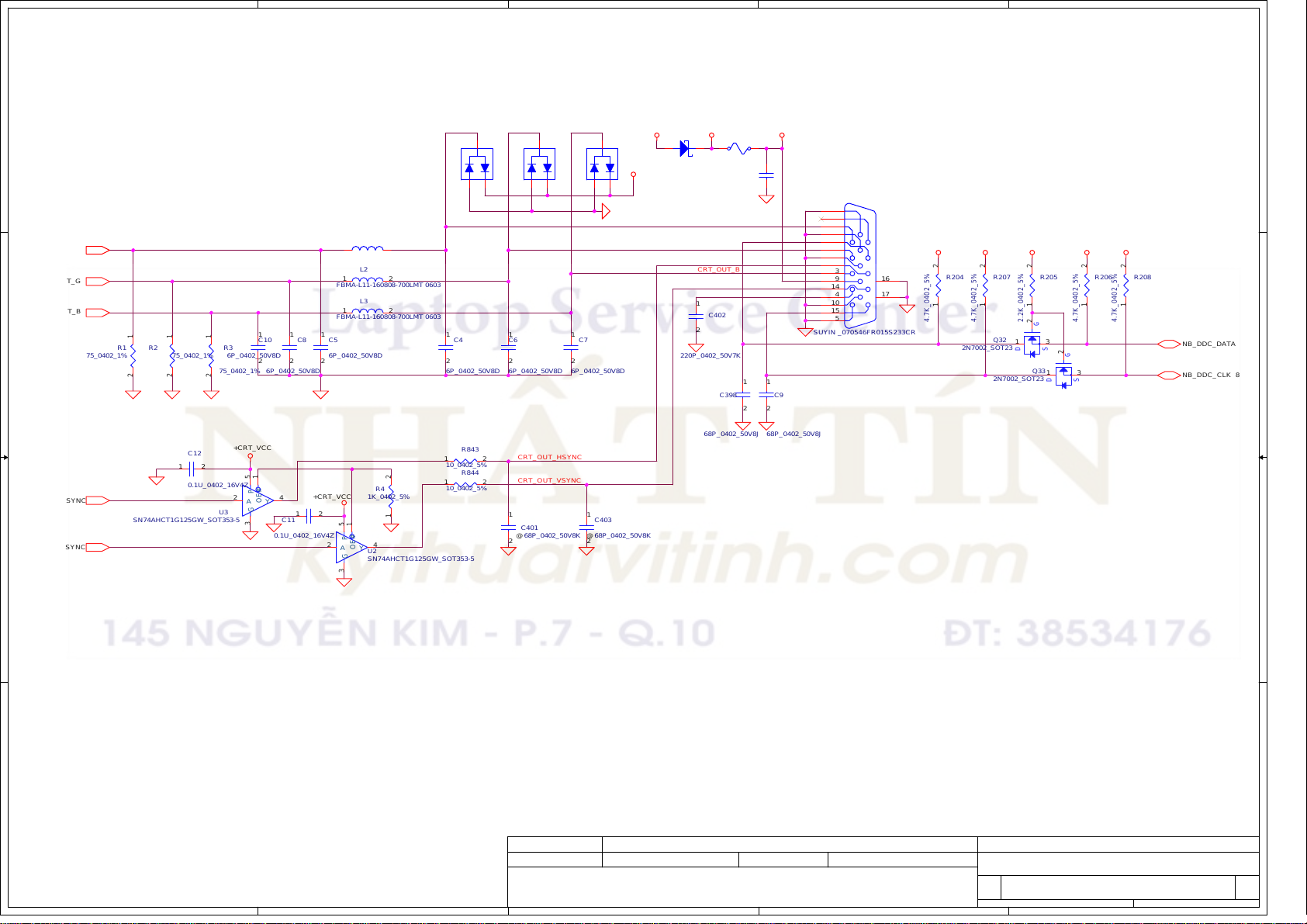

CRT Conn.

page 14

LCD Conn

page 13

LVDS & TV-OUT Conn.

3 3

2 2

CARDBUS

CB1410

PAGE 21

CARD BUS

SOCKET

PAGE 22

VIA6311S

PAGE 23

1394-Port

PAGE 23

page 13

PCI BUS

33MHz (3.3V)

Mini Card

FOR WLAN

PAGE 24

LAN

RTL8100CL

PAGE 20

RJ-45

PAGE 20

PCI-E X1

Mobile Yonah

uFCPGA-478 Pin

PAGE 4,5,6

FSB

533/667 MHz

ATI-RC410MD/ME

VGA M10P Embeded

707 pin BGA

A-Link Express x 4

2.5GHz(1.2V)

Bandwidth 500MB

PAGE 7,8,9

ATI-SB450

564 pin BGA

PAGE 15,16,17,18,19

LPC BUS 33MHz (3.3V)

Embedded

Controller

ENE KB910

PAGE 29

Thermal Sensor

ADM1032ARM

533/667MHz

(1.8V)

Memory Bus

480MHz(5V)

Primary SATA

3.3V,5V 1.5GHz(150MB/s)

Primary SATA

3.3V,5V 1.5GHz(150MB/s)

Secondary

ATA-100 (5V)

AZALIA

24MHz(3.3V)

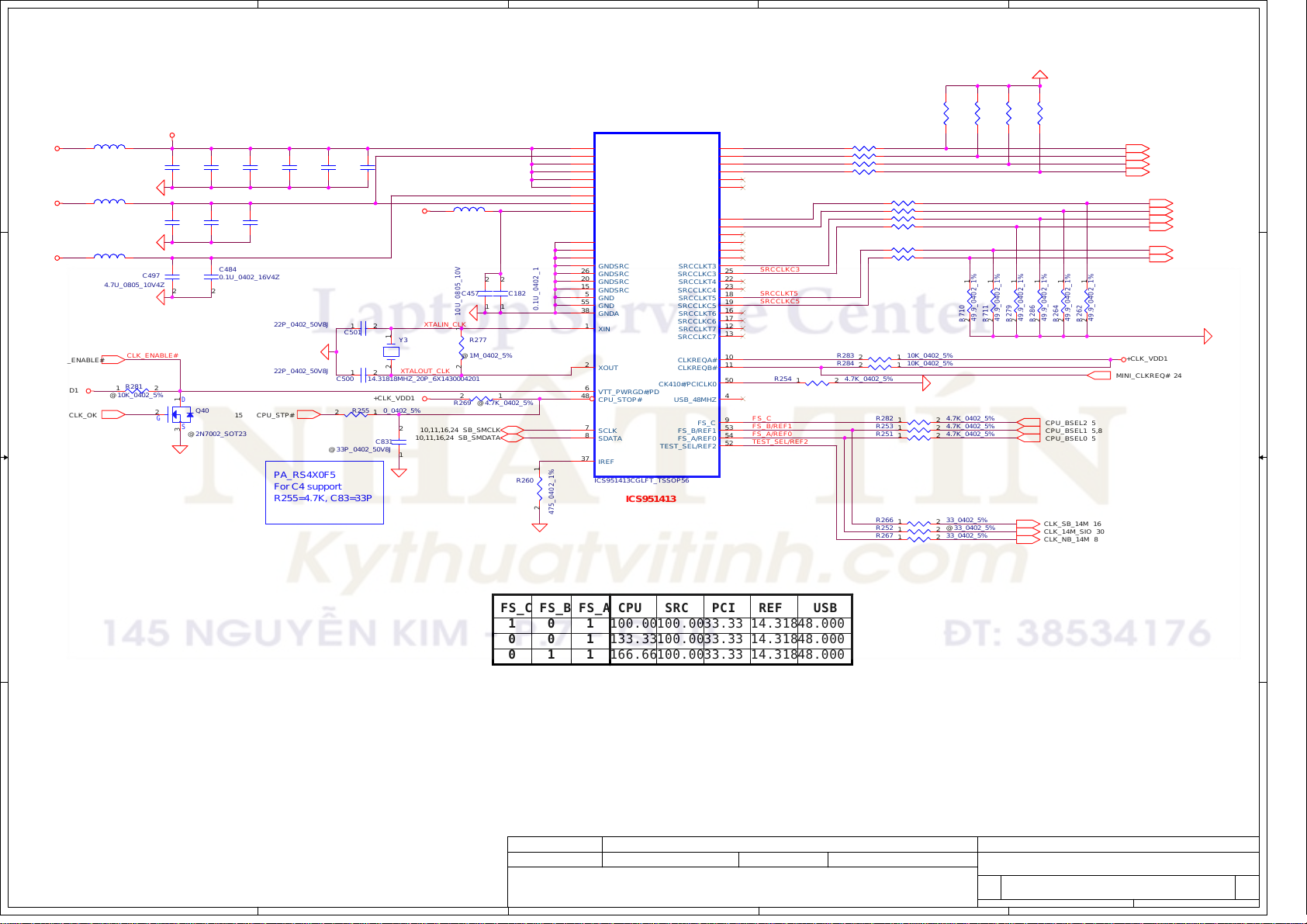

Clock Generator

ICS951413CGT

PAGE 5

SO-DIMM x 2(DDRII)

BANK 0,1,2,3

USB 2.0 Port *5

0,1,2,4,6

SATA HDD0

SATA HDD1

IDE ODD

HD CODEC

PAGE 28

PAGE 17

PAGE 17

PAGE 27

ALC 861

PAGE 11

PAGE 25

PAGE 10,11

CPU VID

PAGE 5

Audio Amplifier

APA2056

PAGE 26

FANController

RTC Battery

DC/DC Interface

Power Buttom

DCIN&DETECTOR

BATT CONN/OTP

CHARGER

3V/5V/

DDR_1.8V/0.9VEP

1.8VCORE

1.5V/PROCHOT

CPU_CORE

PAGE 33

PAGE 15

PAGE 34

PAGE 31

PAGE 35

PAGE 36

PAGE 37

PAGE 38

PAGE 39

PAGE 39

PAGE 40

PAGE 41

MDC

BIOS(1M)

1 1

A

B

& I/O PORT

PAGE 30

Security Classification

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Scan KB

PAGE 32

2006/05/18 2007/05/18

C

Compal Secret Data

PAGE 27

Deciphered Date

Compal Electronics, Inc.

Title

Black Diagram

Size Document Number Rev

IAYAA (LA-3391P) 0.3

Custom

Thursday, O cto ber 05, 2006

D

Date: Sheet

248

E

of

A

B

C

D

E

Rb

0

NC7

SIGNAL

HIGH

LOW

LOW

AD_BID

0.436 V

0.712 V

1.036 V

1.935 V

2.500 V

SLP_S5#STATE

HIGHHIGH

HIGH

HIGH

LOW

LOWLOW

minV

0 V

+VALW

ON

ON

ON

ON

ON

+V

ON

ON

ON

OFF

OFF

AD_BID

0.503 V

0.819 V

1.650 V1.453 V

2.200 V

3.300 V

typV

0 V

+VSSLP_S3#

ON

OFF

OFF

OFF

Clock

ONON

LOW

OFF

OFF

OFF

V

AD_BID

0.289 V0.250 V0.216 V

0.538 V

0.875 V

1.264 V1.185 V

1.759 V

2.341 V

3.300 V

max

0 V

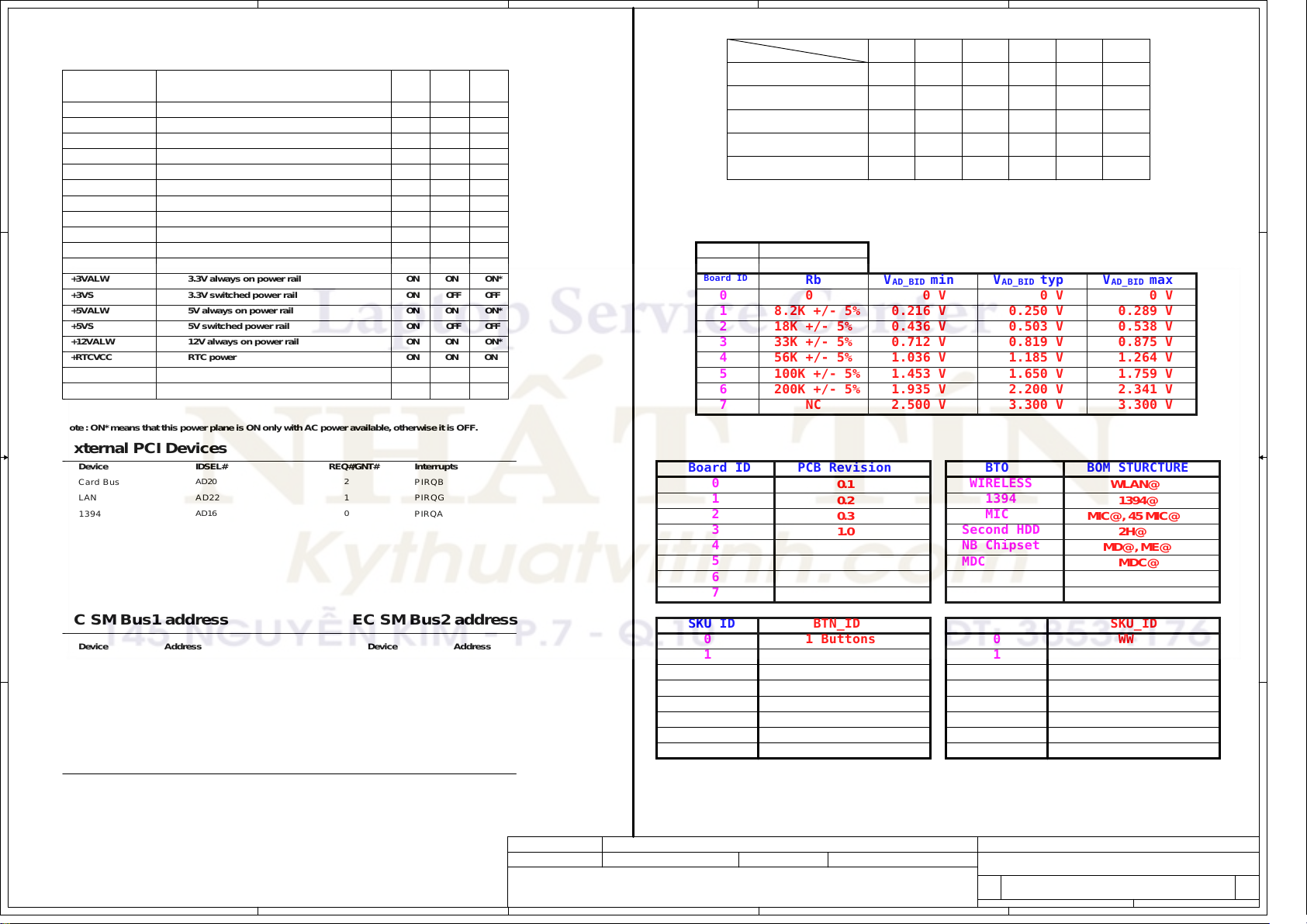

Voltage Rails

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+CPUVID

+VGA_CORE ON OFF OFF1.0V/1.2V switched power rail for VGA chip

+1.2VS 1 .2 VS fo r PCI-Express OFFON OF F

+0.9VS 0.9V switched power rail

+1.5VS

+1.8VS 1.8VS switched power rail OFFOFFON

+1.8VALW 1.8V always on power rail ON*ONON

+1.8V

+3VALW

+3VS

+5VS

+12VALW

+RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapter power supply (19V)

AC or batte ry power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

DOTHAN B

1.8V power rail

3.3V always on power rail

3.3V switched power rail

5V always on power rail

5V switched power rail

RTC power

S1 S3 S5

ON

ON ONONON

ON OFF

ON OFF

ON OFF OF F

ON OFF OF F

ON ON

ON

ON

ON+5VALW

ON

ON

ON

OFF

ON

OFF

ON

ON

ON

OFF

OFF

OFF

ON*ON

OFF

ON*

OFF

ON*12V always on power rail

ON

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board ID Table for AD channel

Vcc

Ra

Board ID

0

1

2

3

4

5

6

3.3V +/- 5%

100K +/- 5%

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

External PCI Devices

Device IDSEL # REQ # / GNT # Interrupts

Card Bus

LAN

1394

AD20

AD22

AD16

2

1PIRQG

0

PIRQB

PIRQA

Board ID

0

1

2

3

4

3 3

5

6

7

PCB Revision

0.1

0.2

0.3

1.0

WIRELESS

1394

MIC

Second HDD

NB Chipset

MDC

BOM STURCTUREBTO

WLAN@

1394@

MIC@, 45 MIC@

2H@

MD@, ME@

MDC@

EC SM Bus1 address

Device

Smart Bat tery

Address Address

EC SM Bus2 address

Device

ADM1032

1001 100X b0001 011X b

SKU ID

0

1

2

3

4

5

6

7

BTN_ID

1 Buttons

7 Buttons

SKU_ID

0

WW

1

2

3

4

JP

5

6

7

SB450 SM Bus address

4 4

Device

Clock Generator

(ICS951413CGLFT)

DDR DIMM0

DDR DIMM1

A

Address

1101 001Xb

1010 0100b

1010 0110b

A4

A6

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/05/18 2007/05/18

C

Compal Secret Data

Deciphered Date

Title

Size Document Number Rev

B

D

Date: Sheet

Compal Electronics, Inc.

Notes List

IAYAA (LA-3391P) 0.3

Thursday, O cto ber 05, 2006

348

E

of

5

4

3

2

1

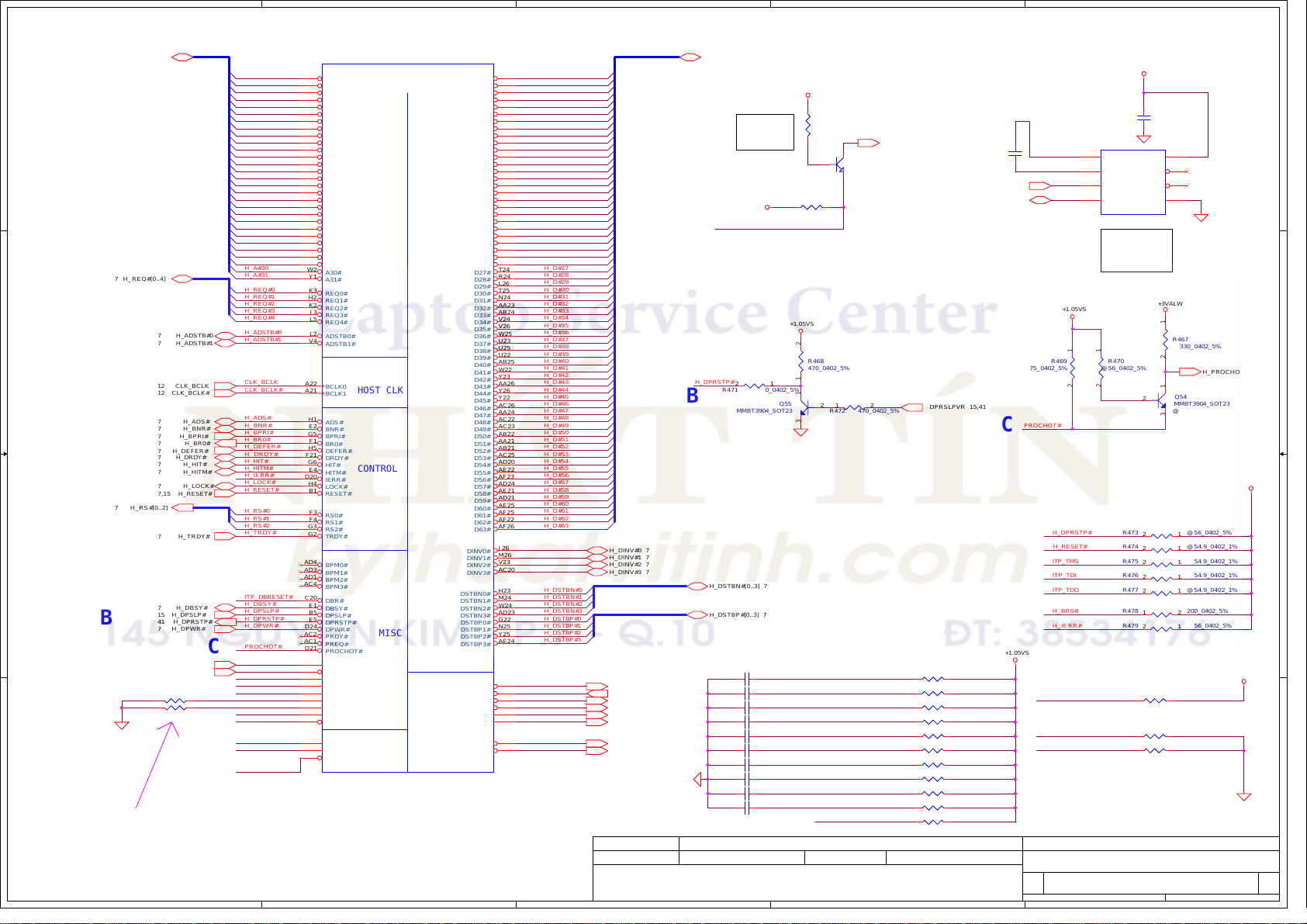

H_A#[3..31]7

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]7

H_ADSTB#07

H_RS#[0..2]7

R482 1K_0402_5%@

R484 51_0402_5%

H_ADSTB#17

CLK_BCLK12

CLK_BCLK#12

H_ADS#7

H_BNR#7

H_BPRI#7

H_BR0#7

H_DEFER#7

H_DRDY#7

H_HIT#7

H_HITM#7

H_LOCK#7

H_RESET#7,15

H_TRDY#7

H_DBSY#7

H_DPSLP#15

H_DPRSTP#41

H_DPWR#7

H_PWRGOOD15

H_CPUSLP#15

12

12

C C

B B

B

H_THERMDA, H_THERMDC routing together.

Trace width / Spacing = 10 / 10 mil

A A

For B-0 ste p ping engineering samples (ES) of Celeron M

processor need to pop this 51 ohm resistor.

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CLK_BCLK

CLK_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_DBRESET#

H_DBSY#

H_DPSLP# H_BR0#

H_DPRSTP#

H_DPWR#

PROCHOT#

C

H_PWRGOOD

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

H_THERMTRIP#

A

JCPU1A

J4

A3#

L4

A4#

M3

A5#

K5

A6#

M1

A7#

N2

A8#

J1

A9#

N3

A10#

P5

A11#

P2

A12#

L1

A13#

P4

A14#

P1

A15#

R1

A16#

Y2

A17#

U5

A18#

R3

A19#

W6

A20#

U4

A21#

Y5

A22#

U2

A23#

R4

A24#

T5

ADDR GROUP

A25#

T3

A26#

W3

A27#

W5

A28#

Y4

A29#

W2

A30#

Y1

A31#

K3

REQ0#

H2

REQ1#

K2

REQ2#

J3

REQ3#

L5

REQ4#

L2

ADSTB0#

V4

ADSTB1#

A22

BCLK0

AD4

AD3

AD1

AC4

C20

D24

AC2

AC1

D21

AC5

AA6

AB3

C26

D25

AB5

AB6

A21

H1

E2

G5

F1

H5

F21

G6

E4

D20

H4

B1

F3

F4

G3

G2

E1

B5

E5

D6

D7

A24

A25

C7

HOST CLK

BCLK1

ADS#

BNR#

BPRI#

BR0#

DEFER#

DRDY#

HIT#

CONTROL

HITM#

IERR#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

BPM0#

BPM1#

BPM2#

BPM3#

DBR#

DBSY#

DPSLP#

DPRSTP#

DPWR#

PRDY#

PREQ#

PROCHOT#

PWRGOOD

SLP#

TCK

TDI

TDO

TEST1

TEST2

TMS

TRST#

THERMAL

THERMDA

DIODE

THERMDC

THERMTRIP#

FOX_PZ47903-2741-42_YONAH

YONAH

MISC

DATA GROUP

LEGACY CPU

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

J26

M26

V23

AC20

H23

M24

W24

AD23

G22

N25

Y25

AE24

A6

A5

C4

B3

C6

B4

D5

A3

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20H_A#23

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_A20M# 15

H_FERR# 15

H_IGNNE# 15

H_INIT# 15

H_INTR 15

H_NMI 15

H_STPCLK# 15

H_SMI# 15

H_D#0H_A#3

E22

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

H_D#[0..63] 7

+CPU_CORE

12

12

1 2

+1.05VS

Q55

R464

47K_0402_5%

R466

56_0402_5%

R468

470_0402_5%

1 2

3 1

1

C

2

B

Q53

E

2SC2411K_SC59

3

2

1 2

R472 470_0402_5%

MAINPWON 16,35,36,38

A

H_DPRSTP#

B

H_DSTBN#[0..3] 7

H_DSTBP#[0..3] 7

PU to 1.05V,

No reserve

longer

+1.05VS

H_THERMTRIP#

R471 0_0402_5%

MMBT3904_SOT23

Place Caps Close to CPU Socket

C666 180P_0402_50V8J@

1 2

C667 180P_0402_50V8J@

1 2

C668 180P_0402_50V8J@

1 2

C669 180P_0402_50V8J@

1 2

C670 180P_0402_50V8J@

1 2

C671 180P_0402_50V8J@

1 2

C672 180P_0402_50V8J@

1 2

C673 180P_0402_50V8J@

1 2

C674 180P_0402_50V8J@

1 2

C675 180P_0402_50V8J@

1 2

2006/05/18 2007/05/18

H_INIT#

H_A20M#

H_CPUSLP#

H_INTR

H_NMI

H_SMI#

H_STPCLK#

H_IGNNE#

H_PWRGOOD

H_FERR#

H_DPSLP#

Compal Secret Data

Deciphered Date

C664

2200P_0402_50V7K

EC_SMB_CK229

EC_SMB_DA229

DPRSLPVR 15,41

R480 390_0402_5%@

1 2

R481 390_0402_5%@

1 2

R485 200_0402_5%

1 2

R486 390_0402_5%@

1 2

R487 390_0402_5%@

1 2

R489 390_0402_5%@

1 2

R491 390_0402_5%

1 2

R492 390_0402_5%@

1 2

R493 200_0402_5%

R494 56_0402_5%

R495 200_0402_5%

2

12

12

1 2

+3VS

1

C663

0.1U_0402_16V4Z

1

H_THERMDA

2

H_THERMDC

75_0402_5%

PROCHOT#

C

+1.05VS

ITP_DBRESET#

ITP_TRST#

Title

Size Document Number Re v

Custom

Date: Sheet

2

3

8

7

+1.05VS

12

R469

H_DPRSTP#

H_RESET#

ITP_TMS

ITP_TDI

ITP_TDO

H_IERR#

ITP_TCK

Compal Electronics, Inc.

Yonah(1/2)-GTLITP

IAYAA (LA-3391P) 0.3

Thursday, October 05, 2006

2

U26

D+

DSCLK

SDATA

ADM1032ARM_RM8

THERM# PU to +3VS

No reserve longer

12

R470

56_0402_5%@

R473 56_0402_5%@

R474 54.9_0402_1%@

R475 54.9_0402_1%

R476 54.9_0402_1%

R477 54.9_0402_1%@

R478 200_0402_5%

R479 56_0402_5%

R483 150_0402_5%

R488 680_0402_5%

R490 54.9_0402_1%

VDD1

ALERT#

THERM#

GND

2

1 2

1

1

6

4

5

+3VALW

12

R467

330_0402_5%

Q54

MMBT3904_SOT23

@

3 1

12

12

12

12

12

12

12

12

12

448

H_PROCHOT# 16

+1.05VS

+3VALW

of

5

4

3

2

1

Length match with i n 2 5 mils

Layout close CPU

20mils

1

C677

2

0.01U_0402_16V7K

CPU_BSEL2

VCCSENSE

VSSSENSE

1

2

PSI#41

CPU_VID041

CPU_VID141

CPU_VID241

CPU_VID341

CPU_VID441

CPU_VID541

CPU_VID641

+GTL_REF0

CPU_BSEL012

CPU_BSEL18,12

CPU_BSEL212

1

1

+1.05VS

+CPU_CORE

PSI#

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

COMP0

COMP1

COMP2

COMP3

JCPU1B

AF7

VCCSENSE

AE7

VSSSENSE

B26

VCCA

K6

VCCP

J6

VCCP

M6

VCCP

N6

VCCP

YONAH

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

VID6

GTLREF

BSEL0

BSEL1

BSEL2

COMP0

COMP1

COMP2

COMP3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

FOX_PZ47903-2741-42_YONAH

K21

M21

N21

R21

V21

W21

G21

AE6

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AD26

B22

B23

C21

R26

U26

AB20

AA20

AF20

AE20

AB18

AB17

AA18

AA17

AD18

AD17

AC18

AC17

AF18

AF17

AF1

D22

C23

C24

AA1

AA4

AB2

AA3

B25

J21

T21

T22

T6

R6

V6

U1

V1

E7

D2

F6

D3

C1

M4

N5

T2

V3

B2

C3

AB26

VSS

AA25

VSS

AD25

VSS

AE26

VSS

AB23

VSS

AC24

VSS

AF24

VSS

AE23

VSS

AA22

VSS

AD22

VSS

AC21

VSS

AF21

VSS

AB19

VSS

AA19

VSS

AD19

VSS

AC19

VSS

AF19

VSS

AE19

VSS

AB16

VSS

AA16

VSS

AD16

VSS

AC16

VSS

AF16

VSS

AE16

VSS

AB13

VSS

AA14

VSS

AD13

VSS

AC14

VSS

AF13

VSS

AE14

VSS

AB11

VSS

AA11

VSS

AD11

VSS

AC11

VSS

AF11

VSS

AE11

VSS

AB8

VSS

AA8

VSS

AD8

VSS

AC8

VSS

AF8

VSS

AE8

VSS

AA5

VSS

AD5

VSS

AC6

VSS

AF6

VSS

AB4

VSS

AC3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AE4

AB1

AA2

AD2

AE1

B6

C5

F5

E6

H6

J5

M5

L6

P6

R5

V5

U6

Y6

A4

D4

E3

H3

G4

K4

L3

P3

N4

T4

U3

Y3

W4

D1

C2

F2

G1

POWER, GROUNG, RESERVED SIGNALS AND NC

+CPU_CORE

D D

+1.05VS

R_A

12

+GTL_REF0

C C

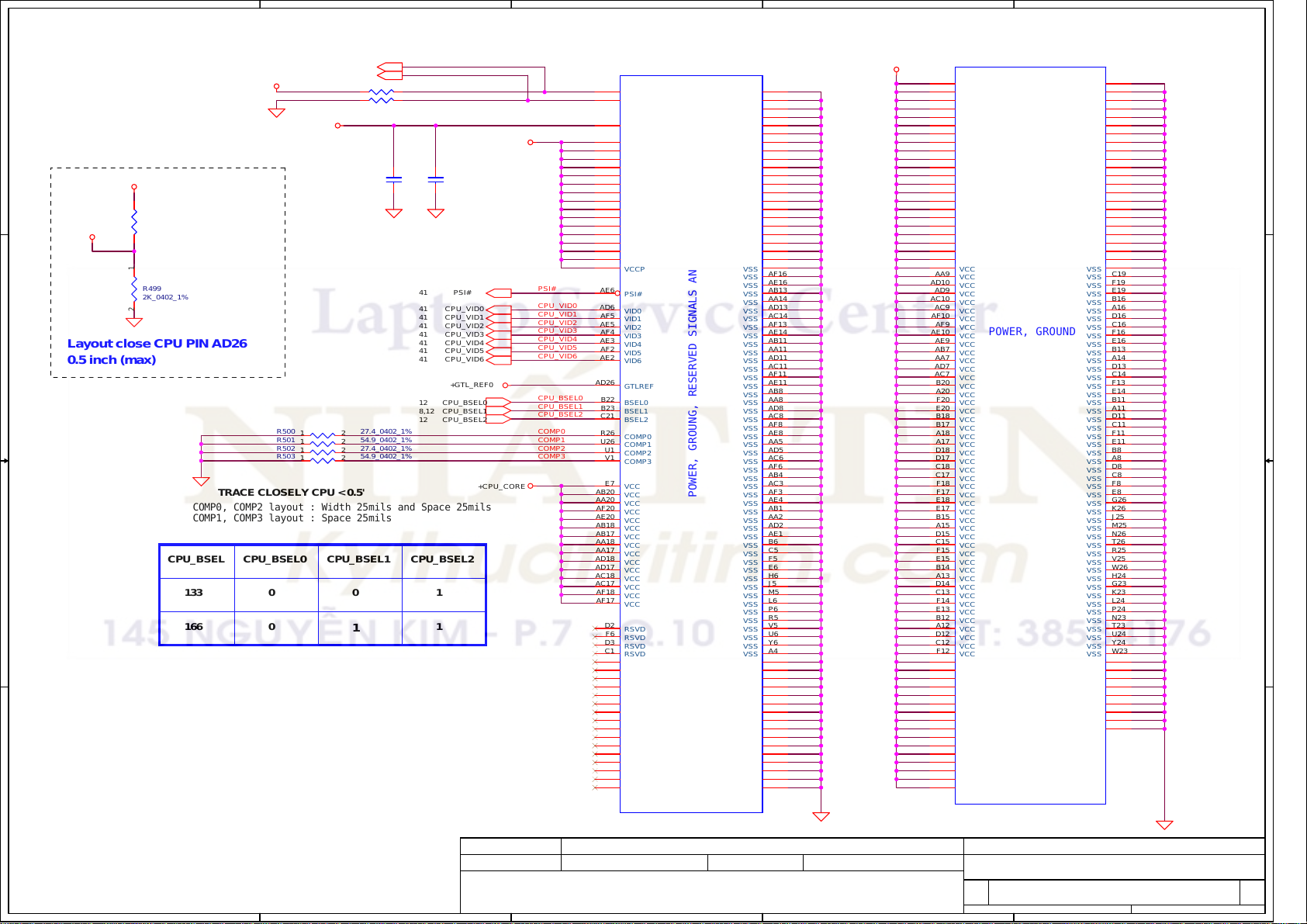

Layout close CPU PIN AD26

0.5 inch (max)

R498

1K_0402_1%

R_B

12

R499

2K_0402_1%

R500 27.4_0402_1%

R501 54.9_0402_1%

R502 27.4_0402_1%

R503 54.9_0402_1%

VCCSENSE41

VSSSENSE41

R496 100_0402_1%

1 2

R497 100_0402_1%

1 2

+1.5VS

C676

10U_0805_10V4Z

1 2

1 2

1 2

1 2

TRACE CLOSELY CPU < 0.5'

COMP0, COMP2 layout : Width 25mils and Space 25mils

COMP1, COMP3 layout : Space 25mils

CPU_BSEL CPU_BSEL0 CPU_BSEL1

B B

133

166

A A

00

0

1

+CPU_CORE

JCPU1C

AE18

VCC

AE17

VCC

AB15

VCC

AA15

VCC

AD15

VCC

AC15

VCC

AF15

VCC

AE15

VCC

AB14

VCC

AA13

VCC

AD14

VCC

AC13

VCC

AF14

VCC

AE13

VCC

AB12

VCC

AA12

VCC

AD12

VCC

AC12

VCC

AF12

VCC

AE12

VCC

AB10

VCC

AB9

VCC

AA10

VCC

AA9

VCC

AD10

VCC

AD9

VCC

AC10

VCC

AC9

VCC

AF10

VCC

AF9

VCC

AE10

AE9

AB7

AA7

AD7

AC7

B20

A20

F20

E20

B18

B17

A18

A17

D18

D17

C18

C17

F18

F17

E18

E17

B15

A15

D15

C15

F15

E15

B14

A13

D14

C13

F14

E13

B12

A12

D12

C12

F12

E12

B10

A10

D10

C10

F10

E10

B9

A9

D9

C9

F9

E9

B7

A7

F7

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

FOX_PZ47903-2741-42_YONAH

YONAH

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K1

J2

M2

N1

T1

R2

V2

W1

A26

D26

C25

F25

B24

A23

D23

E24

B21

C22

F22

E21

B19

A19

D19

C19

F19

E19

B16

A16

D16

C16

F16

E16

B13

A14

D13

C14

F13

E14

B11

A11

D11

C11

F11

E11

B8

A8

D8

C8

F8

E8

G26

K26

J25

M25

N26

T26

R25

V25

W26

H24

G23

K23

L24

P24

N23

T23

U24

Y24

W23

H21

J22

M22

L21

P21

R22

V22

U21

Y21

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INF ORMATION. THIS SHEE T MAY N OT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/05/18 2007/05/18

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

Yonah(2/2)-PWR/GND

Size Doc u ment Number Re v

IAYAA (LA-3391P) 0.3

Custom

Thursday, October 05, 2006

2

Date: Sheet

548

1

of

5

+CPU_CORE

4

3

2

1

Place these inside

socket cavity on L8

D D

(North side

Secondary)

Place these inside

socket cavity on L8

(Sorth side

Secondary)

Place these inside

socket cavity on L8

(North side

C C

Primary)

Place these inside

socket cavity on L8

(Sorth side

Primary)

1

C678

10U_0805_6.3V6M

2

+CPU_CORE

1

C688

10U_0805_6.3V6M

2

+CPU_CORE

1

C698

10U_0805_6.3V6M

2

+CPU_CORE

1

C704

10U_0805_6.3V6M

2

1

C679

10U_0805_6.3V6M

2

1

C689

10U_0805_6.3V6M

2

1

C699

10U_0805_6.3V6M

2

1

C705

10U_0805_6.3V6M

2

1

C680

10U_0805_6.3V6M

2

1

C690

10U_0805_6.3V6M

2

1

C700

10U_0805_6.3V6M

2

1

C706

10U_0805_6.3V6M

2

1

C681

10U_0805_6.3V6M

2

1

C691

10U_0805_6.3V6M

2

1

C701

10U_0805_6.3V6M

2

1

C707

10U_0805_6.3V6M

2

1

C682

10U_0805_6.3V6M

2

1

C692

10U_0805_6.3V6M

2

1

C702

10U_0805_6.3V6M

2

1

C708

10U_0805_6.3V6M

2

1

C683

10U_0805_6.3V6M

2

1

C693

10U_0805_6.3V6M

2

1

C703

10U_0805_6.3V6M

2

1

C709

10U_0805_6.3V6M

2

1

C684

10U_0805_6.3V6M

2

1

C694

10U_0805_6.3V6M

2

22uF 0805 X5R -> 85 degree C

1

C685

10U_0805_6.3V6M

2

1

C695

10U_0805_6.3V6M

2

1

C686

10U_0805_6.3V6M

2

1

C696

10U_0805_6.3V6M

2

1

C687

10U_0805_6.3V6M

2

1

C697

10U_0805_6.3V6M

2

High Frequence Decoupling

Near VCORE regulator.

+1.05VS

C716

1

+

2

330U_D2E_2.5VM_R9

1

C717

0.1U_0402_10V7K

2

1

C718

0.1U_0402_10V7K

2

Place these inside

socket cavity on L8

(North side

Secondary)

1

C719

0.1U_0402_10V7K

2

1

C720

0.1U_0402_10V7K

2

1

C721

0.1U_0402_10V7K

2

1

C722

0.1U_0402_10V7K

2

South Side Secondary

B B

+CPU_CORE

C710

C711

1

+

2

1

+

2

C712

1

+

2

North Side Secondary

C713

1

+

2

C714

1

+

2

C715

1

+

2

330U_D_2VM

9mOhm

7343

A A

PS CAP

330U_D_2VM

9mOhm

7343

PS CAP

330U_D_2VM

@

9mOhm

7343

PS CAP

9mOhm

7343

PS CAP

330U_D_2VM

@

330U_D_2VM

9mOhm

7343

PS CAP

ESR <= 1.5m ohm

Capacitor > 1980uF

5

330U_D_2VM

9mOhm

7343

PS CAP

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/05/18 2007/05/18

3

Compal Secret Data

Deciphered Date

Compal Electronics, Inc.

Title

Yonah Bypass

Size Docu ment Number Rev

IAYAA (LA-3391P) 0.3

B

Thursday, October 05, 2006

2

Date: Sheet

1

of

648

A

H_A#[3..31]4

H_REQ#[0..4]4

H_RS#[0..2]4

U21A

H_A#3

G28

H26

G27

G30

G29

G26

H28

H25

K28

H29

K24

K25

G25

E29

H27

M28

K29

K30

M30

K27

M29

K26

N28

N25

N24

E25

G24

E27

C11

D23

G23

E26

D26

E24

D11

B11

H22

D25

E11

G22

J28

J29

F29

F26

F28

J26

L28

L29

L26

L25

L27

F25

F24

E23

F23

F22

CPU_A3#

CPU_A4#

CPU_A5#

CPU_A6#

CPU_A7#

CPU_A8#

CPU_A9#

CPU_A10#

CPU_A11#

CPU_A12#

CPU_A13#

CPU_A14#

CPU_A15#

CPU_A16#

CPU_REQ0#

CPU_REQ1#

CPU_REQ2#

CPU_REQ3#

CPU_REQ4#

CPU_ADSTB0#

CPU_A17#

CPU_A18#

CPU_A19#

CPU_A20#

CPU_A21#

CPU_A22#

CPU_A23#

CPU_A24#

CPU_A25#

CPU_A26#

CPU_A27#

CPU_A28#

CPU_A29#

CPU_A30#

CPU_A31#

CPU_ADSTB1#

CPU_ADS#

CPU_BNR#

CPU_BPRI#

CPU_DEFER#

CPU_DRDY#

CPU_DBSY#

CPU_LOCK#

CPU_CPURSET#

CPU_RS2#

CPU_RS1#

CPU_RS0#

CPU_TRDY#

CPU_HIT#

CPU_HITM#

CPU_COMP_N

CPU_COMP_P

CPU_VREF

RESERVED0

RESERVED1

CPU_DPWR#

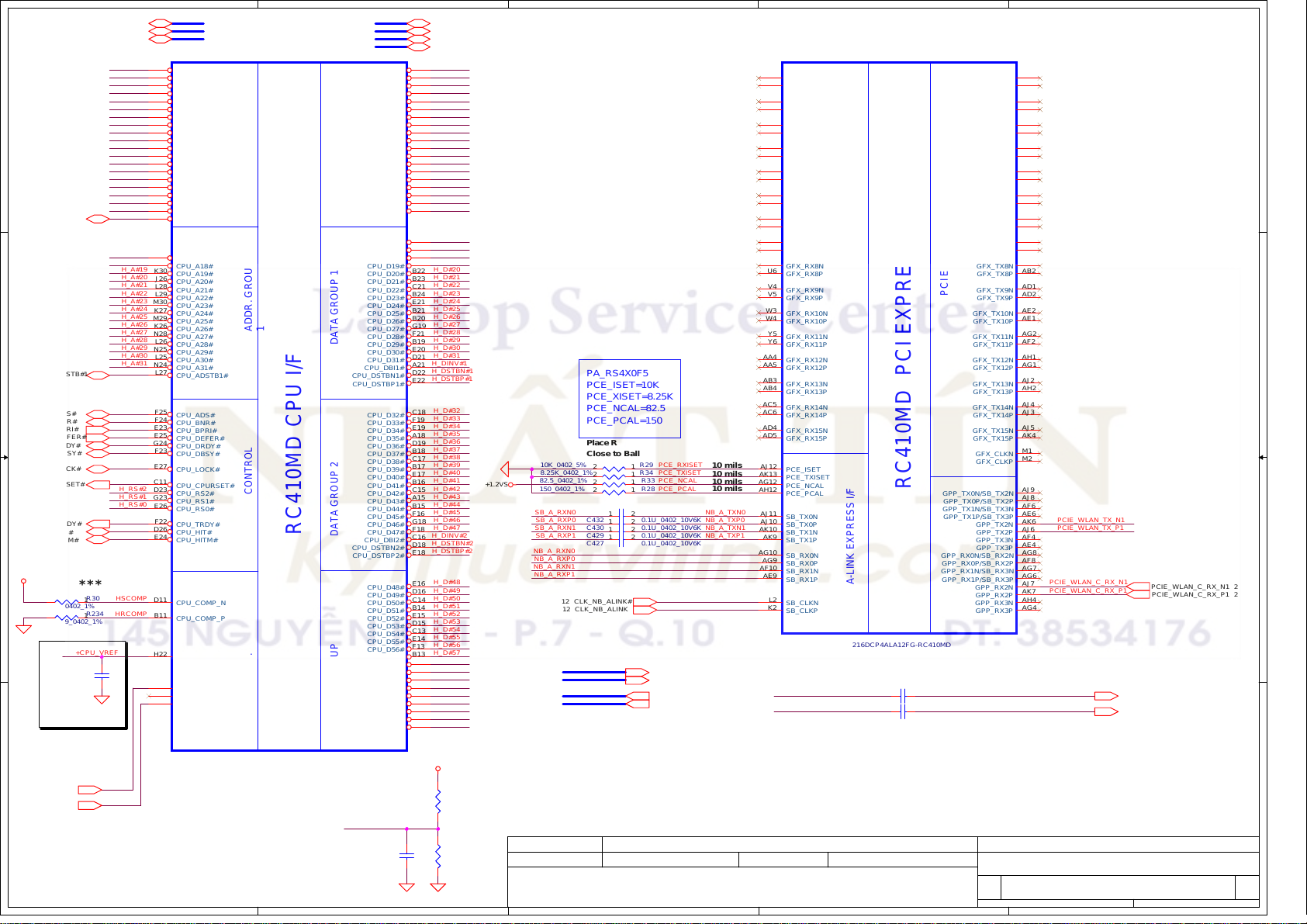

ADDR. GROUP

ADDR. GROUP

PART 1 OF 6

0

1

CPU I/F

CONTROLMISC.

RC410MD

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

***

R30

12

R234

12

+CPU_VREF

1

C123

2

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_RS#2

H_RS#1

H_RS#0

HSCOMP

HRCOMP

1 1

H_ADSTB#04

2 2

H_ADSTB#14

H_ADS#4

H_BNR#4

H_BPRI#4

H_DEFER#4

H_DRDY#4

H_DBSY#4

H_LOCK#4

H_RESET#4,15

H_TRDY#4

H_HIT#4

H_HITM#4

3 3

+1.05VS

24.9_0402_1%

49.9_0402_1%

220P_0402_50V7K

Place C close

to Ball H22

CPU_D0#

CPU_D1#

CPU_D2#

CPU_D3#

CPU_D4#

CPU_D5#

CPU_D6#

CPU_D7#

CPU_D8#

CPU_D9#

CPU_D10#

CPU_D11#

CPU_D12#

CPU_D13#

DATA GROUP 0

CPU_D14#

CPU_D15#

CPU_DBI0#

CPU_DSTBN0#

CPU_DSTBP0#

CPU_D16#

CPU_D17#

CPU_D18#

CPU_D19#

CPU_D20#

CPU_D21#

CPU_D22#

CPU_D23#

CPU_D24#

CPU_D25#

CPU_D26#

CPU_D27#

CPU_D28#

DATA GROUP 1

CPU_D29#

CPU_D30#

CPU_D31#

CPU_DBI1#

CPU_DSTBN1#

CPU_DSTBP1#

CPU_D32#

CPU_D33#

CPU_D34#

CPU_D35#

CPU_D36#

CPU_D37#

CPU_D38#

CPU_D39#

CPU_D40#

CPU_D41#

CPU_D42#

CPU_D43#

CPU_D44#

CPU_D45#

CPU_D46#

CPU_D47#

DATA GROUP 2

CPU_DBI2#

CPU_DSTBN2#

CPU_DSTBP2#

CPU_D48#

CPU_D49#

CPU_D50#

CPU_D51#

CPU_D52#

CPU_D53#

CPU_D54#

CPU_D55#

CPU_D56#

CPU_D57#

CPU_D58#

CPU_D59#

CPU_D60#

CPU_D61#

CPU_D62#

CPU_D63#

DATA GROUP

3

CPU_DBI3#

CPU_DSTBN3#

CPU_DSTBP3#

B

H_D#[0..63] 4

H_DINV#[0..3] 4

H_DSTBN#[0..3] 4

H_DSTBP#[0..3] 4

H_D#0

E28

H_D#1

D28

H_D#2

D29

H_D#3

C29

H_D#4

D30

H_D#5

C30

H_D#6

B29

H_D#7

C28

H_D#8

C26

H_D#9

B25

H_D#10

B27

H_D#11

C25

H_D#12

A27

H_D#13

C24

H_D#14

A24

H_D#15

B26

H_DINV#0

C27

H_DSTBN#0

A28

H_DSTBP#0

B28

H_D#16

C19

H_D#17

C23

H_D#18

C20

H_D#19

C22

H_D#20

B22

H_D#21

B23

H_D#22

C21

H_D#23

B24

H_D#24

E21

H_D#25

B21

H_D#26

B20

H_D#27

G19

H_D#28

F21

H_D#29

B19

H_D#30

E20

H_D#31

D21

H_DINV#1

A21

H_DSTBN#1

D22

E22

C18

F19

E19

A18

D19

B18

C17

B17

E17

B16

C15

A15

B15

F16

G18

F18

C16

D18

E18

E16

D16

C14

B14

E15

D15

C13

E14

F13

B13

A12

C12

E12

D13

D12

B12

E13

F15

G15

H_DSTBP#1

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DINV#2

H_DSTBN#2

H_DSTBP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DINV#3

H_DSTBN#3

H_DSTBP#3

+1.2VS

SB_A_RXN0

SB_A_RXP0

SB_A_RXN1

SB_A_RXP1

NB_A_RXN0

NB_A_RXP0

NB_A_RXN1

NB_A_RXP1

PA_RS4X0F5

PCE_ISET=10K

PCE_XISET=8.25K

PCE_NCAL=82.5

PCE_PCAL=150

Place R

Close to Ball

C432 0.1U_0402_10V6K

C430 0.1U_0402_10V6K

C429 0.1U_0402_10V6K

C427 0.1U_0402_10V6K

CLK_NB_ALINK#12

CLK_NB_ALINK12

SB_A_RXN[0..1]

SB_A_RXP[0..1]

NB_A_RXN[0..1]

NB_A_RXP[0..1]

To SB A-PCIE Link

1 2

1 2

1 2

1 2

C

PCE_RXISET

R2910K_0402_5%

12

PCE_TXISET

R348.25K_0402_1%

12

PCE_NCAL

R3382.5_0402_1%

12

PCE_PCAL

R28150_0402_1%

12

SB_A_RXN[0..1] 15

SB_A_RXP[0..1] 15

NB_A_RXN[0..1] 15

NB_A_RXP[0..1] 15

10 mils

10 mils

10 mils

10 mils

NB_A_TXN0

NB_A_TXP0

NB_A_TXN1

NB_A_TXP1

D

U21C

J4

GFX_RX0N

J5

GFX_RX0P

L4

GFX_RX1N

K4

GFX_RX1P

L5

GFX_RX2N

L6

GFX_RX2P

M4

GFX_RX3N

M5

GFX_RX3P

P4

GFX_RX4N

N4

GFX_RX4P

P5

GFX_RX5N

P6

GFX_RX5P

R4

GFX_RX6N

R5

GFX_RX6P

T3

GFX_RX7N

T4

GFX_RX7P

U5

GFX_RX8N

U6

GFX_RX8P

V4

GFX_RX9N

V5

GFX_RX9P

W3

GFX_RX10N

W4

GFX_RX10P

Y5

GFX_RX11N

Y6

GFX_RX11P

AA4

GFX_RX12N

AA5

GFX_RX12P

AB3

GFX_RX13N

AB4

GFX_RX13P

AC5

GFX_RX14N

AC6

GFX_RX14P

AD4

GFX_RX15N

AD5

GFX_RX15P

AJ12

PCE_ISET

AK13

PCE_TXISET

AG12

PCE_NCAL

AH12

PCE_PCAL

AJ11

SB_TX0N

AJ10

SB_TX0P

AK10

SB_TX1N

AK9

SB_TX1P

AG10

SB_RX0N

AG9

SB_RX0P

AF10

SB_RX1N

AE9

SB_RX1P

L2

SB_CLKN

K2

SB_CLKP

216DCP4ALA12FG-RC410MD

PCIE_WLAN_TX_N1 PCIE_WLAN_C_TX_N1

PCIE_WLAN_TX_P1

PART 3 OF 6

PCI EXPRESS I/F

RC410MD

A-LINK EXPRESS I/F

C723 0.1U_0402_10V7K

1 2

C724 0.1U_0402_10V7K

1 2

GFX_TX0N

GFX_TX0P

GFX_TX1N

GFX_TX1P

GFX_TX2N

GFX_TX2P

GFX_TX3N

GFX_TX3P

GFX_TX4N

GFX_TX4P

GFX_TX5N

GFX_TX5P

GFX_TX6N

GFX_TX6P

GFX_TX7N

GFX_TX7P

GFX_TX8N

GFX_TX8P

GFX_TX9N

PCI EXPRESS I/F

GFX_TX9P

GFX_TX10N

GFX_TX10P

GFX_TX11N

GFX_TX11P

GFX_TX12N

GFX_TX12P

GFX_TX13N

GFX_TX13P

GFX_TX14N

GFX_TX14P

GFX_TX15N

GFX_TX15P

GFX_CLKN

GFX_CLKP

GPP_TX0N/SB_TX2N

GPP_TX0P/SB_TX2P

GPP_TX1N/SB_TX3N

GPP_TX1P/SB_TX3P

GPP_TX2N

GPP_TX2P

GPP_TX3N

GPP_TX3P

GPP_RX0N/SB_RX2N

GPP_RX0P/SB_RX2P

GPP_RX1N/SB_RX3N

GPP_RX1P/SB_RX3P

GPP_RX2N

GPP_RX2P

GPP_RX3N

GPP_RX3P

PCIE_WLAN_C_TX_P1

N2

N1

R2

P2

T1

R1

U2

T2

V1

V2

W2

W1

AA2

Y2

AB1

AA1

AC2

AB2

AD1

AD2

AE2

AE1

AG2

AF2

AH1

AG1

AJ2

AH2

AJ4

AJ3

AJ5

AK4

M1

M2

AJ9

AJ8

AF6

AE6

PCIE_WLAN_TX_N1

AK6

PCIE_WLAN_TX_P1

AJ6

AF4

AE4

AG8

AF8

AG7

AG6

PCIE_W LAN_C_RX_N1

AJ7

PCIE_WLAN_C_RX_P1

AK7

AH4

AG4

E

PCIE_W L AN_ C_RX_N1 24

PCIE_WLAN_C_RX_P1 24

PCIE_WLAN_C_TX_N1 24

PCIE_WLAN_C_TX_P1 24

216DCP4ALA12FG-RC410MD

H_BR0#4

4 4

H_DPWR#4

H_BR0#

H_DPWR#

A

CPU_VREF

Trace=12Mil

Space=15Mil

+CPU_VREF

+1.05VS

12

R38

49.9_0402_1%

***

12

1

C121

2

B

R37

100_0402_1%

1U_0402_6.3V4Z

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

2006/05/18 2007/05/18

C

Compal Secret Data

Deciphered Date

D

Compal Electronics, Inc.

Title

RC410MD-FSB, PCIE,A-PCIE

Size Document Number Rev

IAYAA (LA-3391P) 0.3

B

Thursday, O cto ber 05, 2006

Date: Sheet

748

E

of

A

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DQS#[0..7]

DDR_DM[0..7]

DDR_SMA[0..17]

1 1

+1.8V

12

R42

1

1K_0402_1%

1K_0402_1%

2 2

2

0.1U_0402_10V6K

12

R46

1

2

0.1U_0402_10V6K

MEM_VMODE: 1.8V: DDR2

+1.8V

R242

12

61.9_0603_1%

MEM_COMPN

MEM_COMPP

R237

3 3

4 4

12

61.9_0603_1%

Place these R and C

close to relative Ball.

FSB SPEED

NB STRAPING PINS

BM_REQ# NB_CRT_HSYNC NB_CRT_VSYNC

0

166MHZ

133MHZ

0

BM_REQ#

NB_CRT_VSYNC

NB_CRT_HSYNC

DDR_DQ[0..63] 10,11

DDR_DQS[0..7] 10,11

DDR_DQS#[0..7] 10,11

DDR_DM[0..7] 10,11

DDR_SMA[0..17] 10,11

C172

+DDR_VREF

C174

1

0

R222 4.7K_0402_5%

1 2

+3VS

R228

1 2

4.7K_0402_5%

R20

12

4.7K_0402_5%

Q35

MMBT3904_SOT23

A

DDR_SRAS#10,11

DDR_SCAS#10,11

DDR_SWE#10,11

DDR_CLK0#10

DDR_CLK010

DDR_CLK1#10

DDR_CLK110

DDR_CLK3#11

DDR_CLK311

DDR_CLK4#11

DDR_CLK411

DDR_SCKE010

DDR_SCKE110,11

DDR_SCKE210

DDR_SCKE310,11

DDR_SCS#010

DDR_SCS#110

DDR_SCS#210,11

DDR_SCS#310,11

12

R227

4.7K_0402_5%

2

3 1

+1.8V

10mil

10mil

20mil

1

1

R229

4.7K_0402_5%

1 2

1K_0402_5%

MEM_COMPP

MEM_COMPN

+DDR_VREF

12

DDR_SMA0

DDR_SMA1

DDR_SMA2

DDR_SMA3

DDR_SMA4

DDR_SMA5

DDR_SMA6

DDR_SMA7

DDR_SMA8

DDR_SMA9

DDR_SMA10

DDR_SMA11

DDR_SMA12

DDR_SMA13

DDR_SMA14

DDR_SMA15

DDR_SMA16

DDR_SMA17

DDR_SCS#0

DDR_SCS#1

DDR_SCS#2

DDR_SCS#3

R43

DDR_DQS#0

DDR_DQS0

DDR_DQS#1

DDR_DQS1

DDR_DQS#2

DDR_DQS2

DDR_DQS#3

DDR_DQS3

DDR_DQS#4

DDR_DQS4

DDR_DQS#5

DDR_DQS5

DDR_DQS#6

DDR_DQS6

DDR_DQS#7

DDR_DQS7

+1.05VS

CPU_BSEL1

U21B

AK27

MEM_A0

AJ27

MEM_A1

AH26

MEM_A2

AJ26

MEM_A3

AH25

MEM_A4

AJ25

MEM_A5

AH24

MEM_A6

AH23

MEM_A7

AJ24

MEM_A8

AJ23

MEM_A9

AH27

MEM_A10

AH22

MEM_A11

AJ22

MEM_A12

AF28

MEM_A13

AJ21

MEM_A14

AG27

MEM_A15

AJ28

MEM_A16

AH21

MEM_A17

AJ29

MEM_RAS#

AG28

MEM_CAS#

AH30

MEM_WE#

AC26

MEM_CK0N

AC25

MEM_CK0P

AF16

MEM_CK1N

AE16

MEM_CK1P

V29

MEM_CK2N

V30

MEM_CK2P

AC24

MEM_CK3N

AC23

MEM_CK3P

AG17

MEM_CK4N

AF17

MEM_CK4P

W29

MEM_CK5N

W28

MEM_CK5P

AH20

MEM_CKE0

AJ20

MEM_CKE1

AE24

MEM_CKE2

AE21

MEM_CKE3

AH29

MEM_CS#0

AG29

MEM_CS#1

AH28

MEM_CS#2

AF29

MEM_CS#3

AG30

MEM_ODT0

AE28

MEM_ODT1

AC30

MEM_ODT2/RSV2

Y30

MEM_ODT3/RSV3

AD28

MEM_VMODE

AJ14

MEM_CAP1

N30

MEM_CAP2

AJ15

MEM_COMPP

AE29

MEM_COMPN

AB27

MEM_VREF

AH17

MEM_DQS0N

AJ18

MEM_DQS0P

AF15

MEM_DQS1N

AE14

MEM_DQS1P

AE22

MEM_DQS2N

AF22

MEM_DQS2P

AF26

MEM_DQS3N

AE25

MEM_DQS3P

W26

MEM_DQS4N

W27

MEM_DQS4P

AB30

MEM_DQS5N

AB29

MEM_DQS5P

R25

MEM_DQS6N

P25

MEM_DQS6P

R30

MEM_DQS7N

R29

MEM_DQS7P

CPU_BSEL1 PU to +3VS

No reserve longer

B

PART 2 OF

ADDRESS

DATA CLKMISC

216DCP4ALA12FG-RC410MD

CPU_BSEL1 5,12

B

MEM_DQ0

MEM_DQ1

MEM_DQ2

MEM_DQ3

MEM_DQ4

MEM_DQ5

6

MEMORY I/F

RC410MD

MEM_DQ6

MEM_DQ7

MEM_DQ8

MEM_DQ9

MEM_DQ10

MEM_DQ11

MEM_DQ12

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ16

MEM_DQ17

MEM_DQ18

MEM_DQ19

MEM_DQ20

MEM_DQ21

MEM_DQ22

MEM_DQ23

MEM_DQ24

MEM_DQ25

MEM_DQ26

MEM_DQ27

MEM_DQ28

MEM_DQ29

MEM_DQ30

MEM_DQ31

MEM_DQ32

MEM_DQ33

MEM_DQ34

MEM_DQ35

MEM_DQ36

MEM_DQ37

MEM_DQ38

MEM_DQ39

MEM_DQ40

MEM_DQ41

MEM_DQ42

DATA

MEM_DQ43

MEM_DQ44

MEM_DQ45

MEM_DQ46

MEM_DQ47

MEM_DQ48

MEM_DQ49

MEM_DQ50

MEM_DQ51

MEM_DQ52

MEM_DQ53

MEM_DQ54

MEM_DQ55

MEM_DQ56

MEM_DQ57

MEM_DQ58

MEM_DQ59

MEM_DQ60

MEM_DQ61

MEM_DQ62

MEM_DQ63

MEM_DM0

MEM_DM1

MEM_DM2

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

STRP_DATA

NB_DDC_CLK

MMBT3904_SOT23

C

DDR_DQ0

AJ16

DDR_DQ1

AH16

DDR_DQ2

AJ19

DDR_DQ3

AH19

DDR_DQ4

AH15

DDR_DQ5

AK16

DDR_DQ6

AH18

DDR_DQ7

AK19

DDR_DQ8

AF13

DDR_DQ9

AF14

DDR_DQ10

AE19

DDR_DQ11

AF19

DDR_DQ12

AE13

DDR_DQ13

AG13

DDR_DQ14

AF18

DDR_DQ15

AE17

DDR_DQ16

AF20

DDR_DQ17

AF21

DDR_DQ18

AG23

DDR_DQ19

AF24

DDR_DQ20

AG19

DDR_DQ21

AG20

DDR_DQ22

AG22

DDR_DQ23

AF23

DDR_DQ24

AD25

DDR_DQ25

AG25

AE27

AD27

AE23

AD24

AE26

AD26

AA25

Y26

W24

U25

AA26

Y25

V26

W25

AC28

AC29

AA29

Y29

AD30

AD29

AA30

Y28

U27

T27

N26

M27

U26

T26

P27

P26

U29

T29

P29

N29

U28

T28

P28

N27

AJ17

AG15

AE20

AF25

Y27

AB28

R26

R28

3 1

Q5

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

DDR_DQ32

DDR_DQ33

DDR_DQ34

DDR_DQ35

DDR_DQ36

DDR_DQ37

DDR_DQ38

DDR_DQ39

DDR_DQ40

DDR_DQ41

DDR_DQ42

DDR_DQ43

DDR_DQ44

DDR_DQ45

DDR_DQ46

DDR_DQ47

DDR_DQ48

DDR_DQ49

DDR_DQ50

DDR_DQ51

DDR_DQ52

DDR_DQ53

DDR_DQ54

DDR_DQ55

DDR_DQ56

DDR_DQ57

DDR_DQ58

DDR_DQ59

DDR_DQ60

DDR_DQ61

DDR_DQ62

DDR_DQ63

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

DDR_DM4

DDR_DM5

DDR_DM6

DDR_DM7

R225

1 2

4.7K_0402_5%

2

1 2

2K_0402_5%

R11

CLK_NB_14M12

+3VS

+3VS

SB_PWRGD# 17

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

NB_LUMA13

NB_CRMA13

1 2

R27 75_0402_1%

NB_CRT_R14

NB_CRT_G14

NB_CRT_B14

NB_CRT_HSYNC14

NB_CRT_VSYNC14

1 2

R232 715_0402_1%

NB_DDC_CLK14

NB_DDC_DATA14

CLK_NB_BCLK12

CLK_NB_BCLK#12

NB_EDID_CLK13

NB_EDID_DATA13

R230

1 2

Low: Normal Mode(Fixed)

High: Test Mode

R219

1 2

4.7K_0402_5%

R226

1 2

4.7K_0402_5%

STRP_DATA: DEBUG STRAP

DEFAULT: 1

0: MEMORY CHA NNEL STRAPING

1: E2PROM STRAPING

NB_DDC_CLK: CPU VCC SEL

DEFAULT: 0 1: DESKTOP CPU 0: MOBILE CPU

2006/05/18 2007/05/18

NB_DDC_CLK

NB_DDC_DATA

C422

12

15P_0402_50V8D@

10_0402_5%

1 2

R217 10K_0402_5%

NB_EDID_CLK

NB_EDID_DATA

NB_DVI_DDCDATA

STRP_DATA

TESTMODE

1.8K_0402_5%

NB_EDID_CLK

NB_EDID_DATA

NB_DVI_DDCDATA

Compal Secret Data

NB_COMPS

RSET

15mil

R218

12

U21D

F9

D9

E9

F10

E10

D10

C3

B3

B10

B2

C2

G1

F1

G2

J1

K1

D2

C1

H3

D1

C4

AH13

AJ13

R22

1 2

4.7K_0402_5%

Deciphered Date

Y

C

COMP

RED

GREEN

BLUE

DACHSYNC

DACVSYNC

RSET

DACSCL

DACSDA

OSCIN

OSCOUT

TVCLKIN

CPU_CLKP

CPU_CLKN

I2C_CLK

I2C_DATA

DDC_DATA

STRP_DATA

TESTMODE

THERMALDIODE_P

THERMALDIODE_N

D

CRT & TV

I/F

CLK. GEN.

216DCP4ALA12FG-RC410MD

LVDS_ENBKL

LVDS_ENVDD

D

PART 4 OF 6

RC410MD

SUS_STAT#

NB_PWRGD

E

TXCLK_UN

TXCLK_UP

TXOUT_L0N

TXOUT_L0P

TXOUT_L1N

TXOUT_L1P

TXOUT_L2N

TXOUT_L2P

TXOUT_L3N

TXOUT_L3P

TXCLK_LN

TXCLK_LP

LVDS_BLEN

SUS_STAT#

BMREQ#

TMDS_HPD

+1.8V

R236

220K_0402_5%

1 2

+3VALW

C128 0.1U_0402_16V4Z

14

U5A

P

A

O

B

G

SN74LVC08APW_TSSOP14

7

B4

A4

B5

C6

B6

A6

B7

A7

F7

F8

E5

F5

D5

C5

E6

D6

E7

E8

G6

F6

G3

E2

F2

A3

AH14

E3

H2

J2

3

LVDS_ENBKL

LVDS_ENVDD

2 1

2 1

NB_TXOUT0NB_TXOUT0+

NB_TXOUT1NB_TXOUT1+

NB_TXOUT2NB_TXOUT2+

NB_TXCLKNB_TXCLK+

1 2

1 2

NB_RST#

SUS_STAT#

NB_PWRGD

BM_REQ#

12

R216

10K_0402_5%

D21

CH751H-40_SC76

D20

NB_RST#

CH751H-40_SC76

ENBKL 29

NB_TXOUT0- 13

NB_TXOUT0+ 13

NB_TXOUT1- 13

NB_TXOUT1+ 13

NB_TXOUT2- 13

NB_TXOUT2+ 13

NB_TXCLK- 13

NB_TXCLK+ 13

R21 4.7K_0402_5%@

R224

NB_RST# 15

NB_PWRGD 17

BM_REQ# 15

4.7K_0402_5%@

NB_SUS_STAT# 16

LVDS

POWERGOOD

TXOUT_U0N

TXOUT_U0P

TXOUT_U1N

TXOUT_U1P

TXOUT_U2N

TXOUT_U2P

TXOUT_U3N

TXOUT_U3P

LVDS_BLON

LVDS_DIGON

SYSRESET#

1

2

***

+3VALW

14

U5B

4

P

A

6

O

5

B

G

SN74LVC08APW_TSSOP14

7

Compal Electronics, Inc.

Title

RC410MD-DDR/DISP/MISC

Size Document Number Re v

Date: Sheet

IAYAA (LA-3391P) 0.3

Custom

Thursday, October 05, 2006

NB_ENVDD 13

E

848

of

A

1 2

C65 10U_0805_10V4Z

1 2

C64 10U_0805_10V4Z

1 2

C75 1U_0402_6.3V4Z

1 2

C107 1U_0402_6.3V4Z

1 2

C88 1U_0402_6.3V4Z

1 2

C90 1U_0402_6.3V4Z

1 2

C104 1U_0402_6.3V4Z

1 1

1 2

C73 1U_0402_6.3V4Z

1 2

C74 1U_0402_6.3V4Z

1 2

C105 1U_0402_6.3V4Z

1 2

C36 1U_0402_6.3V4Z

1 2

C55 1U_0402_6.3V4Z

1 2

C89 1U_0402_6.3V4Z

1 2

C71 1U_0402_6.3V4Z

1 2

C106 1U_0402_6.3V4Z

1 2

C49 1U_0402_6.3V4Z

1 2

C50 1U_0402_6.3V4Z

1 2

C79 10U_0805_10V4Z

1 2

C118 10U_0805_10V4Z

1 2

C80 1U_0402_6.3V4Z

2 2

1 2

C100 1U_0402_6.3V4Z

1 2

C131 1U_0402_6.3V4Z

1 2

C91 1U_0402_6.3V4Z

1 2

C69 1U_0402_6.3V4Z

1 2

C133 1U_0402_6.3V4Z

1 2

C150 1U_0402_6.3V4Z

1 2

C151 1U_0402_6.3V4Z

1 2

C92 1U_0402_6.3V4Z

1 2

C95 1U_0402_6.3V4Z

1 2

C99 1U_0402_6.3V4Z

1 2

C144 1U_0402_6.3V4Z

1 2

C59 1U_0402_6.3V4Z

+1.8VS

3 3

4 4

L8

1 2

CHB1608U301_0603

+1.8VS +AVDDI

C46

+1.2VS

+1.2VS

M13

M15

M17

M19

N12

N14

N16

N18

P13

P15

P17

P19

R12

R14

R16

R18

T13

T15

T17

T19

U12

U14

U16

U18

V13

V15

V17

V19

W12

W14

W16

W18

A10

F11

F12

F17

G11

G12

G13

G14

G16

G17

G20

H11

H12

H13

H14

H16

H17

H19

H23

H24

L23

L24

N23

P23

P24

C9

B8

D8

H21

AB26

ATI recommend 2.2uF

1

2

22U_0805_6.3V6M

+LPVDD

1

C33

C30

1U_0402_6.3V4Z

2

10U_0805_10V4Z

U21E

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CORE

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

VDD_CPU

AVDD

AVDDQ

AVDDDI

CPVDD

MPVDD

0.1U_0402_16V4Z

C29

1 2

CHB2012U170_0805

CORE PWR

216DCP4ALA12FG-RC410MD

+AVDD

1

1

C44

1U_0402_6.3V4Z

2

2

L6

5A

+1.05VS

+1.05VS

5A

+AVDDQ

1

1

C53

C57

2

2

10U_0805_10V4Z

2

2

C725

1

1

1U_0402_6.3V4Z

0.1U_0402_16V4Z

220U_Y_4VM@

C48

C54

1

1

2

2

0.1U_0402_16V4Z

A

+AVDD

+AVDDI

+CPVDD

+MPVDD

1U_0402_6.3V4Z

22U_0805_6.3V6M

1

1

+

2

0.1U_0402_16V4Z

C650

C47

1

2

C985

2

1

2

0.1U_0402_16V4Z

B

PART 5 OF

6

POWER

RC410MD

L5

1 2

CHB2012U170_0805

C32

+1.8VS

B

MEM I/F PWR

CPU I/F

PWR

+1.8VS

+

1

2

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

VDDR_MEM

+3VS

VDD_18

VDD_18

VDD_18

VDD_18

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_12

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDA_18

VDDR3

VDDR3

LPVDD

LVDDR18D

LVDDR18A

LVDDR18A

PLLVDD

C289

470U_D2_2.5VM

AB23

AB24

AC13

AC16

AC19

AC21

AC22

AD13

AD16

AD19

AD21

AD22

AD23

AK21

AK24

AK28

T23

T24

V23

V24

Y23

Y24

0.1A

AB22

AB9

J22

J9

AB7

AC7

AC8

AD9

H4

H5

J6

K6

L7

L8

M7

M8

P7

P8

T7

T8

W7

W8

0.75A

AB8

AC10

AC9

AD10

AE11

AF11

AG11

U7

U8

Y7

Y8

G4

G5

J8

C7

H7

H8

H10

+CPVDD

C137

1

2

+1.8V

2A

+1.2VS

2.25A

0.1A

+VDDQ

+LPVDD

+PLLVDD

C648

10U_0805_10V4Z

1

C138

2

10U_0805_10V4Z

C

+1.8V

1 2

C87 0.1U_0402_16V4Z

1 2

C103 0.1U_0402_16V4Z

1 2

C149 0.1U_0402_16V4Z

L4

1 2

CHB1608U301_0603

1 2

C134 0.1U_0402_16V4Z

1 2

C135 0.1U_0402_16V4Z

1 2

C58 0.1U_0402_16V4Z

1 2

C67 0.1U_0402_16V4Z

1 2

C31 10U_0805_10V4Z

1 2

C28 10U_0805_10V4Z

L7

1 2

CHB1608U301_0603

1 2

C70 1U_0402_6.3V4Z

1 2

C56 1U_0402_6.3V4Z

1 2

C68 1U_0402_6.3V4Z

1 2

C63 1U_0402_6.3V4Z

1 2

C62 1U_0402_6.3V4Z

1 2

C51 1U_0402_6.3V4Z

1 2

C45 10U_0805_10V4Z

20mils

20mils

20mils

1

1

2

1

2

1U_0402_6.3V4Z

1 2

0.1U_0402_16V4Z

C37

0.1U_0402_16V4Z

2

L11

CHB1608U301_0603

C114

C158

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITT EN CON SENT O F COMPAL ELECTRONICS, INC.

+1.8VS

L37

1 2

CHB2012U170_0805

+1.8VS

1

2

10U_0805_10V4Z

1U_0402_6.3V4Z

C

+1.8VS

C641

2006/05/18 2007/05/18

1 2

C115 10U_0805_10V4Z

1 2

C72 10U_0805_10V4Z

1 2

C119 10U_0805_10V4Z

1 2

C93 10U_0805_10V4Z

1 2

C166 1U_0402_6.3V4Z

1 2

C76 1U_0402_6.3V4Z

1 2

C124 1U_0402_6.3V4Z

1 2

C152 1U_0402_6.3V4Z

1 2

C132 1U_0402_6.3V4Z

1 2

C117 1U_0402_6.3V4Z

1 2

C122 1U_0402_6.3V4Z

1 2

C139 1U_0402_6.3V4Z

1 2

C110 1U_0402_6.3V4Z

1 2

C86 1U_0402_6.3V4Z

1 2

C77 1U_0402_6.3V4Z

1 2

C130 1U_0402_6.3V4Z

1 2

C129 1U_0402_6.3V4Z

1 2

C141 1U_0402_6.3V4Z

1 2

C140 1U_0402_6.3V4Z

+1.2VS

1 2

C61 10U_0805_10V4Z

1 2

C418 10U_0805_10V4Z

1 2

C66 10U_0805_10V4Z

1 2

C23 10U_0805_10V4Z

1 2

C417 10U_0805_10V4Z

1 2

C22 1U_0402_6.3V4Z

1 2

C25 1U_0402_6.3V4Z

1 2

C85 1U_0402_6.3V4Z

1 2

C43 1U_0402_6.3V4Z

1 2

C84 1U_0402_6.3V4Z

1 2

C102 1U_0402_6.3V4Z

1 2

C41 1U_0402_6.3V4Z

1 2

C42 1U_0402_6.3V4Z

1 2

C78 1U_0402_6.3V4Z

1 2

C40 1U_0402_6.3V4Z

+

1 2

470U_D2_2.5VM

C414

+

1 2

470U_D2_2.5VM

C15

@

+3VS+VDDQ

Place L close to Ball AB26

Place C between Ball AB26,AA27

1 2

1

1

2

C175

2

1U_0402_6.3V4Z

1

C159

0.1U_0402_16V4Z

2

Compal Secret Data

Deciphered Date

+1.8VS+MPVDD

L12

CHB1608U301_0603

D

0.1U_0402_16V4Z

D

AA23

AA24

AA28

AC11

AC12

AC14

AC15

AC17

AC18

AC20

AC27

AD11

AD12

AD14

AD15

AD17

AD18

AD20

AE30

AF12

AF27

AG14

AG16

AG18

AG21

AG24

AG26

AH11

AJ30

AK12

AK15

AK18

AK22

AK25

AK29

C60

AK2

B30

D14

D17

D20

D24

D27

G10

H15

H18

K23

M12

M14

M16

M18

M23

M24

M26

N13

N15

N17

N19

P12

P14

P16

P18

A13

A16

A19

A22

A25

A29

AJ1

F27

F30

J23

J24

J27

J30

E

U21F

VSS

VSS

VSS

A2

VSS

VSS

VSS

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D3

VSS

D4

VSS

VSS

F3

VSS

VSS

F4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J3

VSS

VSS

VSS

K8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

216DCP4ALA12FG-RC410MD

+PLLVDD

1

1

C81

1U_0402_6.3V4Z

2

2

Title

RC410MD PWR/GND

Size Document Number Rev

IAYAA (LA-3391P) 0.3

Custom

Date: Sheet

PART 6 OF 6

GOUNDRC410MD

+1.8VS

L10

1 2

CHB1608U301_0603

1

C82

10U_0805_10V4Z

2

Compal Electronics, Inc.

Thursday, October 05, 2006

E

R13

VSS

R15

VSS

R17

VSS

R19

VSS

R23

VSS

R24

VSS

R27

VSS

T12

VSS

T14

VSS

T16

VSS

T18

VSS

T30

VSS

U13

VSS

U15

VSS

U17

VSS

U19

VSS

U23

VSS

U24

VSS

V12

VSS

V14

VSS

V16

VSS

V18

VSS

V27

VSS

V28

VSS

W13

VSS

W15

VSS

W17

VSS

W19

VSS

W23

VSS

W30

VSS

AA3

VSSA

AA7

VSSA

AA8

VSSA

AB5

VSSA

AB6

VSSA

AC3

VSSA

AD3

VSSA

AD7

VSSA

AD8

VSSA

AE8

VSSA

AF3

VSSA

AF5

VSSA

AF7

VSSA

AF9

VSSA

AG5

VSSA

AH10

VSSA

AH3

VSSA

AH5

VSSA

AH6

VSSA

AH7

VSSA

AH8

VSSA

AH9

VSSA

K5

VSSA

L3

VSSA

M3

VSSA

N5

VSSA

N6

VSSA

N7

VSSA

N8

VSSA

P3

VSSA

R3

VSSA

R7

VSSA

R8

VSSA

T5

VSSA

T6

VSSA

U3

VSSA

V3

VSSA

V7

VSSA

V8

VSSA

W5

VSSA

W6

VSSA

Y3

VSSA

C10

AVSSN

B9

AVSSQ

C8

AVSSDI

J7

LPVSS

G7

LVSSR

G8

LVSSR

G9

LVSSR

H9

PLLVSS

H20

CPVSS

AA27

MPVSS

1

C116

10U_0805_10V4Z

2

of

948

A

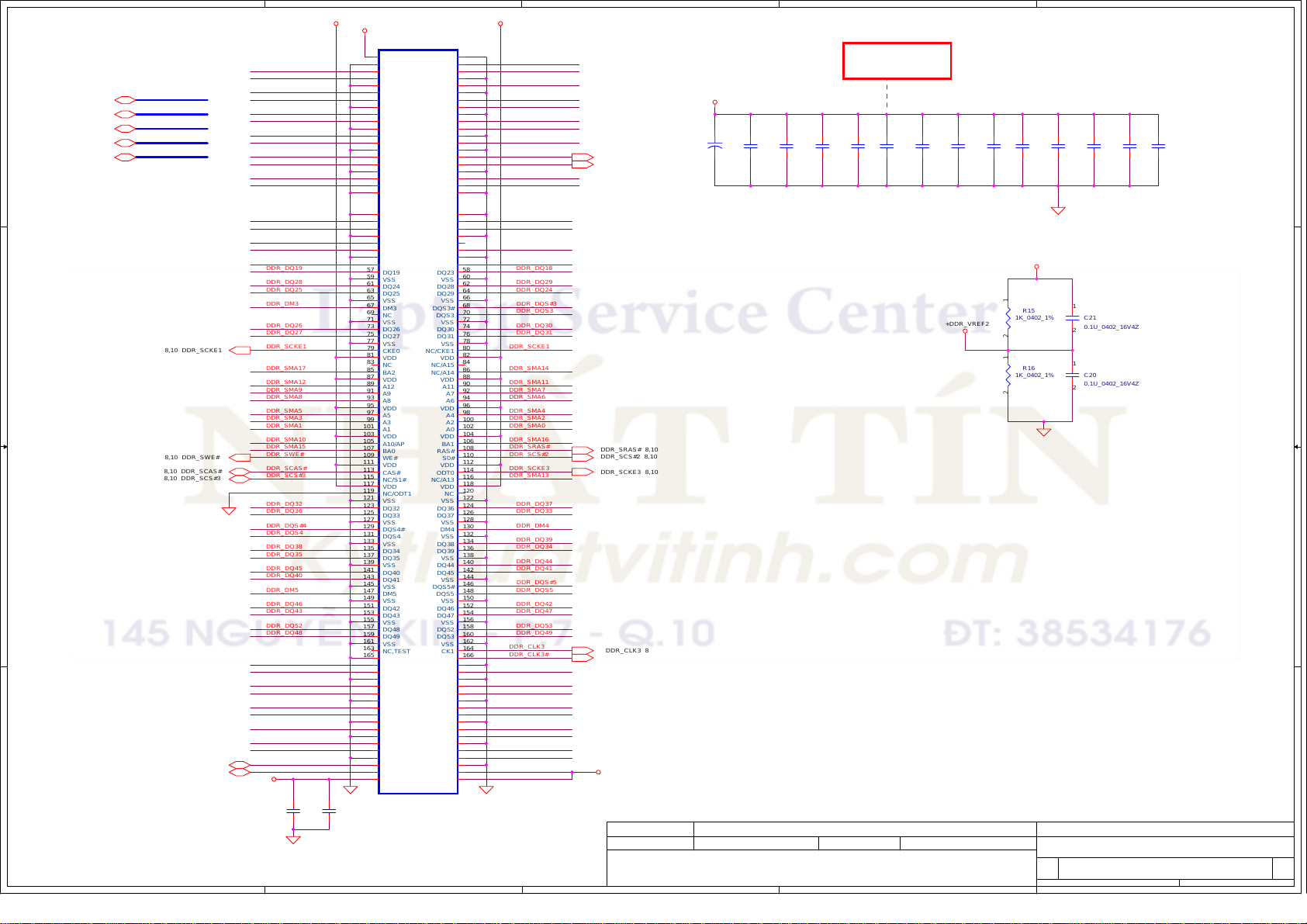

+1.8V +1.8V

DDR_DQ10

DDR_DQ14

DDR_DQS#1

1 1

2 2

DDR_SCKE08

DDR_SWE#8,11

DDR_SCAS#8,11

DDR_SCS#18

3 3

4 4

SB_SMDATA11,12,16,24

SB_SMCLK11,12,16,24

A

DDR_DQS1

DDR_DQ9

DDR_DQ13

DDR_DQ1

DDR_DQ0

DDR_DQS#0

DDR_DQS0

DDR_DQ3 DDR_DQ6

DDR_DQ2 DDR_DQ7

DDR_DQ16

DDR_DQ20

DDR_DQS#2

DDR_DQS2

DDR_DQ23

DDR_DQ19

DDR_DQ28

DDR_DQ25

DDR_DM3

DDR_DQ26

DDR_DQ27

DDR_SCKE0

DDR_SMA17

DDR_SMA12

DDR_SMA9 DDR_SMA7

DDR_SMA8

DDR_SMA5

DDR_SMA3

DDR_SMA1

DDR_SMA10

DDR_SMA15

DDR_SWE#

DDR_SCAS#

DDR_SCS#1

DDR_DQ32

DDR_DQ36

DDR_DQS#4

DDR_DQS4

DDR_DQ38

DDR_DQ35

DDR_DQ45

DDR_DQ40

DDR_DM5

DDR_DQ43

DDR_DQ52

DDR_DQS#6

DDR_DQS6

DDR_DQ50 DDR_DQ55

DDR_DQ54

DDR_DQ61

DDR_DM7 DDR_DQS#7

DDR_DQ62

DDR_DQ58

+3VS

2.2U_0805_10V6K

C187

0.1U_0402_16V4Z

1

1

2

2

Trace=20mil

+DDR_VREF1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

C185

B

201

202

JP16

VREF

VSS

GND1

GND2

DQ0

DQ1

VSS

DQS0#

DQS0

VSS

DQ2

DQ3

VSS

DQ8

DQ9

VSS

DQS1#

DQS1

VSS

DQ10

DQ11

VSS

VSS

DQ16

DQ17

VSS

DQS2#

DQS2

VSS

DQ18

DQ19

VSS

DQ24

DQ25

VSS

DM3

NC

VSS

DQ26

DQ27

VSS

CKE0

VDD

NC

BA2

VDD

A12

A9

A8

VDD

A5

A3

A1

VDD

A10/AP

BA0

WE#

VDD

CAS#

NC/S1#

VDD

NC/ODT1

VSS

DQ32

DQ33

VSS

DQS4#

DQS4

VSS

DQ34

DQ35

VSS

DQ40

DQ41

VSS

DM5

VSS

DQ42

DQ43

VSS

DQ48

DQ49

VSS

NC,TEST

VSS

DQS6#

DQS6

VSS

DQ50

DQ51

VSS

DQ56

DQ57

VSS

DM7

VSS

DQ58

DQ59

VSS

SDA

SCL

VDDSPD

P-TWO_A5692B-A0G16-P

DQ12

DQ13

CK0#

DQ14

DQ15

DQ20

DQ21

DQ22

DQ23

DQ28

DQ29

DQS3#

DQS3

DQ30

DQ31

NC/CKE1

NC/A15

NC/A14

RAS#

ODT0

NC/A13

DQ36

DQ37

DQ38

DQ39

DQ44

DQ45

DQS5#

DQS5

DQ46

DQ47

DQ52

DQ53

CK1#

DQ54

DQ55

DQ60

DQ61

DQS7#

DQS7

DQ62

DQ63

DIMMA

Reverse

B

DM0

VSS

DQ6

DQ7

VSS

VSS

DM1

VSS

CK0

VSS

VSS

VSS

VSS

DM2

VSS

VSS

VSS

VSS

VSS

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

DM4

VSS

VSS

VSS

VSS

VSS

VSS

CK1

VSS

DM6

VSS

VSS

VSS

VSS

VSS

SAO

VSS

DQ4

DQ5

VSS

A11

BA1

S0#

SA1

C

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

NC

52

54

56

58

60

62

64

66

68

70

72

74

76

78

80

82

84

86

88

90

92

A7

94

A6

96

98

A4

100

A2

102

A0

104

106

108

110

112

114

116

118

120

NC

122

124

126

128

130

132

134

136

138

140

142

144

146

148

150

152

154

156

158

160

162

164

166

168

170

172

174

176

178

180

182

184

186

188

190

192

194

196

198

200

DDR_DQ15

DDR_DQ12

DDR_DM1

DDR_DQ8

DDR_DQ11

DDR_DQ4

DDR_DQ5

DDR_DM0

DDR_CLK1

DDR_CLK1#

DDR_DQ17

DDR_DQ21

DDR_DM2

DDR_DQ22

DDR_DQ18

DDR_DQ29

DDR_DQ24

DDR_DQS#3

DDR_DQS3

DDR_DQ30

DDR_DQ31

DDR_SCKE0

DDR_SMA14

DDR_SMA11

DDR_SMA6

DDR_SMA4

DDR_SMA2

DDR_SMA0

DDR_SMA16

DDR_SRAS#

DDR_SCS#0

DDR_SCKE2

DDR_SMA13

DDR_DQ37

DDR_DQ33

DDR_DM4

DDR_DQ39

DDR_DQ34

DDR_DQ44

DDR_DQ41

DDR_DQS#5

DDR_DQS5

DDR_DQ42DDR_DQ46

DDR_DQ47

DDR_DQ53

DDR_DQ49DDR_DQ48

DDR_CLK0

DDR_CLK0#

DDR_DM6

DDR_DQ51

DDR_DQ60DDR_DQ56

DDR_DQ57

DDR_DQS7

DDR_DQ63

DDR_DQ59

C

+3VS

DDR_DQ[0..63]

DDR_DQS[0..7]

DDR_DQS#[0..7]

DDR_DM[0..7]

DDR_SMA[0..17]

DDR_CLK1 8

DDR_CLK1# 8

DDR_SRAS# 8,11

DDR_SCS#0 8

DDR_SCKE2 8

DDR_CLK0 8

DDR_CLK0# 8

D

DDR_DQ[0..63] 8,11

DDR_DQS[0..7] 8,11

DDR_DQS#[0..7] 8,11

DDR_DM[0..7] 8,11

DDR_SMA[0..17] 8,11

C148

220U_Y_4VM

DDR_SCKE18,11

DDR_SCS#28,11

+1.8V

Security Classification

Issued Date

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

D

1

+

2

+0.9VS

E

C143 0.1U_0402_16V4Z

1

2

C445 0.1U_0402_16V4Z

C447 0.1U_0402_16V4Z

1

1

2

2

2006/05/18 2007/05/18

E

C154 0.1U_0402_16V4Z

C111 0.1U_0402_16V4Z

1

2

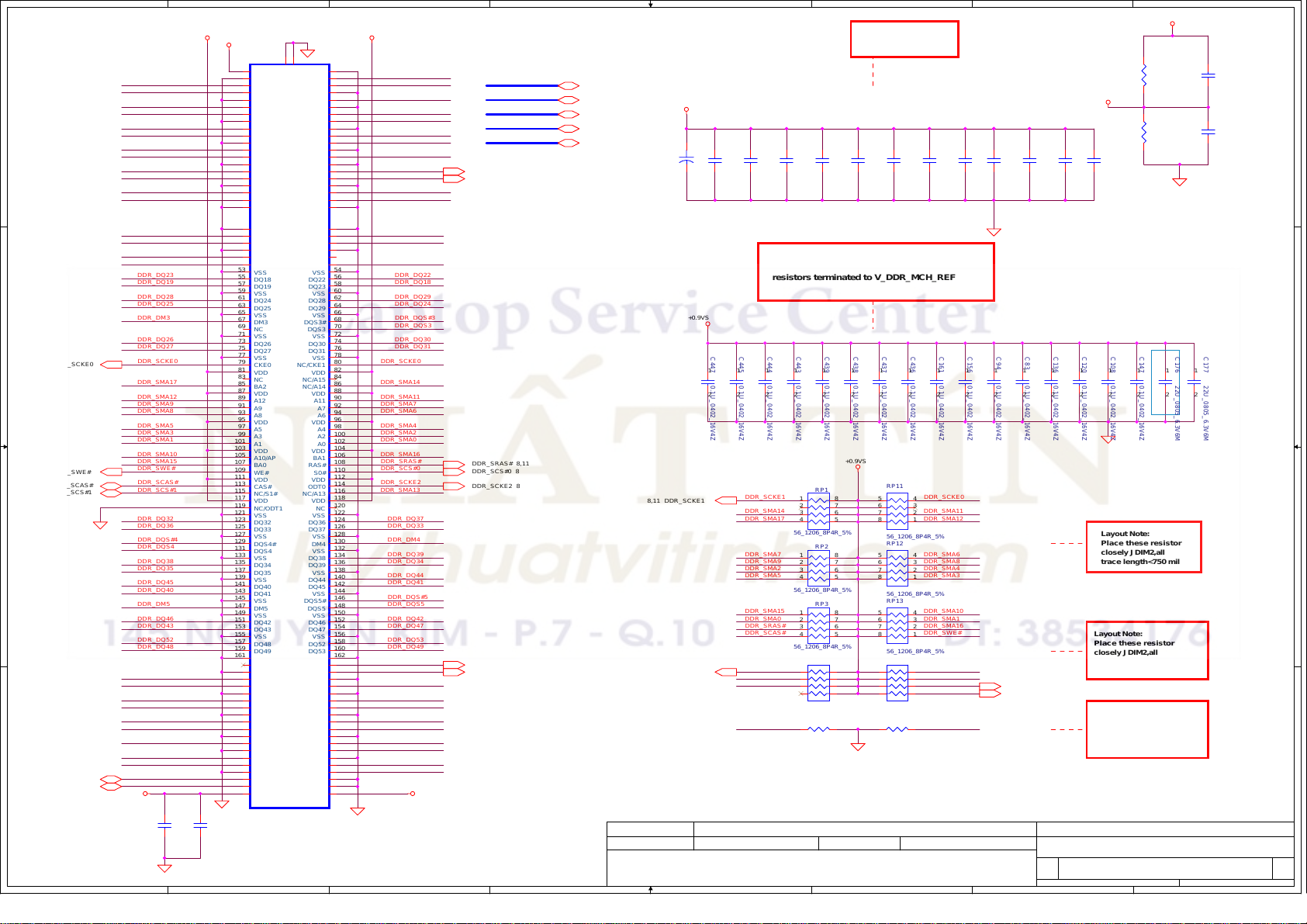

Layout Note:

Place one cap close to every 2 pullup

resistors terminated to V_DDR_MCH_REF

C444 0.1U_0402_16V4Z

1

2

DDR_SCKE1 DDR_SCKE0

DDR_SMA17

DDR_SMA9

DDR_SMA2

DDR_SMA5

DDR_SMA15

DDR_SMA0

DDR_SRAS#

DDR_SCAS#

DDR_SCS#2

DDR_SMA13

DDR_SCS#1

DDR_SCKE3 DDR_SCKE2

C101 0.1U_0402_16V4Z

1

1

2

2

C439 0.1U_0402_16V4Z

C443 0.1U_0402_16V4Z

1

1

2

2

RP1

1 8

2 7

3 6

4 5

56_1206_8P4R_5%

RP2

1 8

2 7

3 6

4 5

56_1206_8P4R_5%

RP3

1 8

2 7

3 6

4 5

56_1206_8P4R_5%

RP4

1 8

2 7

3 6

4 5

56_1206_8P4R_5%

1 2

R12

180_0402_5%

+0.9VS

Compal Secret Data

Deciphered Date

F

Layout Note:

Place near JDIM1

C163 0.1U_0402_16V4Z

C162 0.1U_0402_16V4Z

1

1

2

2

C437 0.1U_0402_16V4Z

C438 0.1U_0402_16V4Z

1

1

2

2

RP11

56_1206_8P4R_5%

RP12

56_1206_8P4R_5%

RP13

56_1206_8P4R_5%

RP14

56_1206_8P4R_5%

1 2

R17

180_0402_5%

F

C436 0.1U_0402_16V4Z

1

2