5

5

5

5

8

2

4

東芝トランジスタ シリコンNPNエピタキシャルプレーナ形

MT6L71FS

○ VHF~UHF 帯低位相雑音タイプ

Fine pich small mold パッケージ(6 ピン)に 2 素子を内蔵しています。

• 低位相雑音タイプです。

• OSC / Buffer 用途に最適です。

搭載チップ

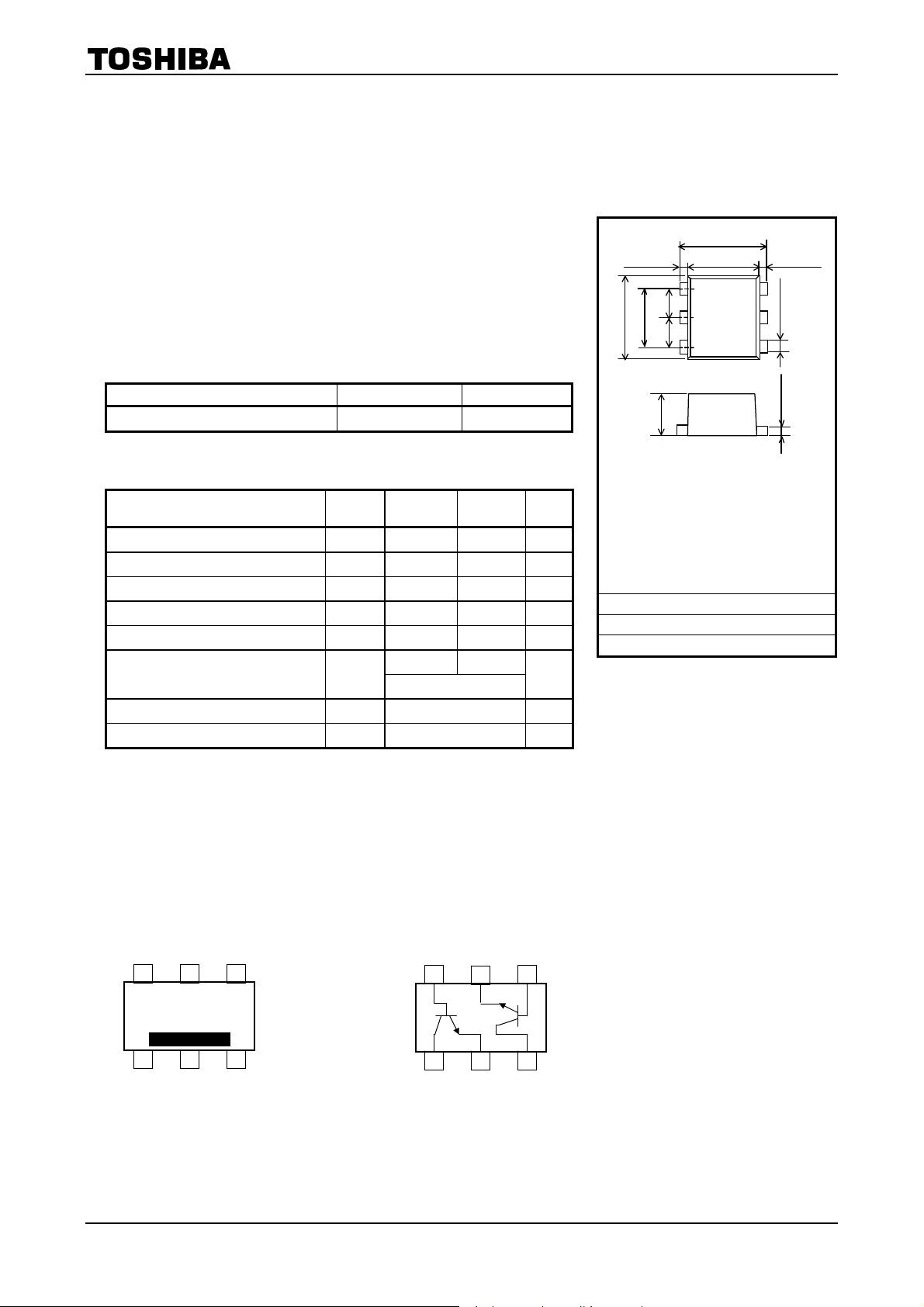

0.1±0.05

1.0±0.05

0.7±0.0

0.3

0.3

1

2

3

MT6L71FS

単位: mm

1.0±0.05

0.8±0.05

6

5

4

0.1±0.05

0.15±0.0

Q1 Q2

相当する 3 ピン: fSM−Mold 製品

MT3S07FS MT3S11AFS

絶対最大定格 (Ta = 25°C)

項目 記号 Q1 Q2 単位

コレクタ・ベース間電圧 V

コレクタ・エミッタ間電圧 V

エミッタ・ベース間電圧 V

コレクタ電流 IC 25 40 mA

ベース電流 IB 10 10 mA

許容損失 PC(注 1)

接合温度 Tj 125 °C

保存温度 T

10 13 V

CBO

5 6 V

CEO

1.5 1 V

EBO

stg

100 90

2 素子動作 105

−55~125 °C

mW

質量: 1 mg (標準)

fS6

JEDEC

JEITA

東芝

-0.0

+0.0

0.4

1.

2.

3.

4.

5.

6.

コレクタ 1

エミッタ1

コレクタ2

ベース2

エミッタ2

ベース

1

2-1F1A

0.1±0.05

(C1)

(E1)

(C2)

(B2)

(E2)

(B1)

―

―

注: 本製品の使用条件 (使用温度/電流/電圧等) が絶対最大定格以内での使用においても、高負荷 (高温および大

電流/高電圧印加、多大な温度変化等) で連続して使用される場合は、信頼性が著しく低下するおそれがあり

ます。

弊社半導体信頼性ハンドブック (取り扱い上のご注意とお願いおよびディレーティングの考え方と方法) お

よび個別信頼性情報 (信頼性試験レポート、推定故障率等) をご確認の上、適切な信頼性設計をお願いします。

注 1: 10 mm ×10 mm × 1.0mm(t) のガラスエポキシプリント基板実装時

現品表示

(top view)

内部接続図 (top view)

6 5 4

1W

1 2 3

B1 E2

Q1

C1

E1

B2

Q2

C2

2011-01-07 1

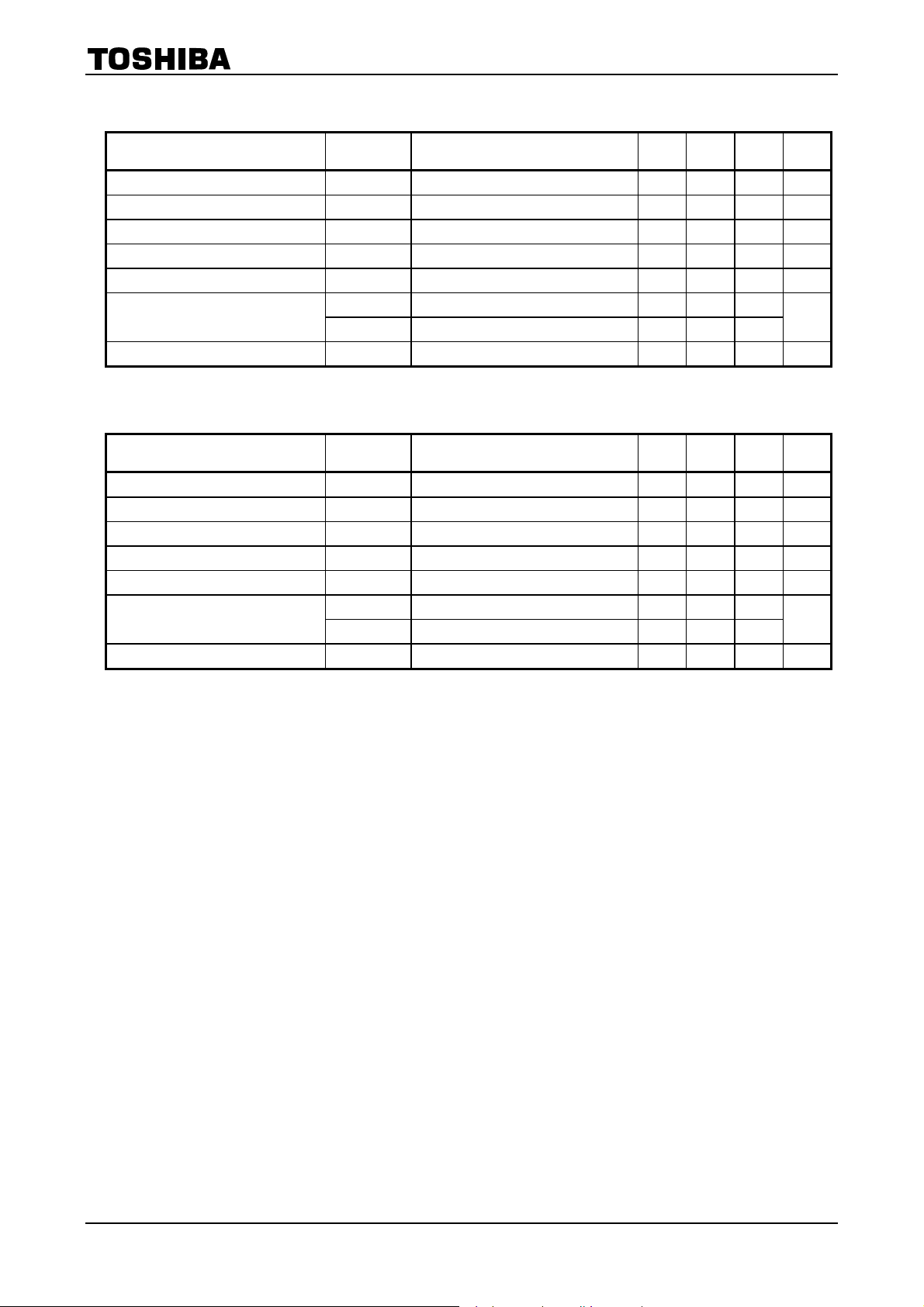

電気的特性 Q1 (Ta = 25°C)

項目 記号 測定条件 最小 標準 最大 単位

MT6L71FS

コレクタしゃ断電流 I

エミッタしゃ断電流 I

直流電流増幅率 hFE VCE = 1 V, IC = 5 mA 70 ⎯ 140 ⎯

帰還容量 C

トランジション周波数 f

挿入電力利得

雑音指数 NF VCE = 1 V, IC = 5 mA, f = 2 GHz ⎯ 1.5 3 dB

VCB = 5 V, IE = 0 ⎯ ⎯ 0.1 μA

CBO

VEB = 1 V, IC = 0 ⎯ ⎯ 1 μA

EBO

(注) VCB = 1 V, IE = 0, f = 1 MHz ⎯ 0.4 0.65 pF

re

VCE = 3 V, IC = 10 mA 10 12 ⎯ GHz

T

⎪S

⎪2 (1) VCE = 1 V, IC = 5 mA, f = 2 GHz ⎯ 8 ⎯

21e

⎪2 (2) VCE = 3 V, IC = 15 mA, f = 2 GHz 7.5 10 ⎯

⎪S

21e

電気的特性 Q2 (Ta = 25°C)

項目 記号 測定条件 最小 標準 最大 単位

コレクタしゃ断電流 I

エミッタしゃ断電流 I

直流電流増幅率 hFE VCE = 1 V, IC = 5 mA 100 ⎯ 160 ⎯

帰還容量 C

トランジション周波数 f

挿入電力利得

雑音指数 NF VCE = 1 V, IC = 5 mA, f = 2 GHz ⎯ 2.4 3.2 dB

注 : C

は 3 端子法でエミッタ端子をブリッジのガード端子に接続して測定する。

re

VCB = 5 V, IE = 0 ⎯ ⎯ 0.1 μA

CBO

VEB = 1 V, IC = 0 ⎯ ⎯ 1 μA

EBO

(注) VCB = 1 V, IE = 0, f = 1 MHz ⎯ 0.6 0.85 pF

re

VCE = 1 V, IC = 5 mA 4 6 ⎯ GHz

T

⎪S

⎪2 (1) VCE = 1 V, IC = 5 mA, f = 2 GHz ⎯ 3.5 ⎯

21e

⎪2 (2) VCE = 3 V, IC = 20 mA, f = 2 GHz 4 6.5 ⎯

⎪S

21e

取り扱い上の注意

dB

dB

この製品は構造上静電気に弱いため製品を取り扱う際、作業台・人・はんだごてなどに対し必ず静電対策を講じて下さい。

2011-01-07 2

MT6L71FS

製品取り扱い上のお願い

• 本資料に掲載されているハードウェア、ソフトウェアおよびシステム(以下、本製品という)に関する情

報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

• 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を

得て本資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

• 当社は品質、信頼性の向上に努めていますが、半導体製品は一般に誤作動または故障する場合があります。

本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないよう

に、お客様の責任において、お客様のハードウェア・ソフトウェア・システムに必要な安全設計を行うこ

とをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、デー

タシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の

取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品デー

タ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する

場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断し

てください。

• 本製品は、一般的電子機器(コンピュータ、パーソナル機器、事務機器、計測機器、産業用ロボット、家

電機器など)または本資料に個別に記載されている用途に使用されることが意図されています。本製品は、

特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な

財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下“特定用途”とい

う)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、

航空・宇宙機器、医療機器、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各

種安全関連機器、昇降機器、電力機器、金融関連機器などが含まれます。本資料に個別に記載されている

場合を除き、本製品を特定用途に使用しないでください。

• 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

• 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用すること

はできません。

• 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して

当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

• 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報

に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、

情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

• 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あ

るいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、

「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行っ

てください。

• 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず弊社営業窓口までお問合せください。本

製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分

調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じ

た損害に関して、当社は一切の責任を負いかねます。

2011-01-07 3

Loading...

Loading...