THIS DRAWING AND SPECIFICATIONS,HEREIN,ARE THE PROPERTY OF INVENTEC

CORPORATION AND SHALL NOT BE REPODUCED,COPIED,OR USED IN WHOLE OR

IN PART AS THE BASIS FOR THE MANUFACTURE OR SALE OF ITEMS WITHOUT

WRITTEN PERMISSION,INVENTEC CORPORATION,2009 ALL RIGHT RESERVED.

8

7 6 5 4 3 2 1

HSF Property:ROHS or Halogen-Free

E

D

DAKAR10F/FG

(45W CPU)

MP(A02) BUILD

2012.03.23

FF

E

D

C

B

A

21-OCT-2002

DATE CHANGE NO.

8

REV

7 6 5 4 3

DRAWER

DESIGN

CHECK

RESPONSIBLE

SIZE=

FILE NAME:

P/N

LOREN

LOREN

BRYAN

BRYAN

C

B

A

POWER

DATEDATEEE

EDISON

EDISON

BY

BY

2

2012.03.23

2012.03.23

2012.03.23

2012.03.23

VER:

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

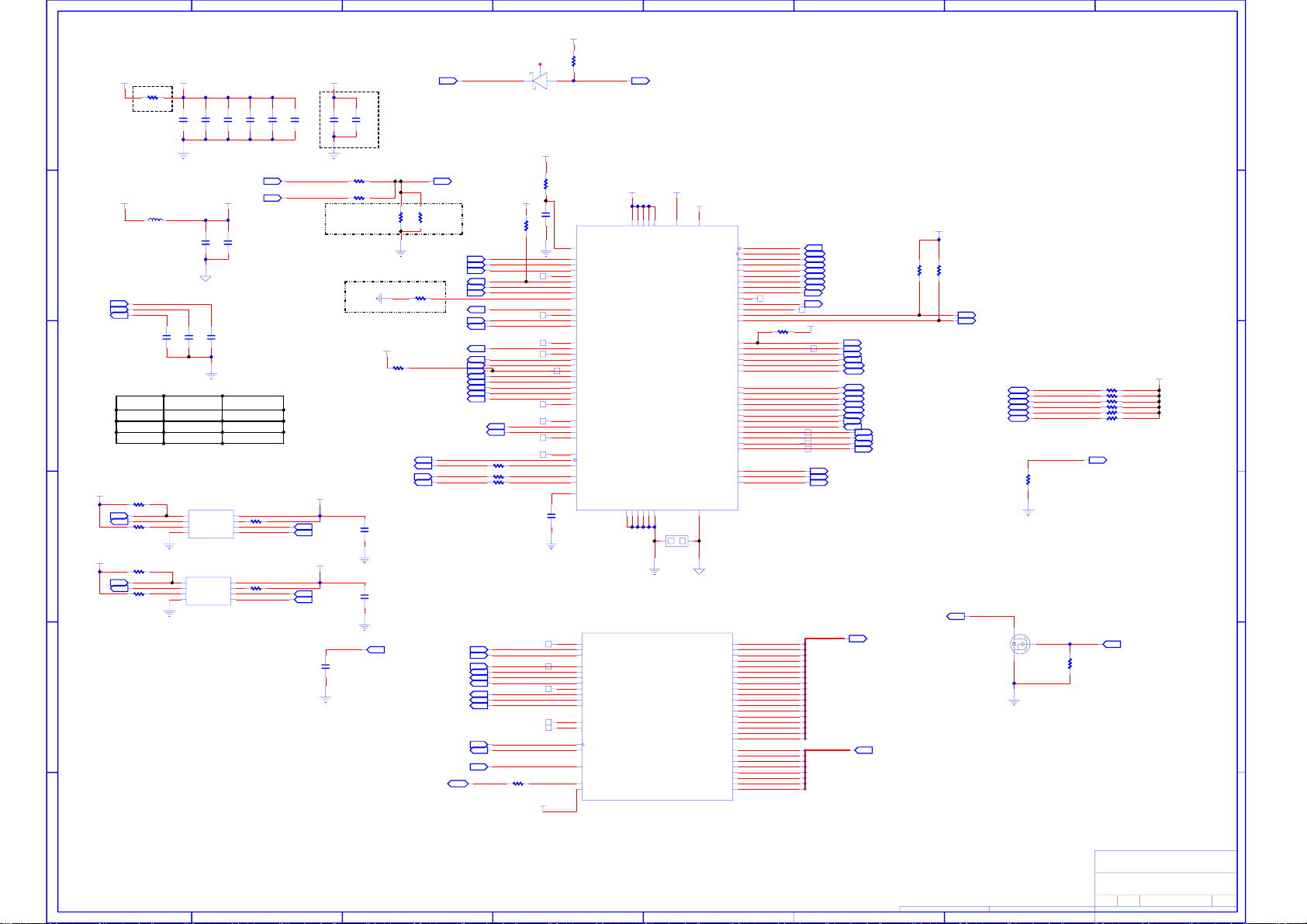

DAKAR10F/FG MAIN BOARD

CODE

SIZE

C

CS

SHEET

DOC.NUMBER REV

1310A2491301-0-MTR

1310xxxxx-0-0

of

1

X01

701

2012.03.23

2012.03.23

2012.03.23

2012.03.23

XXX

8 7

6 5

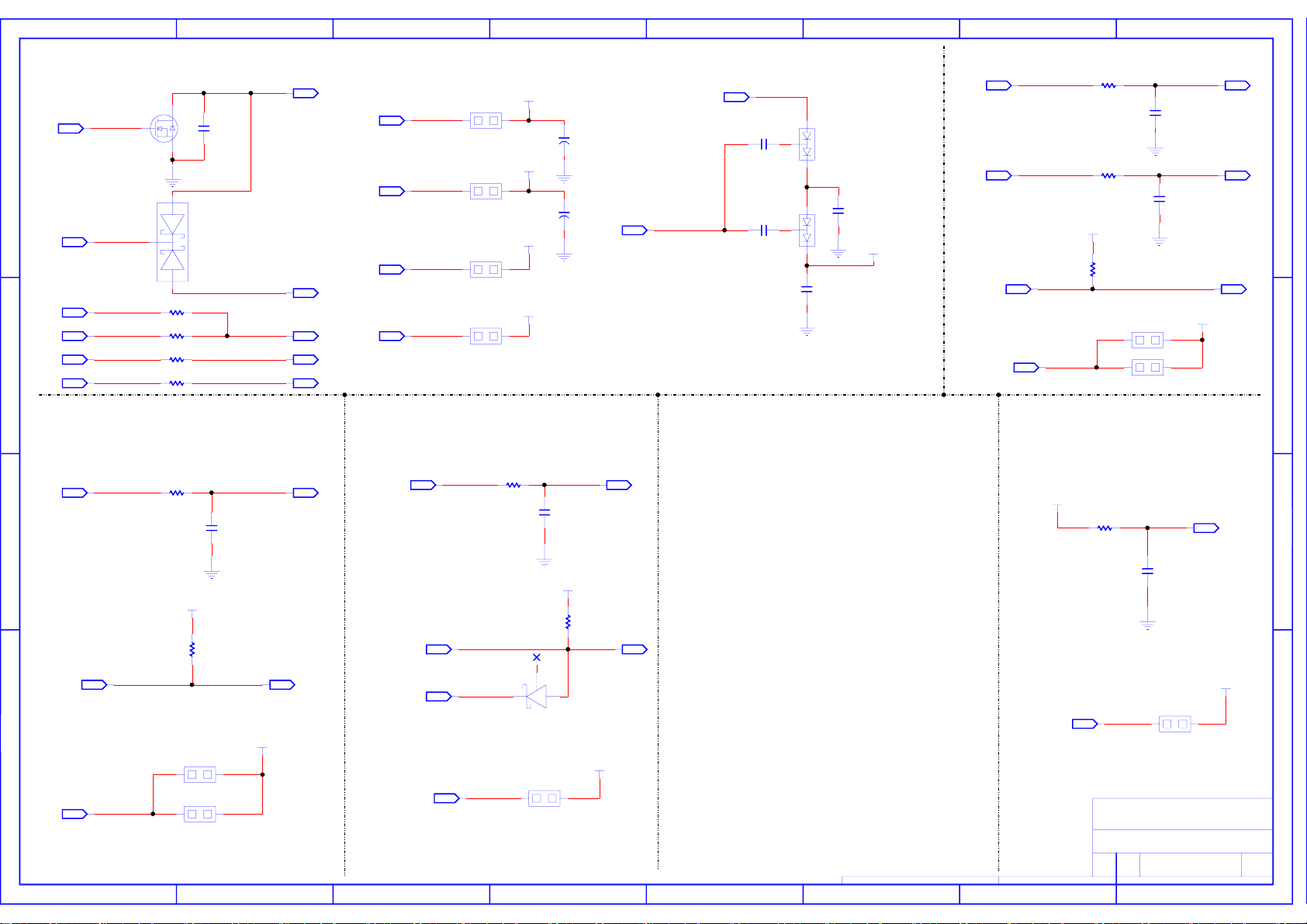

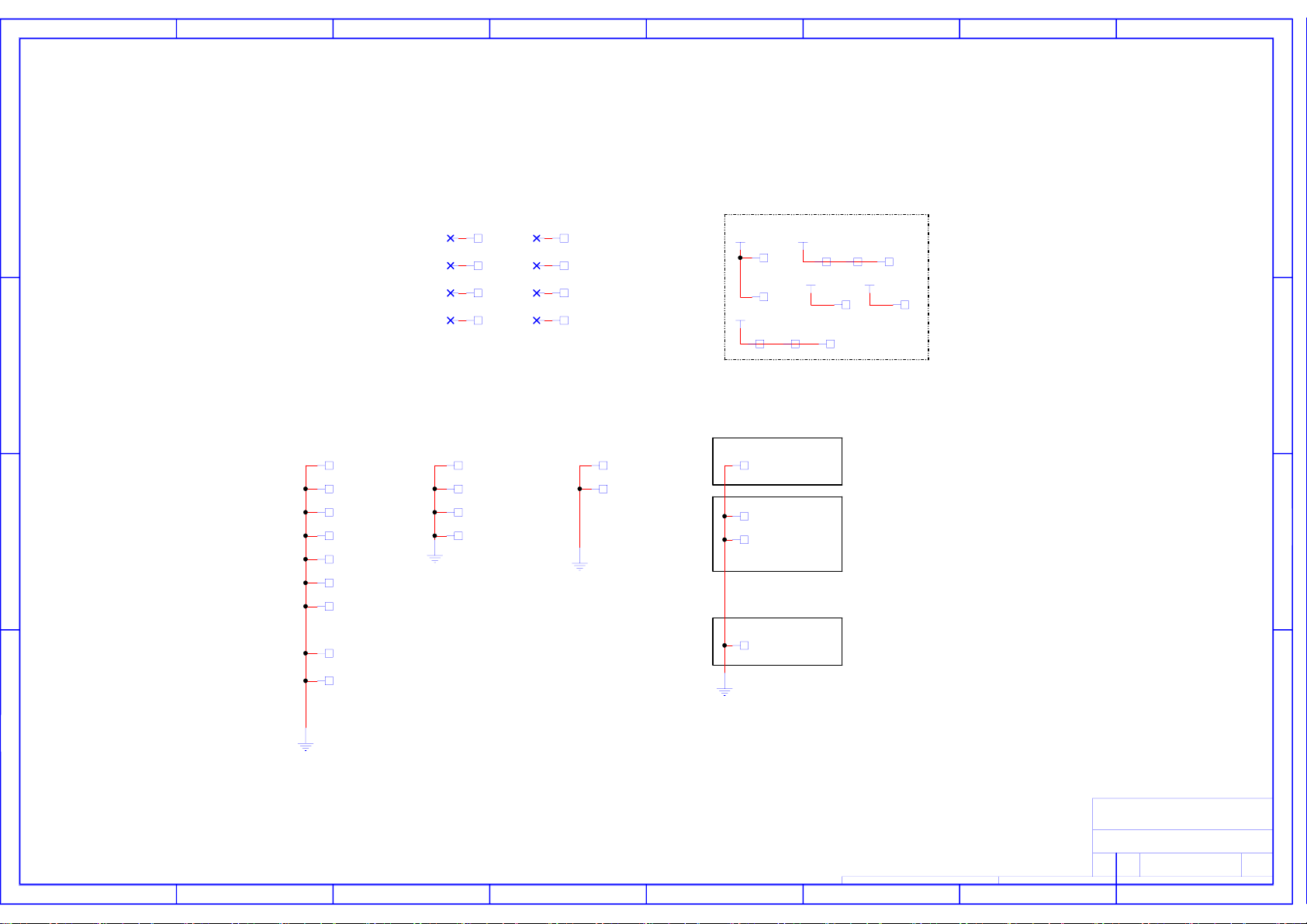

TABLE OF CONTENTS

4

3 2 1

D

PAGE

1. COVER PAGE

2. INDEX

3. BLOCK DIAGRAM

4. POWER MAP

5. POWER CHARGER

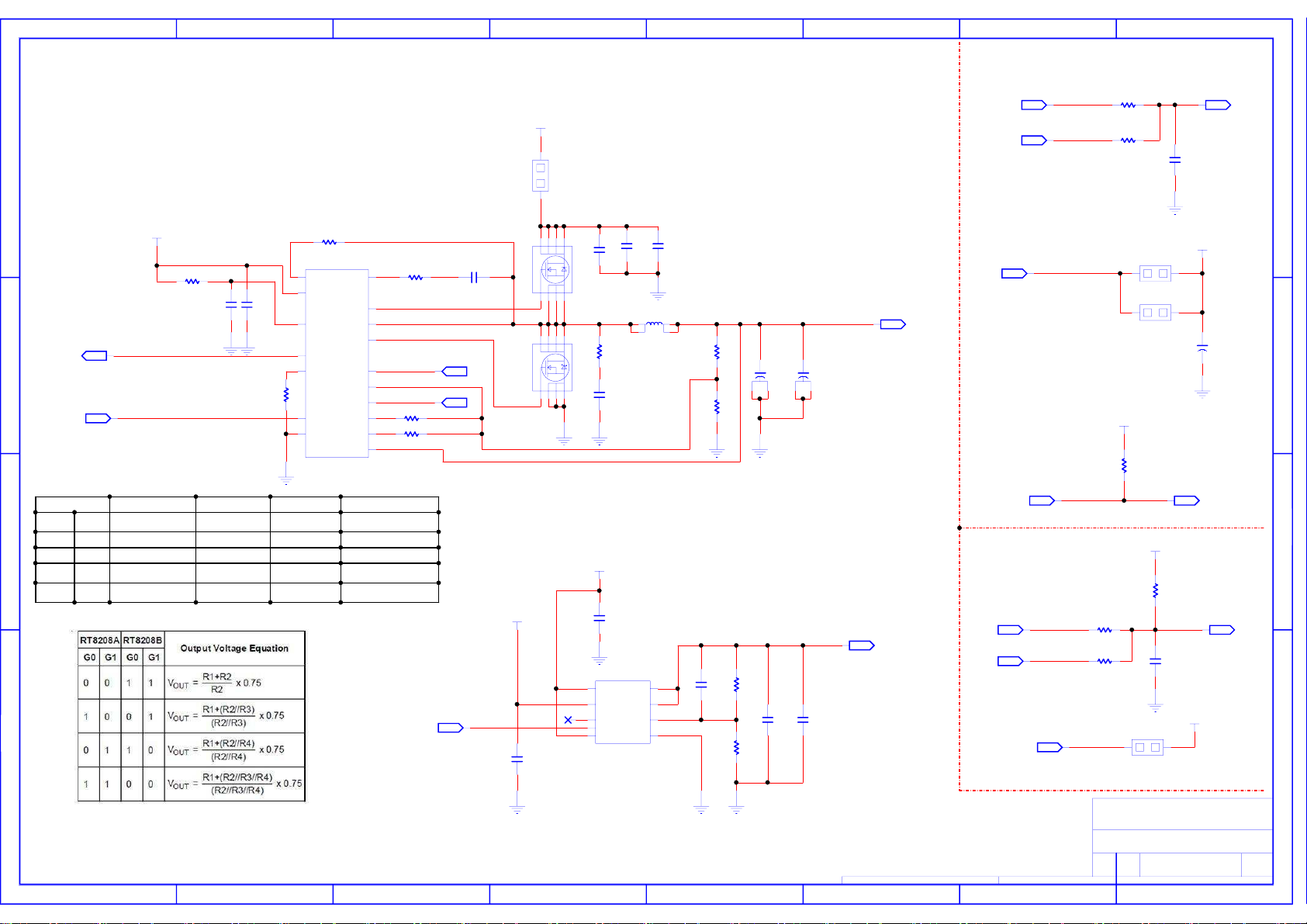

6. POWER +V3LA/+V3A/+5A

7. POWER +V1.5/+V0.75

8. POWER +V1.8S

9. POWER VCCIO

10. POWER VCCSA

11. POWER VCORE

12. POWER VGFX

13. POWER VCORE_DGPU

14. ENABLE PIN

15. LOAD SWITCH-1

16. LOAD SWITCH-2

17. PCB SCREW

B

18. HALL SENSOR

19. LED

20. K/B & TP/B CONN

21. EC

22. LAN

23. RJ45 & TRANSFORMER

24. AUDIO CODEC

PAGE

26. CARDREADER

27. MINI1 WLAN/DEBUG CARD

28. MINI2 3G/LTE

29. SATA HDD/ODD CONN

30. USB 2.0 CONN

31. USB 3.0 CONTROLLER(REMOVE)

32. USB 3.0 CONN W/ S&C

33. USB 3.0 CONN

34. LCM CONN

35. CRT CONN

36. HDMI CONN

37. HDMI CEC

38. DDR3 DIMM0

39. DDR3 DIMM1

40. FAN & THERMAL SENSOR

41. CPU 1

42. CPU 2

43. CPU 3 DRAM

44. CPU 4 POWER

45. CPU 5 POWER

46. CPU 6 GND

47. PCH 1

48. PCH 2

49. PCH 3

PAGE

51. PCH 5 USB

52. PCH 6 MISC

53. PCH 7 POWER

54. PCH 8 POWER

55. PCH 9 GND

56. VGA 1

57. VGA 2

58. VGA 3

59. VGA 4

60. VGA 5

61. VGA 6

62. VRAM 1

63. VRAM 2

64. VRAM 3

65. VRAM 4

66. USB BOARD

67. PICK BUTTON BOARD(4 PIN)

68. POWER BUTTON BOARD

69. EMI

70. PICK BUTTON BOARD(8 PIN)

D

CC

B

50. PCH 4 AXG25. SPEAKER/HP JACK/MIC JACK

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

SHEET

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

of

1

REV

X011310xxxxx-0-0

702

8 7

6 5

4

3 2 1

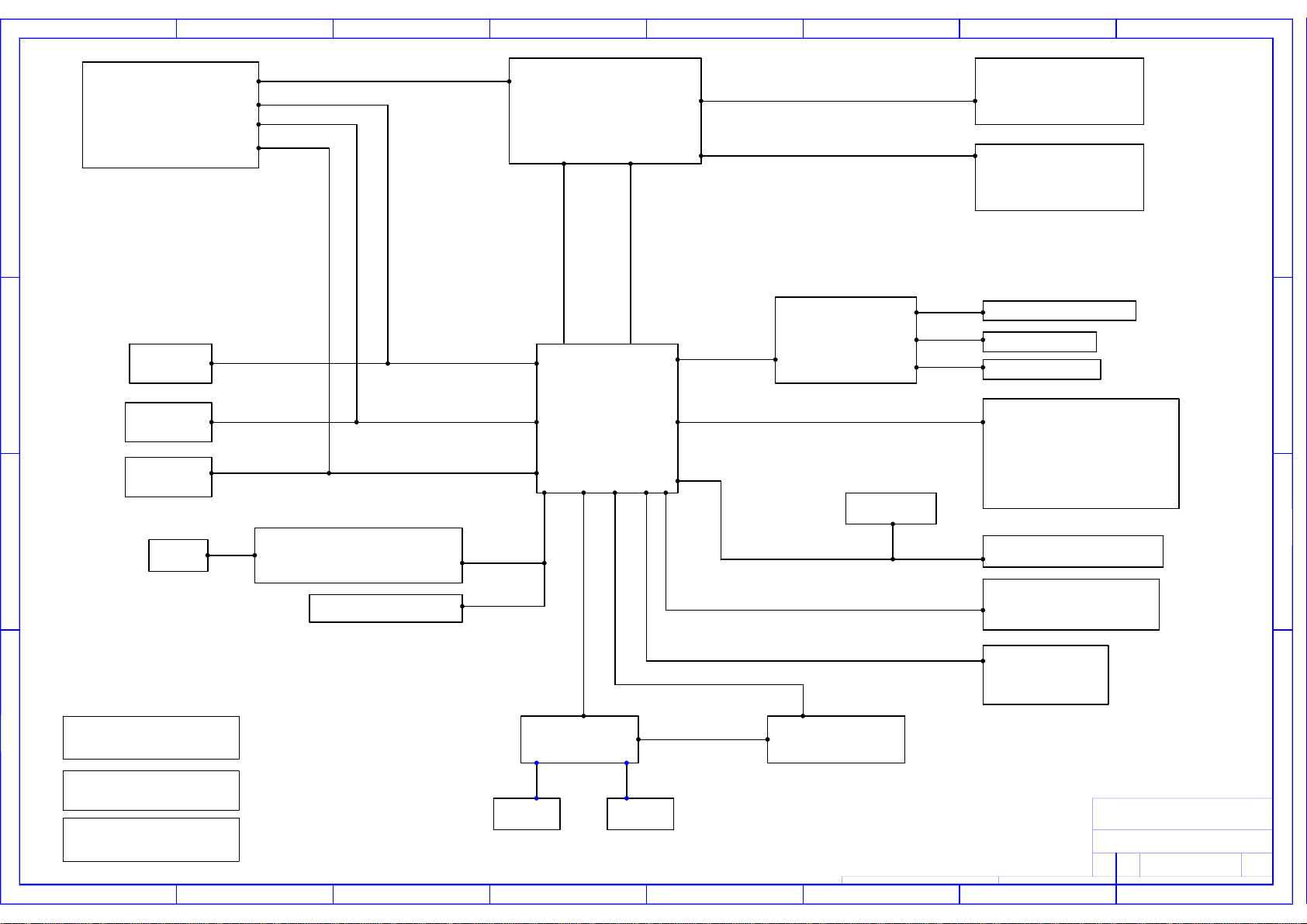

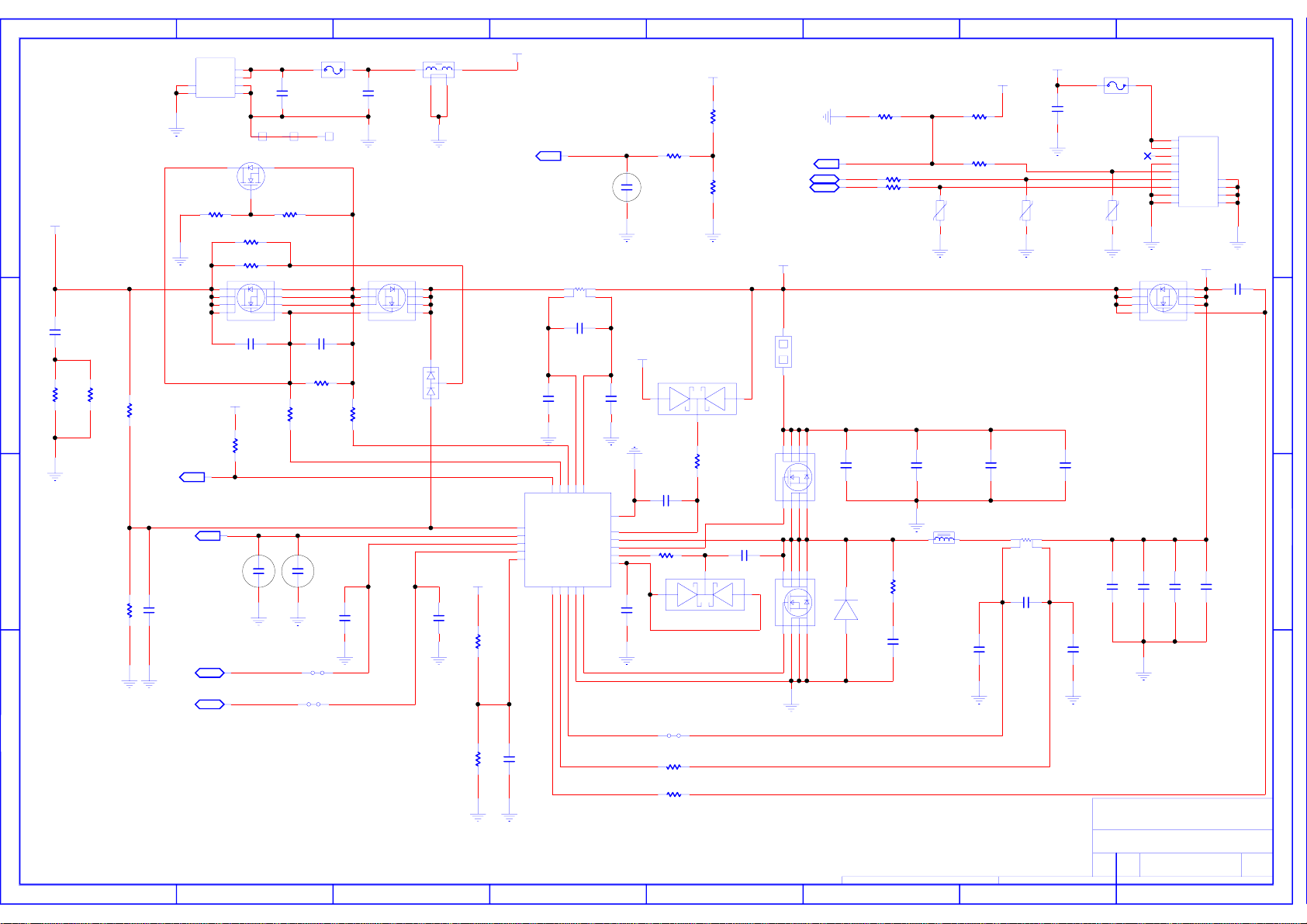

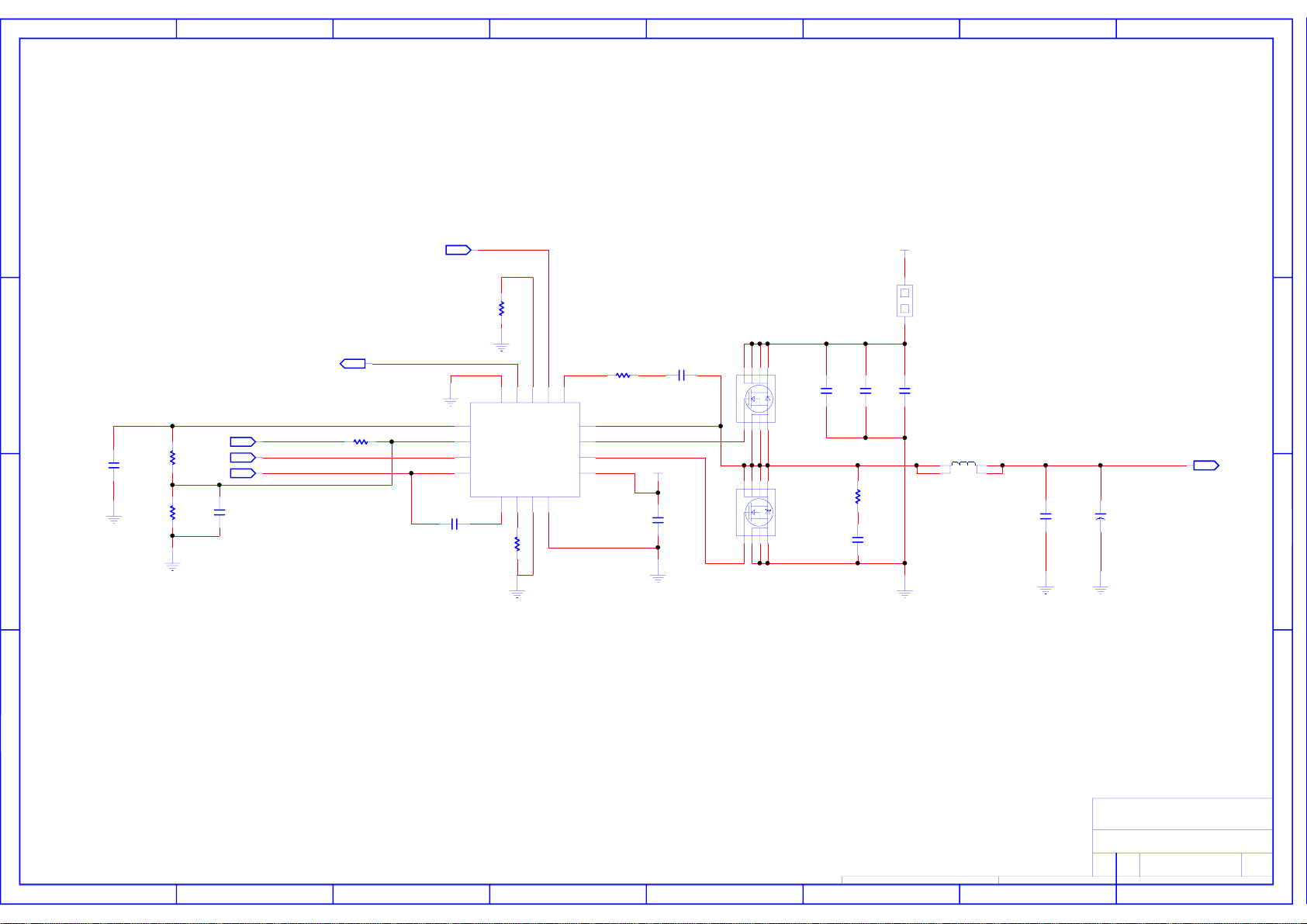

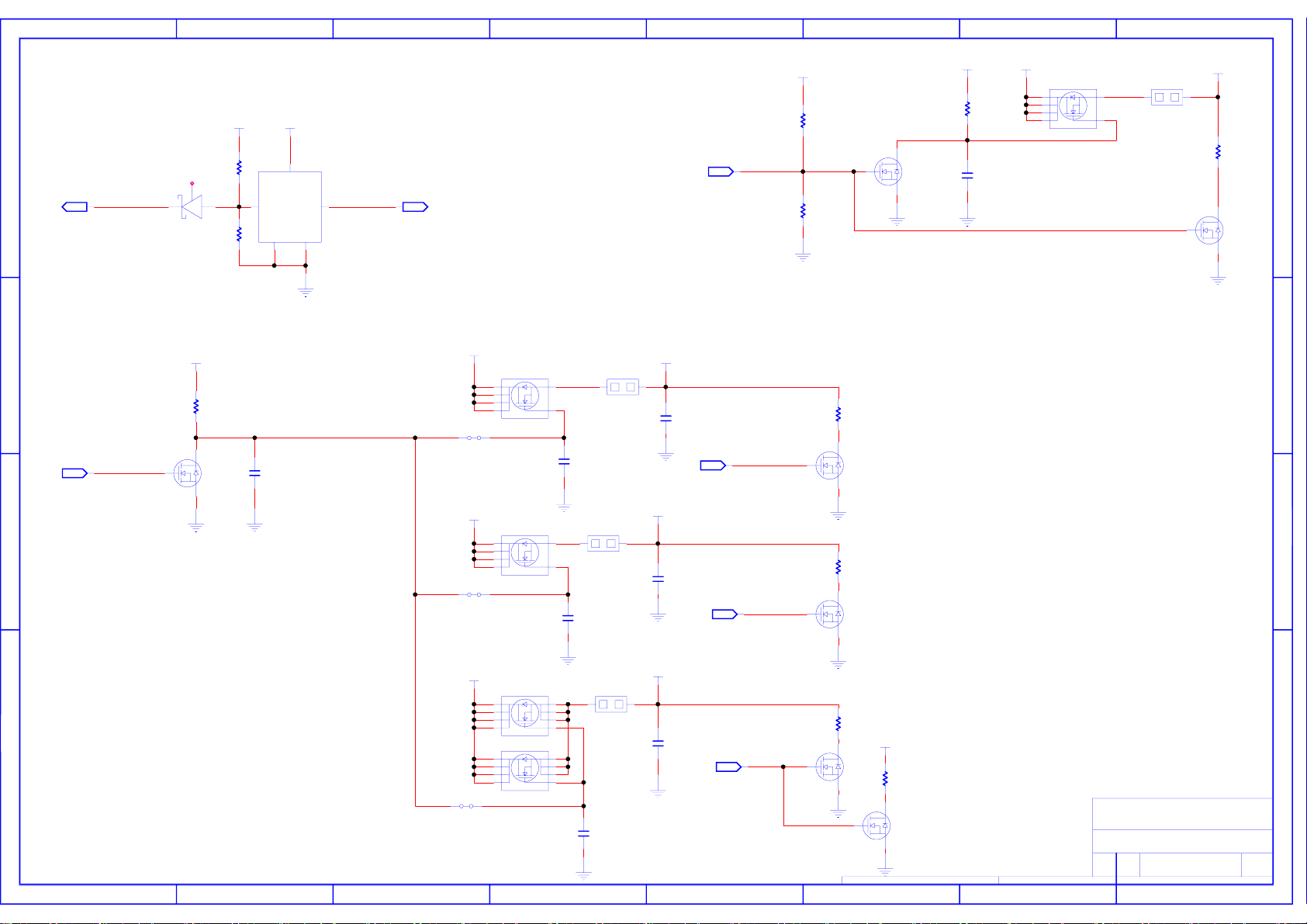

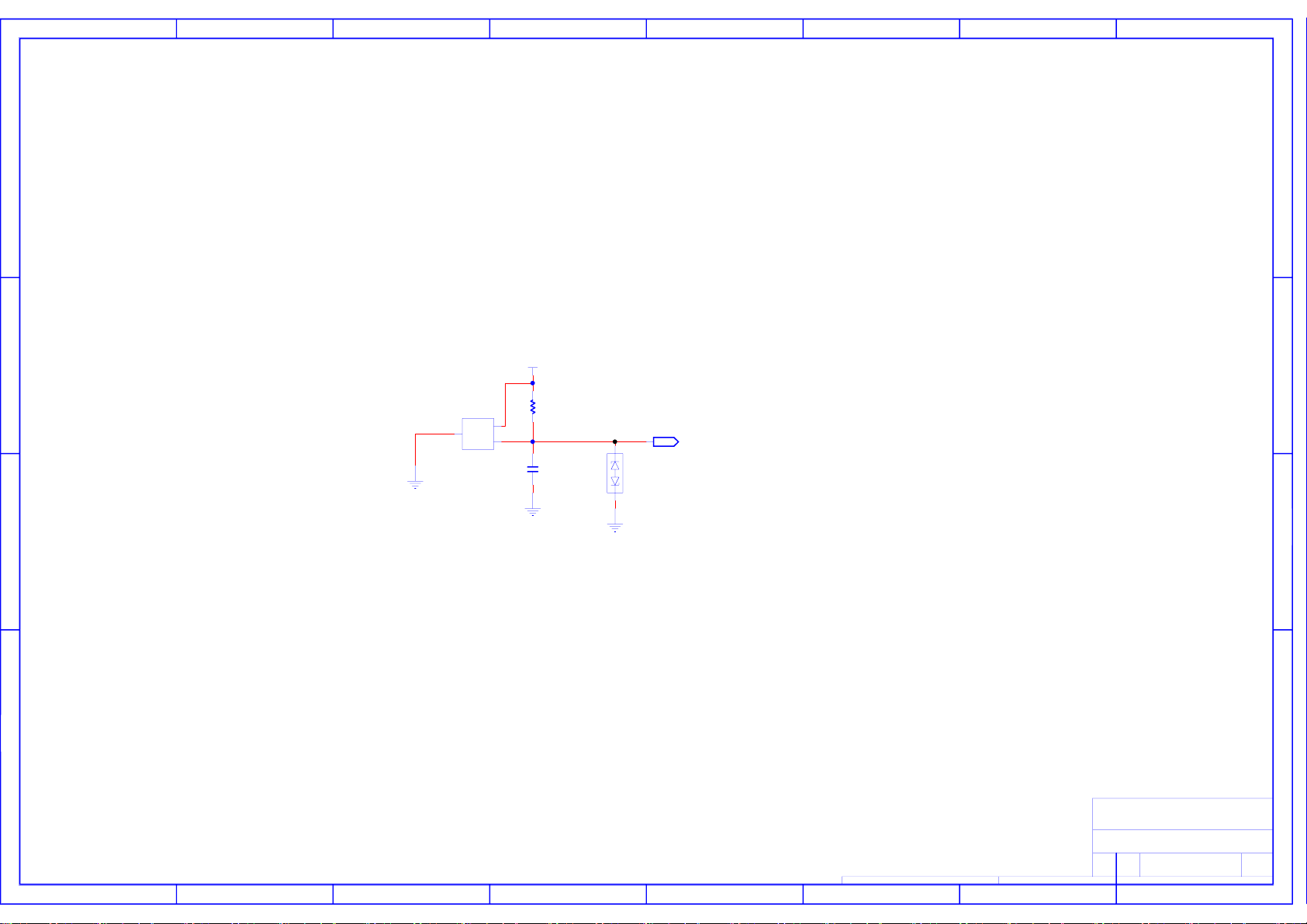

AMD

PEG

W/ POWER EXPRESS

THAMES LE \ THAMES XT \

SEYMOUR XTX

29X 29 MM

D

IVY BRIDGE \

SANDY BRIDGE

QC 45W

SOCKET-RPGA989

37.5 X 37.5 X 5 mm

FDI

DMI 2.0

DDR3 INTERFACE

DDR3 INTERFACE

DDR3@1.5/0.75V

(1333/1600 MHZ)

204-PIN SODIMM0

DDR3@1.5/0.75V

(1333/1600 MHZ)

204-PIN SODIMM1

D

INTERNAL MIC IN

AUDIO CODEC

EXT MIC IN

HEADPHONE

CC

HDMI

HDA

REA_ALC269Q_VB6

PCH

CRT

LCM

PANTHER POINT

USB2.0

25 X 25 X 2.3 mm

LVDS

SLEEP & CHARGE

USB_0: USB CONN

USB_2: USB CONN

USB_8: CARD READER

USB_9: MINICARD WLAN

USB_10:WEBCAM

B

RJ45

PCIE_1:LAN

PCIE

USB3.0

USB_1: USB3.0 CONN

B

ATHEROS_AR8161/8162

PCIE_2:WLAN

PCIE

USB2.0

SATA

SPI

USB_8:

SATA0:HDD

SATA2 ESATA

CARD READER

REA_RTS5129

SATA5: ODD

ENE-P2809A

THERMAL SENSOR

EC WINDBOND

NPCE885LA0DX

SPI

SPI FLASH 4MB

WINB_W25Q32BVSSIG

AA

BATTERY CHARGER &

DC/DC & IMVP 7

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

SHEET

of

703

1

REV

X011310xxxxx-0-0

LI-ION BATTERY

6-Cell

8

7 6

KEYBOARD

TOUCH PAD

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

8 7

6 5

4

3 2 1

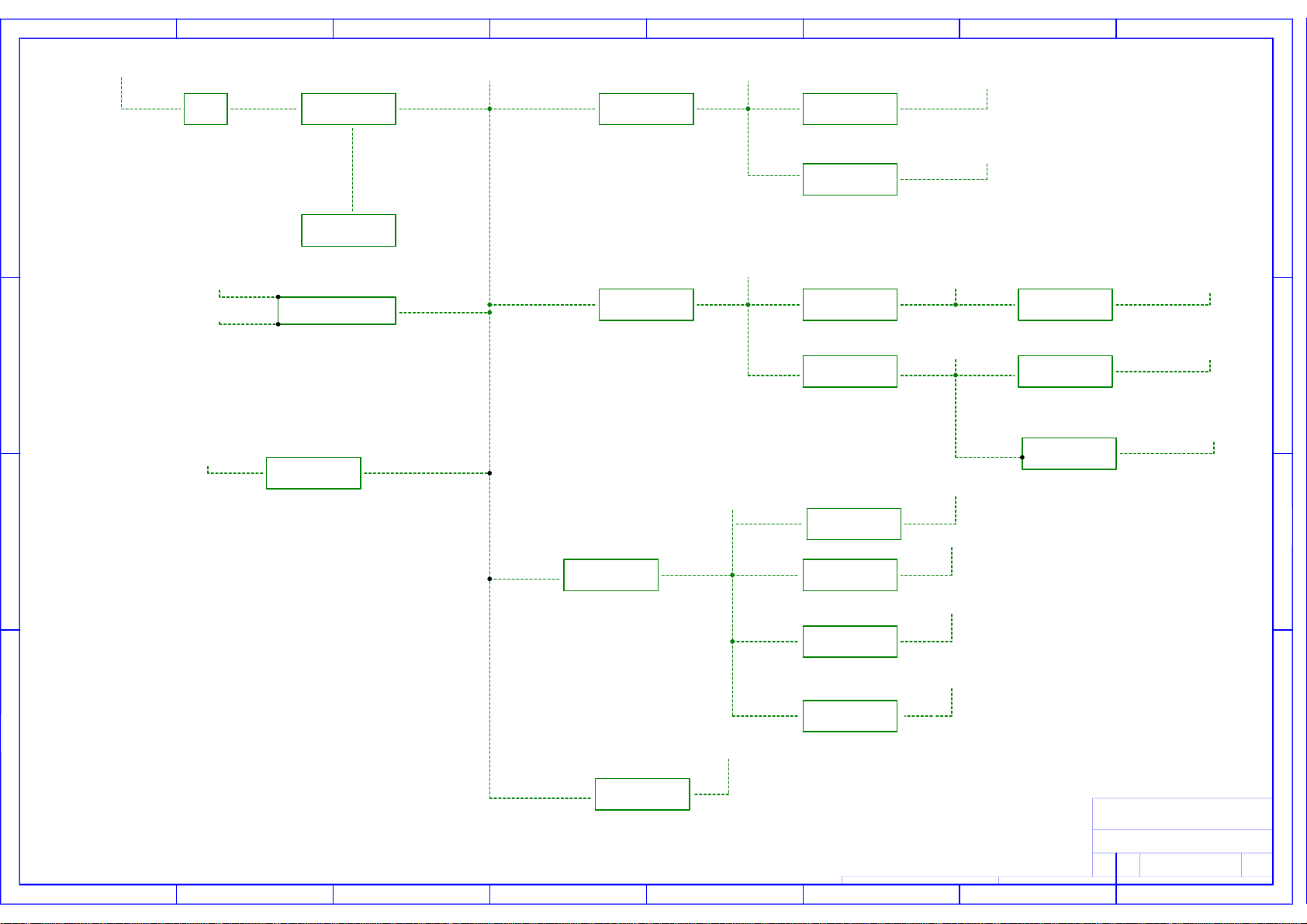

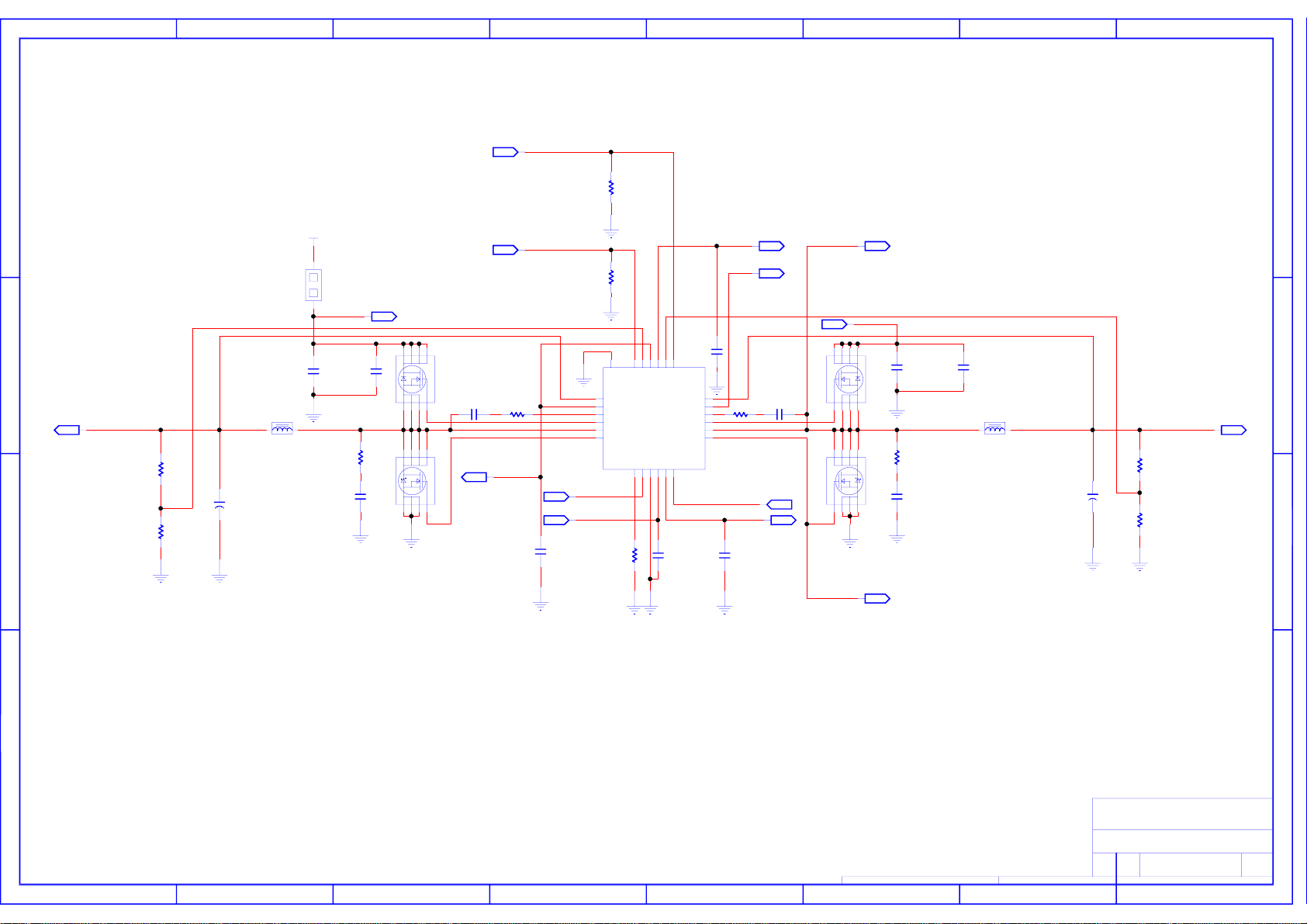

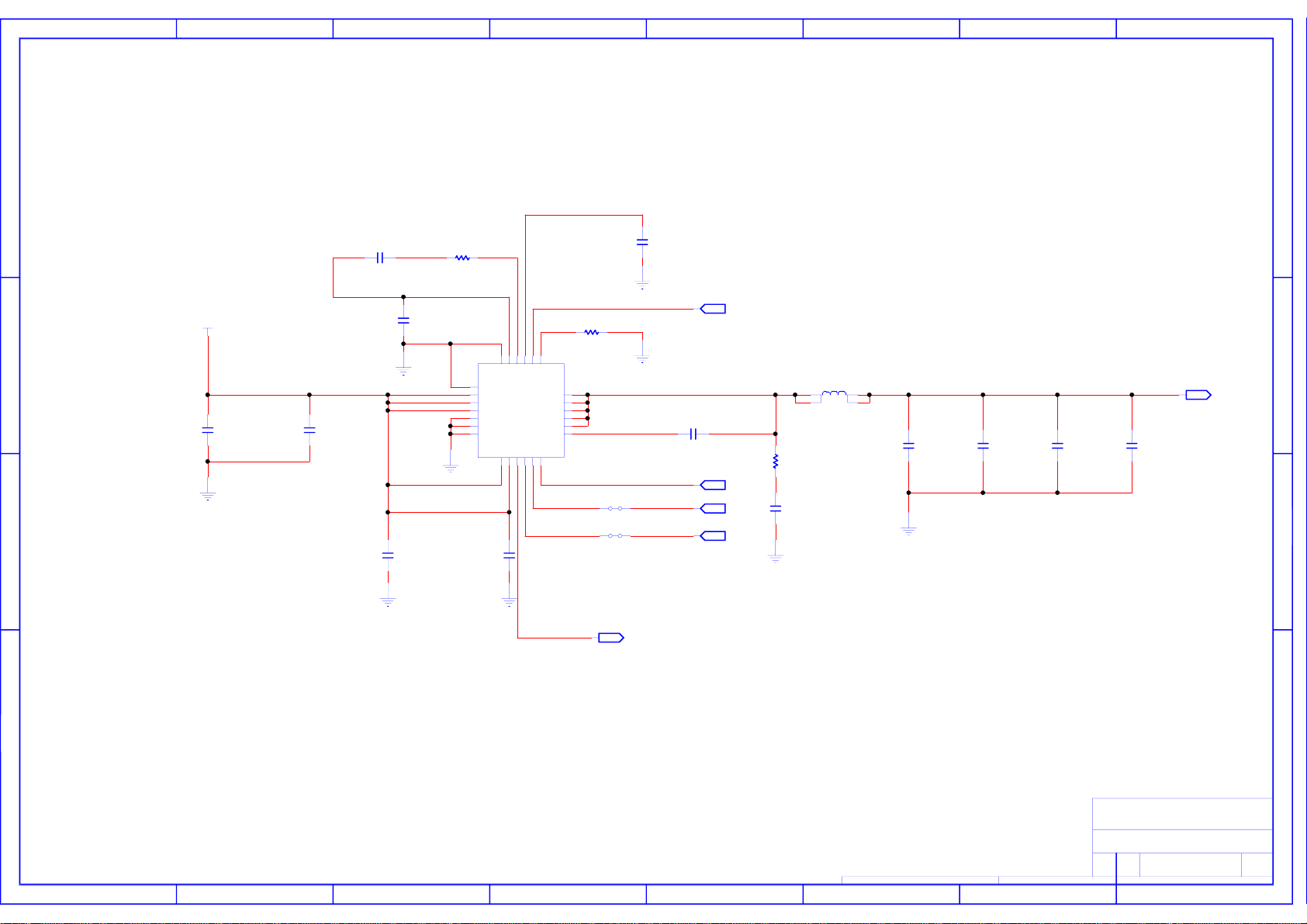

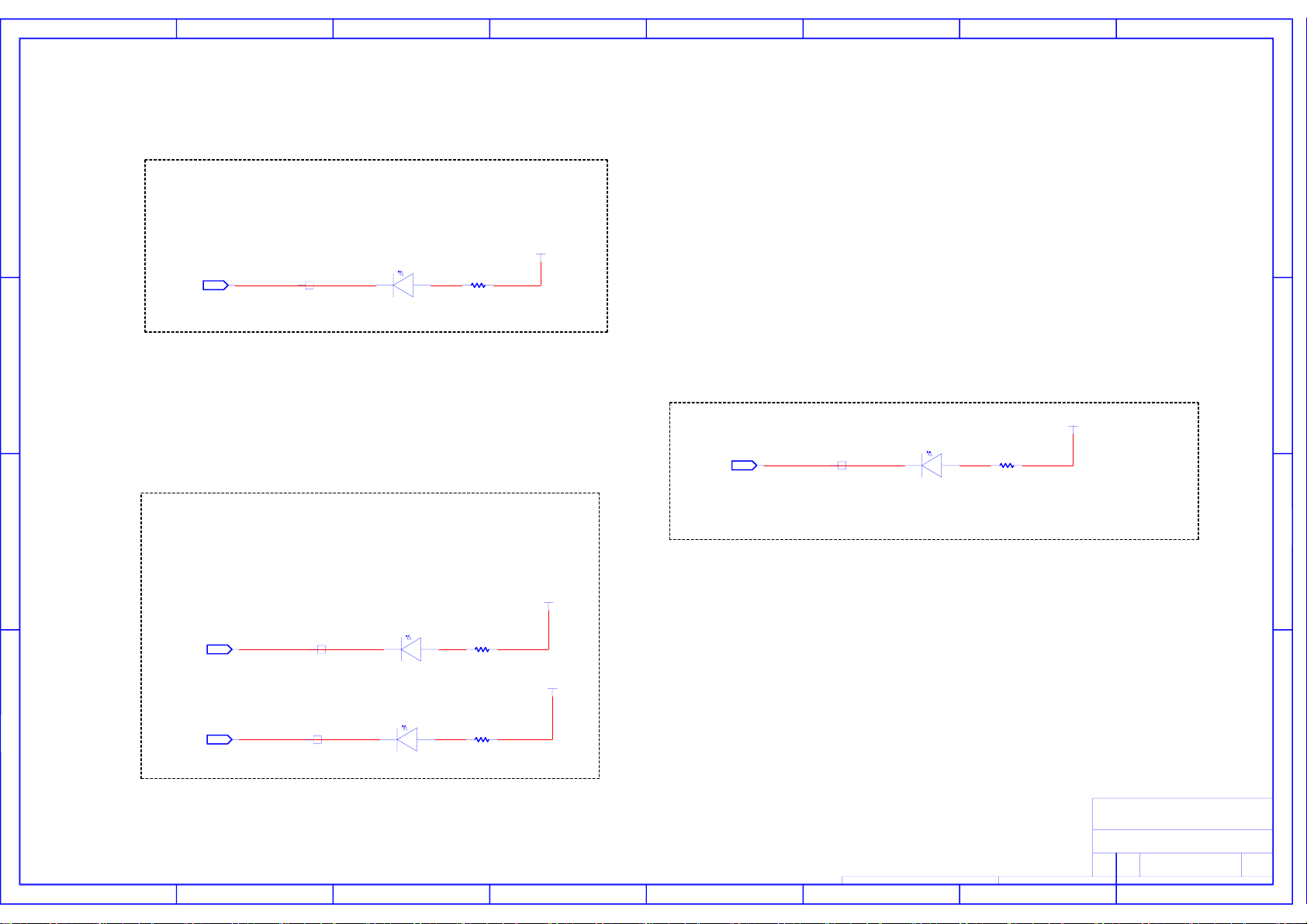

ADAPTOR

FUSE

65W-75W 8A 6036A0003401

90W 10A 6036A0002901

D

120W 12A 6036A0006001

BQ24725RGRR

CHARGER

EC_SMB2

CHG_EN

BATT_IN

ACPRES

+VBAT

TPS51123

POWER BUDGET 14.745 A

F 300K

OCP 10.52A R=140K

PEAK 9.23A AVG 1.809A

330UF_25MΩ // 49.1UF_6.648MΩ

BATTERY PACK

+V5A_+-5%

NMOS

POWER BUDGET 4.711A

PEAK2.592A

122.42UF_0.658MΩ

TSP51461

POWER BUDGET 6A

F 340K

OCP 6A

PEAK 6A AVG 1.262A

+V5S

INRUSH 0.55A

+V0.85S_+-0.5%

D

+V3LA_+-5%

+VCORE_+-0.5%

+VCORE_+-0.5%

TPS51650

POWER BUDGET 94A

F 280K

OCP 104.5A

PEAK 94A AVG 45.3A

1880UF_1.1MΩ // 2276UF_0.203MΩ

TPS51123

POWER BUDGET 12.186 A

F 375K

OCP 8.40A R=120K

PEAK 7.31A AVG1.7 A

3300UF_25MΩ //6.7UF_5.458MΩ

NMOS

POWER BUDGET 4.711A

PEAK2.592A

3.6UF_8.409MΩ PEAK2.592A

NMOS

POWER BUDGET 4.711A

PEAK2.592A

75.6UF_0.986MΩ

+V3A

INRUSH 0.984A

+V3S

INRUSH 1.06A

NMOS

POWER BUDGET 4.711A

5.9UF_9.497MΩ

RT8068

POWER BUDGET 4.711A

PEAK2.592A

56.12UF_1.505MΩ

+V3_LAN

INRUSH 0.464A

+V1.8S

INRUSH 0.6A

CC

+V3S_DGPU

VDD_CORE

TPS51728

POWER BUDGET 46A

F 340K

OCP 50A

B

PEAK 46A AVG 38.7A

560UF_25MΩ // 80UF_0.93MΩ

+V1.5_+-5%

TPS51216

+V0.75S

+V1.5S_DGPU

NMOS

POWER BUDGET 4.711A

PEAK2.592A

13UF_5.803MΩ

INRUSH 0.496A

B

CHANGING POINTS~~

TPS51211 IS NEW IC

+V1.8S IS NEW IC RT8068

VDD CORE IS NEW IC TPS51728

CHARGE IS NEW IC BQ24725

VCC CORE IS NEW IC TPS51650

VTT IS NEW IC TPS51219

V0.85 IS NEW IC TPS 51641

V3_V5 IS NEW IC TPS51123

POWER BUDGET ~~IC SPEC (MAX CURRENT )

PEAK CURRENT ~~RATIO OF INTERNAL PREDICTION

AVG CURRENT ~~TEST RESULT(MAX CURRENT)

INRUSH ~~L/S TURN NO

8

7 6

TPS51216

POWER BUDGET 33.033 A

F 340K

OCP 20.1A R=56.2K

PEAK 19.82A AVG8.802 A

330UF_15MΩ // 480UF_0.560MΩ

+V1.05_+-5%

TPS51219

POWER BUDGET 19.218 A

F 340K

OCP 13.2A R=115K

PEAK 11.53A AVG 6.704A

560UF_25MΩ // 359.9UF_0.213MΩ

5 4

NMOS

NMOS

NMOS

CHANGE by

+V1.5S

+V1.5_CPU

DATE

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

SHEET

21-OCT-2002XXX

23

of

1

REV

X011310xxxxx-0-0

704

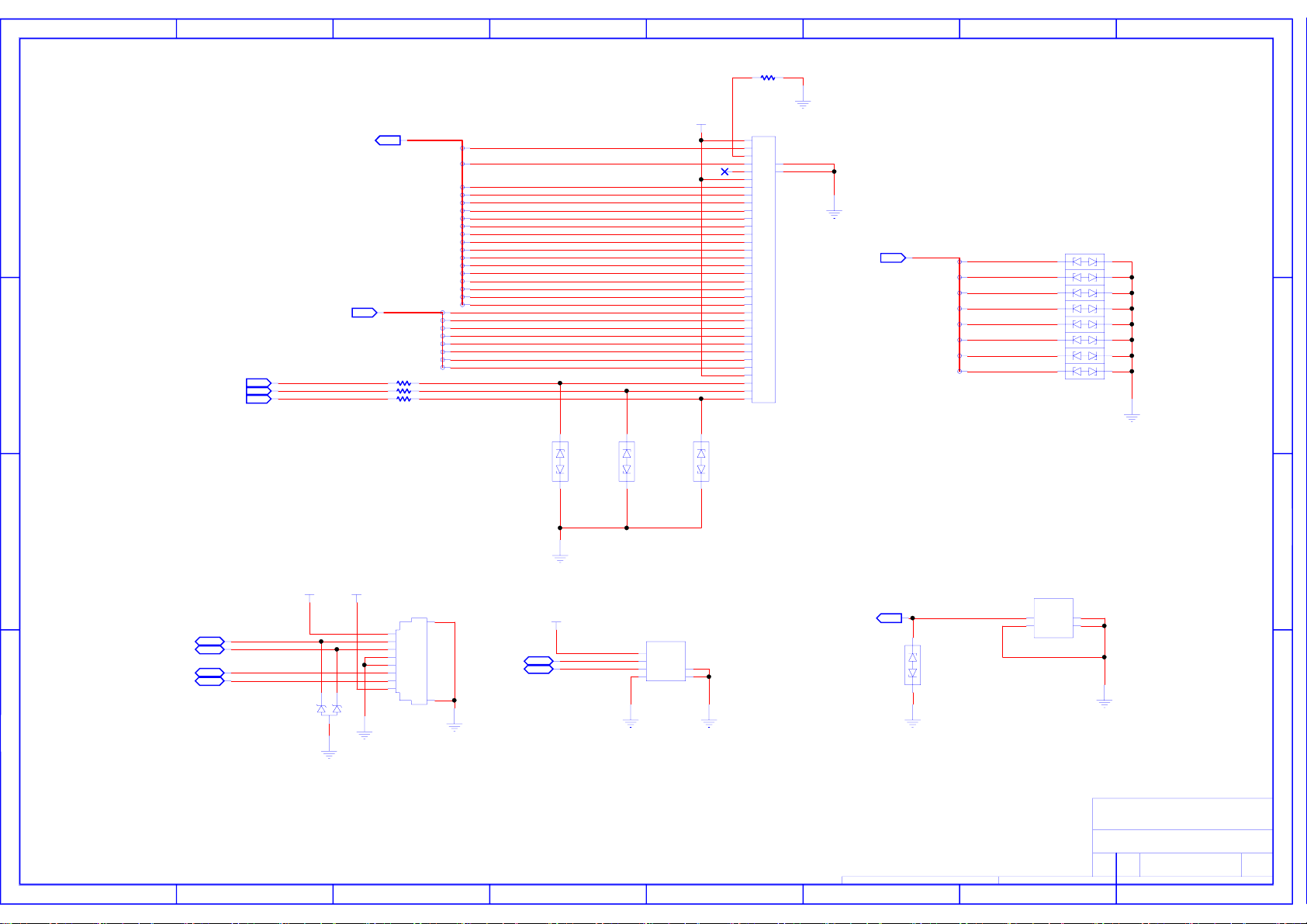

FUSE6000

65W-75W 8A(6036A0003401)

90W 10A(6036A0002901)

120W 12A(6036A0006001)

D

PVADPTR

C6014

2 1

CSC0805_DY

R6018

2 1

B

8 7

G1

G2

ACES_50315_0047N_002_4P

SSM3K7002FU_DY

1M_5%_2_DY

21

R6019

2 1

RSC_1206_DY

RSC_1206_DY

21E6

R6002

20.5K_1%_2

ACPRES

OUT

21E621E8

21

R6003

3.32K_1%_3

C6029

CSC0603_DY

2 1

21D221D3

37C356C8

21D221D337C656D8

8

CN6000

654

Q6002

3

R6021

Q6010

8

7

6

2200PF_50V_2

P3V3AL

HW_I_ADC

OUT

C6037

100PF_50V_2

NEAR EC

EC_SMB2_DATA

BI

EC_SMB2_CLK

BI

FUSE6000

TP30

C6031

21

1

2

3

4 5

21

1

1

2

2

3

3

4

TP60031TP60041TP6005

1

DS

G

1

21

2 1

3M_5%_2_DY

R6015

21

4.7K_5%_3

R6014

21

RSC_0603_DY

D

S

G

NMOS_4D3S

TPCA8065_H

C6030

21

LITTLEFUSE_R451012_12A_65V

C7601

1000PF_50V_2

2 1

TP30TP30

2

R6022

1

2

3

45

0.1UF_25V_3

R6006

21

21

R6013

10K_5%_3

2 1

RSC_0603_DY

21

R6004

4.3K_5%_2

C6036

NEAR IC

2 1

CSC0402_DY

R6016

SHORT_0402

R6017

21

100PF_50V_2

C6035

2 1

21

21

SHORT_0402

7 6

10PF_50V_2

2 1

S

G

TPCA8065_H

R6005

4.3K_5%_2

6 5

L7600

NFE31PT222Z1E9L

21

C7602

NMOS_4D3S

Q6011

4

3

8

D

7

6

3

D6002

DIODES_BAV99

2 1

TI_BQ24725ARGRR_QFN_20P

P3V3AL

C6034

CSC0402_DY

21

2 1

R6007

110K_5%_2

21

R6008

91K_5%_2

PVADPTR

21E621E8

C6021

0.1UF_25V_3

U6000

6

ACDET

7

IOUT

8

SDA

9

SCL

10

ILIM

C6032

0.1UF_16V_2

2 1

RSC_0603_DY

2 1

R6802

33K_5%_2_DY

RSC_0603_DY

HW_V_ADC

OUT

0.1UF_16V_2_DY

0.01_1%_6

R6000

C6020

C6800

NEAR EC

21

43

21

0.1UF_16V_2

PVADPTR

D6000

C6022

3

ACP

CMSRC

GND

SRP

13

2

ACN

PHASE

LODRV

15

14

1UF_10V_2

HIDRV

BTST

REGN

C6028

TML

VCC

2 1

0.1UF_25V_3

21

20

19

18

17

16

2 1

C6026

1UF_25V_3

R6020

4.7_5%_3

D6001

BAT54C_30V_0.2A

R6011

SHORT_0402

R6010

2 1

0_5%_2

R6009

2 1

514

ACOK

ACDRV

BATDRV

SRN

12

11

4.3K_5%_2

5 4

R6800

21

R6801

C

BAT54C_30V_0.2A

3

21

R6012

21

21

21

21

4

PVBAT

21

21

EC_SMB1_DATA

21D2

21D3

21

A2A1

10_5%_5

VRCHARGER_HG

VRCHARGER_PH

C6027

3

0.047UF_16V_2

C

A2A1

VRCHARGER_LG

21E621E8

BATT_IN

21D221D3

EC_SMB1_CLK

PVBAT

12

2 1

AON7410

NMOS_4D3S

G

21

AON7410

NMOS_4D3S

21

G

OUT

BI

BI

PAD6000

POWERPAD_2_0610

678

Q6000

D

S

3

214 5

678

Q6001

D

D6700

S

3

214 5

3 2 1

P3V3AL

R6054

21

1M_5%_2

33_5%_2

R6050

21

21

33_5%_2

R6051

D6701

EZJZ0V500AA_DY

C6001

470PF_50V_2 4.7UF_25V_5 4.7UF_25V_5

2 1

2 1

ETQP3W4R7WFN

21

R7600

RSC_0603_DY

2 1

C7600

SBR3U40P1_DY

CSC0402_DY

2 1

21

C6002

L6000

R6053

21

220K_1%_2

1K_5%_2

R6052

21

D6702

EZJZ0V500AA_DY

C6003

2 1

21

C6024

2 1

0.1UF_25V_3

0.02_1%_6

0.1UF_16V_2

21

EZJZ0V500AA_DY

R6001

21

43

C6023

21

PVPACK

2 1

C6050

1000PF_50V_2

D6703

C6004

CSC0805_DY

2 1

C6025

2 1

0.1UF_25V_3

FUSE6050

LITTLEFUSE_R451015_15A_65V

21

C6010

2 1

INVENTEC

TITLE

CODE

SIZE

CHANGE by

DATE

21-OCT-2002XXX

23

A3

21

CN6050

1

BATT+

2

BATT+

3

ID

4

B-I

5

TS

6

SMD

7

SMC

8

GND

9

GND

SYN_200045GR009G18TZR_9P

PVPACK

Q6012

8

D

7

6

TPCA8065_H

C6011

2 1

4.7UF_25V_5

MODEL,PROJECT,FUNCTION

Block Diagram

CS

SHEET

NMOS_4D3S

C6012

2 1

4.7UF_25V_5

DOC.NUMBER

1

S

2

3

45

G

C6013

4.7UF_25V_5

of

1

G

G

G

G

0.1UF_25V_3

2 1

CSC0805_DY

705

G1

G2

G3

G4

C6033

REV

X011310xxxxx-0-0

D

21

CC

B

AA

8 7

6 5

4

3 2 1

IN

IN

R6114

2.2_5%_3

21

VRP3V3A_LDO

14C7

14C7

C6121

1UF_6.3V_2

EN_5V

EN_3V

21

VRP3V3A_HG

VRP3V3A_PH

VRP3V3A_LG

2 1

R6160

2 1

140K_1%_2

R6110

2 1

120K_1%_2

25

TML

TRIP2

7 24

VO2 VO1

8

VREG3

9 22

VBST2

10 21

DRVH2

LL2

DRVL2

R6113

U6100

EN0

13

2 1

11 20

12 19

SKIP_3V_5V

IN

VRP5V0A_VIN

IN

RSC_0402_DY

5

VFB2

SKIPSEL

14

3

4

TONSEL

VREF

GND

VIN

16

15618

2 1

1

2

VFB1

TRIP1

VREG5

ENC

17

C6122

2VREF

5V_PG

C6123

0.22UF_6.3V_2

2 1

23

PGOOD

DRVH1

TI_TPS51123RGER_QFN_24P

VBST1

DRVL1

R6155

2.2_5%_3

VRP5V0A_HG

VRP5V0A_PH

LL1

VRP5V0A_LG

EN_3V_5V

VRP5V0A_LDO

C6120

1UF_25V_3

10UF_6.3V_3

2 1

21

OUT

OUT

C6155

IN

OUT

6C614C8

21

0.1UF_16V_2

VRP5V0A_PH

IN

678

AON7410

NMOS_4D3S

G

3

678

AON7702A

G

3

VRP5V0A_LG

214 5

214 5

OUT

VBATP

Q6150

D

S

Q6151

D

S

14D6

OUT

6D3

C6160

4.7UF_25V_5

2 1

R7615

RSC_0603_DY

2 1

C7615

CSC0402_DY

2 1

6B3 14D5

C6161

4.7UF_25V_5

2 1

L6150

ETQP3W3R3WFN

D

CC

21

+

C6150

150UF_6.3V

2 1

R6150

15.4K_1%_2

2 1

R6151

10K_1%_2

2 1

VRP5V0A

VO=(( R6150/R6151)+1)*2

OUT

14D6

14C8

14D4

B

14D7

D

PVBAT

14C7

PAD6110

12

POWERPAD_2_0610

VBATP

2 1

4.7UF_25V_5

2 1

21

R7610

RSC_0603_DY

C7610

CSC0402_DY

C6111

C6110

4.7UF_25V_5

OUT

VRP3V3A

R6100

6.8K_1%_2

2 1

R6101

10K_1%_2

2 1

+

2 1

14D6

B

ETQP3W3R3WFN

C6100

150UF_6.3V

L6100

VOUT=((R6100/R6101)+1)*2

6C3 14C8

OUT

678

Q6100

D

2 1

Q6101

14C6

2 1

14C8

2 1

S

D

S

214 5

214 5

NMOS_4D3S

AON7410

G

3

C6115

0.1UF_16V_2

678

OUT

AON7702A

G

3

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

706

8 7

6 5

4

3 2 1

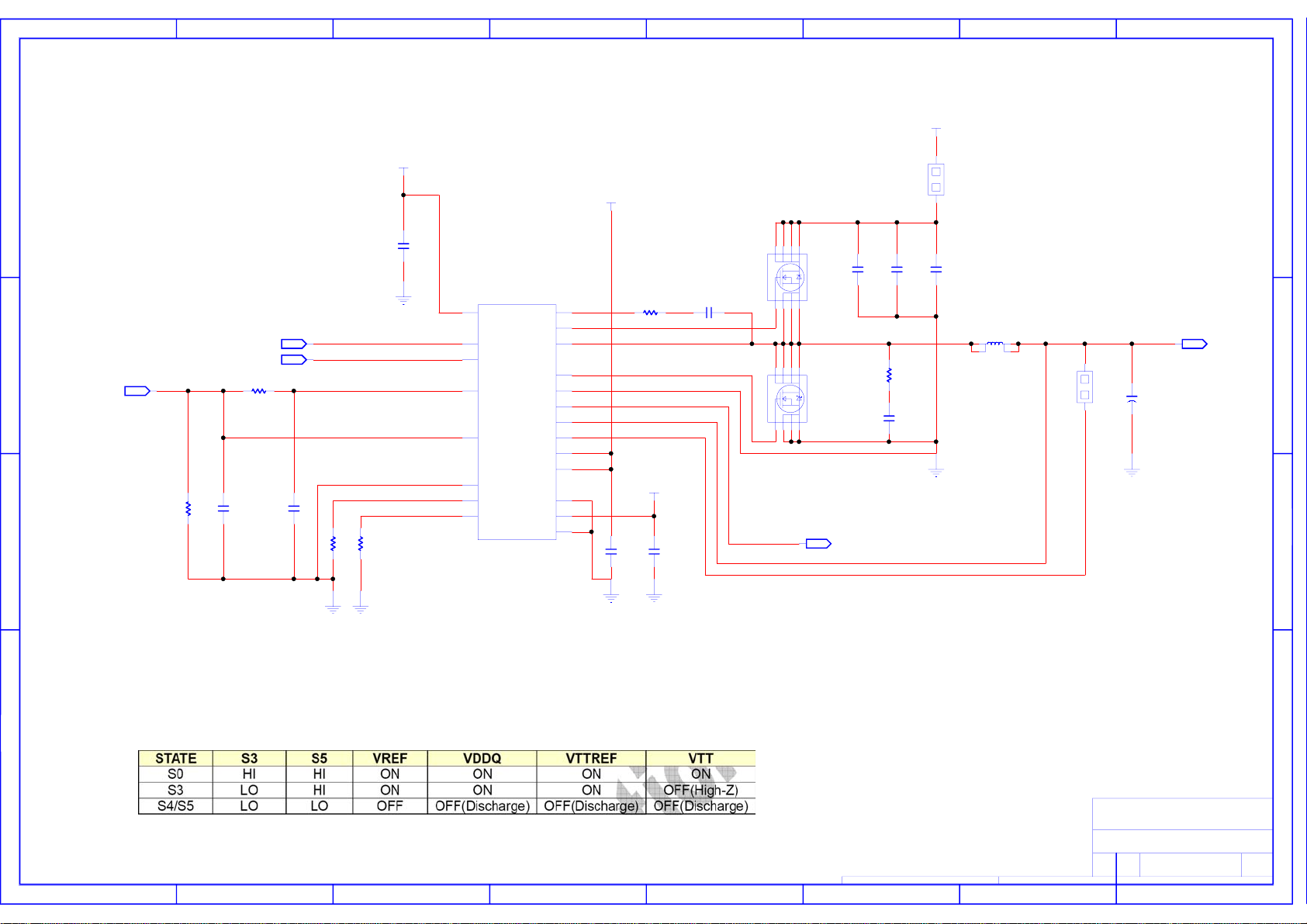

PVBAT

P5V0A

D

P0V75S

21

1 2

PAD6210

D

POWERPAD_2_0610

678

C6216

2 1

2.2UF_6.3V_3

U6200

IN

DDR3L_SEL

R6200

14D1

14D1

EN_0V75

IN

EN_1V5

IN

21

17

S3

16

S5

6

VREF

10.2K_1%_2

8

REFIN

7

21

C6217

R6201

2 1

B

54.9K_1%_2

C6218

2 1

0.01UF_50V_2

0.1UF_16V_2

21

R6203

R6202

2 1

100K_5%_2

75K_1%_2

GND

19

MODE

18

TRIP

TI_TPS51216RUKR_QFN_20P

DRVH

DRVL

PGND

PGOOD

VDDQSNS

VLDOIN

VTTSNS

VTTGND

VTTREF

1512

VBSTV5IN

VRP1V5_HG

14

VRP1V5_PH

13

SW

VRP1V5_LG

11

10

20

9

2

3

VTT

1

4

5

21

TML

C6220

2 1

R6215

2.2_5%_3

P0V75M_VREF

C6221

2 1

10UF_6.3V_3

21

0.22UF_6.3V_2

C6215

0.1UF_16V_2

21

FDMC8884

FDMS0310AS

NMOS_4D3S

G

G

1V5_PG

3

678

3

Q6200

D

C6212

C6211

C6210

S S

2 1

4.7UF_25V_5

2 1

2 1

4.7UF_25V_5

4.7UF_25V_5

214 5

L6200

21

21

Q6201

D

R7620

PCMC104T_1R0MN

RSC_0603_DY

14C2

C7620

CSC0402_DY

2 1

214 5

OUT

43

21

1 2

PAD6220

VRP1V5

OUT

14C2

CC

+

C6200

2 1

POWERPAD1X1M

560UF_2.5V

B

VOUT=REFIN=1.8*(R6201/(R6200+R6201))

MODE=100KOHM:TRACKING DISCHARGE

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

707

8 7

6 5

4

3 2 1

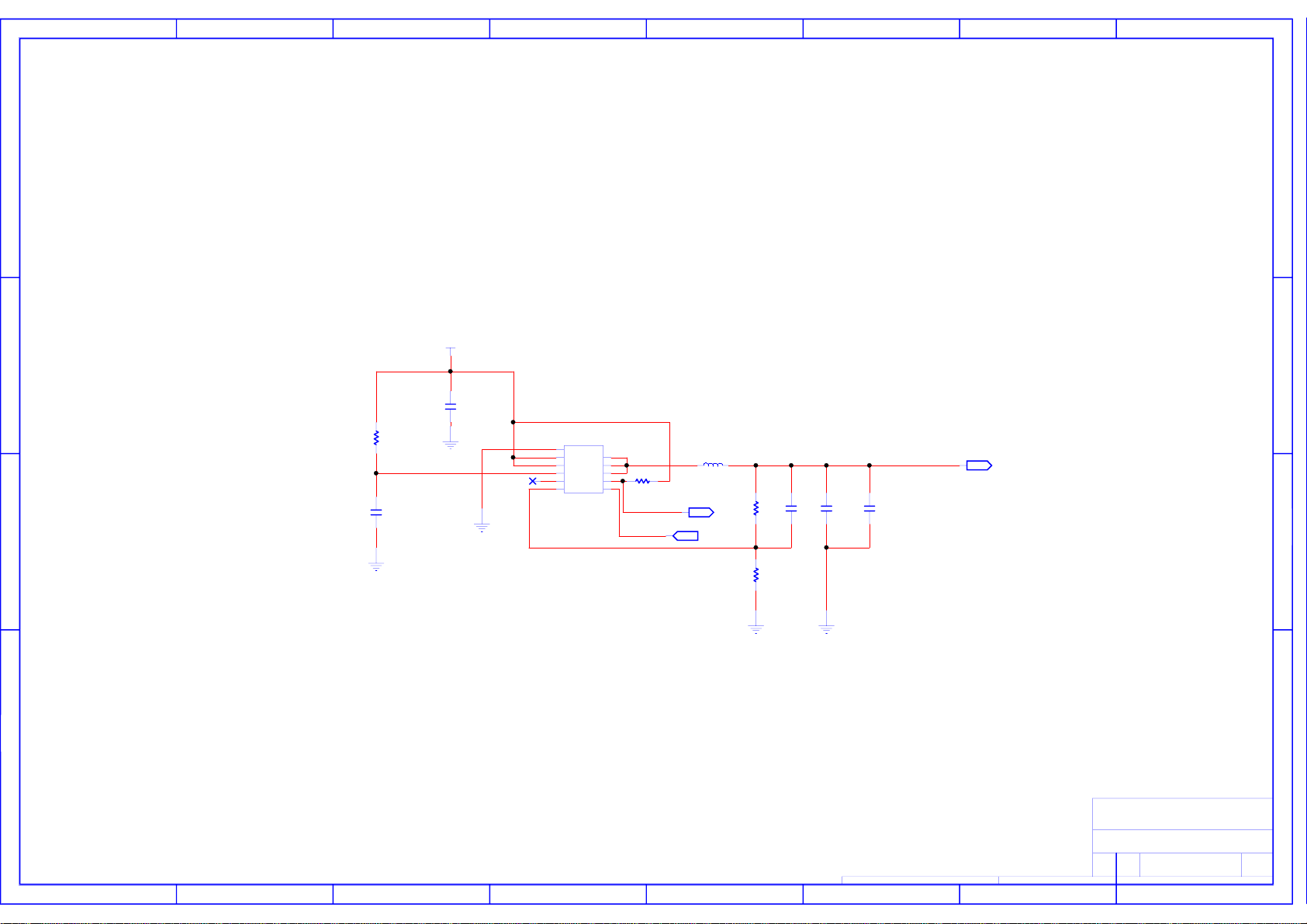

D

D

P3V3S

CC

C6971

2 1

R6970

10_5%_2

2 1

RICHTEK_RT8068AZQW_WDFN_10P

C6972

1UF_10V_2

10UF_6.3V_3

B

2 1

U6970

11

TML

10 1

LX

PVIN

9

LX

PVIN

8

LX

SVIN

7

PGOOD

NC

6 5

EN

FB

2

3

4

100K_5%_2

R6971

1V8S_PG

EN_1V8

21

PAN_ELL5PR2R2N

IN

OUT

L6970

14B1

21

C6970

R6973

C6974

2 1

2 1

20.5K_1%_2

CSC0402_DY

C6975

2 1

2 1

10UF_6.3V_3

VRP1V8S

10UF_6.3V_3

OUT

14A2

B

R6972

10K_1%_2

2 1

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

708

8 7

6 5

4

3 2 1

D

14B7

EN_VCCP

IN

PVBAT

D

21

1 2

R6303

2 1

100K_5%_2

OUT

R6307

0_5%_2_DY

VCCP_PG

21

1

2

3

4

TI_TPS51219RTER_QFN_16P

C6319

2 1

0.01UF_50V_2

U6300

VREF

REFIN

GSNS

VSNS

21

P5V0A

C6316

C6315

0.1UF_16V_2

2 1

2.2UF_6.3V_3

21

R6315

14

PGOOD

TRIP

13

EN

MODE

GND

PGND

2.2_5%_3

BST

SW

DH

DL

V5

VRP1VO_VCCP_PH

12

VRP1VO_VCCP_HG

11

VRP1V0_VCCP_LG

10

9

7

17

16815

PWPD

COMP

6

5

21

R6302

678

FDMC8884

Q6300

D

NMOS_4D3S

C6310

G

S S

3

214 5

678

FDMS0310AS

Q6301

D

G

3

214 5

2 1

4.7UF_25V_5

C7630

14A814B6

2 1

IN

IN

IN

0.01UF_50V_2

VCCIO_SEL

VSS_SENSE_VCCIO

VCC_SENSE_VCCIO

46B4

44A3

R6306

C6318

2 1

2.2UF_6.3V_3

B

44A3

10K_1%_2

2 1

C6320

R6308

2 1

11.3K_1%_2

52.3K_1%_2

PAD6310

POWERPAD_2_0610

CC

C6312

C6311

21

R7630

2 1

2 1

2 1

4.7UF_25V_5

4.7UF_25V_5

L6300

21

21

43

43

CYN_PCMB063T_R68MS_4P

RSC_0603_DY

C6300

C6301

2 1

22UF_6.3V_5

VRP1V05S

+

2 1

560UF_2.5V

OUT

14A8

B

CSC0402_DY

VOUT=1.05V@REFIN=3.3V; VOUT=1.0V@REFIN=GND

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

709

8 7

6 5

4

3 2 1

D

C6522

0.01UF_50V_2

2 1

VCCSA_SENSE

EN_SA

VCCSA_VID0

21

VCCSA_VID1

21

C6515

0.1UF_16V_2

45A2

IN

L6500

21

21

43

21

14B5

IN

45A2

IN

45A2

IN

CYN_PCMB063T_R33MS_4P

R7650

RSC_0603_DY

2 1

C7650

CSC0402_DY

2 1

43

C6500

22UF_6.3V_5

2 1

C6501

22UF_6.3V_5 22UF_6.3V_5_DY

2 1

C6502

2 1

22UF_6.3V_5

VRPVCCSA

C6503

2 1

OUT

14A6

C6521

0.22UF_6.3V_2

R6520

5.11K_1%_2

25

24

23

22

21

20

19

21

TML

VIN

VIN

PGND

PGND

PGND

R6521

21

1

2

3

GND

VREF

COMP

U6500

V5FILT

V5DRV

PGOOD

18

16

RSC_0402_DY

5

4

6

TI_TPS51461RGER_QFN_24P

VOUT

SLEW

MODE

SWVIN

SW

SW

SW

SW

BST

VID0

VID1

EN

151417

13

7

8

9

10

11

12

VRPVSA_PH

R6524

SHORT_0402

R6525

SHORT_0402

C6524

2 1

1UF_6.3V_2

C6520

21

3300PF_50V_2

P5V0A

2 1

C6510

22UF_6.3V_5

2 1

C6511

2 1

0.1UF_16V_2

B

C6523

2 1

1UF_6.3V_2

D

CC

B

SA_PG

OUT

14A6 21B6

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7010

D

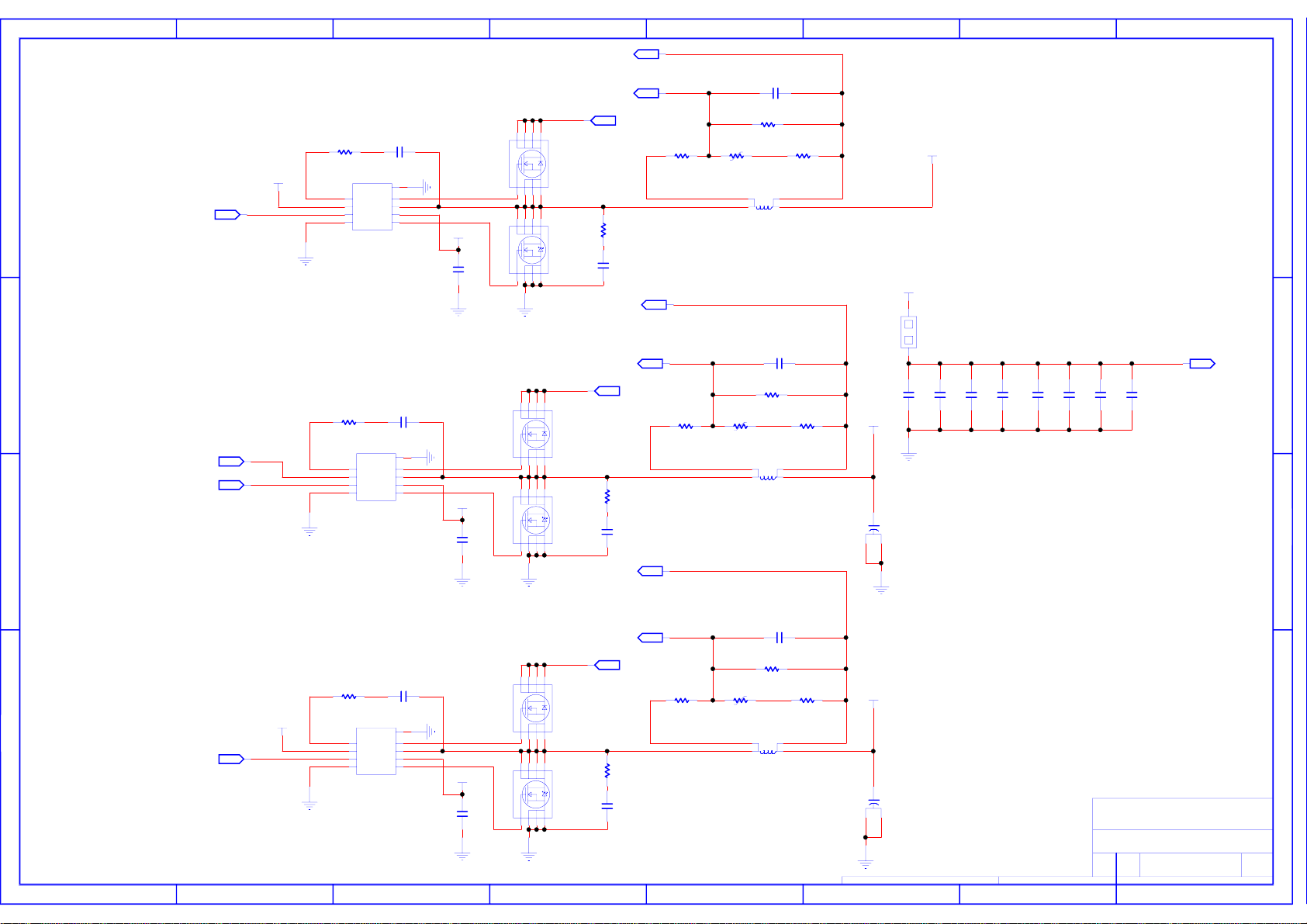

B

R6620

R6621

R6622

R6626

R6711

R6712

R6719

R6723

R6635

R6636

R6714

R6716

R6721

R6725

R6726

R6722

R6720

R6713

R6715

VREF_CPU

R6711

100K_1%_2

2 1

R6712

24K_1%_2

2 1

21D3

8 7

DIS.

UMA/PX

3+0

71.5K 71.5K

42.2K

100K

4.7K

75KR6627

100K

24K

DNP

DNP

DNP DNP

DNP

DNP

DNP

DNP

DNP

0

0R6724

0

0

0

0

R6628

RSC_0402_DY

2+13+2

44.2K

42.2K

90.9K

100K

39K

3.3KDNP

DNP

56K

200K

DNP

30K

DNP

0

DNP

DNP

0

0

DNP

0

0

DNP

DNP

0

0

0

0

0

DNP DNP

DNP

0

DNP

DNP

DNP

0

DNP

0

DNP

0 DNP

DNP

P3V3A

11C8 11D4

11B7

11A4

IN

11A7

C6633

2.2UF_6.3V_3

2 1

2 1

R6629

20K_1%_2

GFX_VSS_SENSE

IN

IN

R6630

0_5%_2

2 1

R6631

RSC_0402_DY

GFX_VCC_SENSE

VR_ON

45C3

2 1

EN_PVCORE

IN

2 1

8

2+0

44.2K

90.9K

39K

DNP

DNP

DNP

DNP

0

0

0

0

0

0

0

0

DNP

DNP

DNP

DNP

11D6 11D7

OUT

2.2UF_6.3V_3

40B4

49B7

R6713

R6715

0_5%_2_DY

OUT

VREF_CPU

C6634

11A4

11A344C2

44C2

11A344C2

0_5%_2

0_5%_2

R6714

11C7

11C8 11B7

IN

VREF_CPU

R6626

4.7K_1%_2

C6632

47PF_50V_2

R6625

15.4K_1%_2

2 1

R6627

75K_1%_2

2 1

VR_ON

IN

CORE_PG

OUT

2 1

21C341D6

11A4

21

21

2 1

IN

OUT

BI

OUT

OUT

11D7

11D6

11C8

11A4

11A7

11D4

R6716

0_5%_2_DY

2 1

VR_SVID_CLK

VR_SVID_ALERT#

VR_SVID_DATA

CPU_PROCHOT#

AXG_PG

VREF_CPU

IN

7.5K_1%_2

11A411B711C811D411D611D7

C6726

47PF_50V_2

R6718

IN

7 6

11A411A711D411D7

13

14

15

16

17

18

19

20

21

22

23

24

VREF_CPU

6 5

2 1

1

36

CPWM3

OUT

100K_1%_2

24K_1%_2

R6618

100K_5%_NTC

OUT

2.2UF_10V_3

CTHERM

GND

V5

CDH1

CBST1

CSW1

CDL1

V5DRV

PGND

CDL2

CSW2

CBST2

CDH2

VBAT

CPWM3

OUT

12D7

VREF_CPU

21

GSKIP#

R6622

R6623

C6629

21

21

C6631

0.1UF_16V_2_DY

2 1

15.4K_1%_2

V5_CPU

2 1

49

V5_CPU

48

47

R6601

46

2.2_5%_3

45

44

43

42

41

40

R6606

39

38

R6616

37

21

10K_5%_3

PVBAT

11A7 11B7 11C8 11D4 11D6 11D7

IN

12B7

OUT

R6620

VREF_CPU

IN

12D5

21

21

44B3

IN

VSSSENSE

12

CGFB

GOCP-R

VREF

V3R3

VR_ON

CPGOOD

VCLK

ALERT#

VDIO

VR_HOT#

SLEW

GPGOOD

GF_IMAX

GGFB

25

IN

44B3

IN

CPU_CSN3

VCCSENSE

9

10

11

CCOMP

CVFB

CCSN3

U6600

TI_TPS51650RSLR_QFN_48P

GCOMP

GCSN1

GVFB

282729

26

P3V3A

21

21

R6719

R6721

R6723

R6725

21

0_5%_2_DY

21

0_5%_2_DY

21

0_5%_2_DY

21

0_5%_2_DY

2 1

71.5K_1%_2

42.2K_1%_2

IN

RSC_0402_DY

CPU_CSP3

8

CCSP3

GCSP1

0_5%_2

0_5%_2

2 1

R6720

R6724

21

RSC_0402_DY

R6621

21

P3V3A

R6635

11C3

11C3

RSC_0402_DY

R6636

21

IN

IN

CPU_CSN2

CPU_CSP2

7

6

CCSP2

CCSN2

GCSN2

GCSP2

30

31

0_5%_2

0_5%_2

2 1

2 1

R6726

R6722

R6624

21

11D3

11D3

IN

IN

CPU_CSN1

CPU_CSP1

5

4

CCSN1

CCSP1

GTHERM

GSKIP#

323334

2 1

2

3

COCP-R

CF-IMAX

GPWM1

GPWM2

35

GPWM1

GPWM2

OUT

12B7

12A7

R6731

RSC_0402_DY

R6619

21

21

R6617

10_5%_3

IN

4

PVBAT

POWERPAD_2_0610

VREF_CPU

21

P5V0A

21

C6630

2 1

11D5

C6622

0.1UF_16V_2

P5V0A

C6624

0.1UF_16V_22.2_5%_3

PAD6610

1 2

C6699

68UF_25V

IN

4.7UF_10V_3

21

21

11D7

21

+

C6610

2 1

2 1

678

NMOS_4D3S

G

3

678

FDMS0306AS

G

3

678

FDMC7696FDMC7696

NMOS_4D3S

G

3

678

FDMS0306AS

G

3

P3V3A

R6730

2 1

R6728

15.4K_1%_2

GPU_CSN2

GPU_CSP2

GPU_CSN1

GPU_CSP1

IN

IN

IN

21

21

12B5

12A5

12C5

12C5

R6729

100K_5%_NTC

IN

2 1

100K_5%_2

C6727

0.1UF_16V_2_DY

11C740B449B7

11B7

OUT

OUT

CORE_PG

AXG_PG

R6732

R6634

2 1

2K_5%_2

2 1

5 4

3 2 1

C6611

4.7UF_25V_5

11B711A711A4

PVBAT_CPU

Q6610

D

S

214 5

Q6611

D

S

214 5

PVBAT_CPU

Q6620

D

S

214 5

Q6621

D

S

214 5

2 1

4.7UF_25V_5

11C8 11D6

2 1

IN

IN

2 1

4.7UF_25V_5

11D5

11D5

R7661

RSC_0603_DY

2 1

C7661

CSC0402_DY

2 1

11D5

11D6

11D1 11D3 12D5

R7662

RSC_0603_DY

2 1

C7662

CSC0402_DY

2 1

4.7UF_25V_5

OUT

OUT

2 1

11D111B3

OUT

OUT

2 1

4.7UF_25V_5

CPU_CSN1

CPU_CSP1

12D5

R6602

17.8K_1%_2

CPU_CSN2

CPU_CSP2

R6607

17.8K_1%_2

2 1

4.7UF_25V_5

21

100K_5%_NTC

21

100K_5%_NTC

4.7UF_25V_5

R6603

2 1

4.7UF_25V_5

0.022UF_16V_2

R6605

240K_1%_2

21

ETQP4LR36AFM

L6610

0.022UF_16V_2

R6610

240K_1%_2

R6608

21

ETQP4LR36AFM

L6620

2 1

C6623

C6625

4.7UF_25V_5

21

21

R6604

28.7K_1%_2

43

21

21

21

R6609

28.7K_1%_2

43

21

C6619

C6618

C6617

C6616

C6615

C6614

C6613

C6612

P1V05S

C6635

R6633

2K_5%_2

11C7

44C2

11C744C2

CHANGE by

IN

BI

VR_SVID_CLK

VR_SVID_DATA

R6632

130_1%_2

54.9_1%_2

2 1

DATE

2 1

2 1

0.1UF_16V_2

INVENTEC

SIZE

21-OCT-2002XXX

23

A3

C6621

C6620

2 1

2 1

4.7UF_25V_5

4.7UF_25V_5

21

1

+

3

2

21

1

C6602

+

3

2

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

CS

SHEET

PVBAT_CPU

2 1

4.7UF_25V_5

C6600

470UF_2V

of

1

PVCORE

2

7011

OUT

C6601

1

470UF_2V

+

3

PVCORE

1

470UF_2V470UF_2V

+

3

2

C6603

REV

X011310xxxxx-0-0

D

CC

B

AA

8 7

R6611

21

2.2_5%_3 0.1UF_16V_2

D

11B5

IN

P5V0A

CPWM3

U6630

3

PWM

4 5

GND DRVL

TI_TPS51601DRBR_SON_8P

6 5

C6626

21

9

PAD

81

DRVHBST

72

SWSKIP#

6

VDD

P5V0A

4

OUT

OUT

11D111B3

CPU_CSN3

CPU_CSP3

11D3

R6612

21

R6613

100K_5%_NTC17.8K_1%_2

C6628

0.022UF_16V_2

R6615

240K_1%_2

21

ETQP4LR36AFM

L6630

21

21

R6614

28.7K_1%_2

43

21

21

11D6

11D6

PVBAT_CPU

678

FDMC7696

FDMS0306AS

Q6630

D

NMOS_4D3S

G

S

3

214 5

678

Q6631

D

IN

R7663

RSC_0603_DY

3 2 1

PVCORE

D

2 1

G

C6627

2 1

1UF_6.3V_2

21

U6710

PWM

GND DRVL

C6720

0.1UF_16V_2

9

PAD

81

DRVHBST

72

SWSKIP#

6

VDD

21

P5V0A

C6721

2 1

1UF_6.3V_2

R6701

2.2_5%_3

11A4

11B5

GSKIP#

IN

GPWM1

IN

3

4 5

TI_TPS51601DRBR_SON_8P

B

S

3

214 5

PVBAT_AXG

678

FDMC7696

Q6710

D

NMOS_4D3S

G

S

3

214 5

678

Q6711

D S

G

S

3

214 5

C7663

CSC0402_DY

2 1

11A6

11A6

IN

R7671

RSC_0603_DY

2 1

C7671

CSC0402_DY

2 1

11A5

OUT

OUT

12A5 12C1

OUT

GPU_CSN1

GPU_CSP1

R6702

17.8K_1%_2

GPU_CSN2

21

100K_5%_NTC

0.022UF_16V_2

R6705

169K_1%_2

R6703

21

ETQP4LR36AFM

L6710

C6722

28.7K_1%_2

43

21

PVBAT

12

PAD6710

POWERPAD_2_0610

21

21

R6704

21

PVAXG

1

+

3

2

C6710

C6700

470UF_2V

2 1

C6716

C6715

C6714

C6713

C6712

C6711

2 1

2 1

2 1

2 1

4.7UF_25V_5

4.7UF_25V_5

4.7UF_25V_5

4.7UF_25V_5

2 1

2 1

4.7UF_25V_5

4.7UF_25V_5

PVBAT_AXG

OUT

12A5 12C5

CC

C6717

2 1

2 1

4.7UF_25V_5

4.7UF_25V_5

B

OUT

12C5

GPU_CSP2

R6707

17.8K_1%_2

21

100K_5%_NTC

11A6

R6706

PVBAT_AXG

678

C6723

21

21

FDMC7696

Q6720

D

NMOS_4D3S

12C1

IN

2.2_5%_3 0.1UF_16V_2

P5V0A

11B5

8

GPWM2

IN

7 6

U6720

3

PWM

4 5

GND DRVL

9

PAD

81

DRVHBST

72

SWSKIP#

6

VDD

TI_TPS51601DRBR_SON_8P

P5V0A

C6724

2 1

G

S

3

214 5

678

FDMS0306ASFDMS0306AS

Q6721

D

R7672

RSC_0603_DY

2 1

G

3

1UF_6.3V_2

214 5

C7672

CSC0402_DY

2 1

5 4

0.022UF_16V_2

R6710

169K_1%_2

R6708

21

ETQP4LR36AFM

L6720

C6725

28.7K_1%_2

43

21

21

21

R6709

PVAXG

21

AA

1

C6701

470UF_2V

+

2

CHANGE by

3

DATE

21-OCT-2002XXX

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

SHEET

of

7012

1

REV

X011310xxxxx-0-0

8 7

6 5

4

3 2 1

13B216A1

16C4

16A8

13D2

16A1

49A1

21D6

14B8

13D2

14A6

14D2

45D3

13C3

16A816C4

21D645D3

13A214A6

14B814D2

49A1

IN

IN

IN

PVBAT

56F7

56C5

P5V0A

C6954

2 1

12

PAD6760

2 1

POWERPAD_2_0610

678

FDMS7692

FDMS0306AS

Q6750

D

NMOS_4D3S

G

S

3

214 5

678

Q6751

D

G

S

3

214 5

ANPEC_APL5930KAI_TRL_SOP_8P

1UF_10V_2

C6761

C6760

2 1

2 1

4.7UF_25V_5

PAN_ETQP4LR36WFC_4P

R7675

2 1

RSC_0603_DY

C7675

2 1

CSC0402_DY

P1V5S_DGPU

C6955

2 1

22UF_6.3V_5

U6950

5

VIN

6

VCNTL

7

POK

8

EN

9

VIN

4.7UF_25V_5

L6750

VOUT

VOUT

FB

GND

C6762

2 1

4.7UF_25V_5

1

+

C6750

3

2

2.7K_1%_2

C6950

2 1

10K_1%_2

VRPVCORE_DGPU

1

C6752

+

470UF_2V

470UF_2V

3

2

VRPVPCIE

C6951

2 1

1UF_10V_2

22UF_6.3V_5

OUT

OUT

13A2

13C2

21

43

R6750

2.2K_1%_2

2 1

R6751

10K_1%_2

2 1

4

C6952

3

2

1

R6950

2 1

2 1

68PF_50V_2

R6951

2 1

D

P5V0A

R6756

21

10_5%_2

C6757

C6754

2 1

2 1

1UF_6.3V_2

1UF_6.3V_2

OUT

IN

:

G1G0

0

1

DGPU_PWRGD

EN_DGPU

SEYMOUR XTX

VOUT

1.15

1.05

1

0.9

THAMES XT

VOUT

N/A

0.9

13B252C6

13D1

VGA TYPE

B

010

0

1

1

R6755

240K_5%_2

U6750

16

TON

9

VDDP

2

VDD

4

PGOOD

10

CS

R6758

13K_1%_2

15 5

2 1

EN_DEM D1

17

GND

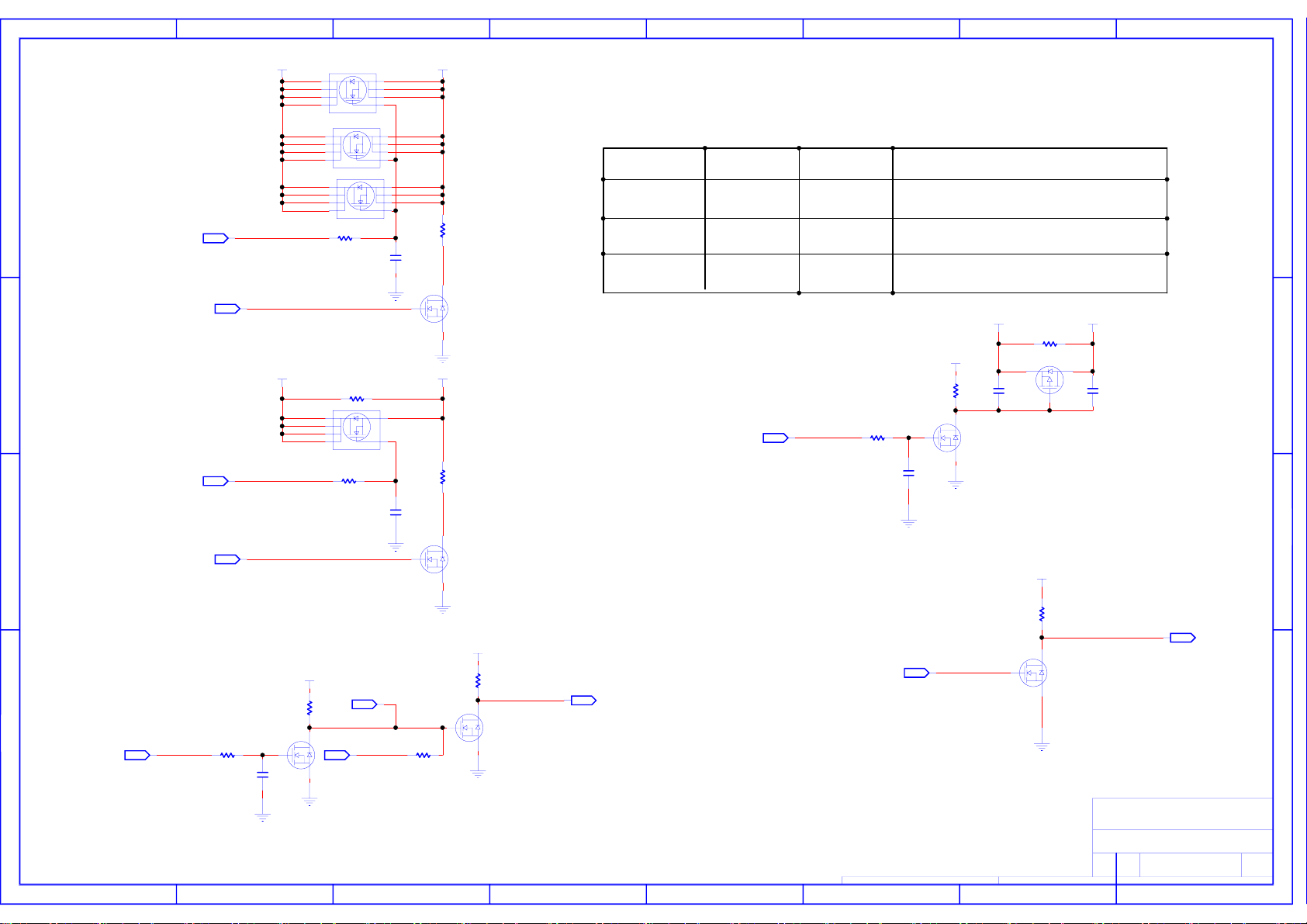

REA_RT8208BGQW_WQFN_16P

THAMES LE

VOUT

RESISTOR VALUE

N/A

N/AN/A

11

0.9

21

13

BOOT

12

UGATE

11

PHASE

8

LGATE

7

G0

3

FB

14

G1

R6753

6

D0

R6754

1

VOUT

R6750(R1)

R6751(R2)

R6754(R3)

R6753(R4)

R6752

2.2_5%_3

21

VRPVCORE_DGPU_HG

VRPVCORE_DGPU_PH

VRPVCORE_DGPU_LG

PWRCNTL_0

PWRCNTL_1

21

10K_1%_2

21

16.5K_1%_2

IN

IN

P.S. R6750(R1)R6751(R2)R6753(R3)R6754(R4)

2.2 K

10 K

16.5 K

10 K

13B1

IN

C6753

0.1UF_16V_2

56D5 56F7

EN_VPCIE

21

DGPU_PWR_EN EN_DGPU

SLP_S3#_3R

IN

VRPVCORE_DGPU

DGPU_PWRGD

IN

DGPU_PWR_EN

SLP_S3#_3R

13A3

VRPVPCIE

IN

10K_5%_2

0_5%_2_DY

P3V3S_DGPU

100K_5%_2_DY

R7019

1K_5%_2

R7030

0_5%_2_DY

R7016

21

R7020

21

C7010

2 1

PVCORE_DGPU

PAD6750

1 2

POWERPAD_2_0610

PAD6751

1 2

POWERPAD_2_0610

R7017

10K_5%_2

2 1

P1V5S_DGPU

1

R7018

2

EN_VPCIE

21

21

C7011

2 1

1UF_6.3V_2

PAD6950

21

1 2

POWERPAD_2_0610

0.1UF_16V_2

21

21

OUT

PVPCIE

OUTIN

C6751

+

560UF_2.5V

2 1

OUT

13C8

D

CC

B

13A6

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7013

D

14D6

3V & 5V

EC_PW_ON#

15D4

IN

21C3

21F6

14C8

IN

15D6

VRP3V3A_LDO

6B614C6

IN

IN

6C36C6

IN

21F6

14D8

IN

15D6

VCCIO

8 7

3

Q7000

DS

1

G

C7000

SSM3K7002BFU

P5VAUXON

3

2

C

A2A1

2 1

0.047UF_16V_2

D7000

BAT54C_30V_0.2A_DY

2 1

R7000

21

RSC_0402_DY

VBATP

P5VAUXON

R7001

10K_5%_2

R7002

0_5%_3

R7003

0_5%_2

21

21

21

SKIP_3V_5VVRP5V0A

VRP5V0A_VIN

EN_3V_5V

EN_5V

EN_3V

OUT

OUT

OUT

OUT

OUT

6 5

6D6

IN

IN

IN

VRP5V0A

VRP3V3A

VRP5V0A_LDO

6C114C814D4

6C8

6B4

6D6

PAD6150

POWERPAD_2_0610

PAD6100

POWERPAD_2_0610

PAD6120

POWERPAD1X1M

1 2

1 2

1 2

21

21

21

P5V0A

P3V3AL

P5V0AL

C6151

++

330UF_6.3V_DY

2 1

C6101

330UF_6.3V_DY

2 1

IN

VRP5V0A_LG

6B3

P3V3_LDO

6B56C114D4

6B5

6B4

IN

POWERPAD1X1M

VRP3V3A_LDO

6B614C8

1 2

PAD6121

21

VCCSA

4

6C114C814D6

IN

DGPU

VRP5V0A

2 1

C7001

0.1UF_16V_2

C7002

0.1UF_16V_2

2 1

D7002

DIODES_BAV99

3

3

21

D7001

DIODES_BAV99

21

C7004

1UF_25V_3

2 1

3 2 1

DDR_P1V5

49A1

C7003

2 1

0.1UF_16V_2

P15V0A

21D6

14A6

13D2

14B8

45D3

49B3

IN

IN

7B314C2

7C1

SLP_S3#_3R

SLP_S5#_3R

1V5_PG

IN

IN

VRP1V5

47K_5%_2

R7012

P3V3S

21

R7013

R7010

0_5%_2

RSC_0402_DY

P1V8S

21

C7005

0.1UF_16V_2

2 1

21

C7006

CSC0402_DY

2 1

PAD6200

1 2

POWERPAD_2_0610

PAD6201

1 2

POWERPAD_2_0610

EN_0V75

1V5_PG

21

21

EN_1V5

P1V5

OUT

OUT

OUT

7C713A2

7C721D3

D

CC

49A1

21D6

14A6

13A2

13D2

14D2

45D3

IN

SLP_S3#_3R

B

R7021

47K_5%_2

EN_VCCP

21

OUT

9D6

C7020

2 1

0.1UF_16V_2

14A8

VCCP_PG

9C6

P3V3S

21

SA_PG SA_PG

SLP_S3#_3R

IN

14B6

R7022

9C614A8

VCCP_PG

IN

10K_5%_2

VCCP_PG

OUT

10A514A621B6

49A1

13A213D214B8

14D221D645D3

P1V05S

PAD6300

21

1 2

POWERPAD_2_0610

VRP1V05S

9B1

IN

8

PAD6301

1 2

POWERPAD_2_0610

21

7 6

10C1

IN

VRPVCCSA

R7040

21

0_5%_2

2 1

2

D7040

NC

BAT54_30V_0.2A

PAD6500

1 2

POWERPAD_2_0610

EN_SA

C7040

CSC0402_DY

10B4

OUTIN

P3V3S

R7041

10K_5%_2

2 1

13

OUTIN

PVSA

21

5 4

CHANGE by

DATE

P3V3S

R7050

10K_5%_2

EN_1V8

21

OUT

8B4

B

C7050

0.01UF_50V_2

2 1

P1V8S

VRP1V8S

8B2

IN

PAD6900

1 2

POWERPAD_2_0610

21

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

SHEET

21-OCT-2002XXX

23

of

1

REV

X011310xxxxx-0-0

7014

8 7

6 5

4

3 2 1

R7105

100K_5%_2

C7100

2200PF_50V_2

P3V3AL

1

2

5

Q7102

D

NMOS_4D1S

AO6402AL

S

G

4

POWERPAD_2_0610

36

PAD7100

1 2

Q7103

1

SSM3K7002BFU

P3V3A

21

R7106

200_5%_2

2 1

D

3

DS

G

2

CC

B

P3V3AL

PVBAT P3V3_LDO

R7491

510K_1%_2

D

56D6

40A8

40B1

THRM_SHUTDWN#

OUT

BAT54_30V_0.2A

D7490

2

NC

R7492

120K_1%_2

2 1

13

2 1

P15V0A

R7107

2 1

470K_5%_2

3

Q7104

16A7

15A4

15B4

49B1

SLP_S3_3R

IN

SSM3K7002BFU

DS

1

G

2

B

4

U7490

VDD

5 3

SENSE RESET#

GND

GND

TI_TPS3801_01_SC70_5P

2

1

C7101

2 1

2200PF_50V_2

P5VAUXON

OUT

14C8 14D8 21F6

P3V3AL

R7108

SHORT_0402

P5V0A

R7110

SHORT_0402

1

1

2

5

2

5

21

21

Q7105

D

NMOS_4D1S

AO6402AL

Q7107

D

NMOS_4D1S

AO6402AL

4

S

36

G

C7102

2 1

4

S

36

G

C7104

2 1

PAD7101

POWERPAD_2_0610

2 1

680PF_50V_2

PAD7102

POWERPAD_2_0610

2 1

12

CSC0402_DY

IN

EC_PW_ON#

14D821C3

P3V3S

12

C7103

2 1

22UF_6.3V_5

49B1

15B8

15A4

15B4

16A7

SLP_S3_3R

IN

P5V0S

C7105

2 1

49B1

22UF_6.3V_5

15B8

15A4

15B4

16A7

SLP_S3_3R

IN

R7104

100K_5%_2_DY

2 1

R7100

10K_5%_2

2 1

Q7106

1

SSM3K7002BFU

Q7108

1

SSM3K7002BFU

G

G

R7109

2 1

3

DS

2

R7111

3

2 1

DS

2

Q7101

1

G

SSM3K7002BFU

200_5%_2

200_5%_2

3

DS

2

P15V0A

2 1

2 1

21

P1V5S

C7107

2 1

REV

X011310xxxxx-0-0

AA

R7113

3

P0V75S

200_5%_2

2 1

Q7110

IN

SLP_S3_3R

15B415B8

22UF_6.3V_5

16A749B1

SSM3K7002BFU

1

DS

G

2

1

SSM3K7002BFU

CHANGE by

Q7111

R7114

200_5%_2

3

2 1

DS

G

2

DATE

21-OCT-2002XXX

23

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

SHEET

of

7015

1

R7112

P1V5

8

7

6

8

7

6

21

Q7109

D

NMOS_4D3S

AM7330N

Q7112

D

NMOS_4D3S

AM7330N_DY

S

G

S

G

PAD7103

POWERPAD_2_0610

1

2

3

45

1

2

3

45

1 2

SHORT_0402

C7106

2 1

CSC0402_DY

8

7 6

5 4

8 7

6 5

4

3 2 1

1

2

3

45

1

2

3

45

2 1

4

36

2 1

0_5%_2_DY

1

G

1

G

SSM3K7002BFU

R7047

P1V5S_DGPU

R7115

200_5%_2

2 1

3

Q7115

DS

SSM3K7002BFU

2

P1V8S_DGPU

R7119

200_5%_2

2 1

3

Q7119

DS

SSM3K7002BFU

2

Q7019

1

G

21

P15V0A

R7034

1M_5%_2

DGPU_PWR_EN_15R

3

2 1

DS

2

POWER EXPRESS

DURING RESET

DGPU_PWR_EN#

DGPU_PWRGD

DGPU_HOLD_RST#

16B7 16D7

OUT

5 4

HIGH

LOW

13B213D216A116A8

IN

AFTER RESET

HIGH

DGPU_PWR_EN

LOW

CHANGE by

0 : DGPU POWER SWITCH TURNED ON

1 : POWER SWITCH TURNED OFF

0 : DGPU POWER IS NOT STABLE

1 : DGPU POWER IS STABLE

0 : KEEP DGPU IN RESET

1 : RESET IS RELEASED

P3V3S

R7031

10K_5%_2

3

R7039

0_5%_2

Q7002

SSM3K7002BFU

21

C7021

51B651C7

1

2 1

CSC0402_DY

IN

2 1

DS

G

2

DGPU_PWR_EN#

P3V3S P3V3S_DGPU

0_5%_2_DY

R7042

21

Q7003

S

C7023

2 1

CSC0402_DY

DIODES_DMP2305U_SOT23_3P

SD

G

G

D

C7024

2 1

CSC0402_DY

P3V3S

R7121

10K_5%_2

1

G

2 1

3

DS

Q7120

SSM3K7002BFU

DGPU_PWR_EN

2

INVENTEC

SIZE

DATE

21-OCT-2002XXX

23

A3

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

CS

SHEET

OUT

of

13B2 13D2 16A8

16C4

7016

1

REV

X011310xxxxx-0-0

D

CC

B

AA

P1V5

D

IN

16A616B7

IN

DGPU_PWR_EN_15R

DGPU_PWR_EN_3R

16A516B7

P1V8S

16A516D7

DGPU_PWR_EN_15R

IN

Q7121

Q7113

8

D

7

6

8

7

6

8

7

6

220K_5%_2

1

2

5

220K_5%_2

NMOS_4D3S

AM7330N

Q7114

D

NMOS_4D3S

AM7330N

D

NMOS_4D3S

AM7330N_DY

R7116

680PF_50V_2

R7038

Q7118

D

NMOS_4D1S

AO6402AL

R7120

680PF_50V_2

S

G

S

G

S

G

21

C7108

0_5%_6_DY

21

S

G

21

C7110

1

2

3

45

B

16A616C7

DGPU_PWR_EN_3R

IN

P3V3_LDO

16B7

IN

16C7

R7033

10K_5%_2

DGPU_PWR_EN_3R

3

Q7018

SSM3K7002BFU

IN

DGPU_PWR_EN

13B213D216A116C4

R7035

0_5%_2

21

C7022

2 1

2 1

DS

1

G

IN

SLP_S3_3R

2

CSC0402_DY

8

7 6

8 7

REFERENCE 0~49(PCB SCREW)

6 5

4

3 2 1

D

FIX1

1

FIX_MASK

FIX2

1

FIX_MASK

FIX3

1

FIX_MASK

FIX4

1

FIX_MASK

FIX5

1

FIX_MASK

FIX6

1

FIX_MASK

FIX7

1

FIX_MASK

FIX8

1

FIX_MASK

BOUNDARY SCAN TEST POINT

PVCORE

1

1

PVADPTR

1

PVBAT

TP1

TP30

TP2

TP30

TP8

TP30 TP30

1

PVCORE_DGPU

TP30

TP9

1

1

TP30

TP4

TP3

1

TP30

TP6

1

TP30

TP10

1

PVAXG

TP30

TP5

TP7

1

TP30

D

CC

S1

1

SCREW300_1000_1P

S2

1

SCREW300_1000_1P

S3

1

SCREW300_1000_1P

S5

1

B

SCREW300_1000_1P

S6

1

SCREW300_1000_1P

S7

1

SCREW300_1000_1P

S8

1

SCREW300_1000_1P

S18

1

SCREW220_700_1P

S20

1

SCREW540_1000_NP_1P

CPU

1

1

1

1

S10

S11

S12

S13

SCREW330_600_1P

SCREW330_600_1P

SCREW330_600_1P

SCREW330_600_1P

GPU

1

1

S14

S15

SCREW330_600_1P

SCREW330_600_1P

WLANPCB

ST16

1

STDPAD_1.15_6-TOP

4.2MM

3G

ST17

1

STDPAD_1.15_6-TOP

4.2MM

ST18

1

STDPAD_1.15_6-TOP

4.2MM

FAN

ST21

1

STDPAD_1.15_6.0_TOP

2MM

B

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7017

8 7

REFERENCE 50-99(HALL SENSOR)

6 5

4

3 2 1

D

P3V3AL

R50

U50

VDD

3

GND

MAG_MH248BESO_SOT23_3P

OUT

100K_5%_2

1

2 1

2

C50

1000PF_50V_2

2 1

LID_SW#_3

OUT

D50

SFI_SFI0402ML120C_LF_SMD_2P_DY

2 1

2 1

21D3

B

D

CC

B

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7018

8 7

REFERENCE 100~199(LED)

6 5

4

3 2 1

D

POWER ON LED

D154 BRIGHT WHEN SYSTEM IS POWER ON

D154 BLINK WHEN SYSTEM GO TO SLEEP

D

P5V0A

21B6

IN

PWR_WLED#

TP100

1

TP30

D154

19_217_T1D_CP1Q2QY_3T

R160

21

21

220_5%_2

CC

WIFI/WIMAX/3G/LTE LED

21D6

WL_OLED#

IN

TP104

1

TP30

D156

HT_191UY

R155

21

150_5%_2

P3V3S

21

DC IN / BATTERY CHARGE LED

B

D152 BRIGHT:BOTH AC-ADAPTER IS PLUGGED IN AND BATTERY IS FULL CHARGED

D155 BRIGHT:WHILE CHARGING BATTERY FROM AC-ADAPTER

BLINK:LOW BATTERY

P5V0A

B

21B6

IN

DCIN_WLED#

TP102

1

TP30

D152

19_217_T1D_CP1Q2QY_3T

R152

21

21

220_5%_2

P3V3AL

21B6

IN

BAT_OLED#

TP103

1

TP30

D155

HT_191UY

R154

21

21

150_5%_2

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7019

8 7

6 5

4

3 2 1

REFERENCE 200~249(POWER CONN)

REFERENCE 250~299(KB/TP CONN)

D

21B6

21D6

21D6

IN

IN

IN

20D321B3

CAPS_LED#_3

SCROLL_LED#_3

NUM_LED#_3

21B3

IN

R250

R251

R252

SCAN_OUT<17..0>

OUT

SCAN_IN<7..0>

21

21

21

SCAN_OUT<16>

16

SCAN_OUT<17>

17

SCAN_OUT<4>

4

SCAN_OUT<2>

2

SCAN_OUT<13>

13

SCAN_OUT<15>

15

SCAN_OUT<1>

1

SCAN_OUT<0>

0

SCAN_OUT<11>

11

SCAN_OUT<9>

9

SCAN_OUT<5>

5

SCAN_OUT<6>

6

SCAN_OUT<10>

10

SCAN_OUT<14>

14

SCAN_OUT<8>

8

SCAN_OUT<12>

12

SCAN_OUT<7>

7

SCAN_OUT<3>

3

SCAN_IN<7>

7

SCAN_IN<2>

2

SCAN_IN<3>

3

SCAN_IN<4>

4

SCAN_IN<0>

0

SCAN_IN<5>

5

SCAN_IN<6>

6

SCAN_IN<1>

1

200_5%_2

200_5%_2_DY

200_5%_2

21

21

D258

SFI_SFI0402ML120C_LF_SMD_2P_DY SFI_SFI0402ML120C_LF_SMD_2P_DY

21

21

D259

R253

0_5%_2_DY

P3V3S

21

21

CN250

34

34

33

33

32

32

31

G

31

30

G

30

29

29

28

28

27

27

26

26

25

25

24

24

23

23

22

22

21

21

20

20

19

19

18

18

17

17

16

16

15

15

14

14

13

13

12

12

11

11

10

10

9

9

8

8

7

7

6

6

5

5

4

4

3

3

2

2

1

1

PTWO_196094_34021_3_34P

KEYBOARD CONN

D260

SFI_SFI0402ML120C_LF_SMD_2P_DY

21

G2

G1

D

IN

SCAN_IN<7..0>

SCAN_IN<0>

0

SCAN_IN<1>

1

SCAN_IN<2>

2

SCAN_IN<3>

3

SCAN_IN<4>

4

SCAN_IN<5>

5

SCAN_IN<6>

6

SCAN_IN<7>

7

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D250

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D251

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D252

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D253

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D254

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D255

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D256

21

SFI_SFI0402ML120C_LF_SMD_2P_DY

21D257

21

CC

20C621B3

B

BI

BI

BI

BI

IM_CLK_5

IM_DAT_5

PCH_3S_SMCLK

PCH_3S_SMDATA

20A521D3

20A521D3

38C839C848A8

38C839C848A8

PHP_PESD5V2S2UT_SOT23_3P_DY

P5V0S P3V3S

1

2

D280

3

CN280

G1

G1

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

G2

ACES_50503_0084N_001_8P

G2

P5V0S

CN281

1

1

20A721D3

20A721D3

IM_CLK_5

BI

IM_DAT_5

BI

2

2

3

4

G

3

G

4

ACES_50503_0044N_001_4P

G1

G2

21D3

PWR_SWIN#_3

OUT

21

21

D200

SFI_SFI0402ML120C_LF_SMD_2P_DY

CN200

1

1

2

2

ACES_50224_0020N_001_2P

3

G

4

G

POWER CONN

B

AA

TOUCHPAD CONN

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7020

8

7 6 5 4 3 2 1

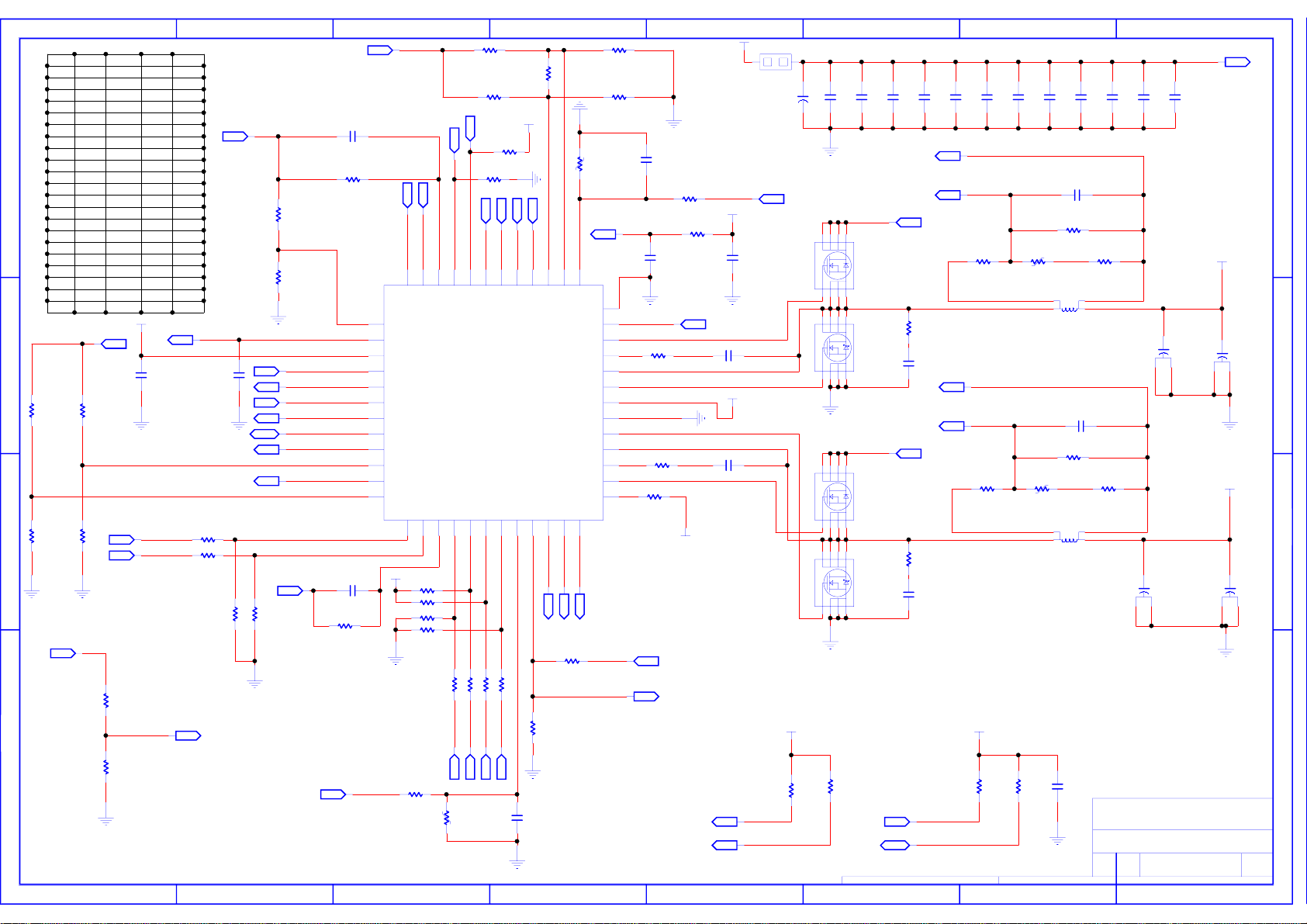

REFERENCE 300~389(KBC)

2.2_5%_3

FOR ESD PROTECT

P3V3AL

FBM_11_160808_121T

E

HW_I_ADC

5B721E6

IN

HW_V_ADC

5D521E6

IN

BATT_IN

5D321E6

OUT

D

C

B

EC_SMB1

1.BATTERY

P3V3A

R313

P3V3A

OUT

OUT

EC_SPI_CS0#

IN

EC_SPI_SO

3.3K_5%_2

R330

R315

EC_SPI_CS1#

IN

EC_SPI_SO

3.3K_5%_2_DY

R331

21D647A6

21C621C8

47A6

47A6

21C621C8

47A6

P3V3AL_RP3V3AL

R318

21

C313

4.7UF_6.3V_3

2 1

L300

21

C314

AGND_KBC

C316

C317

0.1UF_16V_2

0.1UF_16V_2

2 1

2 1

EC_SMB2

1.CHARGE

2.GPU THERMAL

3.CEC

10K_5%_2

21

U300

1

/CS

2

DO_IO1

21

3

/WP_IO2

4

GND

WINB_W25Q32BVSSIG_SOIC_8P

10K_5%_2_DY

21

U302

1

/CS

2

DO_IO1

21

3

/WP_IO2

4

GND

WINB_W25Q32BVSSIG_SOIC_8P_DY

C300

2 1

50D7

2 1

C315

2 1

0.1UF_16V_2

10UF_6.3V_5_DY

/HOLD_IO3

/HOLD_IO3

DI_ID0

C301

0.1UF_16V_2

2 1

P3V3AL_EC

C305

0.1UF_16V_2

2 1

0.1UF_16V_2

EC_SMB3

8

VCC

7

6

CLK

5

DI_ID0

8

VCC

7

6

CLK

5

C302

2 1

R314

R319

0.1UF_16V_2

21

EC_SPI_CLK

EC_SPI_SI

C304

C303

0.1UF_16V_2

2 1

2 1

PCH_LCM_BKLTEN

IN

GM:3CELL OPEN

PM:6CELL STUFF

3.3K_5%_2

EC_SPI_CLK

EC_SPI_SI

21

3.3K_5%_2_DY

P3V3AL

R320

2

P5VAUXON VCC_POR#

P3V3S

CLOSE PIN4

C306

C312

0.1UF_16V_2

0.1UF_16V_2

2 1

2 1

10UF_6.3V_5_DY

14C814D815D6 21B6

D300

BAT54_30V_0.2A

100K_5%_2

NC

2 1

13

OUTIN

FF

P3V3AL_EC

0_5%_1

R301

LCM_BKLTENVGA_LCM_BKLTEN

21

0_5%_1

R302

21

GM: 100K

R344

PM: 10K

100K_5%_2

2 1

3 CELL ID

R303

10K_5%_2

P3V3AL

R346

2 1

100K_5%_2

21C847A6

21C747A6

21C847A6

21C747A6

P3V3A

47A6

21C7 21D6

IN

21C6 21C7

IN

C309

47A6

0.1UF_16V_2

2 1

R345

10K_5%_2_DY

2 1

OUT

OUT

IN

OUT

OUTIN

21

EC_SPI_CS0#

EC_SPI_CLK

EC_SPI_SO

EC_SPI_SI

21E656D6

10K_5%_2

HW_I_ADC

5B721E8

IN

HW_V_ADC

5D521E8

IN

BATT_IN

5D321E8

IN

EC_BKLTEN

34B5

OUT

LCM_BKLTEN

21E6

IN

ACPRES

5B8

IN

EC_CTL3

32A8

OUT

SLP_S3#_3R

13A213D214A614B814D245D349A1

IN

HDMI_HPD_EC

36B237B1

OUT

SCROLL_LED#_3

20C7

OUT

NUM_LED#_3

20C7

OUT

49A549A6

ACPRESENT

IN

EC_PWRSW#

IN

LOW_BAT#_3

49A8

OUT

WL_OLED#

19B4

OUT

USB_OC#_1

33C6

OUT

EC_MUTE#

24A2

OUT

WOL_AUX_ON#

22D7

OUT

EC_ILIM_SEL

32A8

OUT

EC_CTL2

32A8

OUT

33_5%_2

R342

33_5%_2

R340

R341

33_5%_2

R332

21

21

21

P3V3S

2 1

2 1

2 1

TP311

TP30

TP314

TP30

TP315

TP30

TP316

TP30

TP307

TP30

TP317

TP30

TP330

TP30

TP331

TP30

TP318

TP30

EC_SPI_CLK_R

EC_SPI_SO_R

EC_SPI_SI_R

R323

10_5%_2

C323

0.1UF_16V_2

U301

104

VREF

97

GPIO90/AD0

98

GPIO91/AD1

99

GPIO92/AD2

100

1

GPIO93/AD3

108

GPIO05/AD4

96

GPIO04/AD5

95

GPIO03/AD6

94

GPIO07/AD7

101

GPIO94/DA0

105

1

GPIO95/DA1

106

GPIO96/DA2

107

GPIO97/DA3

79

1

GPIO02

114

GPIO16

6

1

GPIO24 GPIO27/PSDAT2

109

GPIO30/F_WP#

GPIO34/CIRRXL

1

GPIO36

80

GPIO41/F_WP#

26

GPIO51/N2TCK

123

73

GPIO70

74

GPIO71

75

1

GPIO72

1

117

GPIO20/TA2/IOX_DIN_DIO

112

GP(I)O84/IOX_SCLK/XORTR#

110

GPO82/IOX_LDSH/TEST#

1

93

GPIO06/IOX_DOUT

91

1

GPIO81/F_WP#

90

F_CS0#

92

F_SCK

86

F_SDI_F_SDIO1

87

F_SDIO_F_SDIO0

44

VCORF

C310

1UF_6.3V_2

2 1

P3V3AL_R

19

VCC1

GND2

GND1

18

887646

VCC4

VCC3

VCC2

GND5

GND4

GND3

897845

116

P3V3AL_EC

115

VCC5

GND6

5

2 1

POWERPAD1X1M

102

AVCC

PAD319

P3V3S

4

VDD

GPIO11/CLKRUN#

GPIO46/SDA4B/CIRRXM/TRST#

AGND

103

12

7

2

3

1

128

127

126

125

8

9

1

29

TP30

124

121

122

27

25

11

10

7114

7215

70

69

67

68

119

120

24

28

17

20

21

23

82

84

83

BUF_PLT_RST#

CLK_KBPCI

LPC_3S_FRAME#

LPC_3S_AD<3>

LPC_3S_AD<2>

LPC_3S_AD<1>

LPC_3S_AD<0>

PCI_3S_SERIRQ

PCI_3S_CLKRUN#

TP324

RUNSCI0#_3

EC_3S_A20GATE

KBRST#

2 1

TP30

EN_PVCORE

USB_OC#_2

IM_DAT_5

IM_CLK_5

EC_SMB1_CLK

EC_SMB1_DATA

EC_SMB2_CLK

EC_SMB2_DATA

AOAC_ON#

WLON#

FLASH_OVERRIDE

LID_SW#_3

TP30

TP30

TP30

TP30

EC_PW_ON#

SB_USB_1

EC_CTL1

LRESET#/GPIOF7

LCLK/GPIOF5

LFRAME#/GPIOF6

LAD3/GPIOF4

LAD2/GPIOF3

LAD1/GPIOF2

LAD0/GPIOF1

SERIRQ/GPIOF0

GPIO65/SMI#

ECSCI#/GPIO54

GPIO10/LPCPD#

GPIO85/GA20

KBRST#/GPIO86

GPIO52/PSDAT3/RDY#

GPIO50/PSCLK3/TDO

GPIO26/PSCLK2

GPIO35/PSDAT1

GPIO37/PSCLK1

GPIO17/SCL1/N2TCKGPIO67/N2TMS

GPIO22/SDA1/N2TMS

GPIO73/SCL2

GPIO74/SDA2

GPIO23/SCL3A

GPIO31/SDA3A

GPIO47/SCL4A

GPIO53/SDA4A

GPIO42/SCL3B/TCK

GPIO43/SDA3B/TMS

GPIO44/SCL4B/TDI

GPIO75/SPI_SCK

GPIO77/SPI_DI

GPIO76/SPI_DO

WINB_NPCE885LA0DX_LQFP_128P

TP30

R300

10K_5%_2

TP306

TP326

TP303

TP304

TP305

1

1

1

1

1

1

IN

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

TP325

P3V3AL

PWR_SWIN#_3

SB_USB_0

SLP_S5#_3R

H_PROCHOT_EC

SB_USB_2

OUT

OUT

OUT

27C3 27C7 28C3 51A8 57A6

51A7

27C3 47C3

27C3 47C3

27C3 47C3

27C3 47C3

27C3 47C3

27B7 47C2

49A5 49B3

51C7 52D6

20B3

OUT

RSMRST#

21D1 49B7 49C2

OUT

11A8

OUT

30A3

IN

20A5 20A7

BI

20A5 20A7

BI

5D3 21D2

BI

5D3 21D2

BI

5A7 21D2 37C6 56D8

BI

5A7 21D2 37C3 56C8

BI

21D2 27C2

BI

21D2 27B2

BI

47B7 47B8

OUT

18C4

IN

OUT

IN

OUT

OUT

14D8 15D4

33D8

32A8

32A8

14D2 49B3

21B1

30B6

P3V3S

E

R326

R312

10K_5%_2

2 1

2 1

10K_5%_2

52C2

OUT

52C2

OUT

EC_SMB1_CLK

5D321D3

BI

EC_SMB1_DATA

5D321D3

BI

EC_SMB2_CLK

5A721D337C656D8

BI

EC_SMB2_DATA

5A721D337C356C8

BI

AOAC_ON#

21D327C2

BI

WLON#

21D327B2

BI

RSMRST#

R333

10K_5%_2

2 1

R322

2 1

R321

2 1

R317

2 1

R316

2 1

R334

2 1

R335

OUT

3.3K_5%_2

3.3K_5%_2

1.8K_5%_2

1.8K_5%_2

10K_5%_2

10K_5%_2

21D3 49B7 49C2

P3V3AL

D

2 1

C

P3V3A

47A6

21C7 21D6

IN

21C6 21C7

IN

47A6

FAN_TACH1

C311

680PF_50V_2

2 1

C318

2 1

0.1UF_16V_2_DY

U301

31

1

21B6 40C8

IN

21B640C8

IN

SA_PG

10A514A6

IN

USB_OC#_0

PCH_PWROK

BAT_OLED#

DCIN_WLED#

FAN1_PWM

CAPS_LED#_3

PWR_WLED#

EC_32KHZ

LAN_RST#

VCC_POR#

R339

43_5%_2

TP320

TP321

TP322

TP323

EC_PECI

21

32A6

IN

49A649B7

OUT

19A7

OUT

19A7

OUT

40C6

OUT

20C7

OUT

19C7

OUT

49B3

IN

22B5

OUT

21F4

IN

H_PECI

41D552C2

BI

TP319

FAN_TACH1

P1V05S

TP30

TP30

TP30

TP30

TP30

GPIO56/TA1

63

GPIO14/TB1

64

GPIO01/TB2

32

1

GPIO15/A_PWM

118

GPIO21/B_PWM

62

GPIO13/C_PWM

65

GPIO32/D_PWM

22

1

GPIO45/E_PWM

81

GPIO66/G_PWM

66

GPIO33/H_PWM

16

GPIO40/F_PWM

111

1

GP(I)O83/SOUT_CR/TRIST#

113

1

GPIO87/CIRRXM/SIN_CR

77

GPIO00/EXTCLK

30

GPIO55/CLKOUT/IOX_DIN_DIO

85

VCC_POR#

13

PECI

12

VTT

WINB_NPCE885LA0DX_LQFP_128P

AGND_KBC

KBSOUT0/GPOB0/JENK#

KBSOUT1/GPIOB1/TCK

KBSOUT2/GPIOB2/TMS

KBSOUT3/GPIOB3/TDI

KBSOUT4/GPOB4/JEN0#

KBSOUT5/GPIOB5/TDO

KBSOUT6/GPIOB6/RDY#

KBSOUT7/GPIOB7

KBSOUT8/GPIOC0

KBSOUT9/GPOC1/SDP_VIS#

KBSOUT10_P80_CLK/GPIOC2

KBSOUT11_P80_DAT/GPIOC3

KBSOUT12/GPIO64

KBSOUT13/GPIO63

KBSOUT14/GPIO62

KBSOUT15/GPIO61/XOR_OUT

GPIO60/KBSOUT16

GPIO57/KBSOUT17

KBSIN0/GPIOA0/N2TCK

KBSIN1/GPIOA1/N2TMS

KBSIN2/GPIOA2

KBSIN3/GPIOA3

KBSIN4/GPIOA4

KBSIN5/GPIOA5

KBSIN6/GPIOA6

KBSIN7/GPIOA7

53

52

51

50

49

48

47

43

42

41

40

39

38

37

36

35

34

33

54

55

56

57

58

59

60

61

SCAN_OUT<0>

SCAN_OUT<1>

SCAN_OUT<2>

SCAN_OUT<3>

SCAN_OUT<4>

SCAN_OUT<5>

SCAN_OUT<6>

SCAN_OUT<7>

SCAN_OUT<8>

SCAN_OUT<9>

SCAN_OUT<10>

SCAN_OUT<11>

SCAN_OUT<12>

SCAN_OUT<13>

SCAN_OUT<14>

SCAN_OUT<15>

SCAN_OUT<16>

SCAN_OUT<17>

SCAN_IN<0>

SCAN_IN<1>

SCAN_IN<2>

SCAN_IN<3>

SCAN_IN<4>

SCAN_IN<5>

SCAN_IN<6>

SCAN_IN<7>

SCAN_OUT<17..0>

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

SCAN_IN<7..0>

0

1

2

3

4

5

6

7

OUT

CPU_PROCHOT#

11C741D6

OUT

20D6

3

Q300

DS

G

SSM3K7002BFU

2

H_PROCHOT_EC

1

R324

100K_5%_2

21D3

IN

2 1

B

20C6 20D3

IN

A

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

1310xxxxx-0-0

CHANGE by

8

7 6 5 4 3

XXX 21-OCT-2002

DATE

2 1

C CS

SHEET

of

21 70

A

REV

X01

8 7

REFERENCE 400~499(LAN)

6 5

4

3 2 1

D

IN

L400

WOL_AUX_ON#

PDVDDL_LAN

21

C406

21D6

PVLX_LAN

LQM21PN2R2MC0D_DY

B

FOR SW MODE

P3V3A

C400

2 1

S

2 1

CSC0402_DY

C407

10UF_6.3V_3_DY

Q400

DIODES_DMP2305U_SOT23_3P

D

SD

G

C401

G

2 1

R400

21

C408

X400

33PF_50V_2

0.047UF_16V_2

RSC_0603_DY

2 1

1000PF_50V_2_DY

25MHZ

100K_5%_2

2 1

0.1UF_16V_2_DY

C409

2 1

R406

21

C410

2 1

POWERPAD_2_0610

21

33PF_50V_2

PAD400

1 2

PAVDDL_LAN

C412

2 1

P3V3A_LAN

21

C402

2 1

C413

2 1

1UF_6.3V_2

C403

2 1

4.7UF_6.3V_3

P3V3S

21

22A5

0.1UF_16V_2

LAN_X1

LAN_X2

R401

C404

2 1

1UF_6.3V_2

0.1UF_16V_2

48C7 48D7 48D8

CLKREQ_LAN#

OUT

30K_5%_2

PAVDDH_LAN

C414

2 1

OUT

OUT

C405

1UF_6.3V_2

23B8

23C6

23B8

2 1

C415

21B6

22A5

22B5

22B5

10UF_6.3V_5_DY

2 1

PDVDDL_LAN

C427

P3V3A_LAN

LAN_RST#

IN

PCIE_WAKE#

OUT

LAN_X1

IN

LAN_X2

IN

23D6

23C8

0.1UF_16V_2

23C8

23D6

23B8

23C6

23B8

23B8

23B8

C426

2 1

1UF_6.3V_2

R405

2.37K_1%_2

BI

BI

BI

BI

BI

BI

BI

BI

PVLX_LAN

2 1

FOR LDO MODE

0.1UF_16V_2

R403

2 1

10K_5%_2

R404

2 1

10K_5%_2_DY

402339

U400

LX

GND

1

VDD33

PERSTN

WAKEN

CLKREQN

ISOLATN

AVDDL_REG

XTLO

XTLI

AVDDH_REG

RBIAS

C416

LED_1

TRXP0

TRXN0

12

2

3

4

6

7

8

10

21

LAN_TRD0_DP

LAN_TRD0_DN

LAN_TRD1_DP

LAN_TRD1_DN

LAN_TRD2_DP

LAN_TRD2_DN

LAN_TRD3_DP

LAN_TRD3_DN

PAVDDL_LAN

0.1UF_16V_2 0.1UF_16V_2

C417:8161 STUFF 8162 OPEN

38541

37

LED_0

DVDDL_REG

TRXP1

AVDDL

141115

13916

2 1

C424

2 1

PAVDDL_LAN

PCIE_LAN_TX_DN

PCIE_LAN_TX_DP

CLK_PCIE_LAN_DP

353633

RX_P

RX_N

TRXN1

AVDD33

CLK_PCIE_LAN_DN

32

34

31

AVDDL

AVDDLTRXP3

TX_P

REFCLK_P

TX_N

REFCLK_N

NC

TESTMODE

SMDATA

SMCLK

PPS

LED_2

AVDDH

TRXN3

AVDDL

TRXN2

TRXP2

ATHEROS_AR8161_BL3A_R_QFN_40P

201918

17

1UF_6.3V_2_DY

C417

2 1

PAVDDVCO_LAN

C425

2 1

1UF_6.3V_2_DY

0.1UF_16V_2

C423

0.1UF_16V_2

2 1

30

PCIE_LAN_RX_C_DP

29

PCIE_LAN_RX_C_DN

28

27

26

25

24

22

21

C418

2 1

R402

0_5%_3

2 1

C421

C422

PAVDDH_LAN

C420

2 1

P3V3A_LAN

C419

0.1UF_16V_2

2 1

48D8

IN

48D8

IN

48C7

IN

48C7

IN

0.1UF_16V_2

21

21

0.1UF_16V_2

0.1UF_16V_2

PCIE_LAN_RX_DP

PCIE_LAN_RX_DN

OUT

OUT

48D8

48D8

D

CC

B

AA

INVENTEC

TITLE

MODEL,PROJECT,FUNCTION

Block Diagram

DOC.NUMBER

CODE

SIZE

CS

A3

8

7 6

5 4

CHANGE by

DATE

21-OCT-2002XXX

23

SHEET

of

1

REV

X011310xxxxx-0-0

7022

8 7

REFERENCE 400~499(LAN)

6 5

4

3 2 1

23C223D3

23C223D3

23B223C3

23B223C2

23B223C2

23B223C3

23B223C2

D

IN

IN

IN

IN

LAN_TRD0_DN

LAN_TRD0_DP

LAN_TRD1_DN

LAN_TRD1_DP

22B523C8

P3V3AL

U460

1

I/O 1

2

GND

PANJIT_PJSRV05_4_DSSOT236P

IN

IN

LAN_TRD0_DP