TMI TAMARACK TC6216M Datasheet

TC6216M

- 1 -

Ver. 2.1

5/24/01

TC6216M

16 Port 10/100 Unmanaged QoS Ethernet Switch

4FL No. 106 Hsin-Tai Wu Road,

Sec. 1, Hsichih,

Taipei Hsien, Taiwan R.O.C.

TEL: 886-2-2696-1669

FAX: 886-2-2696-2220

http://www.tmi.com.tw/

TC6216M

- 2 -

Ver. 2.1

5/24/01

TABLE OF CONTENTS

1 Features......................................................................................................................................... 3

2 Description....................................................................................................................................3

3 Block Diagram.............................................................................................................................. 4

4 Pin Plcement ................................................................................................................................. 5

5 Pin Listing (PQFP 208)................................................................................................................. 6

6 Pin Description.............................................................................................................................. 8

7 Ethernet Media Access Controller.............................................................................................. 12

7.1 R

ECEIVE MAC

...................................................................................................................... 12

7.2 T

RANSMIT MAC

................................................................................................................... 12

8 Traffic Priority ............................................................................................................................ 13

9 Trunk Configuration ................................................................................................................... 14

10 Flow Control.............................................................................................................................. 15

11 Broadcast ................................................................................................................................... 15

12 Auto Negotiation ....................................................................................................................... 16

13 EEPROM Interface.................................................................................................................... 16

14 Programming The EEPROM For Configuration....................................................................... 16

15 EEPROM Address Map............................................................................................................. 17

16 Register Description ..................................................................................................................18

17 Timing Requirements ................................................................................................................ 23

18 Electrical Specifications ............................................................................................................ 26

19 Mechanical Specifications......................................................................................................... 27

Notice................................................................................................................................................. 28

TC6216M

- 3 -

Ver. 2.1

5/24/01

16 Port 10/100 Unmanaged QoS Ethernet Switch

1 Features

!"

Stand Alone Switch On A Chip

!"

16 Ethernet 10/100 ports with RMII Interface

!"

Port 16 is an RMII / MII port

!"

Embedded 512Kbytes SSRAM packet buffer

!"

16K MAC address table

!"

Multiple TC6216M can produce larger switches by trunking

!"

10/100 selectable for each port

!"

Full / Half Duplex for each port

!"

Highly integrated switching logic, including the MAC f unctions on a single ASIC

!"

Flow-control for Full and Half Duplex

!"

Three QoS levels checked via IP Header and 802.1Q VLAN Tag and/or selected per

port basis

!"

Maximum throughput

!"

Broadcast throttling

!"

Serial EEPROM Interface

!"

MDIO master for PHY configuration / polling

!"

3.3V/1.8V dual voltage power

!"

0.6 Watt power consumption

!"

0.18 micron technology

!"

Packaged in PQFP 208

2 Description

TC6216M is a stand-alone 16 ports 10/100 unmanaged switch controller designed for low cost high

performance solutions. In addition to the basic functions of unmanaged switches it provides features usually

associated with managed switches, at very high performance levels. TC6216M offers full wire-speed switching

on all 16 ports, self-learning of up to 16K MAC addresses, highly optimized flow control for full and half

duplex, evolved traffic priority services, flexible trunking capabilities.

A store-and-forward switching method using a non-blocking architecture is implemented within TC6216M to

improve the availability and bandwidth. The chip embeds a 512 Kbytes SSRAM packet buffer so the only

external components required are the physical layer transceivers. Normal, high and very high priority queues are

implemented for each transmission port.

The chip contains IEEE 802.3 MAC functions for 16 ports supporting both 10 Mbit/s and 100 Mbit/s data rates.

All ports are full and half duplex capable. Each port has its dedicated receive and transmit FIFO’s with necessary

logic to implement flow-control for both duplex modes. TC6216M utilizes PAUSE frames as defined in IEEE

802.3x for full duplex flow control, and executes backpressure for half duplex mode. No packet will be lost

when flow control is operational.

TC6216M provides leading edge QoS with three levels of priority. The priority can be checked via layer 2

(802.1Q VLAN Tagging) and/or layer 3 (IP Header TOS bits). Port based priority is also provided to enable user

selectable traffic prioritization. Port based priority ensures transmission with precedence for all packets incoming

from selected port(s). This feature allows effective video switching in multimedia applications and improved

support for voice over packet applications.

The chip handles a 16K MAC address-lookup table with searching, self-learning, automatic aging, at a very high

speed. Forwarding rules are implemented according with IEEE 802.1d specifications. TC6216M also provides

filtering capability for bad packets, only good CRC and valid sized packets will be forwarded.

Larger switches can be produced using TC6216M’s trunking capabilities. Two trunk groups of up to four ports

each can be setup with TC6216M. Several load balancing schemes are provided through pins and EEPROM

configuration.

TC6216M

- 4 -

Ver. 2.1

5/24/01

An external EEPROM device can be used to configure the TC6216M at power-up. Compared with pin

configuration interface, the EEPROM extends the chip’s configuration capability with new features and provides

a jumperless configuration mode using a parallel print port interface for reprogramming. TC6216M can make

effective use of most of its features without using the external EEPROM.

TC6216M use s an MDIO ma ster entity fo r PHY auto negotiate mode poll ing and link sta tus monitor ing. Befor e

extracting the autonegotiation result the chip advertises full duplex flow co ntrol ability on each por t and restarts

the autonegotiation.

Effective broadcast throttling based on both broadcast buffer memory utilization and broadcast ba ndwidth can be

performed by TC6216M.

TC6216M achieves full performance at 50 MHz clock frequency. It is packaged in 208 PQFP.

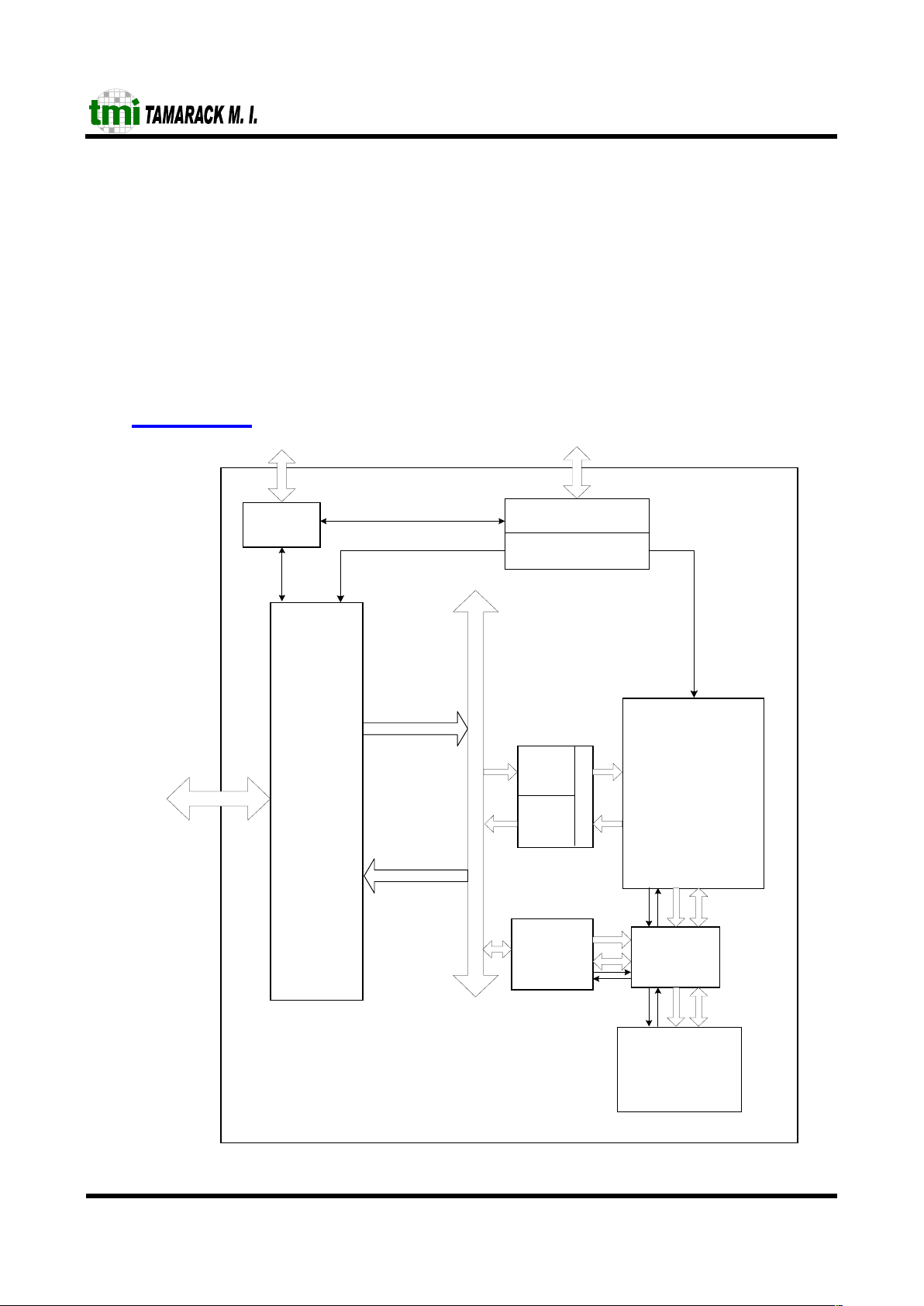

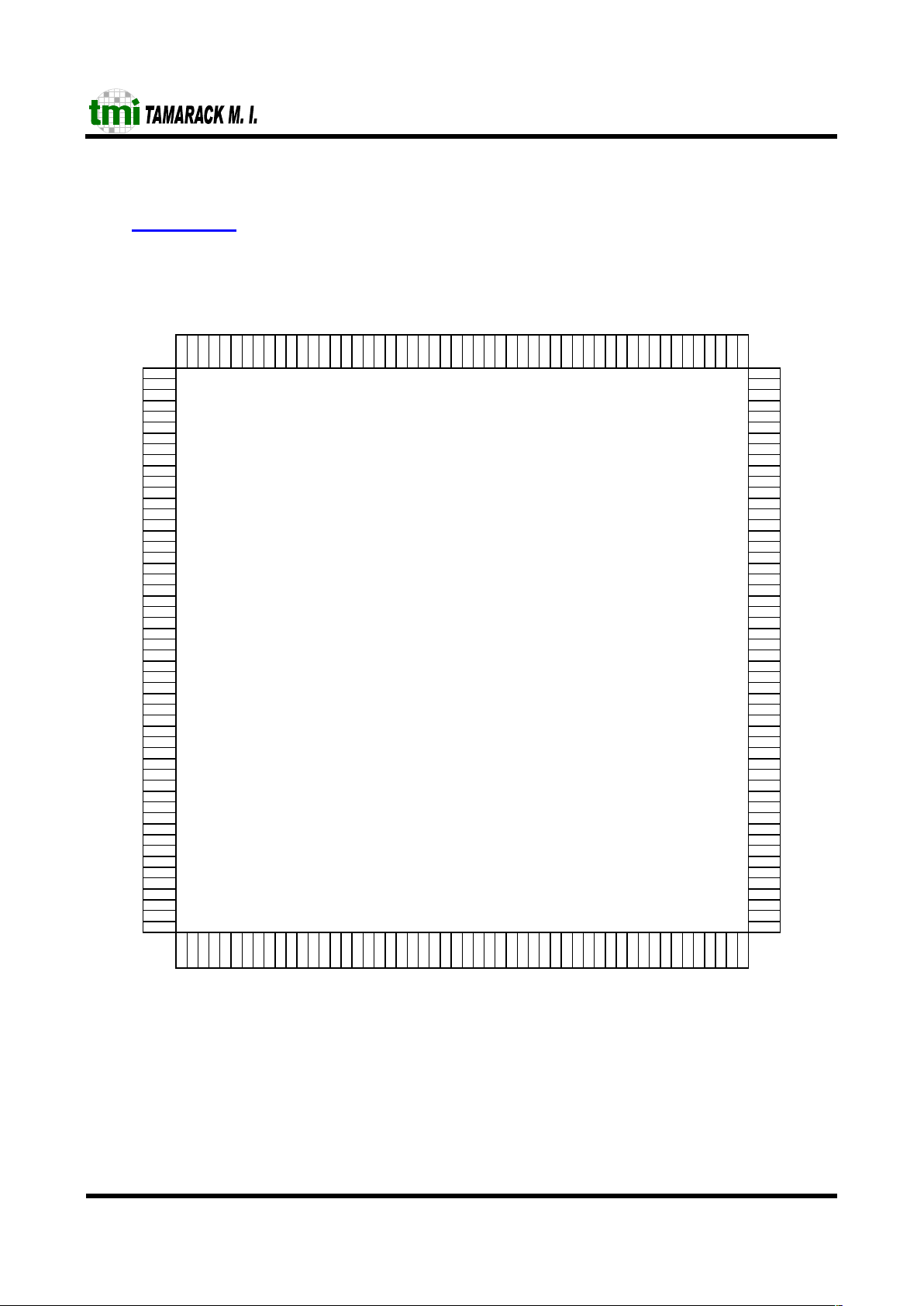

3 Block Diagram

From RX MAC

!

"

#

$$

#

#

$%&'(

)*

To TX MAC

%++*

%++*

,,

-

TC6216M

- 5 -

Ver. 2.1

5/24/01

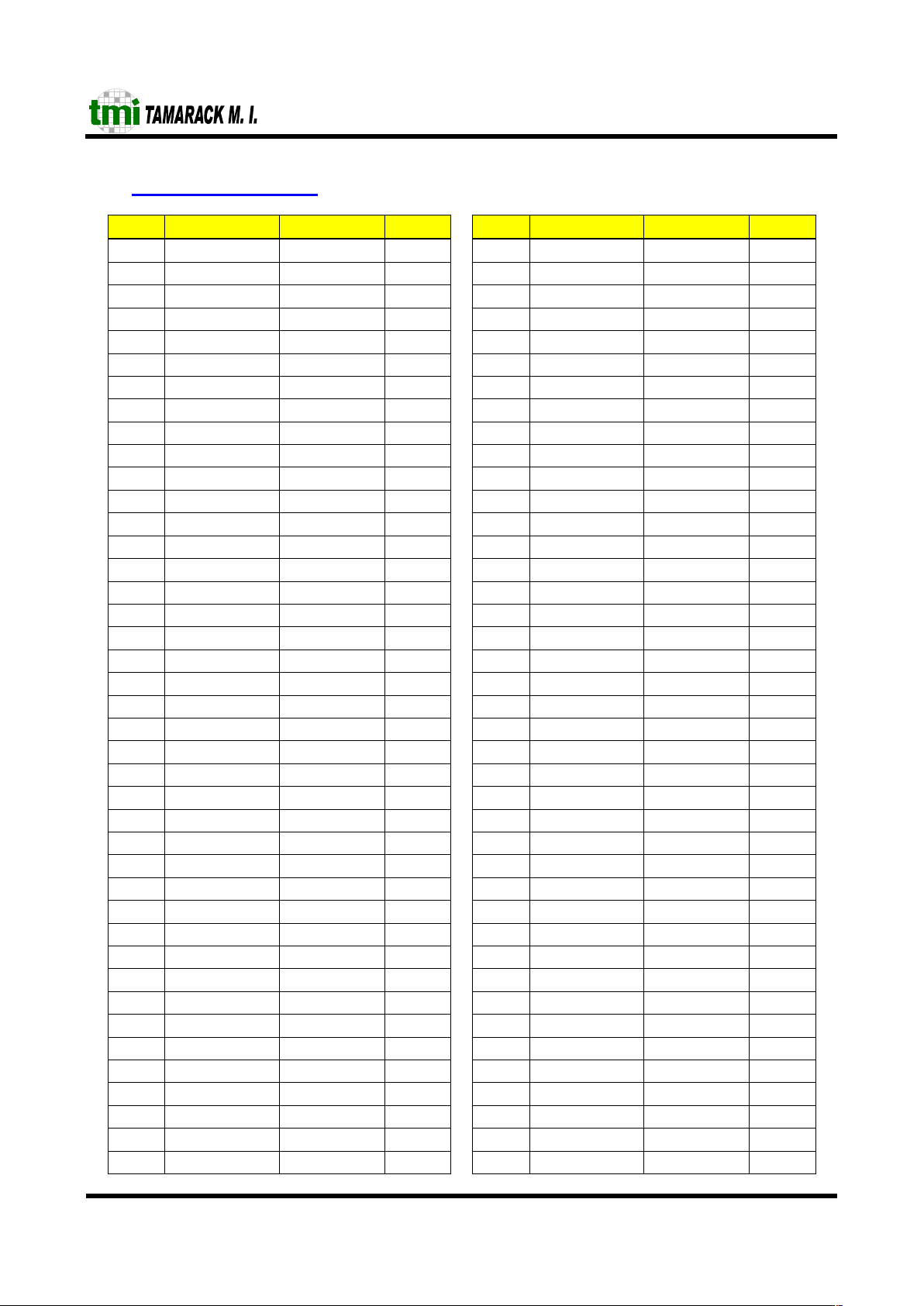

4 Pin Plcement

SDA

SCL

MIIMode

Vss_3.3V

RxClk

Vss_1.8V

RxDat153

RxDat152

RxDat151

RxDat150

Crs_Dv15

CRS15

Col15

Vdd_1.8V

TxClk

Vss_3.3V

TxDat153

TxDat152

TxDat151

TxDat150

TxEn15

Vdd_3.3V

RxDat141

RxDat140

Crs_Dv14

Vss_1.8V

TxDat141

TxDat140

TxEn14

Vdd_1.8V

RxDat131

RxDat130

Crs_Dv13

Vss_3.3V

TxDat131

TxDat130

TxEn13

Vdd_3.3V

RxDat121

RxDat120

Crs_Dv12

Vss_1.8V

TxDat121

TxDat120

TxEn12

Vdd_1.8V

RxDat111

RxDat110

Crs_Dv11

Vss_1.8V

TxDat111

TxDat110

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

Vss_3.3V 1 156 TxEn11

reset 2 155 Vdd_1.8V

TestMode 3 154 MDClk

Vdd_3.3V 4 153 MDIO

TnkA0 5 152 CLK75M

TnkA1 6 151 clk

Vdd_3.3V 7 150 Vdd_3.3V

TnkB0 8 149 refck

TnkB1 9 148 Vss_1.8V

Vss_1.8V 10 147 RxDat101

TnkMod0 11 146 RxDat100

Vss_3.3V 12 145 Crs_Dv10

TnkMod1 13 144 Vdd_1.8V

Vdd_1.8V 14 143 TxDat101

NC 15 142 TxDat100

PrtPri0 16 141 TxEn10

Vdd_3.3V 17 140 Vss_3.3V

PrtPri1 18 139 RxDat91

PrtPri2 19 138 RxDat90

Vss_1.8V 20 137 Crs_Dv9

PrtPri3 21 136 Vdd_3.3V

PrtPri4 22 135 TxDat91

Vss_3.3V 23 134 TxDat90

PrtPri5 24 133 TxEn9

PrtPri6 25 132 Vss_3.3V

Vdd_1.8V 26 131 RxDat81

PrtPri7 27 130 RxDat80

PriLev0 28 129 Crs_Dv8

Vdd_3.3V 29 128 Vdd_3.3V

PriLev1 30

127 TxDat81

PriLev2 31 126 TxDat80

Vss_1.8V 32 125 TxEn8

PriLev3 33 124 Vss_3.3V

PriLev4 34 123 RxDat71

Vdd_1.8V 35 122 RxDat70

PriLev5 36 121 Crs_Dv7

PriLev6 37 120 Vdd_1.8V

PriLev7 38 119 TxDat71

Vss_3.3V 39 118 TxDat70

Vdd_3.3V 40 117 TxEn7

EnIPPr 41 116 Vss_1.8V

EnVLPr 42 115 RxDat61

Vss_1.8V 43 114 RxDat60

FCBcstEn 44 113 Crs_Dv6

BcstAll 45 112 Vdd_1.8V

BcstTr 46 111 TxDat61

RejMCT 47 110 TxDat60

Vdd_1.8V 48 109 TxEn6

FcOpt 49 108 Vss_3.3V

Vdd_3.3V 50 107 RxDat51

DisBPBk 51 106 RxDat50

Vss_3.3V 52 105 Crs_Dv5

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

Vss_1.8V

DisBPr

FullBP

Vdd_1.8V

PowLED

OvBcLED

OVUnLED

Vss_3.3V

TxEn0

TxDat00

TxDat01

Vdd_3.3V

Crs_Dv0

RxDat00

RxDat01

Vss_3.3V

TxEn1

TxDat10

TxDat11

Vdd_1.8V

Crs_Dv1

RxDat10

RxDat11

Vss_1.8V

TxEn2

TxDat20

TxDat21

Vdd_1.8V

Crs_Dv2

RxDat20

RxDat21

Vss_1.8V

TxEn3

TxDat30

TxDat31

Vdd_1.8V

Crs_Dv3

RxDat30

RxDat31

Vss_1.8V

TxEn4

TxDat40

TxDat41

Vdd_3.3V

Crs_Dv4

RxDat40

RxDat41

Vss_3.3V

TxEn5

TxDat50

TxDat51

Vdd_3.3V

TC6216M

PQFP 208

Top View

TC6216M

- 6 -

Ver. 2.1

5/24/01

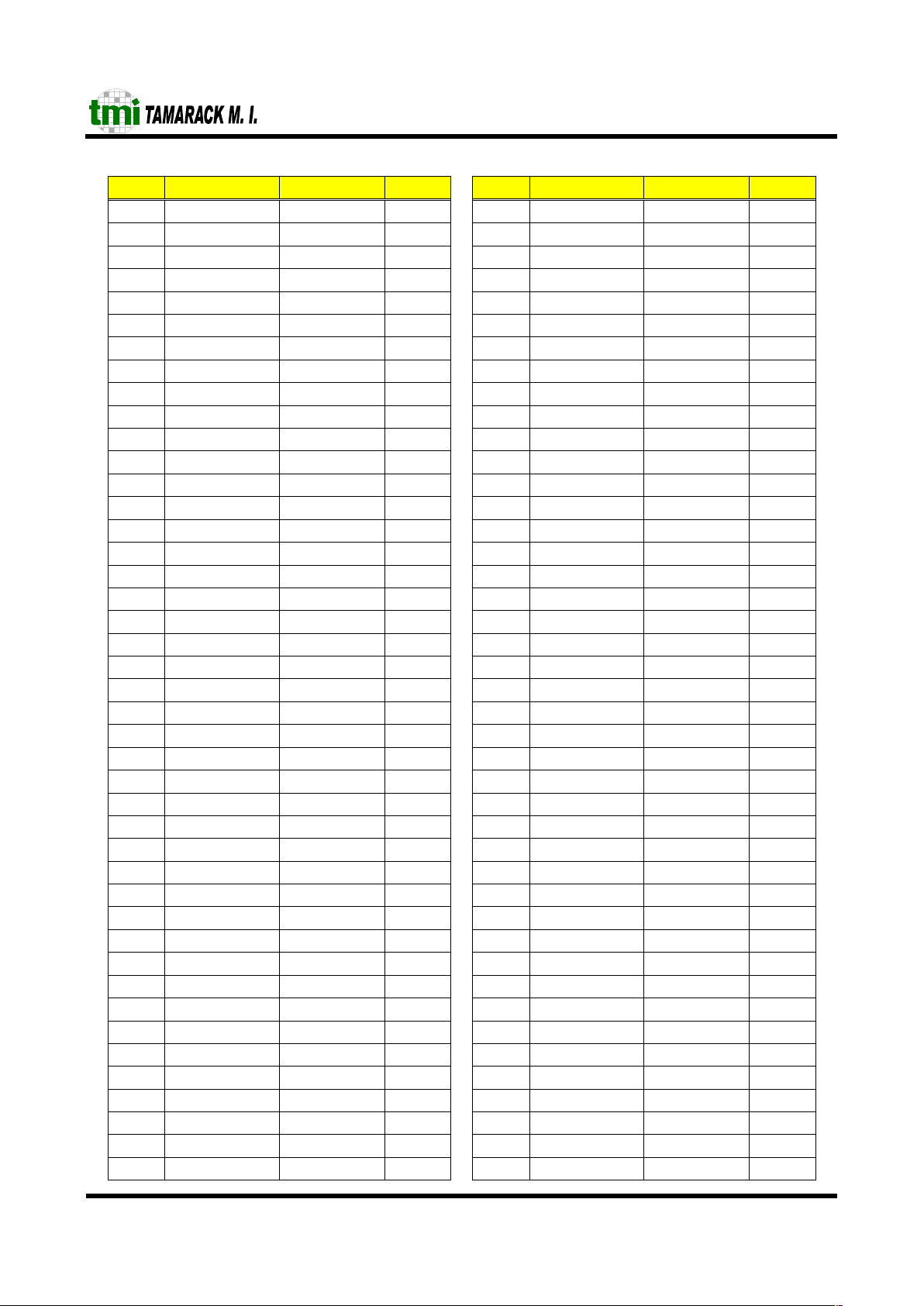

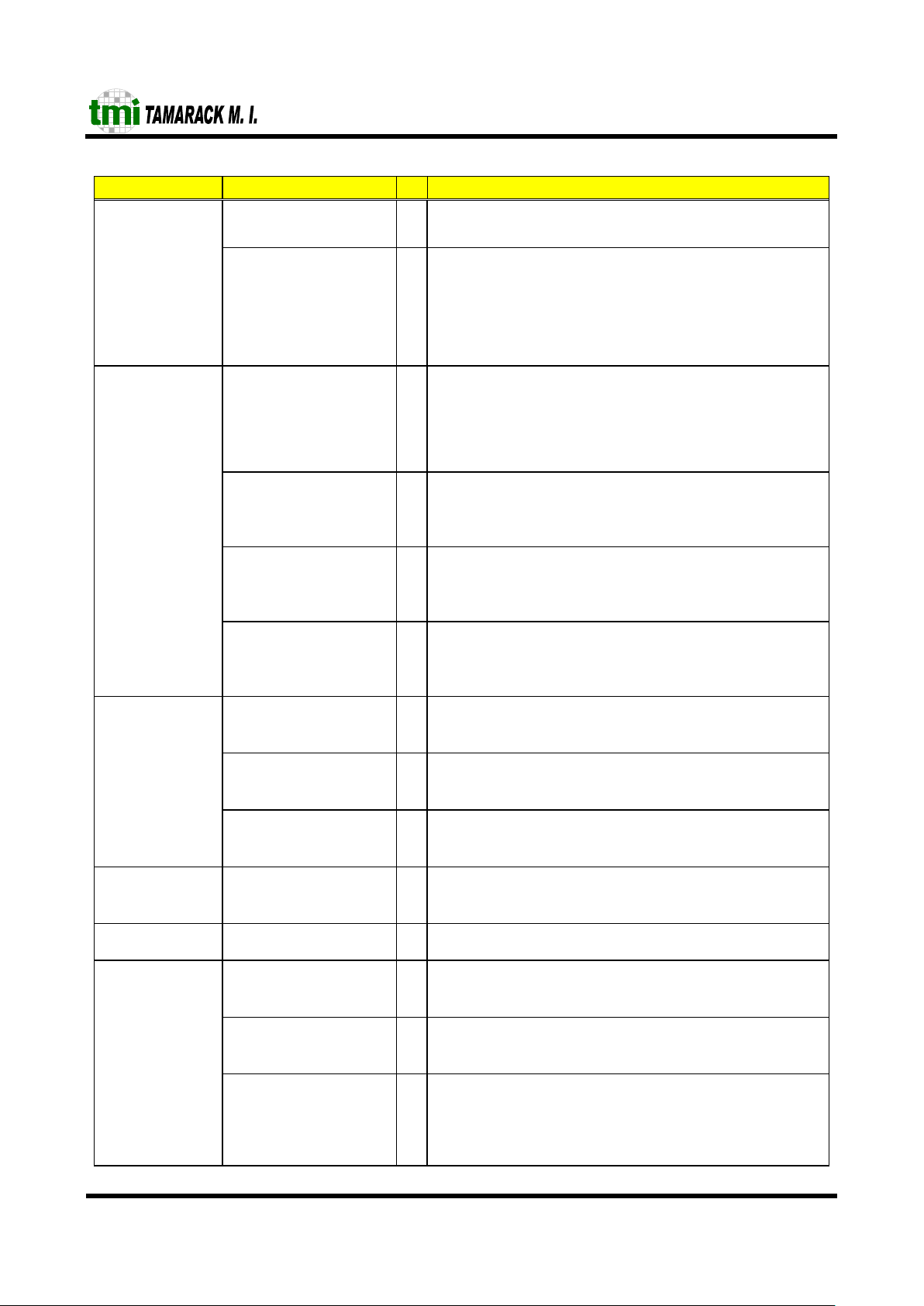

5 Pin Listing (PQFP 208)

Pin Description Pin label Type Pin Description Pin label Type

1 Power Vss_3.3V ~ 105 RMII Crs_Dv5 I

2 Reset reset Ipu 106 RMII RxDat50 I

3 Configuration TestMode Ipd 107 RMII RxDat51 I

4 Power Vdd_3.3V ~ 108 Power Vss_3.3V ~

5 Configuration TnkA0 Ipd 109 RMII TxEn6 O

6 Configuration TnkA1 Ipd 110 RMII TxDat60 O

7 Power Vdd_3.3V ~ 111 RMII TxDat61 O

8 Configuration TnkB0 Ipd 112 Power Vdd_1.8V ~

9 Configuration TnkB1 Ipd 113 RMII Crs_Dv6 I

10 Power Vss_1.8V ~ 114 RMII RxDat60 I

11 Configuration TnkMod0 Ipd 115 RMII RxDat61 I

12 Power Vss_3.3V ~ 116 Power Vss_1.8V ~

13 Configuration TnkMod1 Ipd 117 RMII TxEn7 O

14 Power Vdd_1.8V ~ 118 RMII TxDat70 O

15 NC NC ~ 119 RMII TxDat71 O

16 Configuration PrtPri0 Ipd 120 Power Vdd_1.8V ~

17 Power Vdd_3.3V ~ 121 RMII Crs_Dv7 I

18 Configuration PrtPri1 Ipd 122 RMII RxDat70 I

19 Configuration Prtpri2 Ipd 123 RMII RxDat71 I

20 Power Vss_1.8V ~ 124 Power Vss_3.3V ~

21 Configuration PrtPri3 Ipd 125 RMII TxEn8 O

22 Configuration PrtPri4 Ipd 126 RMII TxDat80 O

23 Power Vss_3.3V ~ 127 RMII TxDat81 O

24 Configuration PrtPri5 Ipd 128 Power Vdd_3.3V ~

25 Configuration PrtPri6 Ipd 129 RMII Crs_Dv8 I

26 Power Vdd_1.8V ~ 130 RMII RxDat80 I

27 Configuration PrtPri7 Ipd 131 RMII RxDat81 I

28 Configuration PriLev0 Ipd 132 Power Vss_3.3V ~

29 Power Vdd_3.3V ~ 133 RMII TxEn9 O

30 Configuration PriLev1 Ipd 134 RMII TxDat90 O

31 Configuration PriLev2 Ipd 135 RMII TxDat91 O

32 Power Vss_1.8V ~ 136 Power Vdd_3.3V ~

33 Configuration PriLev3 Ipd 137 RMII Crs_Dv9 I

34 Configuration PriLev4 Ipd 138 RMII RxDat90 I

35 Power Vdd_1.8V ~ 139 RMII RxDat91 I

36 Configuration PriLev5 Ipd 140 Power Vss_3.3V ~

37 Configuration PriLev6 Ipd 141 RMII TxEn10 O

38 Configuration PriLev7 Ipd 142 RMII TxDat100 O

39 Power Vss_3.3V ~ 143 RMII TxDat101 O

40 Power Vdd_3.3V ~ 144 Power Vdd_1.8V ~

41 Configuration EnIPPr Ipd 145 RMII Crs_Dv10 I

TC6216M

- 7 -

Ver. 2.1

5/24/01

Pin Description Pin label Type Pin Description Pin label Type

42 Configuration EnVLPr Ipd 146 RMII RxDat100 I

43 Power Vss_1.8V ~ 147 RMII RxDat101 I

44 Configuration FCBcstEn Ipu 148 Power Vss_1.8V ~

45 Configuration BcstAll Ipu 149 CLK refck I

46 Configuration BcstTr Ipd 150 Power Vdd_3.3V ~

47 Configuration RejMCT Ipu 151 CLK clk I

48 Power Vdd_1.8V ~ 152 CLK CLK75M O

49 Configuration FcOpt Ipu 153 MDIO MDIO I/Opu

50 Power Vdd_3.3V ~ 154 MDIO MDClk O

51 Configuration DisBPBk Ipd 155 Power Vdd_1.8V ~

52 Power Vss_3.3V ~ 156 RMII TxEn11 O

53 Power Vss_1.8V ~ 157 RMII TxDat110 O

54 Configuration DisBPr Ipd 158 RMII TxDat111 O

55 Configuration FullBP Ipd 159 Power Vss_1.8V ~

56 Power Vdd_1.8V ~ 160 RMII Crs_Dv11 I

57 LED PowLED OL 161 RMII RxDat110 I

58 LED OvBcLED OL 162 RMII RxDat111 I

59 LED OvUnLED OL 163 Power Vdd_1.8V ~

60 Power Vss_3.3V ~ 164 RMII TxEn12 O

61 RMII TxEn0 O 165 RMII TxDat120 O

62 RMII TxDat00 O 166 RMII TxDat121 O

63 RMII TxDat01 O 167 Power Vss_1.8V ~

64 Power Vdd_3.3V ~ 168 RMII Crs_Dv12 I

65 RMII Crs_Dv0 I 169 RMII RxDat120 I

66 RMII RxDat00 I 170 RMII RxDat121 I

67 RMII RxDat01 I 171 Power Vdd_3.3V ~

68 Power Vss_3.3V ~ 172 RMII TxEn13 O

69 RMII TxEn1 O 173 RMII TxDat130 O

70 RMII TxDat10 O 174 RMII TxDat131 O

71 RMII TxDat11 O 175 Power Vss_3.3V ~

72 Power Vdd_1.8V ~ 176 RMII Crs_Dv13 I

73 RMII Crs_Dv1 I 177 RMII RxDat130 I

74 RMII RxDat10 I 178 RMII RxDat131 I

75 RMII RxDat11 I 179 Power Vdd_1.8V ~

76 Power Vss_1.8V ~ 180 RMII TxEn14 O

77 RMII TxEn2 O 181 RMII TxDat140 O

78 RMII TxDat20 O 182 RMII TxDat141 O

79 RMII TxDat21 O 183 Power Vss_1.8V ~

80 Power Vdd_1.8V ~ 184 RMII Crs_Dv14 I

81 RMII Crs_Dv2 I 185 RMII RxDat140 I

82 RMII RxDat20 I 186 RMII RxDat141 I

83 RMII RxDat21 I 187 Power Vdd_3.3V ~

84 Power Vss_1.8V ~ 188 (R)MII TxEn15 O

TC6216M

- 8 -

Ver. 2.1

5/24/01

Pin Description Pin label Type Pin Description Pin label Type

85 RMII TxEn3 O 189 (R)MII TxDat150 O

86 RMII TxDat30 O 190 (R)MII TxDat151 O

87 RMII TxDat31 O 191 (R)MII TxDat152 O

88 Power Vdd_1.8V ~ 192 (R)MII TxDat153 O

89 RMII Crs_Dv3 I 193 Power Vss_3.3V ~

90 RMII RxDat30 I 194 CLK TxClk I

91 RMII RxDat31 I 195 Power Vdd_1.8V ~

92 Power Vss_1.8V ~ 196 (R)MII Col15 I

93 RMII TxEn4 O 197 (R)MII Crs15 I

94 RMII TxDat40 O 198 (R)MII Crs_Dv15 I

95 RMII TxDat41 O 199 (R)MII RxDat150 I

96 Power Vdd_3.3V ~ 200 (R)MII RxDat151 I

97 RMII Crs_Dv4 I 201 (R)MII RxDat152 I

98 RMII RxDat40 I 202 (R)MII RxDat153 I

99 RMII RxDat41 I 203 Power Vss_1.8V ~

100 Power Vss_3.3V ~ 204 CLK RxClk I

101 RMII TxEn5 O 205 Power Vss_3.3V ~

102 RMII TxDat50 O 206 Configuration MIIMode Ipd

103 RMII TxDat51 O 207 EEPROM SCL O

104 Power Vdd_3.3V ~ 208 EEPROM SDA I/Opu

I ⇒ digital input

I

pd

⇒ digital input internally pulled down

I

pu

⇒ digital input internally pulled up

O ⇒ digital output

O

L

⇒ digital output active low

I/O

pu

⇒ digital bidirectional internally pulled up

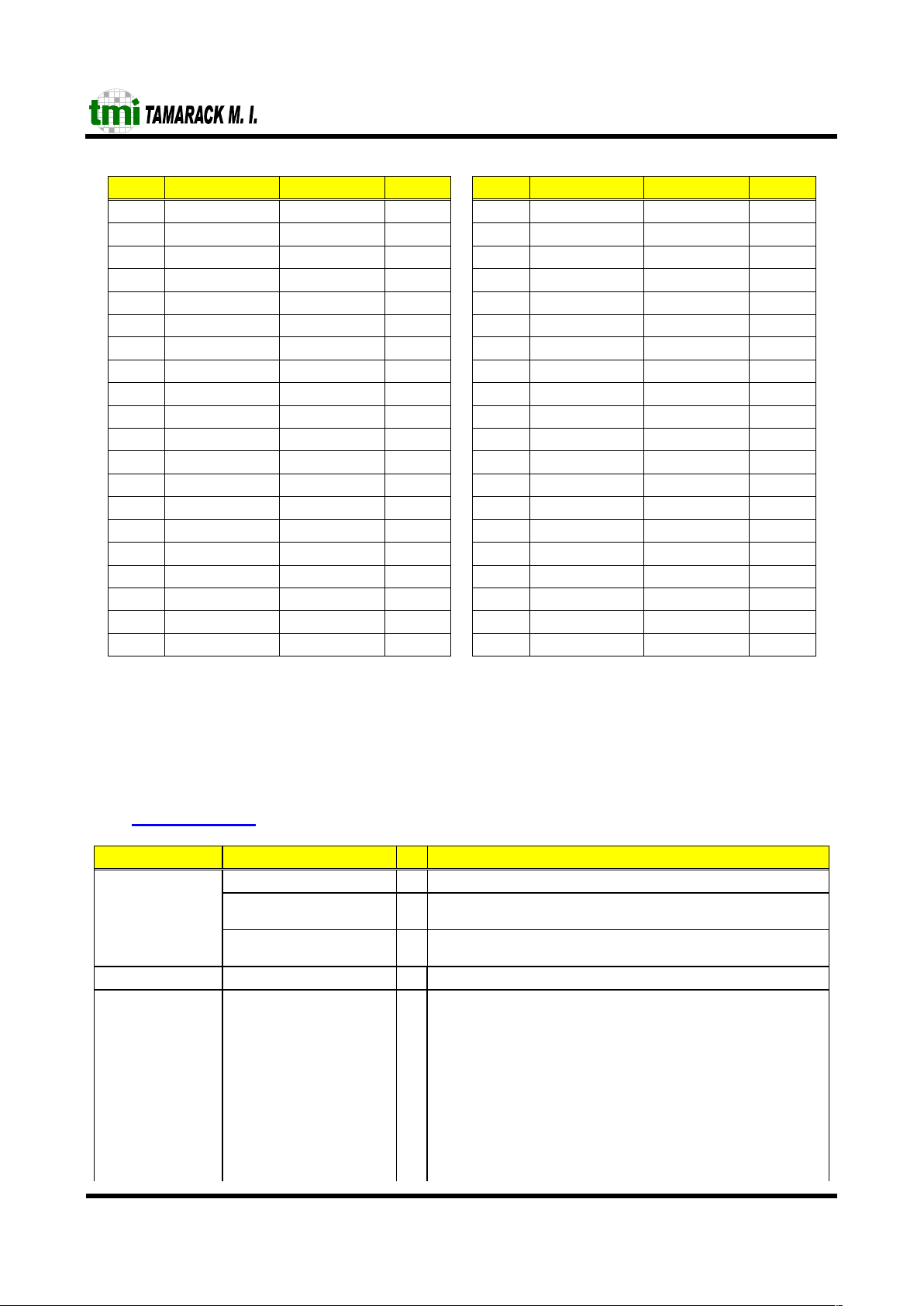

6 Pin Description

Interface Signal I/O Signal Description

reset I General reset.

Clk I System clock. The switch performance is full wire speed at

50Mhz system clock freq uency.

Control/Clock

Clk75M O Output clock from internal PLL. For 75MHz system clock

frequenc y tie this to system clock pin.

Test TestMode I

If set to ′1′ the chip will be in Memory Test Mode.

Trunking TnkA(0:1)

TnkB(0:1)

I Trunking configuration.

•

First trunk channel

TnkA1 TnkA0

0 0 No port is configured as trunk port

0 1 Ports 0 and 1 are configured as trunk ports

1 0 Ports 0,1,2 are configured as trunk ports

1 1 Ports 0,1,2 and 3 are configured as trunk ports

•

Second trunk channel

TnkB1 TnkB0

0 0 No port is configured as trunk port

0 1 Ports 15 and 14 are configured as trunk ports

1 0 Ports 15, 14 , 13 are configu r ed as trunk ports

TC6216M

- 9 -

Ver. 2.1

5/24/01

Interface Signal I/O Signal Description

1 1 Ports 15, 14 , 13 and 12 are configured as trunk

ports

TnkMod(0:1) I Trunk Balance Mode Select

TnkMod1 TnkMod0

0 0 Only source port is used to select the transmission port

inside the trunk.

0 1 Transmission port is selected using SA.

1 0 Transmission port is selected using SA and DA.

1 1 Not used

PrtPri (0:7) I Indicates which ports, if any, are in Priority Mode; when

selected the corresponding port will have high or very high

priority depending of the state of PriLev pin.

PrtPri(0:7) are used to set the priorities for por ts 4 to 11.

TC6216M Port (4 to 11) ! PrtPri (0:7)

PriLev (0:7) I Selects the high or very high priority for priority ports.

′1′ – Very high priority

′0′ – High priority

PriLev (0:7) refers to TC6216M ports 4 to 11.

EnIPPr I Enables QoS resolution to consider TOS Precedence bits from

IP Header.

′1′ – IP priority will be considered

′0′ – IP priority will be neglected

QoS configuration

EnVLPr I Enables QoS resolution to consider user_prio r ity bits (TCI

field) from 802.1Q VLAN Tag Header.

′1′ – VLAN priority will be considered

′0′ – VLAN priority will be neglected

FcBcstEn I Enables Flow Control for Broadcast operation.

′1′ – Enable

′0′ – Disable

BcstAll I Br oadcast All Mode Select

′1′– forward broadcast packes to all the ports

′0′– forward broadcast packes to active ports only

Broadcast

configuration

BcstTr I Enables br oadcast throttling.

′1′– Enable

′0′– Disable

MII Mode

Selection

MIIMode I Select MII or RMII interface for port 15

′0′– RMII

′1′– MII

MAC

Configuration

RejMCT I All Mac Control Type Packets will be rejected if this pin is

asserted, otherwise they will be forwarded.

FCOpt I Flow Control resolution option:

′1′- the A-NEG result is considered

′0′– doesn't matter the A-NEG result

DisBPr I Enable / Disable Flow Control for Half Duplex Mode

′1′– Disable

′0′– Enable

Flow Control

FullBP I

When this is set to ′0′ then the backpressure process will be

stopped after reaching 30 consecutive collisions. The default

value (30) can be changed by EEPROM settings. Otherwise the

backpressure can be executed for up to 2048 (default pause

value) slot times if the flow control condition persists.

Loading...

Loading...